Изобретение относится к области радиотехники и связи и может быть использовано в качестве буферного усилителя аналоговых микросхем различного функционального назначения (например, повторителях сигналов с высоким КПД и повышенным петлевым усилением, драйверов линий связи и т.п.).

Известны схемы буферных усилителей (БУ) на основе операционных усилителей со 100%-ной обратной связью, которые стали основой многих серийных изделий, выпускаемых как зарубежными, так и российскими микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры БУ на их модификации выдано более 15 патентов [1-17]. Предлагаемое изобретение относится к данному подклассу устройств.

Ближайшим прототипом заявляемого устройства является выходной буферный усилитель в структуре микросхемы LF155 фирмы National Semiconductor, опубликованный в справочнике «Операционные усилители и компараторы» (М.: Издательский дом «Додэка-XXI», 2001, с.149) [1], содержащий входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, выходной составной транзистор 4, база 5 которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, а эмиттер 6 связан с выходом 7 устройства, дифференциальную цепь согласования потенциалов 8, имеющую неинвертирующий 9 и инвертирующий 10 входы, выходной инвертирующий каскад усиления 11, вход которого 12 связан с выходом 13 дифференциальной цепи согласования потенциалов 8, а выход 14 подключен к выходу устройства 7, первый 15 токостабилизирующий двухполюсник, связанный с первым 2 токовым выходом входного дифференциального каскада 1, второй токостабилизирующий двухполюсник 16.

Существенный недостаток известного устройства состоит в том, что он характеризуется сравнительно небольшим петлевым усилением, что отрицательно сказывается на его динамических параметрах - выходном сопротивлении с обратной связью, динамической ошибке передачи сигнала [2]. Кроме этого он имеет повышенное напряжение смещения нуля и т.п.

Основная цель предлагаемого изобретения состоит в создании условий для повышения коэффициента усиления БУ по напряжению без обратной связи (Ku). Это позволяет снизить погрешности передачи, связанные с величиной петлевого усиления [2].

Поставленная цель достигается тем, что в известном двухтактном буферном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, выходной составной транзистор 4, база 5 которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, а эмиттер 6 связан с выходом 7 устройства, дифференциальную цепь согласования потенциалов 8, имеющую неинвертирующий 9 и инвертирующий 10 входы, выходной инвертирующий каскад усиления 11, вход которого 12 связан с выходом 13 дифференциальной цепи согласования потенциалов 8, а выход 14 подключен к выходу устройства 7, первый 15 токостабилизирующий двухполюсник, связанный с первым 2 токовым выходом входного дифференциального каскада 1, второй токостабилизирующий двухполюсник 16, предусмотрены новые элементы и связи - неинвертирующий вход 9 дифференциальной цепи согласования потенциалов 8 соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и вторым 16 токостабилизирующим двухполюсником, а инвертирующий вход 10 дифференциальной цепи согласования потенциалов 8 связан с выходом 7 устройства.

На фиг.1 показана схема БУ-прототипа.

На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

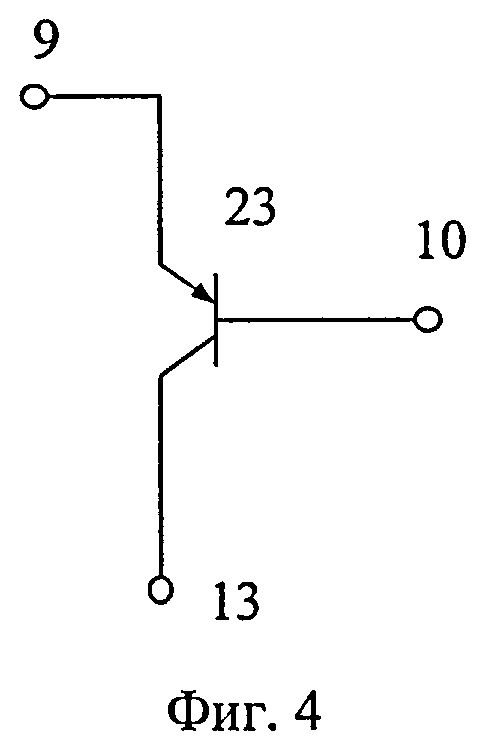

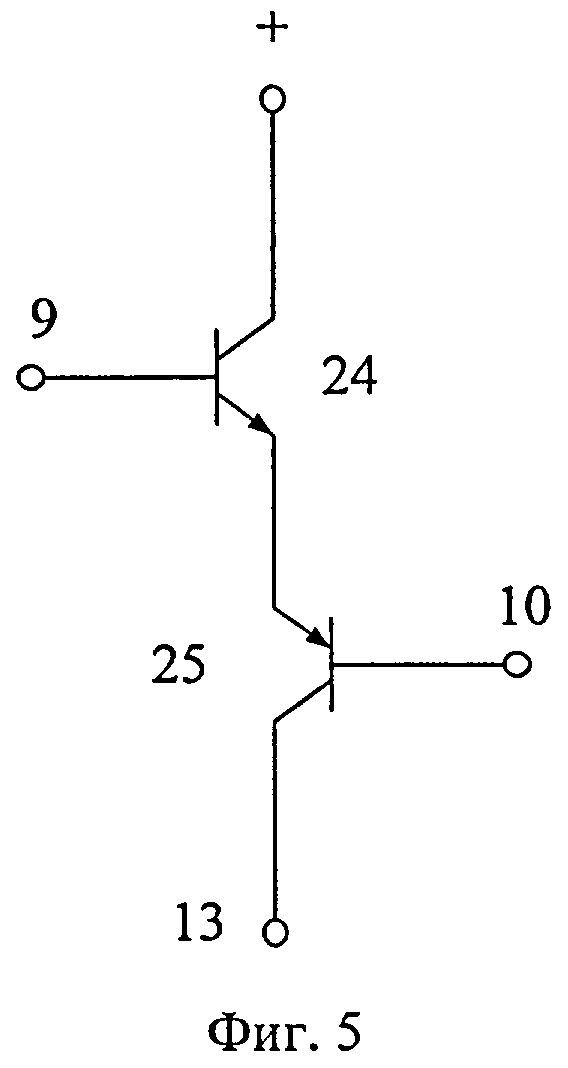

На фиг.3-5 показаны частные случаи выполнения дифференциальной цепи согласования потенциалов 8.

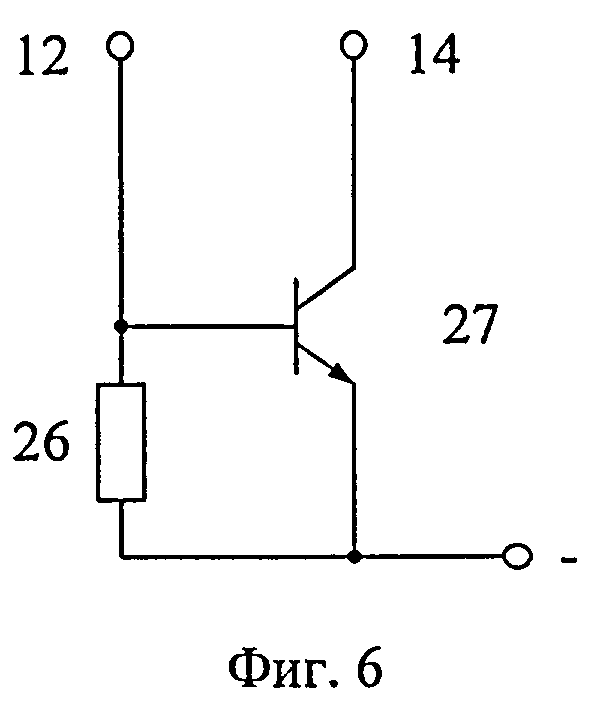

На фиг.6 и фиг.7 показаны варианты построения выходного инвертирующего каскада 11.

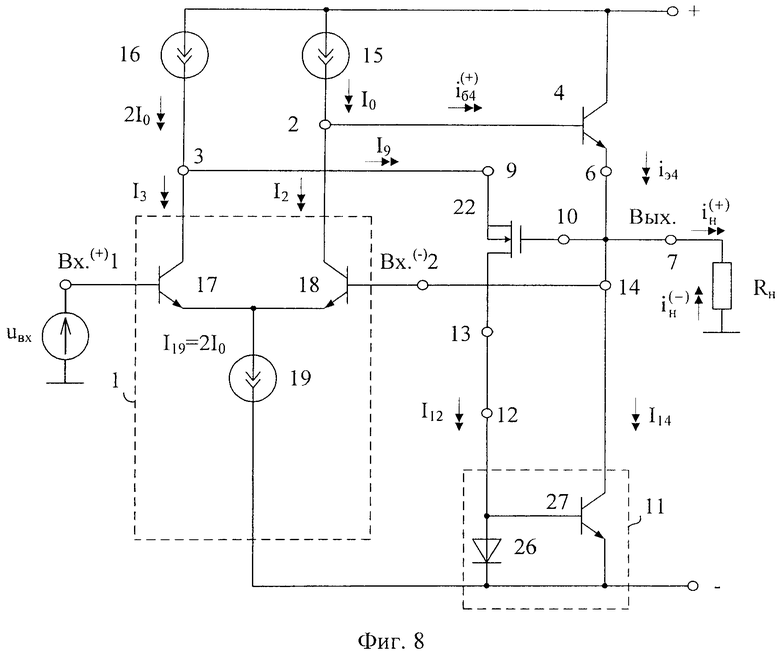

На фиг.8 показана схема фиг.3 для случая, когда дифференциальная цепь согласования потенциалов 8 реализована на полевом транзисторе 22.

На фиг.9 показана схема фиг.4 для случая, когда дифференциальная цепь согласования потенциалов 8 реализована на биполярном транзисторе 23, а между выходом 14 выходного неинвертирующего каскада усиления 11 и выходом устройства 7 в соответствии с п.2 формулы изобретения включен дополнительный двухполюсник 33.

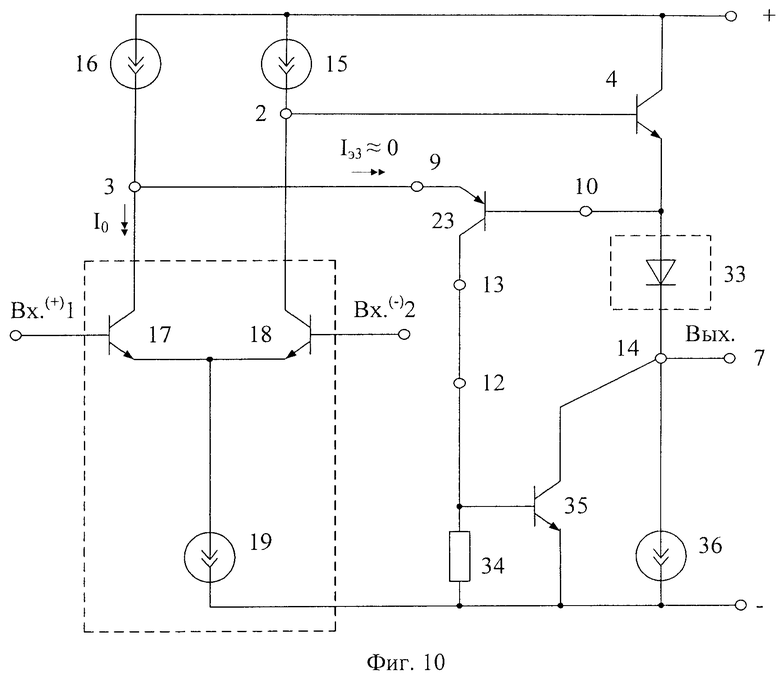

На фиг.10 показана схема фиг.4 для случая, когда дифференциальная цепь согласования потенциалов 8 реализована на биполярном транзисторе 23, а выходной неинвертирующий каскада усиления 11 выполнен на транзисторе 35, резисторе 34 и источнике тока 36.

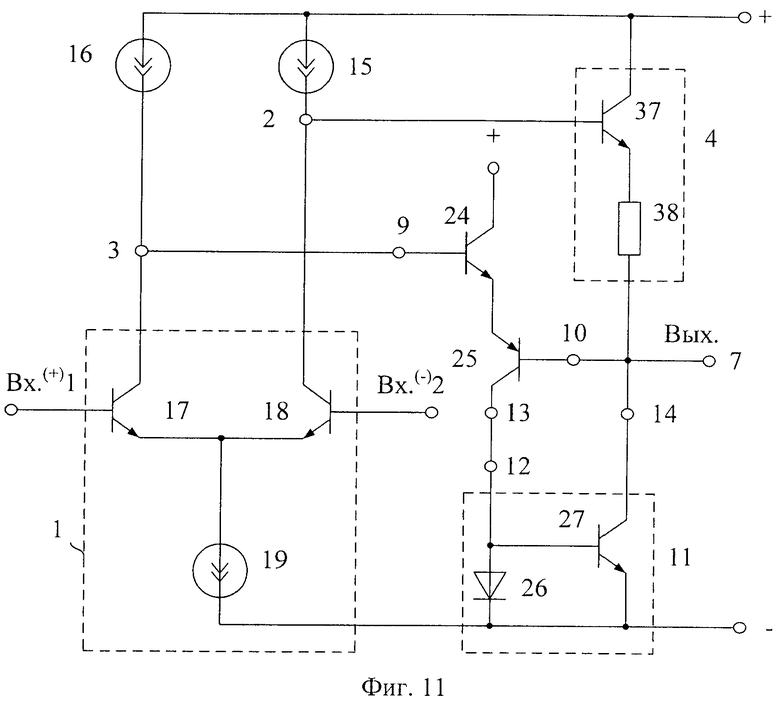

На фиг.11 показана схема фиг.5 для случая, когда дифференциальная цепь согласования потенциалов 8 реализована на биполярных транзисторах 24 и 25, а выходной составной транзистор 4 содержит биполярный транзистор 37 и вспомогательный резистор 38.

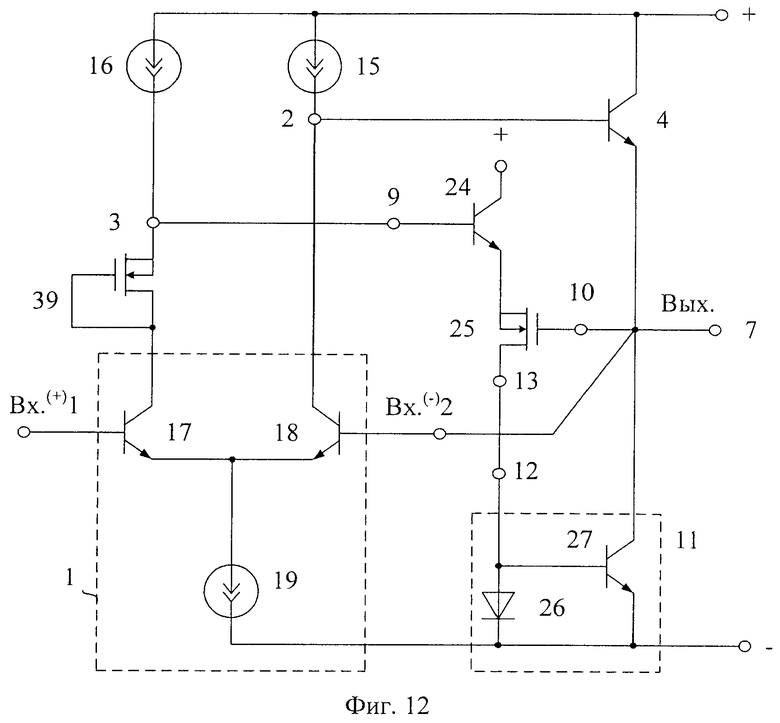

На фиг.12 показана схема фиг.5 для случая, когда дифференциальная цепь согласования потенциалов 8 выполнена на биполярном транзисторе 24 и полевом транзисторе 25.

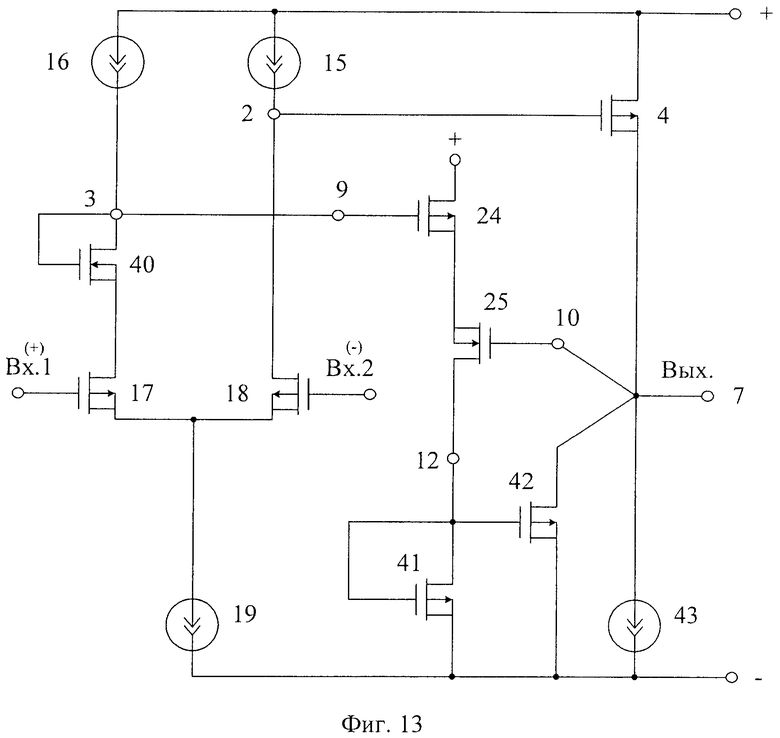

На фиг.13 показана схема фиг.5 для случая, когда все активные элементы схемы реализованы на полевых транзисторах.

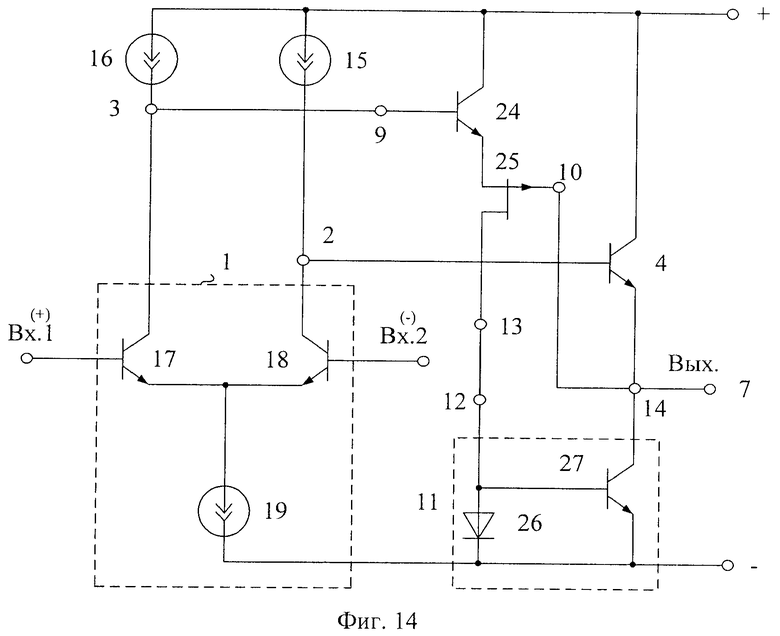

На фиг.14 показана схема фиг.5 для случая, когда дифференциальная цепь согласования потенциалов 8 выполнена на биполярном транзисторе 24 и полевом транзисторе 25 с управляющим p-n переходом.

На фиг.15 показана схема фиг.5 для случая, когда дифференциальная цепь согласования потенциалов 8 выполнена на биполярных транзисторах 24, 25, а выходной составной транзистор 4 реализован на биполярных транзисторах 44 и 45.

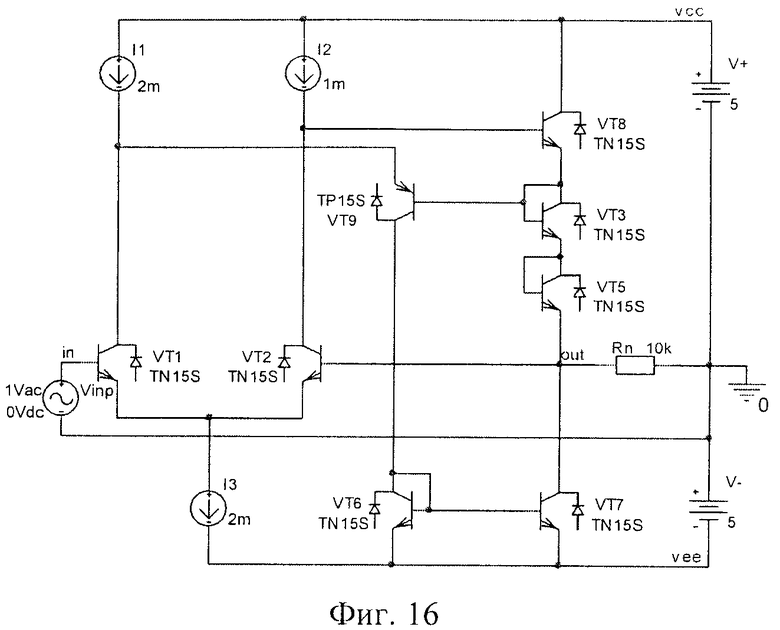

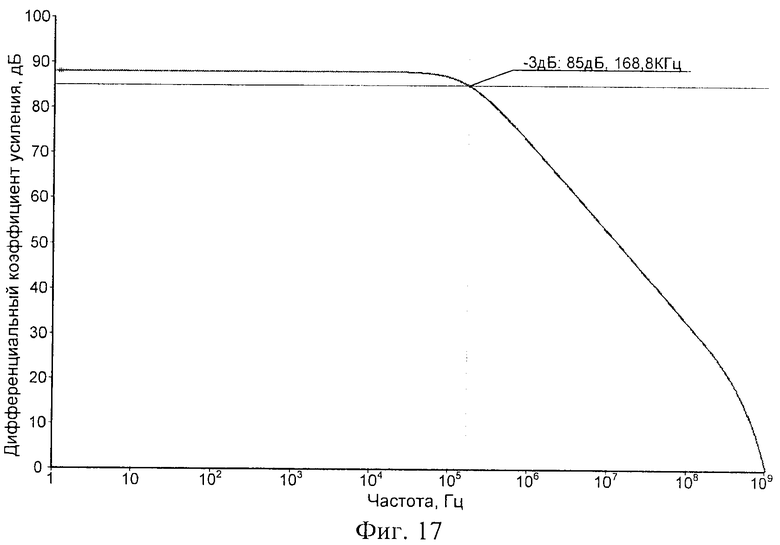

На фиг.16 приведена схема БУ фиг.9 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.17 - зависимость ее коэффициента усиления без обратной связи от частоты.

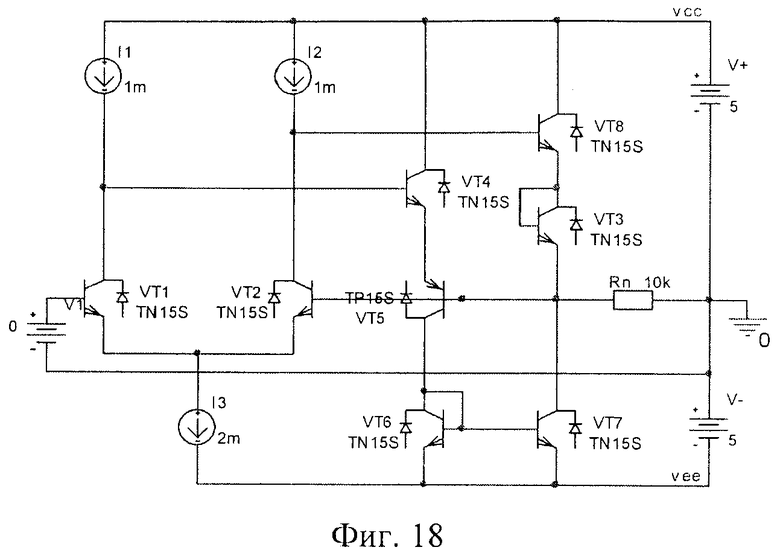

На фиг.18 приведена схема БУ фиг.11 в среде компьютерного моделирования PSpice па моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.19 - его проходная характеристика - зависимость выходного тока от входного напряжения БУ с обратной связью при сопротивлении нагрузки 50 Ом. Данный график показывает, что предлагаемый БУ обеспечивает ток нагрузки ±25 мА, работает в режиме класса АВ и характеризуется сравнительно высоким КПД.

Двухтактный буферный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, выходной составной транзистор 4, база 5 которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, а эмиттер 6 связан с выходом 7 устройства, дифференциальную цепь согласования потенциалов 8, имеющую неинвертирующий 9 и инвертирующий 10 входы, выходной инвертирующий каскад усиления 11, вход которого 12 связан с выходом 13 дифференциальной цепи согласования потенциалов 8, а выход 14 подключен к выходу устройства 7, первый 15 токостабилизирующий двухполюсник, связанный с первым 2 токовым выходом входного дифференциального каскада 1, второй токостабилизирующий двухполюсник 16. Неинвертирующий вход 9 дифференциальной цепи согласования потенциалов 8 соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и вторым 16 токостабилизирующим двухполюсником, а инвертирующий вход 10 дифференциальной цепи согласования потенциалов 8 связан с выходом 7 устройства.

На фиг.9 в соответствии с п.2 формулы изобретения выход 14 выходного инвертирующего каскада усиления 11 подключен к выходу устройства 7 через цепь согласования потенциалов 33 и связан с дополнительным выходом устройства.

На фиг.2 входной дифференциальный каскад 1 реализован на транзисторах 17 и 18 и источнике тока 19. В частном случае выходной неинвертирующий каскад выполнен на базе двухполюсника 20 и транзисторе 21.

В схемах фиг.3-5 дифференциальная цепь согласования потенциалов реализована на транзисторах 22 (фиг.3), 23 (фиг.4), 24, 25 (фиг.5).

В частных случаях выходной неинвертирующий каскад может быть реализован на основе двухполюсника 26, транзистора 27 (фиг.6) или на транзисторе 28 и резисторах 29, 30, 31 и p-n переходе 32 (фиг.7).

Обозначения схемы фиг.8 соответствуют обозначениям фиг.3.

Обозначения элементов схемы фиг.9 соответствуют обозначениям элементов фиг.4. Однако здесь в соответствии с п.2 формулы изобретения введена цепь согласования потенциалов 33.

На фиг.10 выходной инвертирующий усилитель 11 реализован на основе двухполюсников 34, 35, 36, а также транзисторе 35.

В схеме фиг.11 выходной составной транзистор содержит биполярный транзистор 37 и резистор 38.

В схеме фиг.12 введен элемент согласования потенциалов 39.

На фиг.13 также введен элемент согласования потенциалов 40. Выходной инвертирующий усилитель 11 реализован здесь на транзисторах 41, 42 и двухполюснике 43.

На фиг.14 показана схема фиг.5 для случая, когда дифференциальная цепь согласования потенциалов 8 выполнена на биполярном транзисторе 24 и полевом транзисторе 25 с управляющим p-n переходом.

На фиг.15 выходной составной транзистор 4 выполнен на базе биполярных транзисторов 44, 45.

Рассмотрим работу одного из вариантов построения заявляемого устройства (например, фиг.8).

В статическом режиме, когда uвх=0, в схеме фиг.8 устанавливаются следующие токи:

При этом ток в нагрузке Rн равен нулю.

При положительном приращении входного сигнала (uвх>0) коллекторный ток транзистора 17 дифференциального каскада 1 увеличивается, а транзистора 18 - уменьшается. Это вызывает уменьшение тока истока полевого транзистора 22 и, следовательно, запирание выходного усилителя 11. С другой стороны, уменьшение I2 вызывает увеличение тока базы транзистора 4  и, следовательно, тока

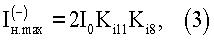

и, следовательно, тока  в нагрузке Rн. При этом максимальный положительный ток в нагрузке Rн может достигать значений

в нагрузке Rн. При этом максимальный положительный ток в нагрузке Rн может достигать значений

Если входное напряжение принимает отрицательное значение (uвх<0), то транзистор 4 запирается, а отрицательное приращение тока в нагрузке создается каскадом 11:

где Ki11 (Ki8) - коэффициент усиления по току каскада 11 (цепи согласования 8).

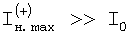

В рассматриваемой схеме фиг.8 коэффициенты усиления по току Ki11=1, Ki8=1. Однако при построении данных функциональных узлов (8, 11) в соответствии фиг.5 (Ki8>>1) и фиг.6, фиг.7 (Ki11>>1) в нагрузке Rн можно получить максимальные токи  , соответствующие

, соответствующие  (см. фиг.11-12).

(см. фиг.11-12).

Таким образом, заявляемый усилитель работает в режиме класса АВ, т.е. отличается достаточно высоким КПД.

Рассмотрим далее работу схемы фиг.8 на переменном токе.

Введение новых элементов в соответствии с формулой изобретения повышает коэффициент усиления по напряжению в схеме без обратной связи.

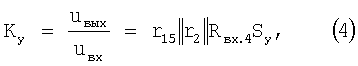

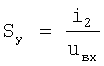

Действительно, замечательной особенностью предлагаемого усилителя является повышение (более чем на порядок) коэффициента усиления БУ по напряжению Kу без обратной связи. Для БУ-прототипа фиг.1

где r15 - выходное сопротивление двухполюсника 15;

r2 - выходное сопротивление дифференциального каскада 1 относительно выхода 2;

Rвх.4 - эквивалентное сопротивление нагрузки Rн, приведенное к узлу «А»(Rвх.4=β4Rн);

- крутизна входного дифференциального каскада 1, зависящая от сопротивлений эмиттерных переходов транзисторов 17 и 18 (rэ17, rэ18);

- крутизна входного дифференциального каскада 1, зависящая от сопротивлений эмиттерных переходов транзисторов 17 и 18 (rэ17, rэ18);

;

;

β4 - коэффициент усиления тока базы транзистора 4.

В связи с тем, что β4>50 при Rн≥1 кОм эквивалентное сопротивление Rэкв в узле «А» определяется транзисторами 17 и 18:

где µ18≈10-3 - коэффициент внутренней обратной связи транзистора 18.

Поэтому численные значения предельного коэффициента усиления БУ (фиг.1) по напряжению

В предлагаемом устройстве (фиг.2-5) максимально возможный коэффициент усиления  Поэтому за счет минимизации влияния статического режима на разность коэффициентов внутренней обратной связи µ17 - µ18 транзисторов 17 и 18 коэффициент усиления по напряжению Kу схемы фиг.8 возрастает и достигает величины порядка 100 дБ (фиг.17). Повышение Kу и, как следствие, петлевого усиления оказывает положительное влияние на ряд динамических параметров буферного усилителя [2].

Поэтому за счет минимизации влияния статического режима на разность коэффициентов внутренней обратной связи µ17 - µ18 транзисторов 17 и 18 коэффициент усиления по напряжению Kу схемы фиг.8 возрастает и достигает величины порядка 100 дБ (фиг.17). Повышение Kу и, как следствие, петлевого усиления оказывает положительное влияние на ряд динамических параметров буферного усилителя [2].

Таким образом, предлагаемое техническое решение характеризуется более высокими качественными показателями, что позволяет рекомендовать его для применения в архитектуре различных аналоговых интерфейсов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Операционные усилители и компараторы [Текст]. - М.: Издательский дом «Додэка-XXI», 2001, с.149, операционные усилители LF155, рис.1.

2. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - 148 с.

3. Патент США №4164716.

4. Патент США №4163908.

5. Патент США №4454479.

6. Патент США №4409561.

7. Патент США №4403200.

8. Патент США №4538116.

9. Патент США №4709216.

10. Патент WO 03/043185.

11. Патент США №6670851.

12. Патент США №6636117.

13. Патент США №5327100.

14. Патент США №6424220.

15. Патент США №6417733.

16. Патент США №6292057.

17. Патент США №6114904.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2420861C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321159C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2310268C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346388C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| ВЫХОДНОЙ КАСКАД BIJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668981C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450425C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве буферного усилителя аналоговых микросхем различного функционального назначения (например, повторителях сигналов с высоким КПД и повышенным петлевым усилением, драйверов линий связи и т.п.). Технический результат: повышение коэффициента усиления по напряжению и снижение погрешности передачи. Двухтактный буферный усилитель (ДБУ) содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, выходной составной транзистор (4), база (5) которого соединена с первым (2) токовым выходом ДК (1), а эмиттер (6) связан с выходом (7) ДБУ, дифференциальную цепь согласования потенциалов (ДЦ) (8), имеющую неинвертирующий (9) и инвертирующий (10) входы, выходной инвертирующий каскад усиления (11), вход которого (12) связан с выходом (13) ДЦ (8), а выход (14) подключен к выходу (7) ДБУ, первый (15) токостабилизирующий двухполюсник (ТД), связанный с первым (2) токовым выходом ДК (1), второй ТД (16). Неинвертирующий вход (9) ДЦ (8) соединен со вторым (3) токовым выходом ДК (1) и вторым ТД (16), а инвертирующий вход (10) ДЦ (8) связан с выходом (7) ДБУ. 1 з.п. ф-лы, 19 ил.

1. Двухтактный буферный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, выходной составной транзистор (4), база (5) которого соединена с первым (2) токовым выходом входного дифференциального каскада (1), а эмиттер (6) связан с выходом (7) устройства, дифференциальную цепь согласования потенциалов (8), имеющую неинвертирующий (9) и инвертирующий (10) входы, выходной инвертирующий каскад усиления (11), вход которого (12) связан с выходом (13) дифференциальной цепи согласования потенциалов (8), а выход (14) подключен к выходу устройства (7), первый (15) токостабилизирующий двухполюсник, связанный с первым (2) токовым выходом входного дифференциального каскада (1), второй токостабилизирующий двухполюсник (16), отличающийся тем, что неинвертирующий вход (9) дифференциальной цепи согласования потенциалов (8) соединен со вторым (3) токовым выходом входного дифференциального каскада (1) и вторым (16) токостабилизирующим двухполюсником, а инвертирующий вход (10) дифференциальной цепи согласования потенциалов (8) связан с выходом (7) устройства.

2. Устройство по п.1, отличающееся тем, что выход (14) выходного инвертирующего каскада усиления (11) подключен к выходу устройства (7) через цепь согласования потенциалов (33) и связан с дополнительным выходом устройства.

| US 6114904 A, 05.09.2000 | |||

| Дифференциальный усилитель | 1983 |

|

SU1138922A1 |

| US 5150074 A, 22.09.1992 | |||

| US 4595883, 17.06.1986. | |||

Авторы

Даты

2010-05-27—Публикация

2009-02-13—Подача