Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных компараторах и операционных усилителях (ОУ) с малыми значениями эдс смещения нуля).

В современной микроэлектронике широко используются дифференциальные усилители, у которых входной параллельно-балансный каскад имеет две группы парафазных выходов [1-13]. Выходы первой группы, так же как и выходы второй группы - синфазны друг с другом, но противофазны выходам второй группы. Нагрузкой входного параллельно-балансного каскада на биполярных транзисторах являются токовые зеркала и буферный усилитель. Данная архитектура характеризуется малым напряжением смещения нуля [1]. Однако данный положительный эффект реализуется только при использовании в качестве токового зеркала и буферного усилителя классических схем на полевых транзисторах. Если в качестве данных функциональных узлов применяются известные схемы на биполярных транзисторах, то напряжение смещения нуля существенно деградирует.

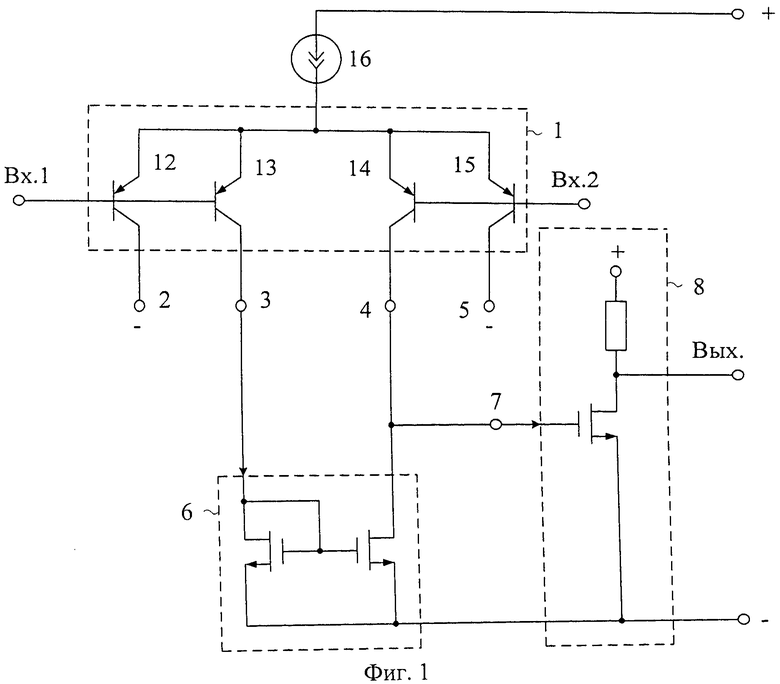

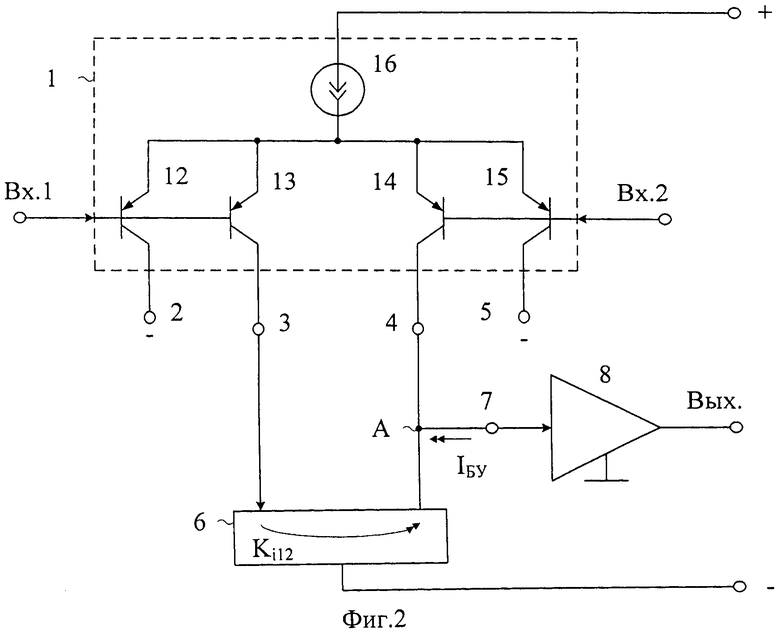

Наиболее близким по сущности к заявляемому техническому решению является схема ДУ фиг.1, представленная в патентной заявке WO 2002/009275, которая также присутствует в большом числе других патентов [1-13]. Функциональная схема ДУ-прототипа соответствует чертежу фиг.2.

Существенный недостаток известного ДУ фиг.1-2 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная цель предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного дрейфа.

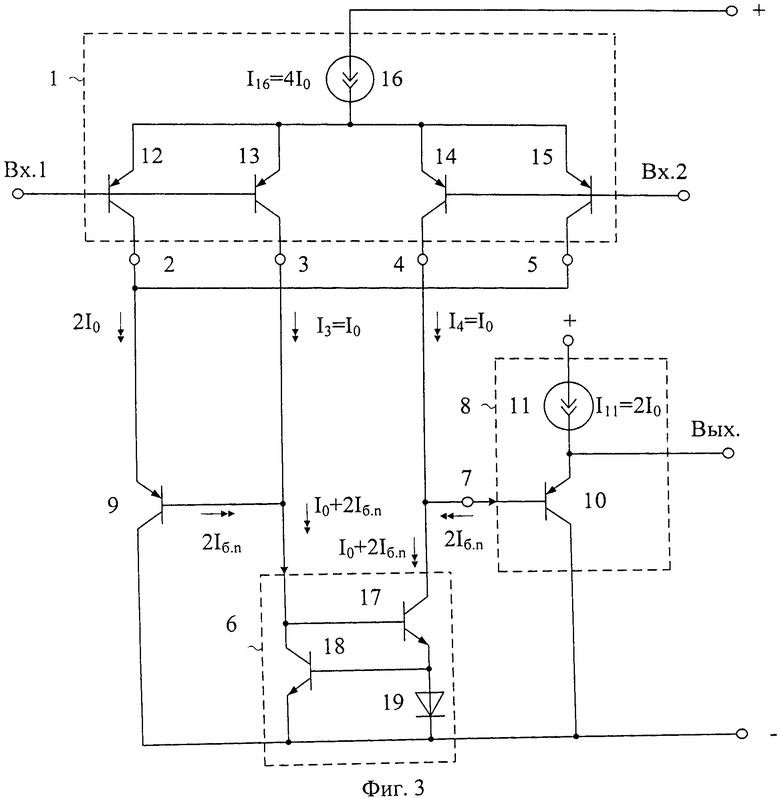

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1 с первым 2 и вторым 3 синфазными токовыми выходами, третьим 4 и четвертым 5 синфазными токовыми выходами, противофазными первому 2 и второму 3 токовым выходам, токовое зеркало 6, вход которого соединен со вторым 3 токовым выходом входного параллельно-балансного каскада 1, а выход подключен к третьему 4 токовому выходу входного параллельно-балансного каскада 1 и входу 7 буферного усилителя 8, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 9, эмиттер которого соединен с первым 2 и четвертым 5 токовыми выходами входного параллельно-балансного каскада 1, база соединена со входом токового зеркала 6, причем тип проводимости входного транзистора 10 буферного усилителя 8 совпадает с типом проводимости дополнительного транзистора 9.

Схема усилителя-прототипа показана на фиг.1-2. На фиг.3 представлена схема заявляемого устройства в соответствии с формулой изобретения.

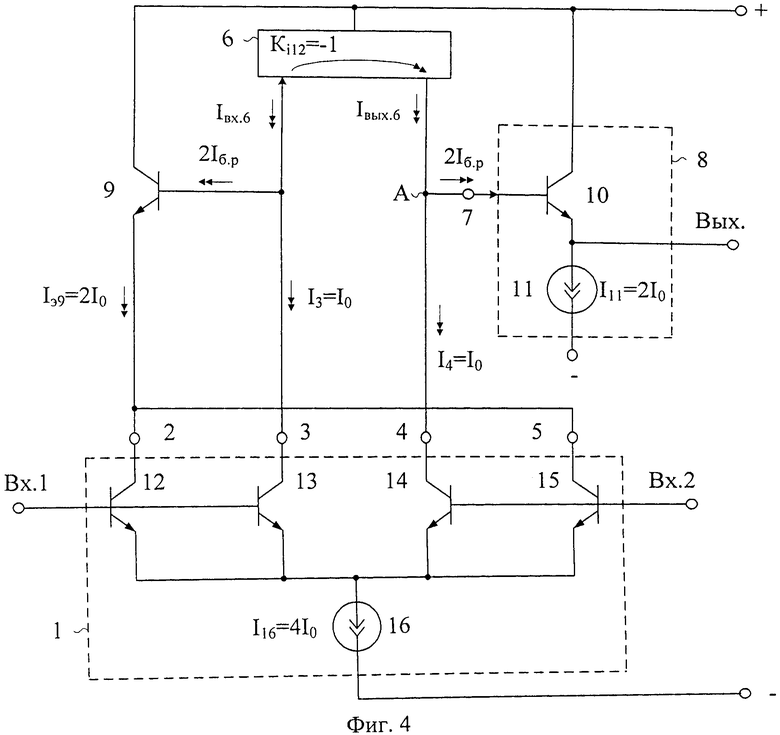

На фиг.4 приведена схема заявляемого устройства фиг.3 для случая, когда основные транзисторы имеют р-тип проводимости.

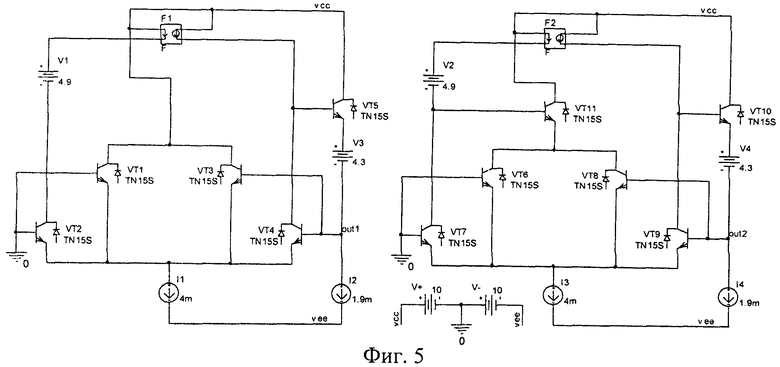

На фиг.5 показаны схемы дифференциального усилителя - прототипа (левая часть) и заявляемого ДУ (правая часть) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

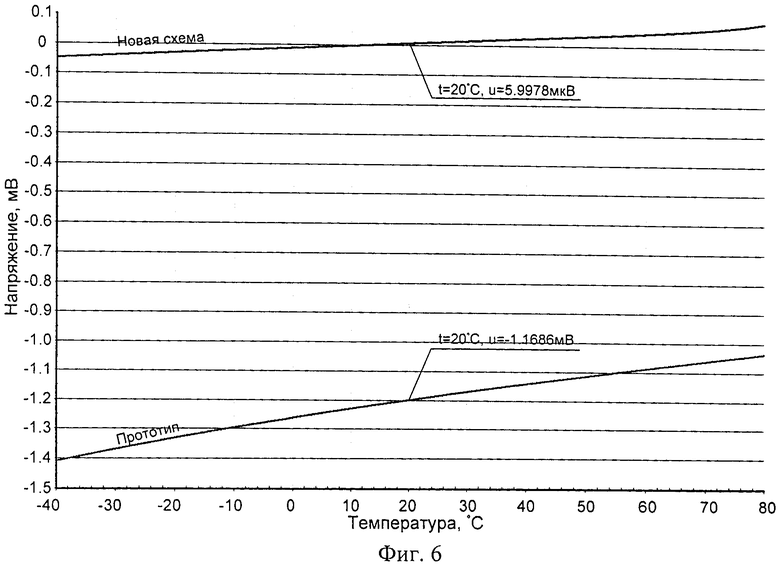

На фиг.6 приведены температурные зависимости напряжения смещения нуля схем фиг.5.

Дифференциальный усилитель фиг.3 (фиг.4) содержит входной параллельно-балансный каскад 1 с первым 2 и вторым 3 синфазными токовыми выходами, третьим 4 и четвертым 5 синфазными токовыми выходами, противофазными первому 2 и второму 3 токовым выходам, токовое зеркало 6, вход которого соединен со вторым 3 токовым выходом входного параллельно-балансного каскада 1, а выход подключен к третьему 4 токовому выходу входного параллельно-балансного каскада 1 и входу 7 буферного усилителя 8. В схему введен дополнительный транзистор 9, эмиттер которого соединен с первым 2 и четвертым 5 токовыми выходами входного параллельно-балансного каскада 1, база соединена со входом токового зеркала 6, причем тип проводимости входного транзистора 10 буферного усилителя 8 совпадает с типом проводимости дополнительного транзистора 9.

В схеме фиг.3 статический режим входного транзистора 10 буферного усилителя 8 устанавливается двухполюсником 11, а входной параллельно-балансный каскад 1 реализован на транзисторах 12, 13, 14, 15 и токостабилизирующем двухполюснике 16. Токовое зеркало в схеме фиг.3 реализовано на транзисторах 17, 18 и 19.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.4, т.е. зависящие только от схемотехники ДУ.

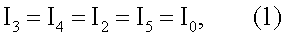

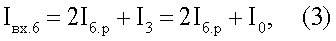

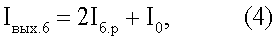

Если ток двухполюсника 16 равен величине 4I0, то токи выходов 2, 3, 4 и 5, а также входной (Iвх.6) и выходной (Iвых.6) токи подсхемы 6

где Iб.р=Iэ.i/βi - ток базы n-p-n транзистора 9 (12, 13, 14, 15, 16) при эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы n-p-n транзистора.

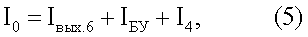

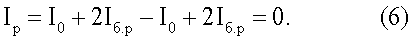

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где IБУ=2Iбр - ток базы n-p-n транзистора 10 буферного усилителя 8. Подставляя (1)÷(4) в (5), находим, что разностный ток, определяющий Uсм.1

Как следствие, при Iр=0 не требуется смещения нуля ДУ фиг.4 на величину Uсм.1, подача которого на его входы Вх.(+)1, Вх.(-)2 компенсирует разностный ток Iр в узле «А».

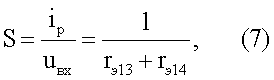

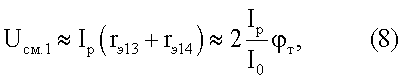

Таким образом, в заявляемом устройстве уменьшается систематическая составляющая Uсм.1, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм.1, так как разностный ток IР в узле «А» создает Uсм.1, зависящее от крутизны преобразования входного дифференциального напряжения uвх ДУ в выходной ток узла «А»

где rэ13=rэ14 - сопротивления эмиттерных переходов входных транзисторов 13 и 14 дифференциального каскада 1.

Поэтому для схем фиг.3-4

где φт=26 мВ - температурный потенциал.

В ДУ-прототипе Iр≠0, поэтому здесь систематическая составляющая Uсм получается на порядок больше (Uсм.1=-1,16 мВ), чем в заявляемой схеме (Uсм.1=5,9 мкВ(фиг.6)).

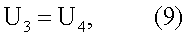

Кроме этого в схеме фиг.4 величина второй составляющей Uсм.2, обусловленной внутренней обратной связью в транзисторах 13 и 14, также существенно уменьшается. При этом условие минимизации этой составляющей (Uсм.2) определяются формулой

где U3, U4 - статические напряжения на выходах 3 и 4.

Для обеспечения равенства (9) в схему могут вводиться цепи смещения потенциалов (V1, V2 - фиг.5).

Компьютерное моделирование схем фиг.5 подтверждает (фиг.6) данные теоретические выводы.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Источники информации

1. Патентная заявка WO 2002/009275

2. Патент США №4267517

3. Патент США №5262682

4. Патент RE035.26 fig.2

5. Авт.св. СССР №1385255

6. Патент США №4147944

7. Патент США №4618833

8. Патент США №5182526

9. Патент США №5880636

10. Патент США №3801923

11. Патент США №4390850

12. Патент США №5734296

13. Патентная заявка США 2001/023251.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2412528C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402871C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2393628C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2402151C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402870C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С СИММЕТРИЧНОЙ НАГРУЗКОЙ | 2009 |

|

RU2394361C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных компараторах и операционных усилителях (ОУ) с малыми значениями эдс смещения нуля). Технический результат: уменьшение абсолютного значения напряжения смещения и его температурного дрейфа. Дифференциальный усилитель содержит входной параллельно-балансный каскад (ПБК) (1) с первым (2) и вторым (3) синфазными токовыми выходами, третьим (4) и четвертым (5) синфазными токовыми выходами, противофазными первому (2) и второму (3) токовым выходам, токовое зеркало (6), вход которого соединен со вторым (3) токовым выходом входного ПБК (1), а выход подключен к третьему (4) токовому выходу входного ПБК (1) и входу (7) буферного усилителя (8). В схему введен дополнительный транзистор (9), эмиттер которого соединен с первым (2) и четвертым (5) токовыми выходами входного ПБК (1), база - соединена со входом токового зеркала (6), причем тип проводимости входного транзистора (10) буферного усилителя (8) совпадает с типом проводимости дополнительного транзистора (9). 6 ил.

Дифференциальный усилитель с малым напряжением смещения нуля, содержащий входной параллельно-балансный каскад (1) с первым (2) и вторым (3) синфазными токовыми выходами, третьим (4) и четвертым (5) синфазными токовыми выходами, противофазными первому (2) и второму (3) токовым выходам, токовое зеркало (6), вход которого соединен со вторым (3) токовым выходом входного параллельно-балансного каскада (1), а выход подключен к третьему (4) токовому выходу входного параллельно-балансного каскада (1) и входу (7) буферного усилителя (8), отличающийся тем, что в схему введен дополнительный транзистор (9), эмиттер которого соединен с первым (2) и четвертым (5) токовыми выходами входного параллельно-балансного каскада (1), база соединена со входом токового зеркала (6), причем тип проводимости входного транзистора (10) буферного усилителя (8) совпадает с типом проводимости дополнительного транзистора (9).

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дифференциальный усилитель | 1983 |

|

SU1166271A1 |

| US 5880636 A, 09.03.1999 | |||

| US 5182526 A, 26.01.1993. | |||

Авторы

Даты

2010-10-20—Публикация

2009-05-25—Подача