ОПИСАНИЕ

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Изобретение относится в целом к аналоговым умножителям и, более определенно, к токовым умножителям.

УРОВЕНЬ ТЕХНИКИ

Аналоговые умножители представляют собой часто используемые компоненты в различного типа аналоговых схемах. По мере развития технологии аналоговых схем различные характеристики схем стали более желательными и/или обязательно необходимыми. Примеры таких характеристик включают в себя низкую сложность схемы, малую площадь схемы, низкое напряжение питания и возможность работы на высоких частотах.

Таким образом, желательно предоставить аналоговые умножители, обладающие одной или несколькими из вышеупомянутых примерных характеристик.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Примерные варианты реализации изобретения представляют схему токового умножителя, основанную на корневой вольт-амперной характеристике МОП транзистора. Схема включает в себя первый, второй и третий МОП транзисторы с общим отношением ширины канала к его длине и первый и второй источники тока, которые соответственно обеспечивают первый и второй входные токи, отображающие первый и второй сомножители. Первый и второй МОП транзисторы производят первое и второе напряжения как функцию первого и второго входных токов, и третий МОП транзистор производит третий ток как функцию первого и второго напряжений. В ответ на третий ток схема производит сигнал произведения, отображающий произведение первого и второго сомножителей.

Перед тем как предоставить подробное описание изобретения, может быть полезно разъяснить определения, некоторые слова и обороты, используемые в данном патентном документе: термины "включает в себя" и "содержит", так же как их производные, означают включение без ограничения; термин "или" является включающим, означая и/или; обороты "связанный с" и "связанный с этим", так же как их производные, могут означать включать, быть включенным в пределах, взаимосвязанным с, содержать, содержаться в пределах, соединяться с, связанным с, обменивающийся с, объединяться с, чередование, сопоставление, быть близким к, граничить с, иметь, иметь свойство или тому подобное; и термин "контроллер" означает любое устройство, систему или их часть, которая управляет, по меньшей мере, одной операцией. Контроллер может быть осуществлен в аппаратных средствах, встроенном программном обеспечении или устанавливаемом программном обеспечении или некоторой комбинации, по меньшей мере, двух из этого же. Следует отметить, что функциональность, связанная с контроллером, может быть централизованной, или распределенной, или локальной, или удаленной. Определения некоторых слов и оборотов относятся ко всему данному патентному документу, причем специалистам в данной области техники должно быть ясно, что во многих, если не в большем числе случаев, эти определения относятся и к предшествующим, и к будущим использованиям некоторых этих слов и оборотов.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для более полного понимания настоящего изобретения и его преимуществ приведено нижеследующее описание вместе с соответствующими чертежами, на которых подобные элементы обозначены одинаковыми номерами:

Фиг.1 схематически изображает одноквадрантную корневую схему токового умножителя в соответствии с примерными вариантами реализации изобретения;

Фиг.2 - более подробное изображение участка Фиг.1;

Фиг.3 - схематическое изображение модели, которая может быть использована для определения снижения усиления схем умножителя на Фиг.1 и 2;

Фиг.4 - схематическое изображение четырехквадрантной корневой схемы токового умножителя в соответствии с примерными вариантами реализации изобретения;

Фиг.5A и 5B - оба показывают детализированное исполнение схемы на Фиг.4;

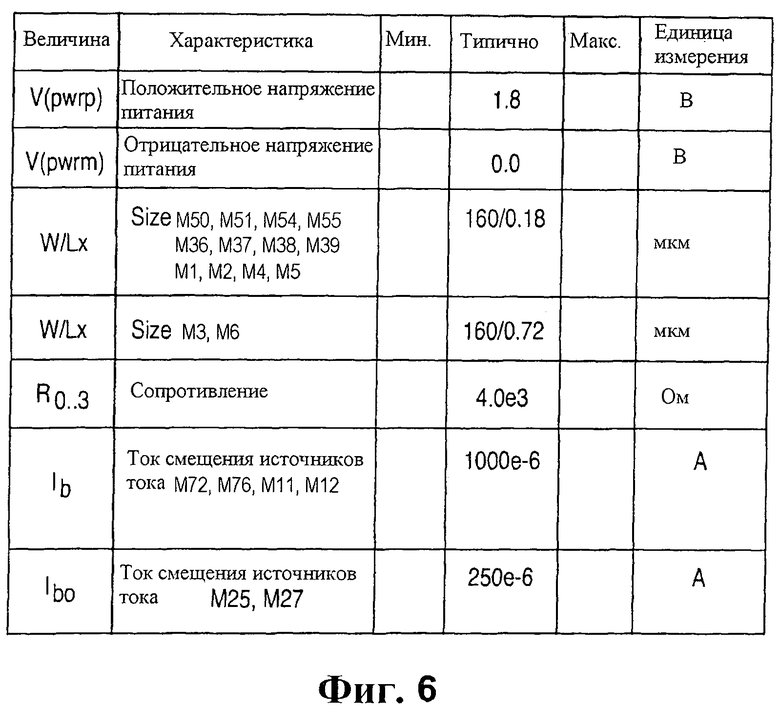

Фиг.6 - табличная форма избранных характеристик различных компонент, показанных на Фиг.5A и 5B;

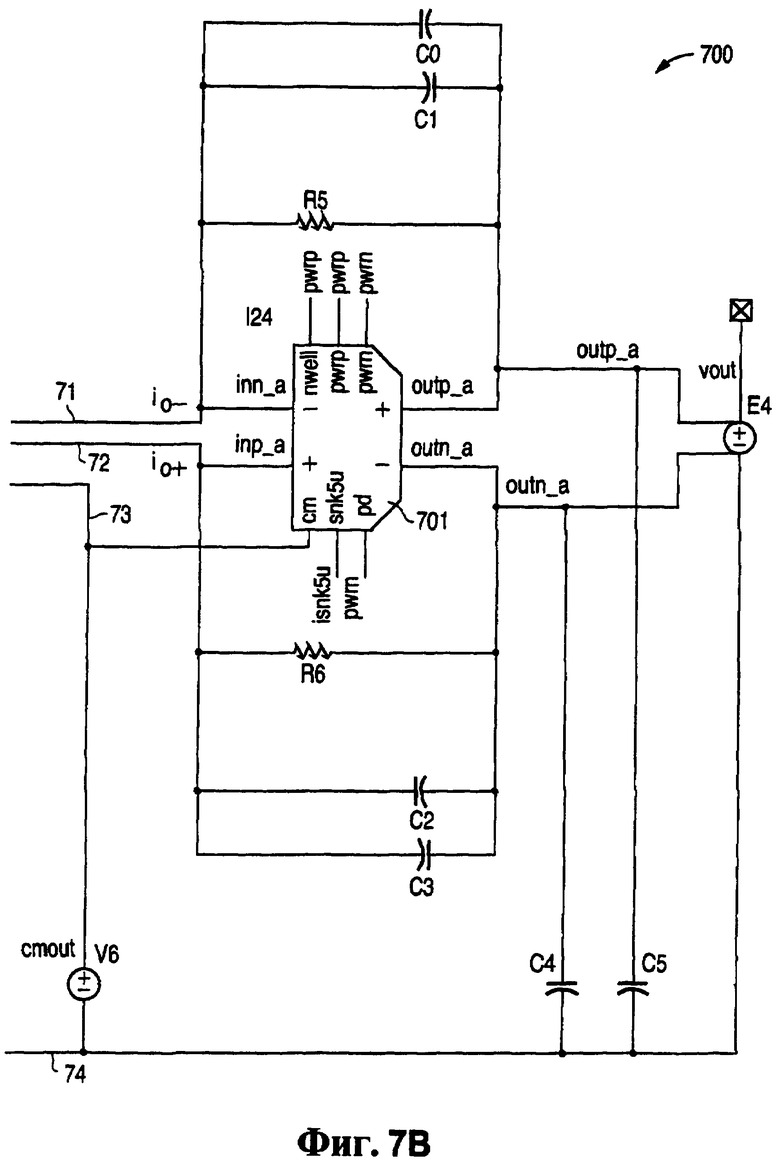

Фиг.7A и 7B - оба схематически показывают смеситель в соответствии с примерными вариантами реализации изобретения;

Фиг.8 - таблица избранных характеристик различных компонент, показанных на Фиг.7A и 7B; и

Фиг.9 и 10 - показывают избранные сигналы для Фиг.5A, 5B, 7A и 7B.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Чертежи на Фиг.1-10 и различные варианты реализации, демонстрирующие принципы настоящего изобретения в данном патентном описании, служат лишь иллюстрацией и не должны быть поняты как ограничение возможностей применения изобретения. Специалистам в данной области техники должно быть ясно, что принципы настоящего изобретения могут быть реализованы в любой соответствующей системе.

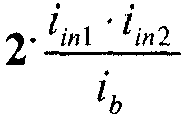

Четырехквадрантный умножитель может быть реализован в соответствии с примерными вариантами реализации изобретения с использованием условий:  , и следующего разложения в ряд:

, и следующего разложения в ряд:

(1)

(1)

где Ib - ток смещения, iin1 и iin2 - токи входного сигнала (которые отображают перемножаемые сомножители), и 0(7) - ошибка усечения 7-го порядка. Требуемым слагаемым является  . Каждое слагаемое с квадратным корнем в левой части равенства порождается выходным током одноквадрантного корневого умножителя (1QSRM). Разностный ток между двумя этими одноквадрантными умножителями обеспечивает требуемый результат перемножения (произведения).

. Каждое слагаемое с квадратным корнем в левой части равенства порождается выходным током одноквадрантного корневого умножителя (1QSRM). Разностный ток между двумя этими одноквадрантными умножителями обеспечивает требуемый результат перемножения (произведения).

Схема одноквадрантного корневого умножителя (1QSRM) в соответствии с примерными вариантами реализации изобретения показана на Фиг.1. Предполагается, что МОП транзисторы M1, M2 и M3 работают в насыщенном режиме. Транзисторы M1 и M2 включены как диоды. Токи входного сигнала iin1 и iin2 и ток смещения Ib обеспечиваются соответствующими источниками тока. Токи i1 и i2 через М1 и M2, соответственно, представляют собой

(2)

(2)

Все МОП транзисторы работают в насыщенном режиме в соответствии с корневой характеристикой МОП транзистора. Кроме того, все МОП транзисторы имеют то же самое отношение ширины канала к его длине. Напряжения на затворах М1 и M2 представляют собой:

(3)

(3)

где VT представляет собой пороговое напряжение и К представляет собой коэффициент передачи. Напряжения на затворе и Vgs1 и Vgs2 являются усредненными и приложены к затвору МОП транзистора M3 так, что:

(4)

(4)

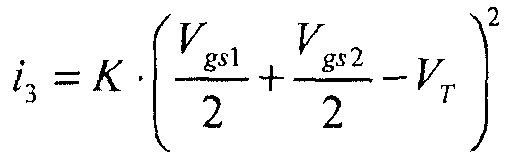

Образующийся ток стока i3 через M3 представляет собой поэтому:

(5)

(5)

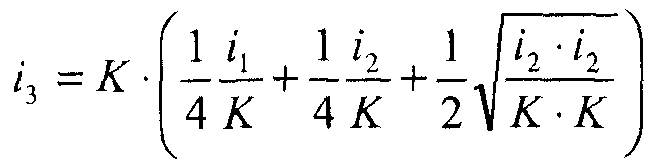

Далее, подстановка для Vgs1 и Vgs2 дает:

(6)

(6)

или

(7)

(7)

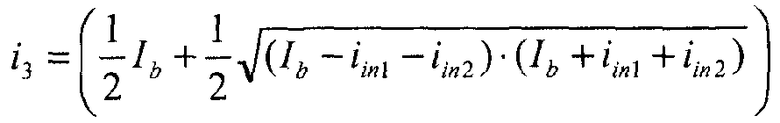

Наконец, подстановка i1 и i2 дает:

(8)

(8)

Постоянная часть Ib (iin1=0, iin2=0), компенсируется подключением источника тока Ib у стока M3. Выходной ток i0 равен i3-Ib, то есть:

(9)

(9)

Это равно половине одного из слагаемых в левой части уравнения (1) минус постоянный ток Ib/2. Следует отметить, что i 0 не содержит множителя, зависящего от процесса.

В соответствии с уравнением (4), среднее значение напряжений VgS1 и VgS2 приложено к затвору M3. В некоторых вариантах реализации для этого используются два резистора. С резисторами возможно простое выполнение 1QSRM, как показано на Фиг.2. При использовании резисторов с равными значениями сопротивления (Rl=R2) выполняется уравнение (4). Резисторы Rl и R2 нагружают источники входного тока in1 и in2. Резисторы Rl и R2 снижают усиление умножителя и приводят к тому, что усиление зависит от процесса. Снижение усиления умножителя может быть аппроксимировано с использованием упрощенной модели малого сигнала, показанной на Фиг.3. Моделируются только M1 и M2. Узлы X1 и X2 на Фиг.3 соответствуют узлам XI и X2 на Фиг.1 и 2.

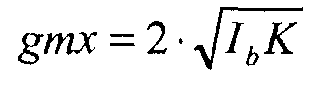

В соответствии с простой корневой моделью МОП транзистора, передаточная характеристика gmx для малого сигнала равна:

(10)

(10)

Это означает, что передаточная характеристика зависит от процесса, но управляется током смещения Ib. Разностный ток id равен:

(11)

(11)

Этот разностный ток снижает ток через сток-исток малого сигнала для М1 и M2 в "r" раз:

(12)

(12)

Этот фактор "r" может поддерживаться близким к 1 выбором Rl и R2 как можно большими и 1/gm1 и 1/gm2 как можно меньшими.

Четырехквадрантный умножитель (4QM) может быть сконструирован с 2 версиями 1QSRM из Фиг.2. Примерные варианты реализации получающейся схемы 4QM показаны на Фиг.4. Все МОП транзисторы работают в насыщенном режиме в соответствии с корневой характеристикой МОП транзистора. Кроме того, все МОП транзисторы имеют то же самое отношение ширины канала к его длине.

Дифференциальный выходной ток вывода i0+ - i0-, как видно на выходном каскаде, равен:

(13)

(13)

Выходной ток может быть аппроксимирован как:

(14)

(14)

Из этого уравнения (14) ясно, что нежелательные слагаемые более высокого порядка могут быть минимизированы увеличением тока смещения Ib.

Умножитель 4QM на Фиг.4 может использоваться при очень низком напряжении питания. В некоторых вариантах реализации минимального напряжения питания при подаче на один затвор-исток, например Vgsi, при токе 2*Ib и одном напряжении насыщения, добавленном к источнику тока Ib, достаточно для нормальной работы.

Множитель 4QM на Фиг.4 может быть масштабирован для работы при очень высоких частотах. В случае высоких частот, например в смесителе, только узлы XI, X2, X4 и X5 должны работать на самой высокой частоте. Узлы X3 и X6 и выходные узлы Xo+ и Xo- работают на более низкой разностной частоте. Это означает, что выходные МОП транзисторы M3 и M6 могут масштабироваться для максимизации низкочастотного выходного тока. Кроме того, ток смещения через МОП транзисторы M3 и M6 может быть снижен независимо от МОП транзисторов M1, M2, M4 и M5.

Четырехквадрантный токовый умножитель 4QM может быть использован как смеситель. В смесителе высокочастотный входной сигнал преобразуется в низкочастотный выходной сигнал умножением на сигнал разностной частоты. На Фиг.5A-10 показаны примерные варианты реализации применения смесителя в четырехквадрантном токовом умножителе 4QM. Узлы, которые являются общими для обеих Фиг.5A и 5B, обозначены как 51, 52, 53, 54 и 55.

Ток I (ibias_snk) = 50 uA подается на вход "ibias_snk" на Фиг.5А, питая токовое зеркало, сформированное МОП транзисторами М28, М29 и М30. Выходные токи М29 и М30 (50 uА) подаются на соединенные как диоды МОП транзисторы М7З и М31-М34. М73 на Фиг.5А формирует зеркало тока смещения с МОП транзисторами М72, М76, М11 и М12 (см. также Фиг.5 В). Последние четыре МОП транзистора повышены в 20 раз относительно М73 и питают током смещения 1 mA соответствующие дифференциальные пары 500, 501, 502 и 503. МОП транзисторы М31-М34 создают каскадное напряжение смещения для каскадных МОП транзисторов М35, М42, М40 и М41 (см. также Фиг.5В). Это поддерживает МОП транзисторы зеркала тока смещения в насыщенном режиме и увеличивает выходной импеданс источников тока смещения.

Дифференциальные пары 501-504 (включая в себя МОП транзисторы М50, М51, М54, М55 и М36-М39) используются для преобразования дифференциальных входных напряжений vinlp, vinln и vin2p, vin2n во входные токи (например iin1 и iin2 на Фиг.4), подходящие для токового умножителя 4QM. В некоторых вариантах реализации преобразование передаточной характеристики малого сигнала составляет gmin=6,8 мС.

МОП транзисторы схем 1QSRM на Фиг.5А и 5В масштабированы в некоторых вариантах реализации для достижения высокочастотной характеристики. Выходной ток включает в себя часть обычного режима и дифференциальную часть. Сигнал выходного тока io+, io-, как видно на выходном каскаде, является дифференциалом. Нежелательный выходной ток обычного режима компенсируется выходным регулировочным блоком 505 обычного режима. В блоке 505 выходное напряжение обычного режима воспринимается МОП транзисторами М7 и М8. Обратная связь осуществляется через источник выходного тока МОП транзисторов 506 и 507. Выходной ток через МОП транзисторы М3 и М6 понижен в некоторых вариантах реализации в 4 раза. Уравнение умножителя (14) реализуется затем посредством аппроксимации:

Выбранные компоненты умножителя 4QM на Фиг.5А и 5В масштабируются в соответствии с Фиг.6 в некоторых вариантах реализации.

На Фиг.7А и 7В показаны примерные варианты реализации смесителя, причем общие узлы на Фиг.7А и 7В обозначены как 71, 72, 73 и 74. Источники напряжения VI и V2 образуют высокочастотные входные сигналы. Управляемые напряжением источники напряжения Е0-Е3 преобразуют несимметричные входные напряжения vin1 и vin2 в дифференциальные напряжения vinlp, vinln и vin2p, vin2n. Они подаются на умножитель 4QM. Входное напряжение обычного режима cmin образуется для источников напряжения Е0-Е3 посредством источника напряжения постоянного тока V4.

Требуемый дифференциальный токовый выходной сигнал i0+, i0-, вышедший из умножителя 4QM, подается на выходной каскад, который включает в себя преобразователь 700 ток-напряжение (I/V-преобразователь), организованный на базе операционного усилителя 701 (см. также Фиг.7В). В некоторых вариантах реализации резисторы преобразователя имеют номиналы - R5=R6=20 кОм, и конденсаторы С0-С3 имеют номиналы 0,1 пФ и используются для надежной стабильности I/V-преобразователя. Конденсаторы С4 и С5 представляют собой нагрузочную емкость преобразователя I/V. На Фиг.8 показаны величины выбранных компонентов на Фиг.7А и 7В в соответствии с некоторыми вариантами реализации.

Когда два входных сигнала, в соответствии с Фиг.8 (vinl на finl и vin2 на fin2) поданы на умножитель, дифференциальный выходной сигнал имеет в идеальном случае две частотных компоненты, сумму и разность частот входных сигналов, 1,01 ГГц и 10 МГц, соответственно. Выходной сигнал 10 МГц представляет собой требуемую компоненту. Компонента 1,01 ГГц фильтруется. Если обратиться к Фиг.5А и 5В, то постоянные времени фильтрации образуются параллельными парами сопротивлений R1 и R2 (R3 и R4) и емкостью затвор-исток соответствующего выходного МОП транзистора М3 (М6). Дальнейшая фильтрация достигается преобразователем I/V, который в некоторых вариантах реализации имеет полосу пропускания 40 МГц.

На Фиг.9 и 10 показаны выбранные сигналы из Фиг.5А, 5В, 7А и 7В. Высокочастотные входные сигналы vinl, vin2 (Фиг.7А) и внутренние узловые напряжения умножителя на xl, х2 и х3 (Фиг.5А) показаны на Фиг.9. Видно, что умножитель сжимает входные сигналы. Низкоомные узлы xl (х4) и х2 (х5) делают схему подходящей для работы на высоких частотах. На узле х3 (х6) низкочастотная компонента сигнала в 10 МГц очевидна. Это указывает, что узел х3 (х6) является уже "низкочастотным" узлом. Из-за масштабирования выхода МОП транзисторов М3 и М6 в некоторых вариантах реализации емкости затвор-исток этих МОП транзисторов фильтруют уже большую часть высокочастотных составляющих сигнала на узле х3 (х6).

На Фиг.10 показано напряжение на узлах vout и outp_a и outn_a на Фиг.7B. Дифференциальное выходное напряжение vout=outp_a-outn_a имеет частоту 10 МГц, демонстрируя характеристику смешения схемы. Амплитуда выходного сигнала vout составляет 0,25 В.

Хотя настоящее изобретение описано в связи с примерными вариантами реализации, специалистами в данной области техники могут быть предложены различные замены и модификации. Это означает, что настоящее изобретение предполагает такие замены и модификации, которые охвачены приложенными формулами.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА ТОКОВОГО ЗЕРКАЛА С АВТОМАТИЧЕСКИМ ПЕРЕКЛЮЧЕНИЕМ ДИАПАЗОНА | 2006 |

|

RU2339156C2 |

| ЧИП УСИЛИТЕЛЯ КЛАССА D С ФУНКЦИЕЙ ОГРАНИЧЕНИЯ КОЭФФИЦИЕНТА ЗАПОЛНЕНИЯ И ЕГО УСТРОЙСТВО | 2014 |

|

RU2598336C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| ВЫСОКОЧАСТОТНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ СТАБИЛИЗАЦИИ ТОКА КОЛЛЕКТОРА | 2012 |

|

RU2509407C1 |

| УСТРОЙСТВО ФОТОЭЛЕКТРИЧЕСКОГО ПРЕОБРАЗОВАНИЯ И СИСТЕМА ФОТОЭЛЕКТРИЧЕСКОГО ПРЕОБРАЗОВАНИЯ | 2016 |

|

RU2638914C2 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ | 2020 |

|

RU2729887C1 |

| ИСТОЧНИК СТАБИЛЬНОГО ТОКА ИЛИ НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 2022 |

|

RU2795478C1 |

| Высокочастотный фазовращатель на МОП-транзисторах | 2015 |

|

RU2607673C1 |

| МАЛОШУМЯЩИЙ ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ ТОКА ОЛЕКСЕНКО-КОЛЕСНИКОВА | 2000 |

|

RU2178235C1 |

| ВЫСОКОЧАСТОТНЫЙ ВЕКТОРНЫЙ ФАЗОВРАЩАТЕЛЬ | 2016 |

|

RU2647217C1 |

Изобретения относятся к аналоговым умножителям. Достигаемый технический результат - уменьшение сложности схемы аналоговых умножителей. Схема токового умножителя включает в себя первый, второй и третий МОП транзисторы с общим отношением ширины канала к его длине и первый и второй источники тока, которые соответственно обеспечивают первый и второй входные токи, отображающие первый и второй перемножаемые множители. Первый и второй МОП транзисторы производят первое и второе напряжения как функции первого и второго входных токов, и третий МОП транзистор производит третий ток как функцию первого и второго напряжений. В ответ на третий ток схема токового умножителя производит сигнал произведения первого и второго сомножителей. 3 н. и 17 з.п. ф-лы, 12 ил.

1. Схема токового умножителя, включающая в себя

первый, второй и третий МОП транзисторы, имеющие обычное отношение ширины канала к его длине;

первый и второй источники тока, которые соответственно обеспечивают первый и второй входные токи, которые соответственно представляют первый и второй перемножаемые сомножители;

каждый упомянутый первый и второй МОП транзисторы связаны с упомянутым первым и вторым источником тока, причем упомянутый первый МОП транзистор производит первое напряжение как функцию упомянутых первого и второго входных токов, и упомянутый второй МОП транзистор производит второе напряжение как функцию упомянутых первого и второго входных токов;

упомянутый третий МОП транзистор связан с упомянутым первым и вторым МОП транзисторами для производства третьего тока как функции упомянутых первого и второго напряжения; и

выходной каскад, связанный с упомянутым третьим МОП транзистором, причем упомянутый выходной каскад производит, в ответ на упомянутый третий ток, сигнал произведения, отображающий произведение упомянутых первого и второго сомножителей.

2. Схема по п.1, включающая в себя четвертый, пятый и шестой МОП транзисторы, имеющие упомянутое обычное отношение ширины канала к его длине, причем каждый из упомянутых четвертых и пятых МОП транзисторов связан с упомянутым первым и вторым источником тока, упомянутый четвертый МОП транзистор производит третье напряжение как функцию упомянутых первого и второго входных токов, и упомянутый пятый МОП транзистор производит четвертое напряжение как функцию упомянутых первого и второго входных токов, упомянутый шестой МОП транзистор связан с упомянутыми четвертым и пятым МОП транзисторами для производства четвертого тока как функции упомянутых третьего и четвертого напряжений, упомянутый выходной каскад связан с упомянутым шестым МОП транзистором, и упомянутый выходной каскад производит упомянутый сигнал произведения в ответ на упомянутый третий и четвертый токи.

3. Схема по п.2, в которой упомянутый сигнал произведения представляет собой дифференциальный токовый сигнал, полученный от упомянутых третьего и четвертого токов.

4. Схема по п.2, в которой затвор каждого из упомянутых первых, вторых, четвертых и пятых МОП транзисторов соединен с их стоком.

5. Схема по п.2, включающая в себя третий источник тока, соединенный с упомянутыми МОП транзисторами и обеспечивающий рабочий ток для упомянутых МОП транзисторов, причем упомянутый первый, второй и третий источники тока объединяются для производства соответствующих токов в упомянутых первом, втором, четвертом и пятом МОП транзисторах, причем упомянутые токи в упомянутых первом и втором МОП транзисторах производятся посредством объединения упомянутого рабочего тока с суммой упомянутых первого и второго токов, и упомянутые токи в упомянутых четвертом и пятом МОП транзисторах производятся посредством объединения упомянутого рабочего тока с разностью упомянутых первого и второго токов.

6. Схема по п.5, в которой упомянутый ток в упомянутом первом МОП транзисторе производится как разность между упомянутым рабочим током и упомянутой суммой упомянутых первого и второго токов, причем упомянутый ток в упомянутом втором МОП транзисторе производится как сумма упомянутого рабочего тока и упомянутой суммы упомянутых первого и второго токов, упомянутый ток в упомянутом четвертом МОП транзисторе производится как разность между упомянутым вторым током и суммой упомянутого рабочего тока и упомянутого первого тока, и упомянутый ток в упомянутом пятом МОП транзисторе производится как разность между упомянутым первым током и суммой упомянутого рабочего тока и упомянутого второго тока.

7. Схема по п.6, включающая в себя первую схему усреднения напряжения, включенную между затвором упомянутого третьего МОП транзистора и упомянутыми первым и вторым МОП транзисторами, причем упомянутая первая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого третьего МОП транзистора первое усредненное напряжение, которое является средним значением упомянутых первого и второго напряжений, и включающая в себя вторую схему усреднения напряжения, включенную между затвором упомянутого шестого МОП транзистора и упомянутыми четвертым и пятым МОП транзисторами, причем упомянутая вторая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого шестого МОП транзистора второе усредненное напряжение, которое является средним значением упомянутых третьего и четвертого напряжений.

8. Схема по п.7, в которой упомянутая первая схема усреднения напряжения включает в себя первый и второй резисторы, соответственно связанные с упомянутыми первым и вторым МОП транзисторами и также связанные с упомянутым затвором упомянутого третьего МОП транзистора, и в которой упомянутая вторая схема усреднения напряжения включает в себя третий и четвертый резисторы, соответственно связанные с упомянутым четвертым и пятым МОП транзисторами, и также связанные с упомянутым затвором упомянутого шестого МОП транзистора.

9. Схема по п.5, включающая в себя первую схему усреднения напряжения, включенную между затвором упомянутого третьего МОП транзистора и упомянутыми первым и вторым МОП транзисторами, причем упомянутая первая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого третьего МОП транзистора первое усредненное напряжение, которое является средним значением упомянутых первого и второго напряжений, и включающая в себя вторую схему усреднения напряжения, включенную между затвором упомянутого шестого МОП транзистора и упомянутыми четвертым и пятым МОП транзисторами, причем упомянутая вторая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого шестого МОП транзистора второе усредненное напряжение, которое является средним значением упомянутых третьего и четвертого напряжений.

10. Схема по п.2, включающая в себя первую схему усреднения напряжения, включенную между затвором упомянутого третьего МОП транзистора и упомянутыми первым и вторым МОП транзисторами, причем упомянутая первая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого третьего МОП транзистора первое усредненное напряжение, которое является средним значением упомянутых первого и второго напряжений, и включающая в себя вторую схему усреднения напряжения, включенную между затвором упомянутого шестого МОП транзистора и упомянутыми четвертым и пятым МОП транзисторами, причем упомянутая вторая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого шестого МОП транзистора второе усредненное напряжение, которое является средним значением упомянутых третьего и четвертого напряжений.

11. Схема по п.2, в которой упомянутый выходной каскад включает в себя дифференциальный преобразователь ток-напряжение для производства сигнала дифференциального напряжения в ответ на упомянутые третий и четвертый токи.

12. Схема по п.1, включающая в себя схему усреднения напряжения, включенную между затвором упомянутого третьего МОП транзистора и упомянутыми первым и вторым МОП транзисторами, причем упомянутая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого третьего МОП транзистора третье напряжение, которое является средним значением упомянутых первого и второго напряжений.

13. Схема по п.12, в которой упомянутая схема усреднения напряжения включает в себя первый и второй резисторы, соответственно связанные с упомянутым первым и вторым МОП транзисторами и также связанные с упомянутым затвором упомянутого третьего МОП транзистора.

14. Схема по п.1, в которой затвор каждого из упомянутых первого и второго МОП транзисторов соединен с их стоком.

15. Смеситель для преобразования входного сигнала, имеющего первую частоту, в выходной сигнал, имеющий вторую частоту, ниже упомянутой первой частоты, посредством перемножения упомянутого входного сигнала с дополнительным сигналом, имеющим третью частоту, которая является разностью между упомянутой первой и упомянутой второй частотами, содержащий

первый, второй, третий, четвертый, пятый и шестой МОП транзисторы, имеющие общее отношение ширины канала к его длине;

первый и второй источники тока, которые соответственно обеспечивают первый и второй входные токи, которые соответственно отображают упомянутый входной сигнал и упомянутый дополнительный сигнал;

упомянутый первый и второй МОП транзисторы, каждый связанный с упомянутым первым и вторым источниками тока, причем упомянутый первый МОП транзистор производит первое напряжение как функцию упомянутых первого и второго входных токов, и упомянутый второй МОП транзистор производит второе напряжение как функцию упомянутых первого и второго входных токов;

упомянутый третий МОП транзистор, связанный с упомянутым первым и вторым МОП транзисторами для производства третьего тока как функции упомянутых первого и второго напряжений;

упомянутые четвертый и пятый МОП транзисторы, каждый связанный с упомянутым первым и вторым источниками тока, причем упомянутый четвертый МОП транзистор производит третье напряжение как функцию упомянутых первого и второго входных токов, и упомянутый пятый МОП транзистор производит четвертое напряжение как функцию упомянутых первого и второго входных токов;

упомянутый шестой МОП транзистор связан с упомянутыми четвертым и пятым МОП транзисторами для производства четвертого тока как функции упомянутых третьего и четвертого напряжений; и

дифференциальный преобразователь ток-напряжение, связанный с упомянутыми третьим и шестым МОП транзисторами для производства, в ответ на упомянутые третий и четвертый токи, дифференциальный сигнал напряжения, отображающий упомянутый выходной сигнал.

16. Смеситель по п.15, включающий в себя третий источник тока, связанный с упомянутым МОП транзистором и обеспечивающий рабочий ток для упомянутых МОП транзисторов, упомянутые первый, второй и третий источники тока, объединяемые для производства соответственного тока в упомянутых первом, втором, четвертом и пятом МОП транзисторах, причем упомянутый ток в упомянутом первом и втором МОП транзисторах производится посредством объединения упомянутого рабочего тока с суммой упомянутых первого и второго токов, и упомянутый ток в упомянутых четвертом и пятом МОП транзисторах производится посредством объединения упомянутого рабочего тока с разностью упомянутых первого и второго токов.

17. Смеситель по п.15, включающий в себя первую схему усреднения напряжения, включенную между затвором упомянутого третьего МОП транзистора и упомянутыми первым и вторым МОП транзисторами, причем упомянутая первая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого третьего МОП транзистора усредненное первое напряжение, которое является средним значением упомянутых первого и второго напряжений, и включающий в себя вторую схему усреднения напряжения, включенную между затвором упомянутого шестого МОП транзистора и упомянутыми четвертым и пятым МОП транзисторами, причем упомянутая вторая схема усреднения напряжения обеспечивает на упомянутом затворе упомянутого шестого МОП транзистора второе усредненное напряжение, которое является средним значением упомянутых третьего и четвертого напряжений.

18. Смеситель по п.15, в котором затвор каждого упомянутого первого, второго, четвертого и пятого МОП транзисторов соединен с их стоком.

19. Способ выполнения токового умножения со множеством МОП транзисторов, имеющих обычное отношение ширины канала к его длине, содержащий

обеспечение первого и второго входных токов, которые соответственно отображают первый и второй перемножаемые сомножители;

создание первого напряжения на первом из упомянутых МОП транзисторов как функции упомянутых первого и второго входных токов;

создание второго напряжения на втором из упомянутых МОП транзисторов как функции упомянутых первого и второго входных токов;

в третьем из упомянутых МОП транзисторов производство третьего тока как функции упомянутых первого и второго напряжений; и

создание в ответ на упомянутый третий ток сигнала произведения, отображающего произведение упомянутых первого и второго множителей.

20. Способ по п.19, включающий в себя производство на четвертом из упомянутых МОП транзисторов третьего напряжения как функции упомянутых первого и второго входных токов, производство на пятом МОП транзисторе упомянутого четвертого напряжения как функции упомянутых первого и второго входных токов, и дополнительно включающий в себя в шестом из упомянутых МОП транзисторов производство четвертого тока как функции упомянутых третьего и четвертого напряжений, и этап производства упомянутого сигнала произведения включает в себя производство упомянутого сигнала произведения в ответ на упомянутые третий и четвертый токи.

| BULT K ЕТ AL: "A CLASS OF ANALOG CMOS CIRCUITS BASED ON THE SQUARE-LAW CHARACTERISTIC OF AN MOS TRANSISTOR IN SATURATION", IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE SERVICE CENTER, PISCATAWAY, NJ, US, том SC-22, номер 3, 01.06.1987 | |||

| JP 2004157757 A, 03.06.2004 | |||

| US 2003005018 A1, 02.01.2003 | |||

| ПЕРЕМНОЖИТЕЛЬ НИЗКОЧАСТОТНЫХ СИГНАЛОВ | 1998 |

|

RU2149447C1 |

Авторы

Даты

2010-11-20—Публикация

2006-04-24—Подача