ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее изобретение относится к устройству фотоэлектрического преобразования и к системе фотоэлектрического преобразования.

УРОВЕНЬ ТЕХНИКИ

[0002] В устройстве фотоэлектрического преобразования, раскрытом на фиг. 2 в выложенной японской патентной заявке № 2005-311487 (далее именуемой PTL 1), дифференциальный усилитель формируется с использованием транзистора усиления пикселя (114 на фиг. 2) для пикселя и дифференциального транзистора (201 на фиг. 2), расположенного в каждом столбце. На транзистор усиления пикселя поступает сигнал на основании электрического заряда, генерируемого в элементе фотоэлектрического преобразования. На дифференциальный транзистор поступает опорное напряжение с пилообразной формой волны. Посредством операции, в которой напряжение на затворе транзистора усиления пикселя сравнивается с напряжением на затворе дифференциального транзистора, сигнал на основании электрического заряда, генерируемого в элементе фотоэлектрического преобразования, преобразуется в цифровой сигнал.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0003] Согласно аспекту, настоящее изобретение предусматривает устройство фотоэлектрического преобразования, включающее в себя элемент фотоэлектрического преобразования, дифференциальную пару, включающую в себя первый транзистор, выполненный с возможностью приема сигнала на основании электрического заряда, генерируемого в элементе фотоэлектрического преобразования, и второй транзистор, выполненный с возможностью приема опорного сигнала, фиксирующую схему, выполненную с возможностью фиксации напряжения на затворе второго транзистора, и выходную схему, выполненную с возможностью осуществления первой операции для вывода напряжения на основании напряжения на затворе первого транзистора на затвор второго транзистора и второй операции для приема тока от второго транзистора, и для вывода сигнала на основании результата сравнения между напряжением на затворе первого транзистора и напряжением на затворе второго транзистора на выходной узел. Выходная схема включает в себя блок управления, выполненный с возможностью управления, во второй операции величиной изменения напряжения на стоке второго транзистора, чтобы она была меньше величины изменения напряжения на выходном узле.

[0004] В другом аспекте, настоящее изобретение предусматривает устройство фотоэлектрического преобразования, включающее в себя элемент фотоэлектрического преобразования, дифференциальную пару, включающую в себя первый транзистор, выполненный с возможностью приема сигнала на основании электрического заряда, генерируемого в элементе фотоэлектрического преобразования, и второй транзистор, выполненный с возможностью приема опорного сигнала, фиксирующую схему, выполненную с возможностью фиксации напряжения на затворе второго транзистора, схему токового зеркала, включающую в себя третий транзистор, электрически соединенный со вторым транзистором и четвертым транзистором, затвор которого соединен с затвором третьего транзистора, и первый переключающий элемент, соединяющий затвор и сток четвертого транзистора.

[0005] Дополнительные признаки настоящего изобретения явствуют из нижеследующего описания иллюстративных вариантов осуществления со ссылкой на прилагаемые чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

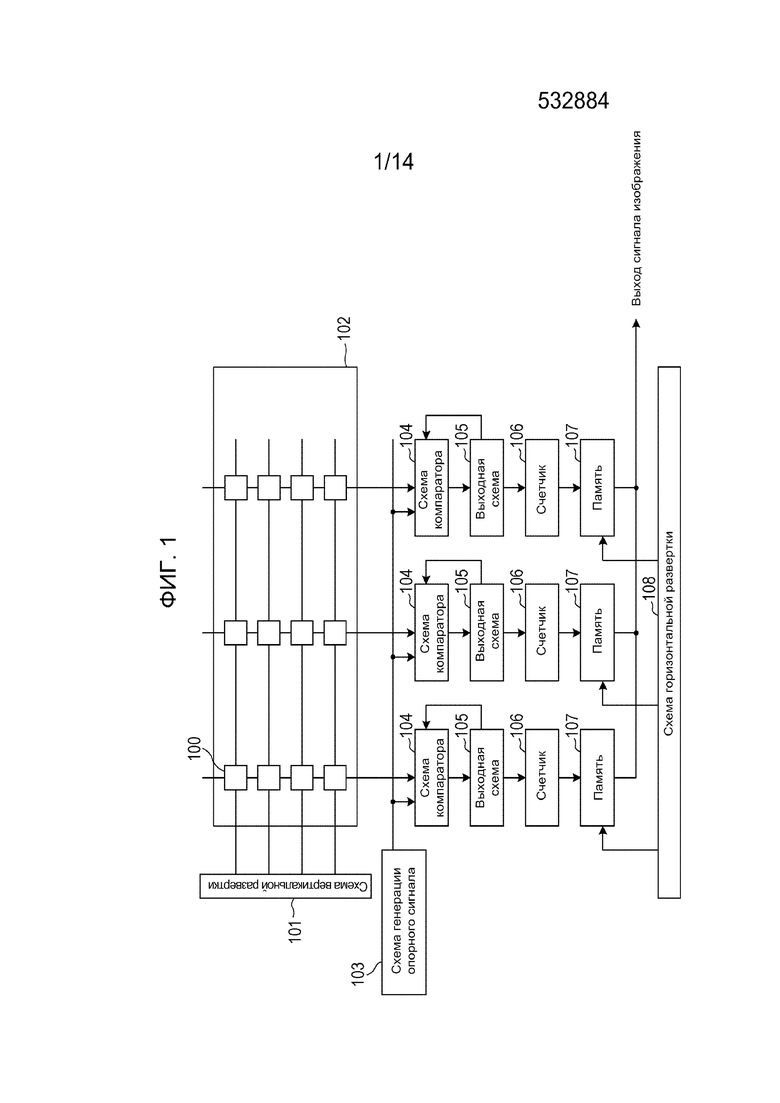

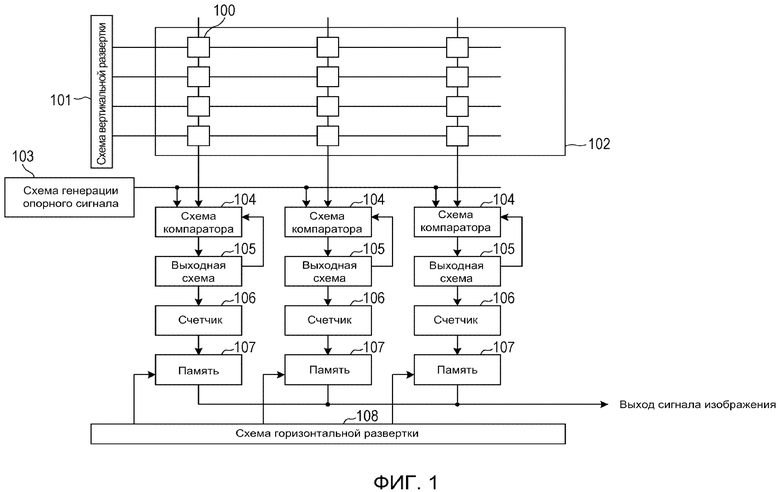

[0006] Фиг. 1 - блок-схема, демонстрирующая общую структуру устройства фотоэлектрического преобразования.

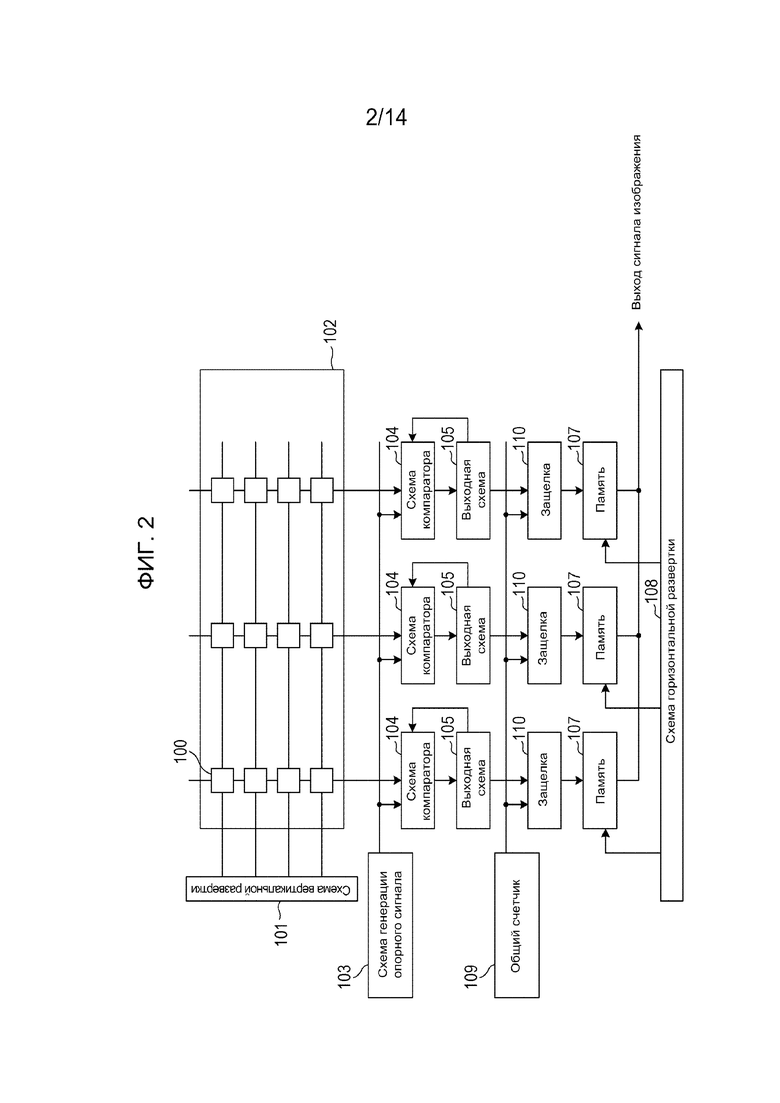

[0007] Фиг. 2 - блок-схема, демонстрирующая общую структуру устройства фотоэлектрического преобразования.

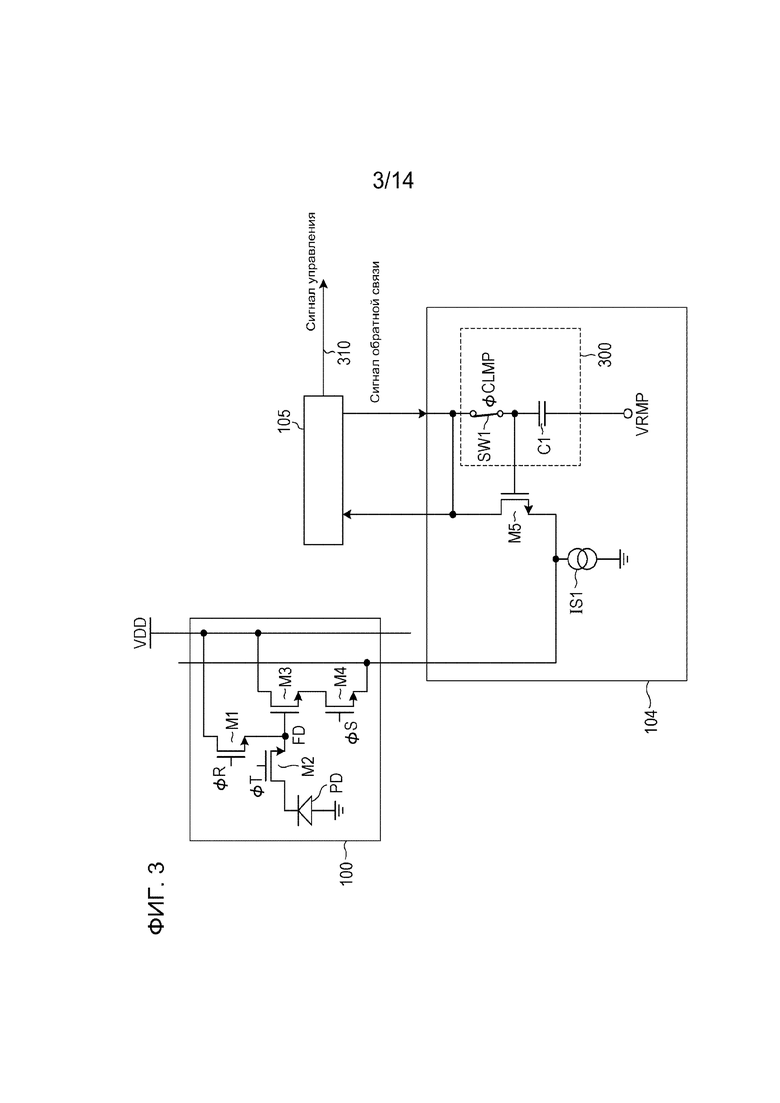

[0008] Фиг. 3 - схема, демонстрирующая структуру устройства фотоэлектрического преобразования.

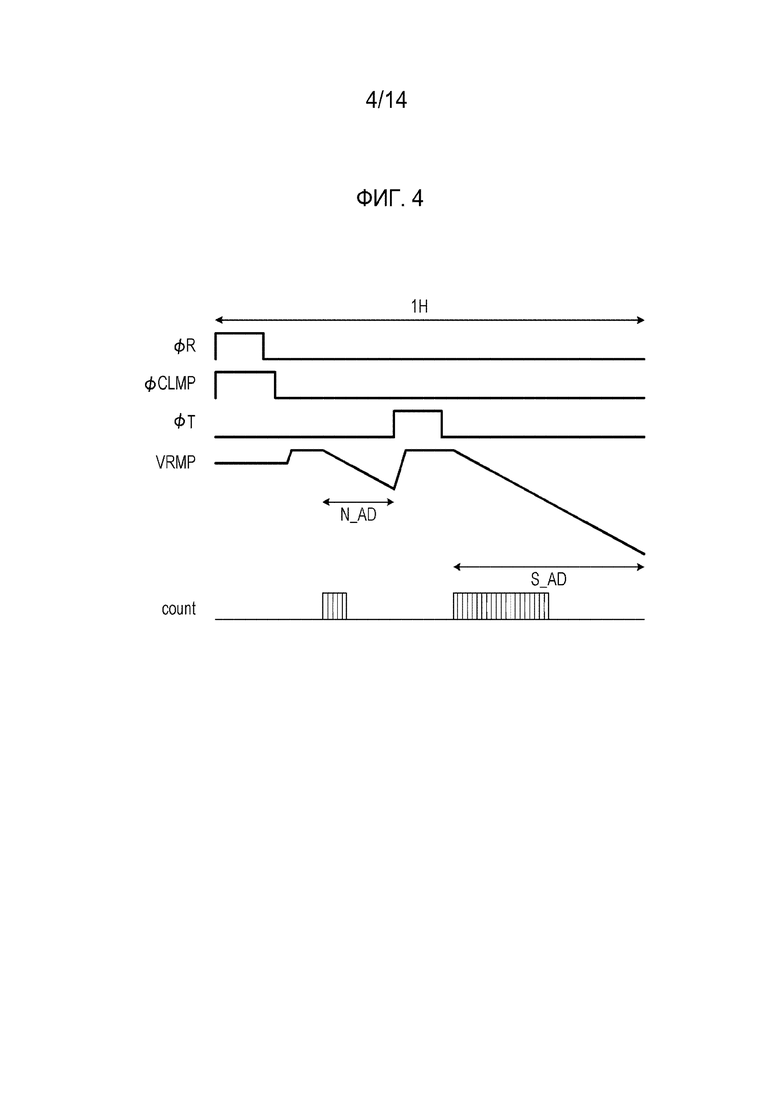

[0009] Фиг. 4 - схема, в упрощенном виде демонстрирующая временную диаграмму в отношении сигналов возбуждения в устройстве фотоэлектрического преобразования.

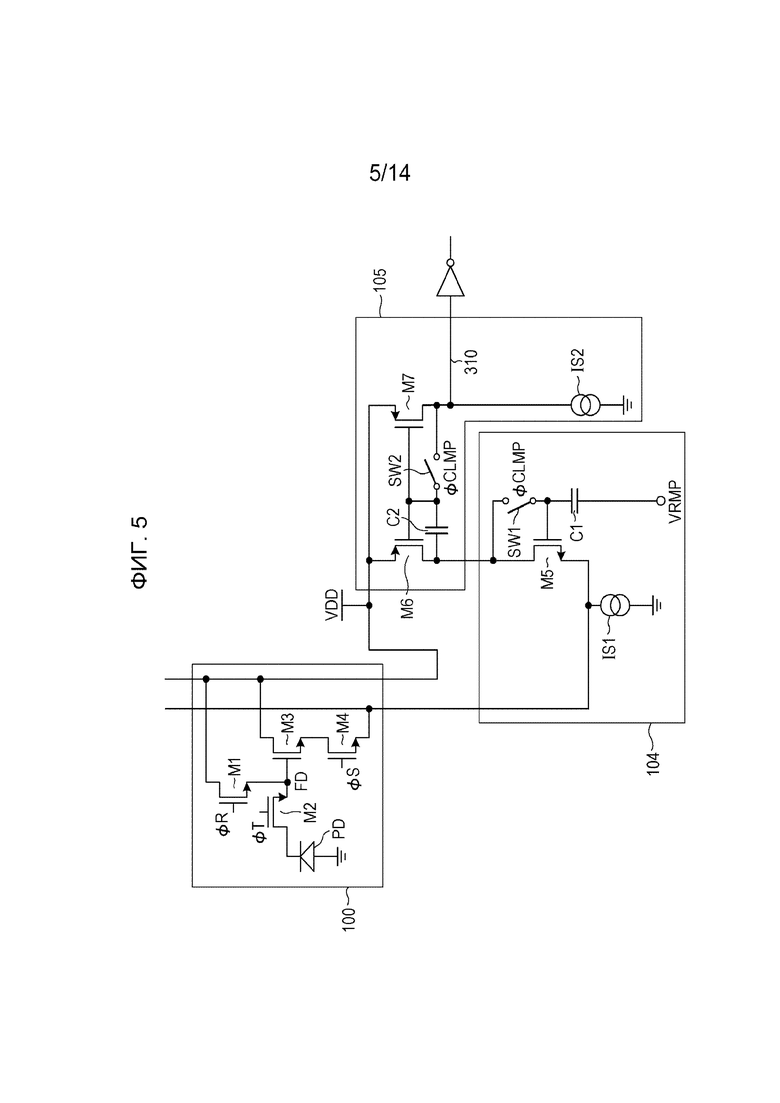

[0010] Фиг. 5 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

[0011] Фиг. 6 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

[0012] Фиг. 7 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

[0013] Фиг. 8 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

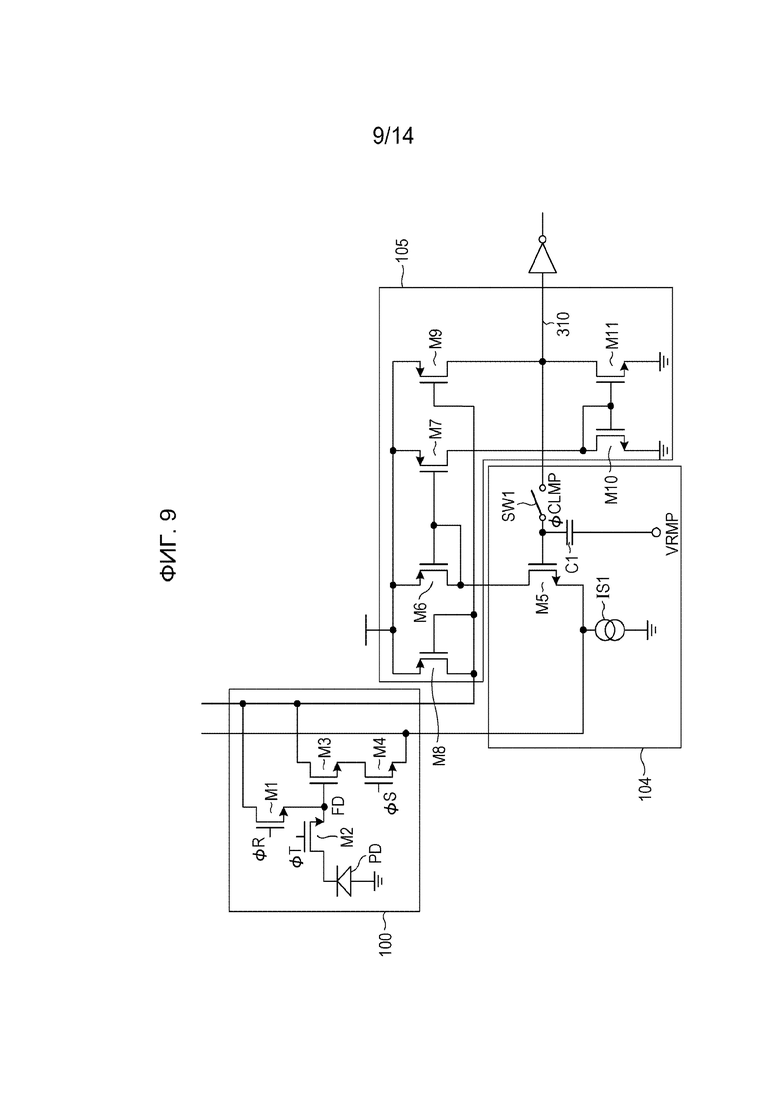

[0014] Фиг. 9 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

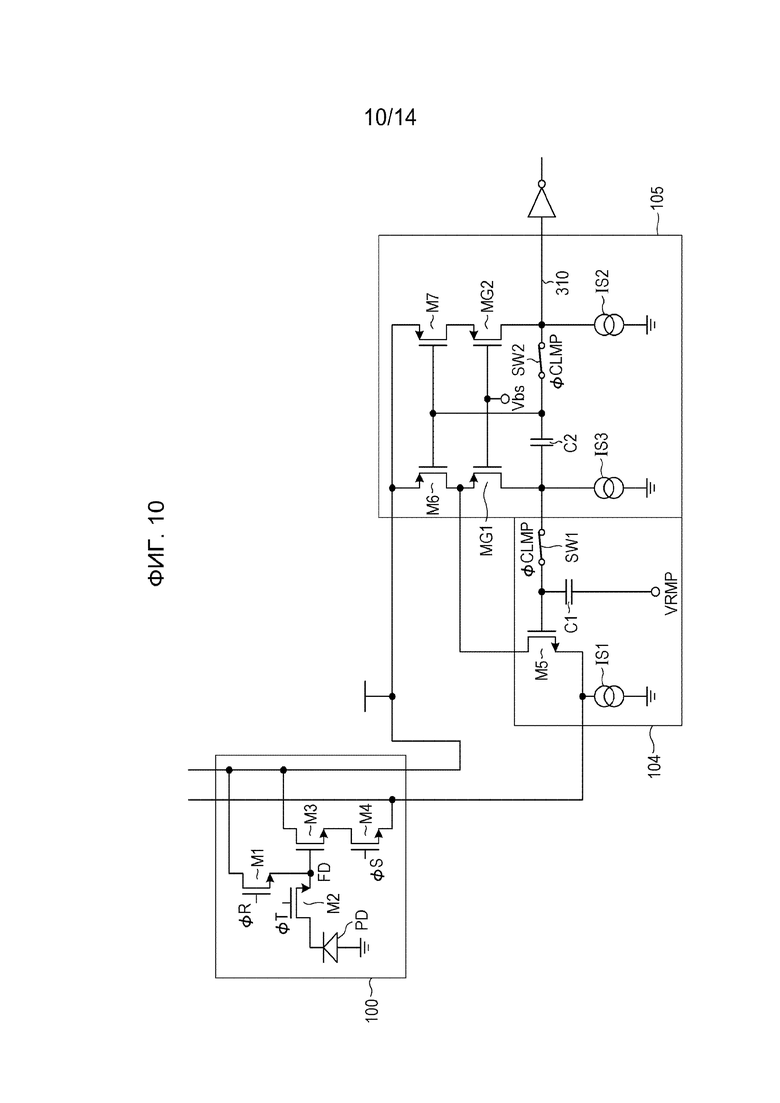

[0015] Фиг. 10 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

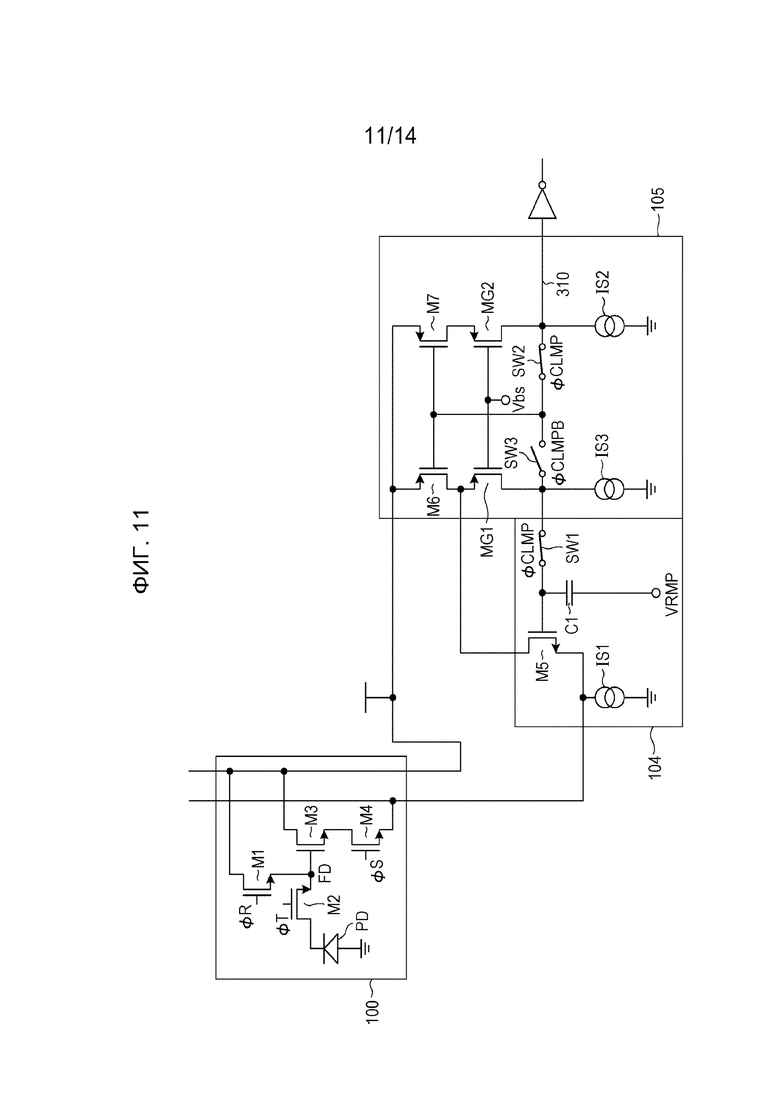

[0016] Фиг. 11 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

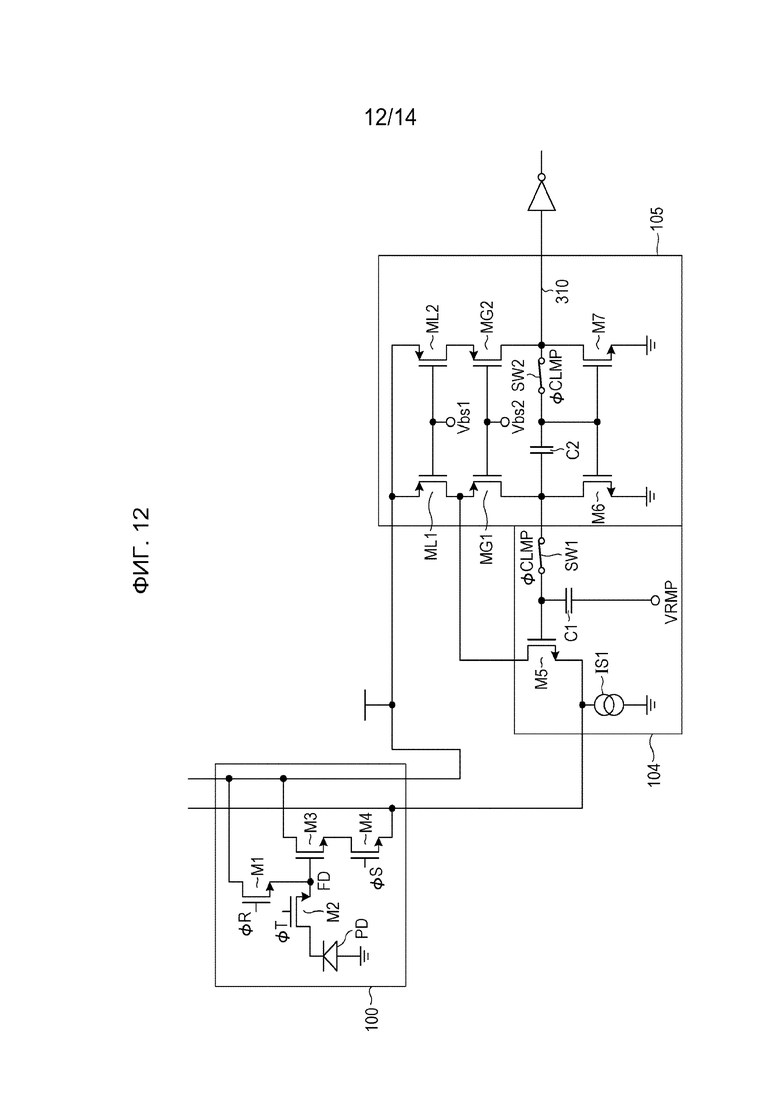

[0017] Фиг. 12 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

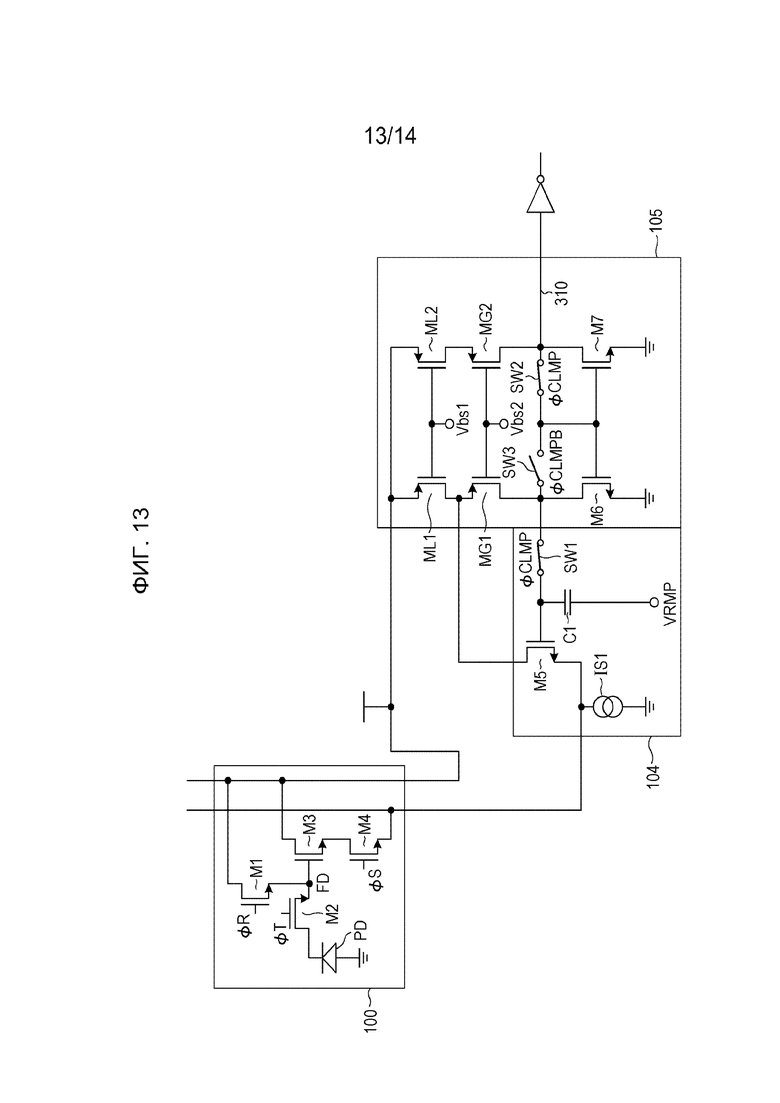

[0018] Фиг. 13 - схема, демонстрирующая принципиальную схему устройства фотоэлектрического преобразования.

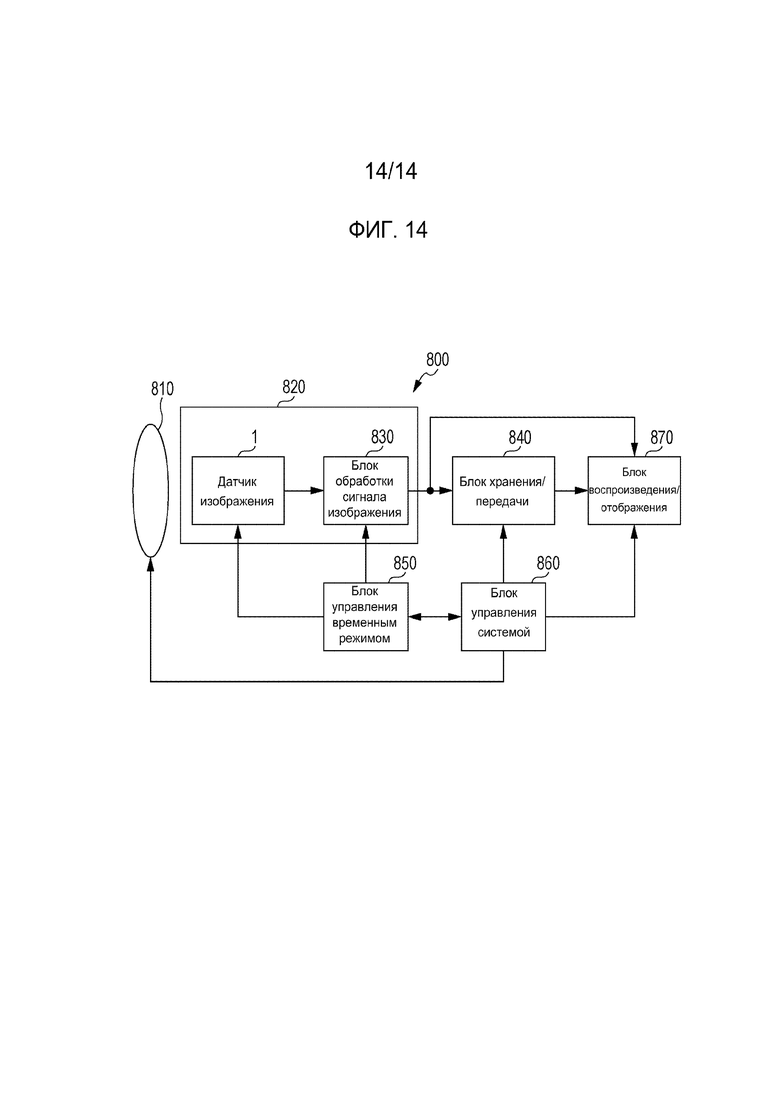

[0019] Фиг. 14 - схема, демонстрирующая структуру системы фотоэлектрического преобразования.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0020] Некоторые варианты осуществления могут повышать точность сигнала, выводимого из устройства фотоэлектрического преобразования.

[0021] В устройстве фотоэлектрического преобразования, существует возможность снижения точности сигнала, выводимого из устройства фотоэлектрического преобразования. В устройстве фотоэлектрического преобразования, раскрытом на фиг. 2 в PTL 1, сток дифференциального транзистора функционирует как выходной узел дифференциального усилителя. Поэтому в операции сравнения, когда происходит инверсия соотношения напряжения между напряжением на затворе транзистора усиления пикселя и напряжением на затворе дифференциального транзистора, т.е. соотношение напряжения инвертируется, напряжение на стоке дифференциального транзистора может значительно изменяться. В частности, величина изменения напряжения на стоке дифференциального транзистора близка к, или примерно равна разности между напряжением земли и напряжением питания (AVD на фиг. 2). Изменение напряжения на стоке дифференциального транзистора может передаваться на затвор дифференциального транзистора, который соединен с узлом, подающим опорный сигнал, через паразитную емкость между затвором и стоком дифференциального транзистора.

[0022] Изменение напряжения на узле, подающем опорный сигнал, может приводить к снижению точности сигнала, выводимого из устройства фотоэлектрического преобразования. Например, если опорный сигнал изменяется в противоположном направлении после инверсии выхода дифференциального усилителя, это может приводить к тому, что выход этого дифференциального усилителя повторно инвертируется. Кроме того, в случае, когда общий опорный сигнал поступает на множество дифференциальных усилителей, изменение опорного сигнала, вызванное инверсией выхода определенного дифференциального усилителя может приводить к инверсии выхода другого дифференциального усилителя. Это может снижать точность аналого-цифрового преобразования. Таким образом, существует возможность уменьшения или снижения точности цифрового сигнала, выводимого из устройства фотоэлектрического преобразования.

[0023] Ниже, со ссылкой на чертежи, описаны аспекты настоящего изобретения. Аспекты, объясненные далее, в целом, относятся к вариантам осуществления с первого по десятый. На фиг. 1 показана блок-схема, в упрощенном виде демонстрирующая общую конфигурацию устройства фотоэлектрического преобразования согласно аспекту. Множество пикселей 100 образует пиксельную матрицу 102. Пиксельная матрица 102 включает в себя множество строк пикселей и множество столбцов пикселей. Схема 101 вертикальной развертки управляет множеством пикселей 100 для считывания сигналов из множества пикселей 100. Сигналы из множества пикселей 100 считываются, например, построчно.

[0024] Схема 104 компаратора сравнивает сигнал пикселя 100 с опорным сигналом. Опорный сигнал, генерируемый схемой 103 генерации опорного сигнала, поступает на схему 104 компаратора. Сигнал управления на основании результата сравнения, произведенного схемой 104 компаратора, выводится на счетчик 106 через выходную схему 105. Этот сигнал управления на основании результата сравнения управляет периодом отсчета счетчика 106. Счетчик 106 выводит, в память 107, значение отсчета, соответствующее времени приема сигнала управления, или указывающее его. Значение отсчета, выводимое в память 107, сохраняется в ней в качестве цифрового сигнала, указывающего результат аналого-цифрового преобразования (в дальнейшем именуемого AD преобразованием), осуществляемого на сигнале из пикселя 100. Цифровой сигнал, хранящийся в памяти 107, последовательно выводится из устройства фотоэлектрического преобразования через схему 108 горизонтальной развертки.

[0025] Кроме того, выходная схема 105 выводит сигнал как сигнал обратной связи на основании сигнала пикселя 100 на схему 104 компаратора. Схема 104 компаратора способна поддерживать сигнал обратной связи.

[0026] На фиг. 2 показана блок-схема, демонстрирующая общую конфигурацию устройства фотоэлектрического преобразования согласно другому аспекту. В случае устройства фотоэлектрического преобразования, представленного на фиг. 1, в каждом столбце пикселей располагается по одному счетчику 106. Устройство фотоэлектрического преобразования, представленное на фиг. 2, отличается от устройства фотоэлектрического преобразования, представленного на фиг. 1, тем, что общий счетчик 109 совместно используется множеством столбцов пикселей. В частности, значение отсчета, выводимое общим счетчиком 109, поступает на защелку 110 в каждом столбце пикселей. В зависимости от времени вывода сигнала управления из выходной схемы 105, защелка 110 каждого столбца пикселей фиксирует значение отсчета, выводимое из общего счетчика. Другие операции аналогичны операциям устройства фотоэлектрического преобразования, представленного на фиг. 1.

[0027] Фиг. 3 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 3 показан только один пиксель 100.

[0028] Пиксель 100 включает в себя элемент PD фотоэлектрического преобразования, транзистор M1 сброса, транзистор M2 переноса, пиксельный транзистор M3 и транзистор M4 выбора. Возбуждающий сигнал ϕR поступает на затвор транзистора M1 сброса, возбуждающий сигнал ϕT поступает на затвор транзистора M2 переноса, и возбуждающий сигнал ϕS поступает на затвор транзистора M4 выбора.

[0029] Затвор пиксельного транзистора M3 соединен с узлом плавающей диффузионной области (в дальнейшем именуемым FD). Электрический заряд, генерируемый в элементе PD фотоэлектрического преобразования, переносится транзистором M2 переноса на узел FD. Таким образом, сигнал на основании электрического заряда, генерируемого в элементе PD фотоэлектрического преобразования, поступает на затвор пиксельного транзистора M3. Другими словами, пиксельный транзистор M3 принимает сигнал на основании электрического заряда, генерируемого в элементе PD фотоэлектрического преобразования, на своем затворе. Транзистор M1 сброса сбрасывает напряжение на затворе пиксельного транзистора M3. Заметим, что поскольку затвор пиксельного транзистора M3 соединен с узлом FD, затвор пиксельного транзистора M3 также именуется узлом FD в настоящем описании.

[0030] Схема 104 компаратора включает в себя дифференциальный транзистор M5. Опорный сигнал VRMP поступает на затвор дифференциального транзистора M5. Другими словами, дифференциальный транзистор M5 принимает опорный сигнал на своем затворе. Опорный сигнал VRMP является, например, пилообразным сигналом напряжения, напряжение которого изменяется со временем. Пиксельный транзистор M3 и дифференциальный транзистор M5 могут быть соединены с источником IS1 следового тока, образуя дифференциальную пару. На фиг. 3, источник IS1 следового тока может быть выполнен в виде, например, n-МОП-транзистора, на затвор которого подается конкретное напряжение смещения. В некоторых вариантах осуществления источник IS1 следового тока можно исключить. Пиксельный транзистор M3 и дифференциальный транзистор M5 одинаковы в отношении типа проводимости. В настоящем аспекте, пиксельный транзистор M3 и дифференциальный транзистор M5 являются МОП-транзисторами с каналом N-типа.

[0031] Схема 104 компаратора включает в себя фиксирующую схему 300, которая фиксирует напряжение на затворе дифференциального транзистора M5 равным конкретному напряжению. Фиксирующая схема 300 включает в себя, например, фиксирующий переключающий элемент SW1 и фиксирующий конденсаторный элемент C1. Фиксирующий переключающий элемент SW1 соединен с затвором дифференциального транзистора M5. Фиксирующий переключающий элемент SW1 управляется возбуждающим сигналом ϕCLMP. Когда фиксирующий переключающий элемент SW1 закрывается, затвор дифференциального транзистора M5 переходит в состояние высокого электрического импеданса. Это позволяет фиксировать напряжение на затворе дифференциального транзистора M5 равным конкретному напряжению. Один электрод фиксирующего конденсаторного элемента C1 соединен с затвором дифференциального транзистора M5. На другой электрод фиксирующего конденсаторного элемента C1 поступает опорный сигнал VRMP. В этой конфигурации, составляющая переменного тока опорного сигнала VRMP поступает на затвор дифференциального транзистора M5 через фиксирующий конденсаторный элемент C1.

[0032] Одна схема 104 компаратора, показанная на фиг. 3, предназначена для множества пикселей 100, включенных в один столбец пикселей, хотя они не показаны на фиг. 3. В частности, истоки транзисторов M4 выбора множества пикселей 100 совместно соединены с источником IS1 следового тока. Кроме того, стоки пиксельных транзисторов множества пикселей 100 соединены друг с другом. Один дифференциальный транзистор M5 образует дифференциальную пару совместно с каждым пиксельным транзистором M3 множества пикселей 100, включенных в один столбец пикселей. Другими словами, каждый пиксельный транзистор M3, включенный в каждый из множества пикселей 100, и дифференциальный транзистор M5 образуют дифференциальную пару. Устройство фотоэлектрического преобразования для использования при захвате изображения, то есть устройство получения изображения, включает в себя множество наборов из столбца пикселей и схемы 104 компаратора.

[0033] Выходная схема 105, имеющая выходной узел 310, электрически соединена с дифференциальным транзистором M5. Выходной узел 310 представляет собой узел, отличный от любого из истока и стока пиксельного транзистора M3 и истока и стока дифференциального транзистора M5.

[0034] Выходная схема 105 осуществляет первую операцию, в которой напряжение на основании напряжения на затворе пиксельного транзистора M3 выводится на затвор дифференциального транзистора M5. Выходная схема 105 также осуществляет вторую операцию, в которой выходная схема 105 принимает ток от дифференциального транзистора M5, и выводит сигнал на основании результата сравнения между напряжением на затворе пиксельного транзистора M3 и напряжением на затворе дифференциального транзистора M5 на выходной узел 310. В другом аспекте, выходная схема 105 во второй операции выводит сигнал на основании результата сравнения между напряжением на затворе пиксельного транзистора M3 и напряжением на затворе дифференциального транзистора M5 на выходной узел 310, принимая ток от дифференциального транзистора M5. В еще одном аспекте, выходная схема 105 во второй операции выводит сигнал на основании результата сравнения между напряжением на затворе пиксельного транзистора M3 и напряжением на затворе дифференциального транзистора M5 на выходной узел 310 в ответ на прием тока от дифференциального транзистора M5. На фиг. 3, "сигнал обратной связи" обозначает напряжение на основании напряжения на затворе пиксельного транзистора M3, и "сигнал управления" обозначает сигнал на основании результата сравнения.

[0035] В первой операции выходная схема 105 может действовать как источник тока, который подает ток на дифференциальный транзистор M5. В этом случае, выходная схема 105 функционирует как нагрузка операционного усилителя, образованного пиксельным транзистором M3 и дифференциальным транзистором M5. Таким образом, когда затвор и сток дифференциального транзистора M5 накоротко соединены друг с другом, выходная схема 105 выводит напряжение на основании напряжения на затворе пиксельного транзистора M3 на затвор дифференциального транзистора M5.

[0036] При закрытии фиксирующего переключающего элемента SW1, фиксирующая схема 300 поддерживает напряжение, выводимое на затвор дифференциального транзистора M5. Таким образом, фиксирующая схема 300 фиксирует напряжение на затворе дифференциального транзистора M5 равным напряжению на основании напряжения на затворе пиксельного транзистора M3. Напряжение на основании напряжения на затворе пиксельного транзистора M3 включает в себя, например, напряжение, по существу, равное напряжению на затворе пиксельного транзистора M3. Ввиду различия в характеристиках транзисторов, разницы температур, теплового шума и пр., два вышеописанные напряжения могут быть не в точности равны.

[0037] Во второй операции выходная схема 105 может действовать как схема обнаружения тока, которая обнаруживает ток дифференциального транзистора M5. Схема обнаружения тока выводит изменение тока дифференциального транзистора M5 в качестве другого сигнала на выходной узел 310, отличный от стока дифференциального транзистора M5. С использованием этой функции, выходная схема 105 выводит сигнал на основании результата сравнения между напряжением на затворе пиксельного транзистора M3 и напряжением на затворе дифференциального транзистора M5 на выходной узел 310.

[0038] Например, в случае, когда напряжение на затворе дифференциального транзистора M5 выше напряжения на затворе пиксельного транзистора M3, выходная схема 105 выводит первое напряжение на выходной узел 310. С другой стороны, в случае, когда напряжение на затворе дифференциального транзистора M5 ниже напряжения на затворе пиксельного транзистора M3, выходная схема 105 выводит второе напряжение, отличное от первого напряжения, на выходной узел 310.

[0039] В вышеприведенном описании, паразитным сопротивлением проводки, соединенной с источником IS1 следового тока, можно пренебречь. Паразитное сопротивление проводки может приводить к смещению в операционном усилителе, образованным пиксельным транзистором M3 и дифференциальным транзистором M5.

[0040] Выходная схема 105 включает в себя блок управления, который управляет, во второй вышеописанной операции, изменением напряжения на стоке дифференциального транзистора M5, чтобы оно было меньше изменения напряжения на выходном узле 310. В частности, блок управления управляет изменением напряжения на стоке дифференциального транзистора M5, чтобы оно было меньше изменения напряжения на выходном узле 310, когда происходит инверсия соотношения относительных величин между величиной напряжения на затворе пиксельного транзистора M3 и величиной напряжения на затворе дифференциального транзистора M5. В этом случае, изменение напряжения на выходном узле 310 можно задавать как разность между вышеописанными первым напряжением и вторым напряжением.

[0041] Блок управления может включать в себя схему токового зеркала. Схема токового зеркала включает в себя, по меньшей мере, два транзистора, затвор каждого из которых соединен с затвором другого из двух транзисторов. Сток одного из двух транзисторов электрически соединен с дифференциальным транзистором M5.

[0042] Блок управления может включать в себя переключающий элемент, который соединяет затвор и сток другого из двух транзисторов, причем этот другой из двух транзисторов отличается от того, сток которого электрически соединен с дифференциальным транзистором M5. Использование этого переключающего элемента позволяет переключаться между вышеописанными первой операцией и второй операцией. Другими словами, переключение между первой операцией и второй операцией может осуществляться в ответ на изменение открытого/закрытого состояния переключающих элементов.

[0043] Как описано выше, выходная схема 105 включает в себя блок управления, который уменьшает изменение напряжения на стоке дифференциального транзистора M5. Эта конфигурация позволяет уменьшать изменение опорного сигнала вследствие изменения напряжения на стоке дифференциального транзистора M5. В результате, можно повышать точность сигнала, выводимого из устройства фотоэлектрического преобразования.

[0044] Затем, возбуждение устройства фотоэлектрического преобразования согласно настоящему варианту осуществления описано ниже. На фиг. 4 показана схема, в упрощенном виде демонстрирующая временную диаграмму в отношении сигналов возбуждения в устройстве фотоэлектрического преобразования. На фиг. 4 показаны сигналы возбуждения на протяжении одного периода горизонтальной развертки (период 1H) в течение которого сигнал считывается из одной строки пикселей. Когда возбуждающий сигнал находится на высоком уровне, транзисторы, на которые поступает этот возбуждающий сигнал, открываются. Когда возбуждающий сигнал находится на низком уровне, транзисторы, на которые поступает этот возбуждающий сигнал, закрываются. Конкретное напряжение высокого уровня и низкого уровня определяются в зависимости от типа проводимости транзисторов.

[0045] В настоящем варианте осуществления, когда возбуждающий сигнал ϕCLMP находится на высоком уровне, выходная схема 105 действует как источник тока. Когда возбуждающий сигнал ϕCLMP находится на низком уровне, выходная схема 105 действует как схема обнаружения тока.

[0046] Сначала возбуждающий сигнал ϕR и возбуждающий сигнал ϕCLMP устанавливаются на высокий уровень. В результате, транзистор M1 сброса и фиксирующий переключающий элемент SW1 переходят во открытое состояние, то есть, они открываются. Напряжение на узле FD сбрасывается на конкретное напряжение, например, напряжение питания VDD (в дальнейшем именуемое уровнем сброса). Одновременно, выходная схема 105 выводит напряжение на основании напряжения на узле FD (в дальнейшем именуемое уровнем фиксации) на затвор дифференциального транзистора M5 и фиксирующий конденсаторный элемент C1. Таким образом, выходная схема 105 осуществляет первую операцию, в которой напряжение на основании напряжения на затворе пиксельного транзистора M3 выводится на затвор дифференциального транзистора M5.

[0047] После этого, возбуждающий сигнал ϕR и возбуждающий сигнал ϕCLMP последовательно изменяются до низкого уровня. В результате, уровень сброса поддерживается узлом FD, и уровень фиксации поддерживается фиксирующим конденсаторным элементом C1. Благодаря закрытию транзистора M1 сброса до закрытия фиксирующего переключающего элемента SW1, тепловой шум, генерируемый в транзисторе M1 сброса, влияет на уровень фиксации. В состоянии сразу после закрытия фиксирующего переключающего элемента SW1, напряжение на узле FD, то есть напряжение на затворе пиксельного транзистора M3 примерно равно напряжению на затворе дифференциального транзистора M5.

[0048] Затем опорный сигнал VRMP меняется на более высокое напряжение. В результате, напряжение на затворе дифференциального транзистора M5 повышается относительно напряжения на затворе пиксельного транзистора M3. Поскольку пиксельный транзистор M3 и дифференциальный транзистор M5 образуют дифференциальную пару, большая часть тока источника IS1 следового тока течет через дифференциальный транзистор M5.

[0049] Затем на опорном сигнале VRMP начинается линейное снижение. Линейное снижение является операцией постепенного снижения напряжения опорного сигнала VRMP. В определенное время происходит инверсия соотношения между величиной напряжения на затворе пиксельного транзистора M3 и величиной напряжения на затворе дифференциального транзистора M5. После возникновения инверсии этого соотношения, большая часть тока источника IS1 следового тока течет через пиксельный транзистор M3, и ток дифференциального транзистора M5 снижается.

[0050] Выходная схема 105 обнаруживает изменение тока дифференциального транзистора M5. В частности, во время, когда происходит уменьшение тока дифференциального транзистора M5, выходная схема 105 выводит сигнал, указывающий возникновение изменения тока, в качестве сигнала управления, на выходной узел 310. Другими словами, выходная схема 105 осуществляет вторую операцию, в которой сигнал на основании результата сравнения между напряжением на затворе пиксельного транзистора M3 и напряжением на затворе дифференциального транзистора M5 выводится на выходной узел 310.

[0051] В устройстве фотоэлектрического преобразования, показанном на фиг. 1, сигнал управления управляет счетчиком 106 для измерения времени от начала линейного снижения до возникновения инверсии соотношения величин напряжения. В устройстве фотоэлектрического преобразования, показанном на фиг. 2, сигнал управления управляет защелкой 110 для измерения времени от начала линейного снижения до возникновения инверсии соотношения величин напряжения. По истечении заранее определенного периода с начала линейного снижения, AD преобразование уровня сброса заканчивается. Период, в течение которого осуществляется AD преобразование уровня сброса, обозначен N_AD на фиг. 4.

[0052] После этого опорный сигнал VRMP сбрасывается. При переходе возбуждающего сигнала ϕT на высокий уровень, транзистор M2 переноса открывается, и электрический заряд, генерируемый в элементе PD фотоэлектрического преобразования, переносится на узел FD. В настоящем описании, напряжение на узле FD в состоянии после переноса заряда из элемента PD фотоэлектрического преобразования на узел FD именуется уровнем оптического сигнала.

[0053] После перехода возбуждающего сигнала ϕT на низкий уровень, начинается линейное снижение опорного сигнала VRMP. Затем AD преобразование уровня оптического сигнала осуществляется аналогично AD преобразованию уровня сброса. Период, в течение которого осуществляется AD преобразование уровня оптического сигнала, обозначен S_AD на фиг. 4.

[0054] Хотя здесь не приведено подробное описание, в устройстве фотоэлектрического преобразования, цифровая коррелированная двухступенчатая выборка (CDS) может осуществляться путем вычитания кодового значения, полученного AD-преобразованием уровня сброса из кодового значения, полученного AD-преобразованием уровня оптического сигнала.

[0055] В настоящем варианте осуществления, выходная схема 105 включает в себя блок управления, который уменьшает изменение напряжения на стоке дифференциального транзистора M5. Поэтому, в вышеописанной операции, когда происходит инверсия соотношения напряжения, изменение напряжения на стоке дифференциального транзистора M5 подавляется. Таким образом, можно уменьшить изменение опорного сигнала VRMP. В результате, можно повысить точность цифрового сигнала, выводимого из устройства фотоэлектрического преобразования.

[0056] В вышеописанном аспекте, дифференциальный транзистор M5 образует дифференциальную пару совместно с пиксельным транзистором M3 в каждом из пикселей 100. Однако, в альтернативном аспекте, дифференциальный транзистор M5 может образовывать дифференциальную пару совместно с транзистором, который не включен ни в один пиксель 100. Например, сигнал, выводимый из каждого пикселя 100, выводится усилительным блоком, включенным в каждый пиксель 100, в общую линию сигнала. Затем сигнал на общей выходной линии поступает на затвор вышеописанного транзистора, образующего дифференциальную пару совместно с дифференциальным транзистором M5. Также в вышеописанном альтернативном аспекте, можно повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

[0057] Ниже описаны некоторые варианты осуществления согласно настоящему изобретению. Если не указано обратное, вышеописанные аспекты применяются ко всем вариантам осуществления. Заметим, что часть варианта осуществления можно заменить частью другого варианта осуществления, или часть варианта осуществления можно добавить к другому варианту осуществления.

ПЕРВЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[0058] Ниже описано устройство фотоэлектрического преобразования согласно первому варианту осуществления. Первый вариант осуществления отличается тем, что блок управления выходной схемы 105 включает в себя схему токового зеркала.

[0059] Фиг. 5 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 5 показан только один пиксель 100. Части, аналогичные по функции показанным на фиг. 3, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[0060] Блок управления выходной схемы 105 включает в себя схему токового зеркала, включающую в себя МОП-транзистор M6 с каналом P-типа и МОП-транзистор M7 с каналом P-типа. Сток транзистора M6 электрически соединен со стоком дифференциального транзистора M5. Затвор транзистора M6 и затвор транзистора M7 соединены друг с другом.

[0061] Когда выходная схема 105 осуществляет первую операцию, схема токового зеркала, образованная транзисторами M6 и M7, отражает ток транзистора M7 на транзистор M6. Когда выходная схема 105 осуществляет вторую операцию, схема токового зеркала отражает ток транзистора M6 на транзистор M7.

[0062] В настоящем варианте осуществления, в первой операции схема токового зеркала действует как источник тока, который подает ток из транзистора M6 на дифференциальный транзистор M5. Во второй операции схема токового зеркала действует как схема обнаружения тока, которая отражает ток, поступающий на транзистор M6, от дифференциального транзистора M5 на транзистор M7.

[0063] Блок управления выходной схемы 105 включает в себя конденсаторный элемент C2. Первый вывод конденсаторного элемента C2 электрически соединен со стоком транзистора M6, и второй вывод электрически соединен с затвором транзистора M6. Посредством конденсаторного элемента C2, сток и затвор транзистора M6 связаны друг с другом по переменному току, что позволяет отражать ток транзистора M6 на транзистор M7.

[0064] Блок управления выходной схемы 105 включает в себя первый переключающий элемент SW2. Первый переключающий элемент SW2 соединяет затвор и сток транзистора M7. При открытии первого переключающего элемента SW2, схема токового зеркала способна отражать ток транзистора M7 на транзистор M6. При закрытии первого переключающего элемента SW2, схема токового зеркала способна отражать ток транзистора M6 на транзистор M7. Таким образом, первый переключающий элемент SW2 переключается между первой операцией и второй операцией, осуществляемыми выходной схемой 105.

[0065] Заметим, что емкость конденсаторного элемента C2 больше емкости связи между двумя концами первого переключающего элемента SW2 в состоянии, в котором первый переключающий элемент SW2 находится в закрытом состоянии. В случае, когда МОП-транзистор используется в качестве первого переключающего элемента SW2, два конца первого переключающего элемента SW2 являются истоком и стоком этого МОП-транзистора. Вышеописанная конфигурация позволяет повысить устойчивость работы схемы токового зеркала.

[0066] Фиксирующая схема 300 включает в себя фиксирующий переключающий элемент SW1 и фиксирующий конденсаторный элемент C1. В настоящем варианте осуществления, фиксирующий переключающий элемент SW1 соединяет затвор и сток дифференциального транзистора M5. Фиксирующий переключающий элемент SW1 может электрически соединять затвор и сток дифференциального транзистора M5 посредством схемы с общим затвором.

[0067] Может быть желательно, чтобы фиксирующий переключающий элемент SW1 и первый переключающий элемент SW2 действовали синфазно. В настоящем варианте осуществления, благодаря управлению фиксирующим переключающим элементом SW1 и первым переключающим элементом SW2 с использованием общего возбуждающего сигнала ϕCLMP, фиксирующий переключающий элемент SW1 и первый переключающий элемент SW2 действуют синфазно.

[0068] В настоящем варианте осуществления, выходная схема 105 включает в себя источник IS2 опорного тока, соединенный с выходным узлом 310. Источник IS2 опорного тока выводит опорный ток на транзистор M7. Выходной узел 310 соединен со схемой инвертора.

[0069] В настоящем варианте осуществления, устройство фотоэлектрического преобразования возбуждается сигналами возбуждения, показанными на фиг. 4. В течение периода, в течение которого возбуждающий сигнал ϕCLMP находится на высоком уровне, фиксирующий переключающий элемент SW1 и первый переключающий элемент SW2 открываются. Опорный ток из источника IS2 опорного тока выводится на дифференциальный транзистор M5 через токовое зеркало, образованное транзисторами M6 и M7. Таким образом, транзистор M6 действует как источник тока, который подает ток на дифференциальный транзистор M5.

[0070] Фиксирующий переключающий элемент SW1 соединяет затвор и сток дифференциального транзистора M5. В результате, пиксельный транзистор M3, дифференциальный транзистор M5 и источник IS1 следового тока действуют как повторитель напряжения, в котором источник тока, обеспеченный транзистором M6 функционирует как нагрузка. Таким образом, напряжение на узле FD выводится на затвор дифференциального транзистора M5 и фиксирующий конденсаторный элемент C1. Другими словами, выходная схема 105 осуществляет первую операцию, в которой напряжение на основании напряжения на затворе пиксельного транзистора M3 выводится на затвор дифференциального транзистора M5.

[0071] Когда возбуждающий сигнал ϕCLMP переходит на низкий уровень, фиксирующий переключающий элемент SW1 и первый переключающий элемент SW2 закрываются. После этого, выходная схема 105 осуществляет вторую операцию, в которой напряжение на затворе пиксельного транзистора M3 сравнивается с напряжением на затворе дифференциального транзистора M5.

[0072] Как описано выше, затвор и сток транзистора M6 связаны друг с другом по переменному току посредством конденсаторного элемента C2. Поэтому ток, текущий через дифференциальный транзистор M5, отражается из транзистора M6 на транзистор M7. Напряжение на выходном узле 310 изменяется в зависимости от соотношения между величиной отраженного тока и опорного тока из источника IS2 опорного тока. Таким образом, сигнал выводится на выходной узел 310 на основании результата сравнения.

[0073] Здесь описаны примеры значений различных элементов. Например, транзисторы M6 и M7, образующие схему токового зеркала, имеют, по существу, одинаковый размер. Величина тока I_IS1 источника следового тока и величина тока I_IS2 источника IS2 опорного тока по существу, удовлетворяют соотношению I_IS1=2×I_IS2.

[0074] В вышеописанных условиях, в первой операции ток с величиной, примерно равной одной второй величины тока I_IS1 источника IS1 следового тока течет через каждый из пиксельного транзистора M3 и дифференциального транзистора M5, то есть, ток, по существу, равный величине тока I_IS2, течет через каждый из них. Во второй операции, когда напряжение на затворе дифференциального транзистора M5 выше напряжения на затворе пиксельного транзистора M3, большая часть тока источника IS1 следового тока течет через дифференциальный транзистор M5, и ток, по существу, не течет через пиксельный транзистор M3. Поэтому ток, по существу, той же величины, что и источника IS1 следового тока, течет через транзистор M7. В результате, напряжение на стоке транзистора M7, то есть напряжение на выходном узле 310, становится примерно равным напряжению питания VDD.

[0075] Когда опорный сигнал линейно уменьшается, напряжение на затворе дифференциального транзистора M5 становится ниже напряжения на затворе пиксельного транзистора M3. В этом состоянии, большая часть тока источника IS1 следового тока течет через пиксельный транзистор M3, и ток дифференциального транзистора M5 становится, по существу, равным нулю. Поэтому ток транзистора M7 также становится, по существу, равным нулю. В результате, напряжение на стоке транзистора M7, то есть, напряжение на выходном узле 310, становится примерно равным напряжению земли.

[0076] Как описано выше, выходная схема 105 обнаруживает изменение тока дифференциального транзистора M5. В этой операции, транзистор M6 функционирует как вход схемы токового зеркала. Даже в случае изменения тока стока дифференциального транзистора M5, не происходит значительного изменения напряжения на стоке транзистора M6. Другими словами, схема токового зеркала управляет изменением напряжения на стоке дифференциального транзистора M5, чтобы оно было меньше изменения напряжения на выходном узле. Таким образом, можно уменьшить изменение напряжения опорного сигнала VRMP. В результате, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

[0077] В сравнительном примере устройства фотоэлектрического преобразования, раскрытом в патентном документе 1, по окончании операции фиксации, p-МОП-транзистор 203 по-прежнему действует как постоянный источник тока. В этой ситуации, напряжение на стоке дифференциального транзистора 201 считывается как выходной сигнал. Поэтому, когда происходит инверсия соотношения напряжения, происходит значительное изменение напряжения на стоке дифференциального транзистора 201. Это изменение напряжения приводит к изменению напряжения опорного сигнала, которое, в результате, может приводить к снижению качества изображения.

[0078] Как описано выше, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

ВТОРОЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

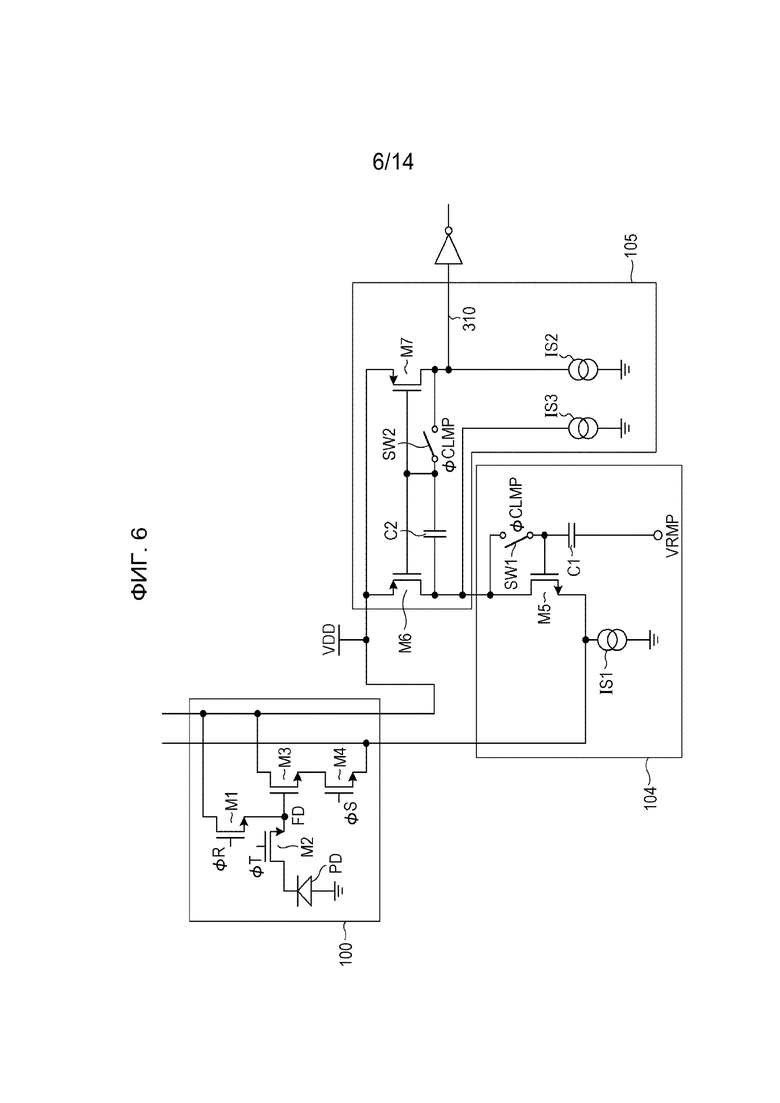

[0079] Ниже описано устройство фотоэлектрического преобразования согласно второму варианту осуществления. Этот вариант осуществления отличается от первого варианта осуществления тем, что выходная схема 105 включает в себя источник IS3 тока. Отличия от первого варианта осуществления описаны ниже, но описание частей, аналогичных соответствующим частям в первом варианте осуществления, опущено.

[0080] Фиг. 6 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 6 показан только один пиксель 100. Части, аналогичные по функции показанным на фиг. 3 или фиг. 5, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[0081] Выходная схема 105 включает в себя источник IS3 тока. Источник IS3 тока соединен со стоком транзистора M6 схемы токового зеркала. Обеспечение источника IS3 тока позволяет предотвратить обнуление тока транзистора M6, когда ток дифференциального транзистора M5 становится, по существу, равным 0. Это позволяет улучшить амплитудно-частотную характеристику выходной схемы 105.

[0082] Здесь описаны примеры значений различных элементов. Может быть желательно, чтобы величина тока I_IS3 источника IS3 тока была меньше величины тока I_IS1 источника IS1 следового тока и величины тока I_IS2 источника IS2 опорного тока. В случае, когда транзисторы M6 и M7, образующие схему токового зеркала, имеют примерно равный размер, может быть желательно, чтобы величина тока I_IS1, величина тока I_IS2 и величина тока I_IS3, по существу, удовлетворяла соотношению I_IS1=2×(I_IS2-I_IS3).

[0083] Как описано выше, настоящий вариант осуществления позволяет повысить быстродействие устройства фотоэлектрического преобразования. Кроме того, как и в первом варианте осуществления, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

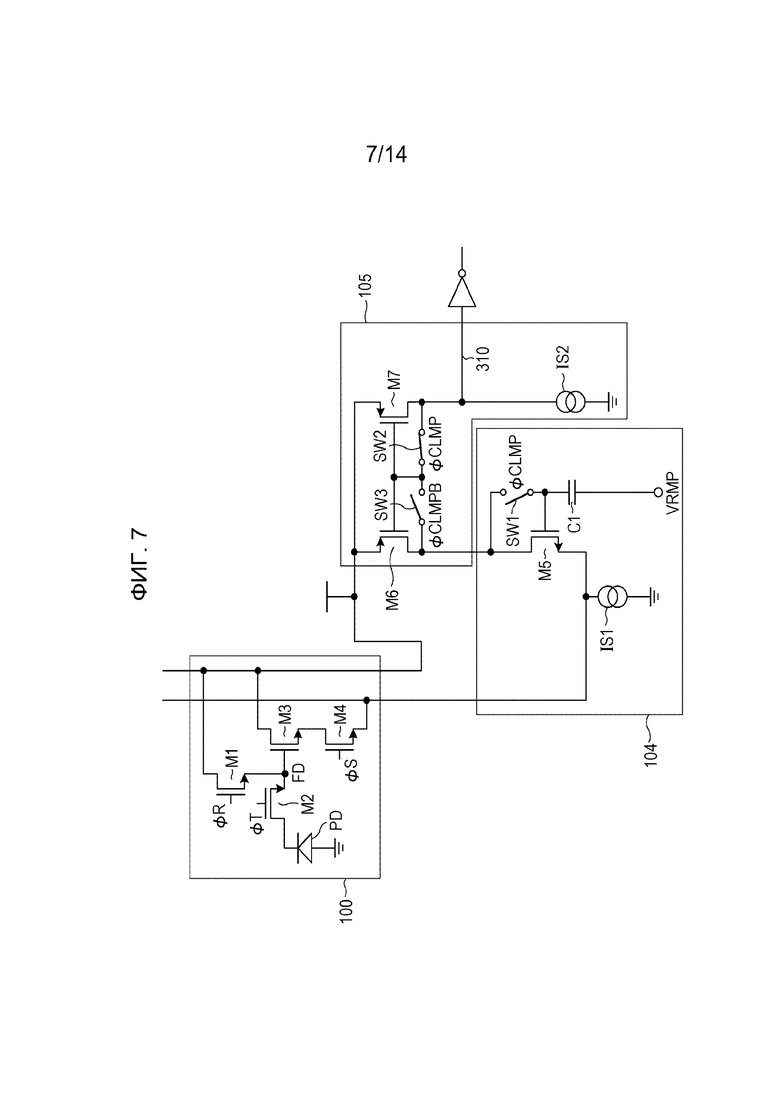

ТРЕТИЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[0084] Ниже описано устройство фотоэлектрического преобразования согласно третьему варианту осуществления. Третий вариант осуществления отличается от первого и второго вариантов осуществления тем, что конденсаторный элемент C2 блока управления выходной схемы 105 заменен вторым переключающим элементом SW3. Отличия от первого и второго вариантов осуществления описаны ниже, но описание частей, аналогичных соответствующим частям в первом или втором варианте осуществления, опущено.

[0085] Фиг. 7 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 7, показан только один пиксель 100. Части, аналогичные по функции показанным на фиг. 3, фиг. 5 или фиг. 6, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[0086] Блок управления выходной схемы 105 включает в себя схему токового зеркала, включающую в себя МОП-транзистор M6 с каналом P-типа и МОП-транзистор M7 с каналом P-типа. Сток транзистора M6 электрически соединен со стоком дифференциального транзистора M5. Затвор транзистора M6 и затвор транзистора M7 соединены друг с другом.

[0087] Когда выходная схема 105 осуществляет первую операцию, схема токового зеркала, образованная транзисторами M6 и M7, отражает ток транзистора M7 на транзистор M6. Когда выходная схема 105 осуществляет вторую операцию, схема токового зеркала отражает ток транзистора M6 на транзистор M7.

[0088] В настоящем варианте осуществления, в первой операции схема токового зеркала действует как источник тока, который подает ток из транзистора M6 на дифференциальный транзистор M5. Во второй операции схема токового зеркала действует как схема обнаружения тока, которая отражает ток, поступающий на транзистор M6, от дифференциального транзистора M5 на транзистор M7.

[0089] Блок управления выходной схемы 105 включает в себя первый переключающий элемент SW2 и второй переключающий элемент SW3. Первый переключающий элемент SW2 соединяет затвор и сток транзистора M7. Второй переключающий элемент SW3 электрически соединяет сток и затвор транзистора M6.

[0090] В настоящем варианте осуществления, первый переключающий элемент SW2 и второй переключающий элемент SW3 действуют попеременно. Другими словами, когда первый переключающий элемент SW2 находится в открытом состоянии, второй переключающий элемент SW3 закрывается. С другой стороны, когда первый переключающий элемент SW2 находится в закрытом состоянии, второй переключающий элемент SW3 открывается. В частности, первый переключающий элемент SW2 управляется возбуждающим сигналом ϕCLMP. Второй переключающий элемент SW3 управляется возбуждающим сигналом ϕCLMPB, который противоположен по фазе возбуждающему сигналу ϕCLMP.

[0091] При открытии первого переключающего элемента SW2 и закрытии второго переключающего элемента SW3, схема токового зеркала способна отражать ток транзистора M7 на транзистор M6. При закрытии первого переключающего элемента SW2 и открытии второго переключающего элемента SW3, схема токового зеркала способна отражать ток транзистора M6 на транзистор M7. Таким образом, первый переключающий элемент SW2 и второй переключающий элемент SW3 переключаются между первой операцией и второй операцией, осуществляемых выходной схемой 105.

[0092] Таким образом, как и в первом варианте осуществления, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

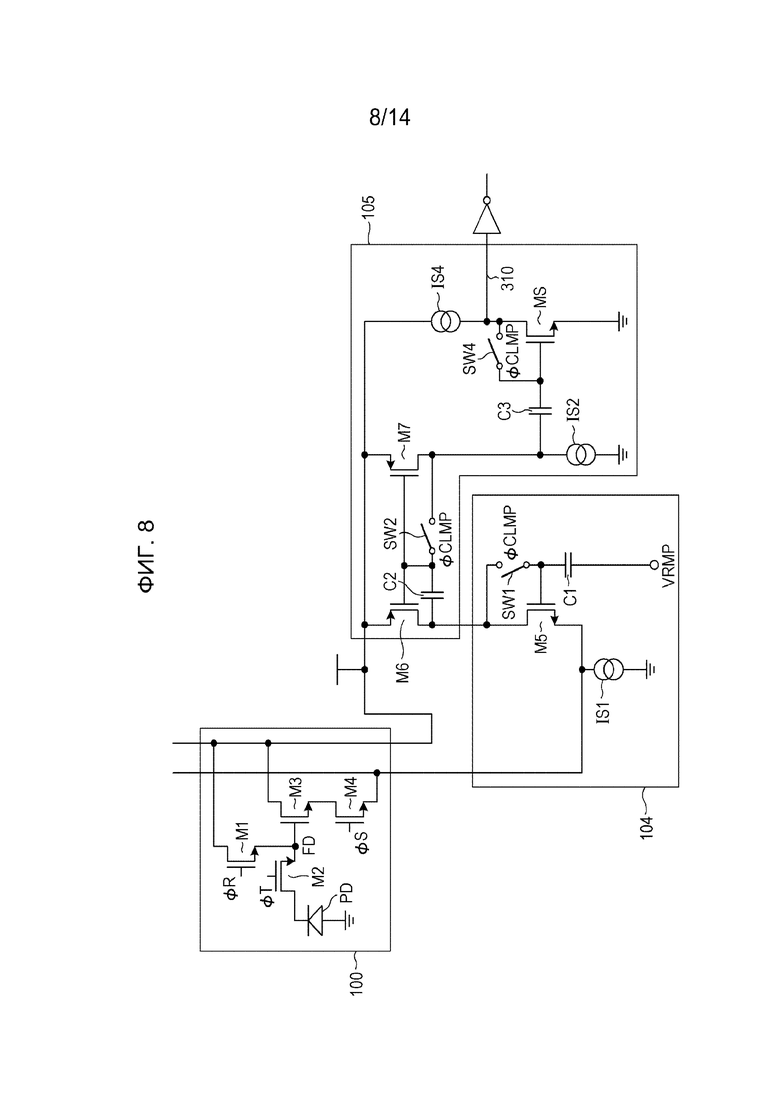

ЧЕТВЕРТЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[0093] Ниже описано устройство фотоэлектрического преобразования согласно четвертому варианту осуществления. Четвертый вариант осуществления отличается от вариантов осуществления с первого по третий тем, что выходная схема 105 включает в себя схему усилителя с общим истоком. Отличия от вариантов осуществления с первого по третий описаны ниже, но описание частей, аналогичных соответствующим частям любого из вариантов осуществления с первого по третий, опущено.

[0094] Фиг. 8 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 8 показан только один пиксель 100. Части, аналогичные по функции показанным на одной из фиг. 3 и фиг. 5-7, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[0095] Выходная схема 105 включает в себя схему усилителя с общим истоком, включающую в себя источник IS4 тока и МОП-транзистор MS с каналом N-типа. Входной узел схемы усилителя с общим истоком соединен со стоком транзистора M7 через конденсаторный элемент C3. Выходной узел схемы усилителя с общим истоком функционирует как выходной узел 310 выходной схемы 105.

[0096] Выходная схема 105 дополнительно включает в себя третий переключающий элемент SW4. Обеспечение третьего переключающего элемента SW4 позволяет, в первой операции фиксировать напряжение входного узла схемы усилителя с общим истоком. Третий переключающий элемент SW4, как и в случае фиксирующего переключающего элемента SW1 и первого переключающего элемента SW2, управляется возбуждающим сигналом ϕCLMP. В течение периода, в течение которого возбуждающий сигнал ϕCLMP находится на высоком уровне, фиксирующий переключающий элемент SW1, первый переключающий элемент SW2 и третий переключающий элемент SW4 открываются, и, таким образом, фиксирующий конденсаторный элемент C1, конденсаторный элемент C2 и конденсаторный элемент C3 фиксируются в своих соответствующих рабочих точках.

[0097] В настоящем варианте осуществления, как описано выше, выходная схема 105 включает в себя схему усилителя с общим истоком. Это позволяет повышать коэффициент усиления во второй операции. Кроме того, как и в первом варианте осуществления, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

ПЯТЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[0098] Ниже описано устройство фотоэлектрического преобразования согласно пятому варианту осуществления. Пятый вариант осуществления отличается от вариантов осуществления с первого по четвертый, тем, что выходная схема 105 включает в себя множество схем токового зеркала. Отличия от вариантов осуществления с первого по четвертый описаны ниже, но описание частей, аналогичных соответствующим частям любой из вариантов осуществления с первого по четвертый, опущено.

[0099] Фиг. 9 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, показан только один пиксель 100 на фиг. 9. Части, аналогичные по функции показанным на одной из фиг. 3 и фиг. 5-8, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[00100] Блок управления выходной схемы 105 включает в себя первую схему токового зеркала, включающую в себя МОП-транзистор M8 с каналом P-типа и МОП-транзистор M9 с каналом P-типа. Сток транзистора M8 электрически соединен со стоком пиксельного транзистора M3. Затвор транзистора M8 и затвор транзистора M9 соединены друг с другом. Первая схема токового зеркала выводит ток пиксельного транзистора M3 на сток, функционирующий как выходной узел первого зеркала, транзистора M9.

[00101] Блок управления выходной схемы 105 включает в себя вторую схему токового зеркала, включающую в себя МОП-транзистор M6 с каналом P-типа и МОП-транзистор M7 с каналом P-типа. Сток транзистора M6 электрически соединен со стоком дифференциального транзистора M5. Затвор транзистора M6 и затвор транзистора M7 соединены друг с другом. Вторая схема токового зеркала выводит ток дифференциального транзистора M5 на сток, функционирующий как выходной узел второго зеркала, транзистора M7.

[00102] Блок управления выходной схемы 105 дополнительно включает в себя третью схему токового зеркала, включающую в себя МОП-транзистор M10 с каналом N-типа и МОП-транзистор M11 с каналом N-типа. Сток транзистора M10 электрически соединен со стоком транзистора M7. Затвор транзистора M10 и затвор транзистора M11 соединены друг с другом. Третья схема токового зеркала выводит выходной узел второго зеркала (сток транзистора M7) на выходной узел первого зеркала (сток транзистора M9).

[00103] Узел, через который сток транзистора M9 и сток транзистора M11, соединены функционирует как выходной узел 310 выходной схемы 105. Фиксирующий переключающий элемент SW1 соединяет затвор дифференциального транзистора M5 и выходной узел 310.

[00104] Когда фиксирующий переключающий элемент SW1 открывается, напряжение на выходном узле 310 возвращается на затвор дифференциального транзистора M5. Таким образом, пиксельный транзистор M3 и дифференциальный транзистор M5 действуют как повторитель напряжения. Как описано выше, выходная схема 105 осуществляет первую операцию, в которой напряжение на основании напряжения на затворе пиксельного транзистора M3 выводится на затвор дифференциального транзистора M5.

[00105] Когда фиксирующий переключающий элемент SW1 закрывается, ток пиксельного транзистора M3 и ток дифференциального транзистора M5 выводятся на выходной узел 310 через транзистор M9 и транзистор M11, соответственно. Ток пиксельного транзистора M3 и ток дифференциального транзистора M5 сравниваются на выходном узле 310, и сигнал, представляющий результат сравнения, выводится на выходной узел 310. Соотношение между током пиксельного транзистора M3 и током дифференциального транзистора M5 определяется соотношением между напряжениями на затворах этих двух транзисторов. Как описано выше, выходная схема 105 осуществляет вторую операцию, в которой напряжение на затворе пиксельного транзистора M3 и напряжение на затворе дифференциального транзистора M5 сравниваются, и сигнал на основании результата сравнения выводится.

[00106] Таким образом, как и в первом варианте осуществления, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

ШЕСТОЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[00107] Ниже описано устройство фотоэлектрического преобразования согласно варианту осуществления 6. Шестой вариант осуществления отличается от вариантов осуществления с первого по пятый тем, что выходная схема 105 включает в себя схему токового зеркала и схему с общим затвором. Отличия от вариантов осуществления с первого по пятый описаны ниже, но описание частей, аналогичных соответствующим частям любого из вариантов осуществления с первого по пятый, опущено.

[00108] Фиг. 10 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 10 показан только один пиксель 100. Части, аналогичные по функции показанным на одной из фиг. 3 и фиг. 5-9, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[00109] Блок управления выходной схемы 105 включает в себя схему токового зеркала, включающую в себя МОП-транзистор M6 с каналом P-типа и МОП-транзистор M7 с каналом P-типа. Сток транзистора M6 электрически соединен со стоком дифференциального транзистора M5. Затвор транзистора M6 и затвор транзистора M7 соединены друг с другом.

[00110] Схема токового зеркала дополнительно включает в себя МОП-транзистор с каналом P-типа MG1 и МОП-транзистор с каналом P-типа MG2. Транзистор MG1 и транзистор MG2 соответственно каскодно соединены с транзистором M6 и транзистором M7. Напряжение Vbs смещения поступает на затвор транзистора MG1 и затвор транзистора MG2. В результате, транзистор MG1 и транзистор MG2 образуют схему с общим затвором.

[00111] Когда выходная схема 105 осуществляет первую операцию, схема токового зеркала, образованная транзисторами M6 и M7, отражает ток транзистора M7 на транзистор M6. Когда выходная схема 105 осуществляет вторую операцию, схема токового зеркала отражает ток транзистора M6 на транзистор M7.

[00112] В настоящем варианте осуществления, в первой операции схема токового зеркала действует как источник тока, который подает ток из транзистора M6 на дифференциальный транзистор M5. Во второй операции схема токового зеркала действует как схема обнаружения тока, которая отражает ток, поступающий на транзистор M6, от дифференциального транзистора M5 на транзистор M7.

[00113] Блок управления выходной схемы 105 включает в себя конденсаторный элемент C2. Конденсаторный элемент C2 имеет первый вывод и второй вывод. Первый вывод конденсаторного элемента C2 электрически соединен со стоком транзистора M6 посредством схемы с общим затвором (транзистора MG1). Второй вывод конденсаторного элемента C2 электрически соединен с затвором транзистора M6. Посредством конденсаторного элемента C2, сток и затвор транзистора M6 связаны друг с другом по переменному току, что позволяет отражать ток транзистора M6 на транзистор M7.

[00114] Блок управления выходной схемы 105 включает в себя первый переключающий элемент SW2. Первый переключающий элемент SW2 электрически соединяет затвор и сток транзистора M7 посредством схемы с общим затвором (транзистора MG2). При открытии первого переключающего элемента SW2, схема токового зеркала способна отражать ток транзистора M7 на транзистор M6. При закрытии первого переключающего элемента SW2, схема токового зеркала способна отражать ток транзистора M6 на транзистор M7. Таким образом, первый переключающий элемент SW2 переключается между первой операцией и второй операцией, осуществляемыми выходной схемой 105.

[00115] Заметим, что емкость конденсаторного элемента C2 больше емкости связи между двумя концами первого переключающего элемента SW2 в состоянии, в котором первый переключающий элемент SW2 находится в закрытом состоянии. В случае, когда МОП-транзистор используется в качестве первого переключающего элемента SW2, два конца первого переключающего элемента SW2 являются истоком и стоком этого МОП-транзистора. Вышеописанная конфигурация позволяет повысить устойчивость работы схемы токового зеркала.

[00116] Фиксирующая схема 300 включает в себя фиксирующий переключающий элемент SW1 и фиксирующий конденсаторный элемент C1. В настоящем варианте осуществления, фиксирующий переключающий элемент SW1 электрически соединяет затвор и сток дифференциального транзистора M5 посредством схемы с общим затвором (транзистора MG1).

[00117] Может быть желательно, чтобы фиксирующий переключающий элемент SW1 и первый переключающий элемент SW2 действовали синфазно. В настоящем варианте осуществления, фиксирующий переключающий элемент SW1 и первый переключающий элемент SW2 управляются общим возбуждающим сигналом ϕCLMP.

[00118] В настоящем варианте осуществления, выходная схема 105 включает в себя источник IS2 опорного тока, соединенный с выходным узлом 310. Источник IS2 опорного тока выводит опорный ток на транзистор M7. Выходной узел 310 соединен со схемой инвертора.

[00119] В настоящем варианте осуществления, устройство фотоэлектрического преобразования возбуждается сигналами возбуждения, показанными на фиг. 4. Таким образом, в настоящем варианте осуществления, возбуждение осуществляется аналогично первому варианту осуществления.

[00120] Описаны примеры значений различных элементов. Например, транзисторы M6 и M7, образующие схему токового зеркала, имеют, по существу, одинаковый размер. Величина тока I_IS1 источника IS1 следового тока, величина тока I_IS2 источника IS2 опорного тока, и величина тока I_IS3 источника IS3 тока по существу, удовлетворяют соотношению I_IS1=2×(I_IS2-I_IS3).

[00121] В вышеописанных условиях, в первой операции ток с величиной, примерно равной одной второй величины тока I_IS1 источника IS1 следового тока пропускается через каждый из пиксельного транзистора M3 и дифференциального транзистора M5, то есть, ток, текущий через каждый из этих двух транзисторов, примерно равен величине тока (I_IS2-I_IS3). Во второй операции, когда напряжение на затворе дифференциального транзистора M5 выше напряжения на затворе пиксельного транзистора M3, большая часть тока источника IS1 следового тока течет через дифференциальный транзистор M5, и ток, по существу, не течет через пиксельный транзистор M3. Поэтому ток, по существу, той же величины, что и источника IS1 следового тока, течет через транзистор M7. Поскольку IS1=2×IS2, напряжение на стоке транзистора M7, то есть, напряжение на выходном узле 310, становится примерно равным напряжению питания VDD.

[00122] Когда опорный сигнал линейно уменьшается, напряжение на затворе дифференциального транзистора M5 становится ниже напряжения на затворе пиксельного транзистора M3. В этом состоянии, большая часть тока источника IS1 следового тока течет через пиксельный транзистор M3, и ток дифференциального транзистора M5 становится, по существу, равным нулю. Поэтому ток транзистора M7 также становится, по существу, равным нулю. В результате, напряжение на стоке транзистора M7, то есть, напряжение на выходном узле 310, становится примерно равным напряжению земли.

[00123] Как описано выше, выходная схема 105 обнаруживает изменение тока дифференциального транзистора M5. В этой операции, транзистор M6 функционирует как вход схемы токового зеркала. Даже в случае изменения тока стока дифференциального транзистора M5, не происходит значительного изменения напряжения на стоке транзистора M6. Другими словами, схема токового зеркала управляет изменением напряжения на стоке дифференциального транзистора M5, чтобы оно было меньше изменения напряжения на выходном узле. Таким образом, можно уменьшить изменение напряжения опорного сигнала VRMP. В результате, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

[00124] В настоящем варианте осуществления, транзистор M6 и транзистор M7, образующие схему токового зеркала, каскодно соединены со схемой с общим затвором. Это позволяет уменьшить изменение напряжения на стоке дифференциального транзистора M5 более эффективно, чем в первом варианте осуществления.

СЕДЬМОЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[00125] Ниже описано устройство фотоэлектрического преобразования согласно варианту осуществления 7. Седьмой вариант осуществления отличается от шестого варианта осуществления тем, что конденсаторный элемент C2 блока управления выходной схемы 105 заменен вторым переключающим элементом SW3. Отличия от шестого варианта осуществления описаны ниже, но описание частей, аналогичных соответствующим частям в шестом варианте осуществления, опущено. Заметим, что в настоящем варианте осуществления, второй переключающий элемент SW3 функционирует аналогично второму переключающему элементу SW3 согласно третьему варианту осуществления.

[00126] Фиг. 11 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 11 показан только один пиксель 100. Части, аналогичные по функции показанным на фиг. 7 или фиг. 10, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[00127] Блок управления выходной схемы 105 включает в себя схему токового зеркала, включающую в себя МОП-транзистор M6 с каналом P-типа и МОП-транзистор M7 с каналом P-типа. Сток транзистора M6 электрически соединен со стоком дифференциального транзистора M5. Затвор транзистора M6 и затвор транзистора M7 соединены друг с другом.

[00128] Схема токового зеркала дополнительно включает в себя МОП-транзистор с каналом P-типа MG1 и МОП-транзистор с каналом P-типа MG2. Транзистор MG1 и транзистор MG2 соответственно каскодно соединены с транзистором M6 и транзистором M7. Напряжение Vbs смещения поступает на затвор транзистора MG1 и затвор транзистора MG2. В результате, транзистор MG1 и транзистор MG2 образуют схему с общим затвором.

[00129] Блок управления выходной схемы 105 включает в себя первый переключающий элемент SW2 и второй переключающий элемент SW3. Первый переключающий элемент SW2 электрически соединяет затвор и сток транзистора M7 посредством схемы с общим затвором (транзистора MG2). Второй переключающий элемент SW3 электрически соединяет затвор и сток транзистора M6 посредством схемы с общим затвором (транзистора MG1).

[00130] в настоящем варианте осуществления, первый переключающий элемент SW2 и второй переключающий элемент SW3 действуют попеременно. Другими словами, когда первый переключающий элемент SW2 находится в открытом состоянии, второй переключающий элемент SW3 закрывается. С другой стороны, когда первый переключающий элемент SW2 находится в закрытом состоянии, второй переключающий элемент SW3 открывается. В частности, первый переключающий элемент SW2 управляется возбуждающим сигналом ϕCLMP. Второй переключающий элемент SW3 управляется возбуждающим сигналом ϕCLMPB, который противоположен по фазе возбуждающему сигналу ϕCLMP.

[00131] При открытии первого переключающего элемента SW2 и закрытии второго переключающего элемента SW3, схема токового зеркала способна отражать ток транзистора M7 на транзистор M6. При закрытии первого переключающего элемента SW2 и открытии второго переключающего элемента SW3, схема токового зеркала способна отражать ток транзистора M6 на транзистор M7. Таким образом, первый переключающий элемент SW2 и второй переключающий элемент SW3 переключаются между первой операцией и второй операцией, осуществляемых выходной схемой 105.

[00132] Таким образом, как и в шестом варианте осуществления, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

ВОСЬМОЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[00133] Ниже описано устройство фотоэлектрического преобразования согласно варианту осуществления 8. Восьмой вариант осуществления отличается от вариантов осуществления с первого по седьмой тем, что выходная схема 105 включает в себя схему токового зеркала и нагрузочный транзистор. Отличия от вариантов осуществления с первого по седьмой описаны ниже, но описание частей, аналогичных соответствующим частям любого из вариантов осуществления с первого по седьмой, опущено.

[00134] Фиг. 12 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 12 показан только один пиксель 100. Части, аналогичные по функции показанным на одной из фиг. 3 и фиг. 5-11, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[00135] Блок управления выходной схемы 105 включает в себя схему токового зеркала, включающую в себя МОП-транзистор M6 с каналом N-типа и МОП-транзистор M7 с каналом N-типа. Сток транзистора M6 электрически соединен со стоком дифференциального транзистора M5 посредством схемы с общим затвором (транзистора MG1). Затвор транзистора M6 и затвор транзистора M7 соединены друг с другом.

[00136] Когда выходная схема 105 осуществляет первую операцию, схема токового зеркала, образованная транзисторами M6 и M7, отражает ток транзистора M7 на транзистор M6. Когда выходная схема 105 осуществляет вторую операцию, схема токового зеркала отражает ток транзистора M6 на транзистор M7.

[00137] Блок управления выходной схемы 105 включает в себя нагрузочные транзисторы ML1 и ML2 с каналом P-типа. Сток нагрузочного транзистора ML1 электрически соединен со стоком дифференциального транзистора M5. Затвор нагрузочного транзистора ML1 и затвор нагрузочного транзистора ML2 соединены друг с другом, и напряжение смещения Vbs1 поступает на соединенные между собой затворы. Каждый из нагрузочных транзисторов ML1 и ML2 действует как источник тока.

[00138] В настоящем варианте осуществления, соединения дифференциального транзистора M5 и транзистора M6 выполнены с возможностью комплементарно принимать ток от нагрузочного транзистора ML1. Другими словами, дифференциальный транзистор M5 и транзистор M6 располагаются параллельно на электрическом пути между стоком нагрузочного транзистора и узлом земли. В этой конфигурации, сумма тока дифференциального транзистора M5 и тока транзистора M6 примерно равна току нагрузочного транзистора ML1.

[00139] В настоящем варианте осуществления, в первой операции нагрузочный транзистор ML1 действует как источник тока, который подает ток на дифференциальный транзистор M5. Во второй операции схема токового зеркала действует как схема обнаружения тока, которая отражает ток, поступающий на транзистор M6 от нагрузочного транзистора ML1 на транзистор M7.

[00140] Блок управления выходной схемы 105 включает в себя конденсаторный элемент C2. Конденсаторный элемент C2 имеет первый вывод и второй вывод. Первый вывод конденсаторного элемента C2 электрически соединен со стоком транзистора M6. Второй вывод конденсаторного элемента C2 электрически соединен с затвором транзистора M6. Посредством конденсаторного элемента C2, сток и затвор транзистора M6 связаны друг с другом по переменному току, что позволяет отражать ток транзистора M6 на транзистор M7.

[00141] Блок управления выходной схемы 105 включает в себя первый переключающий элемент SW2. Первый переключающий элемент SW2 электрически соединяет затвор и сток транзистора M7. При открытии первого переключающего элемента SW2, схема токового зеркала способна отражать ток транзистора M7 на транзистор M6. При закрытии первого переключающего элемента SW2, схема токового зеркала способна отражать ток транзистора M6 на транзистор M7. Таким образом, первый переключающий элемент SW2 переключается между первой операцией и второй операцией, осуществляемыми выходной схемой 105.

[00142] Фиксирующая схема 300 включает в себя фиксирующий переключающий элемент SW1 и фиксирующий конденсаторный элемент C1. В настоящем варианте осуществления, фиксирующий переключающий элемент SW1 электрически соединяет затвор и сток дифференциального транзистора M5 посредством схемы с общим затвором (транзистора MG1).

[00143] В настоящем варианте осуществления, устройство фотоэлектрического преобразования возбуждается сигналами возбуждения, показанными на фиг. 4. Таким образом, в настоящем варианте осуществления, возбуждение осуществляется аналогично первому варианту осуществления.

[00144] Описаны примеры значений различных элементов. Например, транзисторы M6 и M7, образующие схему токового зеркала, имеют, по существу, одинаковый размер. Величина тока I_IS1 источника IS1 следового тока, величина тока I_ML1 нагрузочного транзистора ML1, и величина тока I_ML2 нагрузочного транзистора ML2 по существу, удовлетворяют соотношению I_IS1=I_ML1=2×I_ML2.

[00145] В вышеописанных условиях, в первой операции ток с величиной, примерно равной одной второй величины тока I_IS1 источника IS1 следового тока течет через каждый из пиксельного транзистора M3 и дифференциального транзистора M5, то есть, ток, по существу, равный величине тока I_ML2 течет через каждый из них. Во второй операции, когда напряжение на затворе дифференциального транзистора M5 выше напряжения на затворе пиксельного транзистора M3, большая часть тока источника IS1 следового тока течет через дифференциальный транзистор M5, и ток, по существу, не течет через пиксельный транзистор M3. Ток равный разности между током нагрузочного транзистора ML1 и током источника IS1 следового тока течет через транзистор M6. Однако, поскольку I_IS1=I_ ML1, ток транзистора M6 примерно равен 0.

[00146] Таким образом ток, по существу, не течет через транзистор M7. В результате, напряжение на стоке транзистора M7, то есть напряжение на выходном узле 310, становится примерно равным напряжению питания VDD.

[00147] Когда опорный сигнал линейно уменьшается, напряжение на затворе дифференциального транзистора M5 становится ниже напряжения на затворе пиксельного транзистора M3. В этом состоянии, большая часть тока источника IS1 следового тока течет через пиксельный транзистор M3, и ток дифференциального транзистора M5 становится, по существу, равным нулю. Что касается транзистора M7, через него течет ток, примерно равный току нагрузочного транзистора ML1. Поскольку I_ML1=2×I_ML2, напряжение на выходном узле 310 становится примерно равным напряжению земли.

[00148] Как описано выше, выходная схема 105 обнаруживает изменение тока дифференциального транзистора M5. Даже в случае изменения тока стока дифференциального транзистора M5, не происходит значительного изменения напряжения на стоке транзистора M6. Другими словами, блок управления выходной схемы 105 управляет изменением напряжения на стоке дифференциального транзистора M5, чтобы оно было меньше изменения напряжения на выходном узле. Таким образом, можно уменьшить изменение напряжения опорного сигнала VRMP. В результате, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

ДЕВЯТЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[00149] Ниже описано устройство фотоэлектрического преобразования согласно варианту осуществления 9. Девятый вариант осуществления отличается от восьмого варианта осуществления тем, что конденсаторный элемент C2 блока управления выходной схемы 105 заменен вторым переключающим элементом SW3. Отличия от шестого варианта осуществления описаны ниже, но описание частей, аналогичных соответствующим частям в восьмом варианте осуществления, опущено. Заметим, что в настоящем варианте осуществления, второй переключающий элемент SW3 функционирует аналогично второму переключающему элементу SW3 согласно третьему варианту осуществления, и второму переключающему элементу SW3 согласно седьмому варианту осуществления.

[00150] Фиг. 13 демонстрирует конфигурации пикселя 100, схемы 104 компаратора и выходной схемы 105 устройства фотоэлектрического преобразования. Для простоты иллюстрации, на фиг. 13 показан только один пиксель 100. Части, аналогичные по функции показанным на фиг. 3 или фиг. 5-12, обозначены аналогичными ссылочными позициями, и более подробное их описание опущено.

[00151] Согласно фиг. 13, блок управления выходной схемы 105 включает в себя первый переключающий элемент SW2 и второй переключающий элемент SW3. Первый переключающий элемент SW2 соединяет затвор и сток транзистора M7. Второй переключающий элемент SW3 электрически соединяет сток и затвор транзистора M6.

[00152] Таким образом, как и в восьмом варианте осуществления, настоящий вариант осуществления позволяет повысить точность сигнала, выводимого из устройства фотоэлектрического преобразования.

ДЕСЯТЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[00153] На фиг. 14 показана схема, демонстрирующая конфигурацию системы фотоэлектрического преобразования. Система фотоэлектрического преобразования 800 включает в себя, например, оптический блок 810, датчик 1 изображения, блок 830 обработки сигнала изображения, блок 840 хранения/передачи, блок 850 управления хронированием, блок 860 управления системой и блок 870 воспроизведения/отображения. Устройство получения изображения 820 включает в себя датчик 1 изображения и блок 830 обработки сигнала изображения. Что касается датчика 1 изображения, используется устройство фотоэлектрического преобразования согласно вышеописанным вариантам осуществления.

[00154] Оптический блок 810, который является оптической системой, например, линзой и т.п., фокусирует свет от объекта на пиксельную матрицу 102, включающую в себя двухмерную матрицу множества пикселей в датчике 1 изображения для формирования изображения объекта. Датчик 1 изображения выводит сигнал, соответствующий свету, сфокусированному на пиксельную матрицу 102, в ответ на сигнал от блока 850 управления хронированием. Сигнал, выводимый из датчика 1 изображения, поступает на блок 830 обработки сигнала изображения, выступающий в роли блока обработки сигнала изображения, который осуществляет обработку сигнала согласно заранее определенному способу с использованием программы и т.п. Сигнал, полученный в процессе, осуществляемом блоком 830 обработки сигнала изображения, передается в виде данных изображения на блок 840 хранения/передачи. Блок 840 хранения/передачи передает сигнал для формирования изображения на блок 870 воспроизведения/отображения, тем самым вынуждая блок 870 воспроизведения/отображения воспроизводить и отображать движущееся изображение или неподвижное изображение. Блок 840 хранения/передачи также принимает сигнал от блока 830 обработки сигнала изображения и осуществляет связь с блоком 860 управления системой. Кроме того, блок 840 хранения/передачи также осуществляет операцию сохранения сигнала для формирования изображения на не показанном носителе данных.

[00155] Блок 860 управления системой, в общем случае, управляет работой системы получения изображения и управляет возбуждением оптического блока 810, блока 850 управления хронированием, блока 840 хранения/передачи и блока 870 воспроизведения/отображения. Блок 860 управления системой включает в себя, например, не показанное устройство хранения, выступающее в роли носителя данных, на котором хранится программа и т.п., необходимая при управлении работой системы получения изображения. Блок 860 управления системой также подает, внутрь системы получения изображения, сигнал для переключения режима возбуждения, например, в ответ на операцию, осуществляемую пользователем. Конкретные примеры включают в себя изменение считываемой строки или сбрасываемой строки, изменение полевого угла в электронной трансфокации, сдвиг полевого угла в электронной стабилизации изображения и пр. Блок 850 управления хронированием управляет хронированием возбуждения датчика 1 изображения и блока 830 обработки сигнала изображения под управлением блока 860 управления системой.

[00156] Хотя настоящее изобретение описано со ссылкой на иллюстративные варианты осуществления, следует понимать, что изобретение не ограничивается раскрытыми иллюстративными вариантами осуществления. Объем нижеследующей формулы изобретения следует рассматривать в самой широкой интерпретации для охвата всех подобных модификаций и эквивалентных структур и функций.

Настоящее изобретение относится к устройству фотоэлектрического преобразования и к системе фотоэлектрического преобразования. Устройство фотоэлектрического преобразования, содержащее: элемент фотоэлектрического преобразования; дифференциальную пару, включающую в себя первый транзистор, выполненный с возможностью приема сигнала на основании электрического заряда, генерируемого в элементе фотоэлектрического преобразования, и второй транзистор, выполненный с возможностью приема опорного сигнала; фиксирующую схему, выполненную с возможностью фиксации напряжения на затворе второго транзистора, и выходную схему. Причем выходная схема выполнена с возможностью осуществления первой операции для вывода напряжения на основании напряжения на затворе первого транзистора на затвор второго транзистора, и второй операции для приема тока от второго транзистора, и для вывода сигнала на основании результата сравнения между напряжением на затворе первого транзистора и напряжением на затворе второго транзистора на выходной узел. При этом выходная схема включает в себя блок управления, выполненный с возможностью управления, во второй операции, величиной изменения напряжения на стоке второго транзистора, чтобы она была меньше величины изменения напряжения на выходном узле. 4 н. и 30 з.п. ф-лы, 14 ил.

1. Устройство фотоэлектрического преобразования, содержащее:

элемент фотоэлектрического преобразования;

дифференциальную пару, включающую в себя первый транзистор, выполненный с возможностью приема сигнала на основании электрического заряда, генерируемого в элементе фотоэлектрического преобразования, и второй транзистор, выполненный с возможностью приема опорного сигнала;

фиксирующую схему, выполненную с возможностью фиксации напряжения на затворе второго транзистора; и

выходную схему, выполненную с возможностью осуществления

первой операции для вывода напряжения на основании напряжения на затворе первого транзистора на затвор второго транзистора, и

второй операции для приема тока от второго транзистора, и для вывода сигнала на основании результата сравнения между напряжением на затворе первого транзистора и напряжением на затворе второго транзистора на выходной узел,

причем выходная схема включает в себя блок управления, выполненный с возможностью управления, во второй операции, величиной изменения напряжения на стоке второго транзистора, чтобы она была меньше величины изменения напряжения на выходном узле.

2. Устройство фотоэлектрического преобразования по п. 1, в котором

блок управления включает в себя схему токового зеркала, включающую в себя третий транзистор, электрически соединенный со стоком второго транзистора, и четвертый транзистор, затвор которого соединен с затвором третьего транзистора,

в первой операции схема токового зеркала отражает ток четвертого транзистора на третий транзистор, и

во второй операции схема токового зеркала отражает ток третьего транзистора на четвертый транзистор.

3. Устройство фотоэлектрического преобразования по п. 2, в котором

блок управления включает в себя первый переключающий элемент, который соединяет затвор и сток четвертого транзистора,

в ответ на открытие первого переключающего элемента, схема токового зеркала отражает ток четвертого транзистора на третий транзистор, и

в ответ на закрытие первого переключающего элемента, схема токового зеркала отражает ток третьего транзистора на четвертый транзистор.

4. Устройство фотоэлектрического преобразования по п. 3, в котором блок управления включает в себя конденсаторный элемент, первый вывод которого электрически соединен со стоком третьего транзистора, и второй вывод электрически соединен с затвором третьего транзистора.

5. Устройство фотоэлектрического преобразования по п. 4, в котором первый вывод конденсаторного элемента электрически соединен со стоком третьего транзистора посредством схемы с общим затвором.

6. Устройство фотоэлектрического преобразования по п. 4, в котором емкость конденсаторного элемента больше емкости конденсатора связи между двумя выводами первого переключающего элемента в закрытом состоянии.

7. Устройство фотоэлектрического преобразования по п. 3, в котором блок управления включает в себя второй переключающий элемент, который электрически соединяет сток и затвор третьего транзистора.

8. Устройство фотоэлектрического преобразования по п. 7, в котором второй переключающий элемент электрически соединен со стоком третьего транзистора посредством схемы с общим затвором.

9. Устройство фотоэлектрического преобразования по п. 7, в котором первый переключающий элемент и второй переключающий элемент действуют комплементарным образом.

10. Устройство фотоэлектрического преобразования по п. 3, в котором

фиксирующая схема включает в себя фиксирующий переключающий элемент, соединенный с затвором второго транзистора, и

фиксирующий переключающий элемент и первый переключающий элемент действуют синфазно.

11. Устройство фотоэлектрического преобразования по п. 2, в котором

в первой операции схема токового зеркала действует как источник тока, который подает ток, обеспечиваемый третьим транзистором, на второй транзистор, и

во второй операции схема токового зеркала действует как схема обнаружения тока, которая отражает, в четвертый транзистор, ток, поступающий на третий транзистор от второго транзистора.

12. Устройство фотоэлектрического преобразования по п. 2, в котором

блок управления включает в себя нагрузочный транзистор, электрически соединенный со стоком второго транзистора,

второй транзистор и третий транзистор соединены так, чтобы комплементарно принимать ток от нагрузочного транзистора,

в первой операции нагрузочный транзистор действует как источник тока, который подает ток на второй транзистор, и

во второй операции схема токового зеркала действует как схема обнаружения тока, которая отражает, в четвертый транзистор, ток, поступающий на третий транзистор от нагрузочного транзистора.

13. Устройство фотоэлектрического преобразования по п. 12, в котором блок управления включает в себя схему с общим затвором, расположенную на электрическом пути между нагрузочным транзистором и третьим транзистором.

14. Устройство фотоэлектрического преобразования по п. 1, в котором

блок управления включает в себя