Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычис- лительной техники при разработке счетчиков, регистров, делителей частоты, распределителей импульсов с повышенной достоверностью функционирования и эксплуатационной отказе- устойчивостью.

Целью изобретения является повышение достоверности функционирования устройства и ремонтопригодности..

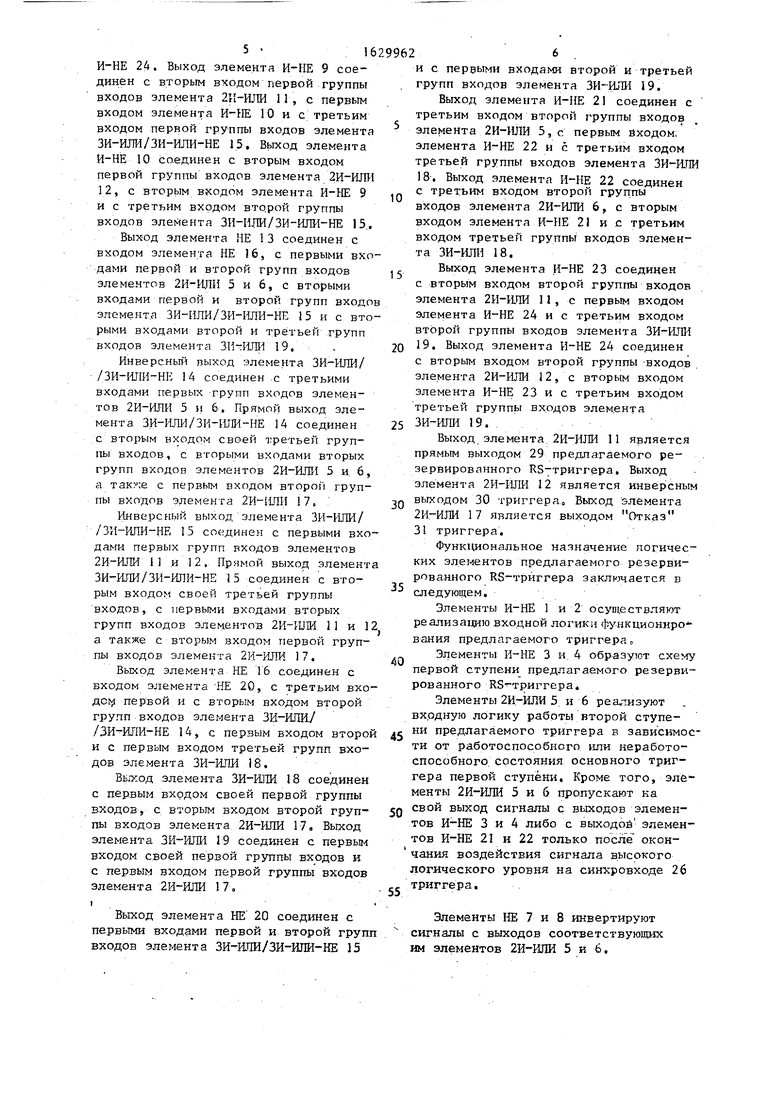

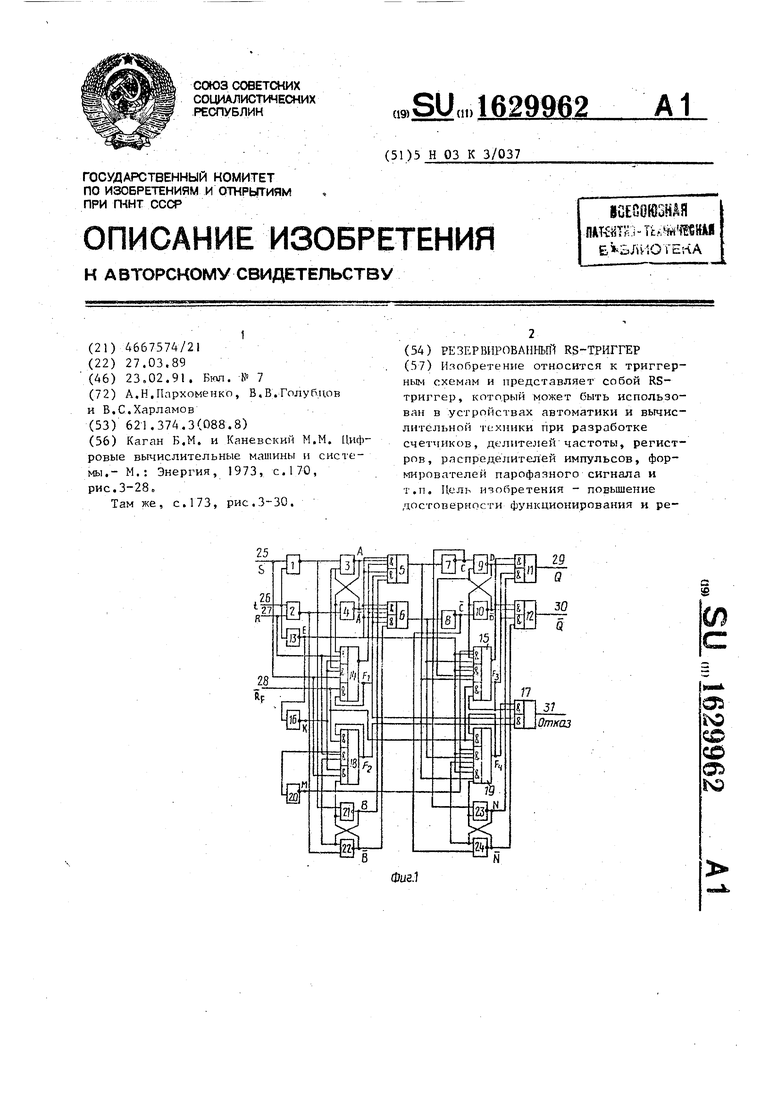

На фиг,1 представлена функциональ ная схема резервированного RS-тригге ра; на фиг.2 - временные диаграммы его работы.

Триггер содержит первый 1, второй 2, третий 3 и четвертый 4 элементы И-НЕ, первый 5 и второй 6 элементы 2И-ИЛИ, элементы НЕ 7 и.8, пятый 9 и шестой 10 элементы И-НЕ, третий 11 и четвертый 12 элементы 2И-ИЛИ, элемент НЕ 13, первый 14 и второй 15 элементы ЗИ-ИЛИУЗИ-ИЛИ-НЕ, четвертый элемент НЕ 16, пятый элемент 2И-ИЛИ 17, первый 18 и второй 19 элементы ЗИ-ИЛИ, пятый элемент НЕ 20, седьмой - десятый элементы И-НЕ 21-24.

S-вход 25 триггера соединен с первым входом элемента И-НЕ 1, с третьим входом второй группы входо элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14 и с вторым входом третьей группы входов элемента ЗИ-ИЛИ 18.

Синхровход 26 триггера соединен с вторым входом .элемента И-НЕ 1, с первым входом элемента И-НЕ 2 и с входом элемента НЕ 13.

R-вход 27 триггера соединен с вторым входом элемента И-НЕ 2, с вторым входом первой группы вхо

5

0 5

д

0 $

0

5

дов элемента ЗИ-ИЛИ/ЗИ-ЩТИ-НЕ 14 и с вторым входом второй группы входов элемента ЗИ-ИЛИ 18.

Вход 28 установки в исходное состояние средств функционального контроля соединен с первыми входами третьих групп входов элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14 и 15, а также с вторыми входами первых групп входов элементов ЗИ-ИЛИ 18 и 19.

Выход элемента И-НЕ 1 соединен с первыми входами элементов И-НЕ 3 и 21. Выход элемента И-НЕ 2 соединен с вторыми входами элементов И-НЕ 4 и 22. Выход элемента И-НЕ 3 соединен с первым входом элемента И-НЕ 4, с вторым входом первой группы входов элементов 2И-ИЛИ 5 и с первым входом первой группы входов элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14. Выход элемента И-НЕ 5 соединен с вторым входом элемента И-НЕ 3, с вторым входом первой группы входов элемента 2И-ИЛИ бис первым входом второй группы входов элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14. Выход элемента 2И-Ш1И 5 соединен с входом элемента НЕ 7, с четвертым входом второй группы входов элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15 и с. третьим входом третьей группы входов элемента ЗИ-ИЛИ 19. Выход элемента 2И-ИЛИ 6 соединен с входом элемента НЕ 8, с четвертым входом первой группы входов элемента ЗИ-ИЛИ/ЗИ-ИЯИ-НЕ 15 и с третьим входом второй группы входов элемента ЗИ-ИЛИ 19. Выход элемента НЕ 7 соединен с первым входом элемента И-НЕ 9 и с первым входом элемента И-НЕ 23. Выход элемента НЕ 8 соединен с вторым-входом элемента И-НЕ 10 и с вторым .входом элемента

И-НЕ 24. Выход элемента И-НЕ 9 соединен с вторым входом первой группы входов элемента 2Н-ИЛИ 11, с первым входом элемента И-НЕ 10 и с третьим входом первой группы входов элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15. Выход элемента И-НЕ 10 соединен с вторым входом первой группы входов элемента 2И-ИЛИ 12, с вторым входом элемента И-НЕ 9 и с третьим входом второй группы входов элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15.

Выход элемента НЕ 13 соединен с входом элемента НЕ 16, с первыми входами первой и второй групп входов элементов 2И-ИДИ 5 и 6, с вторыми входами первой и второй групп входо элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15 и с вторыми входами второй и третьей групп входов элемента ЗИ-ИЛИ 19.

Инверсный выход элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 14 соединен с третьими входами первых групп входов элементов 2И-ИЛИ 5 и 6. Прямой выход элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14 соединен с вторым входом своей третьей группы входов, с вторыми входами вторых групп входов элементов 2И-ИЛИ 5 и 6, a T3Kv;e с первым входом второй группы входов элемента 2И-ШШ 17.

Инверсный выход элемента ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ 15 соединен с первыми входами первых групп входов элементов 2И-ИЛИ 11 и 12, Прямой выход элемент ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15 соединен с вторым входом своей третьей группы входов, с первыми входами вторых групп входов элементов 2И-Ш1И 11 и 1 а также с вторым входом первой группы входов элеменга 2И-ИЛИ 17.

Выход элемента НЕ 16 соединен с входом элемента НЕ 20, с третьим вхо дсу первой и с вторым входом второй групп входов элемента ЗИ-ШЖ/ /ЗИ-ИЛИ-НЕ 14, с первым входом второ и с первым входом третьей групп входов элемента ЗИ-ИЛИ 18.

Выход элемента ЗИ-ИЛИ 18 соединен с первым входом своей первой группы входов, с вторым входом второй группы входов элемента 2И-ИЛИ 17, Выход элемента ЗИ-ИЛИ 19 соединен с первым входом своей первой группы входов и с первым входом первой группы входов элемента 2И-ИЛИ 17,

i

Выход элемента НЕ 20 соединен с первыми входами первой и второй груп входов элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15

5

0

5

0

5

0

S

0

5

и с первыми входами второй и третьей групп входов элемента ЗИ-ИЛИ 19.

Выход элемента И-НЕ 21 соединен с третьим входом второй группы входов элемента 2И-ИЛИ 5, с первым входом, элемента И-НЕ 22 и с третьим входом третьей группы входов элемента ЗИ-ИЛИ

18.Выход элемента И-НЕ 22 соединен с третьим входом второй группы

входов элемента 2И-ИЛИ 6, с вторым входом элемента И-НЕ 21 и с третьим входом третьей группы входов элемента ЗИ-ИЛИ 18.

Выход элемента И-НЕ 23 соединен с вторым входом второй группы входов элемента 2И-ИЛИ 11, с первым входом элемента И-НЕ 24 и с третьим входом второй группы входов элемента ЗИ-ИЛИ

19.Выход элемента И-НЕ 24 соединен с вторым входом второй группы входов элемента 2И-ИЛИ 12, с вторым входом элемента 23 и с третьим входом третьей группы входов элемента ЗИ-ИЛИ 19.

Выход элемента 2И-ИЛИ 11 является прямым выходом 29 предлагаемого резервированного RS-триггера. Выход элемента 2И-ИЛИ 12 является инверсным выходом 30 триггера. Выход элемента 2И-ИЛИ 17 является выходом Отказ 31 триггера.

Функциональное назначение логических элементов предлагаемого резервированного RS-триггера заключается в следующем.

Элементы И-НЕ 1 и 2 осуществляют реализацию входной логики функциониро вания предлагаемого триггера

Элементы И-НЕ 3 и 4 образуют схему первой ступени предлагаемого резервированного RS-триггера.

Элементы 2И-ИЛИ 5 и 6 реализуют входную логику работы второй ступени предлагаемого триггера в зависимое ти от работоспособного или неработоспособного состояния основного триггера первой ступени. Кроме того, элементы 2И-ИЛИ 5 и б пропускают на свой выход сигналы с выходов элементов И-НЕ 3 и 4 либо с выходов1 элементов И-НЕ 21 и 22 только после окончания воздействия сигнала высокого логического уровня на синхровходе 26 триггера.

Элементы НЕ 7 и 8 инвертируют сигналы с выходов соответствующих им элементов 2И-ИЛИ 5 и 6.

Элементы И-НЕ 9 и 10 образуют схему триггера второй ступени.

Элементы 2И-ИЛИ 11 и 12 пропускаю на свои выходы (на прямой 29 и инверсный 30 выходы триггера) сигналы с выходов основной второй .ступени либо с выходов резервной второй ступени, в зависимости от кх работоспособного состояния.

Элемент НЕ 13 предназначен для организации двухтактного режима работы триггера при наличии всего одного синхровхода 26, Кроме того, на выходе элемента НЕ 13 формируется сигнал строба сравнения в режиме хранения информации.

Элемент ЗИ-ИЛИ/ЗИ-ИПИ-НЕ 14 на своих первой и второй группах входов обеспечивает контроль правильности срабатывания логических элементов основной первой ступени. Функционал отказа основной первой ступени, реализованный на входах элемента ЗИ-ИЛИ /ЗИ-ИЛИ-11Е 14, можно представить еле дующим выражением:

R-A-T V S-A-T 1. (1)

Элемент ЗИ-ИЛИ/ЗИ-ИПИ-НЕ 15 на своих первой и второй группах входов осуществляет контроль правильности срабатывания логических элементов триггера основной второй ступени, Функционал отказа основной второй ступени триггера, реализованный на входах элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15, можно представить следующим выражением :

О В . Т V В Т 1. (2)

Элемент НЕ 16 осуществляет инвертирование сигнала с выхода элемента НЕ 33 и, одновременно с этим, задерживает формирование сигнала на своем

выходе на время не менее Т

ср

(где

Т ср - среднее время срабатывания одного логического элемента структуры триггера).

Элемент 2И-ИЛИ 17 формирует на своем выходе (выходе 34 триггера) сигнал Отказ в случае одновремен ного отказа основной и резервной первой ступеней триггера (вторая группа входов по И) ив случае одновременного отказа основной и резервной вто рой ступеней триггера (первая группа входов по И).

Элемент ЗИ-ИЛИ 18 на своих второй и третьей группах входов осуществляет контроль правильности срабатывания логических элементов резервной

0

5

0

5

0

5

0

5

0

5

первой ступени триггера. Функционал отказа резервной первой ступени триггера, реализованный на входах элемента ЗИ-ИЛИ 18, можно представить следующим выражением:

R-B-T V 1, (3) где R - единичное значение сигнала

на входе 27 триггера; S - единичное значение сигнала на входе 25 триггера; В,В - значения сигналов в точках

В и If триггера;

Т - единичное значение сигнала на сихровходе 26 триггера. Элемент ЗИ-ИЛИ 19 на своих второй и третьей группах входов осуществляет контроль правильности срабатывания логических элементов резервной второй ступени триггера. Функционал отказа, реализованный на этих входах элемента ЗИ-ИЛИ 19, можно представить следующим выражением:

ONjr V C N f 1 , (4) где С,С - значения сигналов в точ- ках С и С схемы триггера; N,N - значения сигналов в точках N и N схемы триггера; Т - нулевое значение сигнала на синхровходе 26 триггера.

Элемент НЕ 20 осуществляет инвертирование сигнала с выхода элемента НЕ 16 и, одновременно с этим, производит задержку формирования сигнала на своем выходе на время не менее

ТСГ

Элементы И-НЕ 21 и 22 образуют

схему резервной первой ступени триггера.

Элементы И-НЕ 23 и 24 образуют схему резервной второй ступени триггера.

Триггер работает следующим образом,,

Исходное состояние триггера устанавливается подачей нулевого логического уровня сигнала ня вход 28 триггера, так как в момент включения питания из-за случайного характера переходных процессов элементы ЗИ-ИЛЙ/ /ЗИ-ИЛИ-НЕ 14 и 15 и элементы ЗИ-ИЛИ 18 и 19 могут сразу же установиться в состояние устойчивой логической единицы на своих выходах.

При исправном состоянии всех логических элементов структурно-логической организации резервированного RS-триггера его работа подчиняется

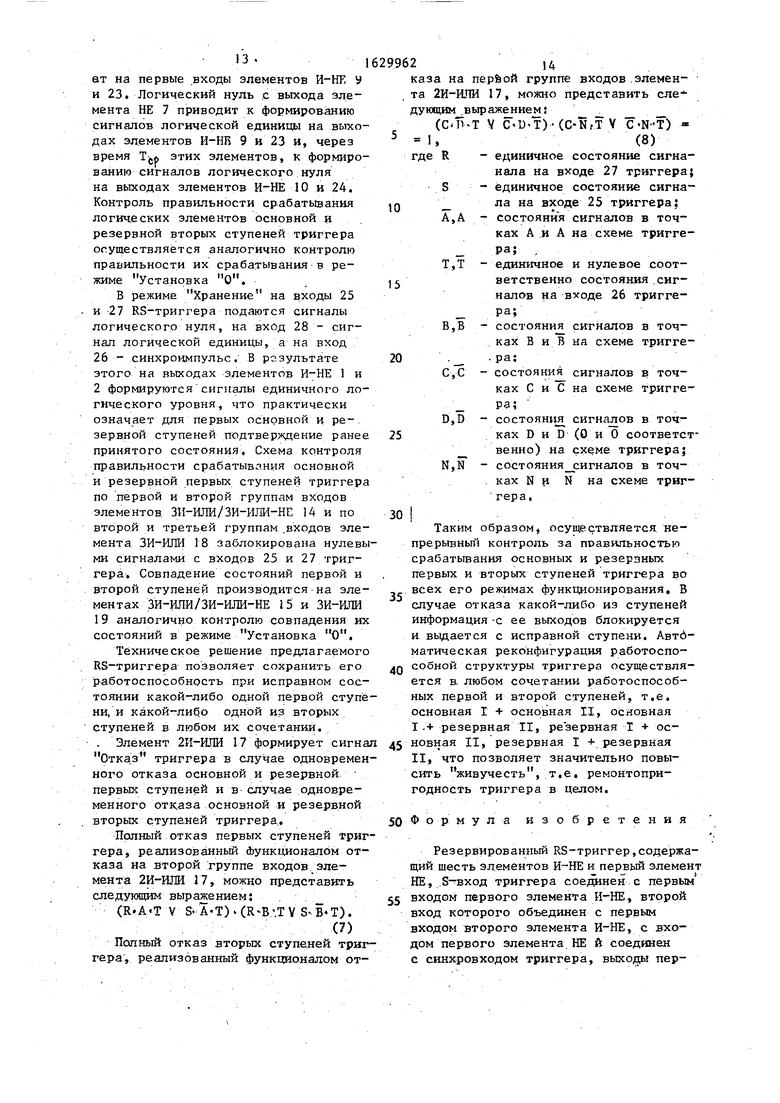

закону функционирования, приведенному в таблице переходов триггера.

Отличительной особенностью элемен ментов НЕ 16 и 20 в структуре триггера является то, что кроме функционально-логической нагрузки они выполняют и функцию времени срабатывания .

Время срабатывания элемента НК 16 должно соответствовать следующему неравенству:ТА(М6 р гпах(Т.п„ + Т,+

ср

ер.г

Т ) V (Т + cp.iy v u cp, i

ср. 4 ср.з

ТСР-3 + тср.4 тср.-1з) Г (5)

Время срабатывания элемента НЕ 20 должно соответствовать следующему неравенству: Тср.(Тср.6+ Tcp.g- Тср,№+ Тср.9 тср.1б ) Y (тСр.5 + ТСр7+ ТСр-д+ Тср,10ТСр.1б )(6)

Эти условия можно выполнить при разработке технологии микросхемы следующими путями: увеличением количества последовательно включенных транзисторов в элементах 16 и 20; технологией изготовления, т.е. увеличением геометрических размеров базы транзисторов этих логических элементов по сравнению с другими логическими элементами структуры RS-триггера; увеличением резнсторной и емкостной нагрузок этих логических элементов.

Рассматривают последовательность срабатывания всех логических элементов структуры предлагаемого резервированного RS-триггера в его трех основных режимах функционирования: Хранение, Установка О и Установка 1,

В режиме Установка О на вход

25подается сигнал логического нуля, а на входы - сигналы логической единицы. Причем на вход

26подается синхроимпульс. В результате этого на выходах элементов И-НЕ I и 2 через время ТСр (где

Тср - время срабатывания одного логического элемента структуры триггера) формируются соответственно сигналы логической единицы и логического нуля. Сигналы логического нуля, поступая с выхода элемента И-НЕ 2 на входы элементов И-НЕ 4 и 22, приводят к формированию на выходах этих элементов через время 2Тет с момента

J629962

to

0

5

появления положительного фронта сигнала на входе 26 сигналов логической единицы. Следовательно, через время ЗТС. на выходах элементов И-НЕ 3 и 21 сформированы сигналы логической единицы. Контроль правильности срабатывания элементов И-НЕ 3 и 4 осуществляется на первой и второй груп0 пах входов элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14 по стробу сравнения с выхода элемента НЕ 16. Контроль правильности срабатывания элементов И-НЕ 21 и 22 осуществляется на второй и третьей

5 группах входов элемента ЗИ-ИЛИ 18 также по стробу сравнения с выхода элемента НЕ 16, который появляется через время не менее ЗТСр.

В случае выполнения условий выражения (1) элемент ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14 пропускает по своей первой или второй группе входов сигнал логической единицы, который посредством своей обратной связи через третью группу входов устанавливает сигнал устойчивой логической единицы на прямом выходе элемента 14, означающий отказ одного или нескольких элементов основной первой ступени триггера.

В случае выполнения условий выражения (3) элемент ЗИ-ШШ 1 пропускает «срез свои вторую или третью группу входов сигнал высокого логического уровня, который посредством своей обратном сиязи через первую группу входоч усч гнпвливает сигнал стойчп- вой логической единитты :;а выходе- элемента 18, коч орый означает отказ одного пли нескольких логических элементов резервной первой ступени триггера.

При откте сповной первой сгугени триггера закрываются первые группы входов элементов 2И-11ЛН 5 и б, предотвращая тем самым Т50змо ное воздействие сигналов с выходов отказавшей основной первой ступени. При отказе резерзной первой ступени закрываются вторые группы входов элементов 2Ц-ШШ 5 и 6, предотвращая тем самым возможное во деьсгвнс сигналгч с выходов отказавшей резервной пергой ступени на элементы второй ступени триггера. Основная и резервная первая ступени предлагаемого RS-триггера принимают свои состояния параллельно и одновременно. Однако введение в структуру триггера элементов ЗИ-1ШИ/ЗИ-ШШ-НЕ 14 и ЗИ-1ШИ-18, которые контролируют

0

5

0

5

0

5

правильность срабатывания логичес- кюс элементов основной и резервной первых ступеней, накладывает дополнительные ограничения на длительность. импульса на входе 26, По сравнению с известным триггером эта длительность должна быть больше не менее чем на 2Тгр (где ТСр - время срабатывания одного элементарного логического элемента структуры RS-тригге- ра)о

По окончании действия сигналя на синхровходе 26 высокий логический уровень сигнала с выхода элемента НЕ 13 (фиг82, UE) .разрешает перенос правильного состояния первой ступени RS-триггера в его вторую ступень путем открытия обеих групп входов элементов 2И-ИЛИ 5 и 6. Сигнал логического нуля с выхода элемента 2И-ИГШ 5 через элемент НЕ 7 поступает на входы элементов И-КЁ 9 и 23, Сигнал логической единицы через элемент НЕ 8 поступает на входы элементов И-НЕ 10 и 24в Так как прохождение сигналов через элементы НЕ 7 и 8 приводит к их инвертированию, то сигнал логического нуля с выхода элемента НЕ 8 устанавливает единичны логический уровень сигнала на выходах элементов И-НЕ 10 и 24, а сигнал логической единицы с выхода элемента НЕ 7 поступает на первые входы элементов И-НЕ 9 и 23. По окончании срабатывания элементов И-НЕ 10 и 24 элементы И-НЕ 9 и 23 начинают переключаться в состояние логического нуля на своих выходах,

Таким образок9 через время 5Tf срабатывания элементов НЕ 139 2И-ИЛИ 5 и 6, НЕ, 7 и 8, И-НЕ 30 и 9, 24 и 23 на выходах основной и резервной второй ступеней триггера устанавливаются устойчивые состояния сигналов логического нуля - на выходах элементов И-НЕ 9 к 23, и логической единицы - на выходах элементов ,И-НЕ 10 и 24 Контроль правильности срабатывания вторых ступеней триггера начинается через время 5Тер стробом сравнения с выхода элемента ЧЕ 20 на первой и второй группах входов элемента ЗИ ИЛИ/ЗИ ИЛИ-НЕ 15 и второй и третьей группах входов элемента ЗИ-ИЛИ 19.

В случае выполнения условий выражения (2) элемент ЗИ-ИЛИ/ЗИ-ИПИ-НЕ 15 пропускает по своей первой или

0

5

второй группе входов сигнал логической единицы, который посредством своей обратной связи через третью группу входов устанавливает сигнал устойчивой логической единицы ка прямом выходе элемента 15, означающий отказ одного или нескольких логических элементов основной второй ступени триггера,

В случае выполнения условий выражения (4) элемент ЗИ-ИЛИ 19 пропускает через вторую или третью группу входов сигнал высокого логического уровня, который посредством своей обратной свази через первую группу входов устанавпивяет сигнал устойчивой логической единицы на выходе элемента 19, означающий отказ одного или нескольких логических элементов резервной второй ступени триггера.

При отказе основной второй ступени триггера закрываются первые группы входов элементов 2И-ИЛИ 1 и 12 ч открываются вторые группы входов, разрешая поступления на выходы 29 и 30 сигналов с резервной второй ступени.,

В режиме Установка 1 на вход

0 27 подается сигнал логического нуля, о на входы 25, 26 и 28 - сигна-гы логической единицы, Причем на вход 26 подается синхроимпульсе В результате этого на выходах элементов И-НЕ 1 и 2 формируются соответственно сигналы логического нуля и логической единицыо Сигнал логического нуля с выхода элемента И-НЕ 1, поступая на входы элементов И-НЕ 3 и 21, приводит к формированию на выходах элементов И-НЕ 3 ч 21 сигналов логической единицы, которые приводят к формированию сигналов логического нуля на выходах элементов И-НЕ 4 и 22. Конт5 роль правильности срабатывакь я логических элементов основной ъ рэзерв ной первых ступеней триггера осуществляется таким же образом, чтс л в режиме Установка- О, По оксячатш действия синхроимпульса на входе 26 начинается перенос правильного сост тояиия первой ступени трщтгпа в его вторую ступень. Сигнал логического ьуля с выхода элемента Ут-ИЛИ С инвертируется элементом НД. 8 и поступает на вторые входы элементов И-КЕ 10 и 24. Сигнал логической еди- ниды с выхода элемента 2И-ИЛИ 5 инвертируется элементом НЕ 7 vf поступа5

0

0

5

ет на первые входы элементов И-НЕ У и 23. Логический нуль с выхода элемента НЕ 7 приводит к формированию сигналов логической единицы на выходах элементов И-НЕ 9 и 23 и, через время Тсл этих элементов, к формированию сигналов логического нуля на выходах элементов И-НЕ 10 и 24. Контроль правильности срабатывания логических элементов основной и резервной вторых ступеней триггера осуществляется аналогично контролю правильности их срабатывания в режиме Установка О.

В режиме Хранение на входы 25 и 27 RS-триггера подаются сигналы логического нуля, на вход 28 - сигнал логической единицы, а на вход 26 - синхроимпульс. В р-ззулътате этого на выходах элементов И-НЕ 1 и 2 формируются сигналы единичного логического уровня, что практически означает для первых основной и резервной ступеней подтверждение ранее принятого состояния. Схема контроля правильности срабатывания основной и резервной первых ступеней триггера по первой и второй группам входов элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 14 и по второй и третьей группам входов элемента ЗИ-ИЛИ 18 заблокирована нулевыми сигналами с входов 25 и 27 триггера. Совпадение состояний первой и второй ступеней производится на элементах ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ 15 и ЗИ-ИЛИ 19 аналогично контролю совпадения их состояний в режиме Установка О.

Техническое решение предлагаемого RS-триггера позволяет сохранить его работоспособность при исправном состоянии какой-либо одной первой ступени, и какой-либ.о одной из вторых ступеней в любом их сочетании.

Элемент 2И-ИЛИ 17 формирует сигнал Отказ триггера в случае одновременного отказа основной и резервной первых ступеней и в случае одновременного отказа основной и резервной вторых ступеней триггера.

Полный отказ первых ступеней триггера, реализованный Функционалом отказа на второй группе входов элемента 2И-ИЛИ 17, можно представить следующим выражением;

(R.A T V S- A T)(R B .TY S-B T).

(7)

Полный отказ вторых ступеней триггера, реализованный функционалом от

0

5

0

5

0

5

каза на первой группе входов элемента 2И-ИЛИ 17, можно представить дующим выражением

(С П-Т V (T LbT) (ONrT V CF-N-T) « -I,(8)

где R - единичное состояние сигна- нала на входе 27 триггера; S - единичное состояние сигнала на входе 25 триггера; А,А - состояния сигналов в точках А и А на схеме триггера; ,

Т,Т - единичное и нулевое соответственно состояния сигналов на входе 26 тригге- ра;

В,В - состояния сигналов в точках В и В на схеме тригге- . -ра:

С,С - состояния сигналов в точках С и С на схеме тригге- ра;

D,D - состоящш сигналов в точках D и D (0 и 0 соответственно) на схеме триггера; N,N - состояния сигналов в точках N у. N на схеме триггера.

Таким образом, осуществляется непрерывный контроль за правильностью срабатывания основных и резервных первых и вторых ступеней триггера во всех его режимах функционирования. В случае отказа какой-либо из ступеней информация -с ее выходов блокируется и выдается с исправной ступени. Автб- матическая реконфигурация работоспособной структуры триггера осуществляется в любом сочетании работоспособных первой и второй ступеней, т.е. основная I + основная II, основная I.+ резервная II, резервная I + основная II, резервная I + резервная II, что позволяет значительно повысить живучесть, т.е. ремонтопригодность триггера в целом.

Формула изобретения

Резервированный RS-триггер,содержащий шесть элементов И-НЕ и первый элемент НЕ, S-вход триггера соединен с первым входом первого элемента И-НЕ, второй вход которого объединен с первым входом второго элемента И-НЕ, с входом первого элемента НЕ и соединен с синхровходом триггера, выходы первого и второго элементов И-НЕ соединены соответственно с первым входом третьего и с вторым входом четвертого элементов И-НЕ, выход третьего элемента И-HF. соединен с первым входом четвертого элемента И-НЕ.выход которого соединен с вторым входом третьего элемента И-НЕ, отличающийся тем, что, с целью повышения достоверности функционирования и ремонтопригодности, дополнительно содержит второй, третий, вертый, пятый элементы НЕ5 четвертый и пятый элементы НЕ имеют время срабатывания не менее 2Т

ер

где Тсрсреднее время срабатывания логического элемента, пять элементов 2И-ИЛИ седьмой - десятый элементы И-НЕ, два эпемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и два элемента ЗИ-ИЛИ, причем R-вход триггера соединен с вторым входом второго элемента И-НЕ, с вторым входом первой группы входов первого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и с вторым входом второй группы входов первого элемента ЗИ-ИЛИ, S-вход триггера дополнительно соединен с третьим входом второй группы входов первого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и с вторым входом третьей группы входов первого элемента ЗИ-ИЛИ, вход установки з исходное состояние средств функционального контроля Rp триггера соединен с первым входом третьей группы входов первого и второго элементов ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и с вторым входом первой .группы входов первого и второго элементов ЗИ-ИЛИ,, выход первого элемента И-НЕ дополнительно соединен с первым входом седьмого элемента И-НЕ, выход второго элемента И-НЕ дополнительно соединен с вторым входом восьмого элемента И-НЕ, выход первого элемента НЕ соединен с входо четвертого элемента НЕ, с первыми входами первых и вторых групп входов первого и второго элементов 2И-ИЛИ, с вторыми входами первой н второй групп входов второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-КЕ и с вторыми входами второй и третьей групп входов второго элемента ЗИ-ИЛИ, выход третьего элемента И-НЕ дополнительно соединен с вторым входом первой группы входов первого элемента 2И-ИЛИ и с первым входом первой группы входов первого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, выход четвертого элемента дополнительно

5

0

5

0

5

0

5

соединен с вторым входом первой группы входов второго элемента 2И-ИЛИ и с первым входом второй группы входов первого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, выход первого элемента 2И-ИЛИ соединен с входом второго элемента НЕ, с четвертым входом второй группы входов второго элемента ЗИ-ИШ/ЗИ-ИПИ-НЕ и с третьим входом третьей группы входов второго элемента ЗИ-ИЛИ, выход второго элемента 2И-ИЛИ соединен с входом третьего элемента НЕ, с четвертым входом первой группы входов второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и с третьим входом второй группы входов второго элемента ЗИ-ИЛИ, выход второго элемента НЕ соединен с первым входом пятого элемента И-НЕ и с первым входом девятого элемента И-НЕ, выход третьего элемента НЕ соединен с вторым входом шестого и с вторым входом десятого элементов И-НЕ, выход пятого элемента И-НЕ соединен с вторым входом первой группы входов третьего элемента 2И-ИЛИ, с первым входом шестого элемента И-НЕ и с третьим входом первой группы входов второго элемент, ЗИ-ИЛИ/ /ЗИ-ИЛИ-НЕ, выход шестого элемента И-НЕ соединен с вторым входом первой группы входов четвертого элемента 2И-ИЛИ, с вторым входом пятого элемента И-НЕ и с третьим входом второй группы входов второго элемента ЗИ-ИЛИ/ЗН-ИЛИ-НЕ, инверсный внхогд первого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с третьим входом первой группь входов первого и второго элементов 2И-ИЛИ, прямой выход первого элемента ЗИ-ИЛИ/ЗИ--ИЛИ-НЕ соединен с вторым входом второй группы входов первого и второго элементов , с вторьгм входом сроек третьей группы входов и с первым входом второй группы входов пятого элемента 2И-ИЛИ1 инверсный выход второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с первым входом первой труппы входов третьего и четвертого элементов 2И-ИЛИ, прямой выход второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ соединен с вторым входом своей третьей групп: входов, с первыми входами вторых групп входов третьего и четвертого элементов 2И-ИЛИ и с вторам входом первой группы входов пятого элемента выход первого элемента ЗИ-ИЛК соединен с первым входом своей первой группы входов ji с вторым входом вто™.

рой группы входов пятого элемента 2И-ИЛИ, выход второго элемента ЗИ-ИЛИ соединен с первым входом своей первой группы входов и с первым входом первой группы входов пятого элемента 2И-ИЛИ, выход четвертого элемента НЕ соединен с третьим входом первой, с вторым входом второй групп входов первого элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ, с первым входом второй, с первым входом третьей групп входов первого элемента ЗИ-ЩТИ и с входом пятого элемента НЕ, выход которого соединен с первыми входами первой и второй групп входов второго элемента ЗИ-ИЛИ/ЗИ-ИЛИ-НЕ и с первыми входами второй и третьей групп входов второго элемента ЗИ-ИЛИ, выход седьмого элемента И-НЕ соединен с первым входом восьмого элемента , с третьим входом второй группы входов первого элемента ЗИ-ИЛИ и с третьим входом второй группы входов первого элемента 2И-ИЛИ, выход восьмого элемента И-НЕ

соединен с вторым входом седьмого элемента И-НЕ, с третьим входом третьей группы входов первого элемента ЗИ-ИЛИ и с третьим входом второй группы входов второго элемента 2И-ИЛИ, выход девятого элемента И-НЕ соединен с первым входом десятого элемента И-НЕ, с третьим входом второй группы входов второго элемента ЗИ-ИЛИ и с вторым входом второй группы входов третьего элемента 2И-ИЛИ, выход десятого элемента И-НЕ соединен с вторым входом девятого эле5 мента И-НЕ, с третьим входом третьей группы входов второго элемента ЗИ-ИЛИ и с вторым входом второй группы входов четвертого элемента 2И-ИЛИ, выход которого является инверсным вы0 ходом триггера, выход третьего элемента 2И-ИЛИ является прямым выходом триггера, выход пятого элемента 2И-ИЛИ является выходом Отказ триггера.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| ДV-триггер | 1989 |

|

SU1629963A1 |

| Двоичный счетчик | 1988 |

|

SU1684927A1 |

| Двоичный счетчик | 1991 |

|

SU1803975A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Управляемый делитель частоты следования импульсов | 1990 |

|

SU1757097A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Двоичный счетчик | 1988 |

|

SU1599988A1 |

| Устройство для управления включением резервных исполнительных элементов | 1990 |

|

SU1749886A1 |

Изобретение относится к триггер- ным схемам и представляет собой RS- триггер, который может быть использован в устройствах автоматики и вычислительной техники при разработке счетчиков, делителей частоты, регистров, распределителей импульсов, формирователей парофазного сигнала и т.п. Цель изобретения - повышение достоверности функционирования и ре

римечание. - - безразличное состояние сигнала на соответствующем входе триггера}

Q(T) - состояние выхода триггера, соответствующее своему предыдущему состоянию; Н - неопределенное состояние соответствующего выхода.

J/R Vt

US

Щ1- lr

UK

UЈ

n

| Каган Б.М | |||

| и Каневский М.М | |||

| Цифровые вычислительные машины и системы.- М.: Энергия, 1973, с.170, рис.3-28 | |||

| Там же, с | |||

| Джино-прядильная машина | 1922 |

|

SU173A1 |

Авторы

Даты

1991-02-23—Публикация

1989-03-27—Подача