Область техники, к которой относится изобретение

Настоящее изобретение относится к способу и устройству для сравнения выходных данных по меньшей мере двух исполнительных блоков микропроцессора согласно ограничительной части независимых пунктов формулы изобретения.

Уровень техники

Нерегулярные или случайные сбои, обусловленные альфа-частицами или космическим излучением, представляют собой все большую проблему для интегральных полупроводниковых схем. В связи с уменьшением структурной ширины, понижением напряжения и повышением тактовой частоты возрастает вероятность того, что пик напряжения, вызванный воздействием альфа-частицы или космического излучения, приведет к искажению логического значения в интегральной схеме. Следствием может стать ошибочный результат вычисления. Поэтому в системах, важных с точки зрения безопасности, такие ошибки необходимо с уверенностью обнаруживать.

В системах, важных в отношении безопасности, например в системе регулирования антиблокировочного устройства автомобиля, в которых сбои электроники должны надежно отслеживаться, обычно используются устройства управления с избыточностью по обнаружению ошибок. Так, например, в известных антиблокировочных системах в каждом случае дублируется целый микроконтроллер, причем все антиблокировочные функции вычисляются с избыточностью и проверяются на соответствие. Если имеет место несоответствие результатов, антиблокировочная система отключается.

Такие процессоры по меньшей мере с двумя интегрированными исполнительными блоками известны также как двухъядерные или многоядерные арихитектуры. Различные исполнительные блоки или модули (ядра) отрабатывают с резервированием и тактовой синхронизацией один и тот же сегмент программы, результаты, полученные обоими ядрами, сравниваются, и при сравнении на соответствие обнаруживается возможная ошибка.

Если в настоящее время двухъядерные процессоры работают в режиме сравнения, то ядра или исполнительные блоки должны быть практически одинаковыми, чтобы обеспечить возможность сравнения выходных сигналов в каждом такте (периоде синхронизации). Вместе с тем, с точки зрения безопасности предпочтительно использовать различные исполнительные блоки. Но если исполнительные блоки различны, то их выходные сигналы уже нельзя сравнивать в каждом такте.

Раскрытие изобретения

В основу настоящего изобретения положена задача сравнения выходных сигналов различных исполнительных блоков. Изобретение решает эту проблему путем введения управляющего сигнала, посредством которого исполнительный блок сигнализирует компаратору, или блоку сравнения, что выданный вместе с этим сигналом элемент данных подлежит сравнению с элементом данных на выходе другого исполнительного блока. Это позволяет использовать различные исполнительные блоки и различное программное обеспечение. Сопоставимыми должны быть только подлежащие сравнению данные и их формат. Вопрос о том, должна ли последовательность передачи подлежащих сравнению данных компаратору также быть одинаковой, зависит от конкретной формы реализации рассматриваемого изобретения.

Таким образом, исполнительный блок сообщает компаратору о необходимости сравнения следующего элемента выходных данных с элементом выходных данных по меньшей мере второго исполнительного блока, после чего происходит сравнение этих по меньшей мере двух элементов выходных данных. В предпочтительном варианте осуществления изобретения по меньшей мере два исполнительных блока обрабатывают входные данные независимо друг от друга. Целесообразно, чтобы исполнительный блок сообщал о необходимости сравнения следующего элемента данных посредством сигнала сравнения. Сигнал сравнения и подлежащий сравнению элемент выходных данных предпочтительно выдавать с возможностью их однозначного соотнесения друг с другом. Подлежащему сравнению элементу данных целесообразно присваивать метку, инициирующую сравнение. Предпочтительно, чтобы все исполнительные блоки, выходные данные которых подлежат сравнению, сигнализировали об этом компаратору. Выходные данные, подлежащие сравнению, целесообразно записывать в заданной последовательности по меньшей мере в одно буферное запоминающее устройство.

Объектом изобретения является также устройство для сравнения данных в вычислительной системе, включающей в себя по меньшей мере два исполнительных блока и компаратор, причем сравнение данных осуществляется в компараторе, а каждый исполнительный блок обрабатывает входные данные и генерирует выходные данные. В предлагаемом в изобретении устройстве исполнительный блок сообщает компаратору о необходимости сравнения следующего элемента выходных данных с элементом выходных данных по меньшей мере второго исполнительного блока, после чего происходит сравнение этих по меньшей мере двух элементов выходных данных. В предлагаемом в изобретении устройстве целесообразно предусмотреть по меньшей мере одно буферное запоминающее устройство, выполненное с возможностью записи в него данных в задаваемой последовательности и последующей выдачи данных компаратору. В предпочтительном варианте осуществления изобретения буферное запоминающее устройство представляет собой память обратного магазинного типа. Осуществление изобретения целесообразно в устройстве, а также в вычислительной системе, включающей в себя такое устройство.

Краткое описание чертежей

Другие преимущества и предпочтительные варианты осуществления изобретения раскрыты ниже со ссылкой на прилагаемые чертежи, на которых показано:

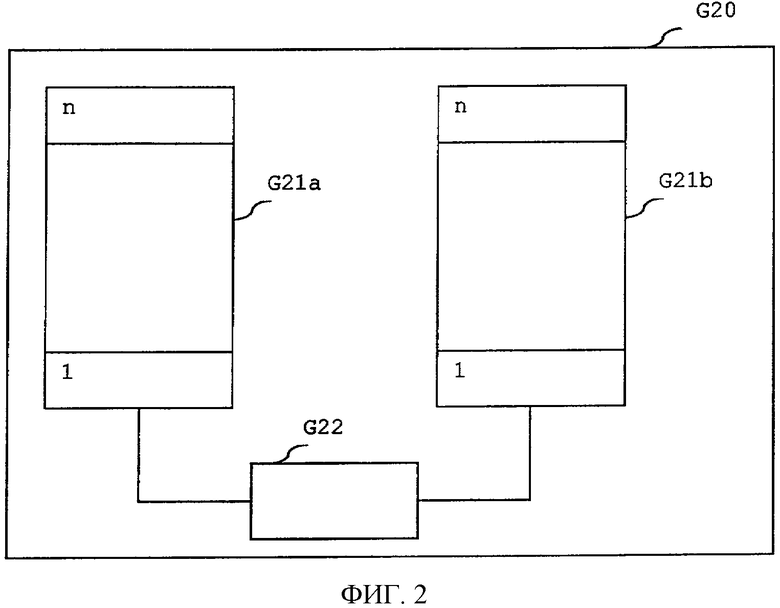

на фиг.1 - многопроцессорная система G60 с двумя исполнительными блоками G10a и G10b и компаратором G20,

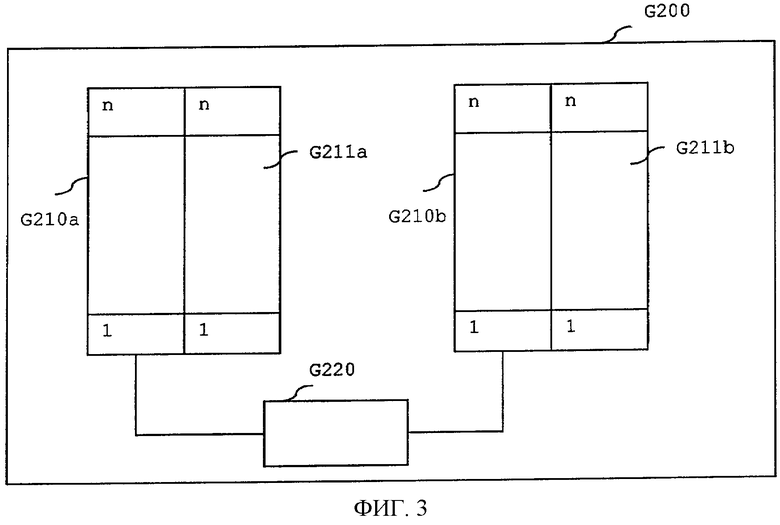

на фиг.2 - вариант исполнения компаратора G20 с двумя очередями G21a и G21b,

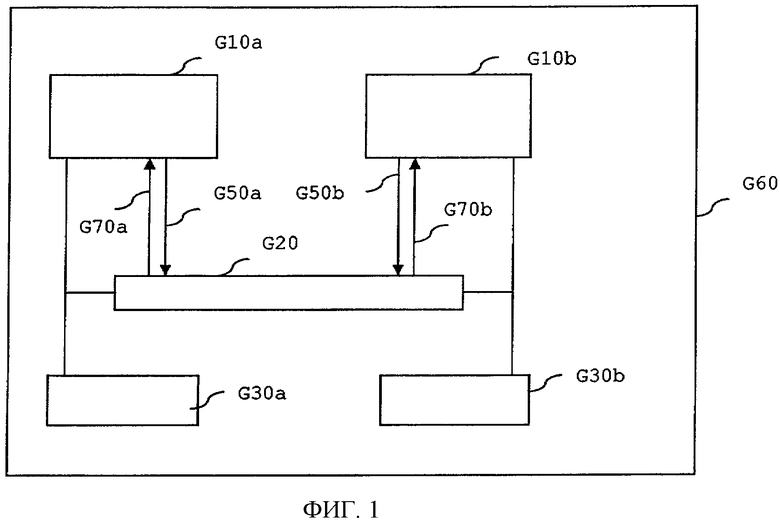

на фиг.3 - вариант исполнения компаратора G200 с двумя списками G210a, С211а и С210b, G211b.

Осуществление изобретения

Исполнительным блоком (модулем) могут в дальнейшем именоваться как процессор/ядро/центральный процессор, так и блок вычислений (сопроцессор) с плавающей точкой, процессор цифровых сигналов, сопроцессор или арифметическое логическое устройство. Осуществление изобретения рассматривается на примере многопроцессорной системы G60, показанной на фиг.1, по меньшей мере с двумя исполнительными блоками G10a, G10b и компаратором (блоком сравнения) G20. Каждый исполнительный блок G10a, G10b имеет по меньшей мере один выход на соответствующие системные интерфейсы G30a, G30b. Через эти интерфейсы можно управлять регистрами, запоминающими или периферийными устройствами, в частности цифровыми выходами, цифроаналоговыми преобразователями, коммуникационными контроллерами (контроллерами связи). Выходные сигналы исполнительных блоков G10a, G10b могут сравниваться в компараторе G20. При несовпадении делается вывод о наличии ошибки, что позволяет принять соответствующие меры. К сравнению привлекаются выходные данные и/или адреса исполнительных блоков. Сравнению могут подвергаться и другие управляющие сигналы. Независимо от выбранных выходных сигналов, подлежащих сравнению, ниже речь идет об элементе данных, который нужно сравнить с другим элементом данных.

На фиг.1 показана возможная реализация многопроцессорной системы G60 с двумя исполнительными блоками G10a и G10b. Компаратор G20 активизируется управляющим сигналом G50a, G50b от исполнительных блоков G10a, G10. Если исполнительному блоку G10a, G10b предстоит передача на системный интерфейс соответственно G30a и G30b элемента данных без необходимости его сравнения, то этот элемент данных передается без выдачи сигналов G50a, G50b. Соответственно, компаратор G20 не обрабатывает эти данные. Если исполнительному блоку G10a, G10b предстоит передача на системный интерфейс соответственно G30a и G30b элемента данных, и этот элемент данных подлежит сравнению с соответствующим элементом данных на выходе другого исполнительного блока G10a, G10b, то дополнительно к выходным сигналам исполнительного блока, необходимым для передачи данных на системный интерфейс, для компаратора G20 генерируется сигнал G50a в случае исполнительного блока G10a и сигнал G50b в случае исполнительного блока G10b. Эти сигналы G50a и G50b также генерируются исполнительными блоками G10a и G10b. Они сигнализируют компаратору G20 о том, что переданный на системный интерфейс элемент данных, при необходимости с соответствующим ему адресом, необходимо сравнить с соответствующим элементом данных другого исполнительного блока. Сравнение выполняется в том случае, если другой исполнительный блок также передает элемент данных на свой системный интерфейс и при этом также сигнализирует компаратору G20 о необходимости выполнения сравнения. Сигналы G50a в случае исполнительного блока G10a и G50b в случае исполнительного блока G10b, указывающие на необходимость сравнения, не обязательно генерировать синхронно с передачей элемента данных исполнительным блоком, но их нужно генерировать таким образом, чтобы такой сигнал можно было однозначно соотнести с этим элементом данных (включая адрес). Посредством сигналов G70a, G70b компаратор G20 может при необходимости временно приостановить работу исполнительных блоков. При этом исполнительный блок G10a останавливается сигналом G70a, а исполнительный блок G10b - сигналом G70b. Исполнительные блоки не работают до тех пор, пока соответствующие сигналы G70a и G70b не будут сняты с выходов компаратора.

В первом варианте, показанном на фиг.2, приведено описание возможной реализации компаратора (блока сравнения) G20. Внутри компаратора организована очередь для каждого подключенного исполнительного блока. Эти очереди построены по принципу памяти обратного магазинного типа: "первым пришел - первым обслужен". В примере исполнения, показанном на фиг.2, - это очередь G21a для исполнительного блока G10a и очередь G21b для исполнительного блока G10b. В очереди имеется n записей, но по меньшей мере одна такая запись. Если исполнительный блок сигнализирует о том, что тот или иной элемент данных необходимо сравнить, этот элемент данных сохраняется в очереди в одной записи. Если в очереди больше нет свободных записей, работа соответствующего исполнительного блока приостанавливается сигналом G70a или G70b, как показано на фиг.1, пока в очереди не освободится какая-либо запись. Как возможный вариант, компаратор G20 может генерировать сигнал ошибки, если исполнительный блок попытается вставить дополнительный элемент данных в уже заполненную очередь. Если во всех очередях компаратора G20 (в данном случае в очередях G21a и G21b) имеется по меньшей мере одна запись, то согласно принципу "первым пришел - первым обслужен" в каждом случае блок G22 сравнивает друг с другом соответствующие первые, т.е. старейшие по времени записи. Если подлежащие сравнению данные различны, генерируется сигнал ошибки, после чего записи в очереди сбрасываются, т.е. удаляются из нее. При идентичности данных они также удаляются из очереди. Как возможный вариант, при числе очередей, большем двух, принимается мажоритарное решение (голосованием). Общим признаком этого варианта осуществления изобретения является то, что подлежащие сравнению данные должны выдаваться всеми подключенными исполнительными блоками в одинаковой последовательности, чтобы они могли выстраиваться в очереди в правильной последовательности. Какие данные с какими подлежат сравнению, определяется только их положением в очередях. Сравниваются всегда самые первые, т.е. самые старые, записи в очередях.

Еще один вариант выполнения компаратора G20 представлен на фиг.3, где компаратор обозначен позицией G200. Для каждого подключенного исполнительного блока в компараторе G200 имеются списки G210a, G210b, в которых сохраняется подлежащий сравнению элемент данных. Дополнительно к спискам G210a, G210b существуют также списки G211a, G211b, в которых для каждого помещенного в списки G210a, G210b элемента данных сохраняется однозначный идентификатор. После заполнения списка работа соответствующего исполнительного блока приостанавливается посредством сигналов G70a или G70b, показанных на фиг.1, или выдается сигнал ошибки, если исполнительный блок попытается вставить дополнительный элемент данных в уже заполненный список. Сравнение данных осуществляется в том случае, если во всех списках G210a, G210b имеются данные с соответствующими идентичными идентификаторами, находящимися в списках G211a, G211b. Данные сравниваются, и при несовпадении генерируется сигнал ошибки. При совпадении данные передаются на подключенные системные интерфейсы G30a, G30b или G32, если системный интерфейс соотнесен с компаратором. После сравнения независимо от его результата из списков G210a, G210b удаляются данные, а из списков G211а, G211b - соответствующие идентификационные номера. При наличии более двух списков, как возможный вариант, может приниматься мажоритарное решение. Особенностью этого варианта является то, что подлежащие сравнению данные не обязательно должны предаваться в компаратор всеми подключенными исполнительными блоками в одинаковой последовательности. Сравнение данных осуществляется в том случае, если в обоих списках G210a и G210b имеются данные, а в списках идентификаторов имеется по меньшей мере два одинаковых идентификатора.

Изобретения относятся к способу и устройству для сравнения данных в вычислительной системе, включающей в себя, по меньшей мере, два исполнительных блока. Техническим результатом является повышение безопасности работы вычислительной системы, использующей различные исполнительные блоки и различное программное обеспечение. Устройство для сравнения данных в вычислительной системе содержит, по меньшей мере, два исполнительных блока и компаратор, причем сравнение данных осуществляется в компараторе, а каждый исполнительный блок обрабатывает входные данные и генерирует выходные данные, при этом исполнительный блок выполнен с возможностью сообщать компаратору о необходимости сравнения следующего элемента выходных данных с элементом выходных данных, по меньшей мере, второго исполнительного блока, после чего происходит сравнение этих, по меньшей мере, двух элементов выходных данных. 3 н. и 8 з.п. ф-лы, 3 ил.

1. Способ сравнения данных в вычислительной системе, включающей в себя по меньшей мере два исполнительных блока, причем сравнение данных осуществляется в компараторе, а каждый исполнительный блок обрабатывает входные данные и генерирует выходные данные, отличающийся тем, что исполнительный блок сообщает компаратору о необходимости сравнения следующего элемента выходных данных с элементом выходных данных по меньшей мере второго исполнительного блока, после чего происходит сравнение этих по меньшей мере двух элементов выходных данных.

2. Способ по п.1, отличающийся тем, что по меньшей мере два исполнительных блока обрабатывают входные данные независимо друг от друга.

3. Способ по п.1, отличающийся тем, что исполнительный блок сообщает о необходимости сравнения следующего элемента данных посредством сигнала сравнения.

4. Способ по п.3, отличающийся тем, что сигнал сравнения и подлежащий сравнению элемент выходных данных выдают с возможностью их однозначного соотнесения друг с другом.

5. Способ по п.4, отличающийся тем, что подлежащему сравнению элементу данных присваивают метку, инициирующую сравнение.

6. Способ по п.1, отличающийся тем, что все исполнительные блоки, выходные данные которых подлежат сравнению, сигнализируют об этом компаратору.

7. Способ по п.1, отличающийся тем, что выходные данные, подлежащие сравнению, записывают в заданной последовательности по меньшей мере в одно буферное запоминающее устройство.

8. Устройство для сравнения данных в вычислительной системе, включающей в себя по меньшей мере два исполнительных блока и компаратор, причем сравнение данных осуществляется в компараторе, а каждый исполнительный блок обрабатывает входные данные и генерирует выходные данные, отличающееся тем, что исполнительный блок сообщает компаратору о необходимости сравнения следующего элемента выходных данных с элементом выходных данных по меньшей мере второго исполнительного блока, после чего происходит сравнение этих по меньшей мере двух элементов выходных данных.

9. Устройство по п.8, отличающееся тем, что в нем предусмотрено по меньшей мере одно буферное запоминающее устройство, выполненное с возможностью записи в него данных в задаваемой последовательности и последующей выдачи данных компаратору.

10. Устройство по п.9, отличающееся тем, что буферное запоминающее устройство представляет собой память обратного магазинного типа.

11. Вычислительная система, содержащая устройство по п.8.

| US 5572662 А, 05.11.1996 | |||

| US 6357024 В, 12.03.2002 | |||

| US 5504859 А, 02.04.1996 | |||

| Микропроцессорная система | 1991 |

|

RU2000603C1 |

Авторы

Даты

2011-02-10—Публикация

2006-07-27—Подача