Область техники, к которой относится изобретение

Настоящее изобретение относится к способу и устройству для сравнения выходных данных по меньшей мере двух исполнительных блоков микропроцессора согласно ограничительной части независимых пунктов формулы изобретения.

Уровень техники

Нерегулярные или случайные сбои, обусловленные альфа-частицами или космическим излучением, представляют собой все большую проблему для интегральных полупроводниковых схем. В связи с уменьшением структурной ширины, понижением напряжения и повышением тактовой частоты возрастает вероятность того, что пик напряжения, вызванный воздействием альфа-частицы или космического излучения, приведет к искажению логического значения в интегральной схеме. Следствием может стать ошибочный результат расчета. Поэтому в системах, важных с точки зрения безопасности, в частности в автомобиле, такие ошибки необходимо с уверенностью обнаруживать.

В системах, важных в отношении безопасности, например в системе регулирования антиблокировочного устройства автомобиля, в которых сбои электроники должны надежно отслеживаться, обычно используются устройства управления с избыточностью по обнаружению ошибок. Так, например, в известных антиблокировочных системах в каждом случае дублируется целый микроконтроллер, причем все антиблокировочные функции вычисляются с избыточностью и проверяются на соответствие. Если имеет место несоответствие результатов, антиблокировочная система отключается.

Такие процессоры по меньшей мере с двумя интегрированными ядрами известны также как двухъядерные или многоядерные архитектуры. Различные исполнительные блоки (ядра) отрабатывают с резервированием и тактовой синхронизацией один и тот же сегмент программы, результаты, полученные обоими ядрами, сравниваются, и при их сравнении на соответствие устанавливается возможное наличие ошибки.

Для ускорения доступа к командам (инструкциям) и данным процессоры оснащают кэш-памятью. Это необходимо при постоянно увеличивающемся объеме данных, с одной стороны, и усложнении обработки данных процессорами с постоянно повышающимся быстродействием, с другой стороны. Устройство кэш-памяти отчасти позволяет ускорить доступ к большой (основной) памяти, и, следовательно, процессору не нужно ожидать подготовки данных. Известны устройства кэш-памяти исключительно для команд и исключительно для данных, но также и "унифицированные устройства кэш-памяти", в которых хранятся как данные, так и команды. Известны также системы с несколькими уровнями (иерархическими ступенями) устройств кэш-памяти. Такие многоуровневые устройства кэш-памяти используются, чтобы посредством градации емкости памяти и различных стратегий адресации устройств кэш-памяти на различных уровнях обеспечить оптимальное согласование быстродействия между процессором и (главной) памятью.

Второй причиной использования устройств кэш-памяти является необходимость устранения конфликтов доступа по системным шинам и шинам памяти в микропроцессорных системах. В этих системах каждый процессор принято оснащать кэш-памятью, а в случае многоуровневых устройств кэш-памяти - соответственно несколькими устройствами кэш-памяти.

В известной конфигурации устройств кэш-памяти в переключаемой двухъядерной системе каждое из двух ядер имеет постоянно приданную ему кэш-память, к которой ядро обращается в режиме повышенной производительности. В режиме сравнения каждое из двух ядер обращается к своей кэш-памяти. Наряду с тем фактом, что в режиме сравнения информация многократно сохраняется в кэш-памяти (отдельно для каждого исполнительного блока), затраты времени на переключение, в частности, из режима повышенной производительности в режим сравнения значительны. При этом переключении состояние устройств кэш-памяти должно быть одинаковым. Только тогда можно гарантировать, что в режиме сравнения не окажется так, что кэш-память одного из участвующих в сравнении блоков окажется пустой (требуемая информация не записана в кэш-память и должна дозагружаться), кэш-память другого -заполненной (требуемая информация записана в кэш-память, и в дозагрузке нет необходимости).

Раскрытие изобретения

Задача изобретения состоит в том, чтобы устранить недостатки известных способов при использовании устройств кэш-памяти в переключаемой многопроцессорной системе. При этом к недостаткам относится прежде всего то, что в известных конфигурациях устройств кэш-памяти они требуют сложной синхронизации при переключении из режима повышенной производительности в режим сравнения.

Для обеспечения возможности переключения в переключаемой многопроцессорной системе между различными режимами, в частности режимом повышенной производительности и режимом сравнения, предпочтительно, чтобы не каждый исполнительный блок имел собственную кэш-память, так как особенно при переключении в режим сравнения пришлось бы выполнять затратное по времени согласование устройств кэш-памяти. В предлагаемых структурах от этого можно практически полностью отказаться.

Далее предпочтительно, чтобы размер различных устройств кэш-памяти для различных режимов (сравнения и повышенной производительности) можно было согласовывать с требованиями режимов. Кроме того, в некоторых режимах может оказаться целесообразным полный отказ от кэш-памяти, в частности, если сам доступ к шине не намного медленнее, чем доступ к кэш-памяти.

Соответственно, объектом изобретения является способ управления доступом к памяти в вычислительной системе по меньшей мере с двумя исполнительными блоками, в которой предусмотрены буферная память, в частности кэш-память, а также средства переключения и средства сравнения, причем переключение осуществляется между режимом повышенной производительности и режимом сравнения, отличающийся тем, что в режиме сравнения доступ к буферной памяти закрывают для всех исполнительных блоков, а в режиме повышенной производительности доступ к буферной памяти открывают по меньшей мере для одного исполнительного блока.

В предпочтительном варианте осуществления предлагаемого в изобретении способа в режиме сравнения соединение исполнительного блока, связанного с буферной памятью, разрывают с помощью средств переключения.

В еще одном предпочтительном варианте осуществления предлагаемого в изобретении способа в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки запрещают доступ к памяти, не являющейся буферной.

В еще одном предпочтительном варианте осуществления предлагаемого в изобретении способа в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки данные в памяти, не являющейся буферной, делают недействительными или блокируют.

В еще одном предпочтительном варианте осуществления предлагаемого в изобретении способа в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки вычислительную систему перезапускают или повторно включают.

В еще одном предпочтительном варианте осуществления предлагаемого в изобретении способа в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки по меньшей мере один исполнительный блок перезапускают или повторно включают.

Объектом изобретения является также устройство для управления доступом к памяти в вычислительной системе по меньшей мере с двумя исполнительными блоками, в которой предусмотрены буферная память, в частности кэш-память, а также средства переключения и средства сравнения, причем переключение осуществляется между режимом повышенной производительности и режимом сравнения, отличающееся тем, что оно содержит средства, выполненные таким образом, чтобы в режиме сравнения закрывать доступ к буферной памяти для всех исполнительных блоков, а в режиме повышенной производительности открывать доступ к буферной памяти по меньшей мере для одного исполнительного блока.

В предпочтительном варианте выполнения предлагаемого в изобретении устройства указанные средства выполнены как средства переключения, запрещающие или разрешающие исполнительному блоку доступ к буферной памяти.

В еще одном предпочтительном варианте выполнения предлагаемого в изобретении устройства средства сравнения выполнены таким образом, чтобы в режиме сравнения проверять данные на соответствие, и при несоответствии данных устанавливать наличие ошибки, в случае которой они запрещают доступ к памяти, не являющейся буферной.

В еще одном предпочтительном варианте выполнения предлагаемого в изобретении устройства средства сравнения выполнены таким образом, чтобы в режиме сравнения проверять данные на соответствие, и при несоответствии данных устанавливать наличие ошибки, в случае которой они делают недействительными или блокируют данные в памяти, не являющейся буферной.

В еще одном предпочтительном варианте выполнения предлагаемого в изобретении устройства средства сравнения расположены между по меньшей мере одним исполнительным блоком и буферной памятью.

В еще одном предпочтительном варианте выполнения предлагаемого в изобретении устройства буферная память расположена между по меньшей мере одним исполнительным блоком и средствами сравнения.

При этом средства переключения и средства сравнения могут быть выполнены в виде одного блока переключения и сравнения.

Краткое описание чертежей

Ниже приводится подробное описание вариантов осуществления изобретения, поясняемое чертежами, на которых показаны:

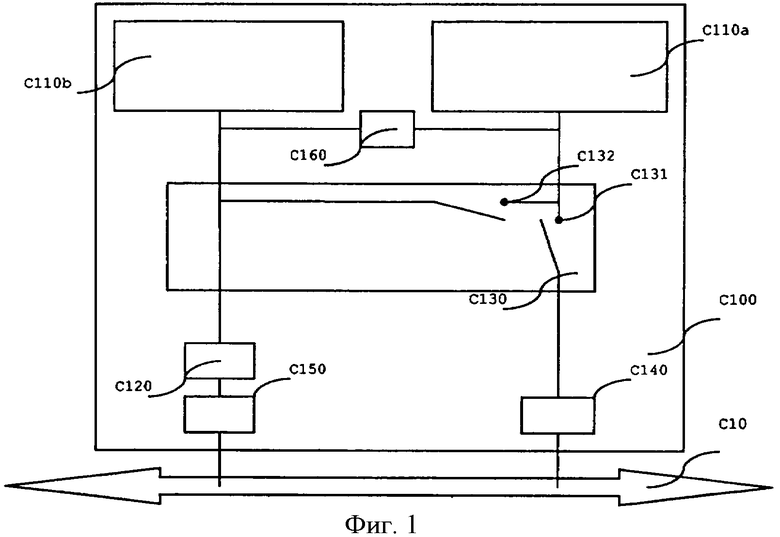

на фиг.1 - система C100 с двумя исполнительными блоками, из которых только один в режиме повышенной производительности и в режиме сравнения через кэш-память имеет доступ к шине C10;

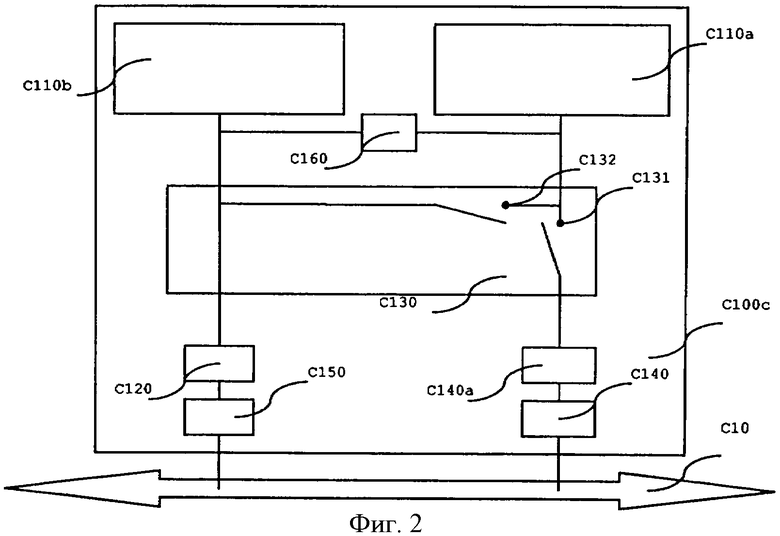

на фиг.2 - система С 100с с двумя исполнительными блоками, каждый из которых в режиме повышенной производительности и в режиме сравнения имеет доступ к шине C10 через свою кэш-память, из которых, однако, в режиме сравнения используется только одна;

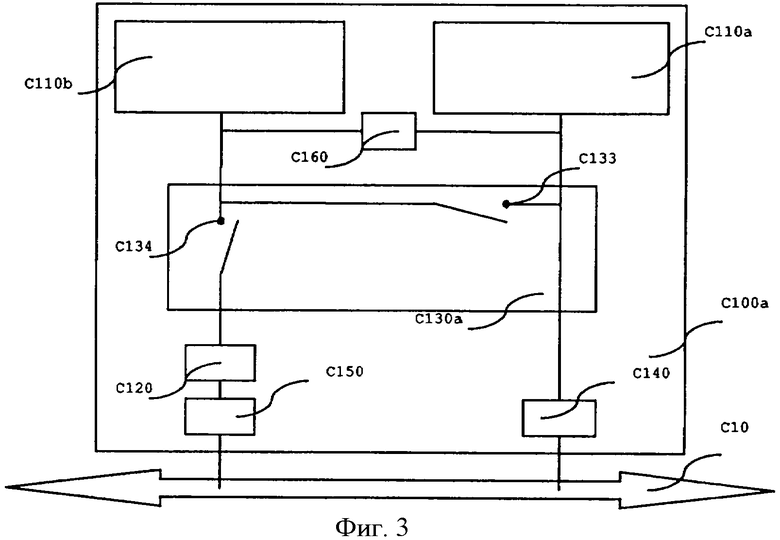

на фиг.3 - система С 100а с двумя исполнительными блоками, из которых только один в режиме повышенной производительности через кэш-память имеет доступ к шине C10; в режиме сравнения кэш-память не используется;

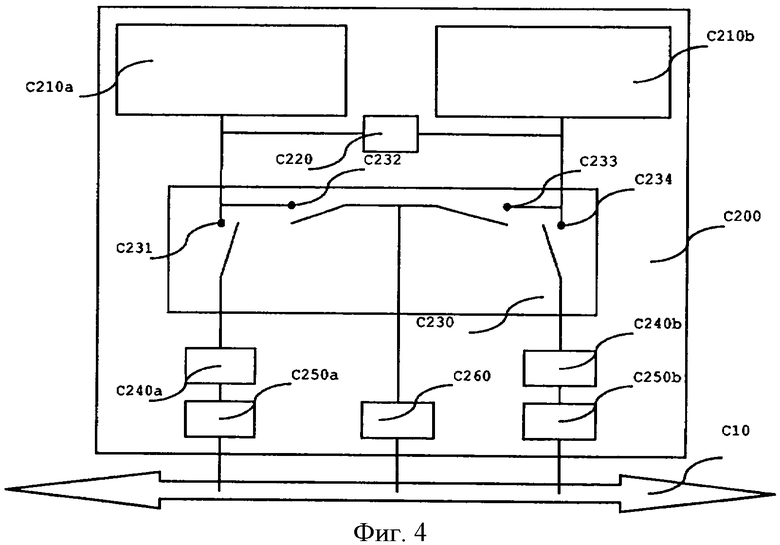

на фиг.4 - система С200 с двумя исполнительными блоками, каждый из которых в режиме повышенной производительности и в режиме сравнения через свою кэш-память имеет доступ к шине C10; в режиме сравнения доступ к шине осуществляется через отдельный блок подключения к шине;

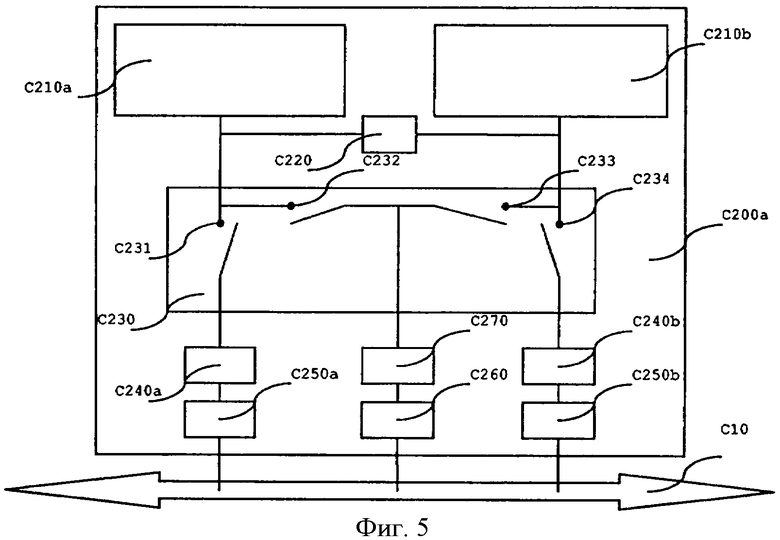

на фиг.5 - система С200а с двумя исполнительными блоками, каждый из которых в режиме повышенной производительности и в режиме сравнения имеет доступ к шине C10 через свою кэш-память; в режиме сравнения доступ к шине осуществляется через отдельную кэш-память и отдельный блок подключения к шине;

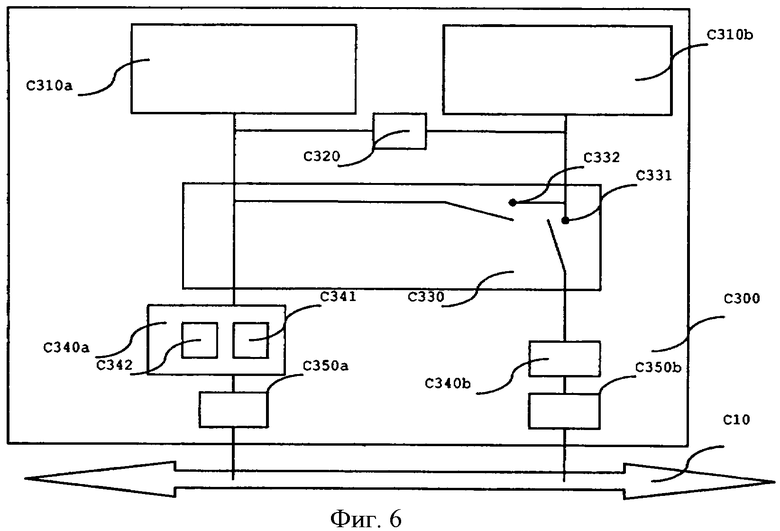

на фиг.6 - система С300 с двумя исполнительными блоками, каждый из которых в режиме повышенной производительности и в режиме сравнения имеет доступ к шине C10 через свою кэш-память, из которых, однако, в режиме сравнения используется только одна; используемая в режиме сравнения кэш-память для решения своих задач использует внутри себя разные запоминающие устройства в зависимости от текущего режима работы системы С300;

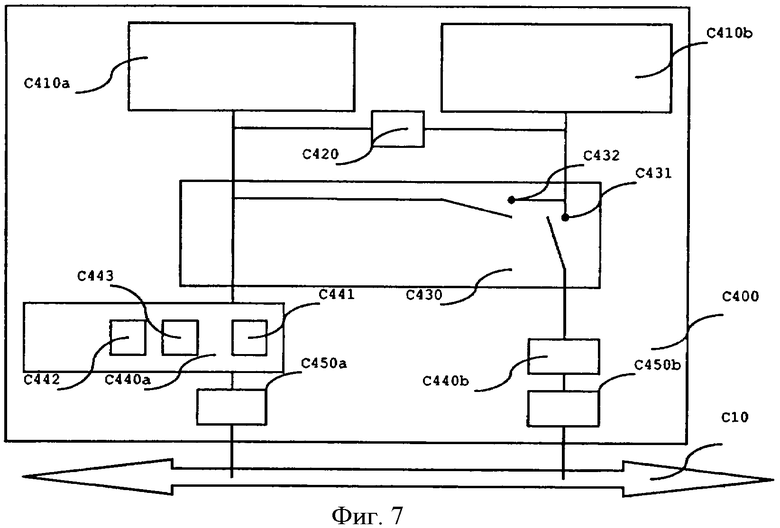

на фиг.7 - система С400 с двумя исполнительными блоками, каждый из которых в режиме повышенной производительности и в режиме сравнения имеет доступ к шине C10 через свою кэш-память, из которых, однако, в режиме сравнения используется только одна; используемая в режиме сравнения кэш-память для решения своих задач использует внутри себя разные запоминающие устройства в зависимости от текущего режима работы системы С400; соотношение размеров этих двух запоминающих устройств регулируется отдельным устройством;

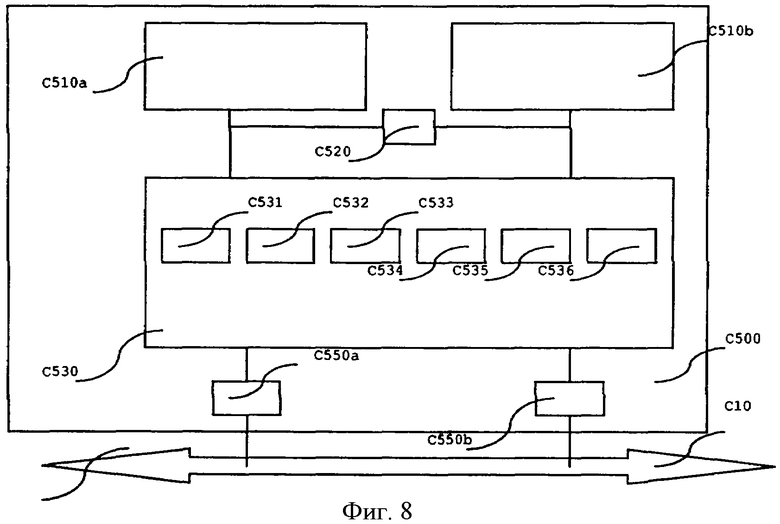

на фиг.8 - система С500 с двумя исполнительными блоками, имеющими доступ к шине C10 через кэш-память; в зависимости от режима работы системы С500 операции обращения исполнительных блоков к памяти обслуживаются по-разному.

Осуществление изобретения

Исполнительным блоком могут в дальнейшем именоваться как процессор, ядро, центральный процессор, так и модуль обработки операций с плавающей точкой, процессор цифровых сигналов, сопроцессор или арифметическое логическое устройство.

В некоторых многопроцессорных системах кэш-память используется только для того, чтобы избежать конфликтов доступа к системной шине и/или шине памяти. Если бы в системе был только один исполнительный блок, то в этом случае кэш-память не потребовалась бы, так как основная память имеет достаточное быстродействие, чтобы выполнять запросы на чтение от исполнительного блока.

На фиг.1 показан первый вариант исполнения многопроцессорной системы C100 с двумя исполнительными блоками С110а и C110b, которая по шине C10 может обращаться к памяти. Блок С130 регулирует доступ к шине C10 в зависимости от режима работы системы C100. В режиме повышенной производительности переключатель С131 замкнут, а переключатель С132 разомкнут. Таким образом, исполнительный блок С110b через кэш-память С120 и блок (разъем) С150 подключения к шине получает доступ к шине C10. Исполнительный блок С110а связан с шиной C10 напрямую через блок С140. Если кэш-память С120 имеет правильный размер или емкость, то обращения исполнительного блока С110b к памяти обслуживаются преимущественно кэш-памятью С120, поэтому доступ к шине C10 требуется лишь в редких случаях. При обращении же к памяти исполнительного блока С110а всегда необходим доступ к шине C10. Только в том случае, если доступ к основной памяти не может обслуживаться кэш-памятью С120, блок С150 обеспечивает доступ к шине. Если в то же время исполнительный блок С110а обращается к шине C10 через блок (разъем) С140, возникает конфликт доступа к шине, который должен быть разрешен протоколом шины. Поскольку кэш-память С120 не видна программному обеспечению, предпочтительно, чтобы блок С120 на шине C10 следил (этот процесс называется "bus snooping") за тем, изменяет ли исполнительный блок С110а через блок С140 информацию в памяти, которая также находится в кэш-памяти С120. Если это так, соответствующая информация в кэш-памяти С120 должна быть заменена новой информацией или помечена как недействительная.

В режиме сравнения переключатель С132 замкнут, а переключатель С131 разомкнут. Оба исполнительных блока получают совместный доступ к шине C10 через кэш-память С120. Компаратор С160 сравнивает выходные сигналы обоих исполнительных блоков и при несоответствии генерирует сигнал ошибки. Как возможный вариант, компаратор С160 может быть соединен с блоком С150 подключения к шине (на схеме такая связь не показана) и запрещать обращение к памяти для записи, если выходные сигналы обоих ядер не совпадают. В режиме повышенной производительности компаратор С160 отключен. Отключение компаратора может быть реализовано различными способами: либо компаратор С160 не выполняет сравнение, и сигналы для сравнения на компаратор С160 не поступают, либо, несмотря на выполненное сравнение, результат игнорируется.

Один из вариантов осуществления изобретения представлен на фиг.2 системой С 100с. В этом варианте известные из фиг.1 элементы работают аналогично. Однако исполнительный блок С100а в режиме повышенной производительности при замкнутом переключателе С131 получает доступ к шине C10 также через кэш-память С140а и блок (разъем) С140 подключения к шине. В режиме сравнения при замкнутом в этом случае переключателе С132 кэш-память С120 используется обоими исполнительными блоками С110а и C110b, тогда как кэш-память С140а используется исполнительным блоком С110 только в режиме повышенной производительности. Обе кэш-памяти С120 и С140а могут иметь различную емкость и соответственно могут быть оптимизированы для выполнения задач, соответствующих различным режимам работы.

На фиг.3 показан еще один вариант осуществления изобретения. При этом многопроцессорная система обозначена как C100а. В данном случае в режиме повышенной производительности переключатель С133 разомкнут, а переключатель С134 замкнут, и исполнительный блок С110b через кэш-память С120 и блок С150 подключения к шине имеет доступ к шине C10. Другой исполнительный блок С110а через блок С140 имеет прямой доступ к шине C10. В режиме же сравнения переключатель С133 замкнут, а переключатель С134 разомкнут, оба исполнительных блока через блок С140 имеют прямой доступ к шине C10, и кэш-память С120 не используется. Компаратор С160 сравнивает выходные сигналы обоих исполнительных блоков и при несоответствии генерирует сигнал ошибки. Как возможный вариант, в данном случае компаратор С160 также может быть соединен с блоком С140 подключения к шине (на схеме это соединение не показано) и препятствовать обращению к памяти для записи, если выходные сигналы исполнительных блоков не совпадают. В режиме повышенной производительности компаратор С160 отключен. Его отключение может быть реализовано различными, уже рассмотренными выше, способами.

В еще одном варианте исполнения многопроцессорной системы устройства кэш-памяти также используются лишь для устранения конфликтов доступа к шине памяти. На фиг.4 показана многопроцессорная система С200 с двумя исполнительными блоками С120а и С120b, которые могут обращаться к памяти по шине C10 различными способами. Блок С230 регулирует порядок доступа к шине C10 в зависимости от режима работы системы С200. В режиме повышенной производительности переключатели С231 и С234 замкнуты, а переключатели С232 и С233 разомкнуты. Поэтому исполнительный блок С210а получает доступ к шине C10 через кэш-память С240а с блоком С250а подключения к шине, а исполнительный блок С210b - через кэш-память С240b с блоком С250b подключения к шине. Доступ к шине C10 должен осуществляться только в том случае, если операции обращения к памяти не могут обслуживаться из соответствующих устройств кэш-памяти исполнительных блоков. Если доступ к шине C10 одновременно получают другие исполнительные блоки, возникает конфликт доступа к шине, который должен быть разрешен протоколом шины. Поскольку программное обеспечение не видит устройства кэш-памяти С240а и С240b, предпочтительно, чтобы информация, записываемая исполнительным блоком С210а, С210b в соответствующую кэш-память С250а, С250b, немедленно записывалась в память через подключение С250а и С250b на шине C10 (стратегия сквозной записи).

Далее предпочтительно, чтобы блоки С240а и С240b (соответственно через блоки С250а и С250b) на шине следили, изменяет ли в памяти исполнительный блок С210а через С250а или исполнительный блок С210b через С250b информацию, которая находится также в других устройствах кэш-памяти. Если это так, соответствующая информация в другой кэш-памяти должна быть заменена на новую или помечена как недействительная.

В режиме сравнения переключатели С232 и С233 замкнуты, а переключатели С231 и С234 разомкнуты. Оба исполнительных блока одновременно через блок С260 подключения к шине получают доступ к шине C10. Устройства кэш-памяти М240а, С240b не используются. Компаратор С160 сравнивает выходные сигналы обоих исполнительных блоков и при несоответствии генерирует сигнал ошибки. Как возможный вариант, компаратор С220 может быть соединен с блоком С260 подключения к шине (на схеме это соединение не показано) и препятствовать обращению к памяти для записи, если выходные сигналы исполнительных блоков не совпадают. В режиме повышенной производительности компаратор С160 отключен. Такое отключение может быть реализовано различными, уже рассмотренными выше, способами.

На фиг.5 показан еще один вариант исполнения многопроцессорной системы С200а, в которую в отличие от варианта исполнения, представленного на фиг.4, включена дополнительная кэш-память С270 для режима сравнения. Рассмотренные выше со ссылкой на фиг.4 компоненты работают в этом варианте аналогичным образом. В этой системе также предпочтительно применять для всех устройств кэш-памяти стратегию сквозной записи и поддерживать непротиворечивость содержимого всех устройств кэш-памяти путем слежения за шиной.

Представленные выше на фиг.4 и 5 варианты можно распространить более чем на два исполнительных блока. На каждый исполнительный блок в этом случае имеется одна кэш-память и один блок подключения к шине, используемые в режиме повышенной производительности. В режиме сравнения все исполнительные блоки через блок С260 подключения к шине (возможно с кэш-памятью С270) получают доступ к шине C10.

На фиг.6 показан следующий вариант осуществления изобретения. В данном случае многопроцессорная система С300 также состоит по меньшей мере из двух исполнительных блоков С310а и С310b, которые обращаются к основной памяти каждый через свою кэш-память С340а, С340b и свой блок С350а, С350b подключения к шине, а также шину C10. В режиме повышенной производительности переключатель С332 разомкнут, а переключатель С331 в блоке С330 переключения замкнут. Исполнительный блок С310а в этой конфигурации получает доступ к шине C10 через кэш-память С340а и блок С350а подключения к шине, а исполнительный блок С310b - через кэш-память С340b и блок С350b подключения к шине.

В режиме сравнения переключатель С332 в блоке C330 переключения замкнут, а переключатель С331 разомкнут. Теперь оба исполнительных блока получают доступ к шине C10 через кэш-память С340а и блок С350а подключения к шине. Сама кэш-память С340а состоит, в свою очередь, из двух запоминающих устройств или областей памяти С341, С342, используемых для кэширования. В режиме повышенной производительности используется только запоминающее устройство или область памяти С341, тогда как в режиме сравнения для кэширования дополнительно к запоминающему устройству или области памяти С341 используется запоминающее устройство или область памяти С342. Компаратор С320 в режиме сравнения сравнивает выходные сигналы обоих исполнительных блоков и при несоответствии генерирует сигнал ошибки. Как возможный вариант, в данном случае компаратор С320 также может быть соединен с блоком С350а подключения к шине (на схеме это соединение не показано) и препятствовать обращению к памяти для записи, если выходные сигналы исполнительных блоков не совпадают. В режиме повышенной производительности компаратор С320 отключен, как это было рассмотрено в отношении компаратора С160, показанного на фиг.1.

В другом варианте исполнения кэш-память С340а может быть организована таким образом, чтобы в режиме сравнения запоминающие устройства С341 и С342 также использовались одновременно, но чтобы при этом только содержимое запоминающего устройства С342 могло вытесняться и заменяться другим содержимым.

Все варианты исполнения, показанные на фиг.6, можно распространить более чем на два исполнительных блока. На каждый исполнительный блок в этом случае имеются кэш-память и блок подключения к шине, используемые в режиме повышенной производительности. В режиме сравнения все исполнительные блоки через кэш-память с340а и блок С350а подключения к шине получают доступ к шине C10.

Другой возможный вариант осуществления изобретения показан на фиг.7. В данном случае многопроцессорная система С400 также состоит по меньшей мере из двух исполнительных блоков С410а и С410b, которые обращаются к основной памяти каждый через свою кэш-память С440а, С440b и блок С450а, С450b подключения к шине, а также шину C10.

В режиме повышенной производительности переключатель С432 разомкнут, а переключатель С431 в блоке С430 переключения замкнут. Исполнительный блок С410а в этой конфигурации получает доступ к шине C10 через кэш-память С440а и блок С450а подключения к шине, а исполнительный блок С410b - через кэш-память С440b и блок С450b подключения к шине.

В режиме сравнения переключатель С432 в блоке С430 переключения замкнут, а переключатель С341 разомкнут. Теперь оба исполнительных блока получают доступ к шине C10 через кэш-память С440а и блок С450а подключения к шине. Сам кэш С340а, в свою очередь, состоит из двух отдельных запоминающих устройств или областей памяти С441, С442, используемых для кэширования. В режиме повышенной производительности используется только запоминающее устройство или область памяти С441, тогда как в режиме сравнения для кэширования используется запоминающее устройство или область памяти С342. Суммарная емкость обоих запоминающих устройств или областей памяти С441+С442 постоянна, но соотношение значений емкости запоминающих устройств или областей памяти С441 и С442 регулируется блоком С443. блок С443 позволяет изменять это соотношение во время работы системы.

Компаратор С420 в режиме сравнения сравнивает выходные сигналы обоих исполнительных блоков и при несоответствии генерирует сигнал ошибки. Как возможный вариант, в данном случае компаратор С420 также может быть соединен с блоком С450а подключения к шине (на схеме это соединение не показано) и препятствовать обращению к памяти для записи, если выходные сигналы исполнительных блоков не совпадают. В режиме повышенной производительности компаратор С420 отключен, как это было рассмотрено в отношении компаратора С160, показанного на фиг.1.

Кэш-память С440а при сохранении функции блока С443 может быть организована следующим образом:

1. В режиме сравнения оба запоминающих устройства С441 и С442 используются в качестве кэш-памяти.

2. В режиме сравнения оба запоминающих устройства С441 и С442 используются в качестве кэш-памяти, однако при этом содержимое запоминающего устройства С442 в режиме сравнения может быть вытеснено и заменено другим содержимым.

Все варианты схемы, показанной на фиг.7, можно распространить более чем на два исполнительных блока. На каждый исполнительный блок в этом случае имеются кэш-память и блок подключения к шине, используемые в режиме повышенной производительности. В режиме сравнения все исполнительные блоки получают доступ к шине C10 через кэш-память С440а и блок С450а подключения к шине.

На фиг.8 показан еще один возможный вариант осуществления изобретения. В микропроцессорной системе С500 имеются по меньшей мере два исполнительных блока С510а и С510b. Оба исполнительных блока связаны с блоком С530 кэш-памяти. Этот блок С530 на каждый исполнительный блок содержит один блок С550а, С550b подключения к шине, через который по шине C10 возможен доступ к основной памяти. Блок С530 кэш-память включает в себя на каждый подключенный к нему исполнительный блок по два запоминающих устройства (С531 и С533 для исполнительного блока С510а, а также С534 и С536 для исполнительного блока С510b). Суммарная емкость этих пар запоминающих устройств постоянна, но соотношение значений емкости в каждой паре можно изменять в процессе работы с помощью соответствующего блока (блока С532 для запоминающих устройств С531, С533 и блока С535 для запоминающих устройств С534, С536).

В режиме повышенной производительности обращения исполнительных блоков к памяти всегда кэшируются парой запоминающих устройств, которая назначена соответствующему исполнительному блоку. При этом используется только одно из двух запоминающих устройств кэш-памяти (в данном случае запоминающее устройство С531 для исполнительного блока С510а и запоминающее устройство С534 для исполнительного блока С510b). Если обращения к основной памяти не могут обслуживаться из кэш-памяти, то необходимые обращения к шине C10 всегда осуществляются через блок подключения к шине, сопряженный с соответствующим исполнительным блоком (в данном случае через блок С550а подключения к шине для исполнительного блока С510а и через блок С550b подключения к шине для исполнительного блока для С510b). Обращения к памяти в режиме повышенной производительности, которые происходят одновременно, могут также одновременно обслуживаться блоком С530 кэш-памяти, если только не возникает конфликт доступа к шине C10.

В режиме сравнения операции обращения исполнительных блоков к основной памяти обслуживаются устройствами кэш-памяти, не используемыми в режиме повышенной производительности (в данном случае устройствами С533 и С536 кэш-памяти). Для доступа к шине можно использовать любой блок подключения к шине. Компаратор С520 в режиме сравнения сравнивает выходные сигналы всех исполнительных блоков и при несоответствии генерирует сигнал ошибки. Как возможный вариант, в данном случае компаратор С520 также может быть соединен с блоками С550а, С550b подключения к шине (на схеме эти соединения не показаны) и препятствовать обращению к памяти для записи, если выходные сигналы исполнительных блоков не совпадают. В режиме повышенной производительности компаратор С520 отключен. Такое отключение может осуществляться, как в случае компаратора С160, показанного на фиг.1.

Еще в одном варианте исполнения блок С530 кэш-памяти может быть организован таким образом, чтобы в режиме сравнения использовались все запоминающие устройства кэш-памяти (в данном случае запоминающие устройства С531, С533, С534, С536), однако при этом содержимое только тех запоминающих устройств, которые в режиме повышенной производительности не используются, сбрасывается и заменяется новым.

Для всех вариантов осуществления изобретения, приведенных здесь в качестве примера, общим является то, что блок переключения и сравнения всегда располагается между исполнительными моделями и сопряженными с ними устройствами кэш-памяти. Если в режиме сравнения используется кэш-память, то она должна быть защищена кодом с исправлением ошибок или кодом четности, чтобы обнаруживать ошибки и этими средствами. Кроме того, для устройств кэш-памяти целесообразно использовать стратегию сквозной записи и путем отслеживания шины поддерживать непротиворечивость содержимого устройств кэш-памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ ГЕНЕРИРОВАНИЯ СИГНАЛА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, ВКЛЮЧАЮЩЕЙ В СЕБЯ НЕСКОЛЬКО КОМПОНЕНТОВ | 2005 |

|

RU2384877C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ОПЕРАНДОВ В ПРОЦЕССОРЕ | 2004 |

|

RU2360280C2 |

| ОТОБРАЖЕНИЕ ВСТРОЕННОГО АДРЕСА ЕСС | 2014 |

|

RU2644529C2 |

| ОБЩАЯ ПОСЛЕДОВАТЕЛЬНОСТЬ ЗАГРУЗКИ ДЛЯ УПРАВЛЯЮЩЕЙ СЕРВИСНОЙ ПРОГРАММЫ, СПОСОБНОЙ К ИНИЦИАЛИЗАЦИИ ВО МНОЖЕСТВЕННЫХ АРХИТЕКТУРАХ | 2015 |

|

RU2665238C2 |

| КОМАНДА ВЕКТОРНОГО ТИПА ДЛЯ ПОИСКА НЕРАВНОЗНАЧНОГО ЭЛЕМЕНТА | 2013 |

|

RU2598814C2 |

| КОНФИГУРАЦИЯ АРХИТЕКТУРНОГО РЕЖИМА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 2015 |

|

RU2664413C2 |

| ОПРЕДЕЛЕНИЕ ДЛИНЫ ГРУППЫ СИМВОЛЬНЫХ ДАННЫХ, СОДЕРЖАЩЕЙ СИМВОЛ ОКОНЧАНИЯ | 2013 |

|

RU2621000C2 |

| АКТИВАЦИЯ/ДЕАКТИВАЦИЯ АДАПТЕРОВ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2010 |

|

RU2562372C2 |

| УПРАВЛЕНИЕ В РЕЖИМЕ НИЗКИХ ПРИВИЛЕГИЙ РАБОТОЙ СРЕДСТВА СБОРА СВЕДЕНИЙ О ХОДЕ ВЫЧИСЛЕНИЙ | 2013 |

|

RU2585969C2 |

| КОМАНДА ВЕКТОРНОГО ТИПА ДЛЯ ПОИСКА РАВНОЗНАЧНОГО ЭЛЕМЕНТА | 2013 |

|

RU2585975C2 |

Изобретение относится к способу и устройству для сравнения выходных данных по меньшей мере двух исполнительных блоков микропроцессора. Технический результат заключается в обеспечении возможности переключения в переключаемой многопроцессорной системе между режимом повышенной производительности и режимом сравнения. Такой результат достигается тем, что в устройстве для управления доступом к памяти в вычислительной системе по меньшей мере с двумя исполнительными блоками, предусмотрены буферная память, в частности кэш-память, а также средства переключения и средства сравнения, причем переключение осуществляется между режимом повышенной производительности и режимом сравнения, причем в режиме сравнения доступ к буферной памяти закрывают для всех исполнительных блоков, а в режиме повышенной производительности доступ к буферной памяти открывают по меньшей мере для одного исполнительного блока. 2 н. и 11 з.п. ф-лы, 8 ил.

1. Способ управления доступом к памяти в вычислительной системе по меньшей мере с двумя исполнительными блоками, в которой предусмотрены буферная память, в частности кэш-память, а также средства переключения и средства сравнения, причем переключение осуществляется между режимом повышенной производительности и режимом сравнения, отличающийся тем, что в режиме сравнения доступ к буферной памяти закрывают для всех исполнительных блоков, а в режиме повышенной производительности доступ к буферной памяти открывают по меньшей мере для одного исполнительного блока.

2. Способ по п.1, отличающийся тем, что в режиме сравнения соединение исполнительного блока, связанного с буферной памятью, разрывают с помощью средств переключения.

3. Способ по п.1, отличающийся тем, что в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки запрещают доступ к памяти, не являющейся буферной.

4. Способ по п.1, отличающийся тем, что в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки данные в памяти, не являющейся буферной, делают недействительными или блокируют.

5. Способ по п.1, отличающийся тем, что в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки вычислительную систему перезапускают или повторно включают.

6. Способ по п.1, отличающийся тем, что в режиме сравнения с помощью средств сравнения проверяют данные на соответствие и при несоответствии данных устанавливают наличие ошибки, причем в случае ошибки по меньшей мере один исполнительный блок перезапускают или повторно включают.

7. Устройство для управления доступом к памяти в вычислительной системе по меньшей мере с двумя исполнительными блоками, в которой предусмотрены буферная память, в частности кэш-память, а также средства переключения и средства сравнения, причем переключение осуществляется между режимом повышенной производительности и режимом сравнения, отличающееся тем, что оно содержит средства, выполненные таким образом, чтобы в режиме сравнения закрывать доступ к буферной памяти для всех исполнительных блоков, а в режиме повышенной производительности открывать доступ к буферной памяти, по меньшей мере, для одного исполнительного блока.

8. Устройство по п.7, отличающееся тем, что указанные средства выполнены как средства переключения, запрещающие или разрешающие исполнительному блоку доступ к буферной памяти.

9. Устройство по п.7, отличающееся тем, что средства сравнения выполнены таким образом, чтобы в режиме сравнения проверять данные на соответствие и при несоответствии данных устанавливать наличие ошибки, в случае которой они запрещают доступ к памяти, не являющейся буферной.

10. Устройство по п.7, отличающееся тем, что средства сравнения выполнены таким образом, чтобы в режиме сравнения проверять данные на соответствие и при несоответствии данных устанавливать наличие ошибки, в случае которой они делают недействительными или блокируют данные в памяти, не являющейся буферной.

11. Устройство по п.7, отличающееся тем, что средства сравнения расположены между по меньшей мере одним исполнительным блоком и буферной памятью.

12. Устройство по п.7, отличающееся тем, что буферная память расположена между по меньшей мере одним исполнительным блоком и средствами сравнения.

13. Устройство по п.11 или 12, отличающееся тем, что средства переключения и средства сравнения выполнены в виде одного блока переключения и сравнения.

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| Устройство для диагностики многопроцессорной системы | 1984 |

|

SU1357957A1 |

| US 6640313, 28.10.2003 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| US 5822767 A, 13.10.1998 | |||

| US 6385755 B1, 07.05.2002 | |||

| Устройство для связывания стержнеобразных предметов | 1979 |

|

SU863464A1 |

Авторы

Даты

2010-12-10—Публикация

2006-07-24—Подача