Область техники, к которой относится изобретение

Настоящее изобретение относится к способу и устройству для генерирования сигнала в вычислительной системе, включающей в себя несколько компонентов, а также к компоненту и вычислительной системе, содержащим такое устройство.

Уровень техники

Нерегулярные или случайные сбои, обусловленные альфа-частицами или космическим излучением, представляют собой все большую проблему для интегральных полупроводниковых схем. В связи с уменьшением структурной ширины, понижением напряжения и повышением тактовой частоты возрастает вероятность того, что пик напряжения, вызванный воздействием альфа-частицы или космического излучения, приведет к искажению логического значения в интегральной схеме. Следствием может стать ошибочный результат расчета. Поэтому в системах, важных с точки зрения безопасности, в частности в автомобиле, такие ошибки необходимо с уверенностью обнаруживать.

В системах, важных в отношении безопасности, например в системе регулирования антиблокировочного устройства автомобиля, в которых сбои электроники должны надежно отслеживаться, обычно используются устройства управления с избыточностью по обнаружению ошибок. Так, например, в известных антиблокировочных системах в каждом случае дублируется целый микроконтроллер, причем все антиблокировочные функции вычисляются с избыточностью и проверяются на соответствие. Если имеет место несоответствие результатов, антиблокировочная система отключается.

Важными компонентами микроконтроллера являются модули памяти (например, ЗУПВ, ПЗУ, кэш-память), ядра и интерфейсы входа/выхода (например, аналогово-цифровые преобразователи, интерфейс локальной сети контроллеров CAN). Поскольку элементы памяти можно эффективно контролировать посредством контрольных кодов (кода четности или кода с исправлением ошибок), а периферийные устройства часто контролируются с ориентацией на конкретный случай применения как часть пути прохождения сигнала датчика или привода, имеется возможность дальнейшего повышения избыточности путем простого удвоения ядер микроконтроллера.

Такие микроконтроллеры с двумя интегрированными ядрами известны так же как двухъядерные архитектуры. Оба ядра отрабатывают с резервированием и тактовой синхронизацией (в режиме жесткого параллелизма) один и тот же сегмент программы. Результаты, полученные обоими ядрами, сравниваются, и при сравнении на соответствие обнаруживается ошибка. Эту конфигурацию двухъядерной системы можно назвать режимом сравнения.

Двухъядерные архитектуры в других случаях применения служат также для повышения производительности, т.е. эффективности. Оба ядра выполняют различные программы, сегменты программ и команды, чем достигается повышение производительности, поэтому такая конфигурация двухъядерной системы может именоваться также режимом повышенной производительности. Эта система называется также симметричной многопроцессорной системой.

Расширением этих систем является программное переключение между двумя указанными режимами посредством обращения к специальному адресу и с помощью специализированных аппаратных средств. В режиме сравнения выходные сигналы ядер сравниваются друг с другом. В режиме повышенной производительности оба ядра работают как симметричная многопроцессорная (СМП) система и выполняют различные программы, сегменты программ и команды.

Такие системы целесообразно использовать, если известен режим, в котором находится система. Поэтому задача изобретения состоит в том, чтобы предложить способы и средства для генерирования сигнала режима.

Раскрытие изобретения

Объектом изобретения является способ генерирования сигнала в вычислительной системе, включающей в себя несколько компонентов, причем в качестве двух компонентов системы предусмотрено по меньшей мере два исполнительных блока, а в качестве еще одного компонента - средство переключения, и в вычислительной системе выполняют переключение между по меньшей мере двумя режимами работы, первый из которых соответствует режиму сравнения, а второй - режиму повышенной производительности, отличающийся тем, что в компоненте вычислительной системы генерируют сигнал режима, указывающий текущий режим работы системы, и/или изменения сигнала режима, причем по меньшей мере изменения сигнала режима и/или сам сигнал режима предоставляют в распоряжение за пределами компонента.

В предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима используют для контроля, для чего имеющуюся информацию, представляющую режим работы, сравнивают с информацией, представленной режимным сигналом и/или изменениями сигнала режима либо выведенной из них.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима анализируют в другом компоненте вычислительной системы.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима анализируют в компоненте, периферийном по отношению к исполнительным блокам.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима анализируют в устройстве защиты памяти.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима анализируют в контроллере прерываний.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа вычислительная система содержит операционную систему, а сигнал режима и/или изменения сигнала режима используют для самоконтроля операционной системы, для чего имеющуюся в операционной системе информацию, представляющую режим работы, сравнивают с информацией, представленной режимным сигналом и/или изменениями сигнала режима либо выведенной из них.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима защищают по меньшей мере одним дополнительным элементом информации.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима защищают путем по меньшей мере дублирования сигнала режима и/или изменений сигнала режима.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима защищают как двухрельсовый или двухканальный сигнал (сигнал, поступающий по двум линиям).

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима генерируют в средстве переключения.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа в качестве средства переключения предусмотрен комбинированный блок переключения и сравнения, причем сигнал режима и/или изменения сигнала режима генерируют в этом блоке переключения и сравнения.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима генерируют по меньшей мере в одном исполнительном блоке.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима и/или изменения сигнала режима генерируют в компоненте, включающем в себя комбинированный блок переключения и сравнения, а также блок распознавания потребности в переключении.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа предусмотрено более двух режимов работы, между которыми можно выполнять переключение.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа для указания соответствующего режима работы предусмотрена конфигурируемая маркировка режима работы.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа для указания соответствующего режима работы предусмотрена конфигурируемая переменная-указатель.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа на основе сигнала режима и/или изменений сигнала режима выполняют обнаружение ошибок, причем в рамках обнаружения ошибок генерируют по меньшей мере один сигнал ошибки.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа анализ сигнала режима используют для подтверждения безопасности.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа сигнал режима является многозначным с возможностью представления им более чем двух режимов.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа в режиме сравнения используют голосование.

В другом предпочтительном варианте осуществления предлагаемого в изобретении способа в режиме сравнения используют помехозащищенный алгоритм.

Объектом изобретения является также устройство для генерирования сигнала в вычислительной системе, включающей в себя несколько компонентов, причем в качестве двух компонентов системы предусмотрено по меньшей мере два исполнительных блока, а в качестве еще одного компонента - средство переключения, и в вычислительной системе выполняется переключение между по меньшей мере двумя режимами работы, первый из которых соответствует режиму сравнения, а второй - режиму повышенной производительности, отличающееся тем, что оно содержится в компоненте вычислительной системы и выполнено с возможностью генерирования сигнала режима, указывающего

текущий режим работы системы, и/или изменений сигнала режима, причем по меньшей мере изменения сигнала режима и/или сам сигнал режима предоставляется в распоряжение за пределами указанного компонента.

В предпочтительном варианте выполнения предлагаемого в изобретении устройства сигнал режима генерируется таким образом, чтобы представлять более двух режимов работы.

В другом предпочтительном варианте выполнения предлагаемого в изобретении устройства значение сигнала режима или синтаксис его интерфейса являются конфигурируемыми (настраиваемыми).

Объектами изобретения являются также компонент и вычислительная система, содержащие описанное выше устройство.

Другие преимущества изобретения и примеры его осуществления раскрыты в формуле и описании изобретения.

Краткое описание чертежей

Осуществление изобретения рассматривается ниже и поясняется чертежами, на которых показано:

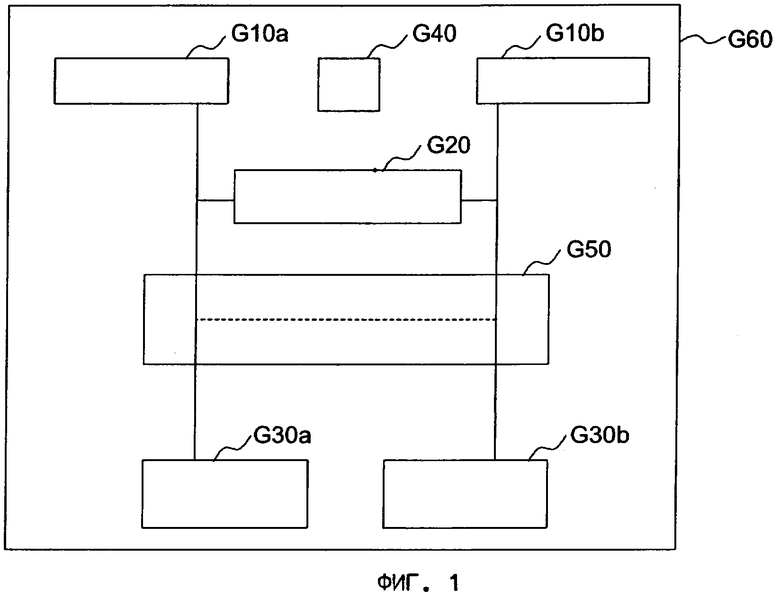

на фиг.1 - многопроцессорная система G60 с двумя исполнительными блоками G10a, G10b, одним блоком G50 переключения и одним блоком G40 распознавания потребности в переключении,

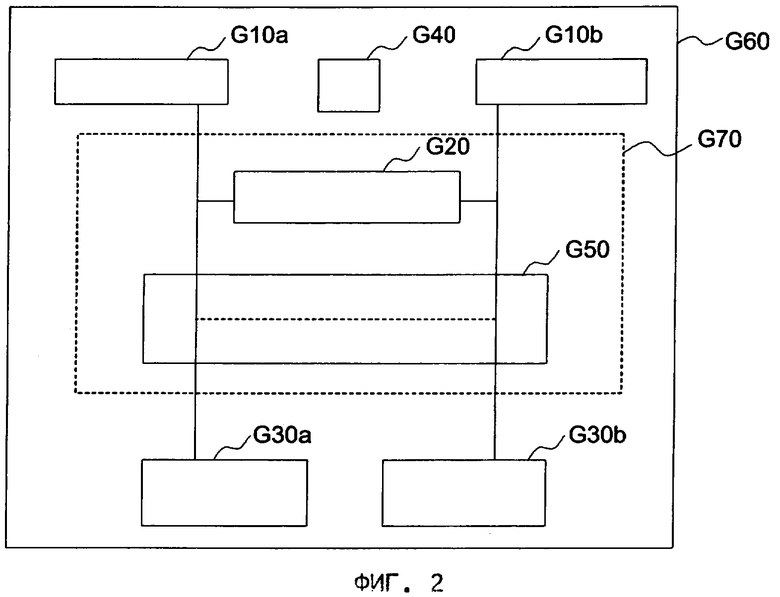

на фиг.2 - многопроцессорная система G60 с двумя исполнительными блоками G10a, G10b, одним комбинированным блоком G70 сравнения и переключения, состоящим из блока G20 сравнения и блока G50 переключения, а также с одним блоком G40 распознавания потребности в переключении,

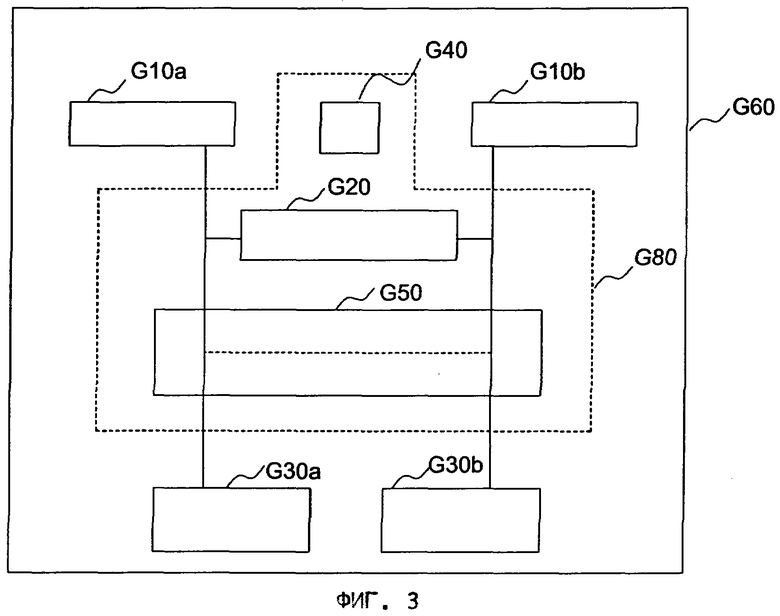

на фиг.3 - многопроцессорная система G60 с двумя исполнительными блоками G10a, G10b, одним комбинированным блоком G80 распознавания потребности в переключении, сравнении и переключении, состоящим из блока G20 сравнения, блока G50 переключения и блока G40 распознавания потребности в переключении,

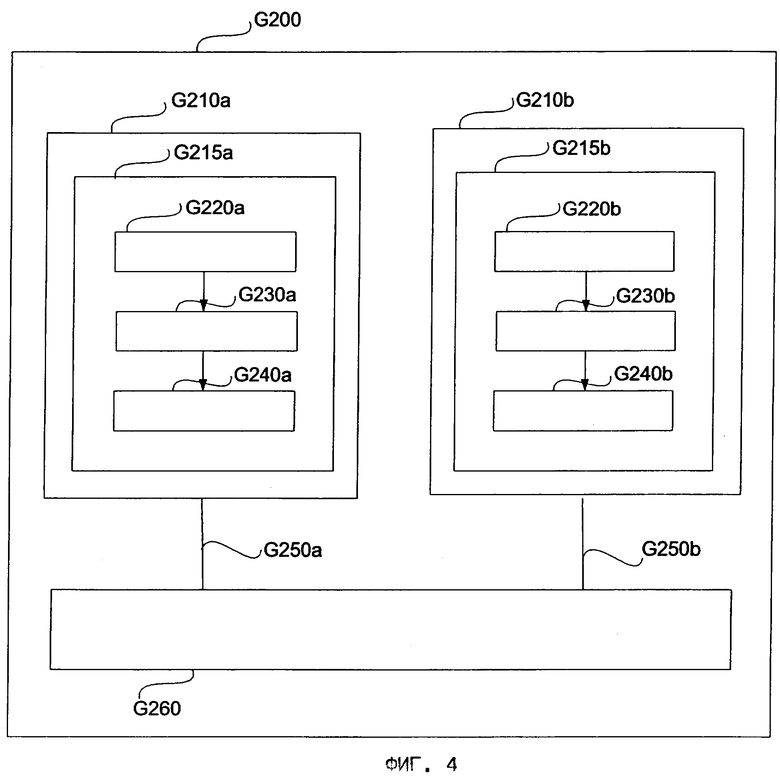

на фиг.4 - многопроцессорная система G200 с двумя исполнительными блоками G210a, G210b и одним блоком G260 переключения и сравнения,

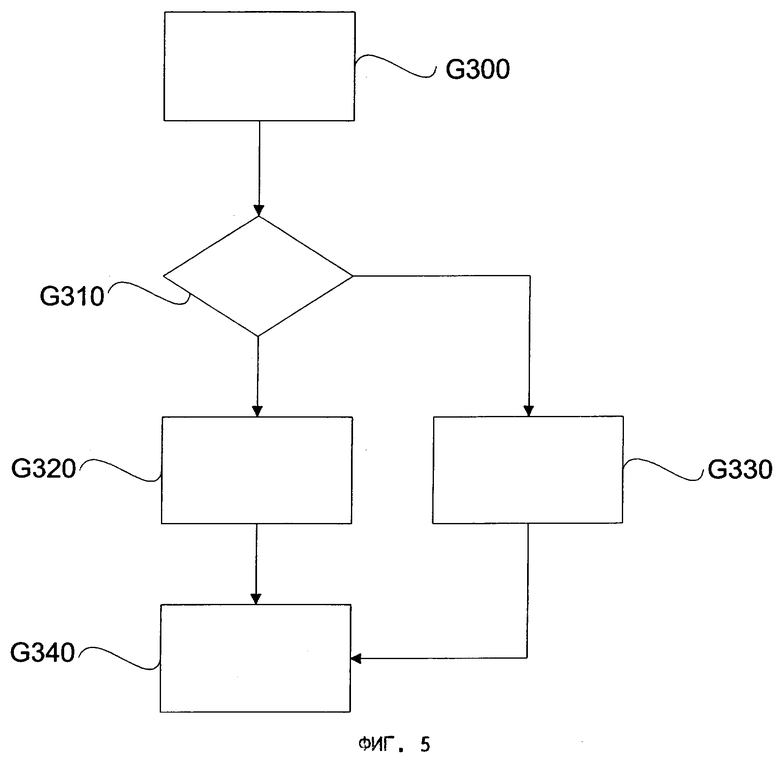

на фиг.5 - представленный в виде блок-схемы способ, который в пределах специальной конвейерной ступени G230a, G230b производит обмен специальной неопределенной двоичной комбинации на NOP (холостую или фиктивную команду) или другую нейтральную двоичную комбинацию,

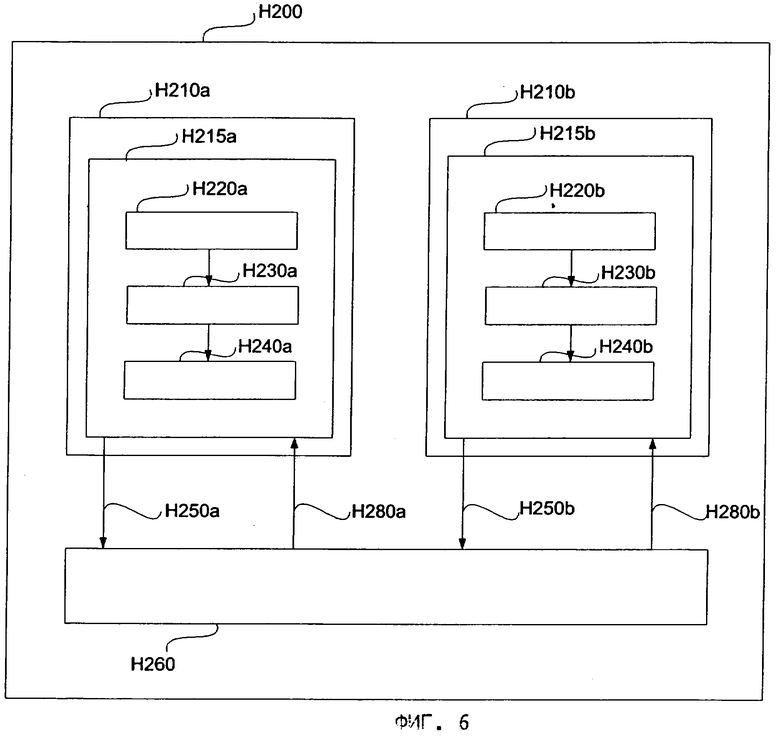

на фиг.6 - многопроцессорная система Н200 с двумя исполнительными блоками Н210а, Н210b и одним блоком Н260 переключения и сравнения,

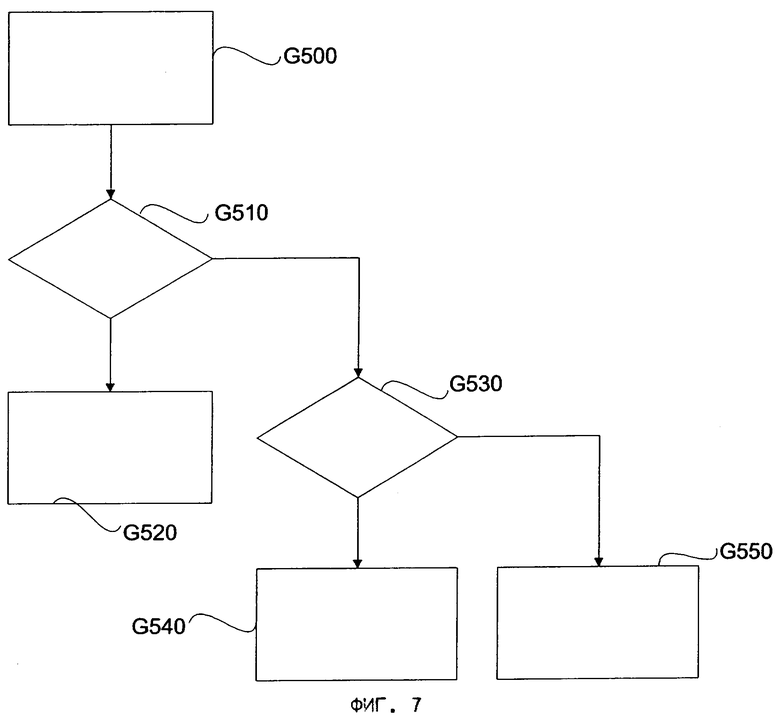

на фиг.7 - представленный в виде блок-схемы способ, показывающий как с помощью идентификации устройств можно разделить процесс выполнения блок-схемы программы при переходе из режима сравнения в режим повышенной производительности в многопроцессорной системе с двумя исполнительными блоками,

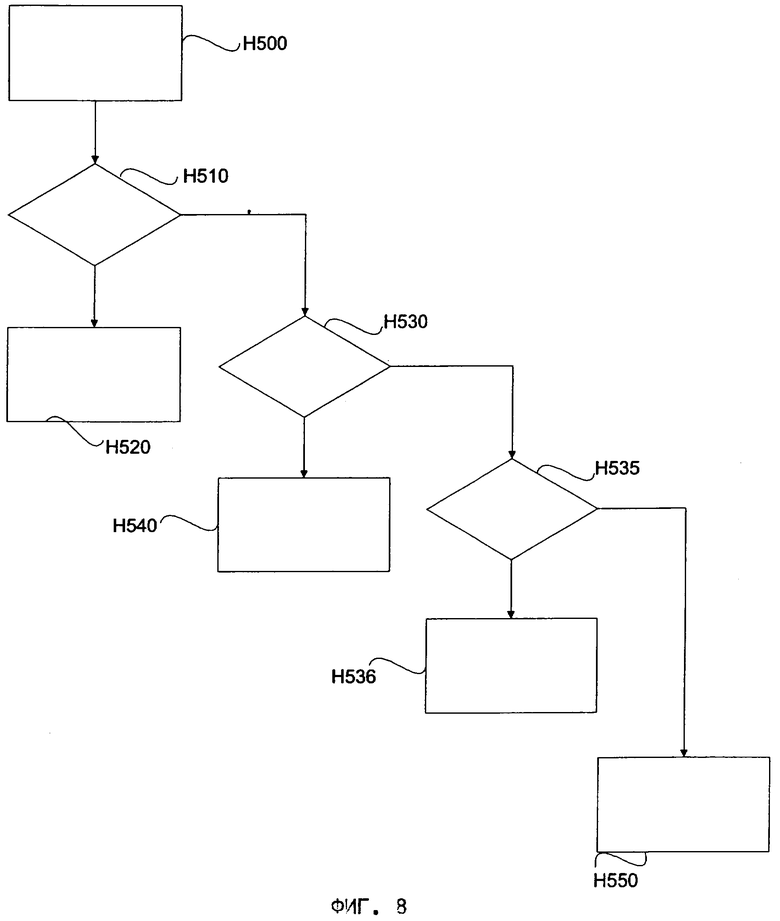

на фиг.8 - возможный способ, показывающий как с помощью идентификации устройств можно разделить процесс выполнения блок-схемы программы при переходе из режима сравнения в режим повышенной производительности в многопроцессорной системе с тремя исполнительными блоками,

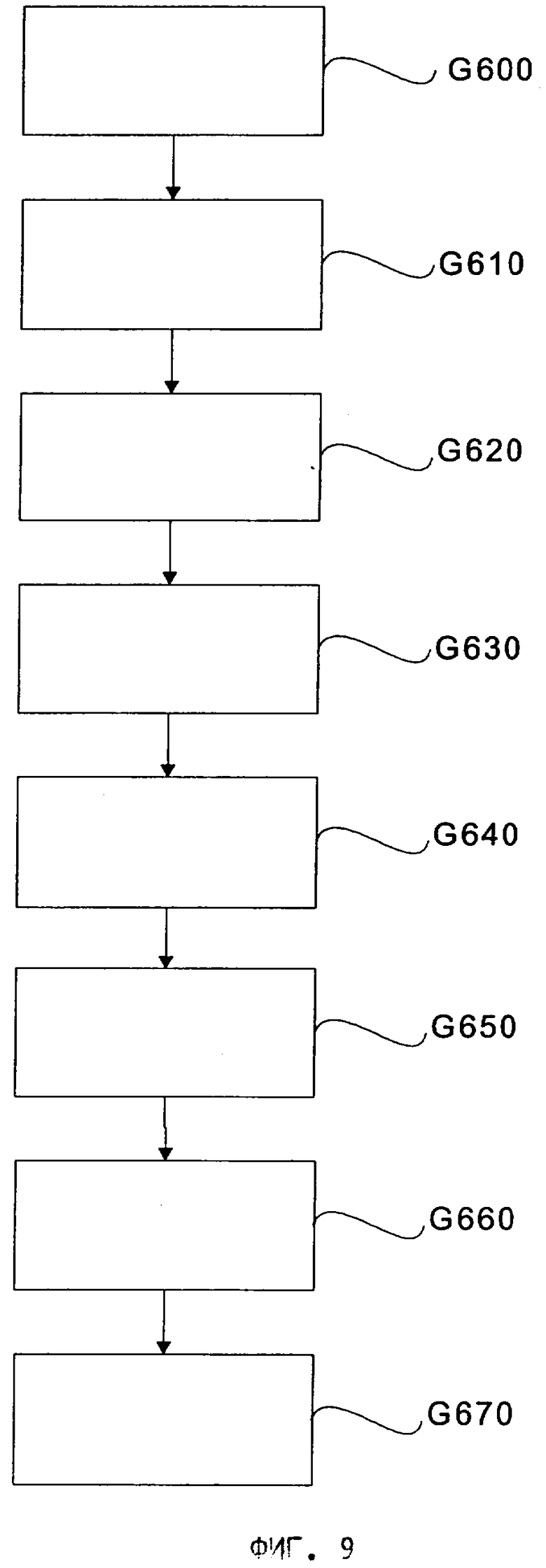

на фиг.9 - представленный в виде блок-схемы способ, синхронизирующий исполнительные блоки при переключении из режима повышенной производительности в режим сравнения,

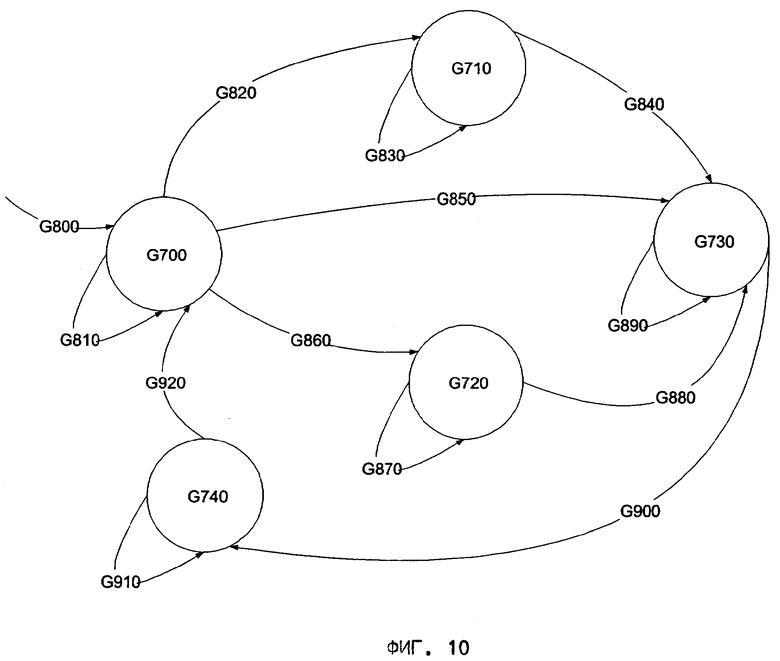

на фиг.10 - конечный автомат, отображающий переключение между режимом повышенной производительности и режимом сравнения,

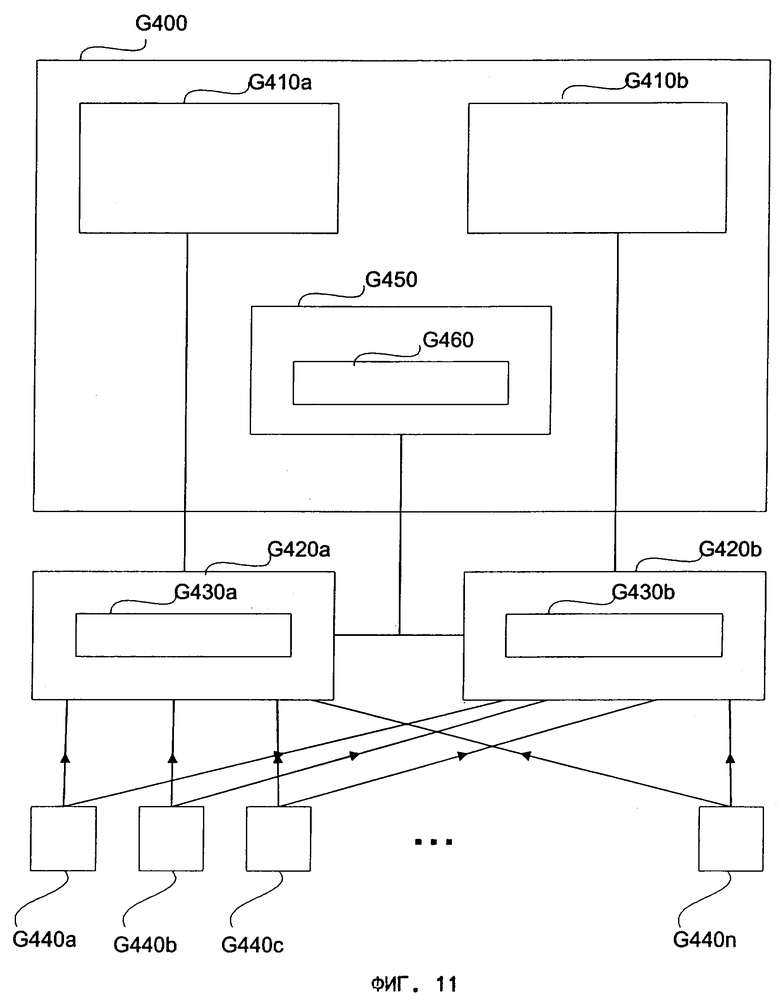

на фиг.11 - многопроцессорная система G400 с двумя исполнительными блоками и двумя контроллерами G420a, G420b прерываний, включающая содержащиеся в них регистры G430a, G430b маскировки прерываний и различные источники G440a-G440n прерываний,

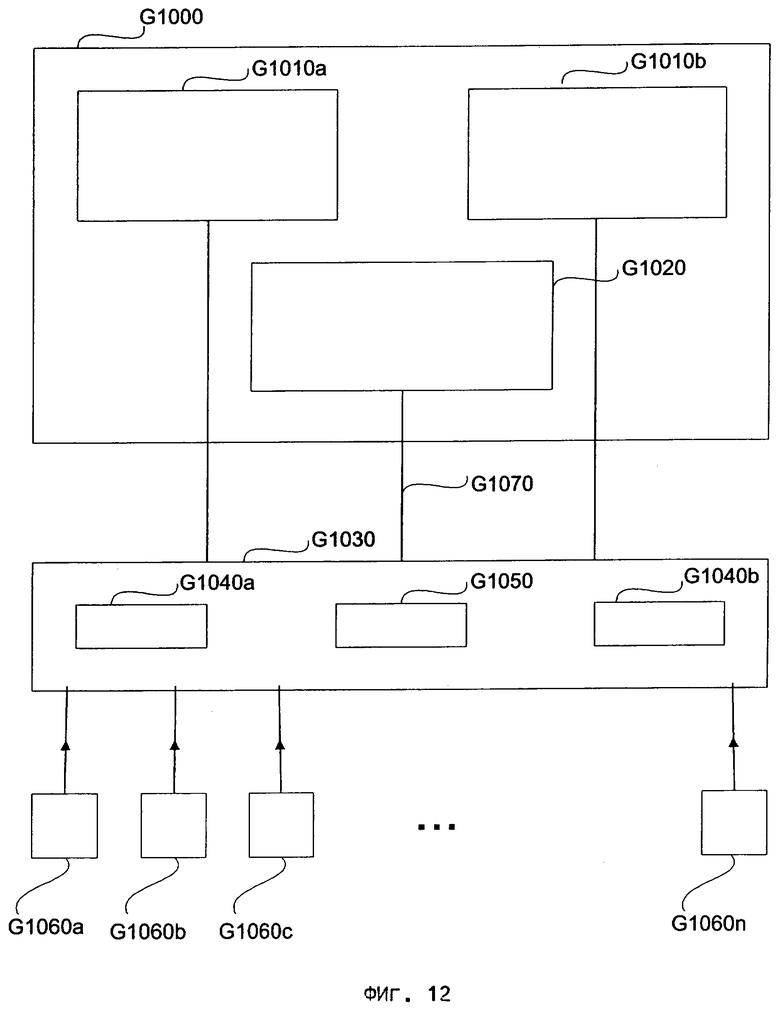

на фиг.12 - многопроцессорная система с двумя исполнительными блоками - одним блоком переключения и сравнения и одним контроллером прерываний с тремя наборами регистров,

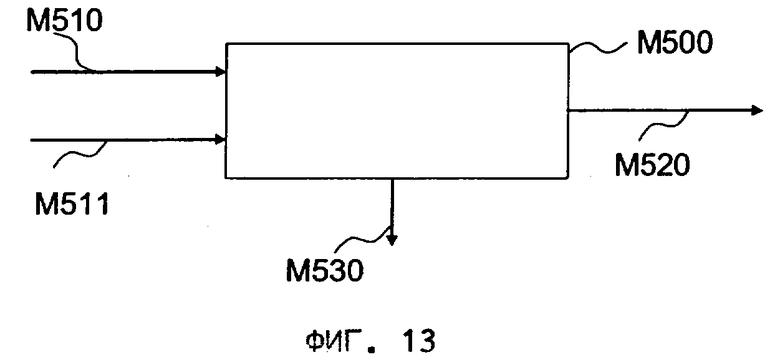

на фиг.13 - простейшая форма компаратора,

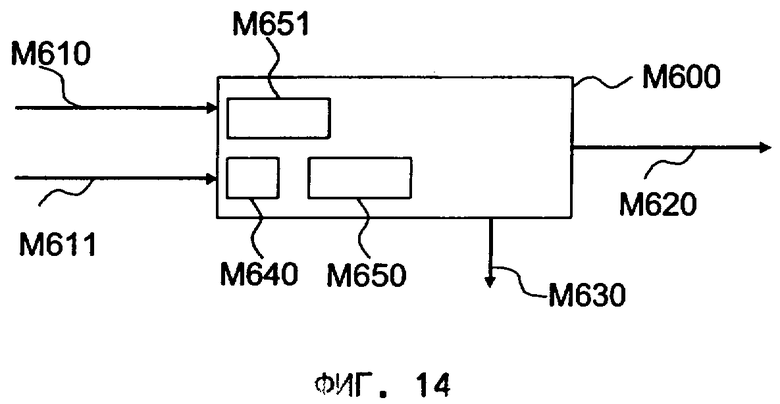

на фиг.14 - компаратор с устройством компенсации сдвига фаз,

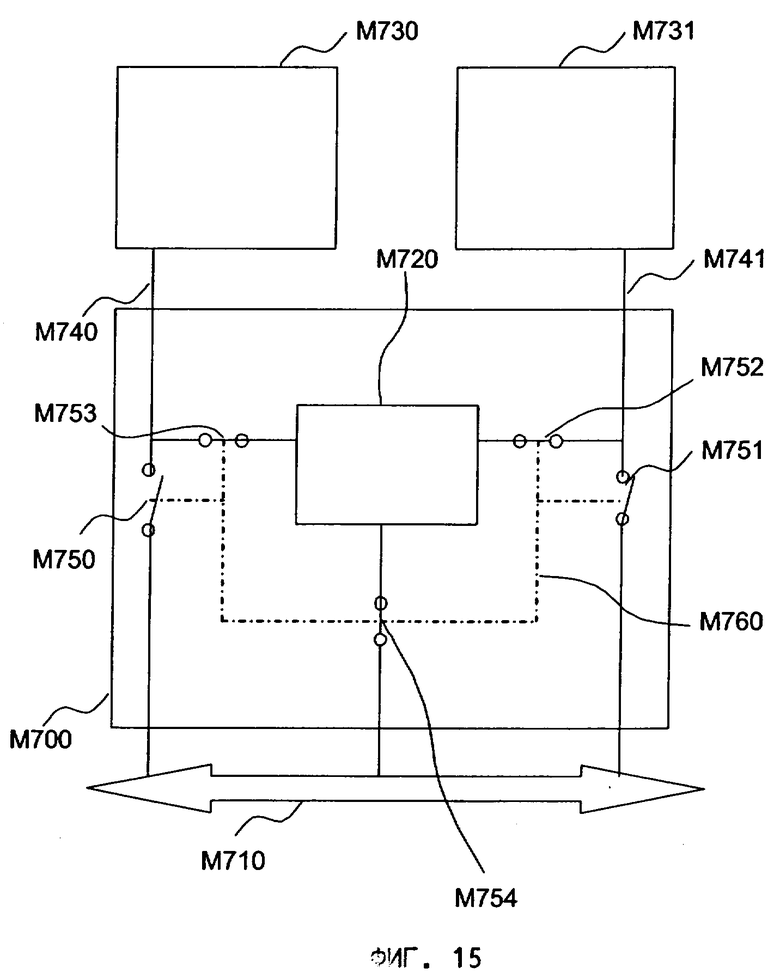

на фиг.15 - принципиальная схема предпочтительного компонента М700 (блока переключения и сравнения) в режиме сравнения,

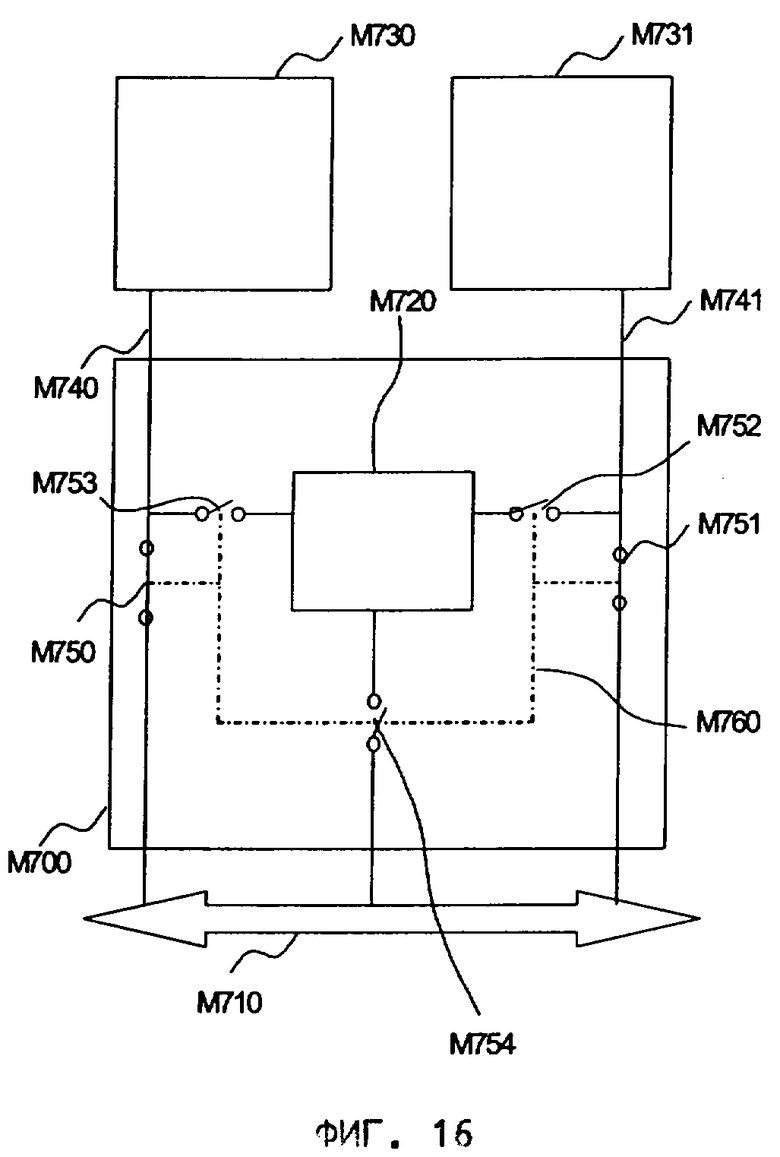

на фиг.16 - принципиальная схема предпочтительного компонента М700 (блока переключения и сравнения) в режиме повышенной производительности,

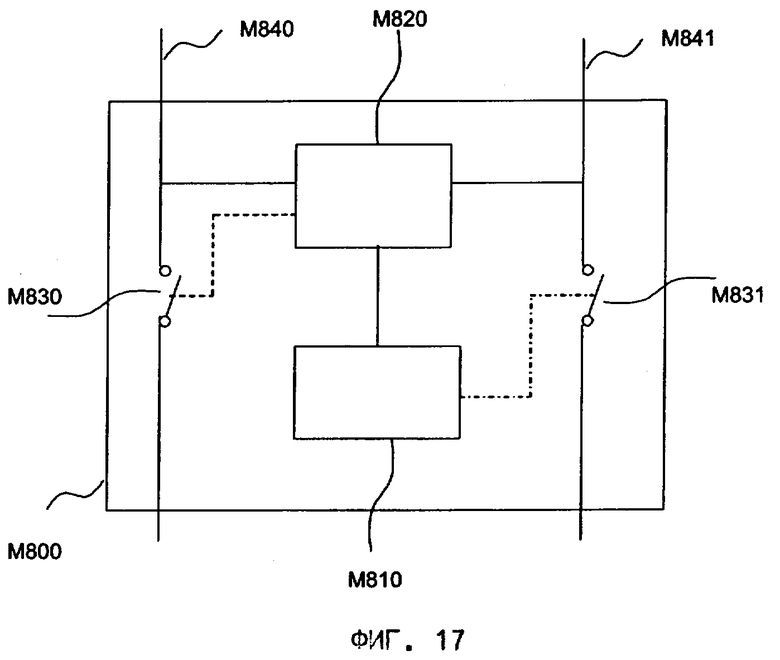

на фиг.17 - вариант исполнения блока переключения и сравнения,

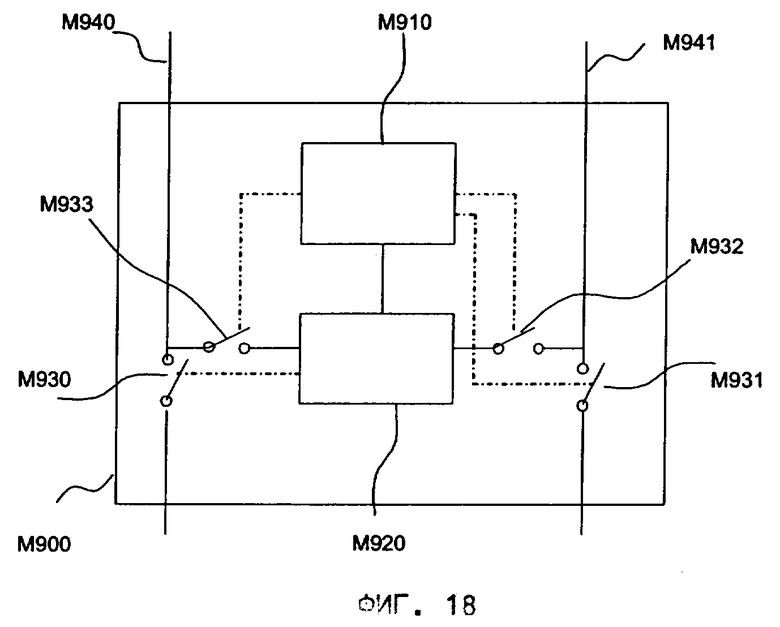

на фиг.18 - еще один вариант исполнения блока переключения и сравнения,

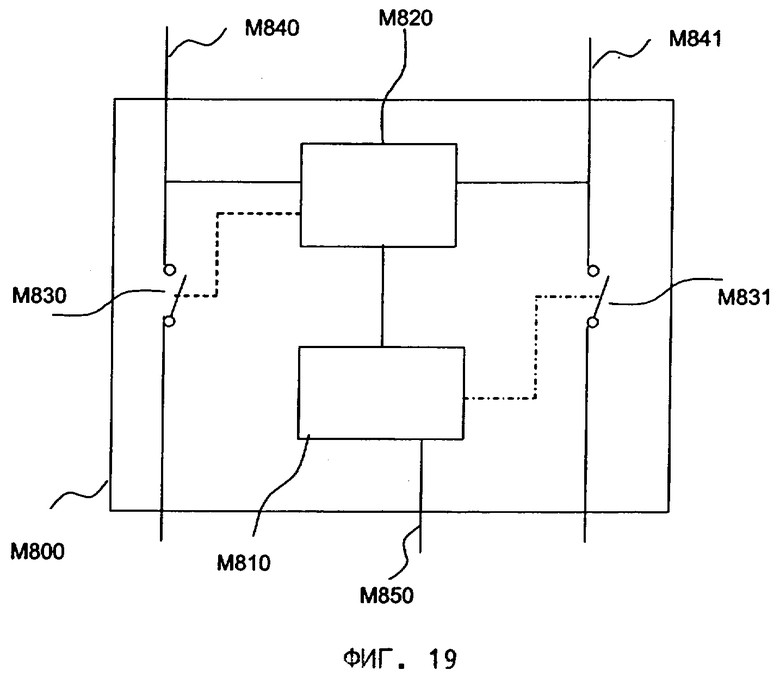

на фиг.19 - блок переключения и сравнения, генерирующий сигнал режима,

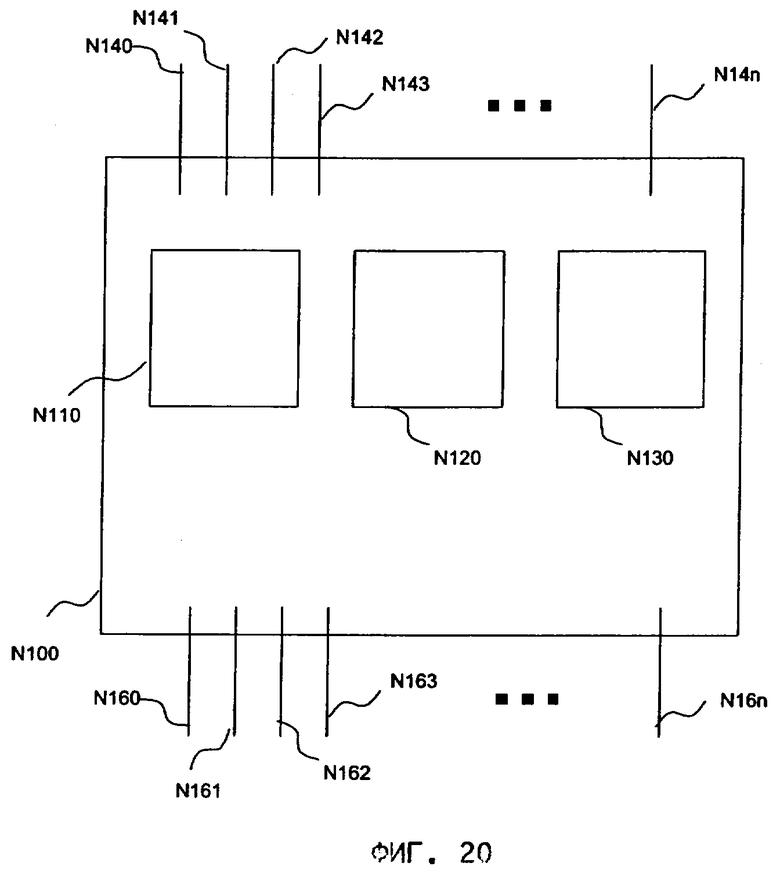

на фиг.20 - общее представление блока переключения и сравнения,

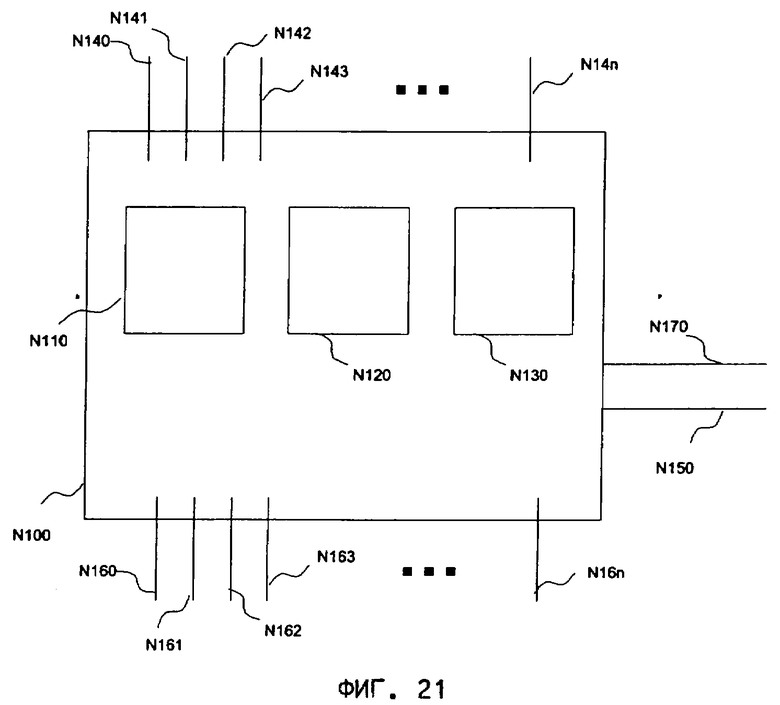

на фиг.21 - общее представление блока переключения и сравнения, генерирующего общий сигнал режима и общий сигнал ошибки,

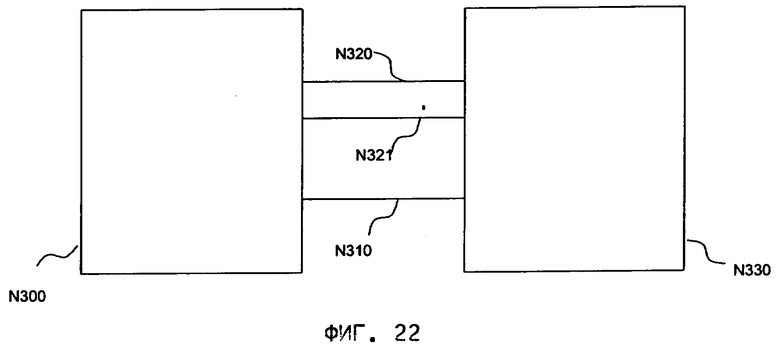

на фиг.22 - связь по типу вопрос - ответ с внешним устройством,

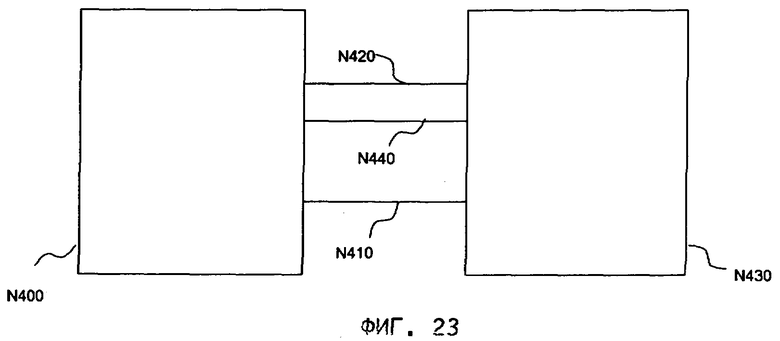

на фиг.23 - связь с интеллектуальным приводом.

Осуществление изобретения

Исполнительным блоком могут в дальнейшем именоваться как процессор, ядро, центральный процессор, так и устройство с плавающей точкой, процессор цифровых сигналов, сопроцессор или арифметическое логическое устройство.

На фиг.1 показана многопроцессорная система G60 с двумя исполнительными блоками (модулями) G10a, G10b, блоком G20 сравнения, блоком G50 переключения и блоком G40 распознавания потребности в переключении.

Изобретение относится к многопроцессорной системе, показанной на фиг.1, 2, 3, по меньшей мере с двумя исполнительными блоками G10a, G10b, блоком G20 сравнения, блоком G50 переключения и блоком G40 распознавания потребности в переключении. Блок G50 переключения имеет по меньшей мере два выхода по меньшей мере к двум системным интерфейсам G30a, G30b. Через эти интерфейсы можно управлять регистрами, запоминающими устройствами или периферийными устройствами, в частности дискретными выходами, цифро-аналоговыми преобразователями, контроллерами связи. Многопроцессорная система может работать по меньшей мере в двух режимах: режиме сравнения (VM) и режиме повышенной производительности (РМ).

В режиме повышенной производительности в различных исполнительных блоках параллельно выполняются различные команды, сегменты программ или программы. В этом режиме работы блок G20 сравнения выключен. Блок G50 переключения в этом режиме конфигурирован таким образом, что каждый исполнительный блок G10a, G10b связан с системным интерфейсом G30a, G30b. При этом исполнительный блок G10a связан с системным интерфейсом G30a, а исполнительный блок G10b - с системным интерфейсом G30b.

В режиме сравнения в обоих исполнительных блоках G10a, G10b обрабатываются одинаковые или однородные команды, сегменты программ или программы. Удобно обрабатывать эти команды с тактовой синхронизацией, но возможна также обработка с асинхронностью или сдвигом такта. Выходные сигналы исполнительных блоков G10a, G10b сравниваются в блоке G20 сравнения. При различии или несовпадении сигналов делается вывод о наличии ошибки (сбоя) и можно принять соответствующие меры. Эти меры могут вызвать подачу сигнала ошибки, начать обработку ошибки, коммутировать переключатели или быть комбинацией этих и других допустимых мер. Блок G50 переключения в одном из вариантов конфигурирован таким образом, что на системные интерфейсы G30a, G30b поступает только один сигнал. В другой конфигурации задача блока переключения состоит лишь в том, чтобы сравненные и по результатам сравнения одинаковые сигналы поступали на системные интерфейсы G30a, G30b.

Блок G40 распознавания потребности в переключении независимо от активного в данный момент режима выдает сигнал потребности в переключении на другой режим.

На фиг.2 показана многопроцессорная система G60 с двумя исполнительными блоками G10a, G10b, комбинированным блоком G70 сравнения и переключения, состоящим из блока G20 сравнения и блока G50 переключения, а также с блоком G40 распознавания потребности в переключении.

В одном из вариантов исполнения описываемой системы блок G50 переключения и блок G20 сравнения могут быть объединены в общий блок G70 переключения и сравнения, как показано на фиг.2. Общий компонент G70 в этом случае выполняет задачи отдельных компонентов G50, G20. На фиг.15, 16, 17, 18 и 19 представлены варианты исполнения блока G70.

В другом варианте исполнения, представленном на фиг.3, блок G40 распознавания потребности в переключении, блок G20 сравнения и блок G50 переключения могут быть объединены в общий блок G80. Еще в одном варианте исполнения, не показанном на фигуре, блок G40 распознавания потребности в переключении и блок G20 сравнения могут быть объединены в общий компонент. Допустимо также объединение в одном компоненте блока G40 распознавания потребности в переключении с блоком G50 переключения.

В дальнейшем при отсутствии иных указаний будем исходить из того, что речь идет о блоке G40 распознавания потребности в переключении и комбинированном блоке G70 переключения и сравнения.

Общий случай компонента переключения и сравнения, в том числе и при использовании для обслуживания более чем двух исполнительных блоков представлен на фиг.20. От n подлежащих учету исполнительных блоков поступает n сигналов N140,…, N14n на компонент N100 переключения и сравнения. На основе этих входных сигналов он может генерировать до n выходных сигналов N160,…, N16n. В простейшем случае, в "чистом режиме повышенной производительности" все сигналы N14i направляются на соответствующие выходные сигналы N160,…, N16n. В противоположном предельном случае, в "чистом режиме сравнения" все сигналы N140,…, N14n направляются точно только на один из выходных сигналов N16i.

На примере этой фигуры можно пояснить, как возникают различные допустимые режимы работы. Для этого фигура содержит логический компонент комбинационной логики N110. Этот компонент необязательно должен присутствовать как самостоятельный компонент. Решающее значение имеет то, что рассмотренные функции реализуются в системе. Комбинационная логика N110 прежде всего определяет, сколько вообще существует выходных сигналов. Далее она определяет, какие из входных сигналов вносят вклад в генерирование какого из выходных сигналов. При этом один входной сигнал может создавать точно один выходной сигнал. Иными словами, в математической форме комбинационная логика определяет одну функцию, которая каждому элементу множества (N140,…, N14n) ставит в соответствие элемент множества (N160,…, N16n).

Затем логика N120 обработки определяет для каждого из выходов N16i, в какой форме входы вносят вклад в генерирование этого выходного сигнала. Также и этот компонент необязательно должен присутствовать как самостоятельный компонент. Решающее значение и в этом случае имеет то, что описываемые функции реализованы в системе. Чтобы, например, описать различные возможности вариаций, примем без ограничения общности, что выход N160 генерируется сигналами N141,…, N14m. Если m=1, то это просто соответствует коммутации сигнала, если m=2, то сравниваются сигналы N141, N142, как, например, в блоке сравнения на фиг.13, 14. Это сравнение может осуществляться синхронно или асинхронно, оно может быть побитовым или рассчитанным только на значимые биты или же на область допусков.

Если m≥3, существуют несколько возможностей.

Первая возможность состоит в том, чтобы сравнивать все сигналы и при наличии по меньшей мере двух различных значений обнаруживать ошибку с подачей в случае необходимости сигнала ошибки.

Вторая возможность состоит в выборе некоторого к из m (k>m/2). Эту возможность можно реализовать путем использования компараторов. В качестве варианта можно генерировать сигнал ошибки, если один из сигналов распознается как отличающийся от заданного. Отличающийся сигнал ошибки можно генерировать, если все три сигнала различны.

Третья возможность состоит в введении этих значений в некоторый алгоритм. Сюда можно отнести, например, формирование среднего значения, медианы распределения или использование помехозащищенного (отказоустойчивого) алгоритма. Такой алгоритм основывается на вычеркивании экстремальных значений из числа входных значений и выполнении своего рода усреднения по остальным значениям. Это усреднение можно проводить для всей совокупности остальных значений или предпочтительнее для подмножества, легко образуемого из максимальных значений. В этом случае не всегда необходимо действительно сравнивать значения. При формировании среднего значения достаточно выполнять только сложение и деление, образование помехозащищенного среднего значения, помехозащищенного алгоритма или медианы распределения требует частичной сортировки. В случае необходимости при достаточно больших экстремальных значениях может и здесь как вариант выдаваться сигнал ошибки.

Перечисленные различные возможности обработки нескольких сигналов в один сигнал для краткости называются операциями сравнения.

Таким образом, задача логики обработки состоит в определении точного характера операции сравнения для каждого выходного сигнала и, следовательно, для соответствующих входных сигналов. Комбинация информации комбинационной логики N110 (т.е. вышеуказанной функции) и логики обработки (т.е. определение операции сравнения для каждого выходного сигнала или каждого значения функции) - это информация о режиме и она определяет режим. Разумеется, эта информация в общем случае многозначна, т.е. не может быть представлена одним логическим битом. Не все теоретически возможные режимы целесообразны в заданной реализации, предпочтительнее ограничить число разрешенных режимов. Следует подчеркнуть, что в случае только двух исполнительных блоков, когда существует только один режим сравнения, всю информацию можно сжать до одного бита.

Переключение из режима повышенной производительности в режим сравнения в обычном случае характеризуется тем, что исполнительные блоки, которые в режиме повышенной производительности отображаются на различные выходы, в режиме сравнения отображаются на один и тот же выход. Преимущественно это реализуется за счет того, что существует подсистема исполнительных блоков, в которой в режиме повышенной производительности все входные сигналы N14i, подлежащие учету в подсистеме, переключаются непосредственно на соответствующие выходные сигналы N16i, тогда как в режиме сравнения все они отображаются на один выход. Альтернативно такое переключение может реализовываться в виде попарного изменения. Это объясняется тем, что в обычном случае нельзя говорить об одном режиме повышенной производительности и одном режиме сравнения, хотя в заданном проявлении изобретения число разрешенных режимов можно ограничивать настолько, что это будет иметь место. Однако всегда можно говорить о переключении из режима повышенной производительности в режим сравнения (и наоборот).

Под управлением программного обеспечения между этими режимами можно переключаться динамически. При этом переключение осуществляется путем выполнения специальных команд переключения, специальных последовательностей команд, определенно помеченных команд или путем обращения к определенным адресам по меньшей мере посредством одного из исполнительных блоков многопроцессорной системы.

Схемная логика N130 переключения при ошибках накапливает сигналы ошибки, генерируемые, например, компараторами, и может, при необходимости, пассивно коммутировать выходы N16i, например, размыкая их выключателем.

Однако следующие примеры посвящены случаю с двумя исполнительными блоками, в котором проще представить большинство концепций.

Переключение между режимами можно кодировать различными методами. При одном из возможных методов используются специальные команды переключения, непосредственно передаваемые в блок G40 распознавания потребности в переключении. Другой возможный способ кодирования переключения определяется обращением к специальному разделу памяти, который опять же обнаруживает блок G40 распознавания потребности в переключении. Еще один метод анализирует в блоке G40 распознавания потребности в переключении внешний сигнал, сообщающий о переключении. Ниже приводится описание способа, который использует в наборе команд процессора неиспользованные двоичные комбинации. Особое преимущество этого способа состоит в том, что он позволяет и дальше использовать существующие среды поддержки разработки (ассемблер, компилятор, редактор связей, отладчик).

На фиг.4 показана многопроцессорная система G200 с двумя исполнительными блоками G210a, G210b и блоком G260 переключения и сравнения. Для переключения из режима сравнения в режим повышенной производительности (и наоборот) используются не определенные в ассемблере двоичные комбинации по меньшей мере двух исполнительных блоков G210а, G210b. Под неопределенными или неопределимыми в этом смысле следует понимать все двоичные комбинации, которые в описании набора команд специфицированы как неопределенные или запрещенные. Таковыми являются, например, запрещенный операнд, запрещенная команда, запрещенная операция. Общим признаком этих двоичных комбинаций является то, что обычный исполнительный блок при выполнении такой двоичной комбинации генерирует сигнал ошибки или обнаруживает неопределенное поведение. Следовательно, эти двоичные комбинации не нужны для представления семантики обычной программы.

Таким образом, для разработки программного обеспечения можно использовать прежнюю среду поддержки в том виде, как она существует для однопроцессорных систем. Это реализуется, например, путем определения макрокоманды "SWITCH MODE TO PM" (переключение в режим повышенной производительности) и макрокоманды "SWITCH MODE TO VM" (переключение в режим сравнения), которые в соответствующем месте вставляют в код соответствующие не определенные в указанном выше смысле двоичные комбинации.

Использование такой комбинации определяется при этом как общая макрокоманда "SWITCH" (переключение). Она обеспечивает переход из активного в данный момент режима в другой режим. Если в системе имеется больше двух различных режимов, то для применения этого способа должно существовать больше таких комбинаций, тогда можно преимущественно использовать одну из них на каждый режим для кодирования переключения.

Согласно изобретению потребность в переключении кодируется неопределенной в наборе команд двоичной комбинацией. Их нельзя обычным образом обрабатывать в исполнительном блоке G210a, G210b. Поэтому предлагается дополнительная конвейерная ступень (ступень ЗАМЕНЫ) G23a, G230b, которая распознает соответствующие двоичные комбинации и заменяет их для дальнейшей обработки нейтральными двоичными комбинациями. Целесообразно использовать для этого команду "NOP" (холостую команду). Команда "NOP" отличается тем, что она не изменяет внутреннее состояние исполнительного блока, за исключением указателя команды. При этом ступень ЗАМЕНЫ G230a, G230b вставляется после обычной первой ступени, ступени ВЫБОРКИ G220a, G220b, а перед остальными конвейерными ступенями G240a, G240b вставляются не определенные в ассемблере двоичные комбинации, которые здесь объединены в одном блоке.

Согласно изобретению представленная здесь реализация блока G40 распознавания потребности в переключении как специальная конвейерная ступень G230a, G230b конвейерного блока G215a, G215b будет генерировать дополнительный сигнал G250a, G250b в случае обнаружения соответствующей двоичной комбинации для переключения, который сообщит отдельному блоку переключения и блоку сравнения G260, что необходимо выполнить замену режима обработки.

Ступени ЗАМЕНЫ G230a, G230b следует располагать преимущественно между ступенями ВЫБОРКИ G220a, G220b и остальными конвейерными ступенями G240a, G240b в конвейерных блоках G215a, G215b исполнительных блоков G210a, G210b. При этом ступени ЗАМЕНЫ G230a, G230b распознают соответствующие двоичные комбинации и передают команды NOP на остальные ступени G240a, G240b. Одновременно активизируется соответствующий сигнал G250a или G250b. Во всех других случаях ступени ЗАМЕНЫ G230a, G230b ведут себя нейтрально, т.е. все другие команды без изменений передаются на другие ступени.

На фиг.5 в виде блок-схемы процесса представлен способ, который в пределах специальной конвейерной ступени G230a, G230b производит обмен специальной неопределенной двоичной комбинации на холостую команду или другую нейтральную двоичную комбинацию. На ступени ВЫБОРКИ G300 из памяти выводится команда, т.е. двоичная комбинация. После этого в блоке G310 определяется, соответствует ли выведенная двоичная комбинация специальной неопределенной двоичной комбинации, которая кодирует переключение. Если это не так, в следующем шаге G320 двоичная комбинация без изменения передается на прочие конвейерные ступени для дальнейшей обработки. Если специальная двоичная комбинация, кодирующая переключение, распознается на шаге G310, то на шаге G330 она заменяется двоичной комбинацией холостой команды и уже эта комбинация передается на последующие конвейерные ступени G340 для дальнейшей обработки. В предпочтительном варианте исполнения блоки G310, G320, G330 представляют функциональность предлагаемой изобретением ступени ЗАМЕНЫ G230a, G230b, причем эти блоки могут содержать также дополнительную функциональность.

На фиг.6 показана многопроцессорная система Н200 с двумя исполнительными блоками Н210а, Н210b и одним блоком Н260 переключения и сравнения. Компоненты Н220а, H220b, H240a, H240b имеют то же значение, что и блоки G220a, G220b, G240a, G240b. В альтернативном исполнении блока G40 распознавания потребности в переключении, описываемого здесь специальными конвейерными ступенями Н230а, Н230b, этот блок наряду с сигналами Н250а, Н250b, сигнализирующими переключение, имеет и другие сигналы. Для того чтобы синхронизировать исполнительные блоки Н210а, Н210b при переходе из режима повышенной производительности в режим сравнения, конвейерные блоки Н215а, Н215b исполнительных блоков Н21а, Н210b в каждом случае имеют сигнальный вход Н280а, Н280b, который может приостановить обработку. Этот сигнал устанавливается блоком Н260 переключения и сравнения для того конвейерного блока Н215а или Н215b, который первым распознал команду на переключение и тем самым активизировал сигнал Н250а или GH50b. Только после того как оба конвейерных блока Н215а, Н250b исполнительных блоков Н210а, Н210b распознают команду на переключение и посредством программы или других аппаратных средств синхронизируют свое внутреннее состояние, этот сигнал Н280а, Н280b будет отменен. При переходе из режима сравнения в режим повышенной производительности сигналы Н280а, Н280b не требуются, так как синхронизация не нужна.

Предпосылкой осуществления описываемого здесь предложения является блок (называемый блоком идентификации) или способ, посредством которого каждый исполнительный блок может определить свой индивидуальный или идентификационный номер. В системе с двумя исполнительными блоками один из них может, например, определить для себя номер 0, а другой - номер 1. В системе более чем с двумя исполнительными блоками номера присваиваются или определяются соответственно. Этот идентификационный номер не различает между режимом сравнения и режимом повышенной производительности, но однозначно обозначает исполнительный блок. Идентификационный номер может содержаться в том или ином исполнительном блоке, будучи реализован как бит или двоичная комбинация в регистре состояния процессора, или как собственный регистр, или же как отдельный бит или внешнее по отношению к исполнительным блокам устройство, которое по запросу выдает соответствующий идентификационный номер.

После того как исполнительные блоки в соответствии с потребностью в переключении выполнят переключение в режим повышенной производительности, блок сравнения становится неактивным, но исполнительные блоки все еще будут выполнять те же самые команды. Дело в том, что переключение не влияет на указатели команд, обозначающие места в программе, в которых исполнительный блок будет работать в следующем шаге или работает в данный момент. Для того чтобы исполнительные блоки после этого могли выполнять различные программные модули, отработка программы исполнительными блоками должны быть раздельной. По этой причине указатели команд в программном блоке, как правило, имеют различное значение, так как обрабатываются независимые согласно изобретению команды, сегменты программ или программы. Разделение программных потоков осуществляется согласно приведенному здесь предложению путем определения номера того или иного исполнительного блока. В зависимости от того, какой идентификационный номер имеет исполнительный блок, он отрабатывает определенный программный модуль. Поскольку каждый исполнительный блок имеет индивидуальный номер или идентификацию, программный поток может быть надежно разделен между участвующими исполнительными блоками.

На фиг.7 в виде блок-схемы процесса представлен способ, показывающий как с помощью идентификации устройств можно разделить процесс выполнения блок-схемы программы при переходе из режима сравнения в режим повышенной производительности в многопроцессорной системе с двумя исполнительными блоками. После выполнения переключения из режима сравнения в режим повышенной производительности на шаге G500 происходит опрос идентификационного номера или номера исполнительного блока на шаге G510 обоими исполнительными блоками. Согласно изобретению исполнительный блок 0 получает номер блока 0, исполнительный блок 1 - номер блока 1. На шаге G510 осуществляется сравнение определенного номера исполнительного блока с номером 0. Если эти номера одинаковы, исполнительный блок, для которого это сравнение оказалось успешным, продолжает работу на шаге G520 с кодом 0 для исполнительного блока. Исполнительный блок, для которого это сравнение не было успешным, продолжает на шаге G530 сравнение с номером 1. Если это сравнение окажется успешным, работа продолжается на шаге G540. Если это сравнение не было успешным, значит, для соответствующего исполнительного блока определен номер, не равный 0 и 1. Это является случаем ошибки и работа продолжается на шаге G550.

На фиг.8 представлен возможный вариант осуществления способа для трех исполнительных блоков. После выполнения переключения из режима сравнения в режим повышенной производительности на шаге Н500 осуществляется опрос исполнительными блоками идентификационных номеров или номеров исполнительных блоков на шаге Н510. Согласно изобретению исполнительный блок 0 получает номер блока 0, исполнительный блок 1 - номер блока 1 и исполнительный блок 2 - номер блока 2. На шаге Н510 осуществляется сравнение определенного номера исполнительного блока с номером 0. Если номера равны, исполнительный блок, для которого это сравнение было успешным, на шаге Н520 продолжает работать с кодом исполнительного блока, равным 0. Исполнительные блоки, для которых это сравнение не было успешным, продолжают на шаге G530 сравнение с номером 1. В исполнительном блоке, для которого сравнение оказалось успешным, работа продолжается на шаге Н540 с кодом для исполнительного блока 1. Исполнительные блоки, для которых это сравнение не было успешным, продолжают на шаге G535 сравнение с номером 2. В исполнительном блоке, для которого сравнение оказалось успешным, работа продолжается на шаге Н536 с кодом для исполнительного блока 2. Если это сравнение не было успешным, значит, для соответствующего исполнительного блока определился номер блока, не равный 0, 1 и 2. Это является случаем ошибки и работа продолжается на шаге Н550. Альтернативно к сравнению с номером можно использовать определенный номер исполнительного блока также непосредственно в качестве индекса в таблице переходов.

В соответствии с этим описанием способ можно применять также и к многопроцессорным системам с числом исполнительных блоков более трех.

Если выполняется переключение из режима повышенной производительности в режим сравнения, необходимо учитывать несколько моментов. При переключении из режима повышенной производительности в режим сравнения необходимо обеспечить, чтобы внутренние состояния исполнительных блоков после переключения были однородными, в противном случае в режиме сравнения была бы обнаружена возможная ошибка, если различные исходные состояния ведут к различным выводам. Однородность состояний может быть обеспечена техническими средствами, программным обеспечением, программно-аппаратным обеспечением или комбинацией всех трех способов. Это возможно при условии, что все исполнительные блоки после переключения в режим сравнения выполняют одинаковые или однородные команды, программы или сегменты программ. Ниже приведено описание способа синхронизации, который можно применять, если режим сравнения отличается тем, что в нем обрабатываются идентичные команды и происходит сравнение с точностью до бита.

На фиг.9 в виде блок-схемы процесса представлен способ, синхронизирующий исполнительные блоки при переключении из режима повышенной производительности в режим сравнения. На шаге G600 преимущественно блокируются все прерывания. Это важно не только потому, что контроллеры прерываний необходимо соответствующим образом перепрограммировать для режима сравнения. Программное обеспечение должно также приводить в соответствие внутреннее состояние исполнительных блоков. Однако если во время подготовки к переключению в режиме сравнения сработает прерывание, то приведение в соответствие станет весьма затруднительным.

Шаг G610: Если оба исполнительных блока имеют отдельную кэш-память, необходимо перед переключением согласовывать также содержимое памяти во избежание того, чтобы в режиме сравнения для одного адреса в одном исполнительном блоке имело место совпадение, а в другом исполнительном блоке - несовпадение. Если устройства кэш-памяти не обеспечивают этого самостоятельно, следует отменить действие, например, путем маркировки всех строк кэша. Необходимо дождаться, чтобы содержимое одного устройства кэш-памяти (или всех) стало полностью недействительным. Для этого по мере надобности можно использовать цикл ожидания в коде программы. Возможно использование и других средств, важно, чтобы после этого шага кэш-блоки находились в одинаковом состоянии.

На шаге G620 происходит очистка буфера записи исполнительных блоков, чтобы после переключения исполнительные блоки не выполняли каких-либо действий, начавшихся еще в режиме повышенной производительности.

На шаге G630 синхронизируется состояние конвейерных ступеней исполнительных блоков. Для этого выполняется, например, соответствующее число холостых команд перед последовательностью/командой переключения. Число холостых команд зависит от числа конвейерных ступеней и, следовательно, от конкретной архитектуры. Какая команда пригодна в качестве холостой, также зависит от архитектуры. Если исполнительные блоки имеют кэш-память команд, то при этом необходимо обеспечить, чтобы цепочки команд ориентировались по границам строки кэша (выравнивание). Поскольку кэш-память команд перед выполнением этих холостых команд маркирована как недействительная, необходимо прежде загрузить холостые команды в кэш-память. Если цепочка команд начинается на границе строки кэша, то передача данных из памяти (например, ЗУПВ/ПЗУ/флэш-памяти) в кэш заканчивается до подачи команды на переключение. Это также необходимо учитывать при определении числа холостых команд.

На шаге G640 фактически выполняется шаг команды на переключение в режим сравнения.

На шаге G650 согласуется содержимое отдельных массивов регистров каждого исполнительного блока. Для этого в регистры до и после переключения необходимо загрузить идентичные содержания. При этом важно, чтобы после переключение содержимое регистра в исполнительных блоках стало идентичным, прежде чем оно будет передано на внешние устройства и, следовательно, подвергнуто сравнению в компараторе.

На шаге G660 происходит перепрограммирование контроллеров прерываний, поэтому один внешний сигнал прерывания вызывает одинаковое прерывание во всех соединенных исполнительных блоках.

На шаге G670 прерывания снова отменяются.

Если из выполнения программы неясно, когда должно происходить переключение в режим сравнения, то участвующие исполнительные блоки должны получать информацию о предполагаемом переключении. Для этого целесообразно, например, посредством программы инициировать прерывание в контроллерах прерываний, относящихся к соответствующим исполнительным блокам. Обработка прерывания в этом случае приведет к выполнению указанной выше последовательности команд на объединение.

На фиг.10 показан конечный автомат, отображающий переключение из режима повышенной производительности в режим сравнения (и наоборот). При пуске системы включение питания или также перезапуск (программного или аппаратного обеспечения) через переход G800 приводят систему в состояние G700. Существует общее правило, что после неопределенного события, способного вызвать перезапуск, система всегда начинает работать в состоянии G700. Примерами событий, которые могут вести к перезапуску, являются внешние сигналы, проблемы с электропитанием или внутренние сбои, делающие нецелесообразным продолжение работы. Таким образом, состояние G700 блока G70 переключения и сравнения, работающего в режиме повышенной производительности, - это состояние системы по умолчанию. Во всех случаях, когда можно ожидать неопределенного состояния, предполагается состояние G700 по умолчанию. При этом состояние G700 по умолчанию обеспечивается аппаратными средствами. Например, состояние системы или состояние блока переключения и сравнения G60 можно кодировать в регистре, бите регистра, посредством двоичной комбинации в регистре или триггерной схемы.

В этом случае аппаратные средства всегда обеспечивают после перезагрузки или включения питания приведение системы в состояние G700. Для этого служит, например, сигнал перезагрузки или сигнал включения питания, подаваемый на вход перезапуска или на вход установки триггерной схемы или регистра.

В состоянии G700 система работает в режиме повышенной производительности. Следовательно, исполнительные блоки G10a, G10b обрабатывают различные команды, программы и элементы программ. Потребность в переключении можно распознать, например, по тому, что один исполнительный блок G10a, G10b выполняет специальную команду переключения. Другими возможностями являются распознавание путем обращения к специальному адресу памяти с помощью внутреннего или внешнего сигнала. Пока нет потребности в переключении, многопроцессорная система G60 и, следовательно, блок G70 переключения и сравнения находятся в состоянии G700. В дальнейшем будем называть потребность в переключении условием переключения, которое обозначено так же, как условие переключения в этой специальной системе.

Пребывание в состоянии G700 представлено переходом G810. Если исполнительный блок G10a распознает потребность в переключении, то через переход G820 блок G70 переключения и сравнения переводится в состояние G710. Таким образом, состояние G710 описывает ситуацию, в которой исполнительный блок G10a распознал потребность в переключении и ожидает, пока исполнительный блок G10b также распознает потребность в переключении. Пока этого не произойдет, блок G70 переключения и сравнения остается в состоянии G710, что представлено переходом G830.

Переход G840 происходит, когда в состоянии G710 исполнительный блок G10b также распознает потребность в переключении. Блок G70 переключения и сравнения при этом принимает состояние G730. Это состояние характеризует ситуацию, когда оба исполнительных блока G10a, G10b распознали потребность в переключении. В состоянии G730 протекают процессы синхронизации, при которых два исполнительных блока G10a, G10b синхронизируются по отношению друг к другу, чтобы в дальнейшем работать в режиме сравнения. В ходе этого процесса блок G70 переключения и сравнения остается в состоянии G730, что представлено переходом G890.

Если в состоянии G700 исполнительный блок G10b первым распознает потребность в переключении, то переход G680 выполнит переключение в состояние G720. Следовательно, состояние G720 характеризует ситуацию, в которой исполнительный блок G10b распознал потребность в переключении и ожидает, пока исполнительный блок G10a также распознает потребность в переключении. Пока это не произошло, блок G70 переключения и сравнения остается в состоянии G720, что представлено переходом G870. Переход G880 происходит, когда в состоянии G720 исполнительный блок G10a также распознает потребность в переключении. Следовательно, блок переключения и сравнения принимает состояние G730.

Если в состоянии G700 оба исполнительных блока G10a, G10b одновременно распознают потребность в переключении, система немедленно переходит в состояние G730. Этот случай представляет переход G850.

Если блок G70 переключения и сравнения находится в состоянии G730, значит, оба исполнительных блока G10a, G10b распознали потребность в переключении. В этом состоянии происходит синхронизация внутренних состояний исполнительных блоков G10a, G10b, чтобы по окончании процесса синхронизации они работали в режиме сравнения. По окончании синхронизации происходит переход G900. Этот переход указывает на окончание синхронизации. В состоянии G740 исполнительные блоки G10a, G10b работают в режиме сравнения. Об окончании процесса синхронизации исполнительные блоки G10a, G10b могут сигнализировать самостоятельно. Это означает, что переход G900 происходит, когда оба исполнительных блока G10a, G10b подали сигнал, что они готовы работать в режиме сравнения. Окончание синхронизации может сигнализироваться также по истечении заранее установленного времени. Это означает, что блок G70 переключения и сравнения жестко закодирован на время пребывания в состоянии G730. Это время устанавливается таким образом, чтобы оба исполнительных блока G10a, G10b успели надежно закончить синхронизацию. По истечении этого времени инициируется переход G900. В другом варианте блок G70 переключения и сравнения может контролировать состояние исполнительных блоков G10a, G10b и самостоятельно определять, когда оба исполнительных блока G10a, G10b закончили синхронизацию. После такого определения инициируется переход G900.

Пока не распознана потребность в переключении, многопроцессорная система G60 остается в режиме сравнения, представленном переходом G910. Если в состоянии G740 распознается потребность в переключении, переход G920 переводит блок G70 переключения и сравнения в состояние G700. Как уже указывалось, в состоянии G700 система работает в режиме повышенной производительности. Разделение программных потоков при переходе из состояния G740 в состояние G700 может осуществляться способом, описание которого приведено выше.

На фиг.11 показана многопроцессорная система G400 с двумя исполнительными блоками G410a, G410b и двумя контроллерами G420a, G420b прерываний, включая содержащиеся в них регистры G430a, G430b маскировки прерываний и различные источники G440a - G440n прерываний. Представлен также блок переключения и сравнение G450 со специальным регистром G460 маскировки прерываний.

Предпочтительно каждый исполнительный блок G410a, G410b имеет свой собственный контроллер G420a, G420b прерываний, чтобы в режиме повышенной производительности можно было одновременно обрабатывать два прерывания. Это особенно удобно в системах, в которых обработка прерываний представляет узкое место в работе системы. Источники G440a - G440n прерываний предпочтительно подключать одновременно к обоим контроллерам G420a, G420b прерываний. Этот способ подключения без дополнительных мер обеспечивает одинаковое прерывание для обоих исполнительных блоков G410а, G410b. В режиме повышенной производительности контроллеры G420a, G420b прерываний программируются таким образом, чтобы соответствующие источники G440a - G440n прерываний соответственно случаю применения распределялись между различными исполнительными блоками G410a, G410b. Для этого требуется специальное программирование регистров G430a, G430b маскировки прерываний. Регистры прерываний предусматривают для каждого источника G440a - G440n прерываний по одному биту в регистре. В случае установки этого бита прерывание блокируется, т.е. не передается на подключенный исполнительный блок G410a, G410b. Удобно в режиме повышенной производительности обрабатывать заданный источник G440a - G440n прерываний именно в одном исполнительном блоке G410a или G410b. Благоприятно, если это относится по меньшей мере к нескольким источникам прерываний. Это позволяет одновременно обрабатывать несколько источников G440a - G440n прерываний, причем не происходит вложение прерывания (обработка прерывания прерывается вторым прерыванием) или повисание прерывания (обработка второго прерывания откладывается до окончания обработки первого).

В режиме сравнения необходимо обеспечить, чтобы контроллеры G420a, G420b прерываний всех исполнительных блоков G410a, G410b одновременно инициировали одинаковое прерывание, в противном случае соответственно режиму сравнения будет обнаружена ошибка. Это означает, что в фазе синхронизации при переключении из режима повышенной производительности в режим сравнения необходимо обеспечить идентичность регистров G430a, G430b маскировки прерываний. Такая синхронизация представлена шагом G660 на фиг.9.

Эту синхронизацию можно выполнить по программе, соответственно запрограммировав оба регистра G430a, G430b маскировки прерываний с одинаковым значением. Предлагается использовать специальный регистр G460, чтобы ускорить процесс переключения. В одном из вариантов исполнения этот регистр G460 расположен в блоке G70 переключения и сравнения, но может содержаться также в блоке G40 распознавания потребности в переключении, в комбинированном блоке распознавания потребности в переключении, сравнения и переключения G80, а также во всех их комбинациях. Кроме того, возможно расположение этого регистра за пределами указанных трех компонентов в другом пригодном для этого месте. Регистр G460 содержит маскировку прерываний, которая должна действовать в режиме сравнения. Блок G450 переключения и сравнения получает от блока G40 распознавания потребности в переключении сигнал на переключение из режима повышенной производительности в режим сравнения. После блокировки прерываний на шаге G600 можно перепрограммировать регистры G430a, G430b маскировки прерываний контроллеров G420a, G420b прерываний. Это осуществляется аппаратными средствами блока G450 переключения и сравнения параллельно прочим шагам синхронизации после получения сигнала переключения и блокировки контроллеров G420a, G420b прерываний. Перепрограммировать регистры G430a, G430b маскировки прерываний в режиме сравнения лучше не по отдельности, а для всего центрального регистра G460. Затем программы аппаратными средствами синхронно передаются на оба регистра G430a, G430b маскировки прерываний. Способ, описание которого приведено здесь для регистра маскировки прерываний, можно переносить на все регистры состояния прерываний, имеющиеся в контроллере прерываний. Разумеется, вместо регистра G460 можно использовать другую запоминающую среду, из которой возможна максимально быстрая передача в регистры G430a, G430b маскировки прерываний.

На фиг.12 показана многопроцессорная система G1000 с двумя исполнительными блоками G1010a, G1010b, блоком G1020 переключения и сравнения и контроллером G1030 прерываний с тремя различными наборами регистров G1040a, G1040b, G1050. В качестве альтернативы к рассмотренному выше решению предлагается специальный контроллер G1030 прерываний, показанный на фиг.12. Он используется в многопроцессорной системе G1000, представленной в примере двумя исполнительными блоками G1010a, G1010b, a также блоком G1020 переключения и сравнения, позволяющим выполнять переключение между режимами сравнения и повышенной производительности.

В режиме повышенной производительности при этом используются наборы регистров G1040a, G1040b. В этом случае контроллер G1030 прерываний работает точно так же, как два контроллера G420a, G420b прерываний. Этот режим с его описанием представлен на фиг.11. Набор регистров G 1040а при этом поставлен в соответствие исполнительному блоку G1010a, а набор регистров G1040b - исполнительному блоку G1010b. Источники прерываний G1060a - G1060n путем маркировки соответствующим образом распределяются между исполнительными блоками G1010a, G1010b. При переключении из режима повышенной производительности в режим сравнения блок G1020 переключения и сравнения генерирует сигнал G1070. Этот сигнал сообщает контроллеру G1030 прерываний, что выполняется переключение в режим сравнения или что система с этого момента работает в режиме сравнения. В соответствии с этим контроллер G1030 прерываний использует набор регистров G1050. Этим обеспечивается поступление одинаковых сигналов прерываний на оба исполнительных блока G1010a, G1010b. С переходом из режима сравнения в режим повышенной производительности, о котором блок G1020 переключения и сравнения снова сообщает контроллеру G1030 прерываний сигналом G1070, опять выполняется переключение на наборы регистров G1040a, G1040b. Удобно, что тем самым обеспечивается также защита соответствующих наборов регистров, поскольку в режиме повышенной производительности разрешена только запись в наборы регистров G1040a, G1040b, а запись в набор регистров G1050, остающемся в режиме сравнения, блокируется аппаратными средствами. То же возможно и в другом направлении, т.е. в режиме сравнения разрешена запись только в набор регистров G1050, а запись в наборы регистров G1040a, G1040b блокирована.

На фиг.13 показана простейшая форма компаратора М500, G20. Важным компонентом в многопроцессорной системе G60 по меньшей мере с двумя исполнительными блоками G10a, G10b с переключением между режимом повышенной производительности и режимом сравнения является компаратор М500. В простейшем виде он представлен на фиг.13. Компонент сравнения М500 может принимать два входных сигнала М510 и М511. Затем он сравнивает их на идентичность, в данном контексте преимущественно в смысле поразрядного совпадения. В случае совпадения значение входных сигналов М510, М511 задается на выходной сигнал М520, и сигнал ошибки не активизируется, т.е. он сигнализирует о состоянии "исправен". При обнаружении несовпадения активизируется сигнал М530 ошибки. Теперь сигнал М520 можно отменить. Преимущество здесь в том, что ошибка не выходит за пределы соответствующей системы (за счет ограничения распространения последствий неисправности). Это означает, что другие компоненты, находящиеся за пределами исполнительного блока, не повреждаются потенциально ошибочным сигналом. Однако существуют системы, в которых не требуется отмена сигнала М520. Это имеет место, например, в том случае, если на уровне системы требуется только скрытие ошибки. Тогда, например, сигнал ошибки может быть выведен на внешнее устройство.

Исходя из этой базовой системы можно представить себе большое число вариантов исполнения. Прежде всего можно выполнить компонент М500 в виде так называемого компонента с полным самоконтролем. В этом случае сигнал М530 ошибки выводится на внешнее устройство по двум линиям или каналам ("dual rail"), а внутренние конструктивные меры и меры по обнаружению ошибок гарантируют, что в каждом возможном случае ошибки компаратора этот сигнал будет корректным или очевидно некорректным. Двухканальный или двухрельсовый сигнал ("dual rail") при этом представляет собой двоичный сигнал, передаваемый по двум линиям преимущественно так, чтобы обе линии в случае отсутствия ошибки были обратными по отношению друг к другу. Согласно изобретению предпочтительным вариантом является система, использующая такой компаратор с полным самоконтролем.

Второй вид вариантов исполнения можно отличить по тому, какую степень синхронности должны иметь оба входа М510, М511 (или М610, М611). Возможное исполнение характеризуется тактовой синхронизацией, т.е. сравнение данных может осуществляться в одном такте.

Небольшое изменение состоит в том, что при постоянном сдвиге фаз между входами используется синхронное звено задержки, обеспечивающее задержку соответствующих сигналов на полуцелые или целые тактовые периоды. Такой сдвиг фаз нужен, чтобы избежать общих ошибок, т.е. исключить такие причины ошибок, которые одновременно и одинаково влияют на несколько процессоров.

Поэтому на фиг.14 показан еще один вариант исполнения. Компоненты и сигналы М600, М610, М611, М620, М630 имеют то же значение, что и соответствующие компоненты и сигналы М500, М510, М511, М520, М530 на фиг.13. На фиг.14 к ним добавлен компонент М640, который задерживает более ранний по времени входной сигнал на величину сдвига фаз. Предпочтительно это запаздывающее звено размещается в компараторе, чтобы использовать его только в режиме сравнения.

Альтернативно или дополнительно во входной цепи можно предусмотреть промежуточные буферы М650, М651, чтобы стала допустимой также асинхронность, представляющая не чистый сдвиг по такту или фазе. Лучше всего рассчитывать эти промежуточные буферы как память обратного магазинного типа. Такая память имеет один вход и один выход и может хранить несколько слов. Входящее слово памяти смещается на один разряд при поступлении нового слова. После последнего разряда (глубины буфера) оно смещается "за пределы памяти". Если имеется такой буфер, можно допустить также асинхронность до максимальной глубины буфера. В этом случае сигнал ошибки должен выдаваться и при переполнении буфера.

Далее варианты исполнения можно различать в компараторе по тому, как генерируется сигнал М520 (или М620). В предпочтительном варианте исполнения входные сигналы М510, М511 (или М610, М611) направляются на выход, а соединение делается прерываемым посредством выключателя. Особым преимуществом этого варианта исполнения является то, что для переключения между режимом повышенной производительности и возможными различными режимами сравнения можно использовать одни и те же переключатели.

Альтернативно сигналы могут генерироваться из внутренних буферов компаратора.

Последний вид вариантов исполнения отличается тем, сколько входов имеет компаратор и как он должен реагировать. При трех входах может осуществляться мажоритарное голосование, т.е. сравнение всех трех или только двух сигналов. При четырех или более входах возможно соответственно большее число вариантов исполнения. Подробное описание возможных вариантов исполнения представлено на фиг.20.

Точный выбор вариантов исполнения лучше объединять с различными режимами работы системы в целом. Это означает, что при наличии нескольких режимов повышенной производительности или сравнения их предпочтительнее комбинировать с соответствующим режимом компаратора.

В некоторых точках осуществления изобретения необходимо или целесообразно выключать (деактивизировать) или делать пассивным компаратор или более общий элемент голосования /обработки/сортировки (который в дальнейшем для простоты будем также всегда называть компаратор). Для этого имеется много возможностей. Во-первых, на компаратор можно подавать сигнал, который будет включать или выключать его. Для этого в компаратор нужно ввести дополнительную логику, которая выполняла бы эти действия. Другая возможность состоит в том, чтобы не вводить в компаратор сравниваемые данные. Третья возможность - на системном уровне игнорировать сигнал ошибки компаратора. Кроме того, можно прерывать и сам сигнал ошибки. Общим для всех возможностей является то, что в системе не имеет значения, различаются ли два или несколько потенциально сравниваемых параметров. Если это имеет место, компаратор рассматривается как пассивный или выключенный.

Ниже рассматривается вариант исполнения переключателя в сочетании с компаратором, т.е. блока G70 переключения и сравнения. Этот вариант исполнения особенно выгоден, если он комбинируется с исполнительными блоками G10a, G10b в одном чипе.

Вследствие объединения компонентов компаратора и переключателя при реализации в одном чипе возникает лишь очень незначительные аппаратные издержки. Поэтому предпочтительный вариант реализации состоит в том, чтобы объединить обе этих части в одном компоненте. Это будет компонент как минимум с входными сигналами (выход исполнительного блока 1, выход исполнительного блока 2), как минимум с выходными сигналами (выход 1, выход 2), логическим выходным сигналом "общий выход" (может физически соответствовать выходу 1 или выходу 2) и компаратором. Компонент способен переключать режим, в режиме повышенной производительности пропускать все сигналы, а в режиме сравнения сравнивать несколько сигналов и при необходимости пропускать один из них. Дополнительно полезно использовать еще и другие входные и выходные сигналы: сигнал ошибки для сигнализации обнаруженной ошибки, сигнал режима для сигнализации режима, в котором находится компонент, и сигналы управления от компонента и к компоненту.

В предпочтительном примере исполнения два или несколько исполнительных блока в режиме повышенной производительности подключены к специализированной шине как ведущие. Блок сравнения выключен или сигнал ошибки, генерируемый при различном поведении исполнительных блоков в одном из возможных режимов сравнения, маскируется. Это означает, что блок переключения и сравнения прозрачен для программы. В рассматриваемом режиме сравнения сравниваемые физические исполнительные блоки рассматриваются как один логический исполнительный блок на шине, т.е. на шине имеется только один ведущий блок. Сигнал ошибки компаратора включен. Для этого блок переключения и сравнения посредством выключателей отключает все исполнительные блоки, кроме одного, от технологической шины, дублирует вводы одного логического исполнительного блока и предоставляет их в распоряжение всем работающим в режиме сравнения исполнительным блокам. При записи на шину выводы сравниваются в блоке сравнения и в случае идентичности эти данные записываются через один из имеющихся доступов к шине.

На фиг.15 и 16 представлена принципиальная схема предпочтительного компонента М700 (соответствует блоку G70 переключения и сравнения). Для простоты здесь изображены только два исполнительных блока. При этом фиг.15 показывает состояние компонента в режиме сравнения, фиг.16 - в режиме повышенной производительности. Различные положения переключателей в этих режимах реализуются компонентом М700 с управлением блоком М760. Оба исполнительных блока М730, М731 могут прежде всего в режиме повышенной производительности вести запись на шину данных и адресную шину М710, когда выключатели М750 и М751 замкнуты, как показано на фиг.16. Предполагается, что возможные конфликты записи будут разрешаться посредством протокола шины или других, не показанных здесь компонентов. В режиме сравнения состояние хотя бы с точки зрения логики иное. Как показано на фиг.15, выключатели М750, М751 в этом случае разомкнуты и, следовательно, возможности прямого доступа отсутствуют. Правда, в отличие от фиг.16 выключатели М730, М731 на фиг.15 замкнуты. Сигналы М740, М741 исполнительных блоков М730, М731 подаются на компонент М720 сравнения. Он как минимум имеет конструкцию, показанную на фиг.13, но может также содержать расширения в соответствии с фиг.14. Сигнал ошибки или другие сигналы компонента М720 сравнения на фиг.15 и 16 не представлены. Если оба сигнала идентичны, выключатель М754 замыкается и один из двух идентичных сигналов направляется на адресную шину/шину данных М710. В целом для этого необходимо, чтобы блок М700 переключения и сравнения мог влиять на выключатели М750 - М754. То или иное положение выключателей зависит от режима и от обнаружения ошибок. Варианты, при которых выключатель М754 всегда замкнут и сигнал ошибки вызывает соответствующую реакцию системы, здесь также учтены.

На фиг.17 представлен вариант блока переключения и сравнения. Даже для простой системы всего с двумя исполнительными блоками G10a, G10b существует много вариантов исполнения блока переключения и сравнения. Другой, особенно удачный вариант, когда в компараторе не используются буферы, показан на фиг.17. Как и на фиг.15, 16, имеются сигналы М840, М841 исполнительных блоков. Последние на фигурах не показаны. В компоненте М800 согласно изобретению имеется режимная логика М810, которая задает режим компонента. В режиме повышенной производительности она замыкает выключатель М830, в режиме сравнения - размыкает. Далее она подает сигнал режима на компаратор М820. Компаратор в этом варианте исполнения всегда выполняет сравнение, но использует результат сравнения и сигнал режима для управления выключателем М830. В режиме повышенной производительности он всегда замкнут, в режиме сравнения он замкнут при отсутствии ошибки.

Разумеется, и в случае обнаружения ошибки выключатель может оставаться разомкнутым, пока не поступит соответствующая команда перезагрузки.

На фиг.18 показан еще один вариант исполнения блока переключения и сравнения. В этом альтернативном варианте больше выключателей, но он оставляет компаратор неактивным в режиме повышенной производительности и поэтому легче решает проблему асинхронности. Здесь также имеются два сигнала М940, М941 исполнительных блоков. Последние и в этом случае не представлены на фигуре. В компоненте М900 согласно изобретению имеется режимная логика М910, задающая режим компонента. В режиме повышенной производительности она замыкает выключатель М931 и размыкает выключатели М932, М933. Следовательно, в компонент М920 сравнения в этом режиме данные не поступают. Это позволяет при асинхронности продлить буферное время или в одном из вариантов исполнения уменьшить глубину буфера. В режиме повышенной производительности выключатель М930 всегда замкнут.В режиме сравнения компонент М910 замыкает выключатели М932, М933 и прерывает прямой доступ к шине путем размыкания выключателя М931. В некоторых случаях режимная логика М910 может также сообщать режим компаратору М920. В режиме сравнения при отсутствии ошибки выключатель М930 замкнут.В случае ошибки компонент М920 сравнения прерывает передачу сигнала М940 на шину путем размыкания выключателя М930.

Как видно из рассматриваемых чертежей, можно без дополнительных мер выводить сигналы режима или сигналы ошибки на внешние устройства. Кроме того, для генерирования внутреннего режимного состояния можно без проблем подавать на компонент другие сигналы.

Таким образом, предпочтительный вариант этого компонента отличается тем, что существуют несколько процессоров, которые могут записывать выходные сигналы на шину (например, адресную шину/шину данных). Важно, что компонент может обрабатывать по меньшей мере два из выходных сигналов исполнительных блоков (например, сравнивать, а иногда также выбирать голосованием или сортировать) и что компонент может воздействовать по меньшей мере на один выключатель, который прерывает по меньшей мере один из прямых доступов к шине. Это особенно полезно, если исполнительные блоки представляют собой процессорные ядра. Кроме того, удобно, когда состояние поддающихся воздействию выключателей характеризует рабочий режим вычислительного блока.

Свойства системы, в частности возможные режимы сравнения, реализуются особенно хорошо, если компонент может подавать сигнал на адресную шину/шину данных. Предпочтительно это реализация переключения выходного сигнала одного из исполнительных блоков. Альтернативой этому может быть обработка различных выходных сигналов разных исполнительных блоков.

Как уже следовало из описания со ссылкой на фиг.17, 18, можно в системе и в зависимости от разделения на компоненты также в одном из компонентов идентифицировать "информацию о режиме. Эта информация о режиме может в зависимости от варианта исполнения существовать в явном виде даже в подкомпоненте. В предпочтительном варианте исполнения этот сигнал может также выводиться из компонента и предоставляться в распоряжение другим частям системы.

В общем случае действие компонентов согласно изобретению можно пояснить на фиг.21. Сигналы и компоненты N100, N110, N120, N130, N140, N141, N142, N143, N14n, N160, N161, N162, N163, N16n имеют то же значение, что и на фиг.20. Кроме того, на этой фигуре показаны сигнал N150 режима и сигнал N170 ошибки. Необязательный сигнал ошибки генерируется схемной логикой N130 переключения при ошибках, собирающей сигналы ошибок, и представляет собой прямую передачу отдельных сигналов ошибок или уплотнение содержащейся в них информации об ошибках. Сигнал N150 режима факультативен, однако его использование во многих местах за пределами компонента может быть полезным. Сочетание информации комбинационной логики N110 (т.е. функция, приведенная в описании к фиг.20) и логики обработки (т.е. определение операции сравнения для каждого выходного сигнала или для каждого значения функции) - это информация о режиме, определяющая режим. Разумеется, в общем случае эта информация многозначна, т.е. ее нельзя представить логическим битом. Не все теоретически возможные режимы целесообразны в том или ином варианте исполнения, число разрешенных режимов преимущественно ограничивается. Сигнал режима в этом случае передает на внешние устройства важную информацию о режиме. Аппаратная реализация обычно представлена таким образом, чтобы можно было конфигурировать наблюдаемый извне сигнал режима. В предпочтительном варианте логика обработки и комбинационная логика также должны быть конфигурируемыми. Эти конфигурации должны согласовываться друг с другом. Альтернативно или дополнительно можно выдавать наружу также изменения сигнала режима. Это создает преимущества, в частности, в системах с двойной конфигурацией.

В предпочтительном варианте осуществления изобретения этот сигнал режима защищен. Вариант исполнения в двухъядерной системе представлен на фиг.19, например, на базе варианта, показанного на фиг.17. Там сигнал М850 выводится из блока переключения и сравнения. В двухъядерной системе эта информация логически представлена одним двоичным разрядом. Защита обеспечивается "двухканальным" сигналом. В обычном случае можно предусмотреть защиту также посредством оптимально инвертированного удвоения. В альтернативном варианте можно генерировать также четность с внутренней защитой или использовать контроль с помощью избыточного циклического кода или же кода исправления ошибок.

Сигнал режима можно использовать за пределами компонента. Прежде всего он используется для самоконтроля операционной системы. Она с программной точки зрения ответственна за переключение и всегда должна знать, в каком режиме находится система и переводить систему в этот режим. Следовательно, проверка сигнала может использоваться для защиты. Сначала это делается непосредственно. Однако альтернативная возможность состоит в том, чтобы посредством таймера или других "независимых" устройств придать семантический смысл запросу в операционной системе.

Обычно этот сигнал в качестве варианта можно использовать также в других устройствах приема данных микроконтроллера (или более общего вычислительного устройства). Например, устройство защиты памяти (УЗП) можно программировать таким образом, чтобы оно допускало определенные обращения к памяти (определенных исполнительных блоков) только в определенных режимах. При этом УЗП является устройством, которое может обеспечить только разрешенный доступ к данным/адресам, например, запрещая определенным частям программы доступ к определенным адресным пространствам. Путем подачи сигнала режима на УЗП, соответствующей конфигурации, программирования этого УЗП и анализа данных конфигурации и сигнала режима может быть обеспечена дополнительная защита. В некоторых случаях это даже упрощает программирование, если сигнал режима уже представляет собой достаточную информацию для проверки. Тогда квазистатического программирования достаточно для времени инициализации микроконтроллера. То же может относиться к периферийным устройствам. Здесь также имеются случаи применения, при которых доступ к соответствующему элементу периферии разрешен только в определенных режимах. Путем подачи сигнала режима на элемент периферии, соответствующей конфигурации и программирования элемента периферии и анализа этих данных конфигурации и сигнала режима, можно обеспечить дополнительную защиту. В некоторых случаях это даже упрощает программирование, если сигнал режима уже представляет собой достаточную информацию для проверки. Тогда квазистатического программирования достаточно для времени инициализации микроконтроллера. Аналогично анализ этого сигнала можно использовать на контроллере прерываний. Такой контроль может стать основой или существенной составной частью концепции защиты информации. Соответствующее исполнение и структуризация программного обеспечения могут позволить разработку концепции защиты от целого класса ошибок в рассматриваемых случаях применения на базе этого сигнала режима. Это создает особые преимущества в тех случаях, когда сигнал режима в рассмотренном выше виде внутренне защищен. Дополнительным преимуществом является то, что рассматриваемый компонент имеет возможность передавать сигнал ошибки или производить отключение при обнаружении несоответствия между сигналом режима и обращением к самому себе.

Другой важной целью применения является анализ сигнала режима за пределами вычислительного блока. Прямое применение - это анализ в декрементирующей схеме безопасности или сторожевой схеме. Такая "схема безопасности" состоит по меньшей мере из одного (счетного) регистра, который с помощью микропроцессора можно установить на целое числовое значение. После установки этого регистра "схема безопасности" с постоянным периодом уменьшает значение регистра. Если значение регистра равно нулю или происходит переполнение регистра, "схема безопасности" генерирует сигнал ошибки. Если сигнал ошибки генерировать не нужно, микропроцессор должен своевременно восстановить значение регистра. Это (в определенных пределах) позволяет проверить, правильно ли микропроцессор выполняет программу. Если микропроцессор перестает правильно выполнять программу, предполагается, что "схема безопасности" уже не получает правильного обслуживания и поэтому она генерирует сигнал ошибки. Целостность аппаратного обеспечения и структур данных можно надежно проверить в режиме сравнения, но для этого необходимо обеспечить, чтобы микропроцессор регулярно снова переключался в этот режим.

Таким образом, задача описываемой здесь "схемы безопасности" состоит в том, чтобы генерировать сигнал ошибки не только в случае, если в пределах определенного периода времени схема не восстанавливает исходное состояние, но и в случае, если микропроцессор в пределах определенного периода времени не переключается обратно в режим сравнения. Например, восстановить исходное состояние "схемы безопасности" можно лишь тогда, когда сигнал режима сообщит вычислительному блоку об определенном режиме сравнения. Благодаря этому обеспечивается регулярное переключение вычислительного блока в режим сравнения. Альтернативно или дополнительно к этому значение в регистре "схемы безопасности" уменьшается лишь тогда, когда микропроцессор инициирует определенные прерывания. Для этого внешние сигналы прерывания микроконтроллера должны поступать и на схему безопасности. В памяти схемы безопасности записано, какие прерывания переключают микроконтроллер в определенный режим сравнения. Схема безопасности "взводится", как только поступает такой сигнал прерывания, она восстанавливает исходное состояние при поступлении правильного сигнала режима.

В целом полезно, в частности применительно к концепции безопасности, анализировать сигнал режима в источнике, внешнем по отношению к микроконтроллеру. Важным моментом обеспечения правильной отработки программы в вычислительном устройстве согласно описанию изобретения является правильное переключение между различными разрешенными режимами. Прежде всего необходимо проверить собственно способность к переключению, преимущественно еще и к правильному переключению. Как сказано выше, важно также и то, чтобы специальный режим устанавливался регулярно. Такой способ удобен во всех случаях, когда сам сигнал режима имеет внутреннюю защиту.

Одной из возможностей является подача сигнала режима на специализированную интегральную схему или другой микроконтроллер. Он позволяет посредством таймера и простой логики с использованием этого сигнала проверить по меньшей мере следующие пункты:

Достаточно ли часто ли (например, самое позднее через каждые 1000 мкс) вычислительный блок входит в один или несколько определенных режимов?

Всегда ли при переходе в какой-либо режим выдается определенный сигнал?

Регулярно ли выходит вычислительный блок из того или иного режима?

Действуют ли определенные простые схемы последовательности режимов?

Действует ли общая временная схема (например, в среднем<70% в режиме 1 и <50% в режиме 2)?

Возможна ли какая-либо комбинация логических, временных свойств сигнала режима, например, сопровождаемая использованием дополнительных сигналов?

На фиг.22 при этом представлена базовая конфигурация для предложения, выходящего за рамки изложенного. Согласно ему между такими партнерскими специализированной интегральной схемой или микроконтроллером и рассматриваемым вычислительным блоком, использующим это изобретение, проводится диалог - игра в вопросы и ответы. N300 - это вычислительный блок, который может подавать такой сигнал режима. Это может быть, например, микроконтроллер с несколькими исполнительными блоками и другим компонентом, который может генерировать сигнал режима. Этот другой компонент может быть реализован, как показано на фиг.19 или 21. N300 подает сигнал N310 партнеру N330 (например, другому вычислительному блоку, другому микроконтроллеру или специализированной интегральной схеме). Этот партнер посредством сигнала N320 может задавать вопросы блоку N300, на которые N300 должно отвечать посредством N321. Таким вопросом может быть вычислительная задача, правильный результат решения которой N300 должно выдать через N321 в течение определенного временного интервала. N330 может проверить правильность этого результата независимо от N300. Результаты могут, например, храниться в памяти N330 или N330 может вычислить их самостоятельно. При обнаружении неправильного значения выдается сообщение об ошибке. Особенностью предлагаемой связи "вопрос - ответ" является то, что параллельно ответу наблюдается сигнал режима. Лучше всего задавать вопросы так, чтобы для ответа на них блоку N300 нужно было входить в определенные режимы. Это позволяет с уверенностью убедиться в том, что все переходы между режимами функционируют и что предусмотренные программой переключения из режима в режим фактически выполняются. В частности, при запуске системы, а также во время ее работы это может быть важным критерием концепции безопасности.