Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в решающих усилителях (ОУ) с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры).

В современной радиоэлектронной аппаратуре находят применение операционные усилители с существенными различными параметрами. Особое место занимают ОУ с простейшей архитектурой, содержащие небольшое число элементов. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу устройств.

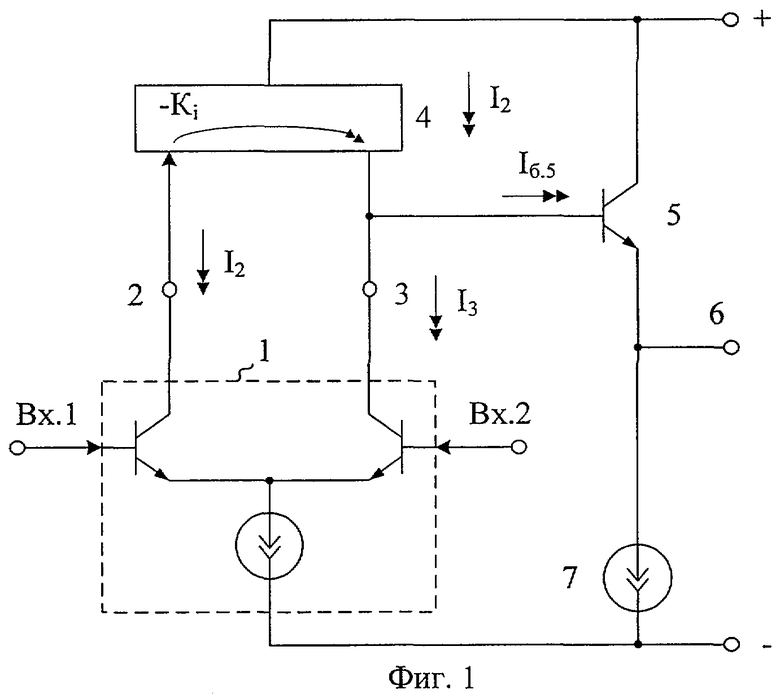

Наиболее близкой по технической сущности к заявляемому ОУ является классическая схема фиг.1, представленная в патенте фирмы Motorola (США) №4042886, fig. 1, которая стала основой построения большого числа аналоговых устройств, например [1-8].

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет повышенное значение напряжения смещения нуля Uсм.

Основная цель предлагаемого изобретения состоит в уменьшении Uсм.

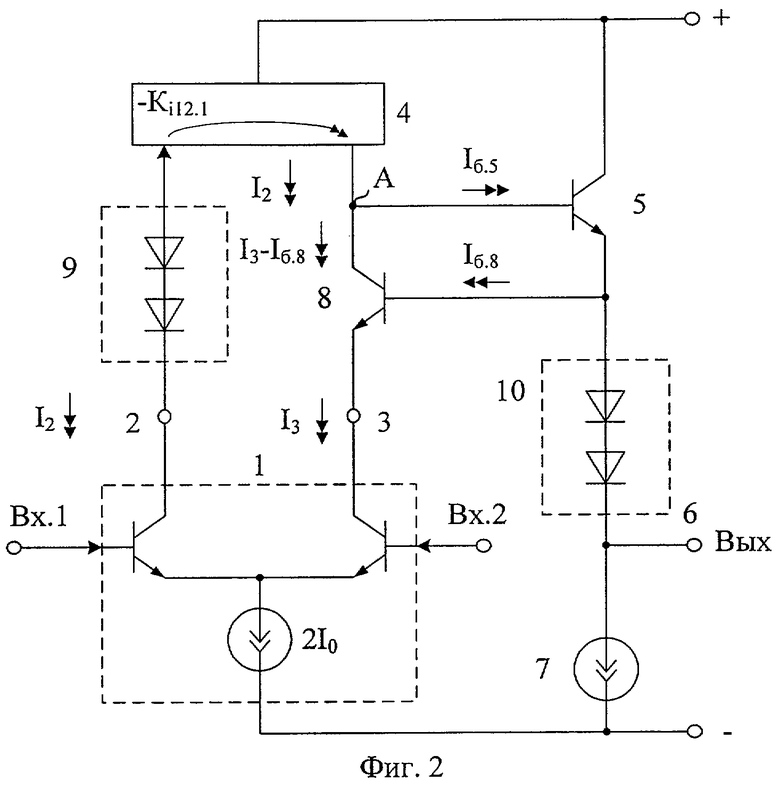

Поставленная цель достигается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, токовое зеркало 4, вход которого связан с первым 2 коллекторным выходом входного дифференциального каскада 1, выходной транзистор 5, база которого соединена с выходом токового зеркала 4, а эмиттер подключен к выходу 6 прецизионного операционного усилителя и цепи эмиттерной нагрузки 7 выходного транзистора 5, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 8, причем коллектор дополнительного транзистора 8 соединен с базой выходного транзистора 5, эмиттер подключен ко второму 3 токовому выходу входного дифференциального каскада 1, база соединена с эмиттером выходного транзистора 5.

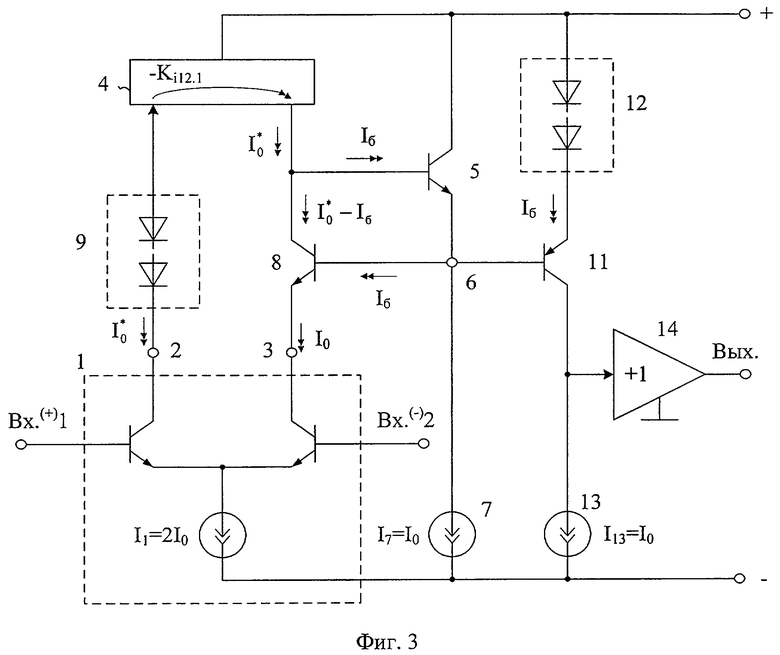

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения. На фиг.3 представлена схема трехкаскадного ОУ, в котором используется заявляемое устройство (фиг.2) для случая, когда его нагрузкой является промежуточный каскад, выполненный на биполярном транзисторе 11, связанном с выходным буферным каскадом.

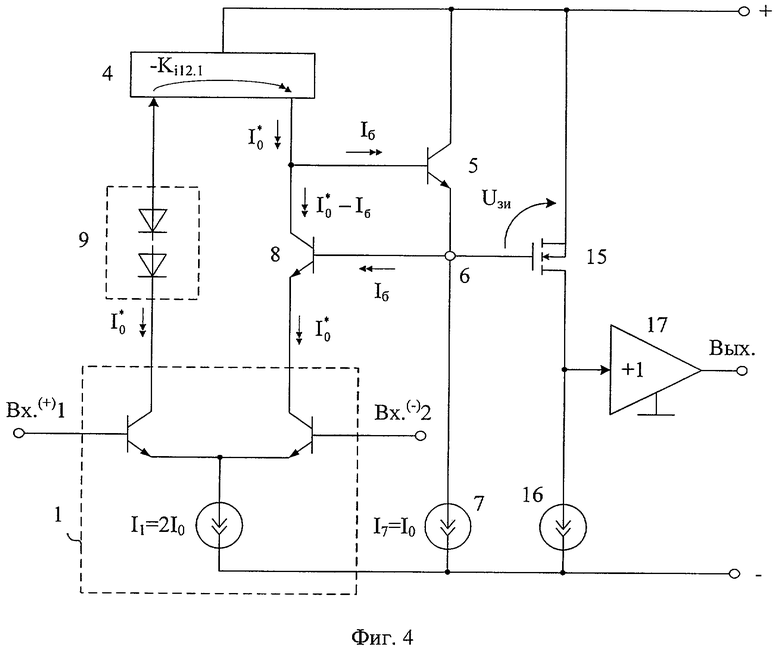

На фиг.4 представлена схема трехкаскадного ОУ, в котором используется заявляемое устройство (фиг.2) для случая, когда в качестве его нагрузки применяется промежуточный каскад на полевом транзисторе 15.

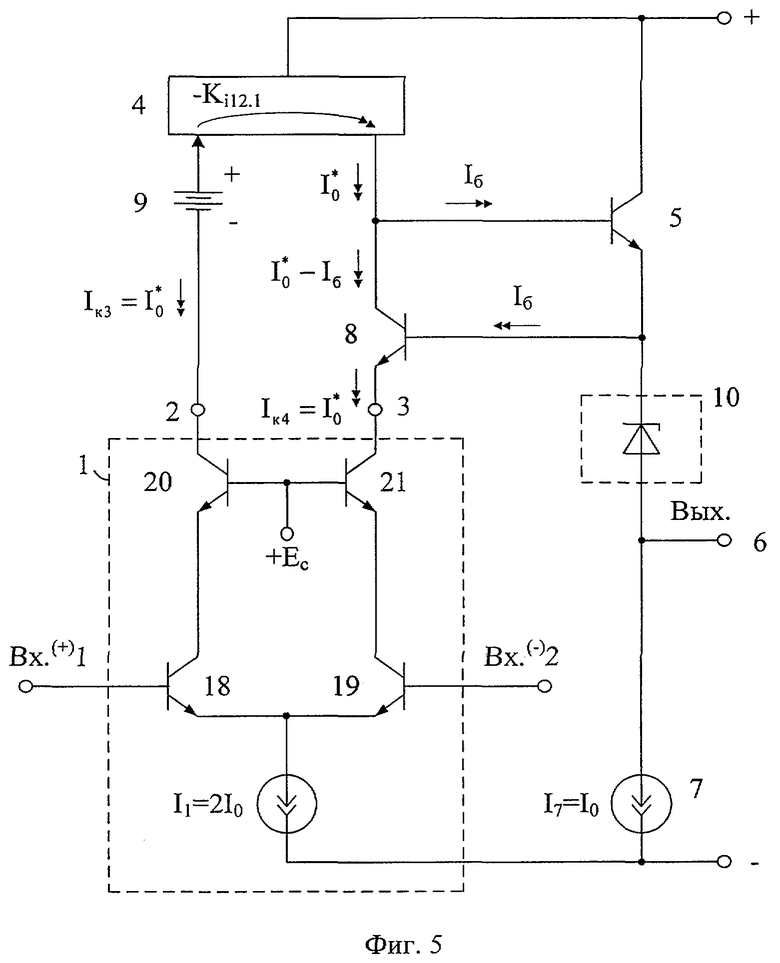

На фиг.5 представлена схема заявляемого устройства для случая, когда в качестве входного дифференциального каскада 1 используется классический каскодный усилитель на транзисторах 18-21.

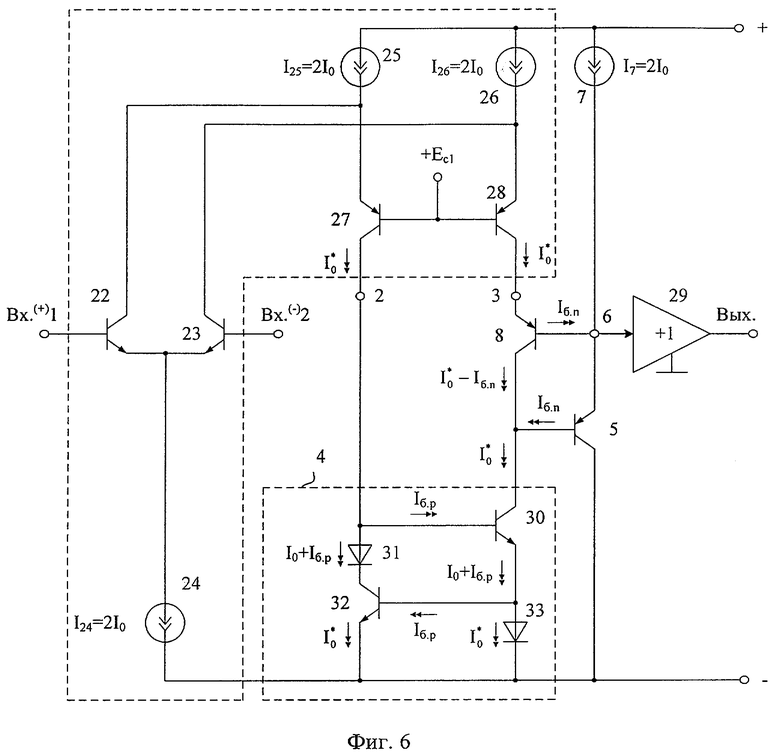

На фиг.6 представлена схема заявляемого устройства (фиг.2) в структуре трехкаскадного операционного усилителя для случая, когда в качестве входного дифференциального каскада 1 используется классический «перегнутый» каскод (элементы 22-28), а в качестве токового зеркала 4 применена известная схема Вильсона.

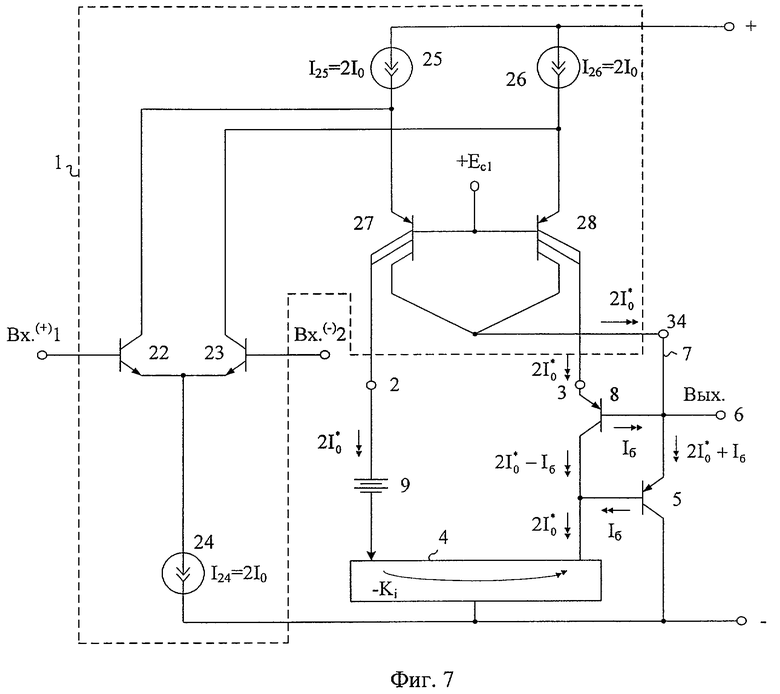

На фиг.7 приведена модификация схемы (фиг.6), в которой в качестве эмиттерной нагрузки 7 используется дополнительный токовый выход 34 входного дифференциального каскада 1.

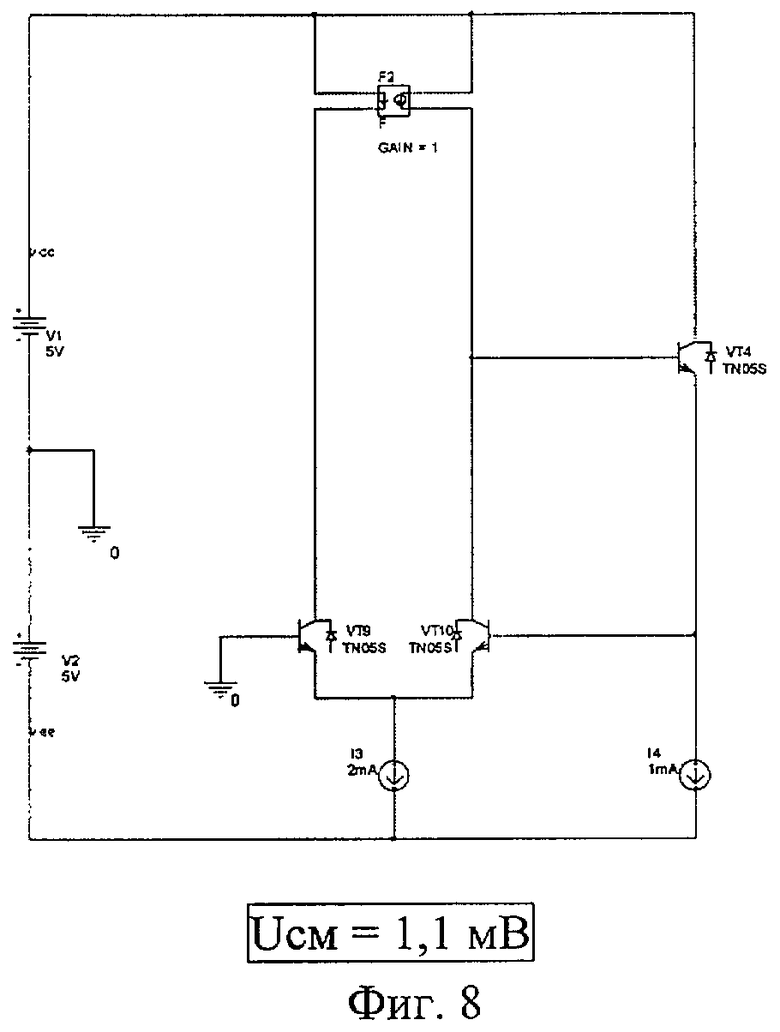

На фиг.8 показана схема ОУ-прототипа (фиг.1) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

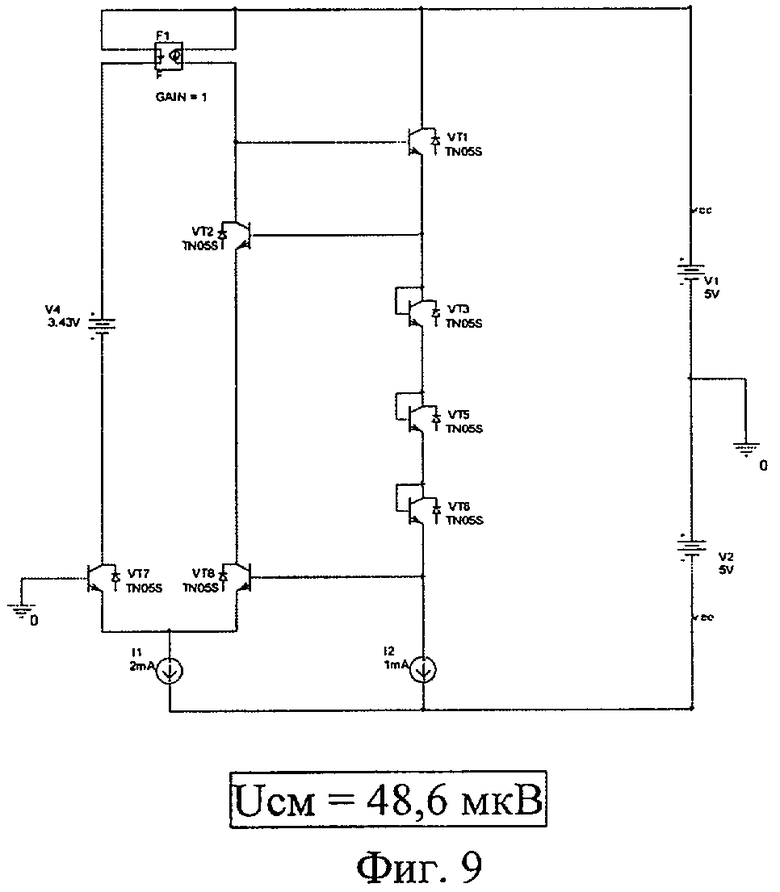

На фиг.9 показана схема заявляемого устройства (фиг.2) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

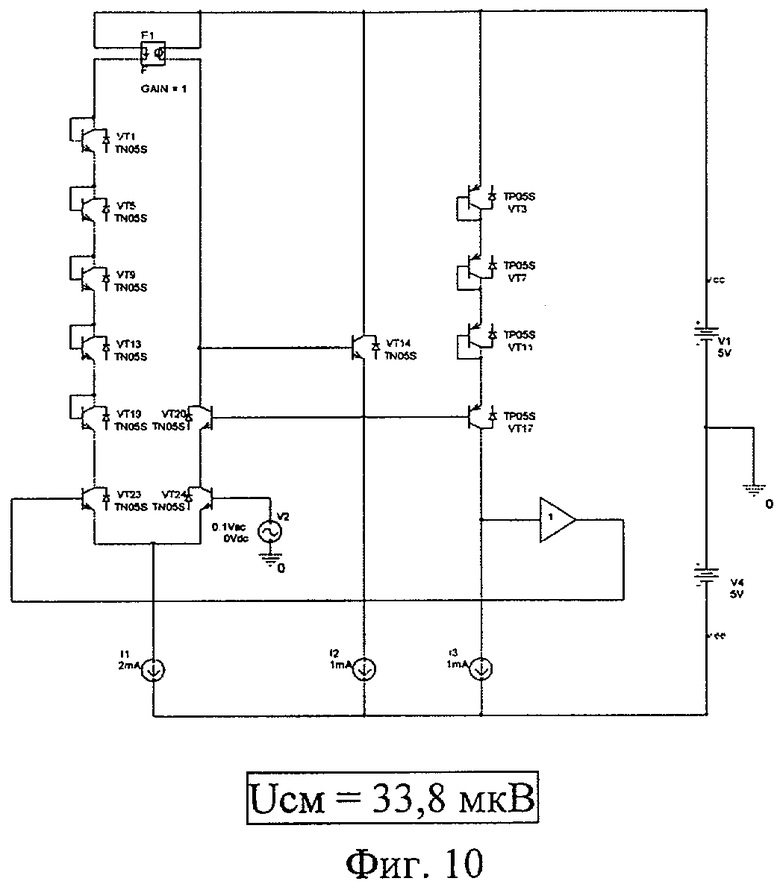

На фиг.10 представлена схема ОУ (фиг.3) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

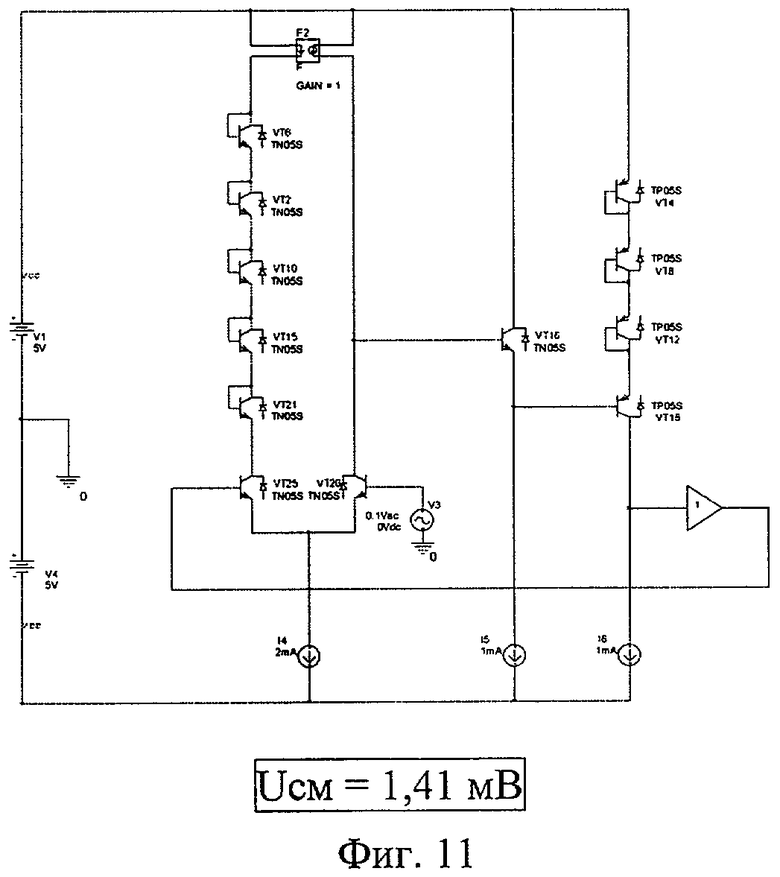

На фиг.11 представлена схема ОУ (фиг.1) с выходной подсхемой, идентичной каскодной подсхеме по фиг.10, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Прецизионный операционный усилитель по фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 коллекторными выходами, токовое зеркало 4, вход которого связан с первым 2 коллекторным выходом входного дифференциального каскада 1, выходной транзистор 5, база которого соединена с выходом токового зеркала 4, а эмиттер подключен к выходу 6 прецизионного операционного усилителя и цепи эмиттерной нагрузки 7 выходного транзистора 5. В схему введен дополнительный транзистор 8, причем коллектор дополнительного транзистора 8 соединен с базой выходного транзистора 5, эмиттер подключен ко второму 3 токовому выходу входного дифференциального каскада 1, база соединена с эмиттером выходного транзистора 5.

На фиг.2, в соответствии с п.2 формулы изобретения, в схему введены первая 9 и вторая 10 цепи согласования потенциалов, причем вход токового зеркала 4 связан с первым коллекторным выходом 2 входного дифференциального каскада 1 через первую цепь 9 согласования потенциалов, а эмиттер выходного транзистора 5 связан с выходом 6 прецизионного операционного усилителя через вторую цепь 10 согласования потенциалов.

В схеме фиг.3 к выходу схемы фиг.2 подключен промежуточный каскад по схеме с общим эмиттером на транзисторе 11 с цепью местной обратной связи 12 и источником тока 13 в качестве нагрузки, выход которого связан со входом буферного каскада 14. Этой схеме присущи повышенные значения коэффициента усиления по напряжению при малом Uсм.

Особенность схемы фиг.4 состоит в том, что здесь к выходу 6 ОУ фиг.2 подключен затвор полевого транзистора 15. Нагрузка в цепи стока транзистора 15 реализована на двухполюснике 16 и буферном усилителе 17.

В схеме фиг.5 входной дифференциальный каскад 1 реализован по каскодной архитектуре на транзисторах 18-21, а источник напряжения смещения 10 выполнен в виде стабилитрона.

Следует заметить, что в качестве элементов 9 и 10 могут применяться последовательно соединенные р-n-переходы.

В схеме фиг.6 входной дифференциальный каскад 1 выполнен на базе параллельно-балансного усилителя (элементы 22-24) и «перегнутого» каскода (элементы 25-28), а к выходу 6 подключен буферный усилитель 29. В частном случае токовое зеркало 4 реализовано по схеме Вильсона на элементах 30, 31, 32, 33.

В схеме фиг.7 входной дифференциальный каскад 1 (так же как и в схеме 6) реализован на базе элементов 22-28. Однако функции цепи эмиттерной нагрузки 7 здесь выполняют многоколлекторные транзисторы 27 и 28 входного дифференциального каскада 1.

Рассмотрим работу схемы фиг.2 на постоянном токе.

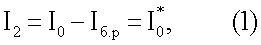

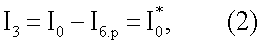

Если принять, что ток общей эмиттерной цепи входного дифференциального каскада 1 равен 2I0, то токи выходов 2 и 3

где Iб.р - ток базы входного n-p-n-транзистора, образующего входной дифференциальный каскад.

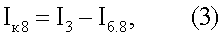

С учетом первого закона Кирхгофа можно найти ток коллектора транзистора 8

где Iб.8 - ток базы транзистора 8.

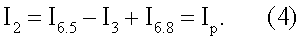

Поэтому сумма токов в узле «А» при коэффициенте передачи по току подсхемы 4 (например, токового зеркала Вильсона), равном единице

Учитывая, что Iб.5=1б.8, из (4) следует, что сумма токов в узле «А» равна нулю, т.е. Ip=0.

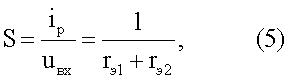

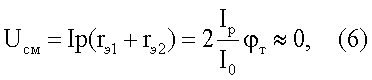

Вследствие воздействия, например, радиации, токи Iб.8 и Iб.5 изменяются в несколько раз, однако и в этом случае Ip≈0, так как изменения 1б.8 и 1б.5 одинаковы. Как следствие, это уменьшает Ucм, так как разностный ток Ip в узле «А» создает Uсм, зависящее от крутизны преобразования входного напряжения uвх ДУ фиг.2 в выходной ток узла «А»

где rэ1=rэ2 - сопротивления эмиттерных переходов входных транзисторов дифференциального каскада 1.

Поэтому для схем фиг.2

где

φт - температурный потенциал.

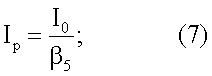

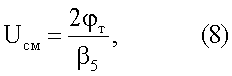

В ДУ-прототипе Ip≠0:

где β5=30÷50 - коэффициент усиления по току базы транзистора 5.

Поэтому здесь систематическая составляющая Uсм получается как минимум на порядок больше (фиг.8, Uсм=1,1 мВ), чем в заявляемой схеме (фиг.9, Uсм=48,6 мкВ).

Введение первой 9 и второй 10 цепей согласования потенциалов в соответствии с п.2 формулы изобретения создает для некоторых схем дополнительные условия, уменьшающие Uсм за счет симметрирования статического режима транзисторов входного дифференциального каскада 1.

Таким образом, заявляемое устройство имеет существенное преимущество в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4042886.

2. Патент Японии JP 10032437.

3. Патент Японии JP 2005033558.

4. Патент США №4595883, fig.4.

5. Патентная заявка США №2005/0063270 А1, fig.2.

6. Патент США №5166638, fig.1.

7. Патент США №5537081, fig.3.

8. Патент США №6114904.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390918C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402156C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455757C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450424C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2402151C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402871C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416151C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401508C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411634C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ) с малыми значениями эдс смещения нуля в условиях воздействия радиации или температуры). Технический результат: уменьшение напряжения смещения. Прецизионный ОУ содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) коллекторными выходами, токовое зеркало (4), вход которого связан с первым (2) коллекторным выходом входного ДК (1), выходной транзистор (Т) (5), база которого соединена с выходом токового зеркала (4), а эмиттер - подключен к выходу (6) ОУ и цепи эмиттерной нагрузки (7) выходного Т (5). В схему введен дополнительный Т (8), причем коллектор дополнительного Т (8) соединен с базой выходного Т (5), эмиттер - подключен ко второму токовому выходу (3) входного ДК (1), база - соединена с эмиттером выходного Т (5). 1 з.п. ф-лы, 11 ил.

1. Прецизионный операционный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) коллекторными выходами, токовое зеркало (4), вход которого связан с первым (2) коллекторным выходом входного дифференциального каскада (1), выходной транзистор (5), база которого соединена с выходом токового зеркала (4), а эмиттер подключен к выходу (6) прецизионного операционного усилителя и цепи эмиттерной нагрузки (7) выходного транзистора (5), отличающийся тем, что в схему введен дополнительный транзистор (8), причем коллектор дополнительного транзистора (8) соединен с базой выходного транзистора (5), эмиттер подключен ко второму (3) токовому выходу входного дифференциального каскада (1), база соединена с эмиттером выходного транзистора (5).

2. Устройство по п.1, отличающееся тем, что в схему введены первая (9) и вторая (10) цепи согласования потенциалов, причем вход токового зеркала (4) связан с первым (2) коллекторным выходом входного дифференциального каскада (1) через первую (9) цепь согласования потенциалов, а эмиттер выходного транзистора (5) связан с выходом (6) прецизионного операционного усилителя через вторую (10) цепь согласования потенциалов.

| US 4042886 А, 16.08.1977 | |||

| RU 2070768 C1, 20.12.1996 | |||

| US 3914704 A, 21.10.1975 | |||

| US 4533844 A, 06.08.1985. |

Авторы

Даты

2010-05-27—Публикация

2009-02-02—Подача