Изобретение относится к устройствам автоматики и вычислительной техники и может быть использовано в качестве генератора цифровых случайных сигналов с равномерным распределением в устройствах автоматики и вычислительной техники.

Известен формирователь цифровой последовательности с равномерным распределением (см. патент РФ №2103725 от 23.11.94, МПК: G06F 7/58, «Датчик случайных чисел с равномерным распределением», Ермаков В.Ф., Гудзовская В.А.; опуб. 27.01.98, БИ №3), содержащий генератор прямоугольных импульсов, элемент И, первый счетчик и второй счетчик, выходы разрядов которого соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группы из n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых являются выходами устройства, в формирователь также введены блок памяти, элемент ИЛИ, кнопка с контактами и резистор, при этом ко вторым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы из n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены через блок памяти выходы соответствующих разрядов первого счетчика, тактовый вход которого подключен к выходу генератора прямоугольных импульсов, соединенному с тактовым входом второго счетчика, выходы которого через элемент И соединены с первым входом элемента ИЛИ, второй вход которого соединен с первым входом установки нуля первого счетчика и через резистор подключен к шине единичного потенциала, а через контакты кнопки - к шине нулевого потенциала, а выход элемента ИЛИ соединен с входом установки нуля второго счетчика.

Вышеуказанное устройство является наиболее близким к заявляемому по технической сущности и поэтому выбрано в качестве прототипа.

Недостатками прототипа являются узкие функциональные возможности и наличие корреляции между числами генерируемой последовательности.

Решаемой задачей является создание формирователя цифровой последовательности с равномерным распределением и с расширенными функциональными возможностями.

Достигаемым техническим результатом заявляемого изобретения является повышение качества генерирования цифровой последовательности и снижение уровня корреляции генерируемых чисел.

Для достижения технического результата в формирователе цифровой последовательности с равномерным распределением, содержащем генератор шумовых сигналов, счетный триггер и схему памяти, новым является то, что дополнительно введены схема стабилизации тока, выход которой соединен со входом генератора шумовых сигналов, схема выравнивания, тактовый генератор, схема выделения постоянной составляющей, схема преобразования аналогового сигнала в цифровой и предварительный усилитель, вход которого соединен с выходом генератора шумовых сигналов, а выход соединен со входом схемы выделения постоянной составляющей и с первым входом схемы преобразования аналогового сигнала в цифровой, второй вход которой соединен с выходом схемы выделения постоянной составляющей, выход схемы преобразования аналогового сигнала в цифровой соединен со входом счетного триггера, выход которого соединен с первым входом схемы выравнивания, второй вход которой соединен с первым выходом тактового генератора, второй выход которого соединен с первым входом схемы памяти, второй вход которой соединен с выходом схемы выравнивания, выход схемы памяти является выходом формирователя.

Введение схемы стабилизации тока, схемы выравнивания, схемы выделения постоянной составляющей и схемы преобразования аналогового сигнала в цифровой позволяет повысить качество генерирования цифровой последовательности и уменьшить уровень корреляции генерируемых чисел, а введение тактового генератора позволяет синхронизировать работу блоков формирователя.

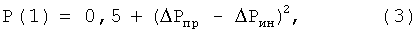

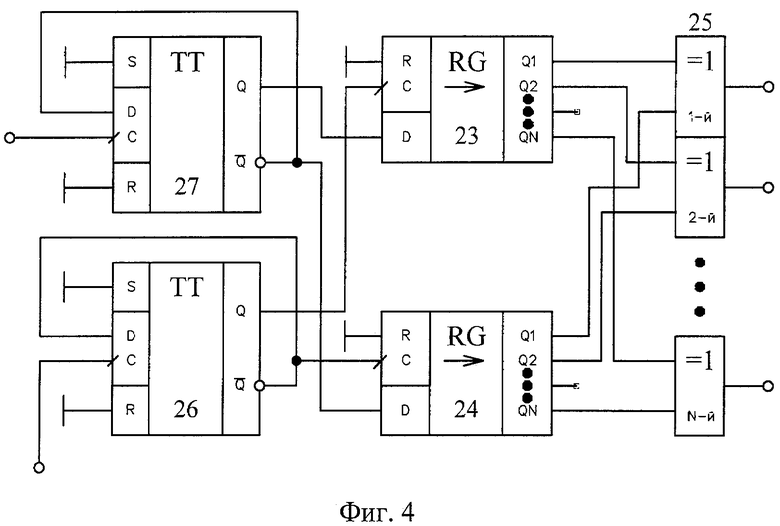

На фиг.1 представлена структурная схема формирователя цифровой последовательности с равномерным распределением, на фиг.2 - схема стабилизации режима, на фиг.3 и 4 - схема выравнивания (первый и второй варианты, соответственно), на фиг.5 приведена схема выделения постоянной составляющей со схемой преобразования аналогового сигнала в цифровой.

Формирователь цифровой последовательности с равномерным распределением (см. фиг.1) содержит генератор шумовых сигналов 1, счетный триггер 2, схему памяти 3, схему стабилизации тока 4, выход которой соединен со входом генератора шумовых сигналов 1, схему выравнивания 5, тактовый генератор 6, схему выделения постоянной составляющей 8, схему преобразования аналогового сигнала в цифровой 9 и предварительный усилитель 7, вход которого соединен с выходом генератора шумовых сигналов 1, а выход соединен со входом схемы выделения постоянной составляющей 8 и с первым входом схемы преобразования аналогового сигнала в цифровой 9, второй вход которой соединен с выходом схемы выделения постоянной составляющей 8, выход схемы преобразования аналогового сигнала в цифровой соединен со входом счетного триггера 2, выход которого соединен с первым входом схемы выравнивания 5, второй вход которой соединен с первым выходом тактового генератора 6, второй выход которого соединен с первым входом схемы памяти 3, второй вход которой соединен с выходом схемы выравнивания 5, выход схемы памяти 3 является выходом формирователя.

Генератор шумового сигнала 1 может быть выполнен на основе шумового диода (например: 2Г401А) или низковольтного стабилитрона, включенного в режиме микротоков.

Счетный триггер 2 может быть выполнен на основе любого D-триггера, включенного в счетном режиме, или двоичного счетчика (делителя частоты), требуемой разрядности.

Схема памяти 3 может быть выполнена на основе любой микросхемы сдвигового регистра или ОЗУ с последовательным входом записи информации (разрядность регистра или ОЗУ выбирается исходя из требуемой разрядности чисел, формируемой последовательности, и может наращиваться стандартными способами). При необходимости работы с системной шиной данных, в качестве выхода схемы памяти 3 может быть использован буферный регистр или магистральный усилитель.

Схема стабилизации тока 4 может быть выполнена на основе любой токостабилизирующей схемы, обеспечивающей стабилизацию микротоков (менее 1 мА). Схема стабилизации тока 4 обеспечивает питание генератора шумового сигнала 1 стабильным током (вариант схемы стабилизации тока приведен на фиг.2).

Схема выравнивания 5 (см. фиг.3 и 4) обеспечивает выравнивание вероятностей формирования «нулей» и «единиц» формируемой последовательности.

Тактовый генератор 6 может быть выполнен на основе кварцевого генератора или кварцевого резонатора со схемой возбуждения и схемы делителя частоты. Тактовый генератор 6 обеспечивает синхронизацию работы схемы памяти 3 и схемы выравнивания 5.

Предварительный усилитель 7 обеспечивает усиление выходного сигнала генератора 1 до требуемого уровня, необходимого для дальнейшей обработки сигнала. Предварительный усилитель 7 может быть выполнен на основе микросхем операционных усилителей, включенных по типовой схеме.

Схема выделения постоянной составляющей 8 обеспечивает выделение постоянной составляющей аналогового шумового сигнала, поступающего с выхода генератора шумового сигнала 1. Схема выделения постоянной составляющей 8 может быть выполнена на основе интегратора, фильтра низких частот или, в простейшем случае, на основе интегрирующей RC-цепочки.

Схема преобразования аналогового сигнала в цифровой 9 обеспечивает преобразование аналогового шумового сигнала в цифровой и может быть выполнена на основе микросхем компараторов напряжения. Последовательно соединенные схема выделения постоянной составляющей 8 и схема преобразования аналогового сигнала в цифровой 9 приведены на фиг.5.

Формирователь цифровой последовательности с равномерным распределением работает следующим образом.

Питание генератора шумового сигнала 1 обеспечивается схемой стабилизации тока 4 (см. фиг.2), которая выполнена на основе дифференциальной оптопары 10 (например, типа - КОД302Б). Ток светодиода дифференциальной оптопары 10 задается транзистором 11, который охвачен отрицательной обратной связью по току через резистор 12. Через один из фотодиодов дифференциальной оптопары 10 осуществляется следящая обратная связь, которая обеспечивает стабилизацию тока, генерируемого вторым фотодиодом дифференциальной оптопары 10. Сигнал рассогласования обратной связи выделяется на резисторах 13, 14 и 15 с помощью операционного усилителя 16, в цепь обратной связи которого включен конденсатор 17 для повышения устойчивости операционного усилителя. Операционный усилитель 16 через токоограничивающий резистор 18 управляет выходным током транзистора 11. С выхода второго фотодиода дифференциальной оптопары 10 стабилизированный ток подается на генератор шумового сигнала 1, который генерирует аналоговый шумовой сигнал. Далее аналоговый шумовой сигнал усиливается до требуемой величины предварительным усилителем 7. Выходной сигнал предварительного усилителя 7 поступает на вход схемы выделения постоянной составляющей 8 и на второй вход схемы преобразования 9 (см. фиг.5). Схема выделения постоянной составляющей 8 выполнена на операционном усилителе 28, включенном в режиме ФНЧ, частота среза которого задается резисторами 29, 30 и конденсаторами 31, 32. С выхода схемы выделения постоянной составляющей 8 сигнал поступает на первый вход схемы преобразования аналогового сигнала в цифровой 9. Использование сигнала постоянной составляющей в качестве опорного для схемы преобразования аналогового сигнала в цифровой 9 позволяет улучшить точность преобразования аналогового шумового сигнала в цифровой за счет стабилизации пороговых уровней, путем уменьшения влияния низкочастотного температурного и временного дрейфа аналогового шумового сигнала. На входе схемы преобразования аналогового сигнала в цифровой 9 расположен входной делитель напряжения (резисторы 33 и 34), задающий пороговые уровни. Ток делителя задается источниками тока 35 и 36, которые могут быть выполнены, например, на комплиментарных парах биполярных транзисторов по схеме «токового зеркала». Компараторы напряжения 37, 38 образуют двухпороговую схему (можно применить микросхемы сдвоенных компараторов напряжения типа - КР597САЗ). Нагрузкой выходных каскадов с открытым коллектором является резистор 39. В качестве выходного буферного элемента можно использовать элемент ТРИГГЕР ШМИТТА 40.

Цифровой шумовой сигнал с выхода схемы преобразования аналогового сигнала в цифровой 9 поступает на вход счетного триггера 2, который обеспечивает деление его частоты в требуемое число раз. Далее сигнал поступает на вход схемы выравнивания 5, которая обеспечивает выравнивание вероятностей формирования «нулей» и «единиц» в числах формируемой последовательности. Два варианта схемы выравнивания 5 для формирования одного двоичного разряда и формирования N-разрядного двоичного числа приведены на фиг.3 и 4, соответственно.

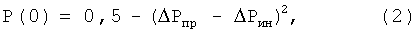

Схема выравнивания 5 (см. фиг.3) реализует двухуровневый алгоритм обработки цифрового шумового сигнала. Первый уровень алгоритма реализуется за счет использования прямых и инверсных состояний считывающих D-триггеров 19 и 20, на выходах которых формируются прямая и инверсная числовые последовательности. При этом, если на прямом выходе считывающего триггера 19 (прямая последовательность) вероятность появления «нуля» равна Р(0)пр=0,5-ΔРпр, а вероятность появления «единицы» равна Р(1)пр=0,5+ΔРпр, то на инверсном выходе считывающего триггера 20 (инверсная последовательность), наоборот, вероятность появления «нуля» равна Р(0)ин=0,5+ΔРин, а вероятность появления «единицы» равна Р(1)ин=0,5-ΔРин. Таким образом, если считывать поочередно прямую и инверсную последовательности, то суммарные вероятности Р(0) и Р(1) выравниваются и стремятся к уровню 0,5. Величины ΔРпр и ΔРин для прямой и инверсной последовательности, вообще говоря, не равны. Это связано с неидеальностями схемы (длительности фронтов и срезов импульсов, наличие задержек распространения сигналов и т.д.).

Поэтому в схему выравнивания 5 добавлен второй уровень алгоритма выравнивания, который реализуется за счет преобразования исходной последовательности Si в последовательность Qi по следующему правилу

Если вероятности появления «нулей» на выходах триггеров 19 и 20 равны Pi(0)=Pi+1(0)=0,5-ΔPm, а вероятности появления «единиц» равны Pi(1)=Pi+1(1)=0,5+ΔPm, то для последовательности Qj, получаемой на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21, вероятности появления «нулей» и «единиц» будут равны Pj(0)=0,5-(ΔPm)2 и Pj(1)=0,5+(ΔPm)2, соответственно. Таким образом, результирующие вероятности появления «нулей» и «единиц» на выходе схемы выравнивания 5 будут равны

Запись информации в считывающие триггеры 19 и 20 происходит по сигналам, поступающим с прямого и инверсного выходов D-триггера 22, который включен в счетном режиме. На вход триггера 22 подается сигнал с тактового генератора 6. Замена триггера 22 на элемент НЕ - нежелательна, так как в этом случае возникает погрешность, связанная с задержкой времени распространения тактового сигнала в элементе НЕ, и сложно обеспечить скваженность импульсов на тактовых входах триггеров 19 и 20, равную 2.

Используя вышеприведенные алгоритмы, легко построить схему выравнивания 5 для формирования N-разрядного двоичного числа. Для этого можно либо наращивать разрядность триггеров 19 и 20 стандартными способами, либо использовать сдвиговые регистры 23, 24 требуемой разрядности. Вариант схемы выравнивания 5 для формирования N-разрядного двоичного числа приведен на фиг.4. Схема содержит сдвиговые регистры 23 и 24, N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25, триггер 26, обеспечивающий формирование прямого и инверсного тактовых сигналов на тактовых входах сдвиговых регистров 23 и 24, соответственно, и триггер 27, обеспечивающий формирование прямой и инверсной последовательности на информационных входах сдвиговых регистров 23 и 24, соответственно. Алгоритмы функционирования схем выравнивания, приведенных на фиг.3 и 4, полностью идентичны. Скорость формирования и качество числовых последовательностей для обеих схем также совпадают, однако применение второго варианта схемы выравнивания 5 в некоторых случаях позволяет существенно упростить схему памяти 3, которая обеспечивает сохранение элементов числовой последовательности, поступающих с выхода схемы выравнивания 5, и выдачу их во внешнее устройство (в шину данных). Синхронизацию работы схемы памяти 3 и схемы выравнивания 5 осуществляет тактовый генератор 6.

В целях подтверждения осуществимости заявляемого объекта и достижения технического результата был изготовлен и исследован лабораторный макет формирователя цифровой последовательности с равномерным распределением, выполненный по схеме, приведенной на фиг.1. Проведенные испытания подтвердили работоспособность формирователя, повышение качества генерирования цифровой последовательности (уменьшение отклонения цифровой последовательности от равномерного закона распределения) и уменьшение уровня корреляции генерируемых чисел. Это подтверждает практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2008 |

|

RU2377721C1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2011 |

|

RU2471287C1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для контроля дребезжания громкоговорителей | 1986 |

|

SU1462518A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2004 |

|

RU2289200C2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

| НУЛЕВОЙ РАДИОМЕТР | 1992 |

|

RU2025743C1 |

| Устройство для контроля физико-механических свойств материалов | 1985 |

|

SU1536301A1 |

| ПРЕОБРАЗОВАТЕЛЬ НЕЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН В ЦИФРОВОЙ КОД | 1991 |

|

RU2020745C1 |

Изобретение относится к устройствам автоматики и вычислительной техники и может быть использовано в качестве генератора цифровых случайных сигналов с равномерным распределением. Техническим результатом изобретения является снижение уровня корреляции генерируемых чисел. Формирователь цифровой последовательности с равномерным распределением содержит генератор шумовых сигналов, счетный триггер, схему памяти, схему стабилизации тока, выход которой соединен со входом генератора шумовых сигналов, схему выравнивания, тактовый генератор, схему выделения постоянной составляющей, схему преобразования аналогового сигнала в цифровой и предварительный усилитель, вход которого соединен с выходом генератора шумовых сигналов, а выход соединен со входом схемы выделения постоянной составляющей и с первым входом схемы преобразования аналогового сигнала в цифровой, второй вход которой соединен с выходом схемы выделения постоянной составляющей, выход схемы преобразования аналогового сигнала в цифровой соединен со входом счетного триггера, выход которого соединен с первым входом схемы выравнивания, второй вход которой соединен с первым выходом тактового генератора, второй выход которого соединен с первым входом схемы памяти, второй вход которой соединен с выходом схемы выравнивания, выход схемы памяти является выходом формирователя. 5 ил.

Формирователь цифровой последовательности с равномерным распределением, содержащий генератор шумовых сигналов, счетный триггер и схему памяти, отличающийся тем, что дополнительно введены схема стабилизации тока, выход которой соединен со входом генератора шумовых сигналов, схема выравнивания, тактовый генератор, схема выделения постоянной составляющей, схема преобразования аналогового сигнала в цифровой и предварительный усилитель, вход которого соединен с выходом генератора шумовых сигналов, а выход соединен со входом схемы выделения постоянной составляющей и с первым входом схемы преобразования аналогового сигнала в цифровой, второй вход которой соединен с выходом схемы выделения постоянной составляющей, выход схемы преобразования аналогового сигнала в цифровой соединен со входом счетного триггера, выход которого соединен с первым входом схемы выравнивания, второй вход которой соединен с первым выходом тактового генератора, второй выход которого соединен с первым входом схемы памяти, второй вход которой соединен с выходом схемы выравнивания, выход схемы памяти является выходом формирователя.

| ДАТЧИК СЛУЧАЙНЫХ ЧИСЕЛ С РАВНОМЕРНЫМ РАСПРЕДЕЛЕНИЕМ | 1994 |

|

RU2103725C1 |

| Генератор случайных чисел | 1988 |

|

SU1566346A1 |

| Генератор случайных равновероятных двоичных чисел | 1986 |

|

SU1374221A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 4395703 26.07.1983. | |||

Авторы

Даты

2011-04-27—Публикация

2008-11-10—Подача