Изобретение относится к области электронных технологий, а именно к аналоговым фазовращателям, и может быть использовано в радиопередатчиках и приемниках, в которых требуется обеспечить сдвиг фазы на 90°.

Из уровня техники известны различные решения проблемы сдвига фазы. В частности, следует упомянуть патент РФ №2367066 [1], в котором заявлен фазовращатель СВЧ, содержащий две линии передачи с одинаковыми волновыми сопротивлениями, одна предназначена для входа СВЧ сигнала, другая - для выхода, полевой транзистор с барьером Шотки, два двухполюсных реактивных элемента либо разной, либо одинаковой величины, при этом сток полевого транзистора с барьером Шотки соединен с одним из концов одного из двухполюсных реактивных элементов, а другой его конец - с линией передачи на выходе, исток полевого транзистора с барьером Шотки заземлен, а на его затвор подают постоянное управляющее напряжение, отличающийся тем, что в фазовращатель СВЧ дополнительно введены два отрезка линии передачи, первый длиной, равной половине длины волны и менее, а второй длиной, равной четверти длины волны, при этом один конец первого отрезка линии передачи соединен с линией передачи на входе и с одним из концов первого двухполюсного реактивного элемента, а второй его конец - с одним из концов второго двухполюсного реактивного элемента и с линией передачи на выходе, один конец второго отрезка линии передачи соединен с другим концом первого двухполюсного реактивного элемента, а второй его конец - с другим концом второго двухполюсного реактивного элемента, при этом сток полевого транзистора с барьером Шотки также соединен либо с одним, либо с другим концом второго отрезка линии передачи, при этом указанная длина волны соответствует средней частоте рабочей полосы частот.

Наиболее близким к заявленному изобретению является фазовращатель, описанный в патенте США №5317276 [2], который преобразует полученный входной сигнал в два выходных сигнала, имеющих разность фаз 90° друг относительно друга, и включает в себя первый и второй входной узел для получения соответственно первого и второго сигналов, имеющих противоположные фазы; первую цепь из двух последовательно включенных резисторов, имеющих одинаковые значения сопротивления, первый конец первой последовательной цепи подключен к первому входному узлу; вторую цепь из двух последовательно включенных конденсаторов, первый и второй конденсаторы с одинаковыми значениями емкости, вторая последовательно соединенная цепь подсоединена между вторым концом первой последовательной цепи и вторым входным узлом, первый выход подключен к узлу между двумя последовательно включенными резисторами, второй выход подключен к узлу между двумя последовательно включенными конденсаторами, разность фаз между выходными сигналами 90°. Выходные напряжения с фазами под прямым углом друг к другу могут быть получены от одного токового пути с амплитудными характеристиками, сходными с обычными 0°/90° фазовращателями, использующими дифференцирующие схемы и интегрирующие схемы. Ортогональность сохраняется в широком диапазоне частот, как в обычном фазовращателе. Данный фазовращатель выбран в качестве прототипа заявленного изобретения.

Недостатки аналога [1] и прототипа [2] заключаются, во-первых, в наличии большого количества элементов, что увеличивает стоимость изготовления, а во-вторых, в использовании емкостей, наличие которых имеет значение в случае высоких частот, поскольку низкономинальные емкости обладают огромной погрешностью из-за геометрических ошибок при изготовлении интегральной схемы, что ухудшает функциональность фазовращателя.

Задачей заявленного изобретения является создание фазовращателя, включающего в своей конструкции меньшее число компонентов, имеющего улучшенную функциональность.

Поставленная задача решена путем создания такой конструкции фазовращателя, в которой уменьшено число компонентов, что позволяет упростить процесс изготовления фазовращателя и снизить его себестоимость, а улучшенная функциональность достигается за счет отсутствия в его конструкции емкости, что имеет значение в случае высоких частот, поскольку емкости с низким номиналом обладают очень большой погрешностью из-за геометрических ошибок при изготовлении интегральной схемы.

Технический результат достигается за счет разработки усовершенствованного фазовращателя, содержащего четыре pMOSFET (где pMOSFET - p-chanal Metal Oxide Semiconductor Field Effect Transistor, известный также как р-канальный МОП-транзистор) и резистор или источник тока, при этом второй и третий pMOSFET управляются противофазными цифровыми сигналами управления, затворы первого и четвертого pMOSFET управляются высокочастотным входным сигналом, а при переключении противофазных цифровых сигналов управления фаза выходного сигнала изменяется на 90°, причем первый и третий pMOSFET соединены последовательно, при этом на исток первого pMOSFET подают напряжение питания (VCC), сток первого pMOSFET связан с истоком третьего pMOSFET, а сток третьего pMOSFET связан с выходом и резистором или источником тока, при этом затвор третьего pMOSFET управляется цифровым сигналом, второй и четвертый pMOSFETs соединены последовательно, при этом на исток второго pMOSFET подают напряжение питания (VCC), сток второго pMOSFET связан с истоком четвертого pMOSFET, а сток четвертого pMOSFET связан с выходом и резистором или источником тока, при этом затвор второго pMOSFET управляется цифровым сигналом.

Таким образом, предлагаются два варианта реализации заявляемого изобретения - либо с резистором, либо с источником тока.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими чертежами.

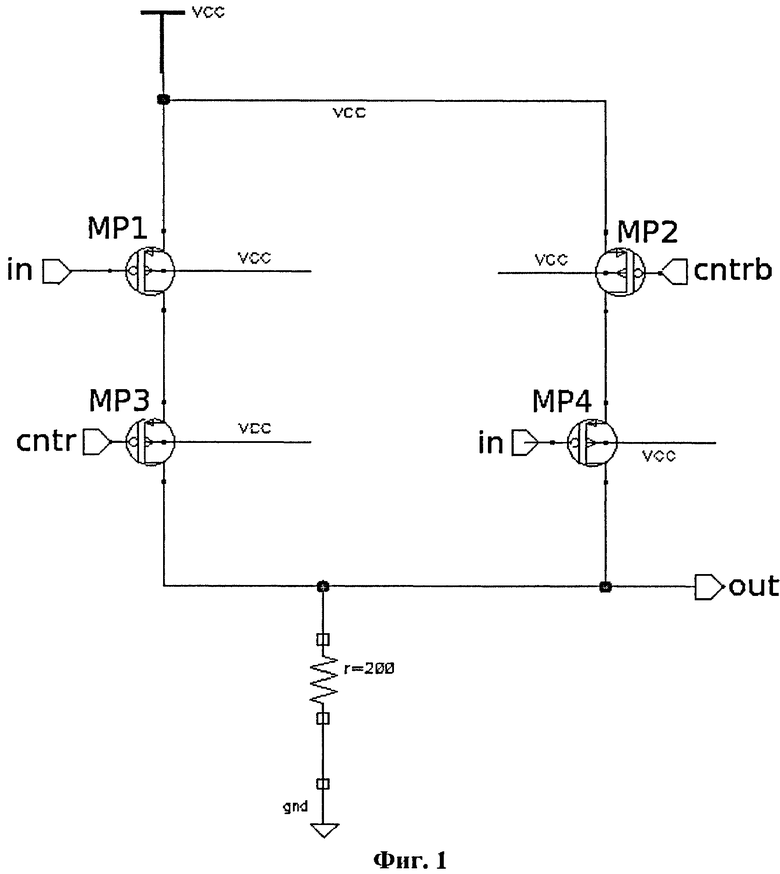

Фиг.1. Схема фазовращателя согласно изобретению.

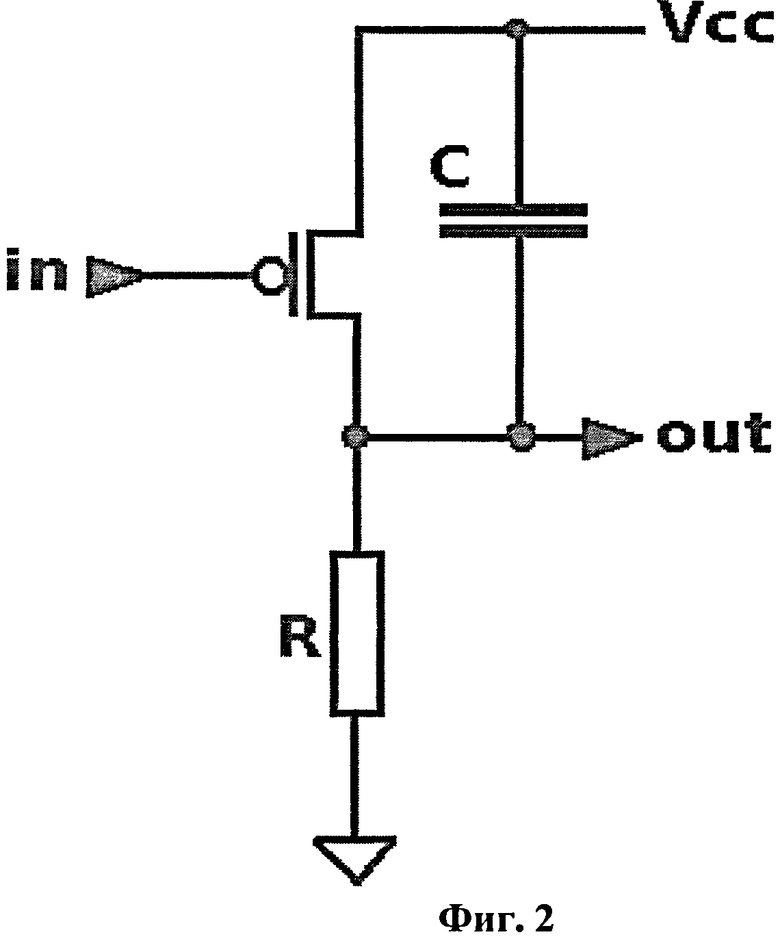

Фиг.2. Принципиальная схема фазовращателя согласно изобретению в случае, когда цифровой сигнал управления cntr равен 1.

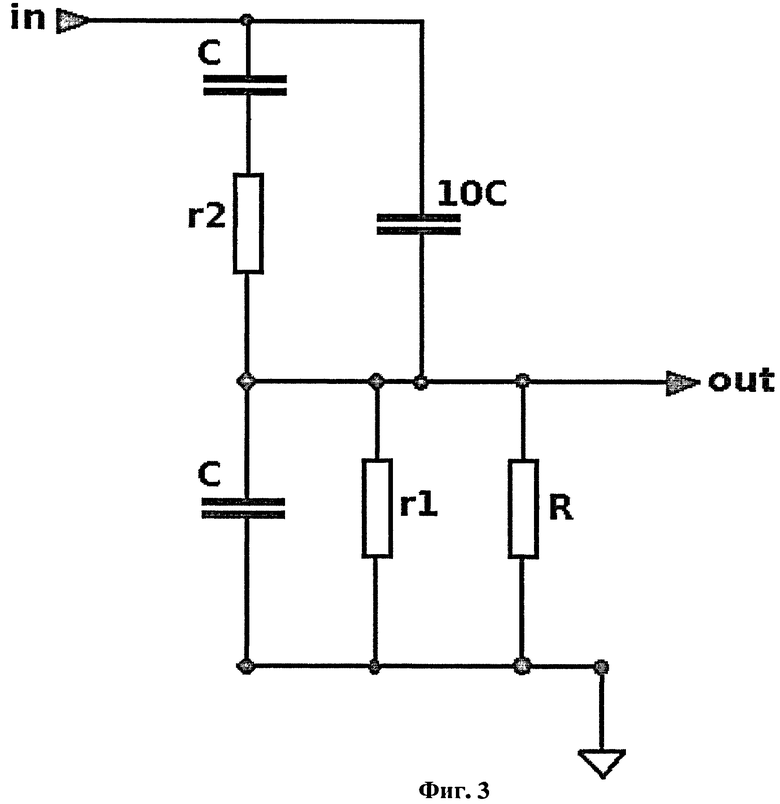

Фиг.3. Принципиальная схема фазовращателя согласно изобретению в случае, когда цифровой сигнал управления cntr равен 0.

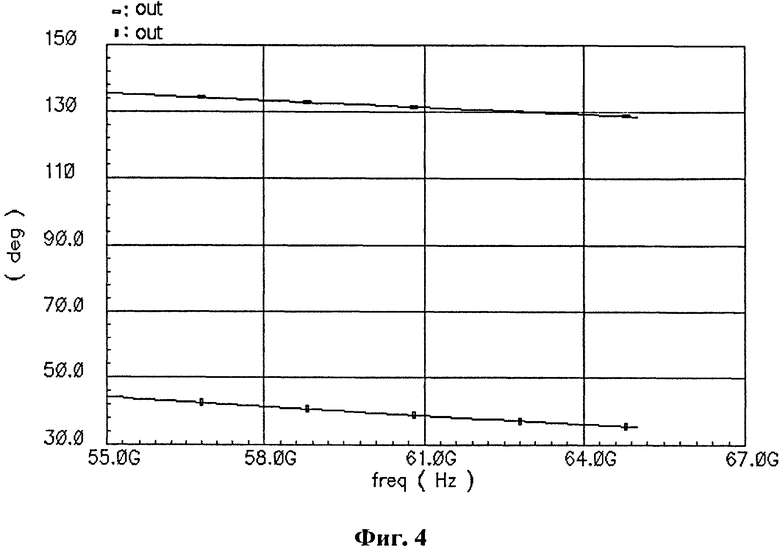

Фиг.4. Фазовая диаграмма фазовращателя согласно изобретению.

Рассмотрим вариант выполнения заявленного фазовращателя, который содержит четыре pMOSFET и резистор или источник тока (Фиг.1). Второй МР2 и третий МР3 pMOSFET управляются противофазными цифровыми сигналами управления cntr, cntrb. На затворы первого МР1 и четвертого МР4 pMOSFET подают высокочастотный входной сигнал. При переключении сигналов управления фаза выходного сигнала изменяется на 90°.

Первый МР1 и третий МР3 pMOSFET соединены последовательно. Исток МР1 связан с VCC (где VCC означает Voltage at the Common Collector, т.е. напряжение питания). Сток МР1 связан с истоком МР3. Исток МР3 связан с стоком МР1. Сток МР3 связан с выходом и источником тока или резистором. Затвор МР3 управляется цифровым сигналом.

Второй МР2 и четвертый МР4 pMOSFET соединены последовательно. Исток МР2 связан с VCC. Сток МР2 связан с истоком в МР4. Исток МР4 связан с стоком МР2. Сток МР4 связан с выходом и источником тока или резистором. Затвор МР2 управляется цифровым сигналом.

Предположим, что цифровой сигнал cntr - 1. В этой ситуации схема па Фиг.1 будет эквивалентна схеме, показанной на Фиг.2. Ток через канал транзистора будет равен  , где Uin(t) - входное напряжение, Vth - пороговое напряжение, K - коэффициент, зависящий от геометрии pMOSFET, подвижности носителей заряда и т.д. Выходное напряжение Uout=0.35*R*K*Vcc*Uin*(2*pi*j*f*R*C-1)*ехр(2*рi*j*f*t), pi=3.1416, j - мнимая единица, f - частота, t - время. Если 2*pi*j*f*R*C=j, то фазовый сдвиг относительно входного сигнала будет 135°.

, где Uin(t) - входное напряжение, Vth - пороговое напряжение, K - коэффициент, зависящий от геометрии pMOSFET, подвижности носителей заряда и т.д. Выходное напряжение Uout=0.35*R*K*Vcc*Uin*(2*pi*j*f*R*C-1)*ехр(2*рi*j*f*t), pi=3.1416, j - мнимая единица, f - частота, t - время. Если 2*pi*j*f*R*C=j, то фазовый сдвиг относительно входного сигнала будет 135°.

Предположим, что цифровой сигнал cntr - 0. В этой ситуации на Фиг.1 будет эквивалентна схеме, показанной на Фиг.3. Если 2*pi*j*f*R*C=j, r2>>R, R>>r1, мы будем иметь Uin(t)/(1-j*R/10*r1). Если j*R/10*r1=j, то фазовый сдвиг относительно входного сигнала будет 45°.

В результате мы имеем фазовую диаграмму, показанную на Фиг.4.

В лучшем варианте выполнения схему заявленного фазовращателя изготавливают на основе CMOS технологии и используют МР1 и МР2 pMOSFET устройства, в которых W/L=51u/0.06u, а также МР3 и МР4, в которых W/L=5U/0.06u.

Хотя указанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕЦИЗИОННЫЙ КМОП УСИЛИТЕЛЬ | 2005 |

|

RU2310270C1 |

| АКТИВНЫЙ ФАЗОВРАЩАТЕЛЬ (ВАРИАНТЫ) | 2012 |

|

RU2510980C1 |

| ФАЗОВРАЩАТЕЛЬ СВЧ | 2008 |

|

RU2367066C1 |

| ТАКТИРУЕМАЯ ИНТЕГРАЛЬНАЯ ПОЛУПРОВОДНИКОВАЯ СХЕМА И СПОСОБ ПРИВЕДЕНИЯ ЕЕ В ДЕЙСТВИЕ | 1999 |

|

RU2216769C2 |

| Каскадная солнечная батарея | 2015 |

|

RU2606756C2 |

| МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО СВЧ | 2010 |

|

RU2411633C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ РАССЕЯНИЯ ЧЕТЫРЕХПОЛЮСНИКА НА СВЧ | 2012 |

|

RU2494408C1 |

| ГЕНЕРАТОР ОПОРНОГО НАПРЯЖЕНИЯ С НИЗКИМ ИМПЕДАНСОМ | 2012 |

|

RU2592719C2 |

| ВЫСОКОЧАСТОТНЫЙ ВЕКТОРНЫЙ ФАЗОВРАЩАТЕЛЬ | 2016 |

|

RU2647217C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ШУМОВЫХ ПАРАМЕТРОВ ЧЕТЫРЕХПОЛЮСНИКА СВЧ | 2012 |

|

RU2499274C1 |

Изобретение относится к области электронных технологий и описывает схему усовершенствованного фазовращателя, содержащего четыре pMOSFET и резистор или источник тока, при этом второй и третий pMOSFET управляются противофазными цифровыми сигналами управления, затворы первого и четвертого pMOSFET управляются высокочастотным входным сигналом, а при переключении противофазных цифровых сигналов управления фаза выходного сигнала изменяется на девяносто градусов, причем первый и третий pMOSFET соединены последовательно, при этом на исток первого pMOSFET подают напряжение питания (VCC), сток первого pMOSFET связан с истоком третьего pMOSFET, а сток третьего pMOSFET связан с выходом и резистором или источником тока, при этом затвор третьего pMOSFET управляется цифровым сигналом, второй и четвертый pMOSFETs соединены последовательно, при этом на исток второго pMOSFET подают напряжение питания (VCC), сток второго pMOSFET связан с истоком четвертого pMOSFET, а сток четвертого pMOSFET связан с выходом и резистором или источником тока, при этом затвор второго pMOSFET управляется цифровым сигналом. Технический результат -упрощение, повышение функциональности. 2 н.п. ф-лы, 4 ил.

1. Фазовращатель, содержащий четыре pMOSFET и резистор, причем первый и третий pMOSFET соединены последовательно, при этом на исток первого pMOSFET подают напряжение питания, сток первого pMOSFET связан с истоком третьего pMOSFET, а сток третьего pMOSFET связан с выходом и резистором, второй и третий pMOSFET управляются противофазными цифровыми сигналами управления, затворы первого и четвертого pMOSFET управляются высокочастотным входным сигналом, затвор третьего pMOSFET управляется цифровым сигналом, второй и четвертый pMOSFETs соединены последовательно, при этом на исток второго pMOSFET подают напряжение питания, сток второго pMOSFET связан с истоком четвертого pMOSFET, а сток четвертого pMOSFET связан с выходом и резистором, при этом затвор второго pMOSFET управляется цифровым сигналом, а при переключении противофазных цифровых сигналов управления фаза выходного сигнала изменяется на девяносто градусов.

2. Фазовращатель, содержащий четыре pMOSFET и источник тока, причем первый и третий pMOSFET соединены последовательно, при этом на исток первого pMOSFET подают напряжение питания, сток первого pMOSFET связан с истоком третьего pMOSFET, а сток третьего pMOSFET связан с выходом и источником тока, второй и третий pMOSFET управляются противофазными цифровыми сигналами управления, затворы первого и четвертого pMOSFET управляются высокочастотным входным сигналом, затвор третьего pMOSFET управляется цифровым сигналом, второй и четвертый pMOSFETs соединены последовательно, при этом на исток второго pMOSFET подают напряжение питания, сток второго pMOSFET связан с истоком четвертого pMOSFET, а сток четвертого pMOSFET связан с выходом и источником тока, при этом затвор второго pMOSFET управляется цифровым сигналом, а при переключении противофазных цифровых сигналов управления фаза выходного сигнала изменяется на девяносто градусов.

| US 5317276 A, 31.05.1994 | |||

| ФАЗОВРАЩАТЕЛЬ СВЧ | 2006 |

|

RU2321106C1 |

| ФАЗОВРАЩАТЕЛЬ СВЧ | 2008 |

|

RU2367066C1 |

Авторы

Даты

2011-05-27—Публикация

2010-03-12—Подача