Изобретение относится к интегральной полупроводниковой схеме с некоторым числом управляемых тактовым сигналом схемных блоков, приводимых в действие как параллельно, так и последовательно, а также к способу приведения в действие таких интегральных полупроводниковых схем.

Интегральные полупроводниковые схемы служат чаще всего для обработки сигналов или данных и реализуются на основе цифровой схемотехники. Такие цифровые схемы обычно требуют использования тактового сигнала, чтобы иметь возможность работы синхронно и в соответствии с процессом, определяемым соответствующим применением. Очень часто определенные процессы обрабатываются согласно определенным протоколам. Эти протоколы требуют определенного числа тактовых периодов.

Во многих применениях, например в случае интегральных полупроводниковых схем для карт с микросхемами, требуемый тактовый сигнал подводится извне посредством соединительного контакта. В применениях, критичных с точки зрения защищенности, в частности таких, при которых обрабатываемые сигналы соответствуют денежным суммам или предоставлению права доступа, злоумышленники проявляют очень большой интерес к получению информации о соответствующих процессах, чтобы иметь возможность влиять на результат. Такая информация может быть получена из длительности отдельных процессов и из требуемого для этого числа периодов тактового сигнала, особенно если уже имеются частичные сведения о типе протекающих процессов.

Интегральные полупроводниковые схемы для карточек с микросхемами включают в себя некоторое число схемных блоков, например таких, как процессор, сопроцессор, энергонезависимая память с соответствующей логикой программирования, схема ввода/вывода, например UART (микросхема приемопередатчика последовательного порта), и другие. В интересах максимально возможной скорости обработки максимально возможное число схемных блоков должны работать одновременно, так что во многих случаях во время записи данных в энергонезависимую память пытаются выполнять задачу в процессоре, а также одновременно приводить в действие сопроцессор, в то время как осуществляется ввод или вывод данных UART.

Реализуемые процессы потребляют энергию напряжения питания главным образом в моменты запускающих фронтов тактового сигнала, так что путем наблюдения или контроля тока, протекающего в интегральную полупроводниковую схему, с одной стороны, можно определить моменты времени запускающих фронтов тактового сигнала, если тактовый сигнал подается извне, а с другой стороны, можно определить длительность отдельных процессов и посредством длительного наблюдения можно установить, когда протекают конкретные процессы. При определенных обстоятельствах можно даже, зная процесс в целом, сделать выводы относительно отдельных процессов и тем самым определить структуру обработки интегральной полупроводниковой схемы.

Поэтому задачей настоящего изобретения является устранение в интегральной полупроводниковой схеме возможности получения информации о типе протекающих процессов путем подсчета пиков тока.

Эта задача решается тем, что в интегральной полупроводниковой схеме вышеописанного типа вывод для выдачи тактового сигнала через соответствующее управляемое средство переключения связано с тактовым входом соответствующих схемных блоков, а управляющие входы средства переключения связаны с выходом генератора случайного сигнала, так что работа конкретного схемного блока осуществляется параллельно или последовательно с одним или несколькими другими схемными блоками в соответствии со случайным сигналом. Задача изобретения решается также согласно способу в соответствии с пунктами 8 и 9 формулы изобретения. Предпочтительные варианты осуществления изобретения приведены в зависимых пунктах формулы изобретения.

В соответствующей изобретению интегральной полупроводниковой схеме различные схемные блоки в зависимости от случайного сигнала приводятся в действие то одновременно, то один за другим, в соответствии с тем, поступает на них тактовый сигнал или нет. При этом может быть так, что процесс в первом схемном блоке прерывается, и начинается или продолжается другой процесс в другом схемном блоке, после чего последовательно или одновременно продолжается выполнение первого процесса. Тем самым достигается то, что определенный процесс при его повторении никогда не имеет той же самой длительности, и поэтому невозможно установить, что речь идет о том же самом процессе.

В предпочтительном варианте осуществления вывод, на котором выдается тактовый сигнал, представляет собой выход управляемого генератора тактового сигнала, управляющий вход которого связан с выходом генератора случайных чисел, так что момент времени запускающего фронта тактового сигнала варьируется в соответствии со случайным сигналом.

При этом особенно предпочтительно, если отклонения случайного сигнала являются относительно медленными по сравнению со средней длительностью периода тактового сигнала, однако амплитуда случайного сигнала от процесса к процессу колеблется так сильно, что аналогичные процессы протекают с различной тактовой частотой и поэтому всегда имеют различную длительность. Тем самым обнаружение запускающих фронтов тактового сигнала существенно затрудняется.

При таком выполнении интегральной полупроводниковой схемы исключается взаимосвязь между приложенным извне тактовым сигналом и тактированием внутри схемы. Внутренний генератор тактового сигнала вырабатывает на основе управления посредством генератора случайного сигнала нерегулярный такт, так что соотнесение определенных процессов с определенными временными интервалами оказывается едва ли возможным.

В другом возможном варианте осуществления изобретения в интегральной полупроводниковой схеме имеются по меньшей мере два генератора тактового сигнала с различной частотой, причем первое число схемных блоков приводится в действие первым тактовым сигналом, а второе число схемных блоков приводится в действие вторым тактовым сигналом. В необходимом случае другие схемные блоки могут приводиться в действие другими тактовыми сигналами. В особенности при перемежении процессов в схемных блоках, тактируемых разной частотой, достигается дополнительное повышение степени случайности длительностей процессов.

В особенно предпочтительном варианте осуществления этого принципа отдельные переключающие средства выполнены в виде мультиплексоров, посредством которых каждый тактовый сигнал может подаваться к каждому схемному блоку. Мультиплексоры управляются случайным сигналом или различными случайными сигналами, так что определенный схемный блок может приводиться в действие различными тактовыми сигналами, которые, кроме того, могут случайным образом варьироваться по своей частоте.

В другом варианте осуществления изобретения генератор тактового сигнала выполнен управляемым, в частности, в виде управляемого напряжением генератора.

В еще одном варианте осуществлении генератор тактового сигнала может быть выполнен с контуром регулирования фазы, который содержит управляемый или настраиваемый делитель частоты, посредством которого в тактовый сигнал вводятся изменения частоты.

Генератор случайного сигнала может представлять собой генератор случайных чисел, который имеет любое количество цифровых выходов, чтобы тем самым непосредственно управлять делителем частоты контура регулирования фазы. К генератору случайных чисел может быть также подключен цифроаналоговый преобразователь, через который, например, может осуществляться управление по управляющему входу генератора. Обычно генератор случайных чисел имеет только один выход, так что имеет место только переключение генератора между двумя частотами.

Но также можно подключить к стабильному генератору делитель частоты, который управляется от генератора случайных чисел. Принципиально речь идет о том, чтобы выработать частотно-модулированный тактовый сигнал, в котором степень модуляции статистически варьируется. При этом предпочтительно, если средняя длительность периода модулирующего сигнала, выработанного генератором случайных чисел, примерно соответствует средней длительности процессов, протекающих в интегральной полупроводниковой схеме.

В особенно предпочтительном варианте осуществления изобретения по меньшей мере один из схемных блоков выполнен в виде вспомогательного схемного блока, хотя примерно с таким же потреблением тока, что и другие схемные блоки, однако без существенной для интегральной полупроводниковой схемы функции. Управляемое генератором случайного сигнала переключение на этот вспомогательный схемный блок перед и/или в течение, и/или после процессов, требующих соответственно определенного числа периодов тактового сигнала, протекающих в интегральной полупроводниковой схеме, приводит к случайному изменению длительности этих процессов, исключая возможность их распознавания по потреблению тока.

Особенно полезным является, если во время процесса в одном схемном блоке происходит либо случайное переключение на вспомогательный схемный блок, либо также случайно приводится в действие или останавливается один или несколько других схемных блоков.

Изобретение поясняется ниже на примерах его осуществления, иллюстрируемых чертежами, на которых показано следующее:

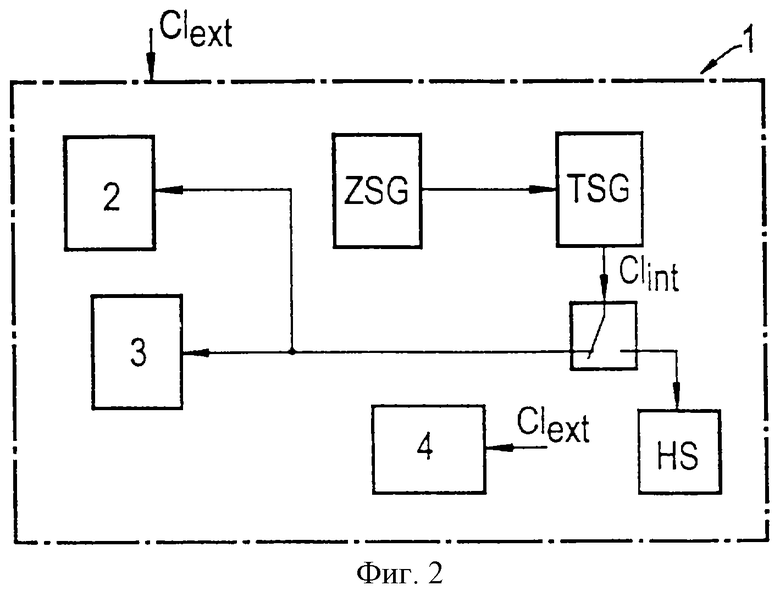

Фиг. 1 - принципиальная блок-схема соответствующей изобретению интегральной полупроводниковой схемы,

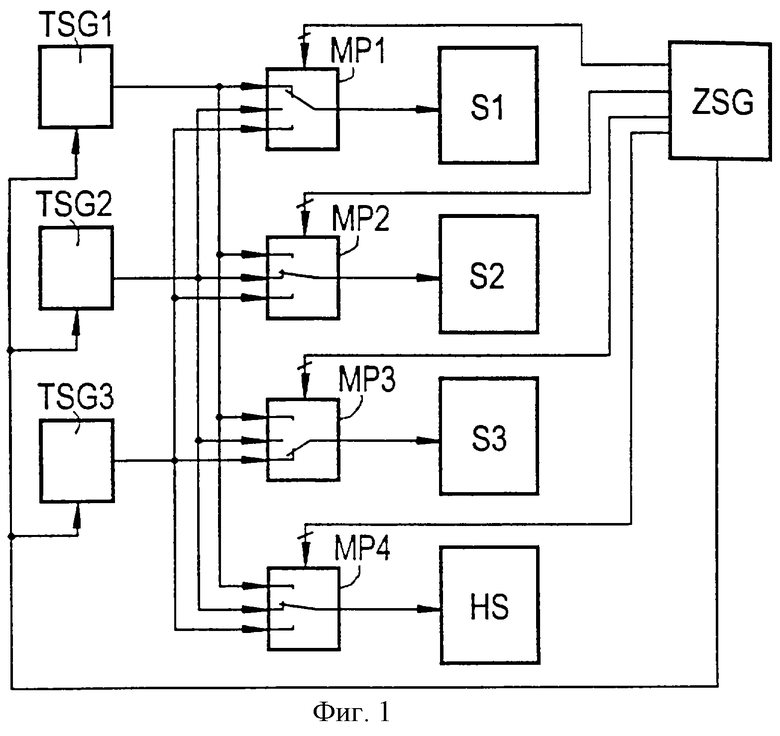

Фиг.2 - другая принципиальная блок-схема соответствующей изобретению интегральной полупроводниковой схемы,

Фиг.3 - вариант генератора тактового сигнала с цифровым генератором случайных чисел,

Фиг. 4 - вариант генератора тактового сигнала с контуром регулирования фазы,

Фиг. 5 - временное изменение процессов с использованием внешнего тактового сигнала и в соответствии с изобретением.

На фиг.1 представлена блок-схема соответствующей изобретению интегральной полупроводниковой схемы с тремя схемными блоками S1, S2, S3. Кроме того, показан вспомогательный схемный блок HS. Имеются три генератора TSG1, TSG2, TSG3, выходные сигналы которых соответственно через мультиплексоры МР1, МР2, МР3, МР4 могут подаваться на схемные блоки S1-S3 и соответственно на схемный блок HS. Мультиплексоры от МР1 до МР4 управляются выходными сигналами генератора ZSG случайных чисел. Еще один выходной сигнал генератора ZSG случайных чисел управляет, кроме того, генераторами TSG1-TSG3 тактового сигнала.

С использованием интегральной полупроводниковой схемы, соответствующей изобретению, можно, таким образом, с помощью тактовых сигналов различных частот путем случайного управления приводить в действие последовательно или параллельно различные схемные блоки S1-S3 и соответственно схемный блок HS, как показано на фиг.1. В частности, путем переключения на вспомогательные схемные блоки HS в процессе осуществления процесса в функциональном схемном блоке могут вводиться "холостые" (фиктивные) такты, так что процесс для внешнего наблюдателя продолжается видимым образом дольше, чем это имеет место на самом деле. Также возможно более короткие процессы за счет параллельного тактирования двух схемных блоков замаскировать под более длительный процесс.

На фиг.2 штрих-пунктирной линией показана интегральная полупроводниковая схема 1, которая, в числе прочего, содержит схемы 2, 3, такие как память или логические схемы. Эти схемы 2, 3 тактируются внутренним тактовым сигналом Clint. Этот внутренний тактовый сигнал вырабатывается генератором TSG тактового сигнала. Генератор TSG тактового сигнала имеет управляющий вход, который соединен с выходом генератора ZSG случайных чисел. Интегральная полупроводниковая схема получает извне внешний тактовый сигнал Clext, который в показанном примере подается в качестве тактового сигнала на схему 4, также содержащуюся в интегральной полупроводниковой схеме 1. За счет дополнительного применения внешнего тактового сигнала Clext в различных схемах могут протекать процессы с различными тактовыми частотами. Тем самым еще больше затрудняется возможность соотнесения процессов в схеме с определенными периодами времени. Кроме того, имеются схемные блоки, как, например, схемы ввода/вывода, которые должны тактироваться внешним тактовым сигналом, так как они получают данные от внешнего терминала и должны работать синхронно с ним.

Генератор TSG тактового сигнала может быть выполнен как управляемый напряжением генератор и может управляться от генератора ZSG случайных чисел с аналоговым выходом.

Как показано на фиг.3, генератор случайных чисел может быть также выполнен как генератор ZZG случайных чисел с любым числом цифровых выходов. В случае показанного на фиг.3 генератора TSG тактового сигнала с аналоговым входом они могут быть связаны с цифроаналоговым преобразователем D/A, аналоговый выходной сигнал которого управляет управляющим входом генератора TSG тактового сигнала.

Принципиально также возможно подключить к обычному генератору тактового сигнала управляемый делитель частоты, который управляется от генератора ZZG случайных чисел. И таким путем можно вырабатывать внутренний тактовый сигнал Сlint, который характеризуется изменяющейся во времени частотой или длительностью периода. Такой пример осуществления показан на фиг.4 внутри штрих-пунктирного блока. Тактовый сигнал Сl', который должен применяться в этом случае, также указан штрих-пунктирной стрелкой.

Фиг. 4 также иллюстрирует добавление генератора тактового сигнала с управляемым делителем Т к контуру регулирования фазы. Для этого выходной сигнал делителя Т, как и внешний тактовый сигнал Сlехt, подается на фазовый детектор, выходной сигнал которого через фильтр нижних частот TPF подается на управляющий вход управляемого генератора VCO. В этом случае выходной сигнал управляемого генератора VCO вырабатывает внутренний тактовый сигнал Clint с отклонениями, определяемыми генератором ZZG случайных чисел.

На фиг. 5 представлены различные длительности двух процессов I и II в случае обычного внешнего тактового сигнала Clext и соответствующего изобретению внутреннего тактового сигнала Clint. Показанный в верхней части фиг.5 внешний тактовый сигнал Clext имеет постоянную частоту. Первый процесс I должен продолжаться в течение восьми периодов, а второй процесс II - в течение четырех периодов. Как можно видеть в верхней части фиг.5, первый процесс I должен был бы продолжаться постоянно в течение одного и того же времени, как и второй процесс II. Потенциальный злоумышленник, который, например, из величины потребления тока определяет, когда в полупроводниковой схеме протекают соответствующие процессы, мог бы при повторяющихся временных периодах определенной длительности прийти к выводу, что речь идет о процессе, уже имевшем место ранее.

В противоположность этому в нижней части фиг.5 представлен внутренний тактовый сигнал Сlint со статистическими отклонениями частоты. Поэтому продолжительность периода в данном случае изменяется к моментам времени t1, t2, t3 и t4. Кроме того, заштрихованными периодами тактового сигнала Clint показаны переключения на вспомогательный схемный блок, т.е. дополнительное введение "холостых" (т.е. формальных, незначащих) тактов. Отдельные тактовые периоды процесса I обозначены цифрами 1-8. Можно видеть, что процесс I сначала имеет длительность Tl, причем в течение этой длительности Tl к моментам времен t1 и t2 частота Сlint переключается и добавляются три холостых периода. Длительность Tl тем самым не имеет никакого отношения в реальной длительности процесса I.

Непосредственно за первым процессом I начинается второй процесс II, тактовые периоды которого также обозначены цифрами от 1 до 8. Здесь после второго тактового периода вводится холостой такт, затем осуществляется переключение на другой схемный блок, в котором осуществляется процесс II. Эти тактовые периоды обозначены цифрами от 1' до 4'. После того как прошли два тактовых периода процесса II, также вводится холостой такт. Затем к моменту времени t3, с одной стороны, переключается частота, а с другой стороны, вновь осуществляется переключение на процесс I. В следующих двух тактовых периодах процессы I и II протекают параллельно. Процесс II затем заканчивается спустя интервал времени T2, в то время как второй процесс I продолжается дальше и заканчивается только спустя интервал времени Т1'.

Процессы I и II требуют, как и прежде, восьми или соответственно четырех длительностей периода тактового сигнала. Отсюда следует общая длительность для соответствующих первых процессов I, равная Т1 и T1', а для вторых процессов II - равная Т2. Как можно видеть в нижней части фиг.5, длительности Т1 и Т1' имеют разные продолжительности, в то время как процесс II вообще реализуется не как единый процесс, так что потенциальный злоумышленник не сможет распознать, о каких процессах действительно идет речь.

С помощью соответствующей изобретению интегральной полупроводниковой схемы можно, таким образом, очень простым, но вместе с тем эффективным способом предотвратить возможность определения длительности определенных процессов и получения сведений об их содержимом.

Изобретение относится к интегральным полупроводниковым схемам, приводимым в действие как параллельно, так и последовательно. Техническим результатом является предотвращение возможности получения информации о типе протекающих процессов путем подсчета пиков тока. Для этого вывод для выдачи тактового сигнала (Clint) через соответственно управляемое средство переключения (МР1, МР2, МР3, МР4) связано с тактовым входом соответствующих схемных блоков (S1, S2, S3, HS), и управляющие входы средств переключения (МР1, МР2, МР3, МР4) связаны с выходом генератора (ZSG) случайного сигнала, так что работа соответствующего схемного блока (S1, S2, S3, HS) осуществляется параллельно или последовательно с одним или несколькими другими схемными блоками (S1, S2, S3, HS) в соответствии со случайными сигналами. 3 с. и 7 з.п.ф-лы, 5 ил.

| JP 60231285 А, 16.11.1985 | |||

| US 5995911 А1, 30.11.1999 | |||

| US 5530431 А1, 25.06.1996 | |||

| ПЕРЕМЕННЫЙ КОРРЕЛЯТОР | 1996 |

|

RU2111538C1 |

Авторы

Даты

2003-11-20—Публикация

1999-07-27—Подача