Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах, изготавливаемых по технологическому процессу SGB25VD).

В современной аналоговой микроэлектронике широко применяются дифференциальные усилители (ДУ) с активными нагрузками в виде токовых зеркал на биполярных транзисторах, тип проводимости которых противоположен типу проводимости входных транзисторов ДУ. Однако SiGe технологический процесс SGB25VD, внедряемый в настоящее время российскими предприятиями для производства РЭА нового поколения, не обеспечивает возможности построения схем с p-n-p транзисторами. Это не позволяет применять традиционные активные нагрузки в ОУ СВЧ диапазона. Как следствие, в качестве элементов коллекторной цепи входного каскада ОУ весьма часто разрешается использовать только пассивные элементы - резисторы [1-15]. В конечном итоге это требование ограничивает Ку входного дифференциального каскада и ОУ в целом.

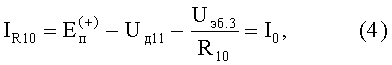

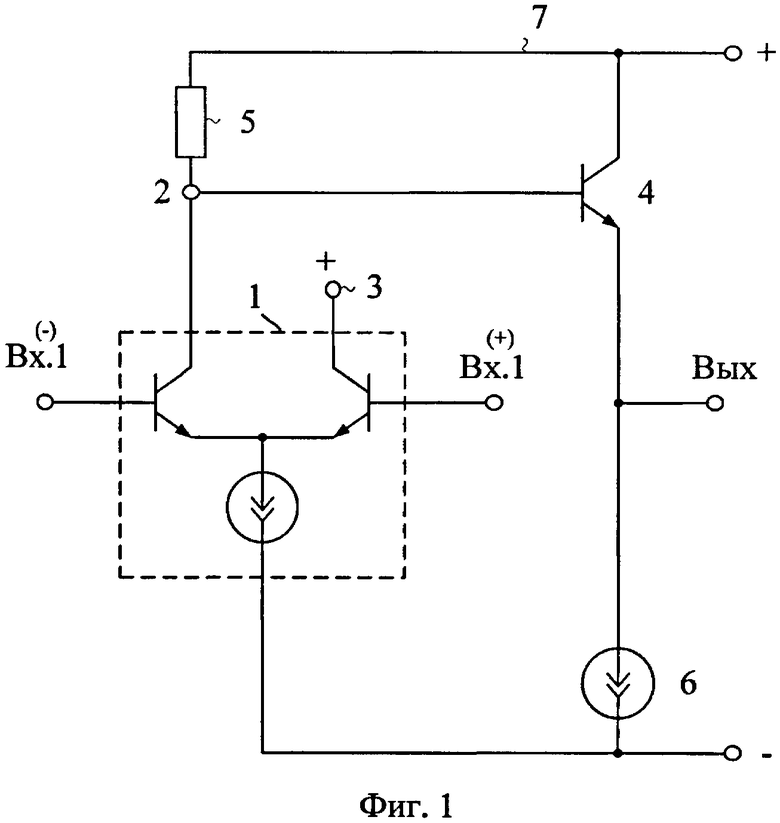

Наиболее близким по технической сущности к заявляемому устройству является ДУ (фиг.1), рассмотренный в патенте США фирмы Hitschi №4.365.207, fig.2. Он содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый выходной транзистор 4, база которого подключена к первому 2 токовому выходу входного дифференциального каскада 1 и первому выводу двухполюсника нагрузки 5, первый токостабилизирующий двухполюсник 6, связанный с эмиттером первого выходного транзистора 4, источник напряжения питания 7

Существенный недостаток известного ДУ состоит в том, что при реализации его двухполюсника нагрузки 5 в виде низкоомного резистора его коэффициент усиления получается небольшим.

Основная задача предполагаемого изобретения состоит в повышении в 8-10 раз коэффициента усиления по напряжению при выполнении двухполюсника нагрузки 5 в виде сравнительно низкоомного (600-800 Ом) резистора.

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый выходной транзистор 4, база которого подключена к первому 2 токовому выходу входного дифференциального каскада 1 и первому выводу двухполюсника нагрузки 5, первый токостабилизирующий двухполюсник 6, связанный с эмиттером первого выходного транзистора 4, источник напряжения питания 7, предусмотрены новые элементы и связи - в схему введены первый 8 и второй 9 дополнительные выходные транзисторы, эмиттер первого 8 дополнительного выходного транзистора соединен с эмиттером первого 4 выходного транзистора, коллектор первого 8 дополнительного выходного транзистора связан с источником напряжения питания 7 через первый дополнительный двухполюсник 10 и подключен к базе второго 9 дополнительного выходного транзистора, эмиттер второго 9 дополнительного выходного транзистора соединен со вторым выводом двухполюсника нагрузки 5 и через второй 11 дополнительный двухполюсник подключен к базе первого 8 дополнительного выходного транзистора и выходу устройства, причем коллектор второго 9 дополнительного выходного транзистора связан с источником напряжения питания 7.

Схема заявляемого устройства, соответствующего п.1 формулы изобретения, приведена на фиг.2. На фиг.2 пунктиром показаны также варианты включения элементов в соответствии с п.2, п.3, п.4 формулы изобретения.

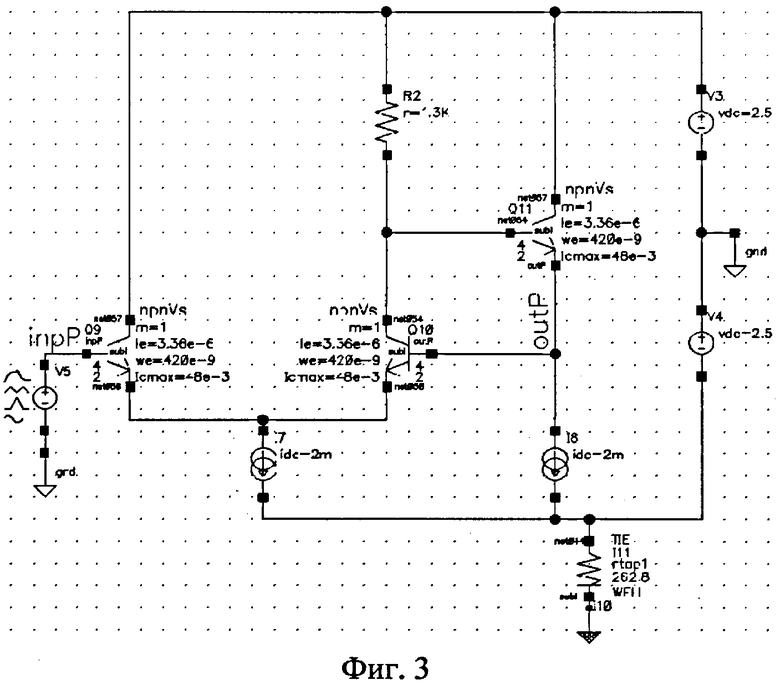

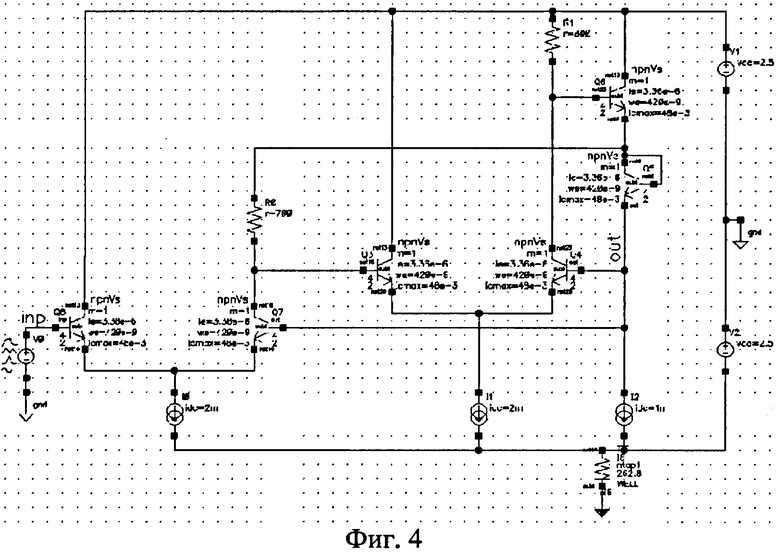

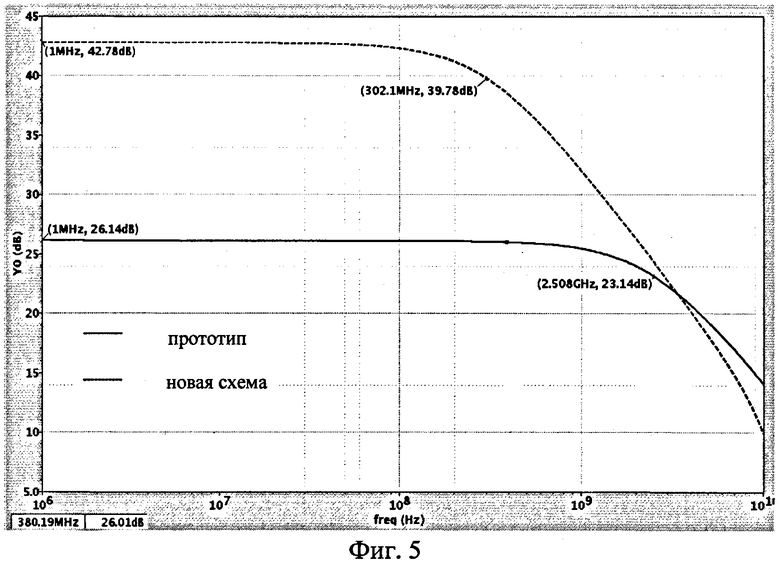

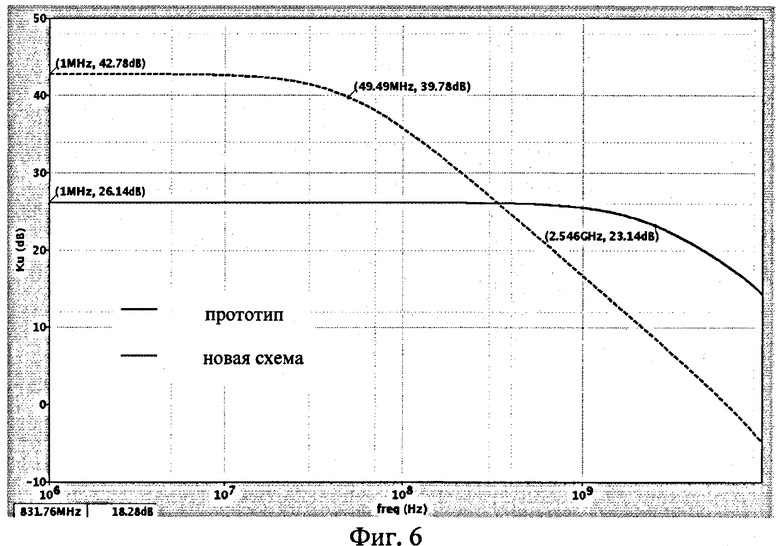

На фиг.3 - фиг.4 показаны схема ДУ-прототипа (фиг.3) и схема заявляемого ДУ (фиг.4) в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на фиг.5, фиг.6 - амплитудно-частотные характеристики коэффициента усиления по напряжению сравниваемых схем без коррекции (фиг.5) и с коррекцией (фиг.6). Данные графики показывают, что, несмотря на применение низкоомного двухполюсника нагрузки 5 (R5=800 Ом), коэффициент усиления по напряжению предлагаемого ДУ улучшается на порядок (21 дБ) в сравнении с Ку известного устройства, имеющего (фиг.5) R5=1,3 кОм. Это важное достоинство предлагаемого ДУ при его реализации в рамках технологического процесса SGB25VD.

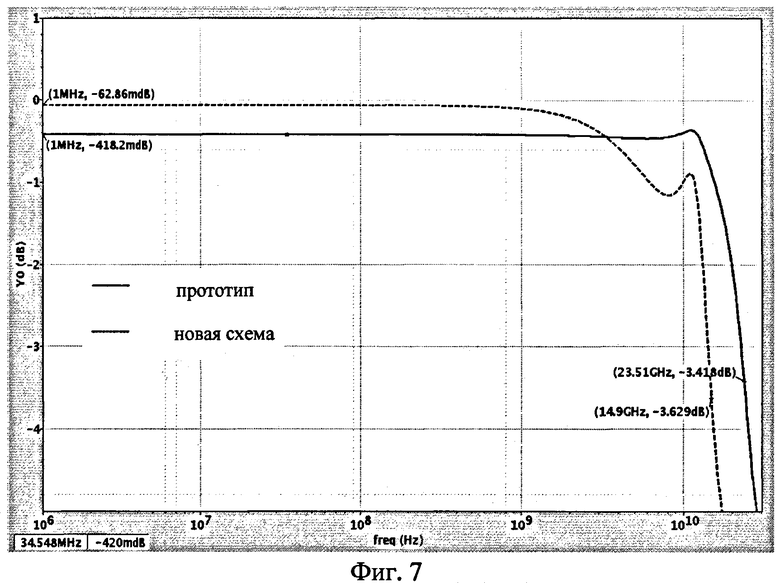

На фиг.7 приведены амплитудно-частотные характеристики сравниваемых схем (фиг.3 и фиг.4) при 100% отрицательной обратной связи. Из этих чертежей следует, что известный ДУ при 100% обратной связи имеет коэффициент передачи

Кп=-0,4 дБ, что обусловлено сравнительно небольшим его усилением в разомкнутом состоянии. В то же время предлагаемый ДУ при емкости коррекции (Скор=7 пФ) имеет верхнюю граничную частоту по уровню (-3 дБ) 14,9 ГГц.

Дифференциальный усилитель с повышенным коэффициентом усиления фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый выходной транзистор 4, база которого подключена к первому 2 токовому выходу входного дифференциального каскада 1 и первому выводу двухполюсника нагрузки 5, первый токостабилизирующий двухполюсник 6, связанный с эмиттером первого выходного транзистора 4, источник напряжения питания 7. В схему введены первый 8 и второй 9 дополнительные выходные транзисторы, эмиттер первого 8 дополнительного выходного транзистора соединен с эмиттером первого 4 выходного транзистора, коллектор первого 8 дополнительного выходного транзистора связан с источником напряжения питания 7 через первый дополнительный двухполюсник 10 и подключен к базе второго 9 дополнительного выходного транзистора, эмиттер второго 9 дополнительного выходного транзистора соединен со вторым выводом двухполюсника нагрузки 5 и через второй 11 дополнительный двухполюсник подключен к базе первого 8 дополнительного выходного транзистора и выходу устройства, причем коллектор второго 9 дополнительного выходного транзистора связан с источником напряжения питания 7.

На фиг.2, в соответствии с п.2 формулы изобретения, к выходу устройства подключен третий 12 дополнительный двухполюсник.

Кроме этого, на фиг.2, в соответствии с п.3 формулы изобретения, второй 3 токовый выход входного дифференциального каскада 1 соединен с базой первого 8 дополнительного выходного транзистора.

В соответствии с п.4 формулы изобретения, коллектор первого 4 выходного транзистора на фиг.2 соединен с эмиттером второго 9 дополнительного выходного транзистора.

В частном случае (фиг.2) входной дифференциальный каскад 1 выполнен на транзисторах 13, 14 и двухполюснике 15.

Рассмотрим работу предлагаемого устройства (фиг.2).

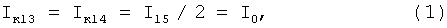

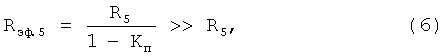

В статическом режиме коллекторные токи (Iкi) транзисторов 13 и 14, 4 и 8 устанавливаются двухполюсниками 15 и 6:

где  .

.

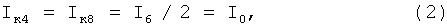

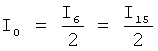

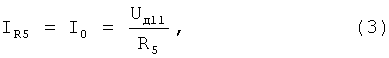

Через двухполюсник нагрузки 5 и первый 10 дополнительный двухполюсник протекают следующие статические токи

где Uд11≈0,7 В - напряжение на двухполюснике 11;

R5, R10 - сопротивления двухполюсников 5 и 10.

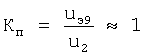

Определим коэффициент усиления по напряжению схемы фиг.2.

Если на вход Вх.(+)2 подается положительное напряжение uвх, то это вызывает увеличение коллекторного тока транзистора 14 и уменьшение коллекторного тока транзистора 13. Как следствие, напряжение на токовом выходе 2 u2 увеличивается. При этом приращение u2 сравнивается с напряжением uвых. Следует обратить внимание на то, что в заявляемой схеме вследствие ее структурных особенностей обеспечивается равенство переменных напряжений

где uэ9 - напряжение на эмиттере транзистора 9.

Таким образом, эффективное сопротивление двухполюсника нагрузки 5 существенно возрастает

где  .

.

Поэтому коэффициент усиления по напряжению предлагаемой схемы не зависит от сопротивления двухполюсника 5, который может быть достаточно низкоомным:

где rэ=φТ/Iэi - дифференциальные сопротивления эмиттерных переходов транзисторов 13 и 14;

φT=25 мВ - температурный потенциал;

Iэi - статический ток эмиттера транзисторов 13 и 14.

В результате предлагаемое схемотехническое решение улучшает (при одинаковых R5) Ky.max более, чем на порядок, причем это обеспечивается при использовании низкоомного резистора в качестве двухполюсника 5 (R5=700 Ом), а также при низковольтном напряжении питания (±2÷2,5 В).

Представленные на фиг.5, фиг.6 графики подтверждают данные теоретические выводы.

Дальнейшим развитием схемы фиг.2 является введение двухполюсника 12, который определяет напряжение на двухполюснике 11.

Кроме этого, подключение коллектора транзистора 4 и транзистора 14 в соответствии с п.3, п.4 формулы изобретения создает условия для дальнейшего увеличения Ку.max за счет уменьшения влияния на Ky.max внутренней обратной связи в транзисторах 4, 8 и 13, 14.

Таким образом, предлагаемое устройство имеет существенные преимущества по сравнению с известным по коэффициенту усиления по напряжению.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4.536.717 fig.1

2. Патент США №4.691.174 fig.1

3. Патент США №4.714.896 fig.3

4. Патент США №4.354.161 fig.4

5. Патент США №4.365.207 fig.1

6. Патент США №3.783.307 fig.1

7. Патент Японии JP 51-112253

8. Патент США №02072436 fig.2

9. Патент США №5.262.688

10. Патент Японии №54-102949 кл. 98(5) А21

11. Патент США №4.847.519 fig.2

12. Патент США №4.689.579

13. Патент США №6.396.346

14. Патентная заявка США №2006/0012432 fig.4A

15. Патент США №4.468.628

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2400924C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416147C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2011 |

|

RU2439783C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416146C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2413356C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439780C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2455756C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах, изготавливаемых по технологическому процессу SGB25VD). Технический результат: повышение в 8-10 раз коэффициента усиления по напряжению при выполнении двухполюсника нагрузки (5) в виде сравнительно низкоомного (600-800 Ом) резистора. Дифференциальный усилитель содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, первый выходной транзистор (Т) (4), база которого подключена к первому (2) токовому выходу ДК (1) и первому выводу двухполюсника нагрузки (5), первый токостабилизирующий двухполюсник (ТД) (6), связанный с эмиттером Т (4), источник напряжения питания (ИП) (7). В схему введены первый и второй дополнительные выходные Т (8), Т (9), эмиттер Т (8) соединен с эмиттером Т (4), коллектор которого связан с ИП (7) через первый дополнительный двухполюсник (10) и подключен к базе Т (9), эмиттер которого соединен со вторым выводом двухполюсника нагрузки (5) и через второй дополнительный двухполюсник (11) подключен к базе Т (8) и выходу устройства, причем коллектор Т (9) связан с ИП (7). 3 з.п. ф-лы, 7 ил.

1. Дифференциальный усилитель с повышенным коэффициентом усиления, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первый выходной транзистор (4), база которого подключена к первому (2) токовому выходу входного дифференциального каскада (1) и первому выводу двухполюсника нагрузки (5), выполненного в виде низкоомного резистора, первый токостабилизирующий двухполюсник (6), связанный с эмиттером первого выходного транзистора (4), источник напряжения питания (7), отличающийся тем, что в схему введены первый (8) и второй (9) дополнительные выходные транзисторы, эмиттер первого (8) дополнительного выходного транзистора соединен с эмиттером первого (4) выходного транзистора, коллектор первого (8) дополнительного выходного транзистора связан с источником напряжения питания (7) через первый дополнительный двухполюсник (10), через который протекает статический ток, и подключен к базе второго (9) дополнительного выходного транзистора, эмиттер второго (9) дополнительного выходного транзистора соединен со вторым выводом двухполюсника нагрузки (5), выполненного в виде низкоомного резистора, и через второй (11) дополнительный двухполюсник Uд11≈0,7В подключен к базе первого (8) дополнительного выходного транзистора и выходу устройства, причем коллектор второго (9) дополнительного выходного транзистора связан с источником напряжения питания (7).

2. Дифференциальный усилитель по п.1, отличающийся тем, что к выходу устройства подключен третий (12) дополнительный двухполюсник, определяющий напряжение на втором (11) дополнительном двухполюснике Uд11≈0,7В.

3. Дифференциальный усилитель по п.1, отличающийся тем, что второй (3) токовый выход входного дифференциального каскада (1) соединен с базой первого (8) дополнительного выходного транзистора.

4. Дифференциальный усилитель по п.1, отличающийся тем, что коллектор первого (4) выходного транзистора соединен с эмиттером второго (9) дополнительного выходного транзистора.

| US 4365207 A, 21.12.1982 | |||

| Дифференциальный усилитель | 1974 |

|

SU764099A1 |

| US 4714896 A, 22.12.1987 | |||

| US 4105942 A, 08.08.1978. | |||

Авторы

Даты

2011-06-10—Публикация

2009-10-29—Подача