Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах).

Известны схемы классических ВЧ и СВЧ дифференциальных усилителей (ДУ), в которых применяются цепи нейтрализации емкостей коллектор-база (Скб) входных транзисторов за счет введения вспомогательных транзисторов с аналогичными Скб и их «перекрестного» противофазного включения [1-9]. Применение таких схемотехнических решений расширяет в 4-5 раз диапазон рабочих частот ДУ за счет уменьшения эффективной входной емкости [9]. В качестве цепей нейтрализации используются емкости Скб как закрытых вспомогательных транзисторов [1, 8, 9], так и работающих в активном режиме [2, 6, 7].

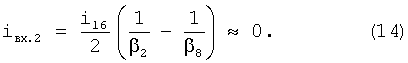

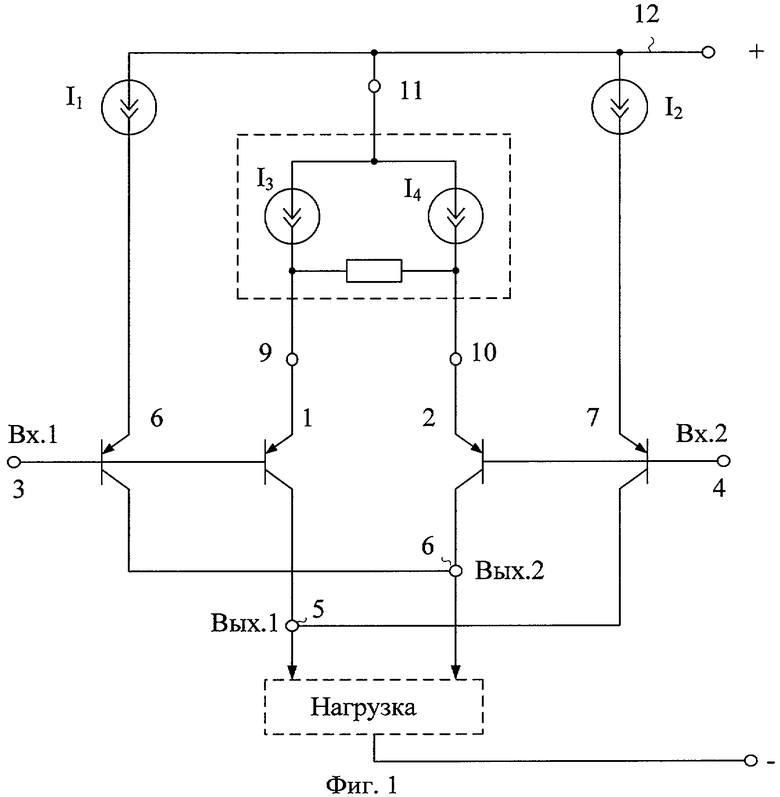

Наиболее близкой по технической сущности к заявляемому ДУ является схема фиг.1, представленная в патенте США №5.420.542 fig.4, которая также присутствует в патенте США №5.977.827.

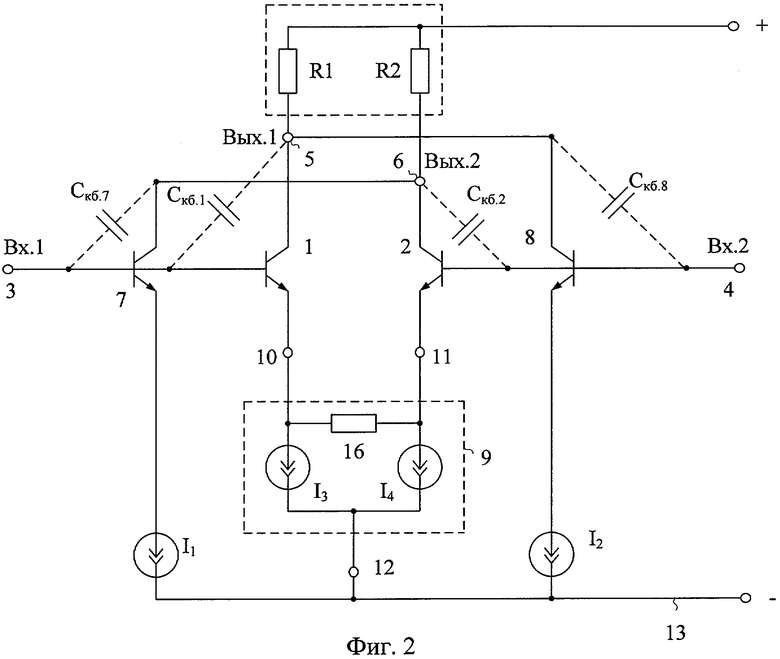

Схемы ДУ-прототипа при его реализации на р-n-р или на n-р-n транзисторах приведены соответственно на чертежах фиг.1 и фиг.2.

ДУ-прототип фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых соединены с первым 3 и вторым 4 входами дифференциального усилителя, а коллекторы связаны с первым 5 и вторым 6 токовыми выходами, первый 7 и второй 8 вспомогательные транзисторы, базы которых подключены к соответствующим базам первого 1 и второго 2 входных транзисторов, коллектор первого 7 вспомогательного транзистора подключен к коллектору второго 2 входного транзистора, коллектор второго 8 вспомогательного транзистора соединен с коллектором первого 1 входного транзистора, дифференциальную цепь 9 установления статического режима с первым 10 и вторым 11 выходами и общим выходом 12, связанным с шиной источника питания 13.

Существенный недостаток известного ДУ состоит в том, что он имеет сравнительно небольшое входное дифференциальное сопротивлением (Rвх) в диапазоне средних частот.

Основная задача предлагаемого изобретения состоит в увеличении на один-два порядка Rвх без ухудшения энергетических параметров в статическом режиме.

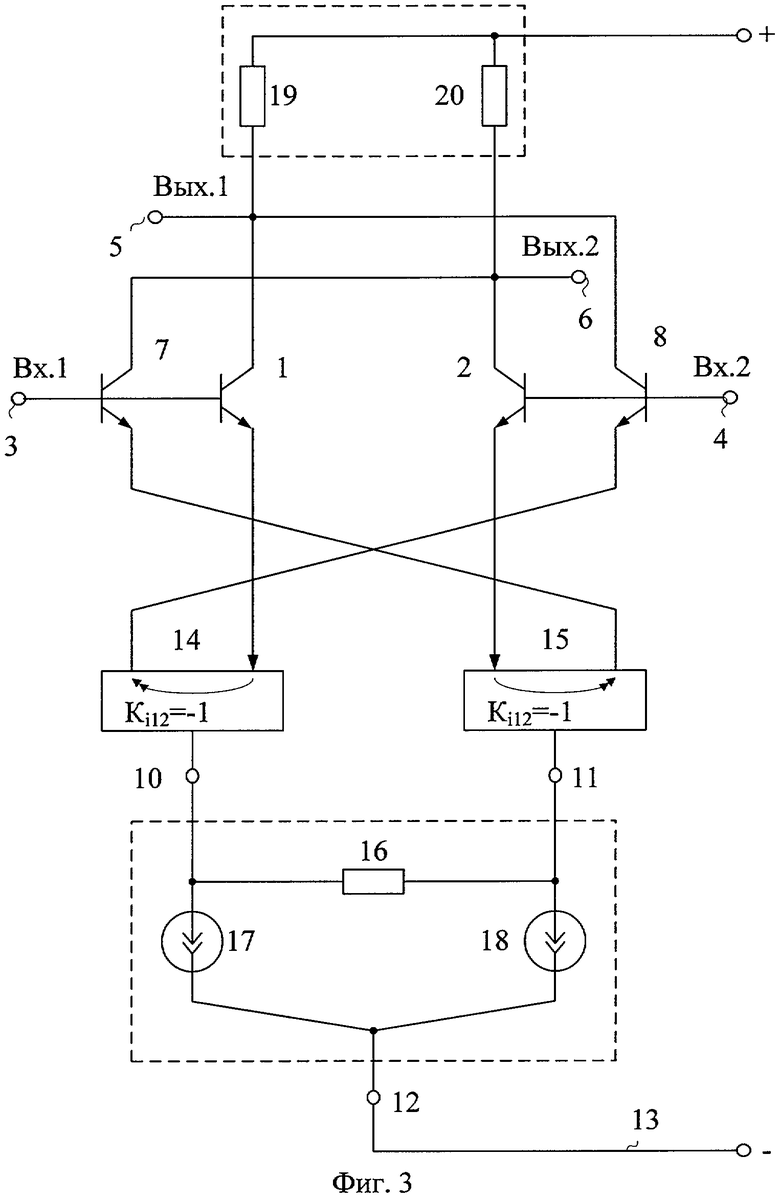

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых соединены с первым 3 и вторым 4 входами дифференциального усилителя, а коллекторы связаны с первым 5 и вторым 6 токовыми выходами, первый 7 и второй 8 вспомогательные транзисторы, базы которых подключены к соответствующим базам первого 1 и второго 2 входных транзисторов, коллектор первого 7 вспомогательного транзистора подключен к коллектору второго 2 входного транзистора, коллектор второго 8 вспомогательного транзистора соединен с коллектором первого 1 входного транзистора, дифференциальную цепь 9 установления статического режима с первым 10 и вторым 11 выходами и общим выходом 12, связанным с шиной источника питания 13, предусмотрены новые элементы и связи - в схему введены первое 14 и второе 15 токовые зеркала, вход первого 14 токового зеркала соединен с эмиттером первого 1 входного транзистора, вход второго 15 токового зеркала соединен с эмиттером второго 2 входного транзистора, выход первого 14 токового зеркала подключен к эмиттеру второго 8 вспомогательного транзистора, выход второго 15 токового зеркала связан с эмиттером первого 7 вспомогательного транзистора, эмиттерный выход первого 14 токового зеркала соединен с первым 10 выходом дифференциальной цепи 9 установления статического режима, эмиттерный выход второго 15 токового зеркала соединен со вторым 11 выходом дифференциальной цепи 9 установления статического режима.

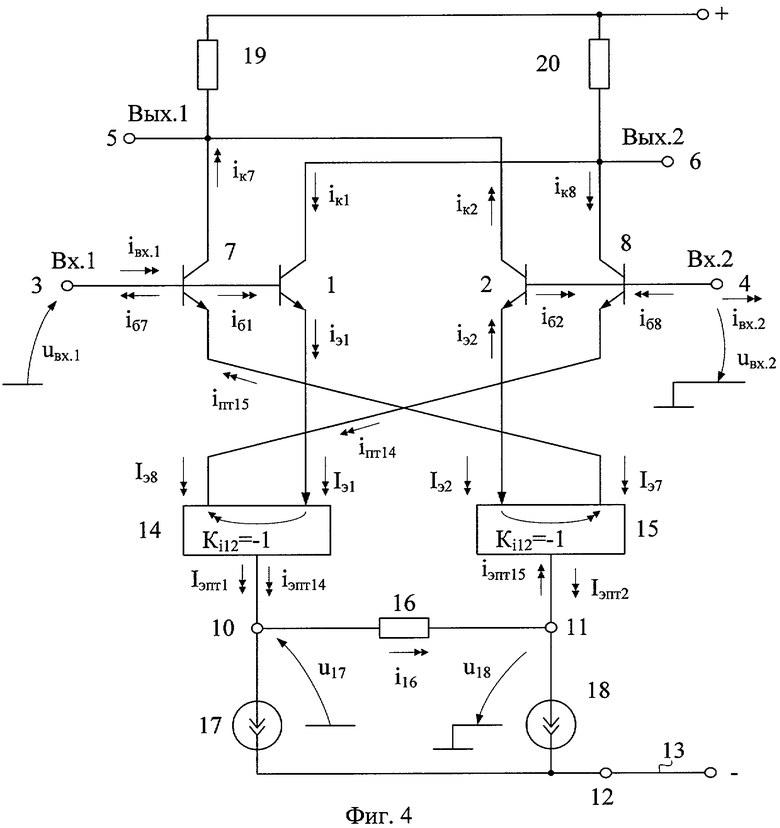

Схема заявляемого устройства, соответствующего формуле изобретения, показана на чертеже фиг.3. На чертеже фиг.4 показаны переменные токи и напряжения в схеме фиг.3.

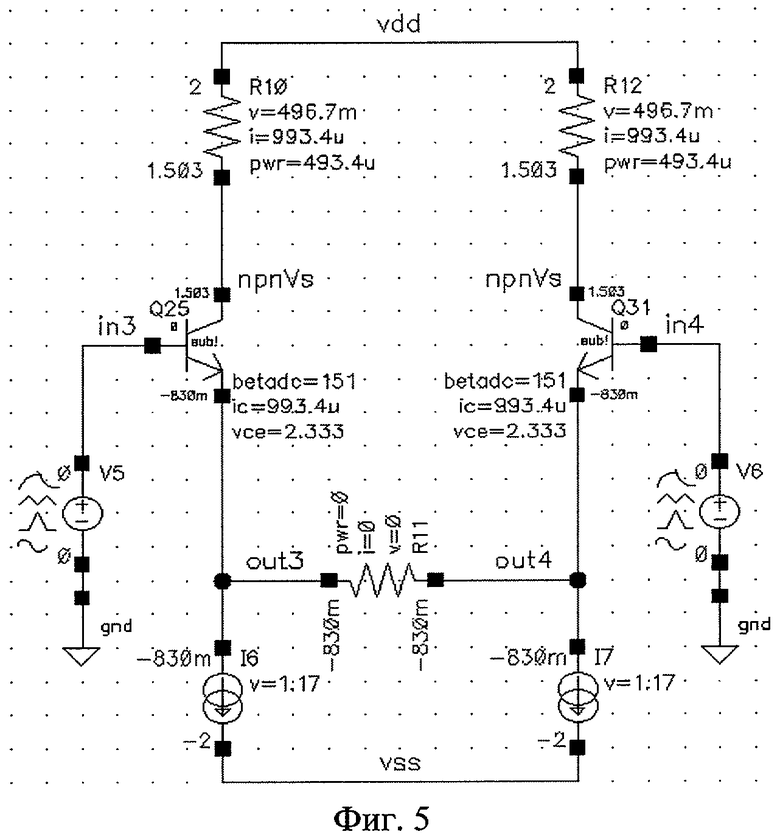

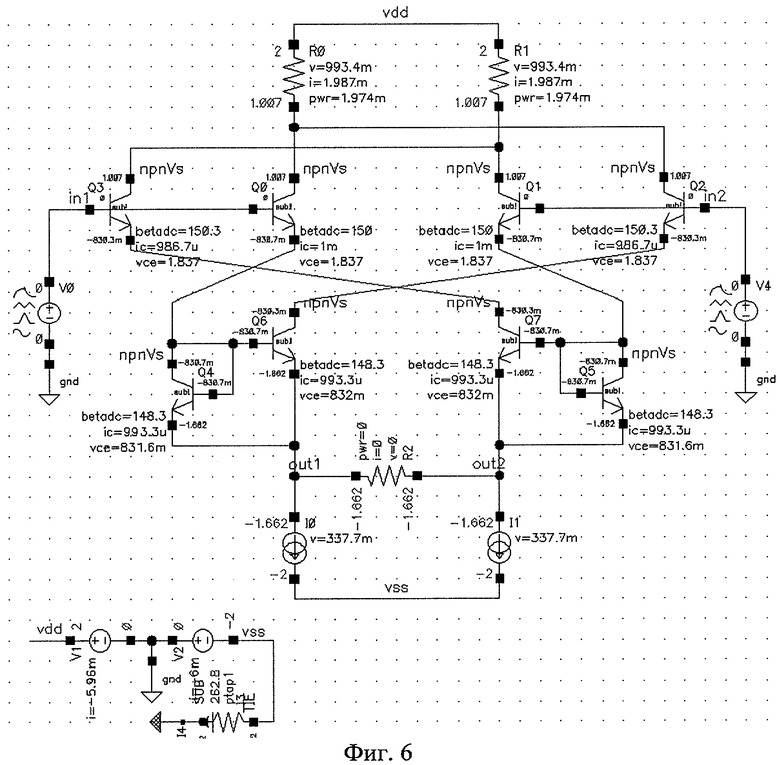

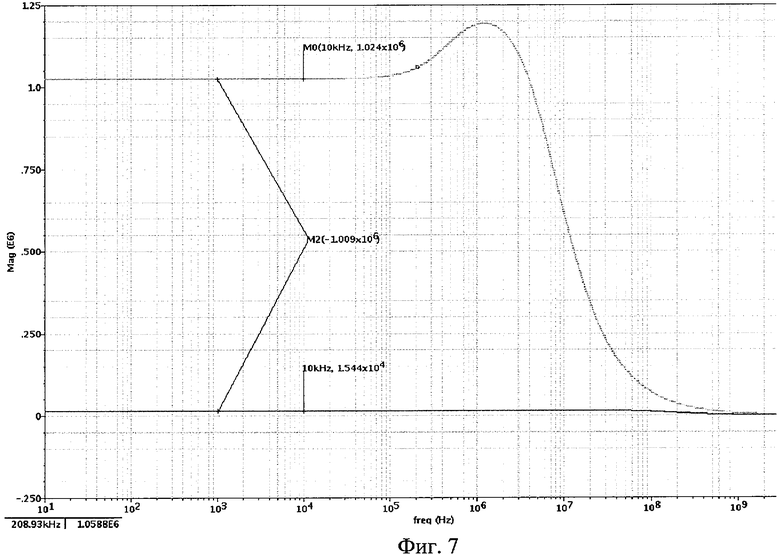

На чертежах фиг.5-фиг.6 показаны упрощенная схема ДУ-прототипа (фиг.5) и полная схема заявляемого ДУ (фиг.6) в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на чертеже фиг.7 - зависимость Rвх сравниваемых схем (фиг.5, фиг.6) от частоты.

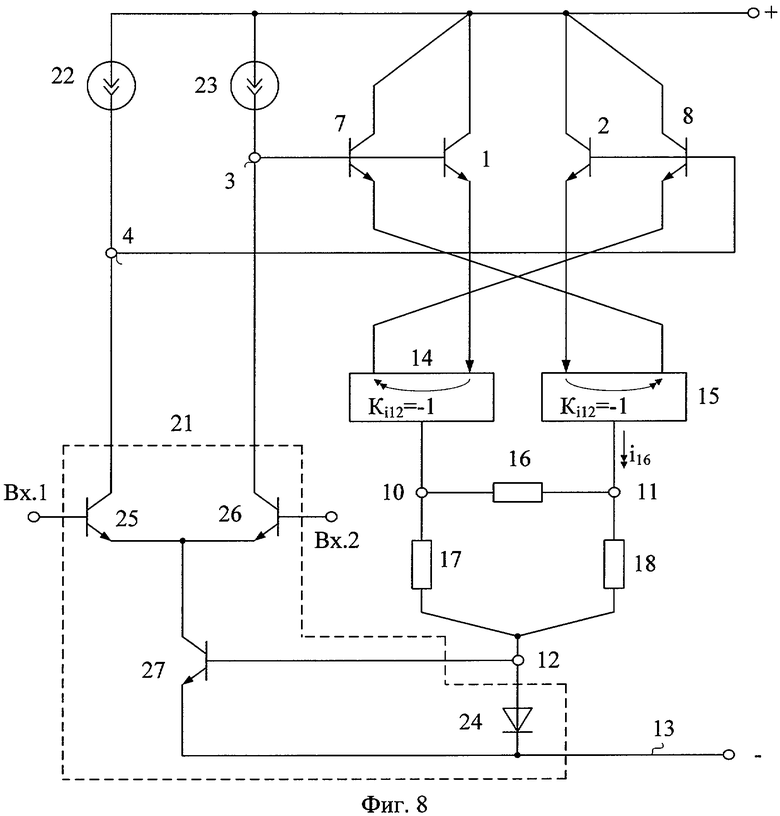

На чертеже фиг.8 приведена схема операционного усилителя, в котором выходной каскад реализован на основе заявляемого устройства фиг.3. Это позволяет оценить эффективность его применения в практических схемах по выигрышу в коэффициенте усиления по напряжению (Ку).

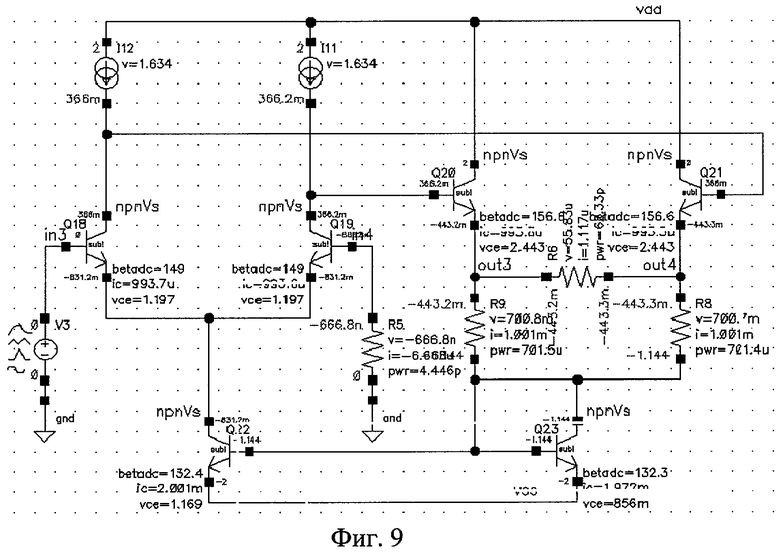

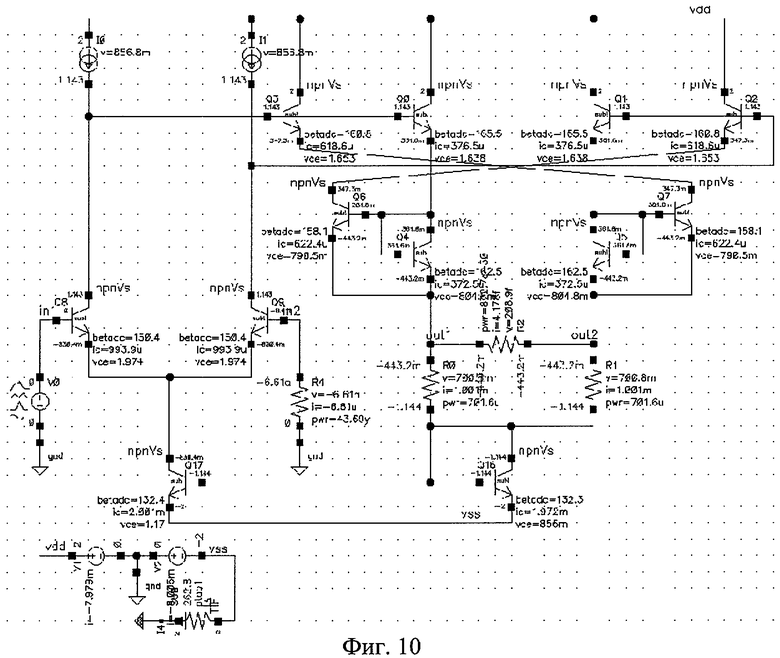

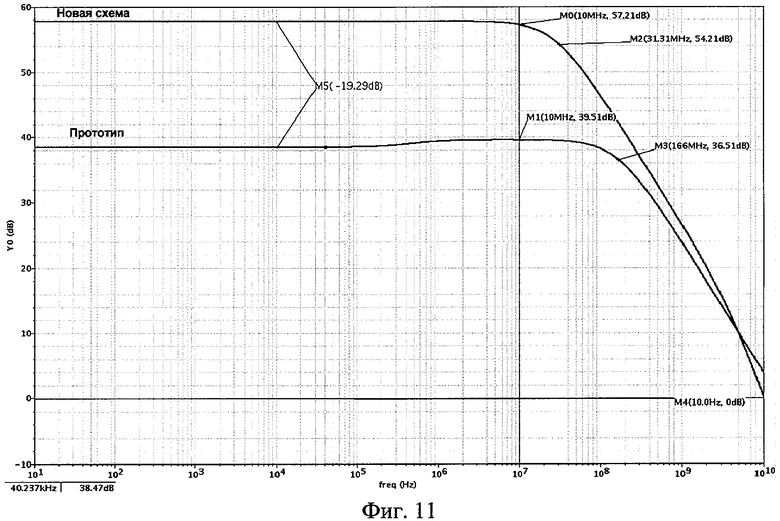

На чертежах фиг.9 и фиг.10 показаны схемы операционных усилителей с классическим выходным каскадом (фиг.9) и с выходным каскадом на базе заявляемого ДУ (фиг.10) в среде компьютерного моделирования Cadence на моделях интегральных СВЧ-транзисторов IHP для случая, когда в ДУ используется симметричное включение низкоомной нагрузки (50 Ом), а на чертеже фиг.11 - зависимость Ку сравниваемых схем (фиг.9, фиг.10) от частоты. Графики фиг.11 показывают, что предлагаемое устройство имеет в 9-10 раз больший коэффициент усиления по напряжению (≈20 дБ). Это важное достоинство предлагаемого ДУ при его реализации в рамках технологического процесса SGB25VD.

Дифференциальный усилитель фиг.3 содержит первый 1 и второй 2 входные транзисторы, базы которых соединены с первым 3 и вторым 4 входами дифференциального усилителя, а коллекторы связаны с первым 5 и вторым 6 токовыми выходами, первый 7 и второй 8 вспомогательные транзисторы, базы которых подключены к соответствующим базам первого 1 и второго 2 входных транзисторов, коллектор первого 7 вспомогательного транзистора подключен к коллектору второго 2 входного транзистора, коллектор второго 8 вспомогательного транзистора соединен с коллектором первого 1 входного транзистора, дифференциальную цепь 9 установления статического режима с первым 10 и вторым 11 выходами и общим выходом 12, связанным с шиной источника питания 13. В схему введены первое 14 и второе 15 токовые зеркала, вход первого 14 токового зеркала соединен с эмиттером первого 1 входного транзистора, вход второго 15 токового зеркала соединен с эмиттером второго 2 входного транзистора, выход первого 14 токового зеркала подключен к эмиттеру второго 8 вспомогательного транзистора, выход второго 15 токового зеркала связан с эмиттером первого 7 вспомогательного транзистора, эмиттерный выход первого 14 токового зеркала соединен с первым 10 выходом дифференциальной цепи 9 установления статического режима, эмиттерный выход второго 15 токового зеркала соединен со вторым 11 выходом дифференциальной цепи 9 установления статического режима.

В качестве токовых зеркал 14 и 15 могут использоваться известные схемотехнические решения, в том числе показанные на чертежах фиг.6 и фиг.10.

В частном случае дифференциальная цепь установления статического режима 9 в схеме фиг.3 реализована на резисторе 16 и двухполюсниках 17, 18, а цепь нагрузки - на резисторах 19 и 20.

Операционный усилитель с заявляемым ДУ в выходном каскаде (фиг.8) содержит входной каскад 21 с токостабилизирующими двухполюсниками 22, 23 в его коллекторной цепи. Статический режим транзисторов 25 и 26 входного каскада 21 устанавливается транзистором 27, обеспечивающим введение через двухполюсник 24 отрицательной обратной связи по синфазному сигналу.

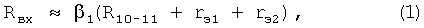

Входное сопротивление ДУ-прототипа фиг.2 определяется по формуле

где β1 - коэффициент усиления по току базы транзистора 1;

R10-11 - эквивалентное сопротивление между выходами 10 и 11 дифференциальной цепи 9 установления статического режима;

rэ1, rэ2 - дифференциальные сопротивления эмиттерных переходов транзисторов 1 и 2.

При малых R10-11≈50 Ом входное сопротивление ДУ фиг.2 получается небольшим.

Рассмотрим работу предлагаемого устройства фиг.4.

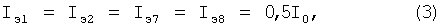

Статический режим по току транзисторов ДУ фиг.4 при коэффициентах передачи по току токовых зеркал 14 и 15 Кil2=-1 устанавливается двухполюсниками 17 и 18 на следующем уровне:

где Iэi - статический эмиттерный ток i-го транзистора;

I0 - статический ток двухполюсников 17 и 18.

Сравнительно низкоомные резисторы нагрузки 19 и 20 определяют статический режим по напряжению коллектор-база транзисторов 1 и 2, 7 и 8.

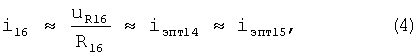

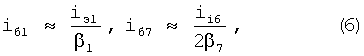

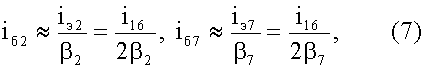

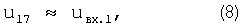

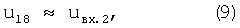

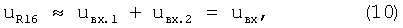

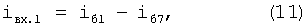

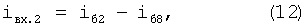

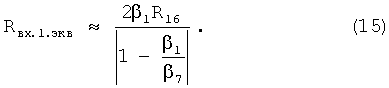

Если на входы ДУ фиг.4 подается дифференциальное напряжение uвх=uвx.1+uвx.2, то это приводит к изменениям напряжений u17 и u18 на выходах 10 и 11, появлению тока i16 в двухполюснике 16 и токов базы транзисторов 1 и 2, 7 и 8:

где βi - коэффициент усиления по току базы i-го транзистора;

iэj - ток эмиттера j-го транзистора.

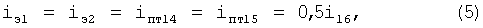

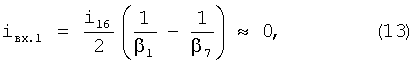

Поэтому суммарное приращение входных токов ДУ iвx.1 и iвx.2:

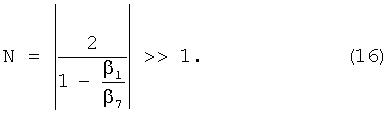

При β7=β1, β2=β8 получаем, что во входной цепи ДУ фиг.4 обеспечивается компенсация близких по величине переменных токов, обусловленных токами базы транзисторов 1 и 7, 2 и 8, что существенно повышает эквивалентное сопротивление по входу 3(4):

Следовательно, с учетом (1) Rвх.экв повышается в Nраз, где

В практической схеме фиг.6 выигрыш по Rвх достигает одного порядка (фиг.7). Предлагаемая схема может быть реализована в рамках низковольтного техпроцесса SGB25VD, внедряемого российскими предприятиями.

Таким образом, заявляемый дифференциальный усилитель имеет повышенное Rвх, а также реализуется на основе техпроцесса SGB25VD, в котором нет р-n-р транзисторов.

Литература

1. Патент США №6.198.348.

2. Патент США №6.690.231, фиг.6.

3. Патент США №6.396.346.

4. Патентная заявка США №2008/0012640, fig.4.

5. Патент США №6.624.699.

6. Патент США №5.420.542, fig.4.

7. Патент США №5.977.827, fig.4.

8. Патентная заявка США №2006/0125561А1, fig.1.

9. Devices Ingineering Inc: 700 series 20 V bipolar array family. DS-mw-01700-01 Rev В 7/14/03, 2003, admin@deiaz.com, pp.5-17, fig. E2.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450423C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2396699C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2396698C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401507C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2393628C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421885C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419186C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах). Технический результат: увеличение на один-два порядка Rвх без ухудшения энергетических параметров в статическом режиме. Дифференциальный усилитель (ДУ) с повышенным входным сопротивлением содержит первый и второй входные транзисторы (Т) (1, 2), базы которых соединены с первым и вторым входами (3, 4) ДУ, а коллекторы связаны с первым и вторым токовыми выходами (5, 6), первый и второй вспомогательные Т (7, 8), базы которых подключены к соответствующим базам первого и второго Т (1, 2), коллектор первого Т (7) подключен к коллектору второго Т (2), коллектор второго Т (8) соединен с коллектором первого Т (1), дифференциальную цепь (ДЦ) установления статического режима с первым и вторым выходами (10, 11) и общим выходом (12), связанным с шиной (13) источника питания. В схему введены первое и второе токовые зеркала (ТЗ) (14, 15), вход ТЗ (14) соединен с эмиттером Т (1), вход ТЗ (15) соединен с эмиттером Т (2), выход ТЗ (14) подключен к эмиттеру Т (8), выход ТЗ (15) связан с эмиттером Т (7), эмиттерный выход первого ТЗ (14) соединен с первым выходом (10) ДЦ, эмиттерный выход ТЗ (15) соединен со вторым выходом (11) ДЦ. 11 ил.

Дифференциальный усилитель с повышенным входным сопротивлением, содержащий первый и второй входные транзисторы, базы которых соединены с первым и вторым входами дифференциального усилителя, а коллекторы связаны с первым и вторым токовыми выходами, первый и второй вспомогательные транзисторы, базы которых подключены к соответствующим базам первого и второго входных транзисторов, коллектор первого вспомогательного транзистора подключен к коллектору второго входного транзистора, коллектор второго вспомогательного транзистора соединен с коллектором первого входного транзистора, дифференциальную цепь установления статического режима с первым и вторым выходами и общим выходом, связанным с шиной источника питания, отличающийся тем, что в схему введены первое и второе токовые зеркала, вход первого токового зеркала соединен с эмиттером первого входного транзистора, вход второго токового зеркала соединен с эмиттером второго входного транзистора, выход первого токового зеркала подключен к эмиттеру второго вспомогательного транзистора, выход второго токового зеркала связан с эмиттером первого вспомогательного транзистора, эмиттерный выход первого токового зеркала соединен с первым выходом дифференциальной цепи установления статического режима, эмиттерный выход второго токового зеркала соединен со вторым выходом дифференциальной цепи установления статического режима.

| US 5420542 A, 30.05.1995 | |||

| Дифференциальный усилитель | 1985 |

|

SU1385255A1 |

| Двухтактный усилитель | 1985 |

|

SU1327274A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

Авторы

Даты

2011-02-27—Публикация

2009-10-19—Подача