Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ) с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры).

В современной радиоэлектронной аппаратуре находят применение операционные усилители с существенными различными параметрами. Особое место занимают ОУ с простейшей архитектурой, содержащие небольшое число элементов. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу устройств.

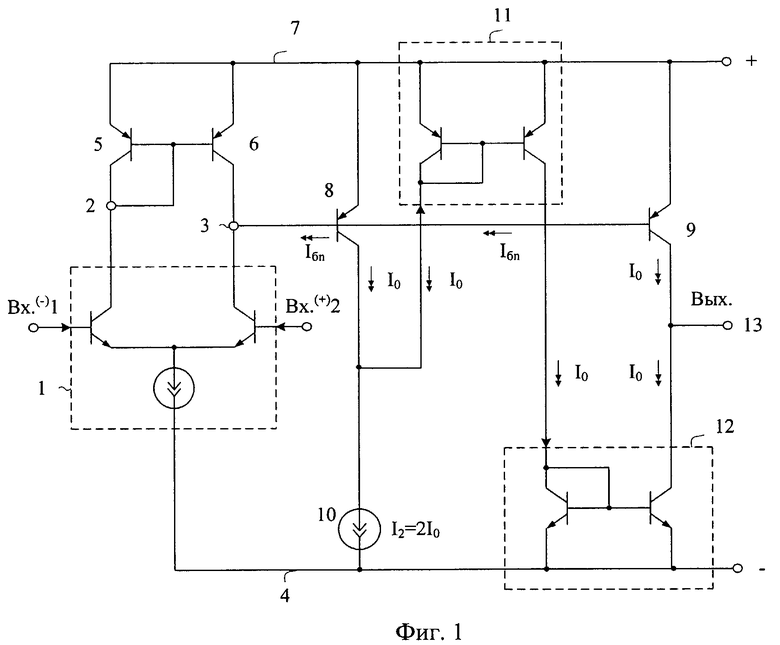

Наиболее близкой по технической сущности к заявляемому ДУ является классическая схема фиг.1 по патенту US 6549072, fig.2, на основе которой реализованы как отечественные (140УД8, 574УД1, 140УД30), так и зарубежные (TL081) микросхемы. Данная схема стала основой построения большого числа аналоговых устройств, например [1-8].

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет повышенное значение напряжения смещения нуля (Uсм).

Основная цель предлагаемого изобретения состоит в уменьшении Uсм.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, эмиттерная цепь которого соединена с первой 4 шиной источников питания, первый 5 и второй 6 транзисторы активной нагрузки, эмиттеры которых связаны со второй 7 шиной источников питания, коллектор первого 5 транзистора активной нагрузки соединен с базой этого же транзистора, а также базой второго 6 транзистора активной нагрузки и подключен ко второму 2 токовому выходу входного дифференциального каскада 1, коллектор второго 6 транзистора активной нагрузки соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и базами первого 8 и второго 9 выходных транзисторов, эмиттеры которых связаны со второй 7 шиной источников питания, первый токостабилизирующий двухполюсник 10, связанный первым выводом с коллектором первого 8 выходного транзистора, а вторым выводом с первой 4 шиной источника питания, первое 11 токовое зеркало, общий эмиттерный выход которого подключен ко второй 7 шине источников питания, выход соединен со входом второго 12 токового зеркала, причем выход второго 12 токового зеркала соединен с коллектором второго 9 выходного транзистора и выходом устройства 13, а общий эмиттерный выход этого токового зеркала соединен с первой 4 шиной источников питания, предусмотрены новые связи - в схему введен дополнительный транзистор 14, коллектор которого соединен со входом первого 11 токового зеркала, эмиттер подключен к первому выводу первого 10 токостабилизирующего двухполюсника, а база соединена с цепью установления статического режима 15.

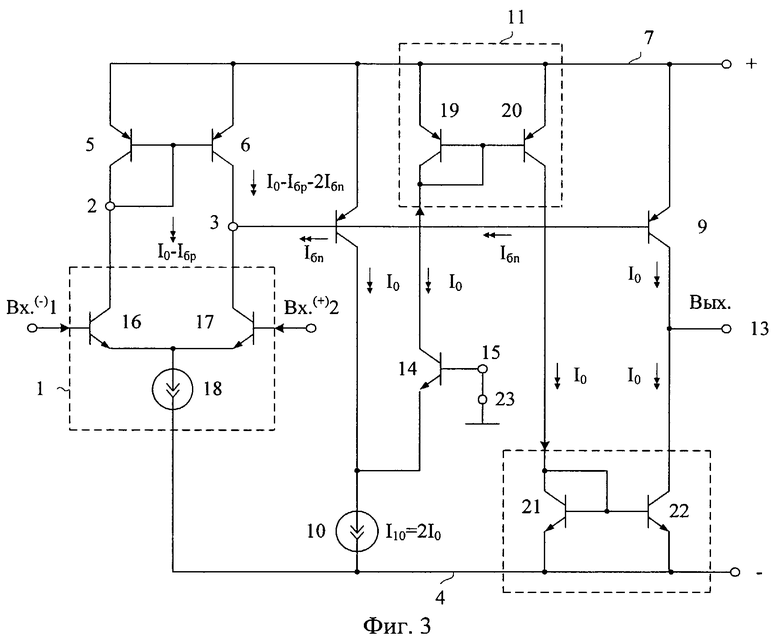

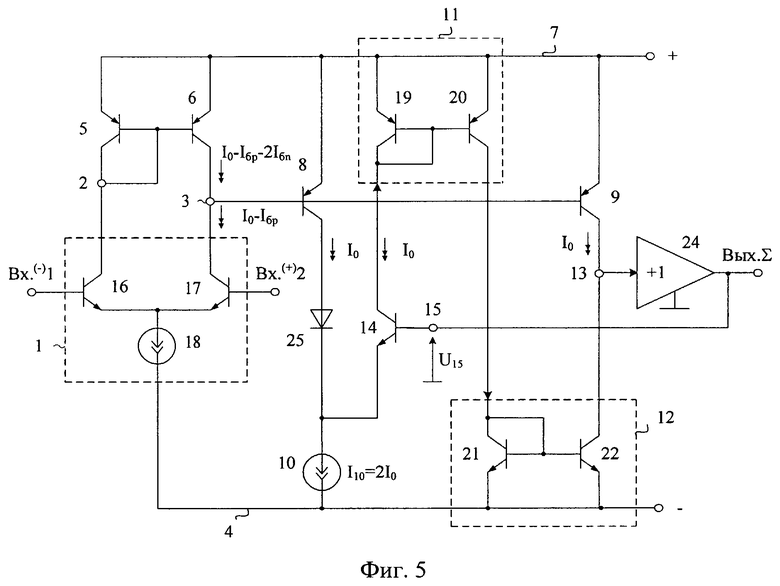

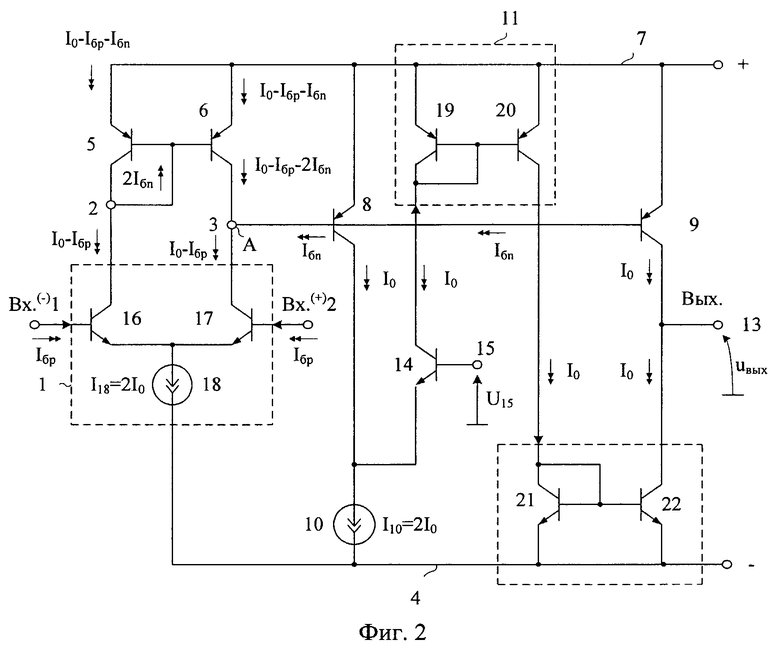

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения. На фиг.3 представлена схема ДУ в соответствии с п.2 формулы изобретения. На фиг.4 приведена схема ДУ в соответствии с п.3 и п.5, а на фиг.5 - то же, в соответствии с п.4 и п.5 формулы изобретения.

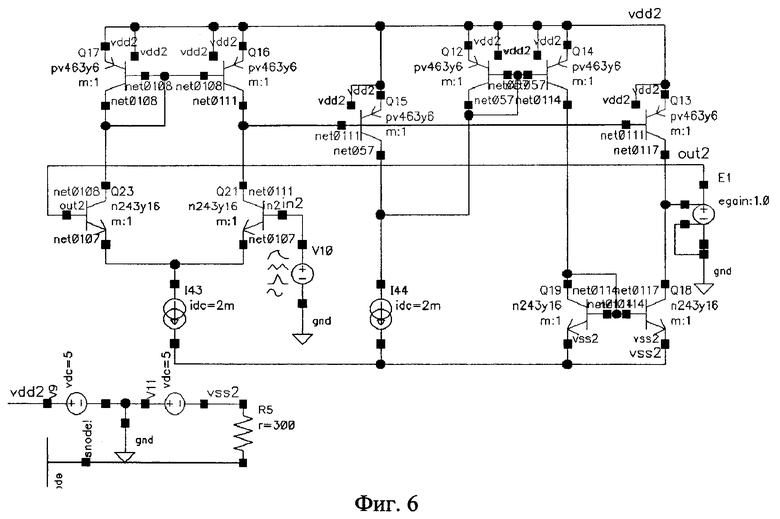

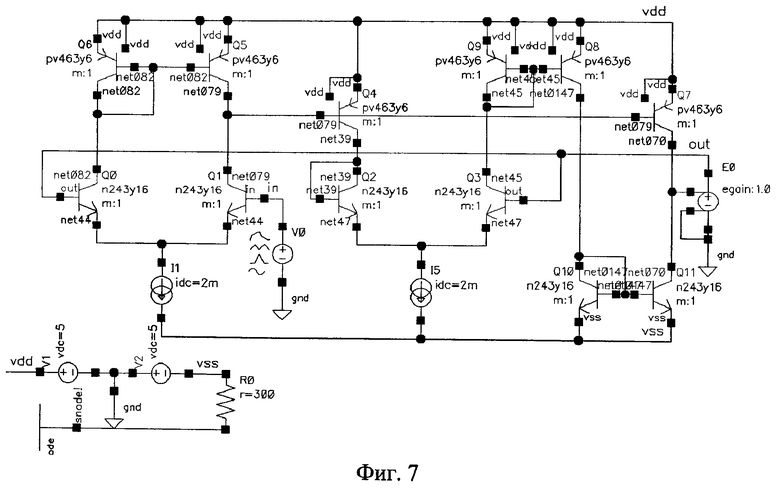

На фиг.6 показана схема ДУ-прототипа фиг.1 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.7 - схема заявляемого ДУ фиг.2.

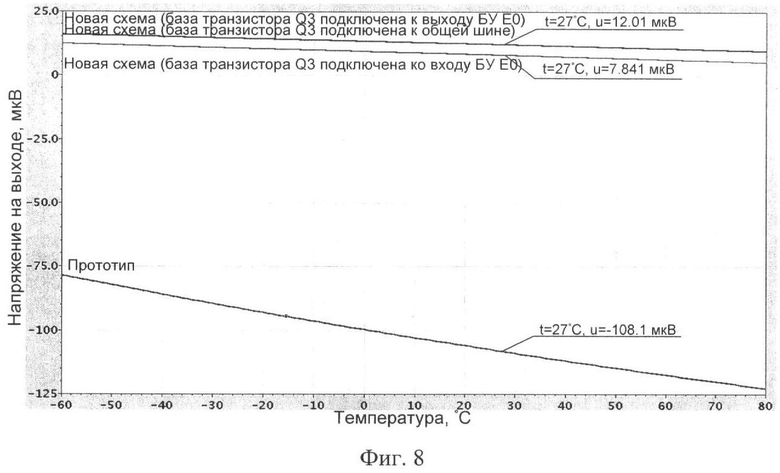

На фиг.8 представлены графики температурной зависимости Uсм сравниваемых схем фиг.6 и фиг.7.

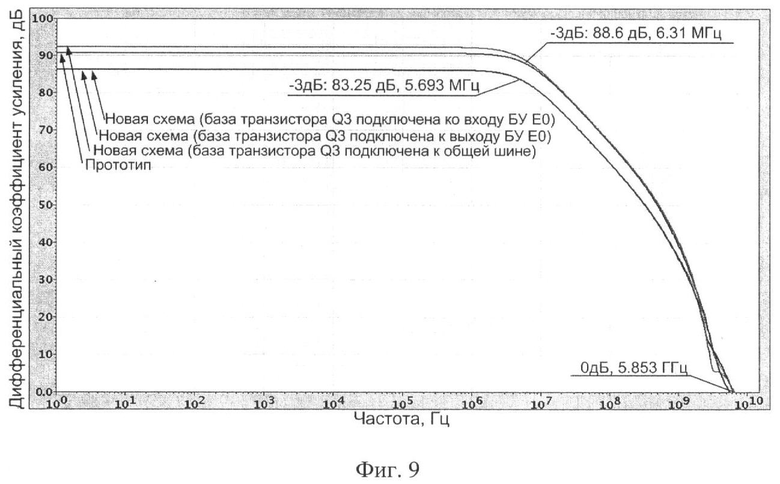

На фиг.9 приведены графики амплитудно-частотных характеристик сравниваемых схем фиг.6 и фиг.7.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, эмиттерная цепь которого соединена с первой 4 шиной источников питания, первый 5 и второй 6 транзисторы активной нагрузки, эмиттеры которых связаны со второй 7 шиной источников питания, коллектор первого 5 транзистора активной нагрузки соединен с базой этого же транзистора, а также базой второго 6 транзистора активной нагрузки и подключен ко второму 2 токовому выходу входного дифференциального каскада 1, коллектор второго 6 транзистора активной нагрузки соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и базами первого 8 и второго 9 выходных транзисторов, эмиттеры которых связаны со второй 7 шиной источников питания, первый токостабилизирующий двухполюсник 10, связанный первым выводом с коллектором первого 8 выходного транзистора, а вторым выводом с первой 4 шиной источника питания, первое 11 токовое зеркало, общий эмиттерный выход которого подключен ко второй 7 шине источников питания, выход соединен со входом второго 12 токового зеркала, причем выход второго 12 токового зеркала соединен с коллектором второго 9 выходного транзистора и выходом устройства 13, а общий эмиттерный выход этого токового зеркала соединен с первой 4 шиной источников питания. В схему введен дополнительный транзистор 14, коллектор которого соединен со входом первого 11 токового зеркала, эмиттер подключен к первому выводу первого 10 токостабилизирующего двухполюсника, а база соединена с цепью установления статического режима 15.

На фиг.3, в соответствии с п.2 формулы изобретения, в качестве цепи установления статического режима 15 используется общая шина 23 источников питания 7 и 4.

На фиг.4, в соответствии с п.3 и п.5 формулы изобретения, в качестве цепи установления статического режима 15 используется выход устройства 13.

На фиг.5, в соответствии с п.4 и п.5 формулы изобретения, в качестве цепи установления статического режима 15 используется выход дополнительного буферного усилителя 24, вход которого соединен с выходом устройства 13.

На фиг.4 и фиг.5, в соответствии с п.5 формулы изобретения, первый вывод первого 10 токостабилизирующего двухполюсника связан с коллектором первого 8 выходного транзистора через дополнительный р-n переход 25.

Рассмотрим работу схемы фиг.2 на постоянном токе.

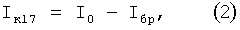

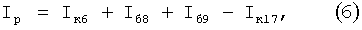

Если принять, что ток общей эмиттерной цепи входного дифференциального каскада 1 на транзисторах 16 и 17 равен 2I0, то токи коллекторов этих транзисторов:

где Iбр - ток базы входных р-n-р транзисторов 16 и 17, образующих входной дифференциальный каскад 1.

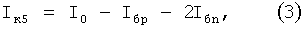

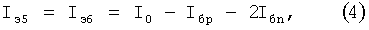

С учетом первого закона Кирхгофа можно найти ток коллектора и ток эмиттера транзистора 5, а также ток коллектора транзистора 6

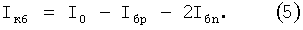

Поэтому сумма токов в узле «А» при I10=2I0

где Iб8=Iб9=Iбn - токи базы транзисторов 8 и 9.

Учитывая (1)-(5), из (6) следует, что сумма токов в узле «А» ДУ фиг.2 при его коротком замыкании на эквипотенциальную общую шину равна нулю, т.е. Ip=0.

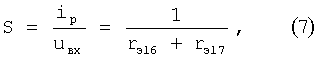

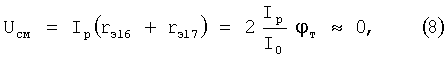

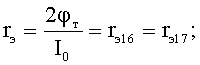

Вследствие воздействия, например радиации, базы р-n-р транзисторов изменяются в несколько раз, но одинаково. В этом случае Iр≈0. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного напряжения uвх ДУ фиг.2 в выходной ток узла «А»

где rэ16=rэ17 - сопротивления эмиттерных переходов входных транзисторов дифференциального каскада 1.

Поэтому для схем фиг.2

где

φт=26 мВ - температурный потенциал.

Как следствие, систематическая составляющая Uсм получается почти на порядок меньше (фиг.8, Uсм=7,8 мкВ), чем в известной схеме (Uсм=-108,1 мкВ).

Кроме этого, снижение Uсм обеспечивается в схеме фиг.2 за счет минимизации влияния напряжений коллектор-база транзисторов 8 и 9 на величину их коэффициента усиления по току базы β. В этой схеме транзисторы 8 и 9 будут работать при одинаковых напряжениях на коллекторе, что обеспечивает равенство β8=β9 и, следовательно, более точную взаимную компенсацию токов базы Iбn транзисторов 5, 6, 8, 9 в узле «А».

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4042886.

2. Патент Японии JP 10032437.

3. Патент Японии JP 2005033558.

4. Патент США №4595883, fig.4.

5. Патентная заявка США №2005/0063270 А1, fig.2.

6. Патент США №5166638, fig.1.

7. Патент США №5537081, fig.3.

8. Патент США №6114904.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412539C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412537C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412538C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412533C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ И ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2010 |

|

RU2426221C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412535C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2008 |

|

RU2346387C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412532C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ) с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры). Технический результат: уменьшение Uсм. Дифференциальный усилитель содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, эмиттерная цепь которого соединена с первой (4) шиной источников питания, первый (5) и второй (6) транзисторы активной нагрузки, эмиттеры которых связаны со второй (7) шиной источников питания, коллектор первого (5) транзистора активной нагрузки соединен с базой этого же транзистора, а также базой второго (6) транзистора активной нагрузки и подключен ко второму (2) токовому выходу входного дифференциального каскада (1), коллектор второго (6) транзистора активной нагрузки соединен со вторым (3) токовым выходом входного дифференциального каскада (1) и базами первого (8) и второго (9) выходных транзисторов, эмиттеры которых связаны со второй (7) шиной источников питания, первый токостабилизирующий двухполюсник (10), связанный первым выводом с коллектором первого (8) выходного транзистора, а вторым выводом с первой (4) шиной источника питания, первое (11) токовое зеркало, общий эмиттерный выход которого подключен ко второй (7) шине источников питания, выход соединен со входом второго (12) токового зеркала, причем выход второго (12) токового зеркала соединен с коллектором второго (9) выходного транзистора и выходом устройства (13), а общий эмиттерный выход этого токового зеркала соединен с первой (4) шиной источников питания. В схему введен дополнительный транзистор (14), коллектор которого соединен со входом первого (11) токового зеркала, эмиттер подключен к первому выводу первого (10) токостабилизирующего двухполюсника, а база соединена с цепью установления статического режима (15). 4 з.п. ф-лы, 9 ил.

1. Дифференциальный усилитель с малым напряжением смещения нуля, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, эмиттерная цепь которого соединена с первой (4) шиной источников питания, первый (5) и второй (6) транзисторы активной нагрузки, эмиттеры которых связаны со второй (7) шиной источников питания, коллектор первого (5) транзистора активной нагрузки соединен с базой этого же транзистора, а также базой второго (6) транзистора активной нагрузки и подключен ко второму (2) токовому выходу входного дифференциального каскада (1), коллектор второго (6) транзистора активной нагрузки соединен со вторым (3) токовым выходом входного дифференциального каскада (1) и базами первого (8) и второго (9) выходных транзисторов, эмиттеры которых связаны со второй (7) шиной источников питания, первый токостабилизирующий двухполюсник (10), связанный первым выводом с коллектором первого (8) выходного транзистора, а вторым выводом с первой (4) шиной источника питания, первое (11) токовое зеркало, общий эмиттерный выход которого подключен ко второй (7) шине источников питания, выход соединен со входом второго (12) токового зеркала, причем выход второго (12) токового зеркала соединен с коллектором второго (9) выходного транзистора и выходом устройства (13), а общий эмиттерный выход этого токового зеркала соединен с первой (4) шиной источников питания, отличающийся тем, что в схему введен дополнительный транзистор (14), коллектор которого соединен со входом первого (11) токового зеркала, эмиттер подключен к первому выводу первого (10) токостабилизирующего двухполюсника, а база соединена с цепью установления статического режима (15).

2. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве цепи установления статического режима (15) используется общая шина (23) источников питания.

3. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве цепи установления статического режима (15) используется выход устройства (13).

4. Дифференциальный усилитель по п.1, отличающийся тем, что в качестве цепи установления статического режима (15) используется выход дополнительного буферного усилителя (24), вход которого соединен с выходом устройства (13).

5. Дифференциальный усилитель по п.1, отличающийся тем, что первый вывод первого (10) токостабилизирующего двухполюсника связан с коллектором первого (8) выходного транзистора через дополнительный p-n переход (25).

| US 6549072 B1, 15.04.2003 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 0 |

|

SU361605A1 |

| US 5166636 A, 24.11.1992 | |||

| US 4418290 A, 29.11.1983. | |||

Авторы

Даты

2011-06-20—Публикация

2010-05-11—Подача