Настоящая заявка испрашивает приоритет предварительной заявки на патент США № 60/883715, названной "OPTIONAL RATE-1/3 CODE BASED ON AT CAPABILITY", поданной 5 января 2007, переданной заявителю настоящей заявки и включенной здесь по ссылке.

Область техники

Настоящая заявка относится в целом к связи, более конкретно к способам для кодирования и декодирования данных.

Уровень техники

В системе связи передатчик может закодировать пакет данных, чтобы получить биты кода, перемежать или переупорядочивать биты кода и преобразовать перемеженные биты в символы модуляции. Передатчик может затем обработать и передать символы модуляции через канал связи. Канал связи может исказить передачу данных с конкретным ответом канала и дополнительно ухудшить передачу данных посредством шума и помех. Приемник может получить принятые символы, которые могут быть искажены, и ухудшенные версии переданных символов модуляции и может обработать принятые символы, чтобы восстановить переданный пакет.

Кодирование посредством передатчика может позволить приемнику надежно восстанавливать переданный пакет на основании ухудшенных принятых символов. Передатчик может выполнить кодирование на основании кода с прямым исправлением ошибок (FEC), который генерирует избыточность в битах кода. Величина избыточности определяется кодовой скоростью для кода FEC. Слишком малая избыточность может привести к неспособности приемника декодировать пакет. Наоборот, слишком большая избыточность может привести к недостаточному использованию емкости канала связи и/или другим отрицательным воздействиям.

Есть поэтому потребность в способах, чтобы эффективно закодировать и декодировать данные.

Сущность изобретения

Способы эффективного кодирования и декодирования данных описываются ниже. В одном аспекте могут поддерживаться множественные кодовые скорости для кода FEC, и подходящая кодовая скорость может быть выбрана на основании размера пакета. Обычно более высокие кодовые скорости могут использоваться для больших размеров пакета, и более низкие кодовые скорости могут использоваться для меньших размеров пакета. Это может улучшить эффективность декодирования для приемника с ограниченным размером памяти.

В одном варианте осуществления передатчик (например, базовая станция) может получить по меньшей мере один порог для использования при выборе кодовой скорости (например, от приемника, такого как терминал). Передатчик может определить размер пакета для использования при передаче данных. Передатчик может затем выбрать кодовую скорость из множества кодовых скоростей для кода FEC на основании размера пакета и по меньшей мере одного порога. Код FEC может быть Турбокодом, кодом проверки на четность малой плотности (LDPC), сверточным кодом или некоторым другим кодом. Передатчик может закодировать пакет в соответствии с основной кодовой скоростью для кода FEC, чтобы получить кодированный пакет, и может выполнить «прокалывание» кодированного пакета, если необходимо, чтобы получить выбранную кодовую скорость этого пакета. Передатчик может затем передать кодированный пакет после какого-либо «прокалывания» на приемник.

В другом аспекте могут поддерживаться множественные коды FEC различных типов, и подходящий код FEC может быть выбран на основании размера пакета. В одном варианте осуществления передатчик может получить по меньшей мере один порог для использования при выборе кода FEC и может определить размер пакета для использования при передаче данных. Передатчик может затем выбрать код FEC из множества кодов FEC различных типов на основании размера пакета и по меньшей мере одного порога. Передатчик может закодировать пакет в соответствии с выбранным кодом FEC, чтобы получить кодированный пакет, и может далее обработать и передать кодированный пакет.

Приемник может выполнить дополнительную обработку, чтобы восстановить пакет, посланный передатчиком. Различные аспекты и признаки раскрытия описываются ниже более подробно.

Краткое описание чертежей

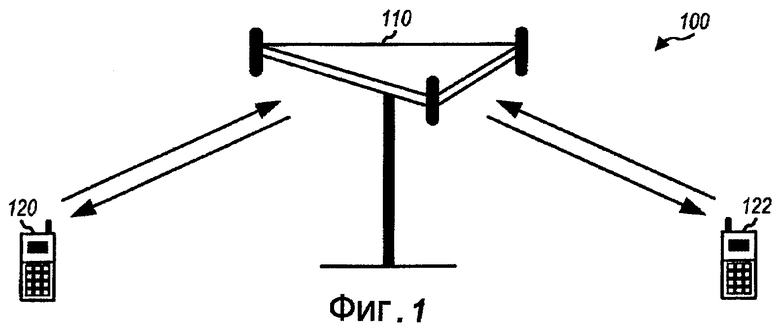

Фиг. 1 показывает систему беспроводной связи.

Фиг. 2 показывает передачу данных с HARQ.

Фиг. 3 показывает блок-схему базовой станции и терминала.

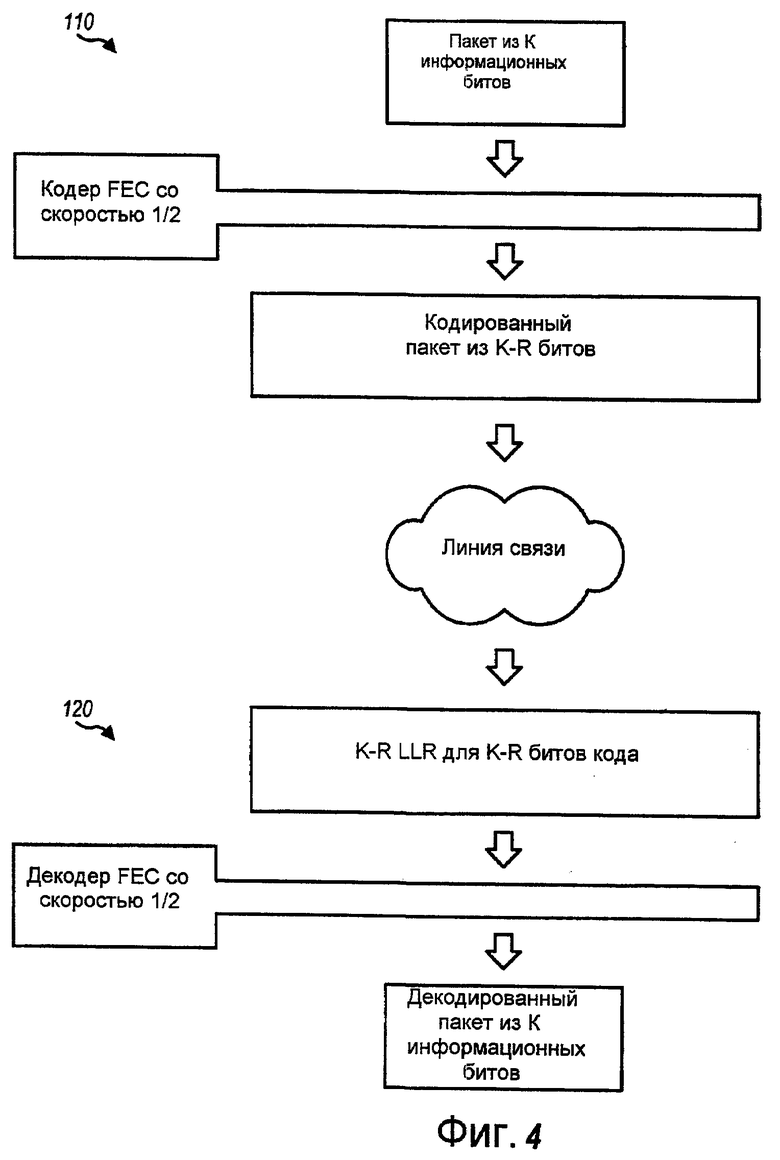

Фиг. 4 показывает кодирование и декодирование для передачи данных.

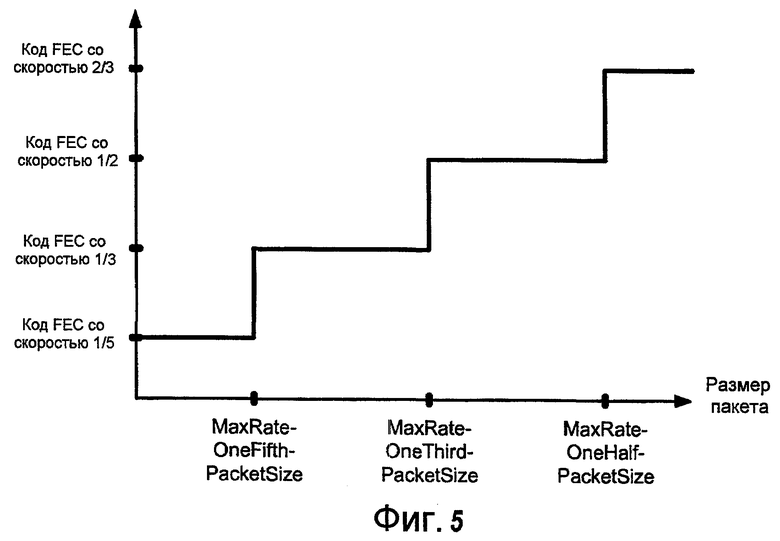

Фиг. 5 показывает график кодовой скорости от размера пакета.

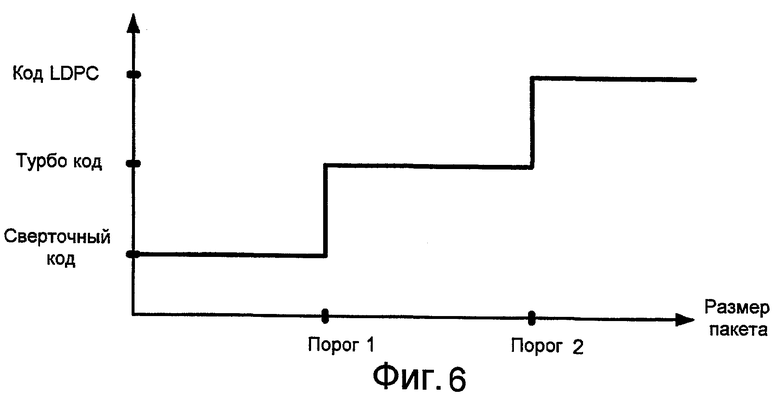

Фиг. 6 показывает график кода FEC от размера пакета.

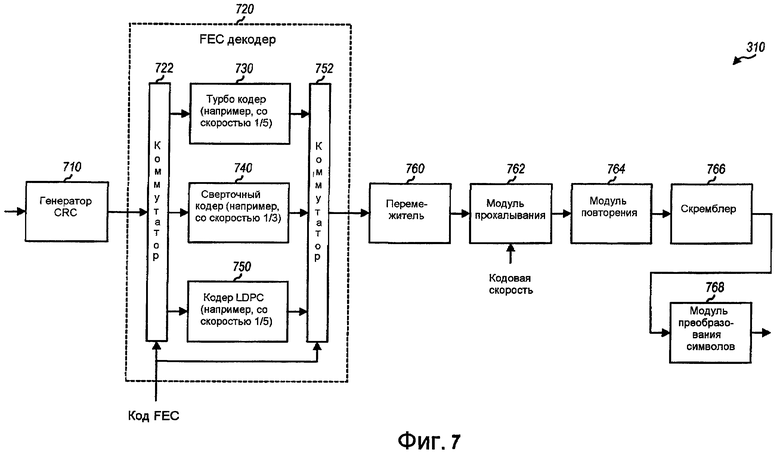

Фиг. 7 показывает блок-схему процессора передачи данных.

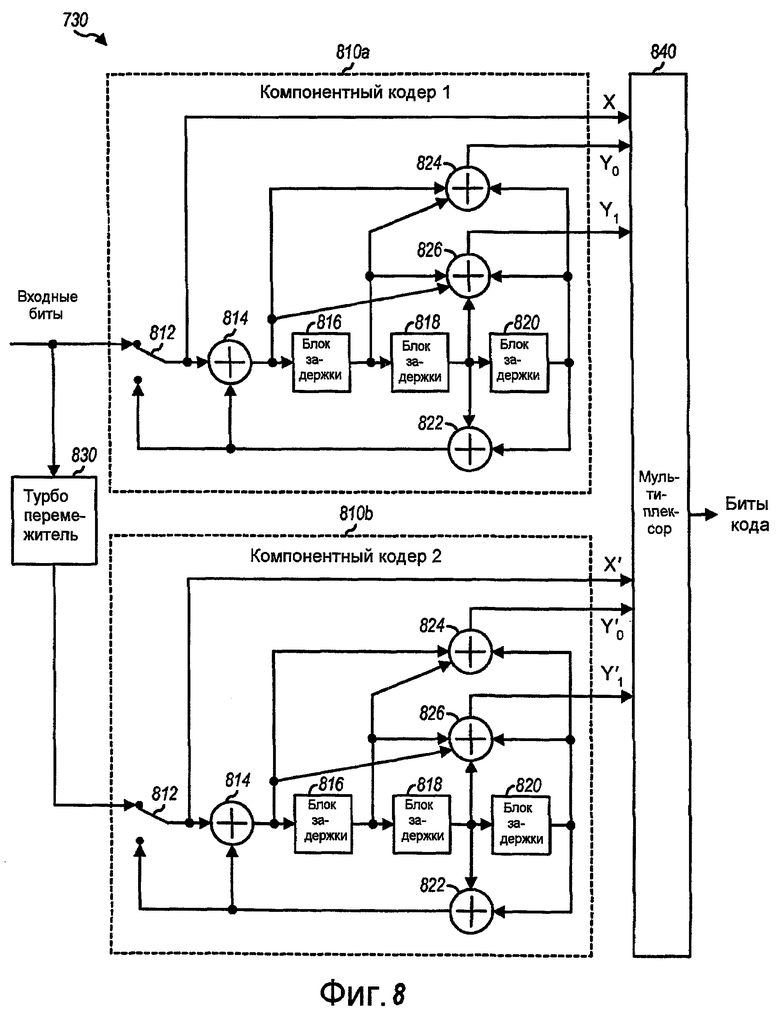

Фиг. 8 показывает блок-схему Турбокодера.

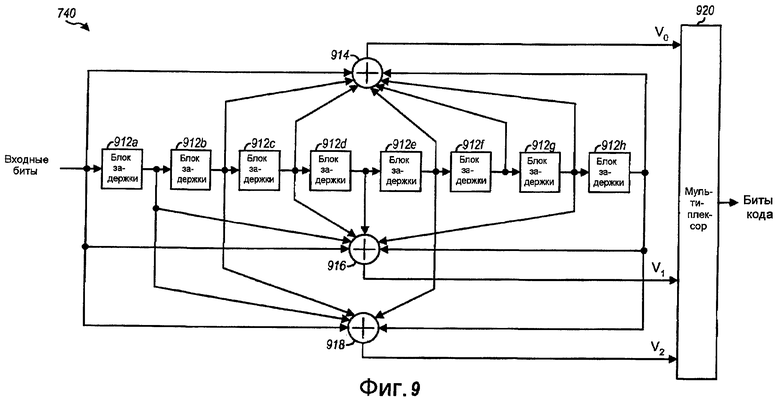

Фиг. 9 показывает блок-схему сверточного кодера.

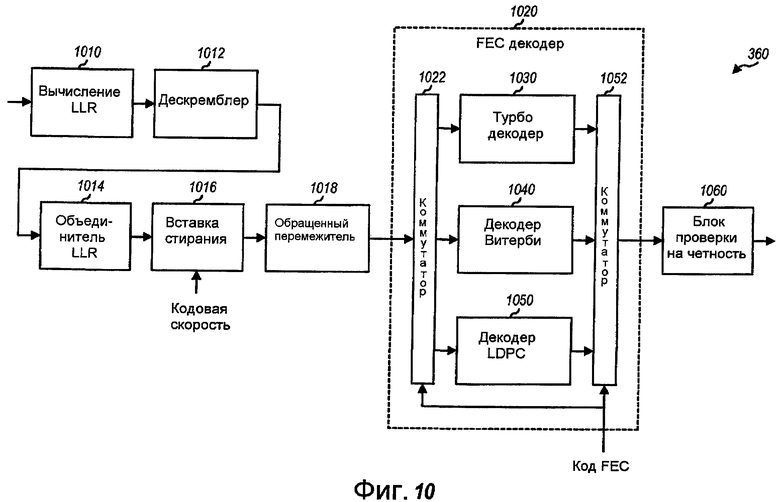

Фиг. 10 показывает блок-схему процессора приема данных.

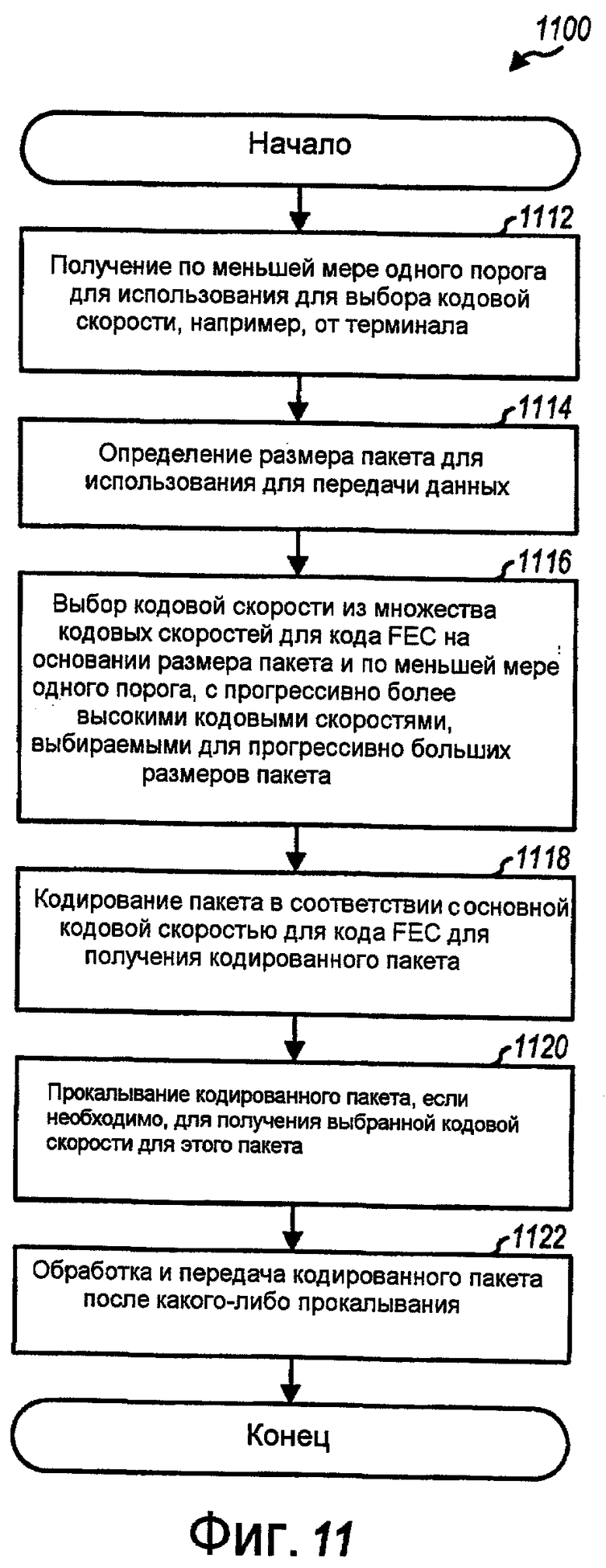

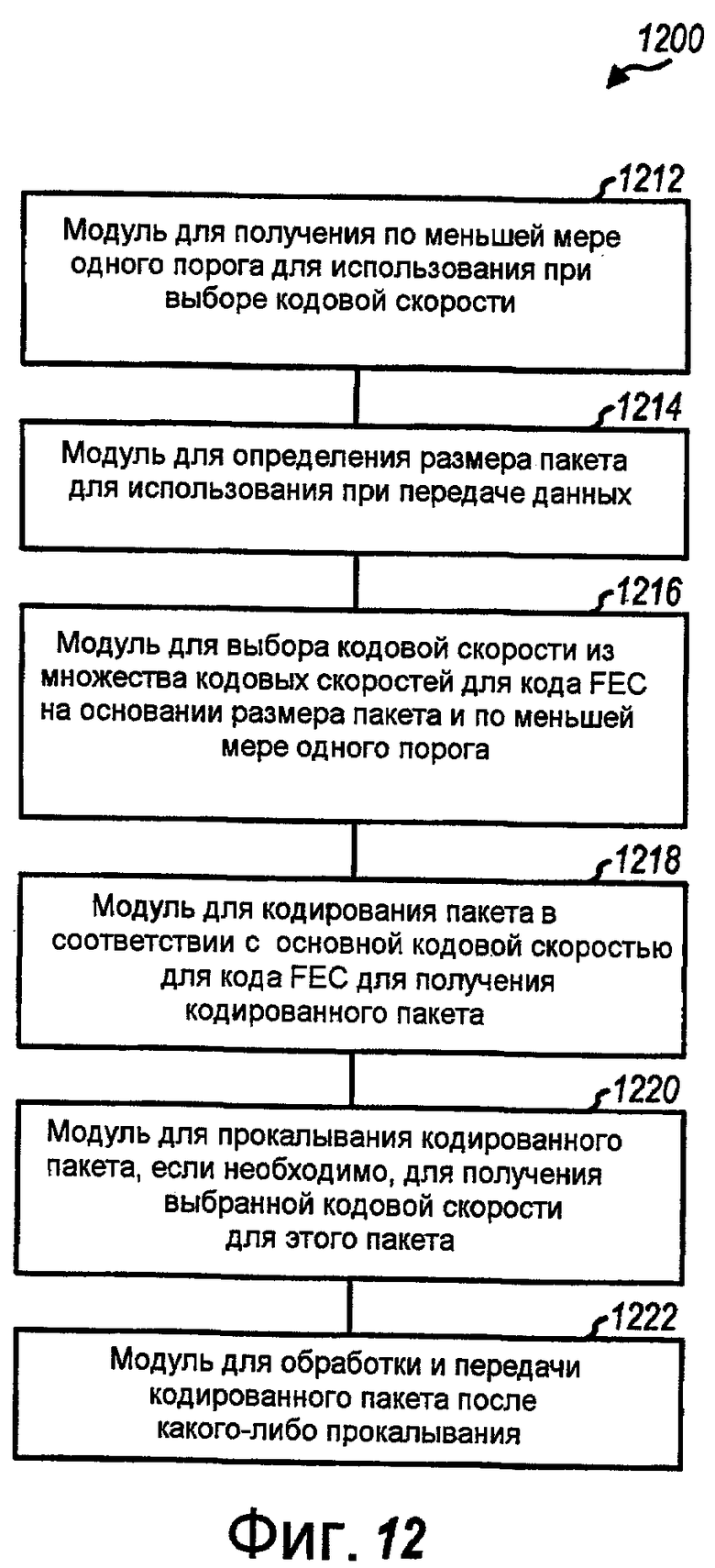

Фиг. 11 и 12 показывают процесс и устройство соответственно для передачи данных с выбором кодовой скорости на основании размера пакета.

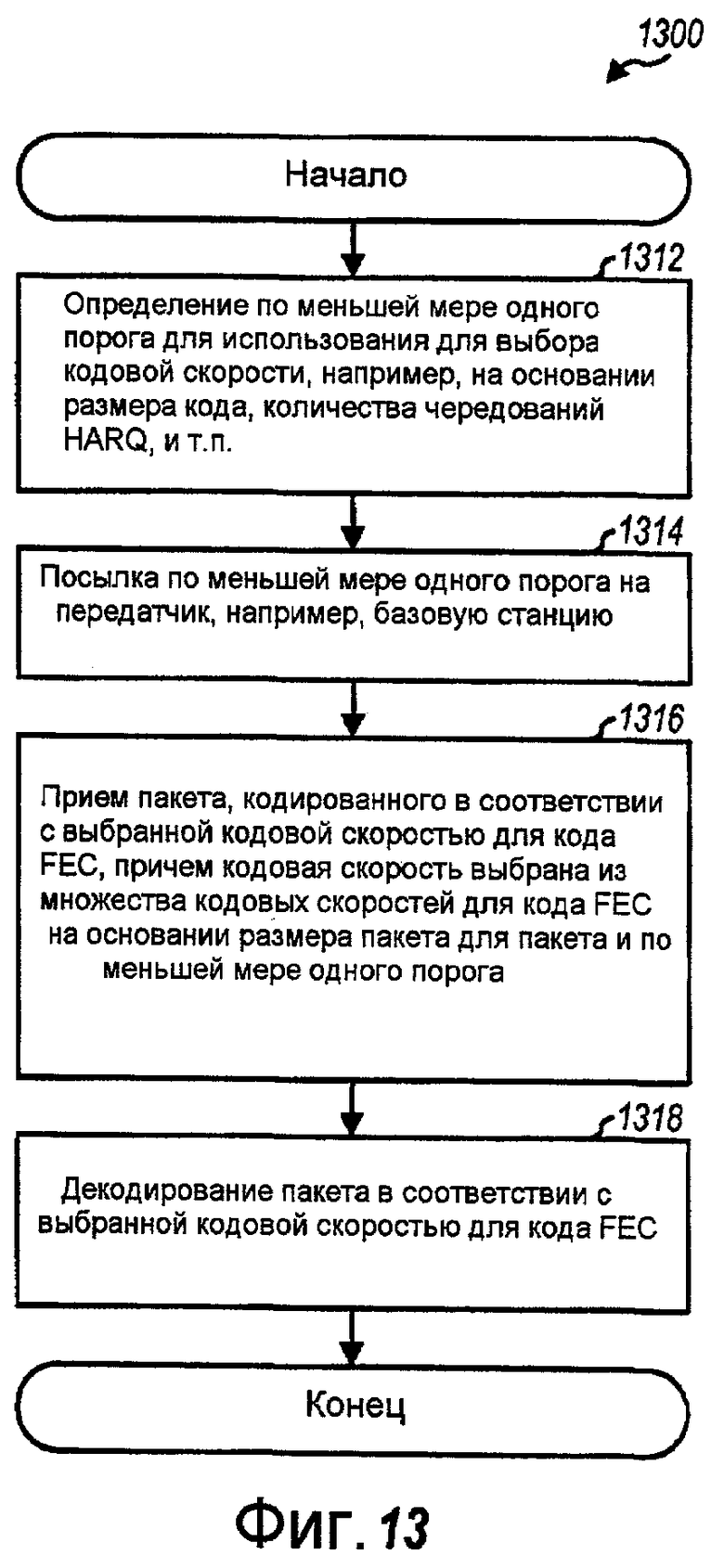

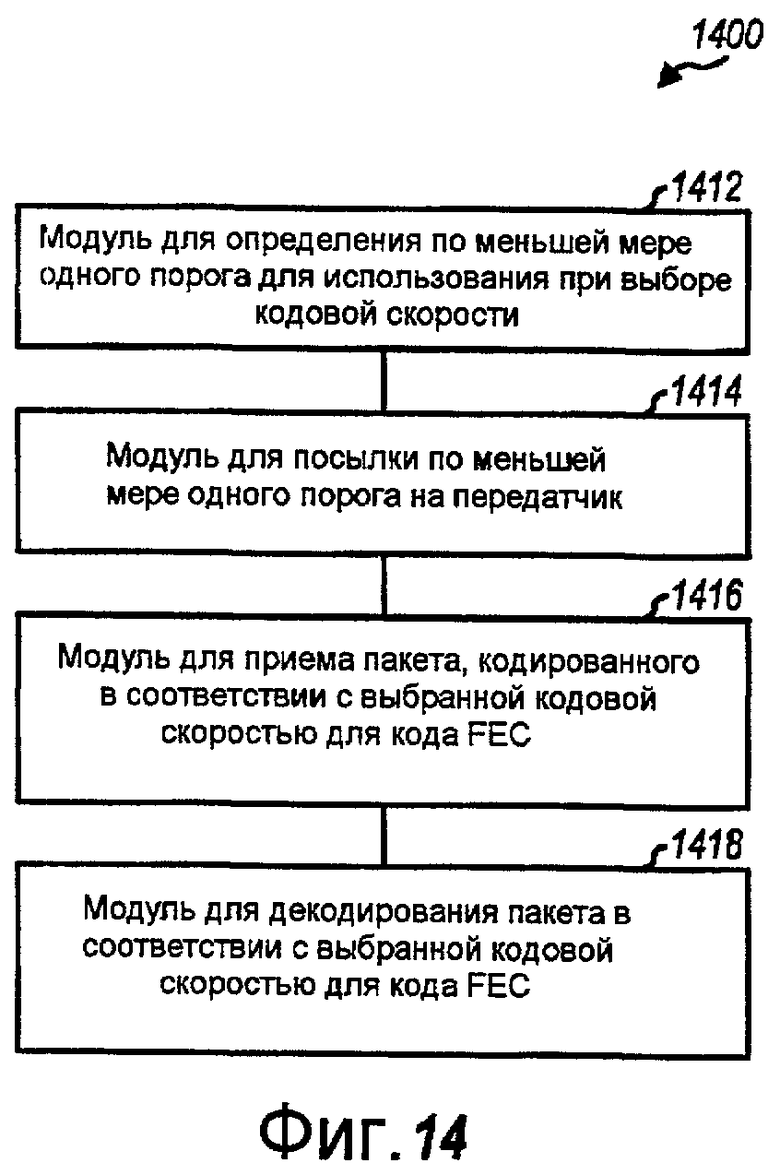

Фиг. 13 и 14 показывают процесс и устройство соответственно для приема данных с выбором кодовой скорости на основании размера пакета.

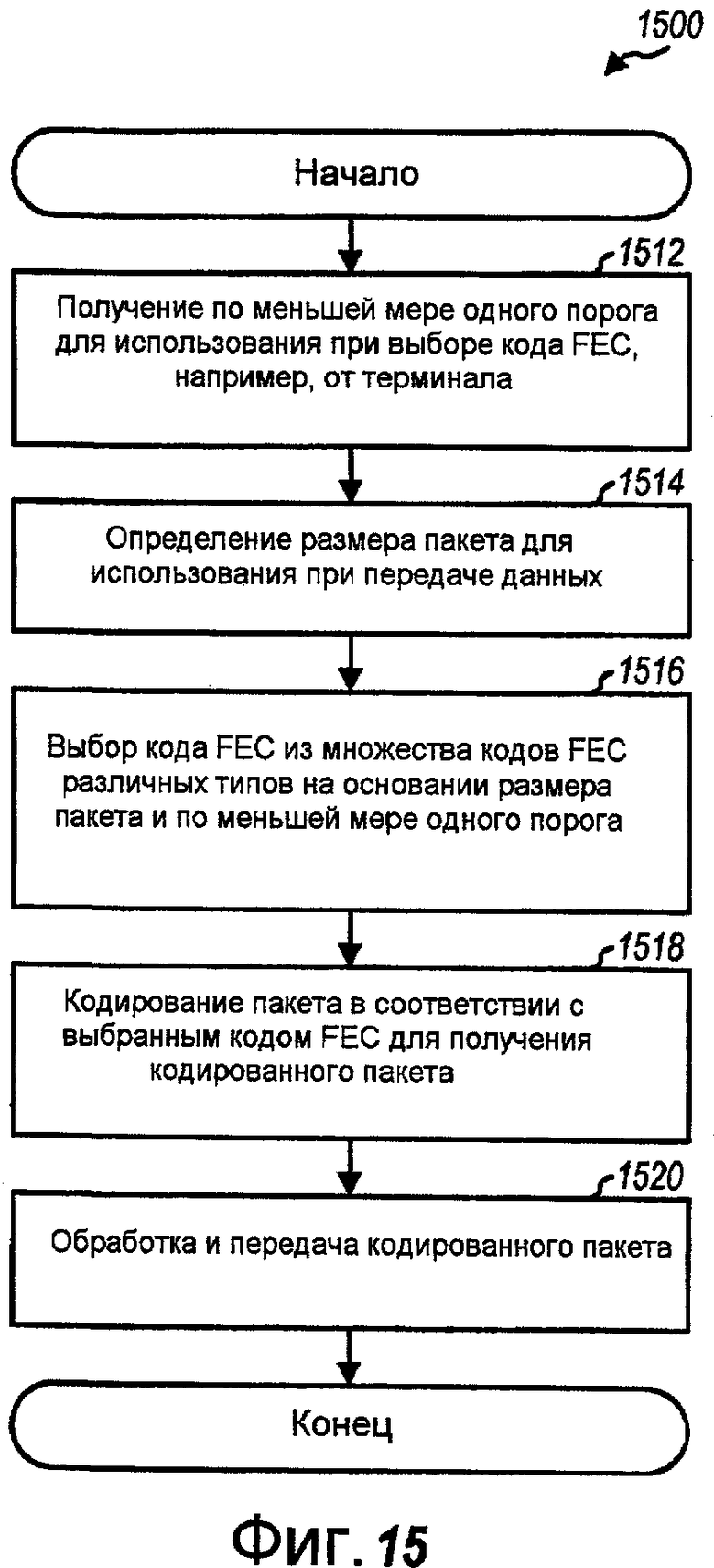

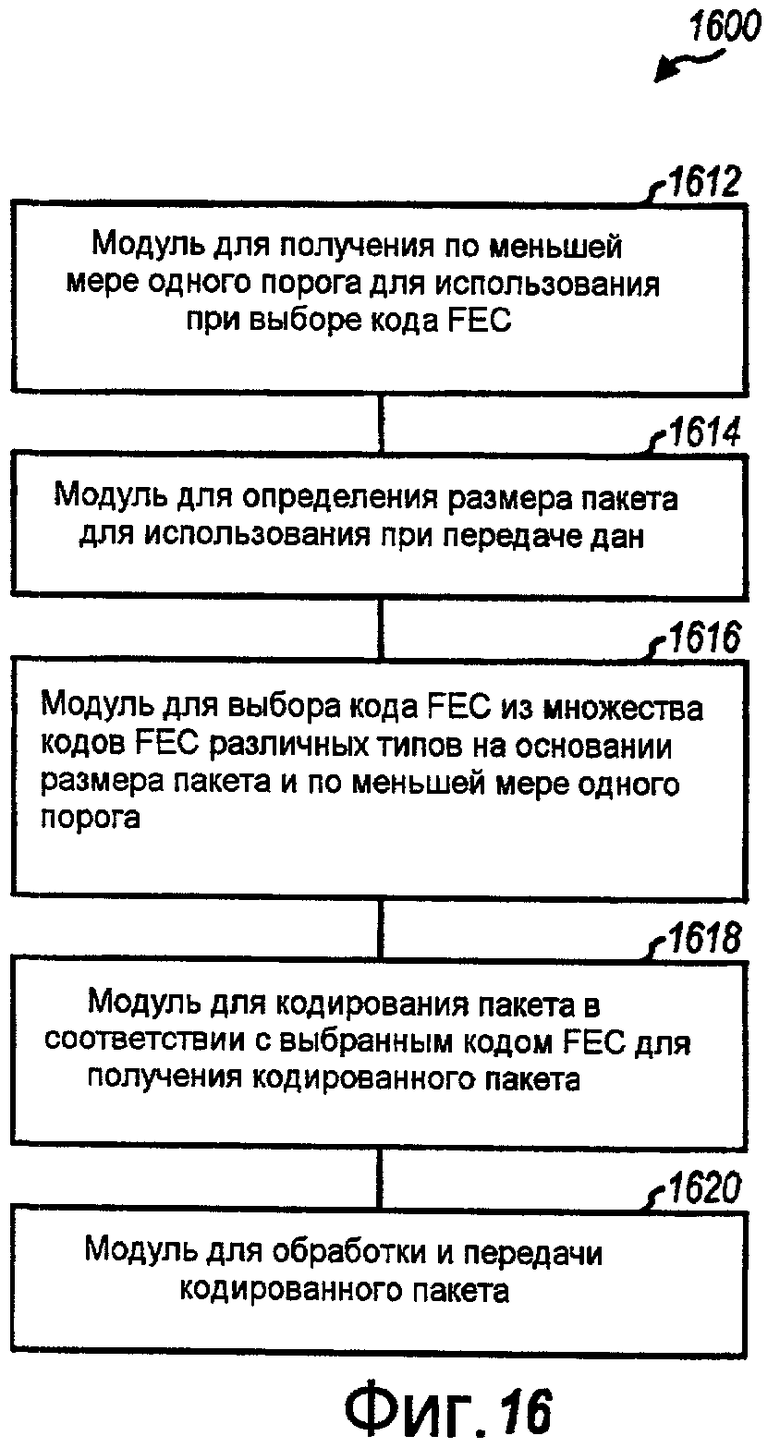

Фиг. 15 и 16 показывают процесс и устройство соответственно для передачи данных с выбором кода FEC на основании размера пакета.

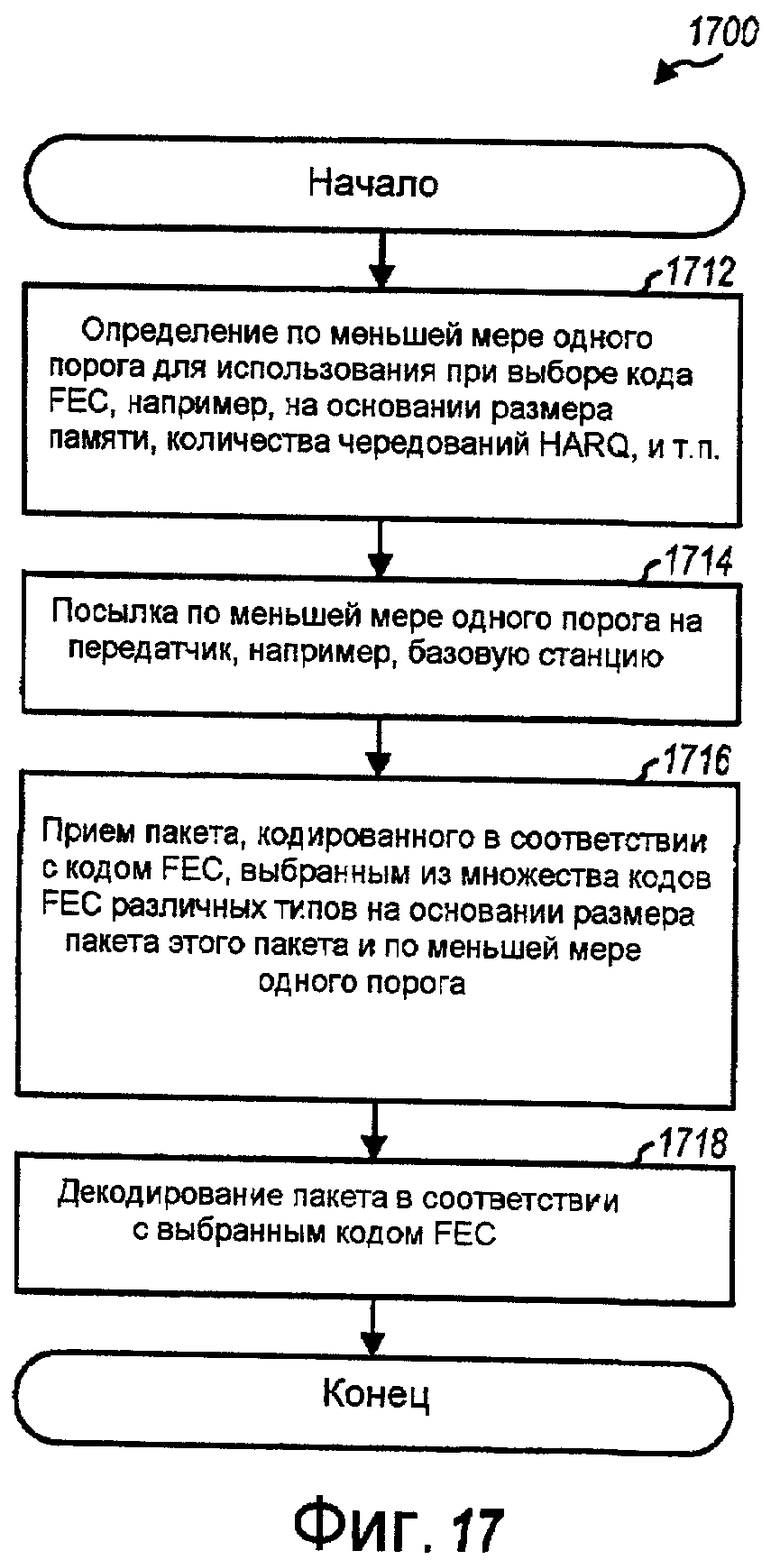

Фиг. 17 и 18 показывают процесс и устройство соответственно для приема данных с выбором кода FEC на основании размера пакета.

Подробное описание

Способы, описанные в настоящем изобретении, могут использоваться для различных систем и сетей беспроводной связи. Термины "система" и "сеть" часто используются взаимозаменяемо. Например, эти способы могут использоваться для систем связи с использованием проводной связи, систем беспроводной связи, беспроводных локальных сетей (WLAN) и т.д. Системы беспроводной связи могут быть системами множественного доступа с кодовым разделением каналов (CDMA), системами множественного доступа с временным разделением каналов (TDMA), системами множественного доступа с частотным разделением каналов (FDMA), системами с ортогональным FDMA (OFDMA), системами FDMA с единственной несущей (SC-FDMA) и т.д. Система CDMA может реализовать радиотехнологию, такую как cdma2000, Универсальный наземный радиодоступ (UTRA) и т.д. Система OFDMA может реализовывать радиотехнологию, такую как Ультрамобильная широкополосная связь (UMB), усовершенствованная (Evolved) UTRA (E-UTRA), IEEE 802.16, IEEE 802.20, Flash-OFDM(R) и т.д. UTRA и E-UTRA описываются в документах от организации, названной "Проект партнерства 3-го поколения" (3GPP). Cdma2000 и UMB описываются в документах от организации, названной "Проект партнерства 3-го поколения 2" (3GPP2). Эти различные радиотехнологии и стандарты известны в технике. Для ясности некоторые аспекты этих методик описываются ниже для UMB, и терминология UMB используется ниже в большей части описания. UMB описывается в документе 3GPP2 C.S0084-001, названном "Physical Layer for Ultra Mobile Broadband (UMB) Air Interface Specification," август 2007, который публично доступен.

Фиг. 1 показывает систему 100 беспроводной связи, которая может также называться как сеть доступа (AN). Для простоты только одна базовая станция 110 и два терминала 120 и 122 показаны на фиг. 1. Базовая станция - станция, которая обменивается с терминалами. Базовая станция может также называться как точка доступа, Узел B, усовершенствованный (evolved) Узел B и т.д. Терминал может быть стационарным или мобильным и может также называться как терминал доступа (АТ), мобильная станция, пользовательское оборудование, абонентская установка, станция и т.д. Терминал может быть сотовым телефоном, персональным цифровым ассистентом (PDA), устройством беспроводной связи, беспроводным модемом, карманным устройством, ноутбуком, беспроводным телефоном и т.д. Терминал может обмениваться с одной или более базовыми станциями по прямой и/или обратной линиям связи в любой заданный момент времени. Прямая линия связи (или нисходящая линия связи) относится к линии связи от базовых станций на терминалы, и обратная линия связи (или восходящая линия связи) относится к линии связи от терминалов к базовым станциям.

Система может поддерживать гибридный автоматический запрос повторной передачи (HARQ). В течение HARQ передатчик может послать одну или более передач для пакета до тех пор, пока пакет не будет декодирован корректно приемником, или максимальное количество передач не будет послано, или до удовлетворения некоторого другого условия завершения. HARQ может улучшить надежность передачи данных.

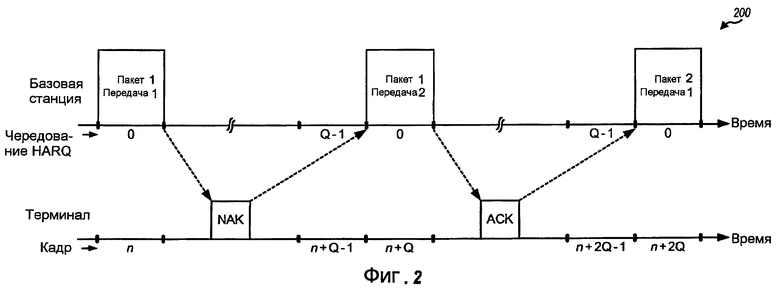

Фиг. 2 показывает передачу данных по прямой линии связи с HARQ. Шкала времени передачи может быть разделена на кадры, где каждый кадр имеет конкретную длительность времени. Может быть определено множество (Q) HARQ чередований, где Q может быть фиксированным или конфигурируемым значением. Например, Q может быть равным 4, 6, 8 и т.д. Каждое чередование HARQ может включать в себя кадры, которые разделены Q кадрами. Таким образом, чередование HARQ q может включать в себя кадры n+q, n+Q+q, n+2Q+q и т.д., для q  {0..., Q-1}.

{0..., Q-1}.

Вплоть до q пакетов можно послать параллельно в Q чередованиях HARQ, один пакет на каждое чередование HARQ. Одна или более передач HARQ может быть послана для каждого пакета в чередовании HARQ, используемом для этого пакета. Передача HARQ является передачей для одного пакета в одном кадре. Пакет может быть обработан (например, кодирован и модулирован) и послан таким образом, что он может быть декодирован корректно с целевым количеством передач HARQ, которое может быть равно 2, 3, 4 и т.д.

Для передачи данных по прямой линии связи терминал 120 может периодически оценивать качество канала прямой линии связи и посылать индикатор качества канала (CQI) в базовую станцию 110. Базовая станция 110 может использовать этот CQI и/или другую информацию, чтобы выбрать формат пакета для использования для каждой передачи HARQ для терминала 120. Формат пакета может быть ассоциирован с размером пакета, спектральной эффективностью, кодовой скоростью, порядком модуляции или схемой и/или другими параметрами для пакета или передачи. Базовая станция 110 может обработать пакет (Пакет 1) на основании формата выбранного пакета и послать первую передачу HARQ (Trans 1) в чередовании HARQ 0. Терминал 120 может принять первую передачу HARQ, декодировать Пакет 1 с ошибкой и послать отрицательное подтверждение (NAK). Базовая станция 110 может принять NAK и послать вторую передачу HARQ (Trans 2) для Пакета 1 в том же самом чередовании HARQ 0. Терминал 120 может принять вторую передачу HARQ, декодировать Пакет 1 корректно на основании первой и второй передач HARQ и послать подтверждение (ACK). Базовая станция 110 может принять ACK и обработать и послать другой пакет (Пакет 2) в чередовании HARQ 0 аналогичным способом.

Для простоты, фиг. 2 показывает передачу данных в одном чередовании HARQ на терминал 120. Базовая станция 110 может передать вплоть до Q пакетов параллельно по вплоть до Q чередованиям HARQ на терминал 120. Эти пакеты могут начинаться и заканчиваться в разное время.

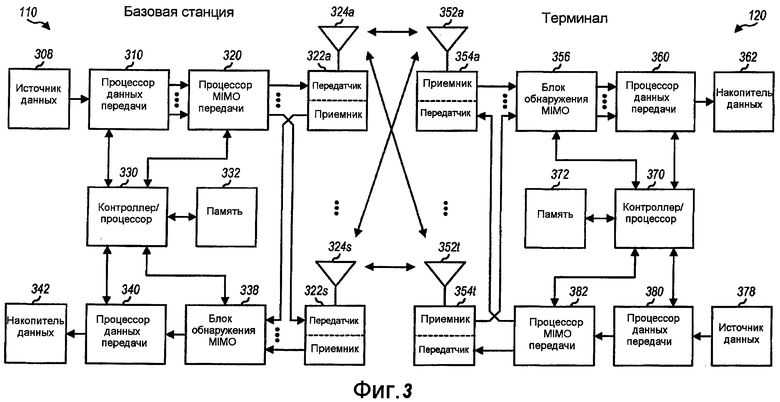

Фиг. 3 показывает блок-схему варианта осуществления базовой станции 110 и терминала 120 согласно фиг. 1. В этом варианте осуществления базовая станция 110 снабжена S антеннами 324a-324s, и терминал 120 оборудуется T антеннами 352a-352t, где в общем S≥1 и T≥1.

В отношении прямой линии связи в базовой станции 110 процессор 310 данных передачи может принять пакет данных для терминала 120 от источника данных 308, обработать (например, закодировать, выполнить перемежение и преобразование символов) пакет на основании формата пакета и выдать символы данных, которые являются символами модуляции для данных. Процессор 320 MIMO передачи может мультиплексировать символы данных с пилот-символами, выполнить прямое отображение MIMO или предварительное кодирование/формирование диаграммы направленности, если это является подходящим, и выдать S потоков символов на S передатчиков (TMTR) 322a-322s. Каждый передатчик 322 может обработать свой выходной поток символов (например, для OFDM), чтобы получить выходной поток элементов сигнала. Каждый передатчик 322 может далее привести к требуемым условиям (например, преобразовать аналоговую форму, отфильтровать, усилить и преобразовать с повышением частоты) свой выходной поток элементов сигнала и сформировать сигнал прямой линии связи. S сигналов прямой линии связи от передатчиков 322a-322s может быть передан от S антенн 324a-324s соответственно.

В терминале 120 T антенн 352a-352t могут принять сигналы прямой линии связи от базовой станции 110 и каждая антенна 352 может выдать принятый сигнал на соответствующий приемник (RCVR) 354. Каждый приемник 354 может обработать (например, отфильтровать, усилить, преобразовать с понижением частоты и перевести в цифровую форму) свой принятый сигнал, чтобы получить выборки, далее обработать выборки (например, для OFDM), чтобы получить принятые символы, и выдать принятые символы на детектор 356 MIMO. Детектор 356 MIMO может выполнить обнаружение MIMO в отношении принятых символов, если это является подходящим, и выдать обнаруженные символы. Процессор 360 данных приема может далее обработать (например, выполнить обратное символьное преобразование, обращенное перемежение и декодирование) обнаруженные символы и выдать декодированные данные на приемник 362 данных. Обычно обработка детектором 356 MIMO и процессором 360 данных приема является комплементарной к обработке процессором 320 MIMO передачи и процессором 310 данных передачи в базовой станции 110.

В отношении обратной линии связи в терминале 110 пакет данных может быть выдан источником данных 378 и обработан (например, кодирован, перемежен и символьно преобразован) процессором 380 данных передачи. Символы данных от процессора 380 данных передачи могут быть мультиплексированы с пилот-символами и пространственно обработаны процессором 382 MIMO передачи и далее обработаны передатчиками 354a-354t, чтобы получить Т сигналов обратной линии связи, которые могут быть переданы через антенны 352a-352t. В базовой станции 110 сигналы обратной линии связи от терминала 120 могут быть приняты антеннами 324a-324s, обработаны приемниками 322a-322s, обнаружены детектором 338 MIMO и далее обработаны процессором 340 данных приема, чтобы восстановить пакет, посланный терминалом 120.

Контроллеры/процессоры 330 и 370 могут направлять работу базовой станции 110 и терминала 120 соответственно. Контроллеры/процессоры 330 и/или 370 могут также выполнить выбор кодовой скорости и/или выбор кода FEC для передачи данных по прямым и обратным линиям связи, как описано ниже. Блоки памяти 332 и 372 могут сохранять данные и программные коды для базовой станции 110 и терминала 120 соответственно.

Способы, описанные в настоящим изобретении, могут использоваться для передачи данных по прямой линии связи, так же как и по обратной линии связи. Для ясности некоторые аспекты описываются ниже для передачи данных по прямой линии связи.

Фиг. 4 показывает кодирование и декодирование для передачи данных по прямой линии связи. В базовой станции 110 пакет K информационных битов может быть закодирован FEC кодером со скоростью 1/R, чтобы сгенерировать кодированный пакет из приблизительно K*R битов кода. Эти биты кода могут быть преобразованы в символы модуляции, которые могут быть далее обработаны и переданы через линию связи. В терминале 120 передача, принятая посредством линии связи, может быть обработана, чтобы получить обнаруженные символы, которые могут быть далее обработаны, чтобы получить вплоть до K*R логарифмических отношений правдоподобия (LLR) для вплоть до K*R битов кода, принятых для этого пакета. Символ модуляции может быть получен посредством отображения B битов кода на комплексное значение в совокупности сигналов, где B≥1. Количество B LLR может быть вычислено для B битов кода символа модуляции, на основании соответствующего обнаруженного символа. LLR для каждого бита кода может указывать вероятность, что этот бит кода равен нулю («0») или единице («1») при наличии обнаруженного символа для этого бита кода. FEC декодер со скоростью 1/R может декодировать эти LLR, чтобы получить декодированный пакет K информационных битов.

Если HARQ используется для передачи данных, то часть K*R битов кода для пакета можно послать в каждой передаче HARQ. Если все K*R битов кода посланы и пакет все еще не декодирован корректно, то некоторые или все те же самые биты кода могут быть снова посланы в последующих передачах HARQ. LLR для битов кода, которые снова посылаются в более поздней передаче HARQ, могут быть объединены с LLR для тех же самых битов кода, принятых в предшествующей передаче HARQ.

Обычно, лучшая эффективность декодирования может быть получена посредством использования более низкой кодовой скорости, так что различные биты кода посылают для этого пакета. Однако более низкая кодовая скорость может также привести к хранению большего количества значений LLR. Наоборот, более высокая кодовая скорость может обеспечить меньше битов кода и, следовательно, привести к хранению меньшего количества LLR. Однако более высокая кодовая скорость может привести к худшей эффективности декодирования. Подходящая кодовая скорость может быть выбрана на основании компромисса между эффективностью декодирования и требуемым объемом и конфигурации памяти.

Размер пакета для пакета может быть выбран по-разному. В одном варианте осуществления размер пакета может быть выбран следующим образом:

где HARQtarget - целевое количество передач HARQ для пакета,

SEtarget - целевая спектральная эффективность для пакета, и

Nresources - количество физических ресурсов, используемых для посылки пакета.

Целевая спектральная эффективность может быть выбрана на основании сообщенного CQI, например более высокая целевая спектральная эффективность для более высокого CQI. Размер пакета может также быть выбран на основании других наборов параметров.

Терминал 120 может вычислять LLR для битов кода, когда принимаются символы данных для пакета, и может временно сохранять эти LLR в буферной памяти. Память может иметь фиксированный размер и может быть в состоянии сохранить вплоть до М LLR. Размер М памяти может быть любым значением и может зависеть от емкости терминала. Соотношения между размером пакета, кодовой скоростью и размером памяти могут быть выражены как

Как показано в уравнении (2), для заданного размера М памяти имеется компромисс между размером К пакета и кодовой скоростью 1/R. Например, память, способная хранить 10000 LLR, может поддерживать размер пакета в 2000 информационных битов с кодовой скоростью 1/5, размер пакета, равный 3333, с кодовой скоростью 1/3, размер пакета, равный 5000, с кодовой скоростью 1/2, размер пакета, равный 6666, с кодовой скоростью 2/3 и т.д.

Уравнение (2) предполагает, что посылают единственный пакет и что память сохраняет LLR только для этого пакета. Как описано выше для фиг. 2, вплоть до Q пакетов могут быть посланы параллельно по вплоть до Q различным HARQ чередованиям. В этом случае память может быть разделена на вплоть до Q секций, где каждая секция хранит LLR для одного пакета. Соотношения между размером пакета, кодовой скоростью, количеством чередований HARQ и размером памяти могут затем быть выражены как

Количество чередований HARQ в уравнении (3) может быть количеством (Q) чередований HARQ, доступных для передачи данных, количеством чередований HARQ, используемых для передачи данных, и т.д.

В одном аспекте различные кодовые скорости для кода FEC могут использоваться для передачи данных в зависимости от размера пакета. Обычно, более высокие кодовые скорости могут использоваться для больших размеров пакета, и более низкие кодовые скорости могут использоваться для меньших размеров пакета.

Фиг. 5 показывает график кодовой скорости в зависимости от размера пакета в соответствии с одним вариантом осуществления. В этом варианте осуществления поддерживаются четыре кодовые скорости FEC 1/5, 1/3, 1/2 и 2/3. Код FEC со скоростью 1/5 выбирается, если размер пакета равен или меньше, чем первый порог MaxRateOneFifthPacketSize. Код FEC со скоростью 1/3 выбирается, если размер пакета больше, чем MaxRateOneFifthPacketSize, и равен или меньше, чем второй порог MaxRateOneThirdPacketSize. Код FEC со скоростью 1/2 выбирается, если размер пакета больше, чем MaxRateOneThirdPacketSize, и равен или меньше, чем третий порог MaxRateOneHalfPacketSize. Код FEC со скоростью 2/3 выбирается, если размер пакета больше, чем MaxRateOneHalfPacketSize. Таблица 1 суммирует выбор кодовой скорости для варианта осуществления, показанного на фиг. 5.

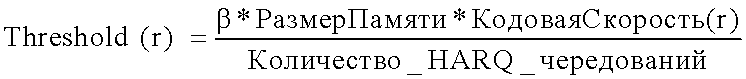

Если множество чередований HARQ может использоваться для передачи данных, то пороги в Таблице 1 могут быть установлены на основании количества HARQ чередований. В одном варианте осуществления пороги могут быть установлены следующим образом:

Если Q=8 HARQ чередований доступны для использования, то

MaxRateOneFifthPacketSize = MaxRateOneFifthPacketSizeEightlnterlace,

MaxRateOneThirdPacketSize = MaxRateOneThirdPacketSizeEightlnterlace, и

MaxRateOneHalfPacketSize = MaxRateOneHalfPacketSizeEightlnterlace.

Если Q=6 HARQ чередований доступны для использования, то

MaxRateOneFifthPacketSize = MaxRateOneFifthPacketSizeSixInterlace,

MaxRateOneThirdPacketSize = MaxRateOneThirdPacketSizeSixInterlace, и

MaxRateOneHalfPacketSize = MaxRateOneHalfPacketSizeSixInterlace.

Количество чередований HARQ может быть конфигурируемым и установлено системой. MaxRateOneFifthPacketSizeEightInterlace, MaxRateOneThirdPacketSizeEightInterlace, MaxRateOneHalfPacketSizeEightlnterlace, MaxRateOneFifthPacketSizeSixInterlace, MaxRateOneThirdPacketSizeSixInterlace и MaxRateOneHalfPacketSizeSixInterlace могут быть конфигурируемыми атрибутами. Терминал 120 может определить значения этих конфигурируемых атрибутов на основании размера своей памяти, количества чередований HARQ и/или других параметров. В одном варианте осуществления пороги для выбора кодовой скорости могут быть определены следующим образом:

где КодоваяСкорость(r) может быть равна 1/5, 1/2, 1/3 или 2/3, β является значением, меньшим чем 1,0, и используется для обеспечения запаса, и Threshold (r) является порогом для КодовойСкорости(r) для данного количества HARQ чередований.

В одном варианте осуществления терминал 120 может определить пороги для всех кодовых скоростей, поддерживаемых для этого кода FEC, например, как показано в уравнении (4). Threshold(r) может соответствовать параметрам MaxRate, заданным выше для различного числа HARQ чередований. Терминал 120 может послать в систему пороги или значения атрибута в качестве своей возможности. В другом варианте осуществления терминал 120 может послать информацию о возможности (например, размер своей памяти) к системе. Система может затем определить пороги для терминала 120 на основании этой информации о возможности. В любом случае система может затем отправить данные на терминал 120 в соответствии с кодовыми скоростями, выбранными на основании этих порогов.

Обычно код FEC, показанный на фиг. 5, может быть любым типом кода FEC. Например, код FEC может быть Турбокодом, сверточным кодом, кодом LDPC, блочным кодом или некоторым другим типом кода.

Система может также поддерживать различные типы кодов FEC. В одном варианте осуществления система может поддерживать Турбокод, сверточный код и код LDPC. У этих различных типов кодов FEC могут быть различные характеристики и эффективность.

В другом аспекте подходящий код FEC может быть выбран для использования на основании размера пакета. Турбокод может обеспечить лучшую эффективность декодирования для больших пакетов, тогда как сверточный код может обеспечить лучшую эффективность декодирования для меньших пакетов.

Фиг. 6 показывает график зависимости кода FEC от размера пакета в соответствии с одним вариантом осуществления. В этом варианте осуществления сверточный код выбирается для использования, если размер пакета меньше чем или равен первому порогу. Турбокод выбирается для использования, если размер пакета больше, чем первый порог, и меньше чем или равен второму порогу. Код LDPC выбирается для использования, если размер пакета больше, чем второй порог. Обычно, первый и второй пороги каждый могут быть фиксированным или конфигурируемым значением. В одном варианте осуществления первый порог - фиксированное значение, которое может составлять 128 битов или некоторое другое значение. В одном варианте осуществления второй порог - конфигурируемое значение, которое может быть определено терминалом 120 и послано в качестве его возможности в систему.

Обычно система может поддерживать любую комбинацию кодов FEC различных типов и любой тип кода FEC. Кроме того, система может поддерживать любое количество кодовых скоростей и любую кодовую скорость для каждого кода FEC. Для каждого кода FEC с множественными кодовыми скоростями ряд порогов может быть определен на основании различных коэффициентов, таких как размер памяти приемника, количество чередований HARQ, доступных для использования, количество чередований HARQ, используемых для передачи данных, количества пакетов для посылки параллельно, целевое количество передач HARQ, скорость декодирования приемника и т.д.

Терминал 120 может определить ряд порогов для каждого кода FEC с множественными кодовыми скоростями и может послать системе эти пороги для всех кодов FEC в качестве своей возможности. Система может выполнить выбор кода FEC и определить подходящий код FEC для использования при передаче данных для терминала 120 на основании размера пакета и порогов для различных кодов FEC. Система может также выполнить выбор кодовой скорости для выбранного кода FEC на основании размера пакета и набора порогов для этого кода FEC.

Хотя и не показано на фиг. 6 для простоты, одна или более кодовых скоростей могут поддерживаться для каждого типа кода FEC. В одном варианте осуществления система может поддерживать скорость 1/5, скорость 1/3, скорость 1/2 и скорость 2/3 для Турбокода. Три порога могут быть определены между первым и вторым порогами и использоваться для выбора одной из этих четырех скоростей Турбокода. Альтернативно или дополнительно, система может поддерживать скорость 1/5, скорость 1/3, скорость 1/2 и скорость 2/3 для кода LDPC. Три порога могут быть определены выше второго порога и использоваться для выбора одной из этих четырех кодовых скоростей LDPC. Система может также поддерживать множественные кодовые скорости для сверточного кода, и один или более порогов могут быть использованы для выбора одной из поддерживаемых кодовых скоростей сверточного кода.

Если пороги для заданного кода FEC определяются на основании количества доступных HARQ чередований (Q), то те же самые пороги могут использоваться независимо от количества пакетов, посылаемых параллельно. Если пороги определяются на основании количества HARQ чередований, используемых для передачи данных, то пороги могут быть вычислены на основании количества пакетов для посылки параллельно.

Фиг. 7 показывает блок-схему варианта осуществления процессора 310 данных передачи, который может также использоваться для процессора 380 данных передачи на фиг. 3. В процессоре 310 данных передачи генератор 710 проверки при помощи циклического кода (CRC) может принять пакет данных, сформировать CRC для пакета и выдать форматированный пакет, имеющий CRC, добавленный к пакету. CRC может использоваться приемником, чтобы определить, декодирован ли пакет корректно или с ошибкой.

FEC кодер 720 может принять форматированный пакет, закодировать пакет в соответствии с кодом FEC, выбранным для пакета, и выдать кодированный пакет. В варианте осуществления, показанном на фиг. 7, FEC кодер 720 включает в себя коммутаторы 722 и 752, кодер Турбо 730, сверточный кодер 740 и кодер LDPC 750. Коммутатор 722 может выдавать форматированный пакет на Турбокодер 730, сверточный кодер 740 или кодер LDPC 750 в зависимости от выбранного кода FEC. ТурбоКодер 730 может кодировать форматированный пакет в соответствии с основной кодовой скоростью (например, скоростью 1/5), если выбирается Турбокод. Сверточный кодер 740 может кодировать форматированный пакет в соответствии с основной кодовой скоростью (например, скоростью 1/3), если выбирается сверточный код. Кодер LDPC 750 может кодировать форматированный пакет в соответствии с основной кодовой скоростью (например, скоростью 1/5), если выбирается код LDPC. Основная кодовая скорость для кода FEC - самая низкая кодовая скорость для кода FEC. В зависимости от выбранного кода FEC коммутатор 752 может выдавать биты кода от Турбокодера 730, сверточного кодера 740 или кодера LDPC 750 в качестве кодированного пакета.

Перемежитель 760 может перемежать или переупорядочивать биты кода от FEC кодера 720 на основании схемы перемежения. В одном варианте осуществления перемежитель 760 реализует усеченный перемежитель с перестановкой битов (PBRI), описанный в вышеупомянутом документе 3GPP2 C.S0084-001. PBRI может быть функционально эквивалентным подходу, где кодированный пакет расширяется до степени двойки посредством добавления битов заполнения, расширенный пакет перемежается в соответствии с перемежителем с перестановкой битов, и «переставленный» пакет получается посредством считывания переставленных битов и посредством удаления битов заполнения.

Модуль 762 прокалывания (исключения битов) может принять все биты кода для пакета от перемежителя 760 и может проколоть (исключить)/отказаться от нуля или более битов кода на основании выбранной кодовой скорости, как описано ниже. Модуль 762 может обеспечить надлежащее количество битов кода на основании выбранной кодовой скорости и размера пакета. Модуль 764 повторения может повторять биты от модуля 762, в случае необходимости, чтобы получить требуемое общее количество битов. Скремблер 766 может скремблировать биты от модуля 764, чтобы рандомизировать данные. Последовательность скремблирования может быть сформирована на основании регистра сдвига с линейной обратной связью (LFSR), реализующего полином конкретного генератора. LFSR может быть инициализирован в начале пакета с помощью значения начального числа, которое может быть определено на основании ID (идентификатора) MAC терминала 120, идентификатора сектора или фазы пилот-сигнала обслуживающего сектора, индекса формата пакета для этого пакета, индекса кадра первого кадра, в котором пакет посылают, и/или некоторого другого параметра. Скремблер 766 может выполнить операцию исключающее ИЛИ (XOR) над битами из модуля 764 с битами последовательности скремблирования, чтобы сформировать скремблированные биты. Преобразователь 768 символа может преобразовать скремблированные биты в символы модуляции на основании выбранной схемы модуляции, такой как QPSK, 16-QAM, 64-QAM и т.д.

Фиг. 7 показывает конкретный вариант осуществления процессора 310 данных передачи. Пакет может также быть обработан другими способами. Например, повторение и/или скремблирование могут быть опущены или могут быть опущены для некоторых передач.

Фиг. 8 показывает блок-схему варианта осуществления Турбокодера 730 согласно фиг. 7. В этом варианте осуществления Турбокодер 730 реализует параллельный конкатенированный сверточный код (PCCC) и включает в себя два компонентных кодера 810a и 810b, Турбоперемежитель 830 и мультиплексор (Mux) 840. Турбокодер 730 кодирует пакет из K информационных битов в соответствии с основной кодовой скоростью 1/5 и выдает кодированный пакет приблизительно 5 КБ битов кода.

В Турбокодере 730 Турбоперемежитель 830 перемежает K информационных битов в пакете на основании схемы перемежения. Компонентный кодер 810a принимает X последовательностей, составленных из K информационных/введенных битов в пакете. Кодер 810a кодирует последовательность X на основании первого компонентного кода, чтобы получить последовательность Y0 битов проверки на четность, и на основании второго компонентного кода, чтобы получить последовательность Y1 битов проверки на четность. Аналогично, компонентный кодер 810b принимает последовательность X', составленную из K перемеженных битов, от Турбоперемежителя 830. Кодер 810b кодирует эту последовательность X' на основании первого компонентного кода, чтобы получить последовательность Y0' битов проверки на четность, и на основании второго компонентного кода, чтобы получить последовательность Y1' битов проверки на четность.

В каждом компонентном кодере 810 коммутатор 812 сначала пропускает все K входных битов (верхнее положение), а затем передает биты от сумматора 822 (нижнее положение) в течение трех тактовых циклов. Сумматор 814 суммирует эти биты от коммутатора 812 с битами от сумматора 822. Устройства задержки 816, 818 и 820 соединяются последовательно с устройством задержки 816, принимающим выходной сигнал сумматора 814. Сумматор 822 суммирует выходные сигналы устройств задержки 818 и 820 и выдает свой выходной сигнал на сумматор 814 и коммутатор 812. Сумматор 824 суммирует выходной сигнал сумматора 814 и выходные сигналы устройств задержки 816 и 820 и выдает биты проверки на четность для последовательности Y0 или Y0'. Сумматор 826 суммирует выходной сигнал сумматора 814 и выходные сигналы устройств задержки 816, 818 и 820 и выдает биты проверки на четность для последовательности Y1 или Y1'. Все сумматоры являются сумматорами по модулю 2. Компонентный кодер 810a выдает 3К+9 битов кода, составленных из последовательности X из K систематических битов, последовательности Y0 из K битов проверки на четность, последовательность Y0' из K битов проверки на четность и 9 хвостовых битов. Точно так же компонентный кодер 810b выдает 3К+9 битов кода, составленных из последовательности X' из K систематических битов, последовательности Y0 из K битов проверки на четность, последовательности Y1' из K битов проверки на четность и 9 хвостовых битов.

Мультиплексор 840 принимает 6К+18 битов кода от компонентных кодеров 810a и 810b и выдает 5К+18 битов кода в пяти последовательностях U, V0, V1, V0, и V1'. Последовательность U содержит K систематических битов в X последовательности плюс 6 хвостовых битов от коммутатора 812 в обоих компонентных кодерах 810a и 810b. Последовательность V0 содержит K битов проверки на четность в последовательности Y0 плюс 3 хвостовых бита от сумматора 824 в компонентном кодере 810a. Последовательность V1 содержит K битов проверки на четность в последовательности Y1 плюс 3 хвостовых бита от сумматора 826 в компонентном кодере 810a. Последовательность V0 содержит K битов проверки на четность в последовательности Y0 плюс 3 хвостовых бита от сумматора 824 в компонентном кодере 810b. Последовательность V1' содержит K битов проверки на четность в последовательности Y1' плюс 3 хвостовых бита от сумматора 826 в компонентном кодере 810b.

Со ссылками на фиг. 7, в одном варианте осуществления перемежитель 760 может перемежать последовательность U и выдавать последовательность U с перестановками. Перемежитель 760 может также перемежать последовательность V0, чтобы получить последовательность A0, перемежать V0' последовательность, чтобы получить последовательность B0, и выдавать последовательность V0/V0' с перестановками, составленную из чередующихся битов из последовательностей A0 и B0. Перемежитель 760 может также перемежать последовательность V1, чтобы получить А1 последовательность, перемежать V1' последовательность, чтобы получить последовательность B1, и выдавать последовательность V1/V1' с перестановками, составленную из чередующихся битов из последовательностей А1 и B1.

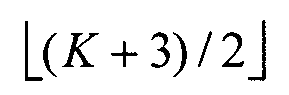

Модуль 762 прокалывания может принимать три последовательности с перестановками от перемежителя 760 и выдавать достаточное количество битов кода на основании выбранной кодовой скорости. Если выбирается скорость 1/5 Турбокода, то модуль 762 может выдавать последовательность U с перестановками (переставленную последовательность), с последующей последовательностью V0/V0' с перестановками, с последующей последовательностью V1/V1' с перестановками. Если выбирается скорость 1/3 Турбокода, то модуль 762 может выдавать последовательность U с перестановками, с последующей последовательностью V0/V0' с перестановками. Последовательность V1/V1' с перестановками можно отклонить. Если выбирается скорость 1/2 Турбокода, то модуль 762 может выдавать последовательность U с перестановками, с последующими первыми K+3 битами последовательности V0/V0' с перестановками. От оставшихся битов можно отказаться. Если выбирается скорость 2/3 Турбокода, то модуль 762 может выдавать последовательность U с перестановками, с перестановками с последующими первыми  битами последовательности V0/V0' с перестановками. От оставшихся битов можно отказаться.

битами последовательности V0/V0' с перестановками. От оставшихся битов можно отказаться.

В варианте осуществления, показанном на фиг. 7 и 8, Турбокод со скоростью 1/5 используется как основная кодовая скорость, и другие кодовые скорости 1/3, 1/2 и 2/3 получаются посредством прокалывания (исключения) некоторых битов кода. Этот вариант осуществления Турбокода может позволить одному Турбодекодеру поддерживать все скорости Турбокода. Множественные скорости Турбокода также могут поддерживаться другими вариантами осуществлениями, например, с различными Турбокодами.

Фиг. 9 показывает блок-схему варианта осуществления сверточного кодера 740 на фиг. 7. В этом варианте осуществления сверточный кодер 740 реализует сверточный код с кодовой скоростью 1/3 с ограничением длины 9. В сверточном кодере 740 восемь устройств задержки 912a - 912h соединяются последовательно, причем устройство задержки 912a принимает биты информации/ввода пакета. Сумматор 914 суммирует входной сигнал устройства задержки 912a и выходные сигналы устройств задержки 912b, 912c, 912e, 912f, 912g и 912h и выдает последовательность V0 битов кода. Сумматор 916 суммирует входной сигнал устройства задержки 912a и выходные сигналы устройств задержки 912a, 912c, 912d, 912g и 912h и выдает последовательность V1 битов кода. Сумматор 918 суммирует входной сигнал устройства задержки 912a и выходные сигналы устройств задержки 912a, 912b, 912e и 912h и выдает последовательность V2 битов кода. Мультиплексор 920 мультиплексирует последовательности V0, V1 и V2 и выдает кодированный пакет из приблизительно 3К битов кода.

Со ссылками на фиг. 7, в одном варианте осуществления перемежитель 760 может принимать последовательности V0, V1 и V2 от сверточного кодера 740 и выдавать переставленную V0/V1/V2 последовательность. Перемежитель 760 может перемежать последовательность V0, чтобы получить последовательность A, перемежать последовательность V1, чтобы получить последовательность B, и перемежать последовательность V2, чтобы получить последовательность C. Перемежитель 760 может затем выдавать последовательность А с последующей последовательностью B, с последующей последовательностью C в качестве переставленной V0/V1/V2 последовательности. Множественные кодовые скорости могут поддерживаться для сверточного кода посредством кодирования в соответствии с основной кодовой скоростью и посредством прокалывания, чтобы получить более высокие кодовые скорости. Множественные кодовые скорости также могут поддерживаться с различными сверточными кодами.

Кодер LDPC 750 может быть реализован так, как описано в вышеупомянутом документе 3GPP2 C.S0084-001, или другими способами, известными в области техники. Множественные кодовые скорости могут поддерживаться для кода LDPC, например, как описано в вышеупомянутом документе 3GPP2 C.S0084-001.

Фиг. 10 показывает блок-схему варианта осуществления процессора 360 данных приема, который может также использоваться для процессора 340 данных приема на фиг. 3. В процессоре 360 данных приема модуль 1010 вычисления LLR может принять обнаруженные символы от детектора 356 MIMO и может вычислить LLR для битов кода, принятых для пакета, на основании обнаруженных символов. Дескремблер 1012 может дескремблировать LLR на основании последовательности скремблирования, используемой передатчиком. Объединитель LLR 1014 может комбинировать LLR для повторных битов кода, например, в посланных позднее HARQ передачах. Модуль 1016 вставки стирания может вставлять стирания для битов кода, не принятых для этого пакета. Стиранием может быть LLR равное 0, что может указывать равную вероятность, что биты кода равны '0' или '1'. Непринятые биты кода могут включать в себя биты кода, отклоненные посредством модуля 762 прокалывания на фиг. 7, так же как биты кода, еще не переданные. Обращенный перемежитель 1018 может выполнять обращенное перемежение LLR от модуля 1016 способом, комплементарным к перемежению посредством перемежителя 760 на фиг. 7.

FEC декодер 1020 может принять LLR для пакета, декодировать эти LLR в соответствии с кодом FEC, выбранным для пакета, и выдавать декодированный пакет. В варианте осуществления, показанном на фиг. 10, FEC декодер 1020 включает в себя коммутаторы 1022 и 1052, Турбодекодер 1030, декодер Витерби 1040 и декодер LDPC 1050. Коммутатор 1022 может выдавать LLR на Турбодекодер 1030, декодер Витерби 1040 или декодер LDPC 1050 в зависимости от выбранного кода FEC. Турбодекодер 1030 может декодировать LLR, если выбирается Турбокод. Декодер Витерби 1040 может декодировать LLR, если выбирается сверточный код. Декодер LDPC 1050 может декодировать LLR, если выбирается код LDPC. В зависимости от выбранного кода FEC коммутатор 1052 может выдавать декодированные биты от Турбодекодера 1030, декодера Витерби 1040 или декодера LDPC 1050 в качестве декодированного пакета. Блок проверки CRC 1060 может проверять декодированный пакет и выдавать состояние декодирования для пакета.

Фиг. 11 показывает вариант осуществления процесса 1100 для передачи данных с выбором кодовой скорости на основании размера пакета. По меньшей мере один порог для использования при выборе кодовой скорости может быть получен, например принят от терминала или вычислен на основании информации о возможности (например, размер памяти), принятой от терминала (этап 1112). Размер пакета для использования при передаче данных может быть определен, например, как показано в уравнении (1) (этап 1114). Кодовая скорость может быть выбрана из множества кодовых скоростей для кода FEC на основании размера пакета, и по меньшей мере один порог с прогрессивно более высокими кодовыми скоростями выбирается для прогрессивно больших размеров пакета (этап 1116). Кодом FEC может быть Турбокод, код LDPC, сверточный код или некоторый другой код. Пакет может быть закодирован в соответствии с основной кодовой скоростью для кода FEC, чтобы получить кодированный пакет (этап 1118). Кодированный пакет может быть проколот, если необходимо, чтобы получить выбранную кодовую скорость для пакета (этап 1120). Кодированный пакет после какого-либо прокалывания может быть далее обработан и передан (этап 1122).

На этапе 1116 размер пакета может сравниваться с по меньшей мере одним порогом и кодовая скорость может быть выбрана из множества кодовых скоростей на основании результата сравнения. В одном варианте осуществления множество кодовых скоростей могут включать в себя кодовую скорость 1/5, кодовую скорость 1/3, кодовую скорость 1/2 и кодовую скорость 2/3. Кодовая скорость 1/5 может быть выбрана, если размер пакета меньше чем или равен первому порогу. Кодовая скорость 1/3 может быть выбрана, если размер пакета больше, чем первый порог, и меньше чем или равен второму порогу. Кодовая скорость 1/2 может быть выбрана, если размер пакета больше, чем второй порог, и меньше чем или равен третьему порогу. Кодовая скорость 2/3 может быть выбрана, если размер пакета больше, чем третий порог.

Фиг. 12 показывает вариант осуществления устройства 1200 для передачи данных с выбором кодовой скорости на основании размера пакета. Устройство 1200 включает в себя средство для получения по меньшей мере одного порога для использования при выборе кодовой скорости (модуль 1212), средство для определения размера пакета для использования при передаче данных (модуль 1214), средство для выбора кодовой скорости из множества кодовых скоростей для кода FEC на основании размера пакета и по меньшей мере одного порога (модуль 1216), средство для кодирования пакета в соответствии с основной кодовой скоростью для кода FEC, чтобы получить кодированный пакет (модуль 1218), средство для прокалывания кодированного пакета, если необходимо, чтобы получить выбранную кодовую скорость для пакета (модуль 1220), и средство для обработки и передачи кодированного пакета после какого-либо прокалывания (модуль 1222).

Фиг. 13 показывает вариант осуществления процесса 1300 для приема данных с выбором кодовой скорости на основании размера пакета. По меньшей мере один порог для использования при выборе кодовой скорости может быть определен, например, на основании размера памяти, количества чередований HARQ, доступных для передачи данных, количества пакетов для параллельного приема и т.д. (этап 1312). По меньшей мере один порог может быть послан в передатчик, например базовую станцию (этап 1314). Альтернативно, информация о возможности (например, размер памяти) может быть послана в передатчик, и передатчик может определить по меньшей мере один порог на основании информации о возможности.

Пакет, закодированный в соответствии с выбранной кодовой скоростью для кода FEC, может быть принят (этап 1316). Код FEC может являться Турбокодом, кодом LDPC, сверточным кодом или некоторым другим кодом. Кодовая скорость может быть выбрана из множества кодовых скоростей для кода FEC на основании размера пакета для пакета и по меньшей мере одного порога. Пакет может быть декодирован в соответствии с выбранной кодовой скоростью для кода FEC (этап 1318). В течение этапа 1318 отношения LLR могут быть вычислены для битов кода, принятых для пакета. Стирания могут быть вставлены для битов кода, не принятых для пакета, например, проколотых (исключенных) битов кода или еще не переданных. Пакет может быть декодирован на основании этих LLR для принятых битов кода и стираний для битов кода, которые не приняты.

Фиг. 14 показывает вариант осуществления устройства 1400 для приема данных с выбором кодовой скорости на основании размера пакета. Устройство 1400 включает в себя средство для определения по меньшей мере одного порога для использования при выборе кодовой скорости (модуль 1412), средство для посылки по меньшей мере одного порога в передатчик (модуль 1414), средство для приема пакета, закодированного в соответствии с выбранной кодовой скоростью для кода FEC, с кодовой скоростью, выбираемой из множества кодовых скоростей для кода FEC на основании размера пакета для пакета и по меньшей мере одного порога (модуль 1416), и средство для декодирования пакета в соответствии с выбранной кодовой скоростью для кода FEC (модуль 1418).

Фиг. 15 показывает вариант осуществления процесса 1500 для передачи данных с выбором кода FEC на основании размера пакета. По меньшей мере один порог для использования при выборе кода FEC может быть получен, например принят от терминала или вычислен на основании информации о возможности (например, о размере памяти), принятой от терминала (этап 1512). Размер пакета для использования при передаче данных может быть определен, например, как показано в уравнении (1) (этап 1514). Код FEC может быть выбран из множества кодов FEC различных типов на основании размера пакета и по меньшей мере одного порога (этап 1516). Пакет может быть закодирован в соответствии с выбранным кодом FEC, чтобы получить кодированный пакет (этап 1518). Кодированный пакет может быть обработан и передан (этап 1520).

В течение этапа 1516 размер пакета может сравниваться по меньшей мере с одним порогом и код FEC может быть выбран из множества кодов FEC на основании результата сравнения. В одном варианте осуществления множество кодов FEC могут включать в себя Турбокод, код LDPC и сверточный код. Сверточный код может быть выбран, если размер пакета меньше чем или равен первому порогу. Турбокод может быть выбран, если размер пакета больше чем первый порог, и меньше чем или равен второму порогу. Код LDPC может быть выбран, если размер пакета больше, чем второй порог.

Фиг. 16 показывает вариант осуществления устройства 1600 для передачи данных с выбором кода FEC на основании размера пакета. Устройство 1600 включает в себя средство для получения по меньшей мере одного порога для использования при выборе кода FEC (модуль 1612), средство для определения размера пакета для использования при передаче данных (модуль 1614), средство для выбора кода FEC из множества кодов FEC различных типов на основании размера пакета и по меньшей мере одного порога (модуль 1616), средство для кодирования пакета в соответствии с выбранным кодом FEC, чтобы получить кодированный пакет (модуль 1618), и средство для обработки и передачи кодированного пакета (модуль 1620).

Фиг. 17 показывает вариант осуществления процесса 1700 для приема данных с выбором кода FEC на основании размера пакета. По меньшей мере один порог для использования при выборе кода FEC может быть определен, например, на основании размера памяти, количества чередований HARQ, доступных для передачи данных, количества пакетов, подлежащих приему параллельно, и т.д. (этап 1712). По меньшей мере один порог может быть послан в передатчик, например базовую станцию (этап 1714). Альтернативно, информация о возможности (например, о размере памяти) может быть послана в передатчик и использоваться передатчиком, чтобы определить по меньшей мере один порог.

Пакет, закодированный в соответствии с выбранным кодом FEC, может быть принят (этап 1716). Код FEC может быть выбран из множества кодов FEC различных типов на основании размера пакета для пакета и по меньшей мере одного порога. Множество кодов FEC может включать в себя Турбокод, код LDPC, сверточный код и т.д. Пакет может быть декодирован в соответствии с выбранным кодом FEC (этап 1718). В течение этапа 1718 отношения LLR могут быть вычислены для битов кода, принятых для этого пакета. Стирания могут быть вставлены для битов кода, не принятых для пакета, например проколотых битов кода или еще не переданных. Пакет может быть декодирован на основании LLR для принятых битов кода и стираний для непринятых битов кода.

Фиг. 18 показывает вариант осуществления устройства 1800 для приема данных с выбором кодовой скорости FEC на основании размера пакета. Устройство 1800 включает в себя средство для определения по меньшей мере одного порога для использования при выборе кода FEC (модуль 1812), средство для посылки по меньшей мере одного порога в передатчик (модуль 1814), средство для приема пакета, кодированного в соответствии с выбранным кодом FEC, причем код FEC выбирается из множества кодов FEC различных типов на основании размера пакета для этого пакета и по меньшей мере одного порога (модуль 1816), и средство для декодирования пакета в соответствии с выбранным кодом FEC (модуль 1818).

Модули на фиг. 12, 14, 16 и 18 могут содержать процессоры, устройства электроники, устройства аппаратного обеспечения, компоненты электроники, логические схемы, блоки памяти и т.д. или любую их комбинацию.

Способы, описанные в настоящем изобретении, могут быть реализованы различными способами. Например, эти способы могут быть реализованы в аппаратном обеспечении, программно-аппаратном обеспечении, программном обеспечении или их комбинации. Для реализации аппаратного обеспечения процессоры, используемые для выполнения способов в объекте (например, базовой станции или терминале), могут быть реализованы в одной или более специализированных интегральных схемах (ASIC), цифровых процессорах сигналов (DSP), цифровых устройствах обработки сигналов (DSPD), программируемых логических устройствах (PLD), программируемых пользователем вентильных матрицах (FPGA), процессорах, контроллерах, микроконтроллерах, микропроцессорах, электронных устройствах, других электронных модулях, предназначенных для выполнения функций, описанных в настоящим изобретении, компьютере или их комбинации.

Для программно-аппаратного обеспечения и/или программной реализации способы могут быть реализованы с кодом (например, процедуры, функции, модули, команды и т.д.), который выполняет функции, описанные в настоящим изобретении. Обычно любой считываемый компьютером/процессором носитель, материально воплощающий программно-аппаратное обеспечение и/или программный код, может использоваться в осуществлении методик, описанных здесь. Например, программно-аппаратное обеспечение и/или программный код могут быть сохранены в памяти (например, памяти 332 или 372 на фиг. 3) и выполнены процессором (например, процессором 330 или 370). Память может быть реализована внутри процессора или быть внешней к процессору. Программно-аппаратное обеспечение и/или программный код могут также быть сохранены в считываемом компьютером/процессором носителе, таком как память с произвольным доступом (ОЗУ, RAM), постоянное запоминающее устройство (ПЗУ, ROM), энергонезависимая память с произвольным доступом (NVRAM), программируемое постоянное ЗУ (ППЗУ), электрически стираемое ППЗУ (СППЗУ), флэш-память, гибкий диск, компакт-диск (CD), цифровой универсальный диск (DVD), магнитное или оптическое запоминающее устройство и т.д. Код может быть выполнимым одним или более компьютерами/процессорами и может вынуждать этот компьютер/процессор выполнить некоторые аспекты функциональных возможностей, описанных здесь.

Предыдущее описание раскрытия предоставляется, чтобы позволить любому специалисту реализовать или использовать изобретение. Различные модификации изобретения являются очевидными для специалистов, и универсальные принципы, определенные здесь, могут быть применены к другим изменениям без отрыва от объема или сущности изобретения. Таким образом, раскрытие не предназначается, чтобы быть ограниченным описанными примерами и вариантами осуществления, но должно получить самый широкий объем, совместимый с раскрытыми принципами и новыми признаками.

Изобретение относится к связи, более конкретно к способам для кодирования и декодирования данных. Раскрыты способы кодирования и декодирования данных. В одном аспекте множество кодовых скоростей для кода с прямым исправлением ошибок (FEC) может поддерживаться, и подходящая кодовая скорость может быть выбрана на основании размера пакета. Передатчик может принять по меньшей мере один порог для использования при выборе кодовой скорости, определить размер пакета для использования при передаче данных и выбирать кодовую скорость из множества кодовых скоростей на основании размера пакета и по меньшей мере одного порога. В другом аспекте могут поддерживаться множественные коды FEC различных типов (например, Турбо, LDPC и сверточные коды), и подходящий код FEC может быть выбран на основании размера пакета. Передатчик может получить, по меньшей мере, один порог для использования при выборе кода FEC и может выбирать код FEC из множества кодов FEC на основании размера пакета и, по меньшей мере, одного порога. Технический результат - обеспечение эффективности кодирования и декодирования данных. 14. н. и 38 з.п. ф-лы, 18 ил.

1. Устройство для передачи данных, содержащее:

по меньшей мере, один процессор, конфигурированный для определения размера пакета для использования при передаче данных и выбора кодовой скорости из множества кодовых скоростей для кода с прямым исправлением ошибок (FEC) на основании размера пакета с прогрессивно более высокими кодовыми скоростями, выбираемыми для прогрессивно больших размеров пакета; и

память, подсоединенную к упомянутому, по меньшей мере, одному процессору;

причем, по меньшей мере, один процессор конфигурируется для сравнения размера пакета, по меньшей мере, с одним порогом и выбора кодовой скорости из множества кодовых скоростей на основании результата сравнения.

2. Устройство по п.1, в котором, по меньшей мере, один процессор конфигурируется, чтобы принимать, по меньшей мере, один порог от терминала и выбирать кодовую скорость для передачи данных на терминал на основании размера пакета и, по меньшей мере, одного порога.

3. Устройство по п.1, в котором, по меньшей мере, один процессор конфигурируется, чтобы принимать информацию о возможности от терминала, определить, по меньшей мере, один порог, на основании информации о возможности, и выбирать кодовую скорость для передачи данных на терминал, на основании размера пакета и, по меньшей мере, одного порога.

4. Устройство по п.1, в котором множество кодовых скоростей содержит кодовую скорость 1/5, кодовую скорость 1/3 и кодовую скорость 1/2.

5. Устройство по п.4, в котором, по меньшей мере, один процессор конфигурируется, чтобы выбирать кодовую скорость 1/5, если размер пакета меньше, чем или равен первому порогу, чтобы выбирать кодовую скорость 1/3, если размер пакета больше, чем первый порог, и меньше, чем или равен второму порогу, и выбирать кодовую скорость 1/2, если размер пакета больше, чем второй порог, и меньше, чем или равен третьему порогу.

6. Устройство по п.5, в котором множество кодовых скоростей также содержит кодовую скорость 2/3 и в котором, по меньшей мере, один процессор конфигурируется, чтобы выбирать кодовую скорость 2/3, если размер пакета больше, чем третий порог.

7. Устройство по п.1, в котором, по меньшей мере, один процессор конфигурируется, чтобы кодировать пакет в соответствии с основной кодовой скоростью для кода FEC, чтобы получить кодированный пакет, и проколоть кодированный пакет, если необходимо, чтобы получить выбранную кодовую скорость для пакета.

8. Устройство по п.1, в котором кодом FEC является Турбо код.

9. Устройство по п.1, в котором код FEC содержит код проверки на четность низкой плотности (LDPC).

10. Способ для передачи данных, содержащий этапы, на которых: определяют размер пакета для использования при передаче данных; и

выбирают кодовую скорость из множества кодовых скоростей для кода с прямым исправлением ошибок (FEC) на основании размера пакета, с прогрессивно более высокими кодовыми скоростями, выбираемыми для прогрессивно больших размеров пакета;

принимают, по меньшей мере, один порог от терминала, и в котором выбор кодовой скорости содержит выбор кодовой скорости для передачи данных на терминал на основании размера пакета и, по меньшей мере, одного порога.

11. Способ по п.10, в котором множество кодовых скоростей содержит кодовую скорость 1/5, кодовую скорость 1/3 и кодовую скорость 1/2 и в котором выбор кодовой скорости содержит выбор кодовой скорости 1/5, если размер пакета меньше, чем или равен первому порогу, выбор кодовой скорости 1/3, если размер пакета больше, чем первый порог, и меньше, чем или равен второму порогу, и выбор кодовой скорости 1/2, если размер пакета больше, чем второй порог, и меньше, чем или равен третьему порогу.

12. Способ по п.11, в котором множество кодовых скоростей также содержит кодовую скорость 2/3 и в котором выбор кодовой скорости также содержит выбор кодовой скорости 2/3, если размер пакета больше, чем третий порог.

13. Способ по п.10, также содержащий: кодирование пакета в соответствии с основной кодовой скоростью для кода FEC, чтобы получить кодированный пакет; и прокалывание кодированного пакета, если необходимо, чтобы получить выбранную кодовую скорость для пакета.

14. Устройство для передачи данных, содержащее:

средство для определения размера пакета для использования при передаче данных; и

средство для выбора кодовой скорости из множества кодовых скоростей для кода с прямым исправлением ошибок (FEC), на основании размера пакета с прогрессивно более высокими кодовыми скоростями, выбираемыми для прогрессивно больших размеров пакета; и

средство для приема, по меньшей мере, одного порога от терминала, и в котором средство для выбора кодовой скорости содержит средство для выбора кодовой скорости для передачи данных на терминал, на основании размера пакета и, по меньшей мере, одного порога.

15. Устройство по п.14, в котором множество кодовых скоростей содержит кодовую скорость 1/5, кодовую скорость 1/3 и кодовую скорость 1/2 и в котором средство для выбора кодовой скорости содержит средство для выбора кодовой скорости 1/5, если размер пакета меньше, чем или равен первому порогу, средство для выбора кодовой скорости 1/3, если размер пакета больше, чем первый порог, и меньше, чем или равен второму порогу, и средство для выбора кодовой скорости 1/2, если размер пакета больше, чем второй порог, и меньше, чем или равен третьему порогу.

16. Устройство по п.15, в котором множество кодовых скоростей также содержит кодовую скорость 2/3 и в котором средство для выбора кодовой скорости также содержит средство для выбора кодовой скорости 2/3, если размер пакета больше, чем третий порог.

17. Устройство по п.14, также содержащее: средство для кодирования пакета в соответствии с основной кодовой скоростью для кода FEC, чтобы получить кодированный пакет; и средство для прокалывания кодированного пакета, если необходимо, чтобы получить выбранную кодовую скорость для пакета.

18. Считываемый компьютером носитель, содержащий коды для того, чтобы заставить, по меньшей мере, один компьютер выполнять способ для передачи данных, в котором определяют размер пакета для использования при передаче данных; выбирают кодовую скорость из множества кодовых скоростей для кода с прямым исправлением ошибок (FEC) на основании размера пакета, с прогрессивно более высокими кодовыми скоростями, выбираемыми для прогрессивно больших размеров пакета; принимают, по меньшей мере, один порог от терминала, и в котором выбор кодовой скорости содержит выбор кодовой скорости для передачи данных на терминал на основании размера пакета и, по меньшей мере, одного порога.

19. Устройство для передачи данных, содержащее: по меньшей мере один процессор, конфигурированный, чтобы принять пакет, закодированный в соответствии с выбранной кодовой скоростью для кода с прямым исправлением ошибок (FEC), причем кодовая скорость выбирается из множества кодовых скоростей для кода FEC на основании размера пакета для пакета, и декодировать пакет в соответствии с выбранной кодовой скоростью для кода FEC; и

память, подсоединенную к упомянутому, по меньшей мере, одному процессору и конфигурированную, чтобы хранить пакет; и

причем упомянутый, по меньшей мере, один процессор конфигурируется, чтобы определить, по меньшей мере, один порог для использования при выборе кодовой скорости и посылать, по меньшей мере, один порог в базовую станцию, и в котором кодовая скорость для пакета выбирается на основании также, по меньшей мере, одного порога.

20. Устройство по п.19, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы определить, по меньшей мере, один порог на основании размера памяти.

21. Устройство по п.19, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы определить, по меньшей мере, один порог на основании количества чередований гибридного автоматического запроса повторной передачи (HARQ), доступных для передачи данных.

22. Устройство по п.19, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы определить, по меньшей мере, один порог на основании количества пакетов для приема их параллельно.

23. Устройство по п.19, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы посылать информацию о возможности в базовую станцию, и в котором кодовая скорость для пакета выбирается также на основании, по меньшей мере, одного порога, определенного на основании информации о возможности.

24. Устройство по п.19, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы вычислить логарифмические отношения правдоподобия (LLR) для битов кода, принятых для пакета, и сохранять эти LLR в памяти.

25. Устройство по п.24, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы вставить стирания для битов кода, не принятых для этого пакета, и декодировать пакет на основании LLR для принятых битов кода и стираний для не принятых битов кода.

26. Способ для передачи данных, содержащий этапы, на которых:

принимают пакет, закодированный в соответствии с выбранной кодовой скоростью для кода с прямым исправлением ошибок (FEC), причем кодовая скорость выбирается из множества кодовых скоростей для кода FEC на основании размера пакета для пакета;

декодируют пакет в соответствии с выбранной кодовой скоростью для кода FEC; и

определяют, по меньшей мере, один порог для использования для выбора кодовой скорости; и посылают, по меньшей мере, один порог в базовую станцию, при этом кодовая скорость для пакета выбирается также на основании, по меньшей мере, одного порога.

27. Способ по п.26, в котором декодирование пакета содержит вычисление логарифмических отношений правдоподобия (LLR) для битов кода, принятых для пакета, вставку стираний для битов кода, не принятых для пакета, и декодирование пакета на основании LLR для принятых битов кода и стираний для не принятых битов кода.

28. Устройство для передачи данных, содержащее:

средство для приема пакета, закодированного в соответствии с выбранной кодовой скоростью для кода с прямым исправлением ошибок (FEC), причем кодовая скорость выбирается из множества кодовых скоростей для кода FEC на основании размера пакета;

средство для декодирования пакета в соответствии с выбранной кодовой скоростью для кода FEC;

средство для определения, по меньшей мере, одного порога для использования при выборе кодовой скорости; и

средство для посылки, по меньшей мере, одного порога в базовую станцию, при этом кодовая скорость для пакета выбирается также на основании, по меньшей мере, одного порога.

29. Устройство по п.28, в котором средство для декодирования пакета содержит средство для вычисления логарифмических отношений правдоподобия (LLR) для битов кода, принятых для пакета, средство для вставки стираний для битов кода, не принятых для этого пакета, и средство для декодирования пакета на основании LLR для принятых битов кода и стираний для непринятых битов кода.

30. Устройство для передачи данных, содержащее:

по меньшей мере, один процессор, конфигурированный, чтобы определить размер пакета для использования при передаче данных и выбирать код с прямым исправлением ошибок (FEC) из множества кодов FEC на основании размера пакета;

память, подсоединенную к упомянутому, по меньшей мере, одному процессору; и

причем упомянутый, по меньшей мере, один процессор конфигурируется для сравнения размера пакета, по меньшей мере, с одним порогом и выбора кода FEC из множества кодов FEC на основании результата сравнения.

31. Устройство по п.30, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы принять, по меньшей мере, один порог от терминала и выбирать код FEC для передачи данных на терминал на основании размера пакета и, по меньшей мере, одного порога.

32. Устройство по п.30, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы принимать информацию о возможности от терминала, определить, по меньшей мере, один порог на основании информации о возможности и выбирать код FEC для передачи данных на терминал, на основании размера пакета и, по меньшей мере, одного порога.

33. Устройство по п.30, в котором множество кодов FEC содержит сверточный код и Турбо код.

34. Устройство по п.33, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы выбирать сверточный код, если размер пакета меньше, чем или равен первому порогу, и выбирать Турбо код, если размер пакета больше, чем первый порог, и меньше, чем или равен второму порогу.

35. Устройство по п.34, в котором множество кодов FEC также содержат код проверки на четность низкой плотности (LDPC) и в котором упомянутый по меньшей мере один процессор конфигурируется, чтобы выбирать код LDPC, если размер пакета больше, чем второй порог.

36. Способ для передачи данных, содержащий этапы:

определение размера пакета для использования при передаче данных;

выбор кода с прямым исправлением ошибок (FEC) из множества кодов FEC на основании размера пакета; и

прием, по меньшей мере, одного порога от терминала, и в котором этап выбора кода FEC содержит выбор кода FEC для передачи данных на терминал на основании размера пакета и, по меньшей мере, одного порога.

37. Способ по п.36, в котором множество кодов FEC содержит сверточный код и Турбо код и в котором выбор кода FEC содержит выбор сверточного кода, если размер пакета меньше, чем или равен первому порогу, и выбор Турбо кода, если размер пакета больше, чем первый порог, и меньше, чем или равен второму порогу.

38. Способ по п.37, в котором множество кодов FEC также содержит код проверки на четность низкой плотности (LDPC) и в котором выбор кода FEC также содержит выбор кода LDPC, если размер пакета больше, чем второй порог.

39. Устройство для передачи данных, содержащее:

средство для определения размера пакета для использования при передаче данных;

средство для выбора кода с прямым исправлением ошибок (FEC) из множества кодов FEC на основании размера пакета; и

средство для приема, по меньшей мере, одного порога от терминала, и в котором средство для выбора кода FEC содержит средство для выбора кода FEC для передачи данных на терминал на основании размера пакета и, по меньшей мере, одного порога.

40. Устройство по п.39, в котором множество кодов FEC содержит сверточный код и Турбо код и в котором средство для выбора кода FEC содержит средство для выбора сверточного кода, если размер пакета меньше, чем или равен первому порогу, и средство для выбора Турбо кода, если размер пакета больше, чем первый порог, и меньше, чем или равен второму порогу.

41. Устройство по п.40, в котором множество кодов FEC также содержит код проверки на четность низкой плотности (LDPC) и в котором средство для выбора кода FEC также содержит средство для выбора кода LDPC, если размер пакета больше, чем второй порог.

42. Считываемый компьютером носитель, содержащий: коды для того, чтобы заставить, по меньшей мере, один компьютер выполнять способ для передачи данных, содержащий этапы, на которых: определяют размер пакета для использования при передаче данных; выбирают код с прямым исправлением ошибок (FEC) из множества кодов FEC на основании размера пакета; и принимают, по меньшей мере, один порог от терминала, и в котором этап выбора кода FEC содержит выбор кода FEC для передачи данных на терминал на основании размера пакета и, по меньшей мере, одного порога.

43. Устройство для передачи данных, содержащее: по меньшей мере, один процессор, конфигурированный, чтобы принять пакет, кодированный в соответствии с кодом с прямым исправлением ошибок (FEC), выбранный из множества кодов FEC на основании размера пакета для пакета, и декодировать пакет в соответствии с выбранным кодом FEC; и память, подсоединенную, по меньшей мере, к одному процессору и конфигурированную, чтобы хранить пакет, причем упомянутый, по меньшей мере, один процессор конфигурируется, чтобы определить, по меньшей мере, один порог для использования при выборе кода FEC и послать, по меньшей мере, один порог в базовую станцию, и в котором код FEC для пакета выбирается на основании также, по меньшей мере, одного порога.

44. Устройство по п.43, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы определить, по меньшей мере, один порог на основании размера памяти.

45. Устройство по п.43, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы определить, по меньшей мере, один порог на основании количества чередований гибридного автоматического запроса повторной передачи (HARQ), доступных для передачи данных.

46. Устройство по п.43, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы посылать информацию о возможности в базовую станцию, и в котором код FEC для пакета выбирается на основании также, по меньшей мере, одного порога, определенного на основании информации о возможности.

47. Устройство по п.43, в котором упомянутый, по меньшей мере, один процессор конфигурируется для вычисления логарифмических отношений правдоподобия (LLR) для битов кода, принятых для пакета, и сохранения этих LLR в памяти.

48. Устройство по п.47, в котором упомянутый, по меньшей мере, один процессор конфигурируется, чтобы вставить стирания для битов кода, не принятых для этого пакета, и декодировать пакет на основании LLR для принятых битов кода и стираний для непринятых битов кода.

49. Способ для передачи данных, содержащий этапы:

прием пакета, закодированного в соответствии с кодом с прямым исправлением ошибок (FEC), выбранным из множества кодов FEC на основании размера пакета для пакета; декодирование пакета в соответствии с выбранным кодом FEC; и определение, по меньшей мере, одного порога для использования для выбора кода FEC; и посылку, по меньшей мере, одного порога в базовую станцию, в котором код FEC для пакета выбирается на основании также, по меньшей мере, одного порога.

50. Способ по п.49, в котором декодирование пакета содержит вычисление логарифмических отношений правдоподобия (LLR) для битов кода, принятых для пакета, вставку стираний для битов кода, не принятых для пакета, и декодирование пакета на основании LLR для принятых битов кода и стираний для непринятых битов кода.

51. Устройство для передачи данных, содержащее:

средство для приема пакета, кодированного в соответствии с кодом с прямым исправлением ошибок (FEC), выбранным из множества кодов FEC на основании размера пакета для пакета;

средство для декодирования пакета в соответствии с выбранным кодом FEC; и

средство для определения, по меньшей мере, одного порога для использования при выборе кода с прямым исправлением ошибок; и средство для посылки, по меньшей мере, одного порога в базовую станцию, в котором код FEC для пакета выбирается на основании также, по меньшей мере, одного порога.

52. Устройство по п.51, в котором средство для декодирования пакета содержит средство для вычисления логарифмических отношений правдоподобия (LLR) для битов кода, принятых для пакета, средство для вставки стираний для битов кода, не принятых для этого пакета, и средство для декодирования пакета на основании LLR для принятых битов кода и стираний для непринятых битов кода.

| RU 94015375 А1, 28.09.1996 | |||

| US 2006218459 А1, 28.09.2006 | |||

| ПЕРЕДАЧА ПАКЕТНЫХ ДАННЫХ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2001 |

|

RU2237977C2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ДИАФРАГМОВЫЙ ВЕНТИЛЬ | 2000 |

|

RU2190141C2 |

| US 2006251010 A1, 09.11.2006 | |||

| Двухполярный источник питания | 1986 |

|

SU1372304A1 |

Авторы

Даты

2011-08-20—Публикация

2008-01-04—Подача