Предлагаемое устройство относится к радиотехнике и может быть использовано для формирования сигналов с широкополосной угловой модуляцией в системах, предназначенных для радиоэлектронной борьбы (РЭБ).

В системах РЭБ широкое применение нашла широкополосная модуляция (заградительная помеха). Для расширения спектра используются различные виды модуляции. В частности, применяются сигналы с линейной частотной модуляцией, а также шумоподобные сигналы.

Синтезаторы частот, основанные на фазовой автоподстройке частоты (ФАПЧ), работающие в режиме частотной и фазовой модуляции, широко известны (патенты на полезные модели RU 56747 H03C 3/09, H03L 7/18, RU 83883 H03C 3/09, H03L 7/18, RU 84651 H03L 7/16, патенты на изобретения SU 1252909 H03C 3/10, H03L 7/18, RU 2358384 H03L 7/18). Синтезаторы позволяют получить модулированные по частоте или фазе колебания с заданным шагом перестройки по частоте, при этом стабильность частоты этих сигналов определяется прецизионным кварцевым опорным генератором. Однако синтезаторы частот, основанные на фазовой автоподстройке частоты, имеют значительное и зачастую слишком длительное для практического применения время перестройки с одной частоты на другую.

Структурная схема типового синтезатора частот, основанного на системе ФАПЧ, приведена на рис.1.1 стр.9 в книге [1].

В таком синтезаторе на первый вход частотно-фазового детектора (ЧФД) подается сигнал опорного генератора после деления его частоты в делителе с фиксированным коэффициентом деления, а на второй вход ЧФД – сигнал с генератора, управляемого напряжением (ГУН) после деления его частоты в делителе с переменным коэффициентом деления (ДПКД).

Выработанный сигнал рассогласования на выходе ЧФД через фильтр нижних частот (ФНЧ) управляет частотой сигнала ГУН таким образом, что она после устранения рассогласования принимает значение, точно равное частоте сигнала опорного генератора, поделенной на коэффициент деления ДФКД и умноженной на коэффициент деления ДПКД.

В книге [2] предложено несколько методов формирования частотной модуляции (ЧМ) в синтезаторах частот на основе импульсно-фазовой автоподстройки частоты (ИФАПЧ). Модуляция осуществляется за счет изменения коэффициента деления ДПКД по закону изменения модулирующего сигнала. При этом имеют место искажения ЧМ сигнала, обусловленные дискретным действием системы ИФАПЧ.

Таким образом, в синтезаторе частот, построенном на основе системы ИФАПЧ, возможно осуществление частотной или фазовой модуляции, но с рядом ограничений, связанных с конечным быстродействием синтезатора и с вносимыми системой ИФАПЧ искажениями.

Наиболее близкий по технической сущности к предлагаемому является синтезатор частот, приведенный в патенте на полезную модель RU 104801 H03C 3/00, Н03L 7/00, 7/18, принятый за прототип.

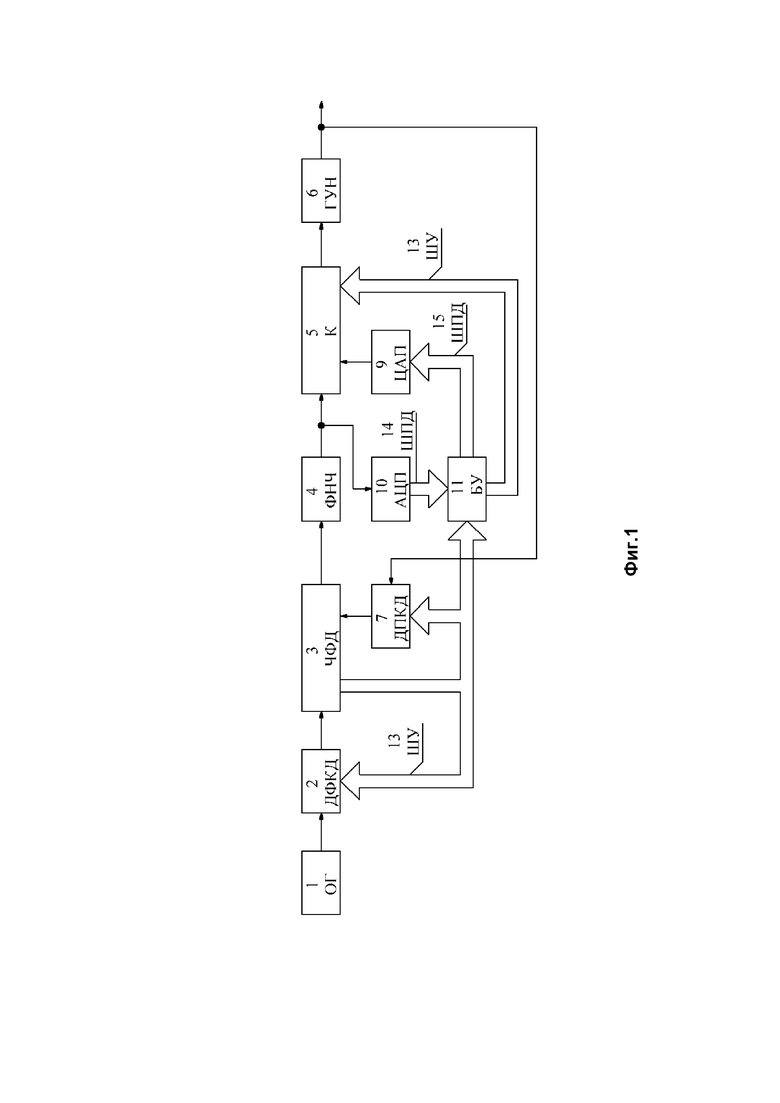

Функциональная схема устройства-прототипа представлена на фиг. 1, где введены следующие обозначения:

1 – опорный генератор (ОГ);

2 – делитель с фиксированным коэффициентом деления (ДФКД);

3 – частотно-фазовый детектор (ЧФД);

4 – фильтр нижних частот (ФНЧ);

5 – коммутатор (К);

6 – генератор, управляемый напряжением (ГУН);

7 – делитель с переменным коэффициентом деления (ДПКД);

9 – цифро-аналоговый преобразователь (ЦАП);

10 – аналого-цифровой преобразователь (АЦП);

11 – блок управления (БУ);

13 – шина управления (ШУ);

14 – первая шина передачи данных (ШПД);

15 – вторая шина передачи данных (ШПД).

Устройство-прототип содержит последовательно соединенные опорный генератор (ОГ) 1, делитель с фиксированным коэффициентом деления (ДФКД) 2, частотно-фазовый детектор (ЧФД) 3, фильтр нижних частот (ФНЧ) 4, коммутатор (К) 5 и генератор, управляемый напряжением (ГУН) 6, выход которого является выходом устройства и подключен к входу делителя с переменным коэффициентом деления 7, выход которого соединен со вторым входом частотно-фазового детектора 3. Выход ФНЧ 4 соединен с входом АЦП 10, выход которого по первой шине передачи данных (ШПД) 14 соединен с первым входом блока управления 11, один выход которого по второй ШПД 15 соединен с входом ЦАП 9, выход которого подключен ко второму входу коммутатора 5, третий вход которого соединен со вторым выходом блока управления 11. Кроме того, второй выход ЧФД 3 по шине управления ШУ 13 соединен со вторыми входами ДФКД 2, ДПКД 7 и блока управления 11.

Устройство-прототип работает следующим образом.

Выходной сигнал ОГ 1 через ДФКД 2 подается на первый вход ЧФД 3, на второй вход которого через ДПКД 7 подается выходное напряжение ГУН 6. Сигнал рассогласования частот двух сигналов с выхода ЧФД 3 через ФНЧ 4 и коммутатор 5 подается на управляющий вход ГУН 6, частота сигнала которого меняется до тех пор, пока, поделенная в заданное число раз в ДПКД 7, она не будет равной частоте выходного сигнала ОГ 1, поделенной в заданное число раз в ДФКД 2. В этом случае выходное напряжение на выходе ЧФД 3 перестанет изменяться, частота выходного сигнала ГУН 6 будет сохраняться требуемой, при этом на блок управления 11 с первого выхода ЧФД 3 по шине управления 13 поступит сигнал о синхронизме в системе.

По ШУ 13 со второго выхода блока управления 11 на коммутатор 5 подается управляющий сигнал, в результате чего на ГУН 6 проходит сигнал с ФНЧ 4. Далее по ШУ 13 в блоки ДФКД 2 и ДПКД 7 поступают сигналы записи коэффициентов деления, соответствующие нижней частоте спектра заданного сигнала. С момента подачи сигнала синхронизма от ЧФД 3 в БУ 11, в АЦП 10 происходит оцифровка напряжения с блока ФНЧ 4, код которого по ШПД 14 передается в БУ 11 и запоминается. Затем происходит аналогичная процедура, только запоминается код напряжения с ФНЧ 4, соответствующего верхней частоте спектра.

ИФАПЧ участвует во время оцифровки управляющих напряжений, а потом отключается.

Далее формируемые в БУ 11 управляющие сигналы по ШПД 15 подаются на вход коммутатора 5, который производит коммутацию выходных сигналов ЦАП 9 с входом ГУН 6. Затем в БУ 11 формируются сигналы кодов управляющих напряжений для блока ГУН 6, соответствующие закону модуляции, адаптированному к значениям управления для верхней и нижней частоты спектра модулированного сигнала, которые по ШПД 15 поступают в ЦАП 9.

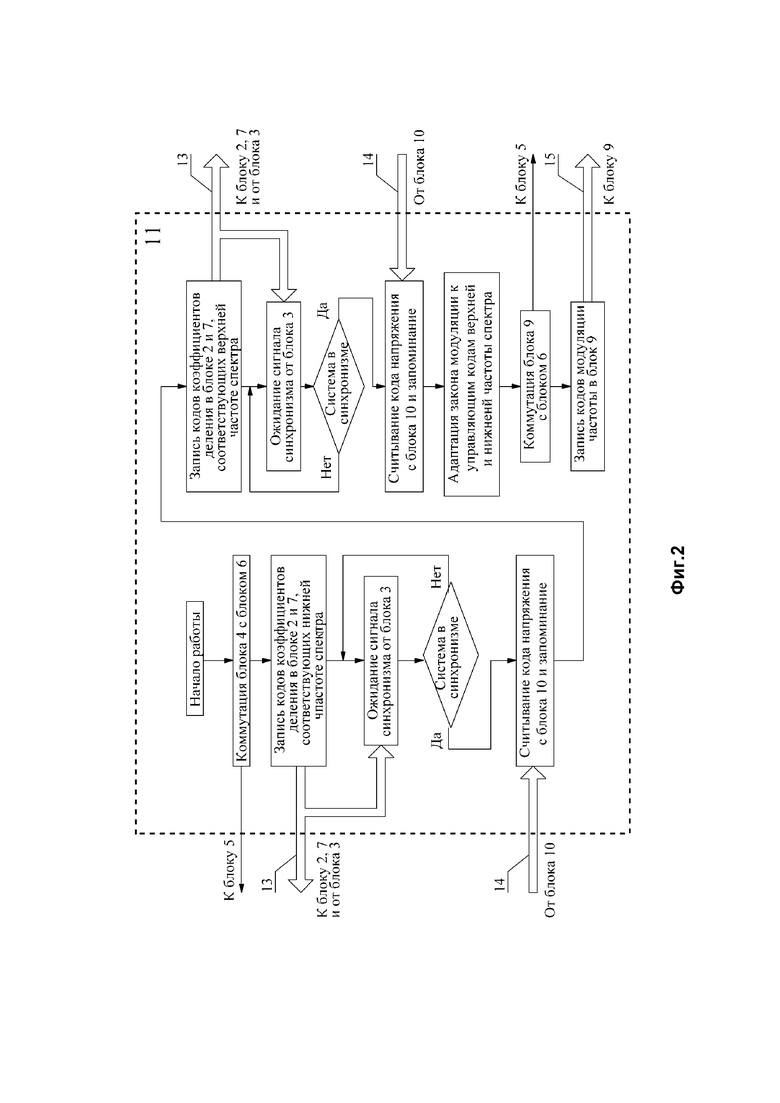

Блок управления 11 может быть выполнен на основе микроконтроллера, укрупнённый алгоритм работы которого приведен на фиг. 2. В представленном алгоритме частота сигнала с широкополосной модуляцией меняется в пределах от нижней до верхней частоты по определённому закону.

Таким образом, происходит изменение частоты сигнала ГУН 6 не системой ИФАПЧ, а непосредственно с выхода ЦАП 9, что повышает быстродействие и не вносит искажений в модулированный сигнал.

Недостатками устройства-прототипа являются:

- влияние нелинейной передаточной функции ГУН на равномерность спектра формируемого сигнала при работе в режиме формирования широкополосных сигналов;

- влияние входного сопротивления АЦП на токи утечки в цепи управления системы ИФАПЧ во время оцифровки напряжения с блока ФНЧ 4, вследствие чего система может выходить из состояния синхронизма и значения напряжений управления будут ошибочными.

Задача, на решение которой направлено заявляемое устройство, заключается в линеаризации передаточной функции ГУН при работе в режиме формирования широкополосных сигналов, а также в устранении влияния входного сопротивления АЦП на токи утечки в цепи управления системы ИФАПЧ.

Для решения поставленной задачи в синтезатор частот с широкополосной модуляцией, содержащий последовательно соединенные опорный генератор, делитель с фиксированным коэффициентом деления (ДФКД), частотно-фазовый детектор (ЧФД), фильтр нижних частот (ФНЧ), коммутатор и генератор, управляемый напряжением (ГУН), выход которого является выходом устройства, и соединен с входом делителя с переменным коэффициентом деления (ДПКД), выход которого соединен со вторым входом ЧФД, второй выход которого по шине управления (ШУ) соединен со вторыми входами ДФКД, ДПКД и блока управления, при этом выход аналого-цифрового преобразователя (АЦП) по первой шине передачи данных (ШПД) соединен с первым входом блока управления, выход которого соединен с соответствующим входом коммутатора; выход цифро-аналогового преобразователя (ЦАП) подключен ко второму входу коммутатора, кроме того, вход ЦАП является входом второй шины передачи данных, согласно изобретению, введены операционный усилитель и генератор шума, вход которого подсоединен ко второму выходу блока управления, а выход по второй шине передачи данных соединен с входом ЦАП; операционный усилитель включен между выходом ФНЧ и входом АЦП.

Блок-схема предлагаемого устройства приведена на фиг. 3, где введены следующие обозначения:

1 – опорный генератор (ОГ);

2 – делитель с фиксированным коэффициентом деления (ДФКД);

3 – частотно-фазовый детектор (ЧФД);

4 – фильтр нижних частот (ФНЧ);

5 – коммутатор (К);

6 – генератор, управляемый напряжением (ГУН);

7 – делитель с переменным коэффициентом деления (ДПКД);

8 – операционный усилитель;

9 – цифро-аналоговый преобразователь (ЦАП);

10 – аналого-цифровой преобразователь (АЦП);

11 – блок управления (БУ);

12 – генератор шума (ГШ);

13 – шина управления (ШУ);

14 – первая шина передачи данных (ШПД);

15 – вторая шина передачи данных (ШПД).

Предлагаемое устройство содержит последовательно соединенные опорный генератор 1, делитель с фиксированным коэффициентом деления 2, частотно-фазовый детектор 3, фильтр нижних частот 4, коммутатор 5 и генератор, управляемый напряжением 6, выход которого является выходом устройства и соединен с входом делителя с переменным коэффициентом деления 7, выход которого соединен со вторым входом частотно-фазового детектора 3. Выход ФНЧ 4 через операционный усилитель 8 соединен с входом АЦП 10, выход которого по первой шине передачи данных (ШПД) 14 соединен с первым входом блока управления 11, выход которого соединен с входом генератора шума 12, выход которого по второй ШПД 15 соединен с входом ЦАП 9, выход которого подключен ко второму входу коммутатора 5, третий вход которого соединен со вторым выходом блока управления 11. Кроме того, второй выход ЧФД 3 по шине управления ШУ 13 соединен со вторыми входами ДФКД 2, ДПКД 7 и блока управления 11.

Заявляемое устройство работает следующим образом.

Выходной сигнал ОГ 1 через ДФКД 2 подается на первый вход ЧФД 3, на второй вход которого через ДПКД 7 подается выходное напряжение ГУН 6. Сигнал рассогласования частот двух сигналов с выхода ЧФД 3 через ФНЧ 4 и коммутатор 5 подается на вход ГУН 6, частота сигнала которого меняется до тех пор, пока поделенная в заданное число раз в ДПКД 7, она не будет равной частоте выходного сигнала ОГ 1, поделенной в заданное число раз в ДФКД 2. В этом случае, выходное напряжение на выходе ЧФД 3 перестанет изменяться, частота выходного сигнала ГУН 6 будет сохраняться требуемой, при этом на блок управления 11 с первого выхода ЧФД 3 по шине управления 13 поступит сигнал о синхронизма в системе.

По ШУ 13 со второго выхода блока управления 11 на коммутатор 5 податься управляющий сигнал, в результате чего на ГУН 6 проходит сигнал с ФНЧ 4. Далее от БУ 11 по ШУ 13 в ДФКД 2 и ДПКД 7 поступают сигналы записи N коэффициентов деления, соответствующие частотам от F1 до FN спектра заданного широкополосного сигнала. С момента подачи сигнала синхронизма от ЧФД 3 в БУ 11, в АЦП 10 происходит оцифровка напряжения с ФНЧ 4, код которого по ШПД 14 передается в БУ 11 и запоминается. Данная процедура повторяется N раз, только запоминаются коды напряжений с ФНЧ 4, соответствующие частотам от F1 до FN спектра. Далее формируемые в БУ 11 управляющие сигналы подаются на ГШ 12 для выработки заданного вида шума, для увеличения эффективности системы, путем зашумления сигнала. С помощью генератора шума внося дополнительные шумоподобные помехи. БУ 11 производит коммутацию выхода ЦАП 9 со входом ГУН 6 и сигнала включения ГШ 12. Из ГШ 12 по ШПД 15 производит запись кодов в ЦАП 9, который формирует напряжения управления для ГУН 6, которые соответствуют закону модуляции, адаптированному к значениям управления для частот спектра от F1 до FN. Так происходит изменение частоты сигнала ГУН 6 не системой ИФАПЧ по цепи управления ГУН 6, а непосредственно с ЦАП 9, что повышает быстродействие и не вносит искажений в модулированный сигнал. При этом ОУ 8 служит в качестве развязки для устранения влияния входного сопротивления АЦП на токи утечки в цепи управления системы ИФАПЧ.

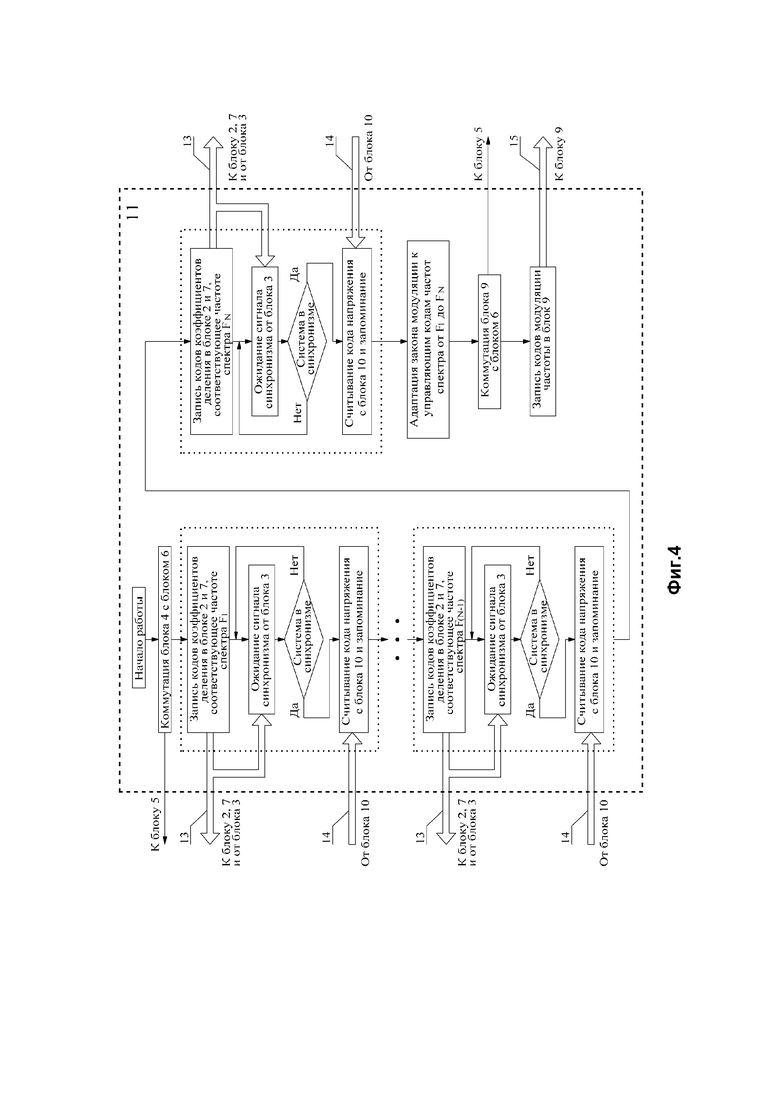

БУ 11 может быть выполнен на основе микроконтроллера, укрупнённый алгоритм работы которого приведен на фиг. 4. В представленном алгоритме частота сигнала с широкополосной модуляцией меняется в переделах от F1 до FN частоты своего спектра по определенному закону.

Источники информации:

1. Синтезаторы частот с системой импульсно-фазовой автопордстройки // Левин В.А., Малиновский В.Н., Романов С.К. – М.: Радио и связь, 1989 г.

2. Формирование ЧМ сигналов в синтезаторах с автоподстройкой // Тихомиров Н.М., Романов С.К., Леньшин А.В. – М.: Радио и связь, 2004 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот с частотной модуляцией в SDR приложениях | 2018 |

|

RU2688243C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2440668C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2394367C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2416158C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

Изобретение относится к синтезатору частот с широкополосной модуляцией в радиопередающих устройствах. Технический результат – достижение линеаризации передаточной функции генератора, управляемого напряжением (ГУН) при формировании широкополосных сигналов и устранение влияния входного сопротивления аналого-цифрового преобразователя (АЦП) на токи утечки в цепи управления в системе импульсно-фазовой автоподстройки частоты (ИФАПЧ). Для этого в указанном синтезаторе предусмотрены: опорный генератор (ОП), делитель с фиксированным коэффициентом деления (ДФКД), частотно-фазовый детектор (ЧФД), фильтр нижних частот (ФНЧ), коммутатор, ГУН, делитель с переменным коэффициентом деления (ДПКД), блок управления (БУ), цифроаналоговый преобразователь (ЦАП). Кроме того, также предусмотрены дополнительно введенные к ним операционный усилитель (ОУ) и генератор шума (ГШ). 4 ил.

Синтезатор частот с широкополосной модуляцией, содержащий последовательно соединенные опорный генератор, делитель с фиксированным коэффициентом деления (ДФКД), частотно-фазовый детектор (ЧФД), фильтр нижних частот (ФНЧ), коммутатор и генератор, управляемый напряжением (ГУН), выход которого является выходом устройства и соединен с входом делителя с переменным коэффициентом деления (ДПКД), выход которого соединен со вторым входом ЧФД, второй выход которого по шине управления (ШУ) соединен со вторыми входами ДФКД, ДПКД и блока управления, при этом выход аналого-цифрового преобразователя (АЦП) по первой шине передачи данных (ШПД) соединен с первым входом блока управления, выход которого соединен с третьим входом коммутатора; выход цифроаналогового преобразователя (ЦАП) подключен к второму входу коммутатора, кроме того, вход ЦАП является входом второй шины передачи данных, отличающийся тем, что введены операционный усилитель и генератор шума, вход которого подсоединен к второму выходу блока управления, а выход по второй шине передачи данных соединен с входом ЦАП; операционный усилитель включен между выходом ФНЧ и входом АЦП.

| Способ получения пищевых продуктов для питания работающих с радиоактивными изотопами | 1956 |

|

SU104801A1 |

| СИНТЕЗАТОР ЧАСТОТ С ЧАСТОТНОЙ ИЛИ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2004 |

|

RU2280945C1 |

| US 7333789 B2, 19.02.2008 | |||

| JP 4282998 B2, 24.06.2009 | |||

| Торцовое уплотнение | 1989 |

|

SU1657813A1 |

Авторы

Даты

2020-02-05—Публикация

2019-09-04—Подача