Изобретение относится к области радиотехники и может быть использовано в устройствах передачи информации для повышения информационной скрытности, помехозащищенности и достоверности передаваемого цифрового сигнала в сети связи.

Известно устройство, описанное в патенте РФ №2142200, H04B 7/005, 26.05.1998 г., «Частотно-адаптивная радиолиния для передачи среднескоростных потоков дискретной информации», в котором производится передача информации на множестве частотных субканалов многочастотного группового канала, ведется подсчет количества ошибок передачи информации в субканалах, при превышении частости ошибок в определенном субканале происходит его замена, при превышении частости смены субканалов производится изменение частоты группового субканала передачи информации.

Недостатком данного устройства является то, что производится адаптация лишь по одному из множества параметров передаваемого сигнала, одновременное использование нескольких частотных субканалов для осуществления связи ухудшает ЭМС описанного устройства.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в авторском свидетельстве №1585902, H04B 7/00, 15.08.1990 г., «Многопараметрическая адаптивная система радиосвязи для передачи дискретной информации», принятое за прототип.

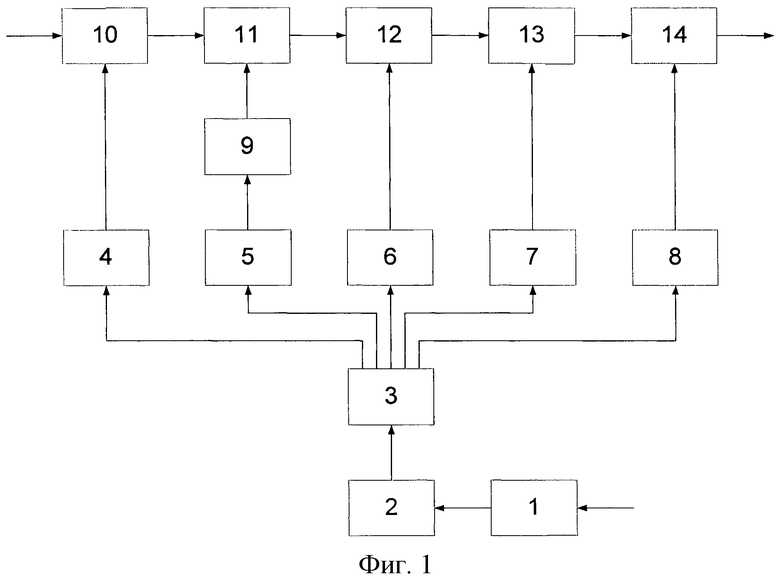

Устройство-прототип представлено на фиг.1 (передающая часть), фиг.2 (приемная часть), где введены следующие обозначения:

1 - приемник обратного канала,

2 - декодер,

3 - дешифратор команд,

4 - блок управления кодированием,

5 - блок управления скоростью передачи,

6 - блок выбора вида модуляции,

7 - блок выбора оптимальной частоты,

8 - блок управления мощностью передачи,

9 - тактовый генератор,

10 - блок кодирования,

11 - буферный накопитель,

12 - блок модуляции,

13 - возбудитель,

14 - усилитель мощности,

15 - блок преобразования частоты,

16 - блок демодуляции,

17 - блок исключения избыточности,

18 - блок выбора частоты,

19 - измеритель уровня сигнала,

20 - нелинейный элемент,

21 - полосовой фильтр,

22 - выпрямитель,

23 - блок оценки качества приема,

24 - блок аналого-цифрового преобразования,

25 - блок формирования эталона,

26 - первый блок сравнения,

27 - второй блок сравнения,

28 - третий блок сравнения,

29 - четвертый блок сравнения,

30 - буферный блок,

31 - дешифратор состояния,

32 - первый счетчик,

33 - второй счетчик,

34 - третий счетчик,

35 - четвертый счетчик,

36 - пятый счетчик,

37 - формирователь команд управления частотой,

38 - формирователь команд управления мощностью,

39 - формирователь команд управления видом модуляции,

40 - формирователь команд управления скоростью передачи,

41 - формирователь команд управления избыточностью кодирования,

42 - блок дешифрации команд,

43 - элемент ИЛИ,

44 - кодер,

45 - передатчик обратного канала.

Передающая часть устройства-прототипа, изображенная на фиг.1, содержит последовательно соединенные приемник обратного канала 1, декодер 2, дешифратор команд 3; последовательно соединенные блок кодирования 10, буферный накопитель 11, блок модуляции 12, возбудитель 13, усилитель мощности 14, выход которого является информационным выходом передающей части устройства-прототипа, а вход блока кодирования 10 является информационным входом передающей части устройства-прототипа; при этом первый выход дешифратора команд 3 через блок управления кодированием 4 соединен со вторым входом блока кодирования 10, второй выход дешифратора команд 3 через последовательно соединенные блок управления скоростью передачи 5 и тактовый генератор 9 соединен со вторым входом буферного накопителя 11, третий выход дешифратора команд 3 через блок выбора вида модуляции 6 соединен со вторым входом блока модуляции 12, четвертый выход дешифратора команд 3 через блок выбора оптимальной частоты 7 соединен со вторым входом возбудителя 13, пятый выход дешифратора команд 3 через блок управления мощностью передачи 8 соединен со вторым входом усилителя мощности 14, вход приемника обратного канала 1 является управляющим входом передающей части устройства-прототипа.

Приемная часть устройства-прототипа, изображенная на фиг.2, содержит последовательно соединенные блок преобразования частоты 15, блок демодуляции 16, блок исключения избыточности 17, выход которого является информационным выходом приемной части устройства-прототипа, а вход блока преобразования частоты 15 является информационным входом приемной части устройства-прототипа; последовательно соединенные блок выбора частоты 18, измеритель уровня сигнала 19, выход которого соединен со вторым входом блока аналого-цифрового преобразования 24, первый вход которого соединен со вторым выходом блока выбора частоты 18, вход которого соединен с информационным входом приемной части устройства-прототипа, последовательно соединенные нелинейный элемент 20, полосовой фильтр 21, выпрямитель 22, выход которого соединен с третьим входом блока аналого-цифрового преобразования 24; выход блока преобразования частоты 15, кроме того, соединен со входом нелинейного элемента 20, а выход блока демодуляции 16 соединен со входом блока оценки качества приема 23, выход которого соединен с четвертым входом блока аналого-цифрового преобразования 24, первый выход которого соединен с первым входом первого блока сравнения 26, выход которого соединен с первым входом буферного блока 30, второй выход блока аналого-цифрового преобразования 24 соединен с первым входом второго блока сравнения 27, выход которого соединен со вторым входом буферного блока 30, третий выход блока аналого-цифрового преобразования 24 соединен с первым входом третьего блока сравнения 28, выход которого соединен с третьим входом буферного блока 30, четвертый выход блока аналого-цифрового преобразования 24 соединен с первым входом четвертого блока сравнения 29, выход которого соединен с четвертым входом буферного блока 30; на вход блока формирования эталона 25 поступают допусковые значения параметров, измеряемых блоками 18-23, выход блока формирования эталона 25 соединен со вторыми входами первого 26, второго 27, третьего 28 и четвертого 29 блоков сравнения; первый, второй, третий и четвертый выходы буферного блока 30 соединены с соответствующими входами дешифратора состояния 31, первый выход которого соединен со входом первого счетчика 32 и со вторым входом формирователя команд управления частотой 37, второй выход дешифратора состояния 31 соединен с третьим входом второго счетчика 33 и со вторым входом формирователя команд управления мощностью 38, третий выход дешифратора состояния 31 соединен с третьим входом третьего счетчика 34 и со вторым входом формирователя команд управления видом модуляции 39, первый выход первого счетчика 32 соединен с первыми входами второго 33, третьего 34, четвертого 35 и пятого 36 счетчиков, первые выходы которых соединены соответственно с первыми входами формирователей команд управления мощностью 38, видом модуляции 39, скоростью передачи 40, избыточностью кодирования 41, выходы которых соединены соответственно со вторым, третьим, четвертым и пятым входами элемента ИЛИ 43, выход которого соединен со входом кодера 44, выход которого соединен со входом передатчика обратного канала 45, выход которого является управляющим выходом приемной части устройства-прототипа; второй выход первого счетчика 32 соединен с первым входом формирователя команд управления частотой 37, выход которого соединен с первым входом элемента ИЛИ 43; выходы формирователей команд управления частотой 37 видом модуляции 39, скоростью передачи 40, избыточностью кодирования 41 также соединены соответственно с первым, вторым, третьим и четвертым входами блока дешифрации команд 42, первый и четвертый выходы которого соединены со вторыми входами блоков преобразования частоты 15 и исключения избыточности 17, второй и третий выходы блока дешифрации команд 42 соединены с соответствующими входами блока демодуляции 16; выход второго счетчика 33 также соединен с третьим входом третьего счетчика 34 и со вторым входом формирователя команд управления видом модуляции 39, выход третьего счетчика 34 также соединен с третьим входом четвертого счетчика 35 и со вторым входом формирователя команд управления скоростью передачи 40, выход четвертого счетчика 35 также соединен с третьим входом пятого счетчика 36 и вторым входом формирователя команд управления избыточностью кодирования 41, выход пятого счетчика 36, кроме того, соединен со вторыми входами первого 32, второго 33, третьего 34, четвертого 35 и пятого 36 счетчиков.

Устройство-прототип работает следующим образом.

Приемник 1 обратного канала производит прием команд управления в виде дискретных сигналов и передает принятые команды управления на декодер 2, который снимает с команд управления кодовую избыточность и передает их на дешифратор команд управления 3, который определяет по поступающей на его вход команде управления адрес одного из исполнительных блоков управления 4-8, а также выдает на их входы сигналы на управление параметрами передачи по радиоканалу. Блок управления кодированием 4 регулирует избыточность и выдает управляющие сигналы на блок кодирования 10, который предназначен для изменения способа кодирования дискретной информации, поступающей на его вход. Блок управления скоростью передачи информации 5 выдает управляющие сигналы на тактовый генератор 9, изменяя его частоту. Тактовый генератор 9 определяет скорость съема информации в тракт передачи из буферного накопителя 11. Буферный накопитель 11 предназначен для согласования скорости передачи дискретной информации от источников информации, поступающей через блок 10, с установленной скоростью передачи по каналу. Блок модуляции 12, возбудитель 13 и усилитель мощности 14 являются узлами радиопередатчика с расширенными возможностями по излучению радиосигналов различного вида и регулируемой мощностью излучения. С выхода усилителя мощности, являющегося информационным выходом передающей части устройства-прототипа, сигнал передается в пространство. Блок выбора вида модуляции 6 формирует управляющие сигналы для блока модуляции 12 с целью изменения вида радиосигнала в канале. Блок выбора оптимальной частоты 7 выдает управляющие сигналы на возбудитель 13 с целью изменения несущей частоты передачи по радиоканалу. Блок управления мощностью передачи 8 выдает управляющие сигналы на усилитель мощности 14 с целью изменения его коэффициента усиления.

Блок преобразования частоты 15 и блок демодуляции 16 представляют собой узлы супергетеродинного радиоприемника с расширенными возможностями по приему радиосигналов различного вида. Блок исключения избыточности 17 предназначен для устранения избыточности, заложенной в дискретную информацию блоком кодирования 10 на передающей стороне системы радиосвязи. Блок выбора частоты 18 предназначен для анализа помеховой обстановки на частотах рабочего диапазона радиоприемника по соотношению сигнал/шум и выбора оптимальной частоты. Блок 19 измерения уровня сигнала измеряет уровень принимаемого сигнала на установленной несущей частоте. Нелинейный элемент 20, полосовой фильтр 21 и выпрямитель 22 представляют собой в совокупности схему выявления помех, сосредоточенных по спектру с принимаемым сигналом. Блок оценки качества приема 23 предназначен для анализа импульсов дискретной информации после блока демодуляции 16, например по краевым искажениям и дроблениям.

Результаты анализа с блоков 18, 19, 22, 23 поступают на блок 24 аналого-цифрового преобразования, который предназначен для преобразования результатов измерения, полученных блоками 18, 19, 22, 23, из аналоговой формы в цифровую, необходимую для работы последующих блоков системы. Блок формирования эталона 25 предназначен для хранения в дискретной форме данных о допусковых значениях параметров, измеряемых блоками 18-23, и выдачи их на блоки сравнения 26-29, которые сравнивают измеренные значения параметров с эталонными и выдают управляющие сигналы «Норма» или «Больше нормы» на буферный блок 30. Блок 30 предназначен для запоминания результатов сравнения с блоков 26-29 и передачи их на дешифратор состояния 31, который предназначен для преобразования двоичного кода, поступающего на четыре его входа с буферного блока 30, в управляющие позиционные сигналы на одном из трех его выходов. Временной режим работы дешифратора состояния 31 задается хронирующим сигналом. Счетчики 32-36 ступеней адаптации предназначены для подсчета количества управляющих сигналов, появляющихся на выходах дешифратора состояния 31, и определяют количество градаций изменений параметров передачи (мощности, несущих частот, видов радиосигналов, скоростей передачи информации и способов кодирования).

Формирователи команд на изменение несущей частоты 37, на изменение мощности излучаемых радиосигналов 38, на изменение вида модуляции 39, на изменение тактовой частоты 40, на введение избыточности 41 формируют по сигналам с дешифратора состояния 31 управляющие дискретные команды на изменение соответствующих параметров передачи по радиоканалу с целью их последующей передачи через элемент ИЛИ 43, кодер 44 и передатчик обратного канала 45 на передающую сторону системы радиосвязи. Эти управляющие дискретные команды (кроме команды управления мощностью) также подаются на входы блока дешифрации команд 42, который, в зависимости от адреса блока, которому предназначается команда, отправляет ее с одного из своих выходов на вход одного из блоков 15-17, чем обеспечивается адаптация параметров приема сигнала.

Недостатком данного устройства является то, что изменение несущих частот передачи подчинено фиксированному закону, что дает возможность для подавления такого радиосигнала следящей помехой, синхронно изменяющей свою частоту по тому же закону; кроме того, адаптируемые параметры изменяются только в сторону повышения помехозащищенности: повышения избыточности кодирования, уменьшения скорости передачи, увеличения мощности излучаемого сигнала, и не изменяются в обратную сторону до полного перебора счетчиками всего ансамбля адаптируемых параметров в случае улучшения помеховой обстановки, что снижает общую эффективность такой системы связи. Передача командных сигналов по обратному каналу производится на фиксированной частоте, а для повышения ее помехозащищенности предусмотрено только кодирование управляющего сигнала, а значит, путем выявления и подавления этого управляющего сигнала будет вызван срыв работы механизма адаптации и работы системы в целом.

Задачей предлагаемого технического решения является устранение предсказуемости в алгоритме изменения адаптируемых параметров, удаление из системы передачи информации обратного канала управления, создание возможности динамического изменения адаптируемых параметров системы в соответствии с изменением помеховой обстановки не только в худшую, но и в лучшую сторону для повышения эффективности системы, учет ЭМС со смежными радиосредствами, удешевление схемы устройства путем исключения необходимости осуществления приема одновременно на всех используемых частотах.

Для решения поставленной задачи в многопараметрическую адаптивную систему передачи информации, содержащую буферный накопитель, блок управления скоростью передачи, блок управления кодированием, выход которого соединен со вторым входом блока кодирования, блок управления мощностью передачи, выход которого соединен со вторым входом усилителя мощности, согласно изобретению введены источник цифровой информации, выход которого соединен с первым входом буферного накопителя, с первым входом динамического счетчика, выход которого соединен с первым входом ключа наличия информации в буфере, выход «0» которого соединен со входом буфера квитирования, выход которого соединен со вторым входом первого сумматора, выход которого соединен с первым входом блока кодирования, а выход «1» ключа наличия информации в буфере соединен со вторым входом буферного накопителя; последовательно соединенные второй сумматор, сумматор по модулю два, модулятор, выход которого соединен с первым входом усилителя мощности, выход которого соединен со входом антенно-фидерного устройства, при этом выход блока кодирования соединен с первым входом второго сумматора, а первый вход блока кодирования соединен с выходом первого сумматора, первый вход которого соединен со вторым выходом буферного накопителя, первый выход которого соединен со входом источника цифровой информации, второй выход буферного накопителя соединен, кроме того, со вторым входом динамического счетчика, третий вход которого соединен с первым выходом блока генерации опорных частот; выход антенно-фидерного устройства соединен со вторыми входами контрольных приемников и с четвертым входом приемника, первый выход которого соединен со вторым входом блока выделения служебной информации, первый выход которого соединен со вторым входом блока декодирования, первый выход которого соединен со входом получателя цифровой информации; первый выход блока выделения служебной информации также соединен со вторым входом блока кодирования и входом 1.4 блока хранения служебной информации; первый выход блока генерации опорных частот соединен также со вторыми входами второго и третьего триггеров, первым входом первого синтезатора частот и третьим входом приемника, второй выход которого соединен с третьим входом блока декодирования, второй выход которого соединен с первыми входами счетчиков 1.4 и 1.5, выходы которых соединены соответственно с первым и вторым входами процессора, первый выход которого соединен со входом блока управления скоростью передачи, выход которого соединен со входом блока генерации опорных частот и со входом 1.2 блока хранения служебной информации; второй выход процессора соединен со входом блока управления кодированием, выход которого соединен со входом 1.4 блока хранения служебной информации; третий выход процессора соединен со входом блока управления мощностью передачи; первый выход блока генерации опорных частот также соединен с первым входом электронных часов, со входом счетчика 1.3, выход которого соединен со входом 1.1 решающего устройства, с первыми входами контрольных приемников, выходы которых соединены со входами 1…K решающего устройства, выходы 1…K которого соединены соответственно со входами 1…K блока генерации псевдослучайной последовательности псевдопеременной перестройки рабочей частоты, первый выход которого соединен с третьим входом первого синтезатора частот, выход которого соединен со вторым входом модулятора; выходы 1…K решающего устройства соединены также соответственно со входами 1…K блока хранения служебной информации; выход счетчика 1.3 соединен также с первым входом блока выделения служебной информации, второй выход которого соединен со входом 1.2 решающего устройства, выход 1.1 которого соединен со входом 1.3 блока генерации псевдослучайной последовательности псевдопеременной перестройки рабочей частоты, второй выход которого соединен с четвертым входом первого синтезатора частоты и с первым входом приемника; третий выход блока выделения служебной информации соединен со вторым входом электронных часов, выход которых соединен со входом 1.1 блока генерации псевдослучайной последовательности псевдопеременной перестройки рабочей частоты, со входом 1.3 блока хранения служебной информации, с первым входом генератора псевдослучайной последовательности шумоподобного сигнала, первый выход которого соединен со вторым входом сумматора по модулю два; четвертый выход блока выделения служебной информации соединен со входом 1.2 блока хранения служебной информации, со входом блока генерации опорных частот, второй выход которого соединен с первым входом второго триггера, выход которого соединен со входом 1.1 блока хранения служебной информации, выход которого соединен со вторым входом второго сумматора; третий выход блока генерации опорных частот соединен с первым входом третьего триггера, выход которого соединен со вторым входом ключа наличия информации в буфере; третий выход блока генерации опорных частот также соединен с первым входом блока декодирования, третий выход которого соединен со вторыми входами счетчиков 1.4 и 1.5; четвертый выход блока генерации опорных частот соединен со вторым входом генератора псевдослучайной последовательности шумоподобного сигнала, второй выход которого соединен со вторым входом приемника; пятый выход блока генерации опорных частот соединен со вторым входом первого синтезатора частоты; на вход 1.2 блока генерации псевдослучайной последовательности псевдопеременной перестройки рабочей частоты поступают начальные настройки разрешенных частот (например, посредством введения с клавиатуры оператором).

Предлагаемая многопараметрическая адаптивная система передачи информации состоит из 2 идентичных приемопередатчиков, схема одного из которых представлена на фиг.3, где введены следующие обозначения:

46 - источник цифровой информации,

11 - буферный накопитель,

47 - первый сумматор,

10 - блок кодирования,

48 - второй сумматор,

49 - сумматор по модулю два,

50 - модулятор,

14 - усилитель мощности,

51 - антенно-фидерное устройство,

52 - динамический счетчик,

53 - блок хранения служебной информации,

54 - первый синтезатор частот,

55 - ключ наличия информации в буфере,

56 - буфер квитирования,

57 - генератор псевдослучайной последовательности шумоподобного сигнала (ГПСП ШПС),

58 - блок генерации опорных частот,

58.1 - генератор тактовых импульсов,

58.2.1.1 - счетчик 1.1,

58.2.1…16.2.K - счетчики 1…K,

58.3 - первый коммутатор,

58.4 - счетчик 1.2,

58.5 - второй коммутатор,

58.6 - первый триггер,

58.7 - первый ключ,

59 - второй триггер,

60 - третий триггер,

5 - блок управления скоростью передачи,

4 - блок управления кодированием,

61 - электронные часы,

62 - блок генерации псевдослучайной последовательности псевдопеременной перестройки рабочей частоты (блок генерации ПСП ППРЧ),

62.1 - первый элемент памяти,

62.2 - третий сумматор,

62.3 - первый блок выборки,

62.4.1…62.4.K - элементы «и» 1.1…1.K,

62.5 - генератор псевдослучайной последовательности (ГПСП),

62.6 - четвертый сумматор,

62.7 - второй элемент памяти,

62.8 - второй блок выборки,

63 - процессор,

8 - блок управления мощностью передачи,

64 - счетчик 1.3,

65 - решающее устройство,

65.1 - линия задержки (ЛЗ),

65.2 - третий элемент памяти,

65.3.1…65.3.K - элементы «и» 2.1…2.K,

65.4 - четвертый элемент памяти,

66.1…66.K - контрольные приемники,

67 - счетчик 1.4,

68 - счетчик 1.5,

69 - получатель цифровой информации,

70 - блок декодирования,

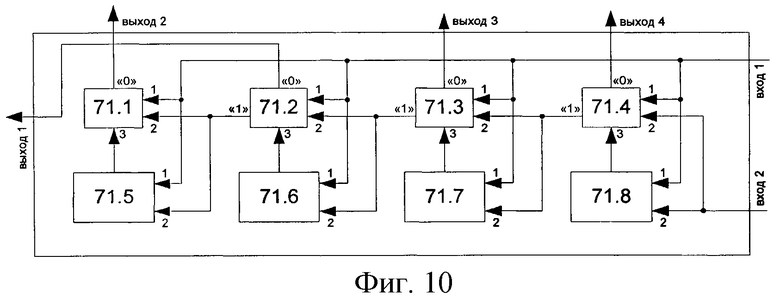

71 - блок выделения служебной информации,

71.1 - второй ключ,

71.2 - третий ключ,

71.3 - четвертый ключ,

71.4 - пятый ключ,

71.5 - четвертый счетчик,

71.6 - пятый счетчик,

71.7 - шестой счетчик,

71.8 - седьмой счетчик,

72 - приемник,

72.1 - блок синхронизации и выделения служебной информации,

72.2 - первый блок корреляционной обработки,

72.3 - первый демодулятор,

72.4 - первый усилитель промежуточной частоты,

72.5 - первый преобразователь частоты,

72.6 - второй синтезатор частот,

72.7 - второй блок корреляционной обработки,

72.8 - второй демодулятор,

72.9 - второй усилитель промежуточной частоты,

72.10 - второй преобразователь частоты,

72.11 - шестой ключ,

72.12 - третий синтезатор частот.

Приемопередатчик содержит: источник цифровой информации 46, выход которого соединен с первым входом буферного накопителя 11 и первым входом динамического счетчика 52, первый выход буферного накопителя 11 соединен со входом источника цифровой информации 46, второй выход буферного накопителя 11 соединен с первым входом первого сумматора 47 и вторым входом динамического счетчика 52; выход первого сумматора 47 соединен с первым входом блока кодирования 10, выход которого соединен с первым входом второго сумматора 48, выход которого соединен с первым входом сумматора по модулю два 49, выход которого соединен с первым входом модулятора 50, выход которого соединен с первым входом усилителя мощности 14, выход которого соединен со входом антенно-фидерного устройства 51; выход динамического счетчика 52 соединен с первым входом ключа наличия информации в буфере 55, выход «0» которого соединен со входом буфера квитирования 56, выход которого соединен со вторым входом первого сумматора 47, а выход «1» ключа наличия информации в буфере 55 соединен со вторым входом буферного накопителя 11; первый выход блока генерации опорных частот 58 соединен с третьим входом динамического счетчика 52, со вторым входом второго триггера 59, выход которого соединен со входом 1.1 блока хранения служебных данных 53, выход которого соединен со вторым входом второго сумматора 48; первый выход блока генерации опорных частот 58 также соединен со вторым входом третьего триггера 60, выход которого соединен со вторым входом ключа наличия информации в буфере 55, первый выход блока генерации опорных частот 58 также соединен с первым входом электронных часов 61, выход которых соединен со входом 1.3 блока хранения служебных данных 53, с первым входом ГПСП ШПС 57, первый выход которого соединен со вторым входом сумматора по модулю два 49, а второй выход ГПСП ШПС 57 соединен со вторым входом приемника 72; первый выход блока генерации опорных частот 58 также соединен с первым входом счетчика 1.3 64, выход которого соединен со входом 1.1 решающего устройства 65, с первыми входами контрольных приемников 66.1…66.K, с первым входом блока выделения служебной информации 71; первый выход блока генерации опорных частот 58 также соединен с первым входом первого синтезатора частот 54 и с третьим входом приемника 72; выход электронных часов 61 также соединен со входом 1.1 блока генерации ПСП ППРЧ 62, первый выход которого соединен с третьим входом первого синтезатора частот 54, выход которого соединен со вторым входом модулятора 50; второй выход блока генерации ПСП ППРЧ 62 соединен с четвертым входом первого синтезатора частот 54 и с первым входом приемника 72; на вход 1.2 блока генерации ПСП ППРЧ 62 подается начальная установка разрешенных частот, второй выход блока генерации опорных частот 58 соединен с первым входом второго триггера 59, третий выход блока генерации опорных частот 58 соединен с первым входом третьего триггера 60 и с первым входом блока декодирования 70, четвертый выход блока генерации опорных частот 58 соединен со вторым входом ГПСП ШПС 57, пятый выход блока генерации опорных частот 58 соединен со вторым входом синтезатора частот 54; выход АФУ 51 соединен со вторыми входами контрольных приемников 66.1…66.K, выходы которых соединены соответственно со входами 1…K решающего устройства 65, выход 1.1 которого соединен со входом 1.3 блока генерации ПСП ППРЧ 62; выходы 1…K решающего устройства 65 соединены соответственно со входами 1…K блока генерации ПСП ППРЧ 62 и входами 1…K блока хранения служебной информации 53, выход АФУ 51 также соединен с четвертым входом приемника 72, первый выход которого соединен со вторым входом блока выделения служебной информации 71, первый выход которого соединен со вторым входом блока декодирования 70, первый выход которого соединен со входом получателя цифровой информации 69; первый выход блока выделения служебной информации 71 также соединен со вторым входом блока кодирования 10 и входом 1.4 блока хранения служебной информации 53, второй выход приемника 72 соединен с третьим входом блока декодирования 70, второй выход блока выделения служебной информации 71 соединен со входом 1.2 решающего устройства 65, третий выход блока выделения служебной информации 71 соединен со вторым входом электронных часов 61, четвертый выход блока выделения служебной информации 71 соединен со входом блока генерации опорных частот 58, со входом 1.2 блока хранения служебной информации 53, второй выход декодера 70 соединен с первыми входами счетчиков 1.4, 1.5, 67, 68, третий выход блока декодирования 70 соединен со вторыми входами счетчиков 1.4, 1.5, 67, 68, выходы которых соединены соответственно с первым и вторым входами процессора 63, первый выход которого соединен со входом блока управления скоростью передачи 5, выход которого соединен со входом блока генерации опорных частот 58 и со входом 1.2 блока хранения служебной информации 53; второй выход процессора 63 соединен со входом блока управления кодированием 4, выход которого соединен со вторым входом блока кодирования 10 и со входом 1.4 блока хранения служебной информации 53, третий выход процессора 63 соединен со входом блока управления мощностью передачи 8, выход которого соединен со вторым входом усилителя мощности 14.

Устройство, реализующее предлагаемую адаптивную систему передачи цифровой информации, работает следующим образом.

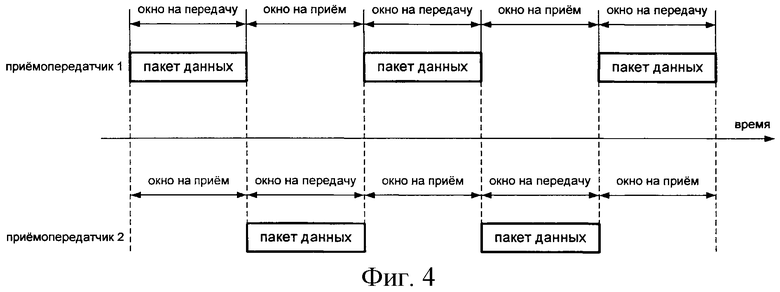

Обмен информацией происходит с разделением по времени так, что все время обмена делится на последовательность равных отрезков, которые будем в дальнейшем называть окнами на передачу и окнами на прием (см. фиг.4). Окно на передачу и окно на прием идут последовательно друг за другом, то есть одна из станций осуществляет передачу информации в четных окнах, а прием - в нечетных, другая - наоборот. Посредством организации жесткой синхронизации двух таких станций по времени и привязки номера следующей частоты приема/передачи, генерируемого по псевдослучайному закону ко времени удается избежать громоздкой, дорогостоящей и труднореализуемой на практике схемы приема получаемых сигналов одновременно на всех частотах, как это предлагается например в [1].

Перед установлением связи в радиолинии на обоих ее концах производится начальная установка разрешенных для осуществления связи частот для обеспечения ЭМС со смежными радиосредствами. В качестве начальной установки на вход 1.2 блока генерации ПСП ППРЧ 62 подается последовательность из K нулей и единиц (K - количество используемых для радиосвязи частот), в котором единица означает, что частота является разрешенной, ноль - запрещенной. Таблицы разрешенных частот на обоих концах радиолинии должны быть одинаковыми. Более подробно использование начальных установок будет представлено ниже при рассмотрении работы блока генерации ПСП ППРЧ 62. Для осуществления вхождения в сеанс связи один из приемопередатчиков, являющийся ведущим, начинает осуществлять передачу тестовых пакетов на фиксированной частоте, которая известна на приемном конце, и низкой скорости для повышения помехоустойчивости. Содержимое тестовых пакетов считывается из буфера квитирования 56 и не содержит полезной информации. Ведомый приемопередатчик осуществляет пассивный прием, при получении тестового пакета он выделяет из его служебной части текущее время в блоке выделения служебной информации 71 и записывает его в электронные часы 61, в следующем окне передает подтверждение его принятия в виде ответного пакета ведущему приемопередатчику. При получении ответного пакета от ведомого приемопередатчика считается, что приемопередатчики на обоих концах радиолинии находятся в синхронизме. Ведущий приемопередатчик устанавливает триггеры 59, 60 в положение «закрыто», сбрасывает счетчик 1.3 64 в нулевое состояние и начинает процесс обмена информацией в следующем окне, которое будет для него окном на передачу. Временная диаграмма, поясняющая данный алгоритм изображена на фиг.5. Рассмотрим работу приемопередатчика, когда уже достигнут синхронизм на обоих концах радиолинии.

С выхода генератора тактовых импульсов 58.1 блока генерации опорных частот 58 (см. фиг.6) тактовые импульсы с частотой F0 одновременно поступают на входы счетчиков 58.2.1.1, 58.2.1…58.2.K и на четвертый выход блока генерации опорных частот 58. Счетчики 58.2.1.1, 58.2.1…58.2.K выдают тактовый импульс на свой выход при накоплении определенного числа тактовых импульсов на своем входе, после чего сбрасываются в ноль и начинают счет снова. Они выполняют функции дискретных делителей частоты, то есть если на вход счетчика поступают импульсы с частотой ω1, на его выходе появляются импульсы с частотой ω2. Каждый выходной импульс появляется при наборе счетчиком α тактов на входе, значит справедливо соотношение:  , α - коэффициент деления. Коэффициент деления для счетчика 58.2.1.1 выбирается таким образом, чтобы он переполнялся, когда на его вход поступит количество тактовых импульсов, которое помещается в размер окна (размер окна выбирается заранее). Таким образом, на выходе счетчика 58.2.1.1 появляются тактовые импульсы с частотой следования окон приема/передачи и поступают на первый выход блока генерации опорных частот 58. Коэффициенты деления счетчиков 58.2.1…58.2.K выбираются в соответствии со скоростями передачи информации, причем частота следования импульсов на выходе счетчика 58.2.1 - наименьшая, на выходе счетчика 58.2.K - наибольшая. Чем больше частота следования импульсов на выходе счетчика, тем меньше длительность считываемых этими импульсами из элементов памяти битов полезной информации, а значит, на том же временном промежутке поместится больше бит полезной информации, и скорость передачи будет выше. Выбор скорости происходит посредством первого коммутатора 58.3, управляющие сигналы на который поступают со входа блока генерации опорных частот 58. Управляющие сигналы на изменение скорости могут поступать как с выхода блока управления скоростью передачи 5, так и с четвертого выхода блока выделения служебной информации 71, чем обеспечивается подстройка приемопередатчика под изменения скорости, произошедшие на дальнем конце радиолинии. Биты полезной информации могут передаваться на различных скоростях передачи, биты же служебной информации всегда передаются на наименьшей скорости из набора для большей помехоустойчивости и упрощения их выделения на приемном конце. Для этого импульсы с выхода счетчика 58.2.1 поступают на второй вход счетчика 58.4, который переполняется при поступлении на его вход r импульсов, где r - число бит служебной информации в пакете данных. При переполнении на его выходе появляется импульс сигнализации о начале части полезной информации пакета, поступающий на пятый выход блока генерации опорных частот, на четвертый вход второго коммутатора 58.5, который подключает на свой выход сигнал со своего второго входа при поступлении импульса на первый вход и сигнал со своего третьего входа при поступлении импульса на четвертый вход. На второй вход второго коммутатора 58.5 поступают импульсы, задающие постоянную скорость передачи r служебных бит пакета, на третий вход - импульсы, задающие адаптируемую переменную скорость передачи бит полезной информации пакета. Тактовый импульс начала нового окна, поступающий с выхода счетчика 58.2.1.1, сбрасывает счетчик 58.4 в нулевое состояние. Первый импульс с выхода счетчика 58.2.1.1, поступающий на первый триггер 58.6, «открывает» его и позволяет сигналам, поступающим на его вход, проходить без изменений на его выход. Это необходимо во избежание формирования неправильного первого пакета, когда счетчик 58.2.1.1 еще не выдал импульс на свой выход, а счетчики 58.2.1…58.2.K уже начали переполняться и выдают импульсы на свои выходы. Ключ 58.7 переключается в положение «1» импульсом начала окна с выхода счетчика 58.2.1.1, и импульсы, предназначенные для считывания служебной информации из блока хранения служебной информации 53, поступающие на его первый вход с выхода счетчика 58.2.1, выдаются на соответствующий выход «1» ключа. Когда счетчик 58.4 отсчитает r служебных бит пакета и переполнится, импульс с его выхода, поступающий на третий вход первого ключа 58.7, переключает его в положение «0», и импульсы считывания полезной информации из буферного накопителя 11 или буфера квитирования 56, поступающие с выхода одного из счетчиков 58.2.1…58.2.K, идут на выход «0» первого ключа 58.7. В результате работы описанного алгоритма, начиная с момента появления импульса на выходе счетчика 58.2.1.1, означающего начало очередного окна, с выхода «1» первого ключа 58.7 на второй выход блока генерации опорных частот 58 поступает r импульсов с периодичностью переполнения счетчика 58.2.1 и в соответствии с наименьшей скоростью передачи - импульсы считывания битов служебной информации, после чего первый ключ 58.7 переключается в положение «0», и с его выхода «0» на третий выход блока генерации опорных частот 58 поступает q импульсов с периодичностью переполнения одного из счетчиков 58.2.1…58.2.K в зависимости от управляющего сигнала выбора скорости передачи, поступающего на вход блока генерации опорных частот 58 - импульсы считывания битов полезной информации. При этом r - постоянная величина, а q - изменяется в соответствии с сигналами адаптации скорости передачи.

, α - коэффициент деления. Коэффициент деления для счетчика 58.2.1.1 выбирается таким образом, чтобы он переполнялся, когда на его вход поступит количество тактовых импульсов, которое помещается в размер окна (размер окна выбирается заранее). Таким образом, на выходе счетчика 58.2.1.1 появляются тактовые импульсы с частотой следования окон приема/передачи и поступают на первый выход блока генерации опорных частот 58. Коэффициенты деления счетчиков 58.2.1…58.2.K выбираются в соответствии со скоростями передачи информации, причем частота следования импульсов на выходе счетчика 58.2.1 - наименьшая, на выходе счетчика 58.2.K - наибольшая. Чем больше частота следования импульсов на выходе счетчика, тем меньше длительность считываемых этими импульсами из элементов памяти битов полезной информации, а значит, на том же временном промежутке поместится больше бит полезной информации, и скорость передачи будет выше. Выбор скорости происходит посредством первого коммутатора 58.3, управляющие сигналы на который поступают со входа блока генерации опорных частот 58. Управляющие сигналы на изменение скорости могут поступать как с выхода блока управления скоростью передачи 5, так и с четвертого выхода блока выделения служебной информации 71, чем обеспечивается подстройка приемопередатчика под изменения скорости, произошедшие на дальнем конце радиолинии. Биты полезной информации могут передаваться на различных скоростях передачи, биты же служебной информации всегда передаются на наименьшей скорости из набора для большей помехоустойчивости и упрощения их выделения на приемном конце. Для этого импульсы с выхода счетчика 58.2.1 поступают на второй вход счетчика 58.4, который переполняется при поступлении на его вход r импульсов, где r - число бит служебной информации в пакете данных. При переполнении на его выходе появляется импульс сигнализации о начале части полезной информации пакета, поступающий на пятый выход блока генерации опорных частот, на четвертый вход второго коммутатора 58.5, который подключает на свой выход сигнал со своего второго входа при поступлении импульса на первый вход и сигнал со своего третьего входа при поступлении импульса на четвертый вход. На второй вход второго коммутатора 58.5 поступают импульсы, задающие постоянную скорость передачи r служебных бит пакета, на третий вход - импульсы, задающие адаптируемую переменную скорость передачи бит полезной информации пакета. Тактовый импульс начала нового окна, поступающий с выхода счетчика 58.2.1.1, сбрасывает счетчик 58.4 в нулевое состояние. Первый импульс с выхода счетчика 58.2.1.1, поступающий на первый триггер 58.6, «открывает» его и позволяет сигналам, поступающим на его вход, проходить без изменений на его выход. Это необходимо во избежание формирования неправильного первого пакета, когда счетчик 58.2.1.1 еще не выдал импульс на свой выход, а счетчики 58.2.1…58.2.K уже начали переполняться и выдают импульсы на свои выходы. Ключ 58.7 переключается в положение «1» импульсом начала окна с выхода счетчика 58.2.1.1, и импульсы, предназначенные для считывания служебной информации из блока хранения служебной информации 53, поступающие на его первый вход с выхода счетчика 58.2.1, выдаются на соответствующий выход «1» ключа. Когда счетчик 58.4 отсчитает r служебных бит пакета и переполнится, импульс с его выхода, поступающий на третий вход первого ключа 58.7, переключает его в положение «0», и импульсы считывания полезной информации из буферного накопителя 11 или буфера квитирования 56, поступающие с выхода одного из счетчиков 58.2.1…58.2.K, идут на выход «0» первого ключа 58.7. В результате работы описанного алгоритма, начиная с момента появления импульса на выходе счетчика 58.2.1.1, означающего начало очередного окна, с выхода «1» первого ключа 58.7 на второй выход блока генерации опорных частот 58 поступает r импульсов с периодичностью переполнения счетчика 58.2.1 и в соответствии с наименьшей скоростью передачи - импульсы считывания битов служебной информации, после чего первый ключ 58.7 переключается в положение «0», и с его выхода «0» на третий выход блока генерации опорных частот 58 поступает q импульсов с периодичностью переполнения одного из счетчиков 58.2.1…58.2.K в зависимости от управляющего сигнала выбора скорости передачи, поступающего на вход блока генерации опорных частот 58 - импульсы считывания битов полезной информации. При этом r - постоянная величина, а q - изменяется в соответствии с сигналами адаптации скорости передачи.

Параллельно с этим происходит поступление информации на передачу (при ее наличии в данный момент) с выхода источника цифровой информации 46 на первый вход буферного накопителя 11 до тех пор, пока он не переполнится и импульсом сигнализации о переполнении со своего первого выхода на вход источника цифровых данных 46 не прервет их поступление. Источник цифровой информации 46 периодически пытается записать новые данные в буферный накопитель 11. Если часть данных считана из буферного накопителя 11 и передана, то буфер принимает новые данные, иначе сигналом переполнения запрещает запись новой информации. Сигнал с выхода источника цифровой информации 46 поступает также и на первый вход динамического счетчика 52, значение которого увеличивается при записи битов полезной информации в буферный накопитель 11 на число, соответствующее количеству бит, поступивших в буфер, и уменьшается при их считывании и отправлении на передачу на соответствующее количество считанных из буфера бит посредством параллельной подачи считываемых бит со второго выхода буферного накопителя 11 на второй вход динамического счетчика 52. Значение этого счетчика в каждый момент времени показывает сколько бит полезной информации ожидает передачи в буферном накопителе 11, если таковые имеются. С первого выхода блока генерации опорных частот 58 импульс начала окна поступает на вторые входы триггеров 59, 60 и открывает их для прохождения сигналов с первых входов триггеров на их выходы. Импульс начала окна с первого выхода блока генерации опорных частот 58 также поступает на третий вход динамического счетчика 52 и вызывает выдачу с его выхода сигнала на первый вход ключа наличия информации в буфере 55. Этот сигнал переключает ключ в нулевое положение, если значение динамического счетчика равно нулю, и в единичное положение при любом другом значении динамического счетчика 52. Таким образом определяется, будет ли происходить считывание битов полезной информации из буферного накопителя 11 или стандартной последовательности битов из буфера квитирования 56 при отсутствии полезных данных на передачу. Импульс начала окна с первого выхода блока генерации опорных частот 58 также поступает на первый вход электронных часов 61 и прибавляет к записанному в них времени длительность окна. Это время и будет считаться текущим для пакета, передаваемого в данном окне. Сами электронные часы являются фактически элементом памяти, хранящим значение текущего времени начала передачи очередного окна. Значение времени с выхода электронных часов 61 поступает на вход 1.3 блока хранения служебной информации 53 и записывается в него; на первый вход ГПСП ШПС 57 и осуществляет привязку генерируемых им псевдослучайных значений к текущему времени для правильной корреляционной обработки сигнала на приемном конце, на котором часы идут синхронно с часами на передающем конце; значение времени также поступает на вход 1.1 блока генерации ПСП ППРЧ 62 и вызывает генерацию нового значения частоты передачи также с жесткой привязкой к текущему времени. Импульс начала окна с первого выхода блока генерации опорных частот 58 также поступает на вход счетчика 64, увеличивая его на единицу. Этот счетчик переполняется при подсчете двух импульсов на своем входе, затем сбрасывается в начальное состояние, он обеспечивает работу приемной части приемопередатчика только в приемном окне. С появлением на первом выходе блока генерации опорных частот 58 импульса начала окна, на его втором выходе начинают появляться импульсы считывания битов служебной информации из блока хранения служебной информации 53. Эти импульсы проходят через открытый импульсом начала окна второй триггер 59 и с его выхода поступают на вход 1.1 блока хранения служебной информации 53. Каждый импульс считывает один бит служебной информации, который с выхода блока хранения служебных данных 53 поступает на второй вход второго сумматора 48, с выхода которого он поступает на первый вход сумматора по модулю два 49, в котором происходит наложение S1 тактов ПСП ШПС на один бит служебной информации. Число S1 определяется тем, во сколько раз частота тактовых импульсов, поступающих с четвертого выхода блока генерации опорных частот 58 на второй вход ГПСП ШПС 57, больше частоты импульсов на втором выходе блока генерации опорных частот 58. Таким образом достигается увеличение помехоустойчивости передаваемого сигнала в KШПС≈2·B раз (согласно [2]), где B=F·T - база сигнала. Согласно [4] база фазоманипулированного шумоподобного сигнала, полученного непосредственной модуляцией несущей псевдослучайной последовательностью, в S1 раз больше базы соответствующего цифрового сигнала без наложения ПСП ШПС при условии, что на длительности одного информационного символа цифровой информации укладывается целое число S1 кодовых элементов ПСП ШПС. Таким образом, результирующее повышение помехоустойчивости определяется соотношением KШПС≈2·S1·B0 где B0 - база фазоманипулированного сигнала цифровой информации без наложения ПСП ШПС. Импульсы с четвертого выхода блока генерации опорных частот 58 задают частоту формирования ГПСП ШПС 57 двоичных псевдослучайных значений на своем выходе, а импульсы на втором выходе блока генерации опорных частот 58 идут с частотой считывания бит служебной информации. Далее биты служебной информации с наложенной на них ПСП ШПС поступают с выхода сумматора по модулю два 49 на вход модулятора 50, в котором осуществляется фазовая манипуляция битов служебной информации пакета на частоте сигнала, поступающего на второй вход модулятора с выхода первого синтезатора частот 54. Первый синтезатор частот 54 производит выдачу частоты на свой выход в соответствии с номером частоты, поступающим на его третий или четвертый вход. По импульсу начала окна на передачу, поступающему с первого выхода блока генерации опорных частот 58, синтезатор частот начинает генерировать сигнал с номером частоты, поступающим на его четвертый вход - на частоте передачи служебной части пакета. При поступлении импульса с пятого выхода блока генерации опорных частот 58 на второй вход первого синтезатора частот 54, сигнализирующего о начале части полезной информации пакета, синтезатор переключается на выдачу на своем выходе сигнала в соответствии с номером адаптируемой частоты, поступающим на его третий вход с первого выхода блока генерации ПСП ППРЧ 62.

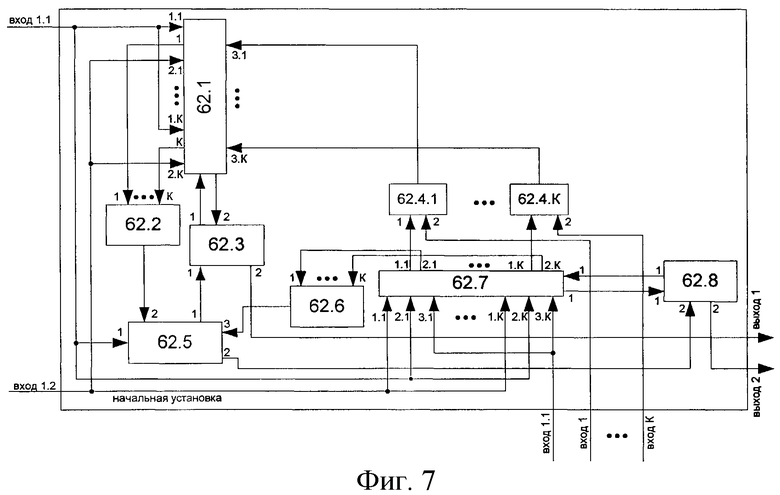

Рассмотрим подробнее работу блока генерации ПСП ППРЧ 62, схема которого представлена на фиг.7. Начальная установка разрешенных частот, поступающая перед началом сеанса связи на вход 1.2 блока генерации ПСП ППРЧ 62, подается на входы 2.1…2.K первого элемента памяти 62.1 и на входы 1.1…1.K второго элемента памяти 62.7 и записывается в них побитно. Начальная установка разрешенных частот представляет собой последовательность из K нулей и единиц, причем единица означает, что частота с соответствующим номером разрешена, 0 - запрещена. В момент начала передачи пакета со входа 1 блока генерации ПСП ППРЧ 62 импульс начала окна поступает одновременно на входы 1.1…1.K первого элемента памяти 62.1 и производит считывание текущей таблицы частот. В первом окне на передачу текущая таблица в первом элементе памяти 62.1 совпадает с таблицей начальной установки, далее она будет корректироваться в соответствии с таблицами разрешенных частот, поступающими с дальнего конца радиолинии и с выходов контрольных приемников, а таблица во втором элементе памяти 62.7 всегда совпадает с таблицей начальной установки разрешенных частот и не изменяется в процессе осуществления сеанса связи. Импульс, поступающий на вход 1.1 первого элемента памяти 62.1, извлекает значение, содержащееся в первой ячейке памяти и отправляет его на первый выход первого элемента памяти 62.1. Аналогично импульс, поступающий на вход 1.2 первого элемента памяти 62.1, извлекает значение, содержащееся во второй ячейке памяти и отправляет его на второй выход первого элемента памяти 62.1, и так далее происходит считывание до K-й ячейки памяти. Считанные значения с выходов 1…K первого элемента памяти 62.1 одновременно поступают на входы третьего сумматора 62.2, на выходе которого появляется сигнал, равный сумме считанных единиц и, таким образом, количеству разрешенных частот (в первом окне количество разрешенных частот равно их количеству в начальной установке, приходящей на вход 1.2 блока генерации ПСП ППРЧ, затем в процессе обмена информацией с приемопередатчиком на дальнем конце радиолинии и учета помеховой обстановки на обоих концах радиолинии количество просуммированных третьим сумматором 62.2 разрешенных частот может меняться). Сигнал с выхода третьего сумматора 62.2 поступает на второй вход ГПСП 62.5. Значение суммы количества разрешенных частот необходимо ГПСП для масштабирования диапазона выдаваемых псевдослучайных чисел с учетом таблиц разрешенных на дальнем и на ближнем концах радиолинии частот и таблицы частот, разрешенных по условиям ЭМС. Одновременно с этим импульс начала окна подается со входа 1.1 блока ПСП ППРЧ 62 на входы 2.1…2.K второго элемента памяти 62.7, содержащего таблицу разрешенных по условиям ЭМС частот. По поступлении этого импульса происходит считывание этой таблицы с выходов 2.1…2.K второго элемента памяти 62.7. Считанные значения поступают на входы 1…K четвертого сумматора 62.6, с выхода которого на третий вход ГПСП 62.5 поступает сумма количества частот, разрешенных по условиям ЭМС, без учета помеховой обстановки на обоих концах радиолинии (эта сумма однозначно определяется начальной установкой и не изменяется в процессе осуществления сеанса связи). Одновременно с описанным считыванием и суммированием, импульс начала окна подается со входа 1.1 блока генерации ПСП ППРЧ 62 на первый вход ГПСП 62.5 и инициирует выработку им на первом выходе псевдослучайного значения номера частоты, на которой будет передаваться полезная информация пакета в текущем окне, а на втором выходе - псевдослучайного значения номера частоты, на которой будет передаваться или приниматься служебная часть пакета в текущем окне. Псевдослучайное значение номера частоты на первом выходе ГПСП 62.5 масштабируется с учетом таблиц разрешенных на ближнем и на дальнем конце радиолинии частот и частот, разрешенных по условиям ЭМС, и является адаптивным. Псевдослучайное значение номера частоты на втором выходе ГПСП 62.5 масштабируется с учетом только разрешенных по условиям ЭМС частот (эта таблица одинакова на обоих концах радиолинии) и не является адаптивным. Этим обеспечивается прием служебной части пакета в соответствии с фиксированным псевдослучайным законом изменения частот, который заранее известен на обоих концах радиолинии, а благодаря жестокой временной синхронизации частота, на которой передавался пакет, всегда известна на приемном конце. Прием же полезной части пакета производится на частоте, которая заранее неизвестна на приемной стороне из-за адаптации ее в соответствии с помеховой обстановкой на дальнем конце радиолинии, изменения которой предугадать невозможно, и номер частоты, на которой необходимо производить прием полезной части пакета, извлекается из принятой на известной частоте служебной части пакета. Выработанное на первом выходе ГПСП 62.5 значение номера частоты i1 поступает на первый вход первого блока выборки 62.3, который осуществляет поиск i1-й разрешенной частоты в общем массиве частот. Для этого первый блок выборки последовательно опрашивает ячейки памяти первого элемента памяти 62.1, начиная с первой. Если в ячейке записана единица, к внутреннему счетчику первого блока выборки прибавляется единица, иначе - не прибавляется. Такой опрос и накопление происходит до тех пор, пока внутренний счетчик на i1 элементов первого блока выборки 62.3 не переполнится, тогда номер ячейки, на которой внутренний счетчик накопил i1 элементов, будет номером частоты j1 в общем наборе, на которой должна производиться передача полезной части пакета в текущем окне. Значение j1 номера частоты, на которой необходимо производить передачу полезной части пакета, учитывающее помеховую обстановку на обоих концах радиолинии и начальную установку разрешенных частот по условиям ЭМС со второго выхода первого блока выборки 62.3, подается на первый выход блока ПСП ППРЧ 62. Аналогично выработанное на втором выходе ГПСП 62.5 значение номера частоты i2 поступает на второй вход второго блока выборки 62.8, который осуществляет поиск i2-й разрешенной частоты в общем массиве частот путем опроса второго элемента памяти 62.7 и внутреннего накопления, как описано выше, и находит соответствующий номер j2 частоты в общем списке используемых частот. Значение j2 номера частоты, учитывающее только начальную установку разрешенных частот по условиям ЭМС, со второго выхода второго блока выборки 62.8, подается на второй выход блока генерации ПСП ППРЧ 62. Учет помеховой обстановки на обоих концах радиолинии осуществляется посредством наложения таблицы разрешенных частот, поступающей с выходов 1…K решающего устройства 65 на таблицу разрешенных частот, установленную начальной установкой для обеспечения ЭМС. При приеме очередного пакета решающее устройство считывает таблицу разрешенных на ближнем конце частот, полученную в результате работы 1…K контрольных приемников 66.1…66.K и сопоставляет ее с таблицей разрешенных частот из служебной части очередного принятого пакета. На выходы 1…K решающего устройства подается таблица, в которой разрешены только те частоты, которые свободны от помех как на ближнем, так и на дальнем конце радиолинии. Параллельно с таблицей разрешенных частот с выхода 1.1 решающего устройства подается синхроимпульс на входы 3.1…3.K второго элемента памяти 62.6 блока генерации ПСП ППРЧ 62. Посредством этого импульса происходит одновременное считывание значений таблицы разрешенных частот, записанной во второй элемент памяти во время начальной установки, и подача их на первые входы соответствующих элементов «и» 62.4.1…62.4.K, на вторые входы которых поступает таблица разрешенных частот с выходов 1…K решающего устройства 65. В результате такого наложения на выходах элементов «и» получается таблица разрешенных частот с учетом помеховой обстановки на обоих концах радиолинии и начальной установки по условиям ЭМС. Результирующая таблица разрешенных частот поступает с выходов соответствующих элементов «и» 62.4.1…62.4.K на входы 3.1…3.K первого элемента памяти 62.1, записывается в соответствующие ячейки памяти этого элемента и будет использована при генерации следующего значения номера частоты в ГПСП 62.5, которое будет выдано с его первого выхода.

Фазоманипулированный сигнал с выхода модулятора поступает на первый вход усилителя мощности 14, с выхода которого он подается на вход антенно-фидерного устройства 51 и излучается в пространство. После прохождения r импульсов со второго выхода блока генерации опорных частот 58, осуществления считывания этими импульсами всей служебной информации из блока хранения служебной информации 53 и передачи их в соответствии с описанным алгоритмом в блоке генерации опорных частот происходит переключение второго коммутатора 58.5 и на его выходе начинают появляться импульсы с его третьего входа. Это импульсы считывания полезной информации, которые идут с периодичностью, определяемой адаптируемой скоростью передачи информации. С третьего выхода блока генерации опорных частот эти импульсы проходят через открытый в окне на передачу третий триггер 60 на второй вход ключа наличия информации в буфере 55. Если есть информация на передачу, ключ наличия информации в буфере находится в состоянии «1», и импульсы с его второго входа поступают на второй вход буферного накопителя 11. Этими импульсами считывается определенное (определяемое скоростью передачи информации) количество бит информации q, которые со второго выхода буферного накопителя поступают на первый вход первого сумматора 47 и в отсутствие сигнала на его втором входе проходят без изменений на первый вход блока кодирования 10, в котором осуществляется их помехоустойчивое кодирование тем кодом из набора используемых, который установлен либо блоком управления кодированием 4 (таким образом осуществляется адаптация передаваемого сигнала по виду кодирования в случае неудовлетворительного качества приема), либо в соответствии с сигналом, пришедшим с первого выхода блока выделения служебной информации 71 (таким образом осуществляется согласование вида кодирования сигнала с тем, который установлен на дальнем конце радиолинии). С выхода блока кодирования 10 закодированная информация поступает на первый вход второго сумматора 48 и в отсутствие сигнала на его втором входе поступает без изменений на первый вход сумматора по модулю два 49. Далее все манипуляции с закодированными битами полезной информации полностью аналогичны преобразованиям битов служебной информации, которые описаны выше. Общая структура пакета изображена на фиг.8.

В следующем окне осуществляется прием пакета с дальнего конца радиолинии. Блок генерации опорных частот 58 выдает со своего первого выхода импульс начала окна, который подается на вторые входы второго и третьего триггеров 59, 60 и закрывает их. Теперь сигналы, поступающие на первые входы этих триггеров не будут проходить на их выходы. Импульс начала окна также подается на первый вход электронных часов 61 и устанавливает текущее время для данного окна (к хранимому в них значению прибавляется длительность окна). С выхода электронных часов 61 сигнал времени поступает на первый вход блока генерации ПСП ППРЧ 62, который генерирует номер частоты, на которой необходимо осуществлять прием заголовка пакета и подает его со своего второго выхода на первый вход приемника 72. Импульс начала окна также подается на вход счетчика 64, который переполняется этим импульсом, выдает импульс на свой выход и сбрасывается в начальное состояние. С выхода счетчика 64 импульс поступает на первый вход блока выделения служебной информации 71, на вход 1.1 решающего устройства 65 и на первые входы контрольных приемников 66.1…66.K. Контрольные приемники непрерывно осуществляют контроль помеховой обстановки на всех K используемых частотах и выдают результаты измерений в виде таблицы разрешенных частот со своих выходов на входы 1…K решающего устройства 65 по приходу на их первые входы импульса с выхода счетчика 64. Одновременно с этим с выхода антенно-фидерного устройства 51 принимаемый сигнал поступает на второй вход приемника 72.

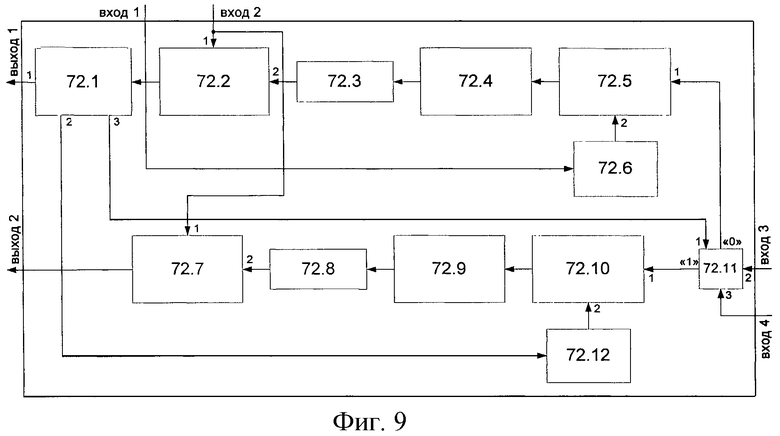

Рассмотрим работу приемника 72, схема которого приведена на фиг.9. В начале окна на прием на третий вход приемника 72 поступает импульс с первого выхода блока генерации опорных частот 58. С третьего входа приемника 72 этот сигнал поступает на второй вход шестого ключа 72.11 и переводит его в нулевое состояние. Биты заголовка принимаемого пакета поступают с выхода АФУ 51 на третий вход ключа 72.11, который находится в нулевом состоянии. Биты заголовка принимаемого пакета с выхода «0» ключа 72.11 поступают на первый вход преобразователя частоты 72.5, на второй вход которого поступает сигнал на частоте, на которую необходимо производить преобразование. Номер этой частоты поступает со второго выхода блока генерации ПСП ППРЧ 62 на вход второго синтезатора частот 72.6, который и осуществляет генерацию необходимого сигнала и подает его на второй вход первого преобразователя частоты 72.5. Далее сигнал с выхода первого преобразователя частоты 72.5 поступает на вход первого усилителя промежуточной частоты 72.4, в которой он усиливается. С его выхода сигнал поступает на второй вход первого блока корреляционной обработки 72.2, в котором с битов заголовка пакета снимается наложенная на них на передающей стороне ПСП ШПС с помощью сигнала, поступающего на его первый вход со второго выхода ГПСП ШПС 57. Биты заголовка пакета в цифровом виде поступают с выхода первого блока корреляционной обработки 72.2 на вход блока синхронизации и выделения служебной информации 72.1. В этом блоке происходит «захват» пакета по его первому заголовку, содержащему синхропоследовательность, в результате чего блок определяет моменты времени, когда начнутся значащие биты заголовка и момент начала бит полезной информации. Сигнал начала следования битов полезной информации поступает с третьего выхода блока синхронизации и выделения служебной информации 72.1 на первый вход шестого ключа 72.11 и переводит его в единичное состояние. Также в блоке синхронизации и выделения служебной информации 72.1 происходит выделение второй заголовочной части r2 бит, информирующих приемник о номере частоты, на которой передавался пакет. Для обеспечения приема полезной части пакета на той же частоте сигнал с выделенным номером частоты поступает со второго выхода блока синхронизации и выделения служебной информации 72.1 на вход третьего синтезатора частот 72.12. Блок синхронизации и выделения служебной информации 72.1, использовав значения первых двух частей заголовка (синхронизации и номера частоты), снимает их и отправляет оставшуюся часть заголовка на свой первый выход, с которого сигнал поступает на первый выход приемника 72. Шестой ключ 72.11 переключается в единичное состояние по сигналу с блока синхронизации и выделения служебной информации 72.1 в момент начала поступления битов полезной информации, которые с четвертого входа приемника 72 поступают на первый вход второго преобразователя частоты 72.10. Входной сигнал, преобразованный на частоту с номером, выделенным из заголовка принимаемого пакета, посредством сигнала, подаваемого с выхода третьего синтезатора частот 72.12 на второй вход второго преобразователя частоты 72.10, поступает на вход второго усилителя промежуточной частоты 72.9, с выхода которого усиленный сигнал поступает на вход второго демодулятора 72.8, с выхода которого выделенный цифровой сигнал поступает на второй вход второго блока корреляционной обработки 72.7, который снимает ПСП ШПС с битов полезной информации с помощью сигнала, поступающего на его первый вход со второго входа ГПСП ШПС 57. Закодированные биты полезной информации с выхода второго блока корреляционной обработки 72.7 поступают на второй выход приемника 72.

С первого выхода приемника 72 на второй вход блока выделения служебной информации 71 поступает заголовок принимаемого пакета данных с неполной служебной частью (заголовки синхронизации и номера частоты были использованы и удалены внутри приемника 72).

Рассмотрим подробнее работу блока выделения служебной информации 71, изображенного на фиг.10. В начале окна на прием с выхода переполнившегося счетчика 64 на первый вход блока выделения служебной информации 71 поступает импульс, который поступает далее на первые входы ключей 71.1…71.4, переводит их в состояние «0», и на первые входы счетчиков 71.5…71.8, сбрасывает их в нулевое состояние. На второй вход блока выделения служебной информации 71 начинают поступать биты неполного заголовка принимаемого пакета, из которого исключены первые r1+r2 бит синхронизации и номера частоты, которые были использованы и удалены из заголовка внутри приемника 72. Биты заголовка принимаемого пакета, поступающие на второй вход блока выделения служебной информации 71, идут на вторые входы пятого ключа 71.4 и седьмого счетчика 71.8. Пятый ключ 71.4 находится в положении «0» и отправляет приходящие на него биты на 4-й выход блока выделения служебной информации. Седьмой счетчик 71.8 переполняется при подсчете r3 бит, поступивших на его второй вход. При переполнении счетчик выдает импульс со своего выхода на третий вход пятого ключа 71.4, который переводит ключ в состояние «1» и все последующие биты информации, поступающие на второй вход ключа будут отправляться дальше по цепочке с выхода «1» пятого ключа 71.4 на второй вход четвертого ключа 71.3 и второй вход шестого счетчика 71.7. В результате работы связки пятый ключ 71.4 - седьмой счетчик 71.8 на 4-й выход блока выделения служебной информации 71 отправлено r3 бит служебной информации, которые извещают приемную часть о скорости, на которой передавался текущий пакет на дальнем конце радиолинии. Аналогичным образом происходит выделение связкой четвертый ключ 71.3 - шестой счетчик 71.7 r4 бит служебной информации, извещающей приемную часть о моменте времени передачи принимаемого пакета; связкой третий ключ 71.2 - пятый счетчик 71.6 r5 бит служебной информации, извещающей приемную часть о номере кода, использовавшегося при кодировании текущего пакета; связкой второй ключ 71.1 - четвертый счетчик 71.5 r6 бит служебной информации, извещающей приемную часть о разрешенных для осуществления радиосвязи частотах на дальнем конце радиолинии. Седьмая служебная часть r7 бит не несет никакой смысловой нагрузки и служит в качестве защитного интервала времени на осуществление обработки аппаратурой заголовочной части и подготовки к приему полезной части пакета с заданными параметрами. Информация третей части заголовка r3 (скорость) подается с четвертого выхода блока выделения служебной информации 71 на вход 1.2 блока хранения служебной информации 53 и записывается в его область памяти r3, а также на вход блока генерации опорных частот 58 и заставляет коммутатор 58.3 переключиться на тот счетчик, который соответствует скорости передачи текущего принимаемого пакета. Таким образом обеспечивается передача пакета в следующем окне на той же скорости, что и на дальнем конце радиолинии - согласование скорости. Информация четвертой части заголовка r4 (время) подается с третьего выхода блока выделения служебной информации 71 на второй вход электронных часов 61. По этому сигналу производится коррекция электронных часов в соответствии с содержимым служебной части принятого пакета. Такая подстройка электронных часов производится для постоянного поддержания приемопередающих устройств на обоих концах радиолинии в синхронизме, осуществляется в конце приемного окна для того, чтобы не сбивался процесс принятия текущего пакета. Информация пятой части заголовка r5 подается с первого выхода блока выделения служебной информации 71 на второй вход декодера 70 и информирует его о том, с помощью какого из наборов используемых кодов следует декодировать текущий пакет; на второй вход блока кодирования 10 и информирует его о необходимости осуществлять кодирование в следующем окне на передачу тем же кодом, что и в принятом пакете - согласование номера кода; на вход 1.4 блока хранения служебной информации 53 и записывается в его область памяти r5. Информация шестой части заголовка r6 (таблица разрешенных частот) подается со второго выхода блока выделения служебной информации 71 на вход 1.2 решающего устройства 65. Посредством этого ведется учет помеховой обстановки на дальнем конце радиолинии.

Рассмотрим подробнее работу решающего устройства 65, схема которого изображена на фиг.11. В начале окна на прием с выхода счетчика 64 поступает импульс на первые входы контрольных приемников 66.1…66.K. Посредством этого импульса происходит считывание значений разрешенных частот в двоичном виде, измеренных контрольными приемниками. Если контрольный приемник, отслеживающий наличие помех на i-й частоте принял решение, что частота свободна от помех, то с его выхода поступает единица, иначе - ноль. Таблица разрешенных частот поступает со входов 1…K решающего устройства 65 на входы 1.1…1.K четвертого элемента памяти 65.4, в котором происходит запись этой таблицы в соответствующие ячейки памяти. С третьего выхода блока выделения служебной информации 71 на вход 1.2 решающего устройства 65 поступает таблица разрешенных на дальнем конце радиолинии частот. Со входа 1.2 решающего устройства 65 эта таблица последовательно поступает на входы 2.1…2.K третьего элемента памяти 65.2 и записывается в соответствующие ячейки памяти. Импульс с выхода счетчика 64 поступает на вход линии задержки 65.1, в которой происходит задержка импульса на время, достаточное для приема текущего пакета, выделения таблицы разрешенных на дальнем конце радиолинии частот из заголовка этого пакета, записи таблиц разрешенных на дальнем и на ближнем концах радиолинии частот в третий и четвертый элементы памяти 65.2 и 65.4. С выхода линии задержки 65.1 импульс поступает на выход 1.1 решающего устройства 65, на входы 1.1…1.K третьего элемента памяти 65.2 и на входы 2.1…2.K четвертого элемента памяти 65.4. Этим импульсом из обоих элементов памяти считываются таблицы разрешенных частот, и с их выходов 1…K считанные значения поступают на первые и вторые входы элементов «и» 65.3.1…65.3.K. В этих элементах происходит логическое умножение значений таблиц разрешенных на ближнем и на дальнем концах радиолинии частот. С выходов соответствующих элементов «и» 65.3.1…65.3.K на выходы 1…K решающего устройства 65 поступает результирующая таблица разрешенных частот, в которой разрешены (имеют единичное значение в таблице) только те частоты, которые разрешены как на ближнем, так и на дальнем конце радиолинии. Эта результирующая таблица частот с выходов 1…K решающего устройства 65 поступает на входы 1…K блока хранения служебной информации 53 и записывается в его область памяти r6 и на входы 1…K блока генерации ПСП ППРЧ 62.

Биты полезной информации принимаемого пакета, поступающие с первого выхода блока выделения служебной информации 71, записываются в элемент памяти блока декодирования 70 в соответствующие ячейки памяти в моменты поступления синхроимпульсов с третьего выхода блока генерации опорных частот 58. Отметим, что синхроимпульсы с третьего выхода блока генерации опорных частот поступают с периодичностью, соответствующей скорости, на которой передавался текущий пакет. Это обеспечивается посредством перестройки генератора опорных частот в соответствии со служебной информацией, выделенной из второй части заголовка r2 (скорость) и поступившей с пятого выхода блока выделения служебной информации 71 на вход блока генерации опорных частот 58. Блок декодирования 70 производит декодирование полученного пакета в соответствии с номером кода, поступившим на его третий вход со второго выхода блока выделения служебной информации 71, и выдает исходную последовательность бит полезной информации со своего первого выхода на вход получателя цифровой информации 69. Если принятый пакет был декодирован верно, в этом случае блок декодирования 70 подает сигнал со своего второго выхода на первые входы счетчиков 67, 68. По этому сигналу происходит накопление счетчика 1.4 и сброс счетчика 1.5. При правильном приеме b пакетов подряд счетчик 1.4 переполняется и с его выхода на первый вход процессора 63 поступает сигнал на адаптацию параметров передачи в следующем окне на передачу в сторону увеличения скорости передачи, выбора кода с меньшей избыточностью, снижения мощности излучаемого сигнала для повышения общей эффективности системы связи. Процессор 63 выдает соответствующие управляющие сигналы на увеличение скорости со своего первого выхода на вход блока управления скоростью передачи 5, с выхода которого управляющий сигнал поступает на вход блока генерации опорных частот 58 и на вход 1.2 блока хранения служебной информации 53, в котором производится запись нового номера используемой скорости обмена данными; на выбор кода с меньшей избыточностью на вход блока управления кодированием 4, с выхода которого управляющий сигнал поступает на второй вход блока кодирования 10 и на вход 1.4 блока хранения служебных данных 53, в котором производится запись нового номера используемого кода; на уменьшение коэффициента усиления на вход блока управления мощностью передачи 8, с выхода которого управляющий сигнал поступает на второй вход усилителя мощности 14. Если принятый пакет был декодирован неверно, в этом случае блок декодирования 70 подает сигнал со своего третьего выхода на вторые входы счетчиков 67, 68. По этому сигналу происходит накопление счетчика 1.4 и сброс счетчика 1.3. При неправильном приеме d пакетов подряд счетчик 1.4 переполняется и с его выхода на второй вход процессора 63 поступает сигнал на адаптацию параметров передачи в следующем окне на передачу в сторону уменьшения скорости передачи, выбора кода с большей избыточностью, увеличения мощности излучаемого сигнала для увеличения помехоустойчивости. Процессор 63 выдает соответствующие управляющие сигналы на уменьшение скорости со своего первого выхода на вход блока управления скоростью передачи 5, с выхода которого управляющий сигнал поступает на вход блока генерации опорных частот 58 и на вход 1.2 блока хранения служебной информации 53, в котором производится запись нового номера используемой скорости обмена информацией; на выбор кода с большей избыточностью на вход блока управления кодированием 4, с выхода которого управляющий сигнал поступает на второй вход блока кодирования 10 и на вход 1.4 блока хранения служебной информации 53, в котором производится запись нового номера используемого кода; на увеличение коэффициента усиления на вход блока управления мощностью передачи 8, с выхода которого управляющий сигнал поступает на второй вход усилителя мощности 14. Числа b и d подбираются эмпирическим путем, а алгоритм, по которому происходит адаптация параметров передаваемого сигнала, может предполагать либо одновременное изменение всех параметров, либо их последовательное изменение по отдельности.

Преобразование исходного цифрового сигнала в излучаемый сигнал представлено на фиг.12. На фиг.12(а) изображен исходный цифровой сигнал на выходе источника цифровой информации, на фиг.12(б) - сигнал на выходе декодера, на фиг.12(в) - начальная часть сигнала на выходе сумматора по модулю два после осуществления наложения на сигнал ПСП ШПС, изображенной на фиг.12(д), на фиг.12(г) - сигнал на выходе модулятора после фазовой манипуляции.

Таким образом, в предлагаемом устройстве достигается следующий технический результат:

- увеличение помехоустойчивости системы связи;

- достижение автоматизированной настройки параметров радиосигнала в зависимости от помеховой обстановки на радиолиниях большой протяженности как в сторону увеличения помехозащищенности при ухудшении помеховой обстановки, так и в сторону увеличения скорости передачи, снижения излучаемой мощности, уменьшения избыточности применяемого помехоустойчивого кода, а значит, и общее повышение эффективности передачи информации;

- обеспечение ЭМС со смежными радиосредствами;

- упрощение и удешевление схемы приема, осуществляемого на одной частоте, а не сразу на всех возможных, как это предлагается в аналогичных работах [1], [5], [6].

Технически вся цифровая часть приемопередатчика может быть реализована посредством ПЛИС Altera, контроллеры скорости, кодов и мощности - на базе микроконтроллеров AVR, кодер и декодер широко применимы на практике и известны, контрольные приемники могут быть реализованы как предложено в [1].

Источники информации

1. Патент РФ №2099886, H04L5/02, Булычев О.А., Калинин В.М., Попов В.И. «Способ передачи информации в радиолинии с псевдослучайной перестройкой рабочих частот и устройство, его реализующее», 20.12.1997.

2. Варакин Л.Е. «Системы связи с шумоподобными сигналами». - М.: Радио и связь, 1985. - 384 с.

3. Диксон Р.К. «Широкополосные системы». Пер. с англ. / Под ред. В.И.Журавлева. - М.: Связь, 1979. - 304 с.

4. Борисов В.И., Зинчук В.М., Лимарев А.Е., Мухин Н.П., Нахмансон Г.С. «Помехозащищенность систем радиосвязи с расширением спектра сигналов модуляцией несущей псевдослучайной последовательностью». - М.: Радио и связь, 2003. - 640 с.

5. Патент РФ №2178237, H04B 1/713, Деркач Е.Н., Попов В.И., Лазоренко B.C., Сивоконев Г.Н. «Способ передачи дискретной информации в радиолинии с псевдослучайной перестройкой рабочей частоты и устройство, его реализующее», 10.01.2002.

6. Патент РФ №2231220, H04B 1/713, Герасименко В.Г., Тупота В.И., Тупота А.В. «Способ передачи дискретной информации в радиолинии с псевдослучайной перестройкой рабочей частоты», 20.06.2004.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АДАПТИВНОЙ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2007 |

|

RU2356167C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ЦИФРОВОЙ ИНФОРМАЦИИ | 2010 |

|

RU2436248C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2008 |

|

RU2356171C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ СО СКАЧКООБРАЗНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2005 |

|

RU2290758C1 |

| Способ формирования сигнала в режиме программной перестройки рабочей частоты с изменяющейся полосой частот | 2020 |

|

RU2749863C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2178237C2 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2210862C1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2311734C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2099886C1 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

Изобретение относится к области радиотехники и может быть использовано в устройствах передачи информации для повышения информационной скрытности, помехозащищенности и достоверности передаваемого цифрового сигнала в сети связи. Достигаемый технический результат: увеличение помехоустойчивости системы связи; достижение автоматизированной настройки параметров радиосигнала в радиолиниях большой протяженности, повышение эффективности передачи информации, обеспечение электромагнитной совместимости со смежными радиосредствами, упрощение схемы приемника. Устройство содержит буферный накопитель, блок управления скоростью передачи, блок управления кодированием, блок управления мощностью передачи, блок генерации псевдослучайной последовательности шумоподобного сигнала, электронные часы, блок генерации псевдослучайной последовательности псевдопеременной перестройки рабочей частоты, приемник, процессор, блок хранения служебной информации, решающее устройство, К контрольных приемников, два счетчика, блок выделения служебной информации, блок генерации опорных частот, сумматоры, синтезатор частот, электронные часы, триггеры, модулятор, антенно-фидерное устройство. 12 ил.