Предлагаемое устройство относится к области радиотехники и может найти применение в адаптивных системах специальной радиосвязи для передачи данных по радиоканалу в условиях воздействия комплекса преднамеренных помех.

Известено устройство для передачи в условиях неопределенных помех, описанное в [1], в котором повышение помехоустойчивости радиолинии в условиях воздействия нестационарных помех достигается при наличии долговременного неоднородного качества отдельных частотных каналов.

Известено устройство передачи информации с псевдослучайной перестройкой частоты (ППРЧ) по патенту [2], в котором значение рабочей частоты формируется по псевдослучайному закону, в псевдослучайные моменты времени, гарантированно синхронные для обеих сторон радиолинии.

Недостатком вышеупомянутых устройств является отсутствие адаптации синхросигнала к изменениям помеховой обстановки.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в [3], принятое за прототип.

Функциональная схема устройства-прототипа приведена на фиг.1, где приняты следующие обозначения:

1 - источник информации (ИИ);

30 - первое оперативное запоминающее устройство (ОЗУ1);

6 - модулятор;

7 - первый антенно-фидерный блок (АФБ1);

31 - первый кодер адреса записи (КАЗ1);

32 - первый кодер адреса считывания (КАС1);

12, 29 - первый и второй синтезаторы частот (СЧ1 и СЧ2);

8 - первый генератор тактовых импульсов (ГТИ1);

33 - первый делитель частоты (ДЧ1);

34 - второй делитель частоты (ДЧ2);

35 - первый формирователь пачек импульсов (ФПИ1);

13 - первый генератор псевдослучайной последовательности (ГПСП1);

21 - второй антенно-фидерный блок (АФБ2);

14 - преобразователь частоты (ПЧ);

15 - усилитель промежуточной частоты (УПЧ);

16 - демодулятор;

36 - второе оперативное запоминающее устройство (ОЗУ2);

20 - приемник информации (ПИ);

37 - второй генератор псевдослучайной последовательности (ГПСП2);

38 - синхрогенератор (СГ);

39 - второй кодер адреса записи (КАЗ2);

40 - второй кодер адреса считывания (КАС2);

41 - третий делитель частоты (ДЧЗ);

42 - четвертый делитель частоты (ДЧ4);

43 - второй формирователь пачек импульсов (ФПИ2);

44 - второй генератор тактовых импульсов (ГТИ2).

Устройство-прототип содержит ИИ 1, ГПСП1 13, ГПСП2 37, СЧ1 12, СЧ2 29, модулятор 6, АФБ1 7, АФБ2 21, ПЧ 14, УПЧ 15, демодулятор 16, СГ 38 и ПИ 20, причем выход ГПСП1 13 через СЧ2 12 соединен с одним входом модулятора 6, выход которого подключен к входу АФБ1 7, выход АФБ2 21 подключен к первому входу ПЧ 14, выход которого соединен с входом УПЧ 15, выход УПЧ 15 подключен к входу демодулятора 16, выход которого соединен с входом СГ 38, выход которого подключен к одному входу ГПСП2 37, выход которого через СЧ2 29 подключен ко второму входу ПЧ 14, кроме того, содержит первое и второе оперативные запоминающие устройства (ОЗУ1 30, ОЗУ2 36), первый и второй кодеры адреса записи (КАЗ1 31, КАЗ2 39), первый и второй кодеры адреса считывания (КАС1 32, КАС2 40), первый, второй, третий и четвертый делители частоты (ДЧ1 33, ДЧ2 34, ДЧЗ 41, ДЧ4 42), первый и второй формирователи пачек импульсов (ФПИ1 35, ФПИ2 43), первый и второй генераторы тактовых импульсов (ГТИ1 8, ГТИ2 44). Причем выход ИИ 1 подключен к первому входу ОЗУ1 30, выход которого соединен с входом модулятора 6, выход ГТИ1 8 подключен в параллель к входам ДЧ1 33, ДЧ2 34 и ФПИ1 35, а выходы ДЧ1 33, ДЧ2 34 и ФПИ1 35 подключены соответственно к входу КАЗ1 31, КАС1 32 и ГПСП1 13, выходы КАЗ1 31 и КАС1 32 подключены к входам ОЗУ1 30, выход демодулятора 16 подключен к первому входу ОЗУ2 36, выход которого соединен с входом ПЧ 14, выход ГТИ2 44 подключен в параллель к входам ДЧЗ 41, ДЧ4 42 и ФПИ2 43, а выходы ДЧЗ 41, ДЧ4 42 и ФПИ2 43 подключены соответственно к входам КАЗ2 39, КАС2 40 и ГПСП2 37, выходам КАЗ2 39 и КАС2 40 подключены к входам ОЗУ2 36.

Работа устройства-прототипа заключается в следующем.

Входной цифровой сигнал записывают в ОЗУ1 30 в ячейки, согласно командам КАЗ1 31. Когда будет записано N блоков, по команде КАС1 32 информационный сигнал считывают из ОЗУ1 30 поблочно со скоростью, необходимой для передачи. При этом осуществляют перекодирование блоков. Считываемый из ОЗУ1 30 сигнал модулируют на частотах, определяемых ГПСП1 13, причем каждый блок модулируют на следующей частоте. ГТИ1 8, ДЧ1 33, ДЧ2 34 и ФПИ1 35 необходимы для общей синхронизации. На приемном конце сигнал после демодуляции записывают с ОЗУ2 36 в ячейки, определяемые КАЗ2 39. Когда в ОЗУ2 36 будет записано N блоков сигнала, то по команде КАС2 40 производят считывание элементов из ОЗУ2 36 в ПИ 20 со скоростью исходного сигнала, одновременно его декодируя.

В устройстве-прототипе преобразование скорости информации имеет целью перемежение битов для последующего применения помехоустойчивого кода. Однако данный метод является эффективным только в условиях воздействия непреднамеренных помех. В средствах специальной радиосвязи центральным направлением является повышение помехозащищенности в условиях непрерывного совершенствования средств радиопротиводействия (СРП), в частности, при воздействии на радиолинию с ППРЧ с целью подавления одной из эффективных с точки зрения энергетических возможностей запаздывающих помех в комплексе с заградительной помехой в части полосы (ЗПП). Применение ППРЧ приводит к выделению временных интервалов для синхронизации радиолинии и для перевода ее с частоты на частоту без потерь элементов сообщений на этих интервалах. Последнее требование приводит к преобразованию блока в слот: информационные биты "обрамляются" битами перестройки частоты (время, затрачиваемое аппаратурой на перестройку) и защитными битами (учет рассинхронизации генераторов). Отсутствие четкой побитовой синхронизации может свести на нет все преимущества ППРЧ. Учитывая это, СРП воздействуют не только на слоты с информацией (запаздывающая помеха, следящая по частотам), но и на слоты с синхросигналами (с применением ЗПП). Для защиты от последнего, целесообразно ввести смену вида синхросигналов в радиолинии.

Однако изменение вида синхросигнала не может не повлиять на общую структуру временной диаграммы работы радиолинии и, как следствие, на общее построение аппаратуры с ППРЧ. Современная аппаратура передачи данных должна быть рассчитана на работу при различной скорости передачи (соответствующих ГОСТ 17422), а также на защиту информации от преднамеренных помех изменением скорости ППРЧ, вида помехоустойчивого кода и применения канала обратной связи между приемником и передатчиком для анализа помеховой обстановки. Таким образом, адаптация синхросигнала должна повлечь за собой адаптацию всей временной диаграммы работы радиолинии.

Последнее условие свидетельствует о том, что неизменяемая радиолиния, образуемая работой устройства-прототипа, не в состоянии обеспечить заданное качество связи на протяжении всего сеанса связи, поскольку входные условия могут время от времени изменяться. Таким образом, недостатком устройства-прототипа является низкое качество передачи информации в условиях преднамеренных помех. В этом случае возникает необходимость использования адаптивного устройства, которое, используя регулярный процесс поиска, постоянно ищет оптимум в пределах допустимого класса возможностей.

Целью предлагаемой работы является введение адаптации устройства передачи данных с ППРЧ к изменениям помеховой обстановки и уменьшение потерь информации.

Для реализации указанной цели в устройство, содержащее источник информации, вход которого является первым входом устройства, приемник информации, выход которого является вторым выходом устройства, последовательно соединенные модулятор и первый антенно-фидерный блок, выход которого является первым выходом устройства; последовательно соединенные генератор псевдослучайной последовательности и первый синтезатор частот, соединенный со вторым сигнальным входом модулятора; генератор тактовых импульсов, второй синтезатор частот, демодулятор, последовательно соединенные второй антенно-фидерный блок, вход которого является вторым входом устройства, преобразователь частоты и усилитель промежуточной частоты, согласно изобретению введены коммутатор скоростей, пакетатор, депакетатор, генератор кодовых последовательностей, блок управления, блок отождествления элемента сигнала, блок фазовой автоподстройки, первый и второй анализаторы качества сигнала, первый и второй демультиплексоры, первый, второй и третий мультиплексоры, М кодеров, М декодеров и К схем сравнения; кроме того, в источнике информации, модуляторе, демодуляторе, генераторе псевдослучайной последовательности, первом и втором синтезаторах частот дополнительно введено по тактовому входу, а в модуляторе и демодуляторе дополнительно введено по управляющему входу; при этом вход источника информации через коммутатор скоростей соединен с первым сигнальным входом пакетатора, выход которого соединен с сигнальным входом первого демультиплексора, М выходов которого соединены с сигнальными входами соответствующих М кодеров, выходы которых соединены соответственно с М сигнальными входами первого мультиплексора, выход которого соединен с первым сигнальным входом модулятора; выход демодулятора соединен с сигнальным входом второго демультиплексора, М выходов которого соединены с сигнальными входами соответствующих М декодеров, выходы которых соединены соответственно с М сигнальными входами второго мультиплексора, выход которого соединен с первым сигнальным входом депакетатора, второй сигнальный вход которого соединен с (М+1)-м выходом второго демультиплексора, а выход депакетатора соединен с сигнальным входом приемника информации; также выходы М декодеров соединены соответственно с М сигнальными входами первого анализатора качества сигнала, (М+1)-й сигнальный вход которого соединен с выходом демодулятора; выход усилителя промежуточной частоты соединен с первым сигнальным входом блока фазовой автоподстройки, выход которого соединен с сигнальным входом демодулятора; второй антенно-фидерный блок выполнен с возможностью разделения сигнала на служебную и информационную составляющие и в нем дополнительно введен второй выход, соединенный с первым сигнальными входом блока отождествления элемента сигнала, выход которого соединен с сигнальными входами К схем сравнения, выходы которых соединены соответственно с К сигнальными входами третьего мультиплексора, выход которого соединен со вторым сигнальным входом блока фазовой автоподстройки; кроме того, выходы М схем сравнения соединены с М сигнальными входами второго анализатора качества сигнала, (М+1)-й сигнальный вход которого соединен с выходом блока отождествления элемента сигнала; с первого по десятый выходы блока управления соединены соответственно с управляющими входами пакетатора, первого демультиплексора, первого мультиплексора, модулятора, депакетатора, второго демультиплексора, второго мультиплексора, демодулятора, генератора кодовых последовательностей и третьего мультиплексора, причем выход генератора кодовых последовательностей соединен со вторым сигнальным входом пакетатора; выходы первого и второго анализаторов качества сигнала соединены соответственно с первым и вторым входами блока управления; второй выход генератора псевдослучайной последовательности соединен с сигнальным входом второго синтезатора частот, первый выход которого соединен с введенным дополнительно третьим сигнальным входом модулятора, (М+1)-й выход первого демультиплексора соединен с введенным дополнительно четвертым сигнальным входом модулятора, в первом синтезаторе частот введен дополнительно второй выход, соединенный со вторым входом преобразователя частоты, во втором синтезаторе частот введен дополнительно второй выход, соединенный со вторым сигнальным входом блока отождествления элемента сигнала; выход генератора тактовых импульсов соединен с тактовыми входами источника информации, коммутатора скоростей, пакетатора, первого и второго демультиплексоров, первого, второго и третьего мультиплексоров, модулятора, генератора кодовых последовательностей, блока управления, блока фазовой автоподстройки, первого и второго анализаторов качества сигнала, первого и второго счетчиков, генератора псевдослучайной последовательности, блока отождествления элемента сигнала, демодулятора, депакетатора, приемника информации, М кодеров, М декодеров и К схем сравнения.

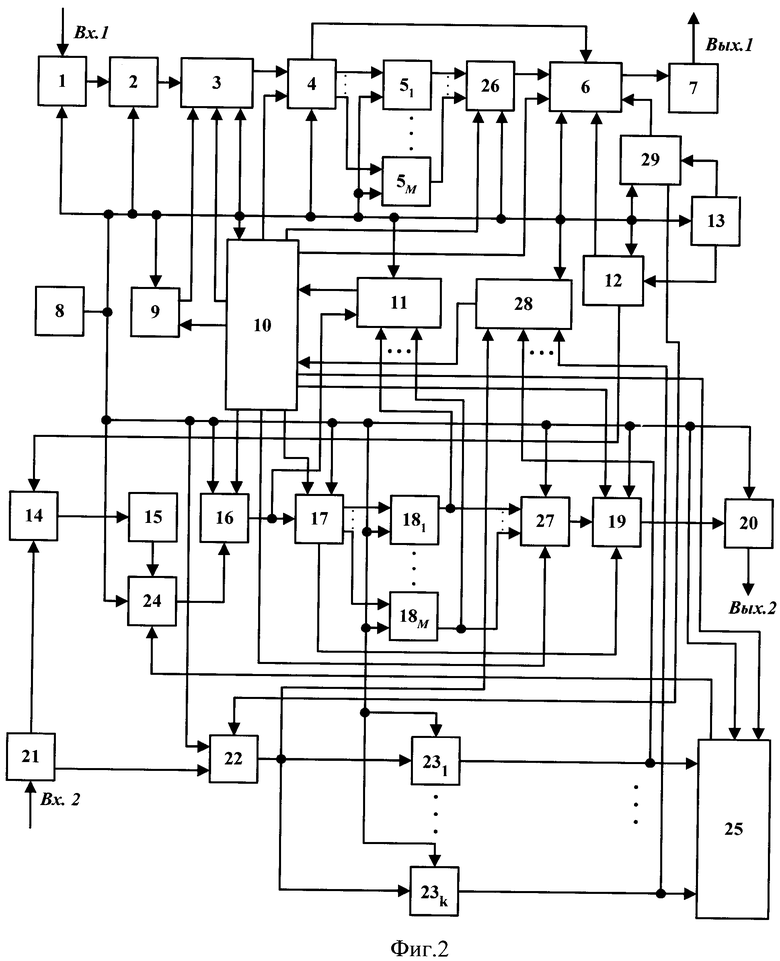

Функциональная схема предлагаемого адаптивного устройства передачи данных с псевдослучайной перестройкой рабочей частоты приведена на фиг.2, где приняты следующие обозначения:

1 - источник информации (ИИ);

2 - коммутатор скоростей (КС);

3 - пакетатор;

4 - первый демультиплексор (Д1);

51-5М - кодеры;

6 - модулятор;

7 - первый антенно-фидерный блок (АФБ1);

8 - генератор тактовых импульсов (ГТИ);

9 - генератор кодовых последовательностей (ГКП);

10 - блок управления (БУ);

11 - первый анализатор качества сигнала (АКС1);

12 - первый синтезатор частот (СЧ1);

13 - генератор псевдослучайной последовательности (ГПСП);

14 - преобразователь частоты (ПЧ);

15 - усилитель промежуточной частоты (УПЧ);

16 - демодулятор;

17 - второй демультиплексор (Д2);

181-18М - декодеры;

19 - депакетатор;

20 - приемник информации (ПИ).

21 - второй антенно-фидерный блок (АФБ2);

22 - блок отождествления элемента сигнала (БОЭС);

231-23К - схемы сравнения (СС);

24 - блок фазовой автоподстройки (БФА);

25 - третий мультиплексор (МЗ);

26 - первый мультиплексор (Ml);

27 - второй мультиплексор (М2);

28 - второй анализатор качества сигнала (АКС2);

29 - второй синтезатор частот (СЧ2).

Предлагаемое устройство содержит последовательно соединенные источник информации (ИИ) 1, вход которого является первым входом устройства, и коммутатор скоростей (КС) 2, выход которого соединен с первым сигнальным входом пакетатора 3, выход которого соединен с сигнальным входом первого демультиплексора (Д1) 4, М выходов которого соединены с сигнальными входами соответствующих М кодеров 51-5М, выходы которых соединены соответственно с М сигнальными входами первого мультиплексора (M1) 26, выход которого соединен с первым сигнальным входом модулятора 6, четвертый сигнальный вход которого соединен с (М+1)-м выходом Д1 4. Выход модулятора 6 соединен со входом первого антенно-фидерного блока (АФБ1) 7, выход которого является первым выходом устройства.

Кроме того, устройство содержит последовательно соединенные второй антенно-фидерный блок (АФБ2) 21, вход которого является вторым входом устройства, преобразователь частоты (ГТЧ) 14 и усилитель промежуточной частоты (УПЧ) 15, выход которого соединен с первым сигнальным входом блока фазовой автоподстройки (БФА) 24, выход которого соединен с сигнальным входом демодулятора 16, выход которого соединен с сигнальным входом второго демультиплексора (Д2) 17, М выходов которого соединены с сигнальными входами соответствующих М декодеров 181-18М, выходы которых соединены соответственно с М сигнальными входами второго мультиплексора (М2) 27, выход которого соединен с первым сигнальным входом депакетатора 19, второй сигнальный вход которого соединен с (М+1)-м выходом Д2 17. Выход депакетатора 19 соединен с сигнальным входом приемника информации (ПИ) 20, выход которого является вторым выходом устройства.

Также выходы М декодеров 181-18М соединены соответственно с М сигнальными входами первого анализатора качества сигнала (АКС1) 11, (М+1)-й сигнальный вход которого соединен с выходом демодулятора 16.

Второй выход АФБ2 21 соединен с первым сигнальными входом блока отождествления элемента сигнала (БОЭС) 22, выход которого соединен с сигнальными входами К схем сравнения (СС) 231-23К, выходы которых соединены с соответствующими К сигнальными входами третьего мультиплексора М3 25, выход которого соединен со вторым сигнальным входом БФА 24. Кроме того, выходы

СС 231-23К соединены соответственно с К сигнальными входами второго анализатора качества сигнала (АКС2) 28, (К+1)-й сигнальный вход которого соединен с выходом БОЭС 22.

С первого по десятый выходы блока управления (БУ) 10 соединены соответственно с управляющими входами пакетатора 3, Д1 4, M1 26, модулятора 6, депакетатора 19, Д2 17, М2 27, демодулятора 16, ГКП 9 и М3 25, причем выход ГКП 9 соединен со вторым сигнальным входом пакетатора 3. Выход АКС1 11 соединен с первым входом БУ 10, а выход АКС2 28 соединен со вторым входом БУ 10.

Первый выход генератора псевдослучайной последовательности (ГПСП) 13 соединен с сигнальным входом первого синтезатора частот (СЧ1) 12, первый выход которого соединен со вторым сигнальным входом модулятора 6, а второй выход - со вторым входом ПЧ 14.

Второй выход ГПСП 13 соединен с сигнальным входом второго синтезатора частот (СЧ2) 29, первый выход которого соединен с третьим сигнальным входом модулятора 6, а второй выход - со вторым сигнальным входом БОЭС 22.

Выход генератора тактовых импульсов (ГТИ) 8 соединен с тактовыми входами ИИ 1, КС 2, пакетатора 3, Д1 4, М кодеров 51-5M, M1 26, модулятора 6, ГКП 9, БУ 10, АКС1 11, АКС2 28, СЧ1 12, СЧ2 29, ГПСП 13, БОЭС 22, БФА 24, демодулятора 16, Д2 17, М декодеров 181-18К, М2 27, депакетатора 19, ПИ 20, М3 25, а также К СС 231-23К.

Устройство работает следующим образом. На передающем конце с первого входа устройства сигнал поступает в ИИ 1. Из ИИ 1 данные со скоростью С бит/сек, предназначенные для передачи по каналу связи, поступают в КС 2, где происходит преобразование информационной скорости С в техническую скорость V Бод. Из КС 2 информация подается на первый сигнальный вход пакетатора 3, где происходит ее деление на блоки информации с организацией слотов, фреймов и пакетов данных на основании управляющего сигнала, приходящего с первого выхода БУ 10. При этом ГКП 9 на основании управляющего сигнала, приходящего с девятого выхода БУ 10, формирует биты синхропоследовательности и выдает их на второй сигнальный вход пакетатора 3 для формирования в нем слотов синхронизации.

С выхода пакетатора 3 блоки информации поступают на сигнальный вход Д1 4, на управляющий вход которого подается сигнал со второго выхода БУ 10, на основании которого блок информации в Д1 4 разделяется на (М+1) каналов. При этом сигналы с соответствующих М выходов блока Д1 4 подаются на сигнальные входы соответствующих М кодеров 51-5M, где происходит помехоустойчивое кодирование информационных битов слота, а сигнал с (М+1)-го выхода подается на четвертый сигнальный вход модулятора 6. С выходов блоков 51-5M кодированные информационные слоты подаются на соответствующие сигнальные входы M1 26, в котором на основании управляющего сигнала, приходящего с третьего выхода БУ 10, происходит мультиплексирование М кодированных сигналов в один кодированный сигнал. С выхода M1 26 на первый сигнальный вход модулятора 6 подается пакет информации, содержащий служебные слоты и кодированные информационные слоты.

ГПСП 13 генерирует различные ПСП для формирования модулирующих частот. При этом с первого выхода ГПСП 13 на сигнальный вход СЧ1 2 подается первый код ПСП, на основании которого в нем формируется частота передачи для модуляции кодированных информационных битов информационных слотов, которая с первого выхода СЧ1 2 подается на второй сигнальный вход модулятора 6, а со второго выхода ГПСП 13 на сигнальный вход СЧ2 29 подается второй код ПСП, на основании которого в нем формируется частота передачи для модуляции синхропоследовательности служебных слотов, которая с первого выхода СЧ2 29 подается на третий сигнальный вход модулятора 6. Таким образом, в блоке 6 происходит модуляция служебных и информационных слотов различными частотами. Причем скорость перестройки частоты в модуляторе 6 определяется на основании управляющего сигнала, приходящего с четвертого выхода БУ 10. Полученный модулированный блок информации излучается в пространство с помощью АФБ1 7.

На приемном конце входной сигнал, представляющий собой смесь полезного сигнала и помех, принимается АФБ2 21, где происходит его разделение на служебную и информационную составляющие.

Часть входного сигнала, содержащая служебную составляющую, со второго выхода АФБ2 21 поступает на первый сигнальный вход БОЭС 22. Последовательность случайных элементов смеси преобразуется в БОЭС 22 в случайную последовательность решений о символах, соответствующих принятым элементам сигнала, с помощью частоты приема, полученной на втором выходе СЧ2 29 на основе второго кода ПСП, подаваемого со второго выхода ГПСП 13. Эта последовательность решений о символах в общем случае за счет действия помех не совпадает ни с одной из последовательностей символов элементов, которые использовались при формировании синхропоследовательностей в ГКП 9. В БОЭС 22 происходит оптимальная обработка смеси элемента сигнала и помехи, и на его выходе выдается последовательность решений о том, какой элемент синхропоследовательности (логический "0" или логическая "1") действовал, которая поступает на (К+1)-й сигнальный вход АКС2 28. Кроме того, полученная последовательность решений о символах поэлементно сравнивается с кодами ожидаемых синхропоследовательностей в соответствующих СС 231-2к.

Результаты сравнения с выходов СС 231-23К поступают на соответствующие сигнальные входы АКС2 28, где происходит анализ качества служебной составляющей сигнала, результат которого подается на второй вход БУ 10.

Кроме того, сигналы с выходов СС 231-23К подаются на соответствующие сигнальные входы М3 25, в котором на основании сигнала, приходящего с десятого выхода БУ 10, происходит их мультиплексирование в один сигнал, подаваемый на второй сигнальный вход БФА 24.

Другая часть входного сигнала, содержащая информационную составляющую, поступает на первый вход ПЧ 14, в котором происходит его преобразование на частоту приема, значение которой, определенное на основе первого кода ПСП, подается на второй вход ПЧ 14 со второго выхода СЧ1 12.

Затем сигнал промежуточной частоты усиливается в УПЧ 15 и поступает на первый сигнальный вход БФА 24, в котором происходит точная фазовая подстройка информационной составляющей и тактовой последовательности на основе служебной составляющей. Сигнал с выхода БФА 24 поступает на сигнальный вход демодулятора 16, где он демодулируется, причем скорость перестройки частоты определяется на основании управляющего сигнала, приходящего с восьмого выхода БУ 10. Причем точность демодуляции определяется точностью синхронизации тактовых импульсов из ГТИ 8 и сигнала из УПЧ 15, определяемой на основании сигнала из М3 25.

С выхода демодулятора 16 информационные слоты подаются на сигнальный вход Д2 17, на управляющий вход которого подается сигнал с шестого выхода БУ 10, на основании которого демодулированный сигнал в Д2 17 разделяется на (М+1) каналов. При этом сигналы с соответствующих М выходов Д2 17 подаются на сигнальные входы соответствующих М декодеров 181-18M, где происходит декодирование помехоустойчивого кода информационных битов слота.

С выходов блоков 181-18M декодированные информационные слоты подаются на соответствующие сигнальные входы М2 27, в котором на основании управляющего сигнала, приходящего с седьмого выхода БУ 10, происходит мультиплексирование М декодированных сигналов в один декодированный сигнал, который с выхода М2 27 подается на первый сигнальный вход депакетатора 19, на второй сигнальный вход которого подается сигнал с (М+1)-го выхода Д2 17.

В депакетаторе 19 происходит объединение в двоичную информационную последовательность, которая затем подается на сигнальный вход ПИ 20, где преобразуется в форму выходного сигнала.

Кроме того, результаты декодирования, определенные декодерами 181-18M, поступают соответственно на М сигнальных входов АКС1 11, на (М+1)-й сигнальный вход которого подаются демодулированные информационные слоты с выхода демодулятора 16. В АКС 11 происходит анализ качества информационной составляющей сигнала, результат которого поступает на первый вход БУ 10.

БУ 10 вырабатывает управляющие сигналы на основе информации, поступаемой на его первый и второй входы из соответствующих АКС1 11 и АКС2 28.

С выхода ГТИ 8 на блоки 1, 2, 3, 4, 51-5M, 26, 6, 29, 12, 13, 28, 11, 10, 9, 24, 22, 16,17,

181-18M, 231-23K, 27, 19, 20 и 25, подаются тактовые импульсы, определяющие начало каждой микрооперации, в результате чего обеспечивается синхронизация работы устройства в целом.

БУ 10 может быть реализован в виде перепрограммируемого цифрового устройства, алгоритм функционирования которого представлен на фиг.3.

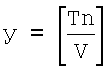

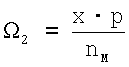

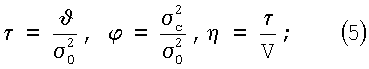

Работа БУ 10 начинается с нулевого состояния блока 10.3, где происходит обнуление количества информационных слотов (р=0), а также с присвоения в блоке 10.1 значения времени перестройки частоты Tn=const 1, в блоке 10.2 - значения времени рассинхронизации синтезаторов частот Тр=const 2, в блоке 10.4 - значения числа повторов слотов синхронизации d=const 3 и в блоке 10.5 - значения минимально необходимого числа бит в служебных фреймах е=const 4. На основании значения блока 10.1 в блоке 10.6 происходит расчет необходимого количества битов перестройки частоты  , где V - скорость передачи в радиосредстве, [] - целая часть. В блоке 10.7 первоначально происходит увеличение значения блока 10.3 на единицу.

, где V - скорость передачи в радиосредстве, [] - целая часть. В блоке 10.7 первоначально происходит увеличение значения блока 10.3 на единицу.

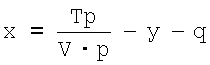

На основании значения блоков 10.6, 10.2 и 10.7 в блоке 10.10 происходит вычисление значения количества информационных битов слота  , где q=[х·λ2] - количества защитных бит информационного слота, и проверка условия х - целое, где λ2 - коэффициент, зависящий от количества частоты ППРЧ и априорно известных условий распространения сигнала (например, для фиксированной частоты можно принять λ2≈3%; для ППРЧ из двух частот - λ2≈6% и т.д.). Если условие не будет выполнено, то из блока 10.10 по линии "нет" происходит переход к блоку 10.7, а если выполнено, то из блока 10.10 по линии "да" в блок 10.15 вводятся значения х, у и р, а в блоки 10.24.1-10.24.М значения х и р, где рассчитывается число кодовых слов в информационном фрейме

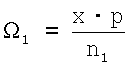

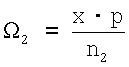

, где q=[х·λ2] - количества защитных бит информационного слота, и проверка условия х - целое, где λ2 - коэффициент, зависящий от количества частоты ППРЧ и априорно известных условий распространения сигнала (например, для фиксированной частоты можно принять λ2≈3%; для ППРЧ из двух частот - λ2≈6% и т.д.). Если условие не будет выполнено, то из блока 10.10 по линии "нет" происходит переход к блоку 10.7, а если выполнено, то из блока 10.10 по линии "да" в блок 10.15 вводятся значения х, у и р, а в блоки 10.24.1-10.24.М значения х и р, где рассчитывается число кодовых слов в информационном фрейме  ,

,  , …,

, …,  , соответственно (n1, n2, …, nM - длины тех М помехоустойчивых кодов, которые используются в данном радиосредстве).

, соответственно (n1, n2, …, nM - длины тех М помехоустойчивых кодов, которые используются в данном радиосредстве).

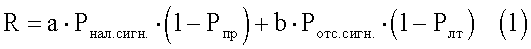

Из блока 28 в блоки 10.9.1-10.9K поступает значение вероятности ошибки на бит в канале синхронизации для определения вероятностей правильного приема Рпр и ложной тревоги Рлт. В этих блоках производится расчет средних рисков Rj (j=1…K) по формуле R=а·Рнал.сигн.·(1-Рпр)+b·Ротс.сигн.·(1-Рлт), где Ротс.сигн. - априорная вероятность отсутствия сигнала; Рнал.сигн. - априорная вероятность наличия сигнала; а и b - весовые коэффициенты, зависящие от того, насколько опасна Рлт по сравнению с 1-Рпр. Полученные в блоках 10.9.1-10.9.К значения средних рисков R1-RК поступают в блок 10.8, где определяется минимальное из них значение - min, которое поступает в блоки 10.11.1-10.11.К, где последовательно, начиная с блока 10.9.1, производится проверка условий:

- если выполняется условие min=R1, то по линии "да" в блоке 10.12.1 присваивается значение длины синхропоследовательности L=L1, если не выполняется - по линии "нет" происходит проверка условия min=R2 в следующем блоке 10.11.2;

- если выполняется условие min=R2, то по линии "да" в блоке 10.12.2 присваивается значение длины синхропоследовательности L=L2, если не выполняется - по линии "нет" происходит проверка условия min=R3 в следующем блоке 10.11.3 и.т.д.

Значение того из блоков 10.12.1-10.12.K, где произошло присвоение, загружается в блоки 9, 25 и в блок 10.13, где происходит вычисление количества защитных бит служебного слота z=[L·λ1], где [] - целая часть, а λ1 - коэффициент, зависящий от количества частот ППРЧ и априорно известных условий распространения сигнала, аналогичный описанному выше.

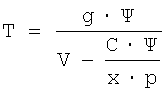

Значения блоков 10.4 и 10.13 вводятся в блок 10.15, где производится расчет количества бит во фрейме Ψ=(y+L+z)·d+(y+x+q)·p. Значения у, L, х, z, d, Ψ и р записываются в блок 10.17 и загружаются в блоки 3 и 19.

Полученное в блоке 10.15 значение ψ и значение блока 10.18 загружаются в блок 10.20, где происходит вычисление значения времени передачи пакета  и проверка условия Т - целое, где С - необходимая скорость передачи информации. Если условие выполняется, по линии "да" в блок 10.21 записываются величины Т и g, которые затем загружаются в блоки 3 и 19. Если условие не выполнено, по линии "нет" происходит переход к блоку 10.18. Кроме того, значения Т и g из блока 10.21 загружаются в блок 10.22, где рассчитывается скорость ППРЧ

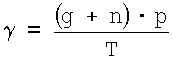

и проверка условия Т - целое, где С - необходимая скорость передачи информации. Если условие выполняется, по линии "да" в блок 10.21 записываются величины Т и g, которые затем загружаются в блоки 3 и 19. Если условие не выполнено, по линии "нет" происходит переход к блоку 10.18. Кроме того, значения Т и g из блока 10.21 загружаются в блок 10.22, где рассчитывается скорость ППРЧ  , которая выдается в блоки 6 и 16.

, которая выдается в блоки 6 и 16.

Из блока 10.15 значение Ψ, кроме того, загружается в блок 10.14, где происходит проверка условия е≤Ψ. Если условие не будет выполнено, то из блока 10.14 по линии "нет" происходит переход к блоку 10.19, где происходит присвоение  , [] - целая часть, а если выполнено - то из блока 10.14 по линии "да" в блоке 10.16 происходит присвоение g=0. Значение того из блоков 10.16 или 10.19, где произошло присвоение, загружается в блок 10.18, где увеличивается на единицу.

, [] - целая часть, а если выполнено - то из блока 10.14 по линии "да" в блоке 10.16 происходит присвоение g=0. Значение того из блоков 10.16 или 10.19, где произошло присвоение, загружается в блок 10.18, где увеличивается на единицу.

Из блока 11 в блоки 10.23.0-10.23.М поступает значение вероятности ошибки на бит в информационном канале для определения вероятностей правильного приема W, W1-WМ кодовых слов тех М помехоустойчивых кодов, которые используются в данном радиосредстве (W рассчитывается для случая, когда помехоустойчивый код не используется). Полученные в блоках 10.23.1-10.23.М значения W1-WM поступают соответственно в блоки 10.25.1-10.25.М.

Значение блока 10.23.0 также поступает в каждый из блоков 10.25.1-10.25.М, где последовательно, начиная с блока 10.25.1, производится проверка условий:

- если выполняется условие W1>W, то по линии "да" в блоке 10.26.1 происходит сравнение Ω1 с целым числом, если не выполняется - по линии "нет" происходит проверка условия W2>W в следующем блоке 10.25.2;

- если выполняется условие W2>W, то по линии "да" в блоке 10.26.2 происходит сравнение Ω2 с целым числом, если не выполняется - по линии "нет" происходит проверка условия W3>W в следующем блоке 10.25.3;

…

- если выполняется условие WM>W, то по линии "да" в блоке 10.26.М происходит сравнение ΩM с целым числом, если не выполняется - по линии "нет" в блоке 10.27.0 происходит присвоение i=0.

Рассчитанные в блоках 10.24.1-10.24.М значения Ω1, Ω2, …, Ω3 поступают соответственно в блоки 10.26.1-10.26.М, где последовательно, начиная с блока 10.26.1, производится проверка условий:

- если выполняется условие, что Ω1 - целое число, то по линии "да" в блоке 10.27.1 происходит присвоение i=1, если не выполняется - по линии "нет" происходит проверка условия W2>W в блоке 10.25.2;

- если выполняется условие, что Ω2 - целое число, то по линии "да" в блоке 10.27.2 происходит присвоение i=2, если не выполняется - по линии "нет" происходит проверка условия W3>W в блоке 10.25.3;

- если выполняется условие, что ΩM - целое число, то по линии "да" в блоке 10.27.М происходит присвоение i=M, если не выполняется - по линии "нет" происходит увеличение значения блока 10.7 на единицу.

Значение того из блоков 10.27.0-10.27.М, где произошло присвоение, загружается в блоки 4, 17, 26 и 27.

АКС1 11 и АКС2 28 могут быть реализованы, например, как BER-тестеры [5, глава 8]. БФА 24 может быть реализован в виде схем привязки синхросигнала к битовым интервалам принимаемых данных [5, глава 9]. БОЭС 22 может быть реализован как решающее устройство [4, глава 7.4]. СС 231-23K могут быть реализованы в виде дискретных согласованных фильтров [4, глава 7.4-7.5].

Модулятор 6 и демодулятор 16 могут быть реализованы как процессоры семейства DSP56800 фирмы Motorola [7, стр.1-11, глава 5].

Реализация других блоков предлагаемого устройства может быть осуществлена с помощью цифровых устройств, известных из технической литературы.

В качестве примера функционирования предлагаемого устройства предположим, что через радиостанцию, имеющую техническую скорость V=19.2 кБод, передаются данные от аппаратуры передачи данных со скоростью С=12 кбит/с. Пример временной диаграммы сформированного пакета информации, состоящего из фреймов и слотов, удовлетворяющей данному случаю, показан на фиг.4, откуда следует, что число информационных битов в блоке х=45, а скорость ППРЧ γ=300 скач/сек. В качестве синхропоследовательностей используются три двоичные М-последовательности с L1=31, L2=63 и L3=127, а в качестве устройства для их определения на приеме - дискретный согласованный фильтр (ДСФ) [4, стр.275]. Предполагается, что используемый ДСФ производит обнаружение синхропоследовательности в реальном масштабе времени [4, стр.279-282] методом равномерного стробирования каждого условного бита не одной, а в u=8 точках, что более полно использует информацию о сигнале: при совпадении не менее 3 подряд последовательностей (из полученных u=8) с копией сигнала (с допуском до u0 ошибок для каждой последовательности) выносится решение о приеме синхросигнала. Вид каждой из М-последовательностей задается путем выстраивания последовательности триггерных ячеек в ДСФ [4, стр.279].

Средние риски Rj, где j∈{1, …, K}, рассчитываются по формуле:

где Ротс.сигн - априорная вероятность отсутствия сигнала;

Рнал.сигн - априорная вероятность наличия сигнала;

а и b - весовые коэффициенты, зависящие от того, насколько опасна Рлт по сравнению с 1-Рпр.

Если в формуле (1) принять Ротс.сигн=0.8, Рнал.сигн =0.2 и отношение a/b=0.01, то при вероятности ошибки на бит р∈{0.15, …, 0.45}, определяемой анализатором качества сигнала, по формуле (1) можно рассчитать средние риски R1, R2, R3.

На фиг.5 представлены средние риски при приеме М-последовательностей различной длины. Анализируя фиг.5, можно определить, что в качестве синхронизирующей для следующего пакета применяется та М-последовательность, чей график лежит "ниже" других.

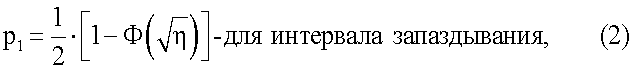

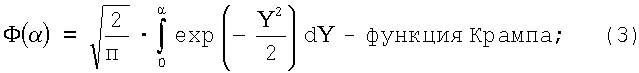

После определения вида синхросигнала решается следующая задача: определение необходимости применения помехоустойчивого кода в условиях воздействия запаздывающих помех. Для этого рассчитываются вероятности ошибки на бит: 1

где

где:

- мощность сигнала;

- мощность сигнала;

- спектральная плотность мощности белого шума;

- спектральная плотность мощности белого шума;

- спектральная плотность мощности запаздывающей помехи.

- спектральная плотность мощности запаздывающей помехи.

На фиг.6 представлена временная диаграмма информационных битов слота при воздействии запаздывающей помехи. Для данной временной диаграмы:

хн=[x·θ] - число непораженных информационных битов в слоте;

хn=х-хн - число пораженных информационных битов в слоте; Т

где:  - коэффициент запаздывания помехи;

- коэффициент запаздывания помехи;

Тсл - время действия запаздывающей помехи;

Тз - время запаздывания помехи.

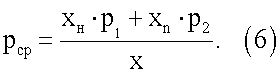

Окончательно средняя вероятность ошибки на бит определяется:

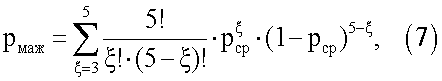

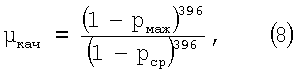

В случае если условия распространения сигнала требуют от пользователя более высокой гарантии доведения информации до получателя, временная диаграмма позволяет "пожертвовать" скоростью передачи информации для увеличения качества передачи последней. Пример временной диаграммы, удовлетворяющей данному случаю, показан на фиг.7. В случае использования в качестве помехоустойчивого кода мажоритарной обработки (правило выбора 3 из 5), временная диаграмма принимает вид, представленный на фиг.7, а средняя вероятность ошибки на бит, согласно [6], определяется:

где ξ - индекс суммирования.

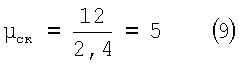

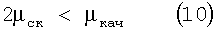

Поскольку в случае применения мажоритара информационная скорость уменьшится с С=12 кбит/с до β=2,4 кбит/с, число битов информации в слоте будет 396. Следовательно, можно рассчитать коэффициент улучшения качества передачи битов как отношение вероятности правильного приема 396 битов информации после и до применения мажоритара

при этом коэффициент использования скорости информации равен

Зависимость µкач от τ при значениях коэффициента запаздывания θ=0.8 и θ=0.2 приведены, соответственно, на фиг.8 и фиг.9. Таким образом, при условии выбора пользователем критерия смены скоростей

(то есть пользователь "жертвует" скоростью передачи только в случае, если ухудшение скорости в µ раз приведет к улучшению качества передачи более чем в 2µ раз) анализируется качество информационного сигнала, по которому определяются значения τ, θ и φ, по которым вычисляются значения µск и µкач, которые сравниваются согласно критерию (10) и по результату сравнения принимается решение: изменять ли скорость передачи информации или нет (то есть, применять ли метод помехоустойчивой защиты или нет).

В данном случае при θ=0,8, применение мажоритара происходит при τ>1,7, а при θ=0,2 - при τ>4,8.

На фиг.10 приведена зависимость µкач от τ и θ для различных случаев: 1) при φ=5; 2) при φ=20000; 3) границы критерия. Если в результате анализа качества сигнала определяется, что рабочая точка лежит на какой-либо из плоскостей (1 или 2) выше плоскости 3, применяется мажоритарная обработка.

Таким образом, введение в предлагаемом устройстве новых блоков и связей позволяет увеличить достоверность приема информации за счет адаптации синхросигнала к изменению помеховой обстановки, что позволяет применять его в спецсвязи в условиях воздействия преднамеренных помех.

Источники информации

1. Патент РФ на изобретение №2185029 "Радиолиния с псевдослучайной перестройкой рабочей частоты", Одоевский С.М., Ерышов В.Г., 2001 год.

2. Заявка РФ на изобретение №2001102653 "Способ и устройство псевдослучайной перестройки рабочей частоты", Постников В.А., Шубенкин В.В., 2001 год.

3. Патент РФ на изобретение №2097923 "Способ передачи дискретной информации в радиолинии с псевдослучайной перестройкой рабочих частот и устройство его реализующее", Булычев О.А.; Игнатов В.В.; Щукин А.Н. 1997.

4. Шумоподобные сигналы в системах передачи информации. Под ред. проф. В.Б.Пестрякова. М., "Сов. радио", 1973.

5. С.Н.Сухман, А.В.Бернов, Б.В.Шевкопляс. Синхронизация в телекоммуникационных системах. Анализ инженерных решений. - М.: Эко-Трендз, 2003.

6. Феер. К. Беспроводная цифровая связь. Методы модуляции и расширения спектра: Пер. с англ. / Под ред. В.И.Журавлева. - М., Радио и связь, 2000.

7. Техническое обеспечение цифровой обработки сигналов. Справочник. Куприянов М.С., Матюшкин Б.Д., Иванова В.Е., Матвиенко Н.И., Усов Д.Ю. - СПб., "Форт", 2000.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АДАПТИВНОЙ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2007 |

|

RU2356167C1 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ДИНАМИЧЕСКИ ИЗМЕНЯЕМОЙ ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2396713C1 |

| УСТРОЙСТВО РАДИОСВЯЗИ СО СКАЧКООБРАЗНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2005 |

|

RU2313178C2 |

| РАДИОМОДЕМ | 2010 |

|

RU2439820C1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| СПОСОБ ЗАЩИТЫ ИНФОРМАЦИИ В РАДИОСЕТИ С ПАКЕТНОЙ ПЕРЕДАЧЕЙ ДАННЫХ | 2009 |

|

RU2425455C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ СО СКАЧКООБРАЗНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2005 |

|

RU2290758C1 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

| СПОСОБ И ЛИНИЯ РАДИОСВЯЗИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2005 |

|

RU2279760C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2097923C1 |

Предлагаемое устройство относится к области радиотехники и может найти применение в адаптивных системах специальной радиосвязи для передачи данных по радиоканалу в условиях воздействия комплекса преднамеренных помех. Достигаемый технический результат - увеличение достоверности приема информации за счет адаптации синхросигнала к изменению помеховой обстановки. Устройство содержит источник информации, коммутатор скоростей, пакетатор, первый и второй демультиплексоры, М кодеров, модулятор, первый и второй антенно-фидерные блоки, генератор тактовых импульсов, генератор кодовых последовательностей, блок управления, первый и второй анализаторы качества сигнала, первый и второй синтезаторы частот, генератор псевдослучайной последовательности, преобразователь частоты, усилитель промежуточной частоты, демодулятор, М декодеров, депакетатор, приемник информации, блок отождествления элемента сигнала, К схем сравнения, блок фазовой автоподстройки, первый, второй и третий мультиплексоры. 10 ил.

Адаптивное устройство передачи данных с псевдослучайной перестройкой рабочей частоты, содержащее источник информации, вход которого является первым входом устройства, приемник информации, выход которого является вторым выходом устройства, последовательно соединенные модулятор и первый антенно-фидерный блок, выход которого является первым выходом устройства; последовательно соединенные генератор псевдослучайной последовательности и первый синтезатор частот, соединенный со вторым сигнальным входом модулятора; генератор тактовых импульсов, второй синтезатор частот, демодулятор, последовательно соединенные второй антенно-фидерный блок, вход которого является вторым входом устройства, преобразователь частоты и усилитель промежуточной частоты, отличающееся тем, что введены коммутатор скоростей, пакетатор, депакетатор, генератор кодовых последовательностей, блок управления, блок отождествления элемента сигнала, блок фазовой автоподстройки, первый и второй анализаторы качества сигнала, первый и второй демультиплексоры, первый, второй и третий мультиплексоры, М кодеров, М декодеров и К схем сравнения; кроме того, в источнике информации, модуляторе, демодуляторе, генераторе псевдослучайной последовательности, первом и втором синтезаторах частот дополнительно введено по тактовому входу, а в модуляторе и демодуляторе дополнительно введено по управляющему входу; при этом вход источника информации через коммутатор скоростей соединен с первым сигнальным входом пакетатора, выход которого соединен с сигнальным входом первого демультиплексора, М выходов которого соединены с сигнальными входами соответствующих М кодеров, выходы которых соединены соответственно с М сигнальными входами первого мультиплексора, выход которого соединен с первым сигнальным входом модулятора; выход демодулятора соединен с сигнальным входом второго демультиплексора, М выходов которого соединены с сигнальными входами соответствующих М декодеров, выходы которых соединены соответственно с М сигнальными входами второго мультиплексора, выход которого соединен с первым сигнальным входом депакетатора, второй сигнальный вход которого соединен с (М+1)-м выходом второго демультиплексора, а выход депакетатора соединен с сигнальным входом приемника информации; также выходы М декодеров соединены соответственно с М сигнальными входами первого анализатора качества сигнала, (М+1)-й сигнальный вход которого соединен с выходом демодулятора; выход усилителя промежуточной частоты соединен с первым сигнальным входом блока фазовой автоподстройки, выход которого соединен с сигнальным входом демодулятора; второй антенно-фидерный блок выполнен с возможностью разделения сигнала на служебную и информационную составляющие и в нем дополнительно введен второй выход, соединенный с первым сигнальными входом блока отождествления элемента сигнала, выход которого соединен с сигнальными входами К схем сравнения, выходы которых соединены соответственно с К сигнальными входами третьего мультиплексора, выход которого соединен со вторым сигнальным входом блока фазовой автоподстройки; кроме того, выходы К схем сравнения соединены с К сигнальными входами второго анализатора качества сигнала, (К+1)-й сигнальный вход которого соединен с выходом блока отождествления элемента сигнала; с первого по десятый выходы блока управления соединены соответственно с управляющими входами пакетатора, первого демультиплексора, первого мультиплексора, модулятора, депакетатора, второго демультиплексора, второго мультиплексора, демодулятора, генератора кодовых последовательностей и третьего мультиплексора, причем выход генератора кодовых последовательностей соединен со вторым сигнальным входом пакетатора; выходы первого и второго анализаторов качества сигнала соединены соответственно с первым и вторым входами блока управления; второй выход генератора псевдослучайной последовательности соединен с сигнальным входом второго синтезатора частот, первый выход которого соединен с введенным дополнительно третьим сигнальным входом модулятора, (М+1)-й выход первого демультиплексора соединен с введенным дополнительно четвертым сигнальным входом модулятора, в первом синтезаторе частот введен дополнительно второй выход, соединенный со вторым входом преобразователя частоты, во втором синтезаторе частот введен дополнительно второй выход, соединенный со вторым сигнальным входом блока отождествления элемента сигнала; выход генератора тактовых импульсов соединен с тактовыми входами источника информации, коммутатора скоростей, пакетатора, первого и второго демультиплексоров, первого, второго и третьего мультиплексоров, модулятора, генератора кодовых последовательностей, блока управления, блока фазовой автоподстройки, первого и второго анализаторов качества сигнала, первого и второго синтезаторов частот, генератора псевдослучайной последовательности, блока отождествления элемента сигнала, демодулятора, депакетатора, приемника информации, М кодеров, М декодеров и К схем сравнения.

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2097923C1 |

| Устройство для резки профильного проката | 1978 |

|

SU774842A2 |

| US 5414771 А, 09.05.1995 | |||

| US 5537434 А, 16.07.1996 | |||

| ЕР 0798874 А2, 01.10.1997. | |||

Авторы

Даты

2009-05-20—Публикация

2008-01-09—Подача