Предлагаемое устройство относится к области радиотехники и может найти применение в системах передачи информации со скачкообразной перестройкой рабочей частоты.

Известно устройство передачи информации с псевдослучайной перестройкой рабочей частоты (ППРЧ), описанное в патенте РФ №2099886, Н 04 L 5/02. Булычев О.А., Калинин В.М., Попов В.И. "Способ передачи информации в радиолинии с псевдослучайной перестройкой рабочих частот и устройство его реализующее", 1997 г., в котором из информационного сигнала формируются пакеты, которые модулируются на соответствующих частотах и излучаются в пространство. Недостатком этого устройства является то, что частота модуляции не является полностью случайной, а выбирается исходя из лучшей помеховой обстановки на частотах, задаваемых генераторами псевдослучайной последовательности, а также то, что передаваемая информация не защищена от несанкционированного доступа.

Известно устройство передачи информации с ППРЧ, описанное в заявке РФ на изобретение №2001102653, Н 04 В 1/713, Н 04 L 5/06, Н 04 J 13/06. Постников В.А., Шубенкин В.В. "Способ и устройство псевдослучайной перестройки рабочей частоты", 2003 г., в котором значение рабочей частоты, по-прежнему формируемой по псевдослучайному закону, изменяется в псевдослучайные моменты времени, гарантированно синхронные для обеих сторон радиолинии (путем использования дополнительных синхронных псевдослучайных последовательностей). Недостатком данного устройства является необходимость точной синхронизации радиолинии, что значительно усложнит аппаратуру, а также то, что передаваемая информация не защищена от несанкционированного доступа.

Наиболее близким по технической сущности к предлагаемому устройству является устройство, описанное в заявке РФ на изобретение №99123808, Н 04 В 1/713. Деркач Е.Н., Попов В.И., Лазоренко B.C., Сивоконев В.Н. "Способ передачи дискретной информации в радиолинии с псевдослучайной перестройкой рабочей частоты и устройство, его реализующее", 2001 г., принятое за прототип.

Функциональная схема устройства-прототипа представлена на фиг.1, где приняты следующие обозначения:

1 - источник информации (ИИ);

2 - пакетатор-депакетатор (ПД);

3 - модулятор;

4 - первый антенно-фидерный блок (АФБ1), (антенное устройство);

5 - синхрогенератор;

6 - приемник информации (ПИ);

7 - первый синтезатор частот (СЧ1);

8 - первый генератор псевдослучайной последовательности (ГНПСП1);

9 - коммутатор;

10 - второй генератор псевдослучайной последовательности (ГНПСП2);

11 - четвертый синтезатор частот (СЧ4);

12 - второй синтезатор частот (СЧ2);

13 - третий синтезатор частот (СЧ3);

14 - пятый синтезатор частот (СЧ5);

15 - второй антенно-фидерный блок (АФБ2), (антенное устройство);

16 - первый преобразователь частоты (ГТЧ1);

17 - первый усилитель промежуточной частоты (УПЧ1);

18 - первый демодулятор (ДМ1);

19 - второй преобразователь частоты (ПЧ2);

20 - второй усилитель промежуточной частоты (УПЧ2);

21 - второй демодулятор (ДМ2);

22 - третий преобразователь частоты (ПЧ3);

23 - первый амплитудный детектор (АД1);

24 - первой пороговый блок (ПБ1), (пороговое устройство);

25 - четвертый преобразователь частоты (ПЧ4);

26 - второй амплитудный детектор (АД2);

27 - второй пороговый блок (ПБ2), (пороговое устройство);

28 - схема сравнения (СС).

Устройство-прототип содержит последовательно соединенные источник информации (ИИ) 1, вход которого является первым входом устройства (передающий конец), пакетатор-депакетатор (ПД) 2, модулятор 3 и первый антенно-фидерный блок (АФБ1) 4, выход которого является первым выходом устройства; последовательно соединенные первый преобразователь частоты (ПЧ1) 16, первый усилитель промежуточной частоты (УПЧ1) 17 и первый демодулятор (ДМ1) 18, выход которого соединен с первым входом синхроге-нератора 5 и вторым входом ПД 2; последовательно соединенные второй преобразователь частоты (ПЧ2) 19, второй усилитель промежуточной частоты (УПЧ2) 20 и второй демодулятор (ДМ2) 21, выход которого соединен со вторым входом синхрогенератора 5 и третьим входом ПД 2; последовательно соединенные третий преобразователь частоты (ПЧ3) 22, первый амплитудный детектор (АД1) 23 и первой пороговый блок (ПБ1) 24, выход которого соединен с первым входом схемы сравнения (СС) 28; последовательно соединенные четвертый преобразователь частоты (ПЧ4) 25, второй амплитудный детектор (АД2) 26 и второй пороговый блок (ПБ2) 27, выход которого соединен со вторым входом СС 28; первый генератор псевдослучайной последовательности (ГНПСП1) 8, выход одного из последующих тактов которого соединен с входом четвертого синтезатора частот (СЧ4) 11, а выход текущего значения ГНПСП 1 8 подключен к входу второго синтезатора частот (СЧ2) 12 и первому входу коммутатора 9; второй генератор псевдослучайной последовательности (ГНПСП2) 10, выход одного из последующих тактов которого соединен с входом пятого синтезатора частот (СЧ5) 14, а выход текущего значения ГНПСП2 10 подключен к входу третьего синтезатора частот СЧ3 13 и второму входу коммутатора 9, выход которого соединен с входом первого синтезатора частот (СЧ1) 7, выход которого соединен с управляющим входом модулятора 3. Вторым входом устройства (приемный конец) является вход второго антенно-фидерного блока (АФБ2) 15, выход которого подключен к первым входам ПЧ1 16, ПЧ2 19, ПЧ3 22 и ПЧ4 25. Выход синхрогенератора 5 подключен к входу ГНПСП1 8, входу ГНПСП2 10 и третьему входу СС 28, выход которой соединен с четвертым входом ПД2, второй выход которого соединен с входом приемника информации (ПИ) 6, выход которого является вторым выходом устройства. Выход СЧ4 11 соединен со вторым входом ПЧ3 22. Выход СЧ2 12 соединен со вторым входом ПЧ1 16. Выход СЧ3 13 соединен с вторым входом ПЧ2 19. Выход СЧ5 14 соединен со вторым входом ПЧ4 25. Третий выход ПД2 подключен к управляющему входу коммутатора 9.

Устройство-прототип работает следующим образом. На передающем конце входной сигнал поступает в ИИ 1. Из ИИ 1 двоичная информационная последовательность поступает в ПД 2, где происходит ее деление на блоки. Каждый блок модулируется в модуляторе 3 с помощью частоты, полученной в СЧ1 7 на основе кода, определенного в ГНПСП1 8 и ГНПСП2 10. Выбор кода определяется коммутатором на основе сигнала управления, поступаемого из ПД2. Модулированный блок излучается в пространство с помощью АФБ1 4.

На приемном конце входной сигнал, принятый АФБ2 15, поступает в ПЧ1 16 и ПЧ2 19, где производится его преобразование с помощью частоты, полученной соответственно в СЧ2 12 и СЧЗ 13 на основе кода, определенного соответственно в ГНПСП1 8 и ГНПСП2 10, на промежуточную частоту с последующим его усилением соответственно в УПЧ1 17 и УПЧ2 20 и демодуляцией соответственно в ДМ1 18 и ДМ2 21. Демодулированные в ДМ1 18 и ДМ2 21 блоки объединяются в ПД 2 в двоичную информационную последовательность, которая поступает в ПИ 6, где преобразуется в форму выходного сигнала.

Кроме того, сигнал, принятый АФБ2 15, поступает в ПЧ3 22 и ПЧ4 25, где производится его преобразование с помощью частоты, полученной соответственно в СЧ4 11 и СЧ5 14 на основе кода, определенного соответственно в ГНПСП1 8 и ГНПСП2 10, для последующего детектирования соответственно в АД1 23 и АД2 26. Детектированные в АД1 23 и АД2 26 сигналы сравниваются с порогом соответственно в ПБ1 24 и ПБ2 27. На основе результатов сравнения СС 28 формирует управляющую информацию для ПД2.

Синхрогенератор 5 синхронизирует работу ГНПСП1 8, ГНПСП2 10 и СС 28. Демодулированные в ДМ1 18 и ДМ2 21 сигналы управляют работой синхрогенератора 5.

Существенным недостатком устройства-прототипа является низкая помехоустойчивость при воздействии преднамеренных помех, а также отсутствие защиты от несанкционированного доступа.

Для устранения указанных недостатков в устройство радиосвязи со скачкообразной перестройкой рабочей частоты, содержащее последовательно соединенные источник информации, информационный вход которого является первым входом устройства, и пакетатор-депакетатор; последовательно соединенные модулятор и первый антенно-фидерный блок, выход которого является первым выходом устройства, второй антенно-фидерный блок, вход которого является вторым входом устройства, пороговый блок, синхрогенератор, синтезатор частот и приемник информации, выход которого является вторым выходом устройства, причем второй выход пакетатора-депакетатора соединен с информационным входом приемника информации, выход синтезатора частот соединен с управляющим входом модулятора, согласно изобретению введены последовательно соединенные микропроцессор, первый блок памяти и генератор кода, выход которого соединен с информационным входом модулятора, а также второй блок памяти, k-частотных фильтров и k-корреляторов, при этом выход второго антенно-фидерного блока соединен с объединенными информационными входами k-частотных фильтров, выходы которых соединены с объединенными соответствующими параллельными входами k-корреляторов, объединенные выходы которых соединены с входом порогового блока, выход которого соединен со вторым входом первого блока памяти, k-параллельных выходов которого соединены с последовательными входами соответствующих корреляторов; второй последовательный выход первого блока памяти соединен со вторым входом микропроцессора, третий выход которого соединен с третьим входом пакетатора-депакетатора, а второй выход - с входом второго блока памяти, k-параллельных выходов которого соединены с управляющими входами соответствующих частотных фильтров; кроме того, в источнике информации, модуляторе и получателе информации дополнительно введены синхронизирующие входы, а в синхрогенераторе дополнительно введен второй выход, причем первый выход синхрогенератора соединен с синхронизирующими входами источника информации, пакетатора-депакетатора, генератора кода и модулятора, а второй выход синхрогенератора соединен с синхронизирующим входом получателя информации, а также с объединенными синхронизирующими входами k-коррелляторов и k-частотных фильтров.

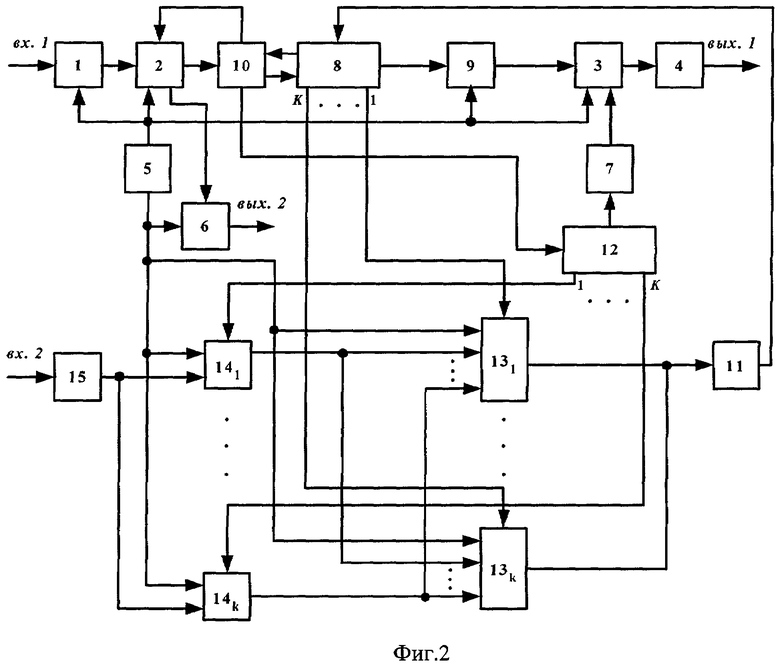

Функциональная схема предлагаемого устройства представлена на фиг.2, где приняты следующие обозначения:

1 - источник информации (ИИ);

2 - пакетатор-депакетатор (ПД);

3 - модулятор;

4 - первый антенно-фидерный блок (АФБ1);

5 - синхрогенератор;

6 - приемник информации (ПИ);

7 - синтезатор частот (СЧ);

8 - первый блок памяти (БП1);

9 - генератор кода (ГК);

10 - микропроцессор;

11 - пороговый блок;

12 - второй блок памяти (БП2);

13l-13k -корреляторы;

14l-l 4k - частотные фильтры (ЧФ);

15 - второй антенно-фидерный блок (АФБ2).

Предлагаемое устройство содержит последовательно соединенные источник информации (ИИ) 1, информационный вход которого является первым входом устройства (передающий конец), пакетатор-депакетатор (ПД) 2, микропроцессор 10, первый блок памяти (БП1) 8, генератор кода (ГК) 9, модулятор 3 и первый антенно-фидерный блок (АФБ1) 4, выход которого является первым выходом устройства; последовательно соединенные второй блок памяти (БП2) 12 и синтезатор частот (СЧ) 7, выход которого соединен с управляющим входом модулятора 3. Вторым входом устройства (приемный конец) является вход второго антенно-фидерного блока (АФБ2) 15, выход которого соединен с объединенными информационными входами k-частотных фильтров (ЧФ) 14l-14k, объединенные синхронизирующие входы которых соединены со вторым выходом синхрогенератора 5, первый выход которого соединен с синхронизирующими входами ИИ 1, ПД 2, ГК 9 и модулятора 3. Выходы ЧФ 14l-14k соединены с объединенными соответствующими параллельными входами k корреляторов 13l-13k объединенные синхронизирующие входы которых соединены со вторым выходом синхрогенератора 5 и синхронизирующим входом приемника информации (ПИ) 6, выход которого является вторым выходом устройства, причем k-параллельных выходов БП1 8 соединены с последовательными входами соответствующих корреляторов 131-13k, объединенные выходы которых соединены с входом порогового блока 11, выход которого соединен со вторым входом БП1 8, второй последовательный выход которого соединен со вторым входом микропроцессора 10, второй выход которого соединен с входом БП2 12, k-параллельных выходов которого соединены с управляющими входами соответствующих ЧФ 14l-14k. Третий выход микропроцессора 10 соединен с третьим входом ПД 2, второй выход которого соединен с информационным входом ПИ 6.

Предлагаемое устройство работает следующим образом.

На передающем конце устройства входной сигнал поступает в ИИ 1, с выхода которого двоичная информационная последовательность поступает в ПД 2, где происходит ее деление на двоичные блоки по Z бит. Z бит двоичного блока составляют двоичное число X. С первого выхода ПД 2 информационные блоки подаются на первый вход микропроцессора 10, в котором производятся следующие преобразования: двоичное Х пересчитывается в десятичное число Y∈[0, 2X-1], которое в свою очередь переводится в другие десятичные числа:

N1=f1(Y)∈[0,2X-1],

N2=f2(Y)∈[0,2X-1],

где f1 и f2 - известные на приеме и передаче алгоритмы.

При этом N1 и N2 определяют десятичные числа:

MПСП=g(N1)∈[0,2M<1], М>X,

Fппрч=h(N2)∈[0,2K-1], K>Х,

где g и h - известные на приеме и передаче алгоритмы, отличные от f1 и f2.

По MПСП в БП1 8 определяется код ПСП, а по FППРЧ в БП2 12 определяется несущая частота. Определенный в БП1 8 код ПСП (L бит) с первого последовательного выхода БП1 8 подается в ГК 9, где он генерируется, а затем поступает на информационный вход модулятора 3, где он модулируется частотой, синтезируемой СЧ 7 на основе определенной в БП2 12 несущей частоты передатчика. Модулированная ПСП излучается в пространство с помощью АФБ1 4.

На приемном конце устройства входной сигнал, принятый АФБ2 15, поступает на информационные входы ЧФ 14l-14k, где происходит выбор того частотного канала, по которому производилась передача. Каждый из ЧФ 14l-14k настроен на частоту (Fппрч), значение которой хранится в БП2 12. При этом коды с k-параллельных выходов БП2 12 подаются на управляющие входы соответствующих из ЧФ 14l-14k, на синхронизирующие входы которых подается синхросигнал со второго выхода синхрогенератора 5.

С выходов ЧФ 14l-14k принятый сигнал поступает на соответствующие параллельные входы корреляторов 13l-13k, где определяются корреляционные пики. Каждый коррелятор 13l-13k настроен на определенную опорную ПСП, значение которой хранится в БП1 8. С k-параллельных выходов БП1 8 управляющие сигналы поступают на последовательные входы соответствующих корреляторов 13l-13k.

Значение пика АКФ на выходах корреляторов 13l-13k сравнивается с порогом в блоке 11. Номер коррелятора, имеющего максимальное значение АКФ, определяет вид ПСП, по которому в БП1 8 определяется NПСП, который со второго последовательного выхода БП1 8 подается на второй вход блока 10. В микропроцессоре 10 на основе десятичного числа NПСП сначала определяется десятичное число N=g-1(NПСП), а затем определяется десятичное число Y=f-1(N), которое переводится из десятичного вида в двоичный X, который подается на третий вход ПД 2, где преобразуется в Z бит двоичного блока. Полученные таким образом двоичные блоки объединяются в ПД 2 в двоичную информационную последовательность, которая со второго выхода ПД 2 подается на информационный вход ПИ 6, где преобразуется в форму выходного сигнала и подается на второй выход устройства.

При этом работа ПИ 6 синхронизируется сигналом со второго выхода синхрогенератора 5, а сигнал с первого выхода синхрогенератора 5 синхронизирует работу ИИ 1, ПД 2, ГК 9 и модулятора 3.

Использование в предлагаемом устройстве корреляторов позволяет поэлементно накапливать принятый сигнал ПСП (равный базе ПСП), что обеспечивает защиту от воздействия преднамеренных помех,

Использование блоков памяти позволяет идентифицировать код ПСП и рабочую частоту, а использование микропроцессора позволяет проводить многократные преобразования передаваемого и принимаемого сигналов, что обеспечивает защиту от несанкционированного доступа.

Таким образом, предлагаемое устройство отличается высокой помехоустойчивостью при соблюдении конфиденциальности.

Предлагаемое устройство по своей сути является полностью цифровым устройством, оно реализуется физически на базе элементов и блоков, широко известных из технической литературы, например, Алексеенко А.Г., Шакулин И.И. "Микросхемотехника" Учебное пособие для вузов. - 2-е изд., перераб. и доп. - Москва, "Радио и связь", 1990 г.

Применение цифровых элементов позволяет: упростить техническое исполнение устройства; значительно уменьшить габариты изделия, в котором оно будет использоваться, а также уменьшить его стоимость; повысить надежность в плане снижения влияния нестабильности параметров элементов схем и их паразитных параметров.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ СО СКАЧКООБРАЗНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2005 |

|

RU2290758C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2008 |

|

RU2356171C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ С ПСЕВДОСЛУЧАЙНЫМИ СИГНАЛАМИ | 2005 |

|

RU2284666C1 |

| СПОСОБ АДАПТИВНОЙ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2007 |

|

RU2356167C1 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ДИНАМИЧЕСКИ ИЗМЕНЯЕМОЙ ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2396713C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ЦИФРОВОЙ ИНФОРМАЦИИ | 2010 |

|

RU2436248C1 |

| РАДИОМОДЕМ | 2010 |

|

RU2439820C1 |

| СПОСОБ КОДОВРЕМЕННОГО РАЗДЕЛЕНИЯ КАНАЛОВ В ПОДВИЖНЫХ СИСТЕМАХ РАДИОСВЯЗИ | 1996 |

|

RU2123763C1 |

| СПОСОБ ЗАЩИТЫ ИНФОРМАЦИИ В РАДИОСЕТИ С ПАКЕТНОЙ ПЕРЕДАЧЕЙ ДАННЫХ | 2009 |

|

RU2425455C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ЦИФРОВОЙ ИНФОРМАЦИИ | 2008 |

|

RU2379842C1 |

Изобретение относится к области радиотехники и может найти применение в системах передачи информации со скачкообразной перестройкой рабочей частоты. Технический результат - повышение помехоустойчивости и обеспечение информационной и структурной скрытности передаваемого сообщения. Наличие в устройстве радиосвязи со скачкообразной перестройкой рабочей часоты корреляторов позволяет поэлементно накапливать принятый сигнал ПСП (равный базе ПСП), что обеспечивает защиту от воздействия преднамеренных помех, наличие блоков памяти позволяет идентифицировать код ПСП и рабочую частоту, а наличие микропроцессора позволяет проводить многократные преобразования передаваемого и принимаемого сигналов, что обеспечивает защиту от несанкционированного доступа. 2 ил.

Устройство радиосвязи со скачкообразной перестройкой рабочей частоты, содержащее последовательно соединенные источник информации, информационный вход которого является первым входом устройства, и пакетатор-депакетатор, последовательно соединенные модулятор и первый антенно-фидерный блок, выход которого является первым выходом устройства, второй антенно-фидерный блок, вход которого является вторым входом устройства, пороговый блок, синхрогенератор, синтезатор частоты и приемник информации, выход которого является вторым выходом устройства, причем второй выход пакетатора-депакетатора соединен с информационным входом приемника информации, выход синтезатора частот соединен с управляющим входом модулятора, отличающееся тем, что введены последовательно соединенные микропроцессор, первый блок памяти и генератор кода, выход которого соединен с информационным входом модулятора, а также второй блок памяти, k частотных фильтров и k корреляторов, при этом выход второго антенно-фидерного блока соединен с объединенными информационными входами k частотных фильтров, выходы которых соединены с объединенными соответствующими входами k корреляторов, объединенные выходы которых соединены с входом порогового блока, выход которого соединен со вторым входом первого блока памяти, при этом в пороговом блоке значения характеристик корреляторов сравниваются с порогом, причем номер коррелятора, имеющего максимальное значение автокорреляционной функции, определяет вид псевдослучайной последовательности (ПСП), в первом блоке памяти хранятся значения опорных ПСП, которые с k выходов поступают на соответствующие k входы корреляторов, при поступлении на первый вход первого блока памяти десятичного числа N по нему определяется код ПСП, который с первого выхода подается на генератор кода, а по сигналу, поступающему на второй вход первого блока памяти, в нем определяют номер ПСП N, который подается на второй вход микропроцессора, при этом во втором блоке памяти хранятся значения частот, которые с k выходов подаются на управляющие входы соответствующих частотных фильтров, а при поступлении на его вход десятичного числа F по нему определяется несущая частота, которая с первого выхода подается на вход синтезатора частот, при этом микропроцессор при поступлении на его первый вход информационного блока пересчитывает двоичное число в десятичное, которое переводится в другие десятичные числа, по одному из которых, формируемом на первом выходе, N определяют код ПСП, а по другому, формируемом на втором выходе, F - несущую частоту, при поступлении на второй вход микропроцессора десятичного числа N оно переводится из десятичного вида в двоичный и с третьего выхода поступает на третий вход пакетатора-депакетатора, при этом пакетатор-депакетатор производит деление двоичной информационной последовательности, поступающей с первого входа, на двоичные блоки по Z бит, которые с первого выхода поступают на первый вход микропроцессора, а при поступлении на третий вход пакетатора-депакетатора двоичного числа оно переводится в Z бит двоичных блоков, которые объединяются в двоичную информационную последовательность, которая со второго выхода подается на информационный вход приемника информации, кроме того, в источнике информации, модуляторе и получателе информации дополнительно введены синхронизирующие входы, а в синхрогенераторе дополнительно введен второй выход, причем первый выход синхрогенератора соединен с синхронизирующими входами источника информации, пакетатора-депакетатора, генератора кода и модулятора, а второй выход синхрогенератора соединен с синхронизирующим входом приемника информации, а также с объединенными синхронизирующими входами k коррелляторов и k частотных фильтров.

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2178237C2 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2210862C1 |

| US 6223048 В1, 24.04.2001 | |||

| US 5459760, 17.10.1995. | |||

Авторы

Даты

2007-12-20—Публикация

2005-05-03—Подача