Изобретение относится к радиотехнике, а именно к области линейного усиления амплитудно-модулированных сигналов, и может быть применено в системах линеаризации характеристик усилителей мощности.

Известны устройства ввода корректируемых и корректирующих сигналов, сигналов предыскажений, в которых коды корректирующих сигналов, сформированные системой линеаризации и занесенные в запоминающее устройство, адресно кодами измеренного уровня огибающей входного корректируемого сигнала считываются из запоминающего устройства, подвергаются цифроаналоговому преобразованию и отфильтрованным аналоговым сигналом поступают на модуляционный вход модулятора-корректора. Корректирующий сигнал на модуляционном входе модулятора-корректора запаздывает относительно корректируемого сигнала на сигнальном входе модулятора-корректора. Время запаздывания τз, определенное инерционностью тракта формирования корректирующего сигнала, включает в себя время задержки в цифровом детекторе, в запоминающем устройстве, в цифроаналоговом преобразователе и в фильтре подавления помех.

Запаздывание приводит к рассогласованию по значениям корректирующего и корректируемого сигналов на входах модулятора-корректора и, как следствие, к ошибкам коррекции нелинейных характеристик усилителя мощности. Совмещение по времени действия корректируемого сигнала с корректирующим в известных устройствах осуществляется с помощью линий задержки, включаемых на сигнальных входах модуляторов-корректоров, то есть задержкой корректируемого сигнала. В модуляторах-корректорах с корректируемыми сигналами в виде цифровых потоков, естественно, и линии задержки имеют решения на базе цифровых технологий. В модуляторах-корректорах с аналоговыми входными корректируемыми сигналами линии задержки аналоговые.

Наиболее близким к заявляемому устройству ввода и совмещения корректируемых и корректирующих сигналов является устройство по патенту US 6512417 «Linear amplifier arrangement» от 28.01.2003, МПК H01F 1/26. Данное устройство взято за прототип.

В устройстве-прототипе, как и в других известных аналогичных устройствах, совмещение корректируемого сигнала по амплитуде или фазе и соответствующих им корректирующих сигналов проводят задержкой корректируемого сигнала с помощью аналоговой линии задержки в цепи корректируемого сигнала.

Цепи управления режимами в устройстве-прототипе, в том числе передачи данных по цепи последовательно включенных цифрового детектора, запоминающего устройства и цифроаналогового преобразователя, соединены с источниками синхроимпульсов и тактовых импульсов, обеспечивающих работу устройства.

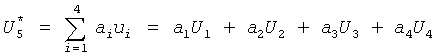

Ввиду однотипности устройств ввода и совмещения корректируемых сигналов и сигналов, корректирующих амплитуду и фазу, принцип работы прототипа рассматривается по обобщенной функциональной схеме, представленной на фиг.1.

В схеме прототипа на фиг.1 цепи управления режимами отображены как цепь синхропосылок-синхроимпульсов, стартовых для операций оцифровывания уровня огибающей и передачи данных на последующие элементы устройства.

В схеме на фиг.1 вход синхропосылок-стартовых импульсов, синхронизирующих обработку сигналов и передачу данных, обозначен как «СИ», сигнальный аналоговый вход устройства-прототипа как «Вх», выход как «Вых».

На фиг.1 устройство ввода и совмещения корректирующего и корректируемого сигналов содержит модулятор-корректор 2, сигнальный вход которого соединен с сигнальным входом «Вх» устройства ввода и совмещения корректирующего и корректируемого сигналов через линию задержки 1, а вход «Вх» устройства ввода и совмещения корректирующего и корректируемого сигналов соединен с модуляционным входом модулятора-корректора 2 через последовательно включенные цифровой детектор 3 огибающей корректируемого сигнала, запоминающее устройство 4, цифроаналоговый преобразователь 5, фильтр 6 подавления помех, при этом входы синхроимпульсов цифрового детектора 3, запоминающего устройства 4 и цифроаналогового преобразователя 5 соединены со входом «СИ» синхропосылок-синхроимпульсов от внешнего источника, функцию которого может выполнять или отдельный узел или микроконтроллер (микропроцессор) системы линеаризации характеристик усилителя.

Устройство на фиг.1 работает следующим образом. По синхроимпульсу со входа «СИ» как стартовому цифровым детектором 3 проводится измерение уровня огибающей корректируемого сигнала, оцифровывание, перевод в коды значения измеренного уровня огибающей и передача в запоминающее устройство 4 по адресной шине кода уровня огибающей как адреса ячейки запоминающего устройства 4, в которой хранится код уровня корректирующего сигнала, определенный и занесенный в память для величины измеренного уровня огибающей. По этому же синхроимпульсу, как стартовому, производится считывание из запоминающего устройства 4 кода уровня корректирующего сигнала в ввод его в цифроаналоговый преобразователь 5, с выхода которого аналоговый сигнал (ток, напряжение) через фильтр 6 подавления помех поступает на модуляционный вход модулятора-корректора 2.

Синхроимпульс является ключевым, разрешающим с помощью внутренних или внешних тактовых импульсов проводить обработку и передачу данных по последовательной цепи элементов устройства ввода и совмещения корректирующего и корректируемого сигналов. Как правило, частота следования синхроимпульсов соответствует частоте дискретизации огибающей. На формирование из входного сигнала устройства ввода и совмещения корректирующего и корректируемого сигналов корректирующего сигнала затрачивается время τз, состоящее из времени детектирования с преобразованием уровня огибающей в код, пересылку кода в запоминающее устройство 4, считывание из запоминающего устройства 4 кода корректирующего сигнала и загрузку кода в цифроаналоговый преобразователь 5, передачу, доведение корректирующего сигнала до модуляционного входа модулятора-корректора 2. Время τз является временем запаздывания, задержки корректирующего сигнала относительно сигнала на входе устройства ввода и совмещения корректирующего и корректируемого сигналов.

Для совмещения корректируемого сигнала с «запаздывающим» корректирующим в устройстве-прототипе между сигнальным входом модулятора-корректора 2 включена аналоговая линия задержки 1 с временем задержки, равным τз. Совмещение сигналов задержкой аналогового корректируемого сигнала с помощью аналоговой линии задержки эффективно в узкой полосе частот несущих и становится проблемным в широкодиапазонных и сверхширокодиапазонных трактах из-за трудностей сохранения характеристик линий задержек как по времени задержки, так и по амплитудно-частотным и частотно-фазовым характеристикам. То есть недостатком прототипа является сложность конструктивной реализации устройства ввода и совмещения корректирующего и корректируемого сигналов из-за громоздкости решений по широкодиапазонным линиям задержек.

Целью заявляемого изобретения является осуществление управляемого в широком диапазоне временных интервалов совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров методами цифровых технологий без применения аналоговых линий задержек.

Цель достигается введением в заявленное устройство ввода и совмещения корректируемых и корректирующих сигналов экстраполятора выходных данных цифрового детектора, обеспечивающего возможность определения величин корректируемого сигнала с упреждением с учетом времени задержки в тракте формирования корректирующего сигнала, разделением со сдвигом по времени синхроимпульсов, синхронизирующих обработку сигнала и передачу данных в тракте формирования корректирующих сигналов, с помощью введенного в заявленное устройство ввода и совмещения корректирующего и корректируемого сигналов звена задержки синхроимпульсов с управляемым внешним сигналом временем задержки синхроимпульсов.

Технический результат достигается тем, что устройство ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров, содержащее модулятор-корректор и последовательно соединенные запоминающее устройство, цифроаналоговый преобразователь, фильтр подавления помех, выход которого соединен с модуляционным входом модулятора-корректора, а также цифровой детектор огибающей корректируемого сигнала, вход которого соединен с сигнальным входом устройства ввода и совмещения корректируемых и корректирующих сигналов, а входы синхроимпульсов обработки и передачи данных цифрового детектора и запоминающего устройства соединены со входом синхропосылок от внешнего устройства, отличается тем, что с целью обеспечения управляемого в широком диапазоне временных интервалов совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров методами цифровых технологий без применения аналоговых линий задержек, сигнальный вход модулятора-корректора соединен с сигнальным выходом устройства ввода и совмещения корректируемых и корректирующих сигналов и в устройство ввода и совмещения корректируемых и корректирующих сигналов введены звено задержки синхроимпульсов с управляемым внешним сигналом временем задержки и экстраполятор, включенный по шине данных между Цифровым детектором и адресным входом запоминающего устройства, при этом вход синхроимпульсов экстраполятора соединен со входом синхропосылок устройства ввода и совмещения корректируемых и корректирующих сигналов непосредственно, а вход синхроимпульсов на ввод данных в цифроаналоговый преобразователь соединен со входом синхропосылок через звено задержки синхроимпульсов с управляемым внешним сигналом временем задержки.

Введенные элементы устройства выполняют следующие функции. Экстраполятор проводит вычисление (экстраполяция «вперед») значений уровня огибающей с опережением относительно последнего считывания с выхода цифрового детектора на определенный интервал времени; при расчете используются величины предшествующих уровней и последнего считанного уровня.

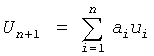

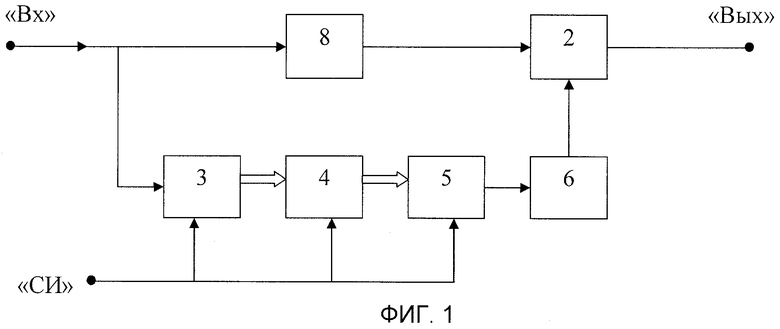

На фиг.2 условно показана огибающая Uвx(t) как функция времени t. В моменты времени ti…t1, t2, t3, t4 проводится считывание измеренных цифровым детектором уровней огибающей соответственно Ui…U1, U2, U3, U4. Используя n значений считанных уровней, включая последнее считанное значение в экстраполяторе, вычисляется значение уровня огибающей, ожидаемое на последующем отсчете. Вычисление проводится по формуле

где Un+1 - ожидаемый расчетный уровень огибающей при считывании первым тактом после n-го последнего считывания.

n - номер (условный) последнего отсчета;

i - 1, 2, 3…n - количество значений считанных уровней огибающей, используемых при вычислениях;

ai - весовой коэффициент.

На фиг.2 показан график для n=4, то есть вычисление значения U5 * проводится по четырем последовательно считанным значениям уровня огибающей в моменты времени t1, t2, t3, t4. Интервалы между моментами времени t1t2, t2t3, t3t4, t4t5 - есть интервалы дискретизации огибающей ΔT.

Звено задержки синхроимпульсов с управляемым внешним сигналом временем задержки осуществляет задержку импульсов (фронтов импульсов на заданное время задержки), то есть является цифровой линией задержки импульсов (регистры сдвига, счетчики, таймеры и т.д.).

По вычисленному значению уровня огибающей U5 * из запоминающего устройства считывается значение необходимого для уровня U5 * корректирующего сигнала и с упреждением по величине (значению) вводится в схему преобразования кодов корректирующего сигнала в корректирующий сигнал.

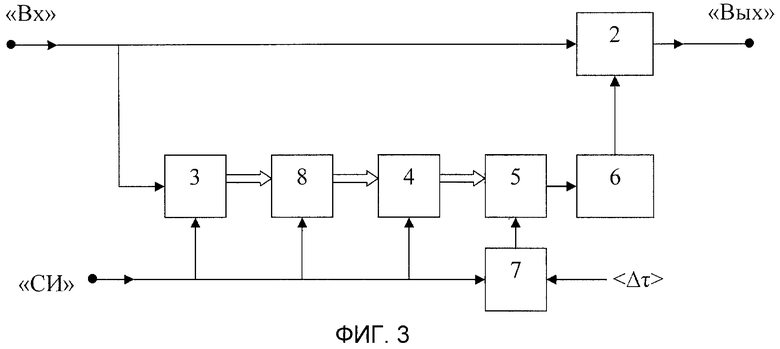

Функциональная схема заявленного устройства ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров представлена на фиг.3.

Устройство ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров, изображенное на фиг.3, содержит модулятор-корректор 2, вход которого соединен с сигнальным входом «Вх» устройства ввода и совмещения корректируемых и корректирующих сигналов непосредственно (без линий задержки), последовательно соединенные запоминающее устройство 4, цифроаналоговый преобразователь 5, фильтр 6 подавления помех, выход которого соединен с модуляционным входом модулятора-корректора 2, цифровой детектор 3 огибающей корректируемого сигнала, вход которого соединен с сигнальным входом «Вх», а входы синхроимпульсов обработки и передачи данных цифрового детектора 3 и запоминающего устройства 4 соединены со входом «СИ» синхропосылок от внешнего устройства, экстраполятор 8 выходных данных цифрового детектора 3, включенный между цифровым детектором 3 и адресным входом запоминающего устройства 4, звено 7 задержки синхроимпульсов с управляемым внешним сигналом временем задержки, при этом вход синхроимпульсов экстраполятора 8 соединен со входом «СИ» синхропосылок непосредственно, а входы синхроимпульсов цифроаналогового преобразователя 5 соединены со входом «СИ» синхропосылок через звено 7 задержки синхроимпульсов.

Введение в устройство экстраполятора 8 и звена 7 задержки синхроимпульсов с внешним управляемым временем задержки и разделение каналов подачи синхроимпульсов на элементы схемы позволяют осуществить совмещение корректируемого и корректирующего сигналов на входах модулятора-корректора 2 не задержкой по времени корректируемого сигнала, а формированием с учетом временных задержек в тракте корректирующего сигнала, упреждающего значение величины корректирующего сигнала, необходимой для коррекции уровня входного сигнала устройства ввода и совмещения корректируемых и корректирующих сигналов при их одновременном приходе на входы модулятора-корректора 2.

Заявленное устройство ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров работает следующим образом. Синхроимпульсом со входа «СИ» устройства ввода и совмещения корректируемых и корректирующих сигналов от внешнего источника синхропосылок цифровой детектор 3, экстраполятор 8 и запоминающее устройство 4 вводятся в режимы, обеспечивающие внутренними или внешними необходимыми тактовыми импульсами, пакетами импульсов, выполнение в определенной последовательности следующих операций: формирование выходных данных цифрового детектора 3, передачу данных с выхода цифрового детектора 3 в регистры экстраполятора 8, вычисление экстраполятором 8 ожидаемого, рассчитанного с упреждением по времени, значения уровня огибающей корректируемого входного сигнала, ввод в адресную шину запоминающего устройства 4 кода рассчитанного уровня огибающей, вывод на шину или в буферный выходной регистр запоминающего устройства 4 из ячейки кода уровня корректирующего сигнала, необходимого для коррекции входного сигнала с уровнем огибающей, равным рассчитанному. Таблица соответствия уровней корректирующих и корректируемых сигналов определенная при тестировании усилителя хранится в памяти в ячейках запоминающего устройства 4 в виде:

адрес ячейки - код уровня огибающей;

данные - код корректирующего сигнала.

Синхроимпульс, поступивший на входы синхроимпульсов цифрового детектора 3, экстраполятора 8, запоминающего устройства 4, одновременно поступает и на вход звена 7 задержки синхроимпульсов. Выходной импульс звена 7 задержки синхроимпульсов является стартовым синхроимпульсом для выполнения считывания с выхода запоминающего устройства 4 кода уровня корректирующего сигнала и ввода этого кода в цифроаналоговый преобразователь 5. Выходной импульс звена 7 задержки синхроимпульсов сдвинут (задержан) относительно основного, входного для звена 7 задержки синхроимпульсов на время Δτ, устанавливаемое внешним сигналом.

В заявленном устройстве ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров для тракта формирования корректирующего сигнала имеют место следующие временные соотношения по временам задержки:

τд - время задержки выходного сигнала цифрового детектора 3, время, затрачиваемое на формирование кодов измеренного уровня огибающей корректируемого сигнала;

τа - время формирования из кодового слова цифроаналоговым преобразователем 5 аналогового сигнала и задержка сигнала фильтром 6 подавления помех;

τцос - время цифровой обработки сигнала от входа экстраполятора 8 до выхода запоминающего устройства 4.

Инерционность цифрового детектора 3 τд приводит к тому, что выходные данные цифрового детектора 3, сформированные и считанные в момент времени ti, соответствуют уровню огибающей в момент реального времени ti-τд (фиг.4).

Следовательно, рассчитанное значение уровня огибающей в приводимом выше примере U5 * для момента считывания t5 будет значением уровня огибающей для времени t5-τд, это и есть время ввода корректирующего аналогового сигнала для уровня огибающей, имеющего место в момент времени t5-τд. Но с момента ввода кода в цифроаналоговый преобразователь 5 аналоговый сигнал достигает модуляционного входа модулятора-корректора 2 через время, равное τа, следовательно, ввод кода корректирующего сигнала в цифроаналоговый преобразователь 5 должен быть выполнен с упреждением на τа относительно реального времени t5-τд. То есть в момент времени t5-τд-τa или относительно последнего отсчета t4+ΔТ-τд-τа (ΔT - интервалы дискретизации огибающей, интервалы прихода синхроимпульсов). Синхроимпульс на ввод кода в цифроаналоговый преобразователь 5 должен быть подан в момент времени t4+ΔТ-τд-τа, то есть с задержкой относительно времени t4 последнего считывания на величину ΔТ-τд-τа, что соответствует опережению будущего последующего момента считывания t5 на время τд+τа.

Время задержки, равное ΔТ-τд-τа, обеспечивается установкой времени задержки в звене 7 задержки синхроимпульсов.

Время τцос цифровой обработки сигнала должно быть меньше времени задержки ΔТ-τд-τа, так как в момент ввода данных (кодов) корректирующего сигнала в цифроаналоговый преобразователь 5 эти данные должны быть сформированы и иметь место на выходе запоминающего устройства 4.

Заявленное устройство ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров имеет следующие качества:

- совмещение корректируемых и корректирующих сигналов на входах модуляторов-корректоров управляемо благодаря введению звена 7 задержки синхроимпульсов с управляемым внешним сигналом временем задержки;

- в устройстве ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров отсутствует аналоговая линия задержки, проблематичная для широкодиапазонных устройств, что повышает технологичность заявленного устройства применением элементной базы цифровой техники.

Реализация введенных в заявленное устройство ввода и совмещения корректируемого и корректирующего сигналов экстраполятора и звена задержки синхроимпульсов с управляемым внешним сигналом временем задержки на базе современной скоростной элементной базы цифровой техники типа ПЛИС не представляет сложностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛОВ ОШИБОК В УСТРОЙСТВАХ ЛИНЕАРИЗАЦИИ ХАРАКТЕРИСТИК УСИЛИТЕЛЕЙ | 2009 |

|

RU2423777C1 |

| СИСТЕМА РАДИОСВЯЗИ | 2005 |

|

RU2296428C1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ ТЕЛЕВИЗИОННОГО СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2046546C1 |

| Устройство автоматической коррекции координатных искажений телевизионного изображения | 1981 |

|

SU1012456A1 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| Радиопередающее устройство с цифровой коррекцией нелинейности | 2019 |

|

RU2731135C1 |

| Устройство для формирования корректирующего сигнала телевизионного датчика | 1982 |

|

SU1125772A1 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2008 |

|

RU2383103C1 |

| Имитатор гидроакустических сигналов | 1978 |

|

SU765865A1 |

| Телевизионная система для передачи изображений нескольких объектов | 1986 |

|

SU1343563A1 |

Устройство ввода и совмещения корректирующих и корректируемых сигналов на входах модуляторов-корректоров относится к радиотехнике, к области линейного усиления амплитудно-модулированных сигналов и может быть применено в системах линеаризации характеристик усилителей мощности. Технический результат: обеспечение управляемого в широком диапазоне временных интервалов совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров методами цифровых технологий без применения аналоговых линий задержек. Устройство содержит модулятор-корректор (2) и последовательно соединенные запоминающее устройство (ЗУ) (4), цифроаналоговый преобразователь (ЦАП) (5), фильтр подавления помех (6), выход которого соединен с модуляционным входом модулятора-корректора (2), а также цифровой детектор (ЦД) (3) огибающей корректируемого сигнала, вход которого соединен с сигнальным входом устройства, а входы синхроимпульсов обработки и передачи данных ЦД (3) и ЗУ (4) соединены со входом синхропосылок от внешнего устройства. Устройство отличается тем, что сигнальный вход модулятора-корректора (2) соединен с сигнальным входом устройства, а также введены звено задержки (7) синхроимпульсов с управляемым внешним сигналом временем задержки и экстраполятор (8), включенный по шине данных между ЦД (3) и адресным входом ЗУ (4), при этом вход синхроимпульсов экстраполятора (8) соединен со входом синхропосылок устройства непосредственно, а вход синхроимпульсов на ввод данных в ЦАП (5) соединен со входом синхропосылок через звено задержки (7) синхроимпульсов с управляемым внешним сигналом временем задержки. 4 ил.

Устройство ввода и совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров, содержащее модулятор-корректор и последовательно соединенные запоминающее устройство, цифроаналоговый преобразователь, фильтр подавления помех, выход которого соединен с модуляционным входом модулятора-корректора, а также цифровой детектор огибающей корректируемого сигнала, вход которого соединен с сигнальным входом устройства ввода и совмещения корректируемых и корректирующих сигналов, а входы синхроимпульсов обработки и передачи данных цифрового детектора и запоминающего устройства соединены со входом синхропосылок от внешнего устройства, отличающееся тем, что, с целью обеспечения управляемого в широком диапазоне временных интервалов совмещения корректируемых и корректирующих сигналов на входах модуляторов-корректоров методами цифровых технологий без применения аналоговых линий задержек, сигнальный вход модулятора-корректора соединен с сигнальным входом устройства ввода и совмещения корректируемых и корректирующих сигналов, и в устройство ввода и совмещения корректируемых и корректирующих сигналов введены звено задержки синхроимпульсов с управляемым внешним сигналом временем задержки и экстраполятор, включенный по шине данных между цифровым детектором и адресным входом запоминающего устройства, при этом вход синхроимпульсов экстраполятора соединен со входом синхропосылок устройства ввода и совмещения корректируемых и корректирующих сигналов непосредственно, а вход синхроимпульсов на ввод данных в цифроаналоговый преобразователь соединен со входом синхропосылок через звено задержки синхроимпульсов с управляемым внешним сигналом временем задержки.

| US 6512417 В2, 28.01.2003 | |||

| Усилитель высокочастотного сигнала | 1987 |

|

SU1480092A1 |

| US 4879519 A, 07.11.1989 | |||

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

Авторы

Даты

2012-02-27—Публикация

2010-03-09—Подача