Область техники, к которой относится изобретение

Изобретение относится к дисплейному устройству с фотодатчиком, который имеет такой фотодетекторный элемент, как фотодиод или фототранзистор, и, в частности, относится к дисплейному устройству, включающему в себя фотодатчик в пиксельной области.

Уровень техники

Традиционно, предлагается дисплейное устройство с фотодатчиком, который, вследствие включения такого фотодетекторного элемента, как фотодиод, внутри пикселя, может определять яркость внешнего света и снимать изображение объекта, который приближается к дисплею. Такое дисплейное устройство с фотодатчиком предположительно должно использоваться в качестве дисплейного устройства с двусторонней связью или дисплейного устройства с функцией сенсорной панели.

В традиционном дисплейном устройстве с фотодатчиком, при использовании технологии производства полупроводниковых приборов для того, чтобы формировать известные составляющие элементы, такие как сигнальные линии, линии сканирования, TFT (тонкопленочные транзисторы) и пиксельные электроды на подложке активной матрицы, фотодиоды и т.п. формируются в то же время на подложке активной матрицы (например, см. PTL 1).

Фиг.25 показывает пример традиционного фотодатчика (например, см. PTL 2 и 3), сформированного на подложке активной матрицы. Традиционный фотодатчик, показанный на фиг.25, выполнен посредством фотодиода D1, конденсатора C2 и транзистора M2. Анод фотодиода D1 подключается к межсоединениям для подачи сигнала RS сброса. Катод фотодиода D1 подключается к одному из электродов конденсатора C2 и затвору транзистора M2. Сток транзистора M2 подключается к межсоединениям для подачи неизменяющегося постоянного напряжения Vsup. Следует отметить, что выходные данные SData схемы датчика фотодатчика выводятся из истока транзистора M2. Другой электрод конденсатора C2 подключается к межсоединениям для подачи сигнала RW считывания.

В этой конфигурации, выходные данные SData схемы датчика, которые соответствуют количеству света, принимаемому посредством фотодиода D1, могут получаться посредством подачи сигнала RS сброса и сигнала RW считывания в соответствии с надлежащим предварительно определенным распределением по времени. Далее приводится описание работы традиционного фотодатчика, показанного на фиг.25, со ссылкой на фиг.26. Следует отметить, что на фиг.26 низкий уровень (например, -4 В) сигнала RS сброса указывается как -Vb, а высокий уровень (например, 8 В) сигнала RW считывания указывается как Vrw. Также следует отметить, что высокий уровень сигнала RS сброса, как предполагается, составляет 0 В, а низкий уровень сигнала RW считывания, как предполагается, составляет 0 В.

Последовательность измерения фотодатчика, показанного на фиг.25, описывается ниже в трех частях, а именно (A) период считывания, (B) период сброса и (C) период измерения.

(A) Период считывания

Период считывания соответствует периоду, в который сигнал RW считывания имеет высокий уровень. В то время, когда сигнал RW считывания имеет высокий уровень, потенциал VINT запоминающего узла "повышается на выходе" через конденсатор C2. Следует отметить, что запоминающий узел является точкой соединения между конденсатором C2, катодом фотодиода D1 и затвором транзистора M2. В это время, при условии, что потенциал запоминающего узла непосредственно перед считыванием - это V0, емкость конденсатора C2 - это Cst, полная внутрисхемная емкость - это Ctotal, а амплитуда сигнала RW считывания - это Vrw, потенциал VINT запоминающего узла может получаться посредством нижеприведенного выражения:

VINT=Cst/Ctotal·Vrw+V0.

Затем, вследствие превышения посредством "повышенного" потенциала VINT порогового значения транзистора M2, транзистор M2 включается, и данные SData датчиков выводятся. В это время, при условии, что пороговое значение транзистора M2 - это Vth, значение тока источника тока постоянной величины - это I, и проводимость транзистора M2 - это β, потенциал Vout SData может получаться посредством нижеприведенного выражения:

Vout≈VINT-Vth-(2I/β)1/2.

(B) Период сброса

Вследствие повышения сигнала RS сброса до высокого уровня (0 В), прямой ток протекает к фотодиоду D1, и потенциал VINT запоминающего узла сбрасывается до 0 В.

(C) Период измерения

Период измерения начинается, когда сигнал сброса возвращен от высокого уровня к низкому уровню. Другими словами, после того как запоминающий узел сброшен в периоде сброса, как упомянуто выше, сигнал RS сброса падает до низкого уровня

(-Vb) и тем самым фотодиод D1 становится обратно смещенным. Затем, запоминающий узел изменяется на направление -Vb вследствие фототока, который находится в соответствии с количеством света, которое падает на фотодиод D1.

Вышеописанные (A) период считывания, (B) период сброса и (C) период измерения, как предполагается, составляют один цикл, и данные датчиков считываются из фотодатчика посредством многократного выполнения этого цикла.

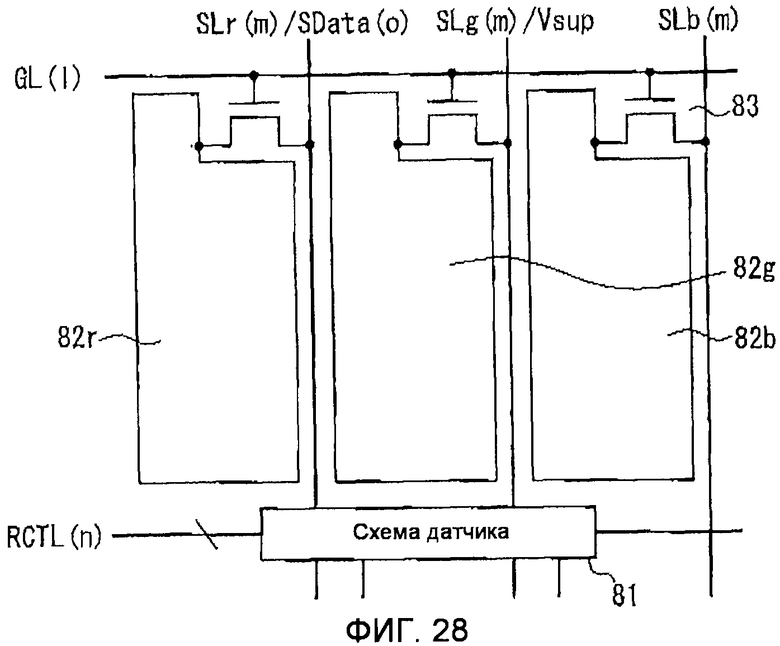

Фиг.27 показывает пример конфигурации фотодатчика внутри пикселя. В примерной конфигурации, показанной на фиг.27, одна схема 81 датчика предоставляется в каждом пикселе, выполненном посредством трех цветов элементов изображений, а именно красного (r), зеленого (g) и синего (b). Из составляющих элементов, показанных на фиг.25, схема 81 датчика соответствует фотодиоду D1, конденсатору C2 и транзистору M2. В примере на фиг.27, линии GL затвора и линии SL истока размещаются в матрице, и TFT 83 для возбуждения пиксельных электродов 82r, 82g и 82b элементов изображений размещаются в пересечениях между линиями GL затвора и линиями SL истока. Затворы TFT 83 подключаются к линиям GL затвора, их истоки подключаются к линиям SL истока, а стоки подключаются к пиксельным электродам 82r, 82g и 82b. Следует отметить, что в примере на фиг.27, три пиксельных электрода 82r, 82g и 82b составляют одну единицу и многократно располагаются вдоль направления строк.

Число линий GL затвора, предоставленных на подложке матрицы, составляет L. Другими словами, число пикселей на подложке матрицы в направлении строк составляет L. Линии GL затвора указываются как GL(l) (l - это натуральное число от 1 до L), когда имеется необходимость различать отдельные линии GL затвора. Линии SLr, SLg и SLb истока составляют один набор линий SL истока, и M наборов (т.е. 3M линий) предоставляются на подложке матрицы. Другими словами, число пикселей на подложке матрицы в направлении столбцов (горизонтальном направлении) составляет M, а число элементов изображений в направлении столбцов составляет 3M. В дальнейшем в этом документе, линии SL истока указываются как SLr(m), SLg(m) и SLb(m), когда имеется потребность различать отдельные линии SL истока. Здесь, m - это натуральное число от 1 до M.

Следует отметить, что N линий межсоединений для подачи вышеописанного сигнала RS сброса и сигнала RW считывания в схемы 81 датчиков предоставляются как группа RCTL линий управляющих сигналов для возбуждения схем 81 датчиков. Следует отметить, что предусмотрены случаи, когда N равно L, которое является числом линий GL затвора, и случаи, когда N меньше L. Например, в конфигурации, в которой схема 81 датчика предоставляется во всех пикселях в направлении строк (вертикальном направлении), N равно L, а в примере, в котором схема 81 датчика предоставляется в каждом втором пикселе в направлении строк, N равно L/2.

Кроме того, в примере на фиг.27, линия Vsup питания, которая предоставляет питание в схему 81 датчика, предоставляется между линиями SLg(m) и SLb(m) истока. Кроме того, выходные межсоединения SData для вывода данных из схемы 81 датчика предоставляются между линиями SLr(m) и SLg(m) истока.

Также возможна конфигурация, в которой, как показано на фиг.28, любая из линий SL истока (в примере на фиг.28, SLr(m) и SLg(m)) также выступает в качестве линии Vsup питания и выходных межсоединений SData. В этой конфигурации, хотя имеется ограничение с точки зрения синхронизации в том, что возбуждение датчика должно выполняться в период, в который линии SL истока не используются при операции отображения видео (например, в период гашения), имеется преимущество наличия высокой пиксельной светосилы, поскольку число линий межсоединений сокращается. В частности, в конфигурации, показанной на фиг.28, видеосигнал применяется к линиям SL истока в то время, когда операция отображения видео выполняется. С другой стороны, в ходе возбуждения датчика (например, периода гашения) переключатель переключается, чтобы инструктировать подачу неизменяющегося постоянного напряжения из источника питания в линию SLg(m) истока, тем самым инструктируя этой линии истока выступать в качестве линии Vsup питания. Аналогично, переключатель переключается, чтобы инструктировать вывод выходных данных схемы датчика из схемы 81 датчика в линию SLr(m) истока. Соответственно, эта линия истока выступает в качестве выходных межсоединений SData в ходе возбуждения датчика.

Список библиографических ссылок

Патентные документы

PTL 1: JP 2006-3857A.

PTL 2: WO 2007/145346.

PTL 3: WO 2007/145347.

Сущность изобретения

В вышеописанной традиционной схеме 81 датчика, как показано на фиг.25, паразитные емкости Cps и Cpd, соответственно, существуют между запоминающим узлом (точкой соединения между катодом фотодиода и конденсатором) и линией Vsup питания, которая предоставляет питание в схему 81 датчика, и между запоминающим узлом и выходными межсоединениями SData. По этой причине, если потенциал таких межсоединений колеблется между временем, когда схема 81 датчика сбрасывается, и временем, когда данные считываются, разность в потенциале распространяется в запоминающий узел через паразитные емкости и заставляет потенциал VINT запоминающего узла колебаться. Это приводит к такой проблеме, что в выводе из схемы 81 датчика появляется шум смещения.

Далее приводится конкретное описание случая, в котором шум смещения появляется в выводе из схемы 81 датчика, со ссылкой на фиг.29 и 30.

Фиг.29 является эквивалентной принципиальной схемой, показывающей конфигурацию, в которой линия Vsup питания и выходные межсоединения SData предоставляются независимо от линий SL истока, как показано на фиг.27, причем показаны только схема 81 датчика и группы межсоединений, обязательные для возбуждения схемы 81 датчика. Как показано на фиг.29, в этой конфигурации, линия Vsup питания и выходные межсоединения SData совместно используются посредством всех схем 81 датчиков, выстроенных в одном столбце.

Даже если транзистор M2 (см. фиг.25) в схеме 81 датчика находится в отключенном состоянии, паразитные емкости (Cps и Cpd) существуют между затвором и истоком транзистора M2 и между затвором и стоком транзистора M2. Кроме того, в зависимости от размещения имеется вероятность наличия емкости связи и интерференционной емкости между запоминающим узлом и выходными межсоединениями SData и между запоминающим узлом и линией Vsup питания. Здесь, Ctotal - это полная емкость, включающая в себя паразитные емкости, подключенные к запоминающему узлу, электрический шум, Noise_SD, который выходные межсоединения SData формируют в запоминающем узле, выражается посредством нижеприведенного выражения. Следует отметить, что V_SData, показанный ниже, указывает колебание в потенциале выходных межсоединений SData.

Noise_SD=Cps/Ctotal·V_SData... (1)

В конфигурации, показанной на фиг.29, в случае если сброс, измерение и считывание выполняются многократно, даже если количество света, которое падает на фотодиод D1, является постоянным, выходные данные схемы датчика, которые считываются на выходные межсоединения SData, колеблются, как показано на фиг.30, вследствие влияния посредством потенциала выходных межсоединений SData непосредственно перед сигналом RW считывания и сигналом RS сброса (Vs1, Vw2, Vs2, ..., показанные на фиг.30). Следует отметить, что потенциал Vs1, Vw2, Vs2, ... выходных межсоединений SData зависит от потенциала непосредственно предыдущих выходных данных схемы датчика.

Следует отметить, что во временной диаграмме, показанной на фиг.30, синхронизация, согласно которой сигнал RW считывания и сигнал RS сброса подаются в одну схему 81 датчика, как предполагается, является постоянной в вертикальных периодах. Соответственно, период от момента после заднего фронта импульса 1 сигнала RS сброса до момента, когда импульс 2 сигнала RW считывания применен в следующем вертикальном периоде, соответствует периоду измерения схемы 81 датчика, в которой применяются этот сигнал RS сброса и этот сигнал RW считывания.

Здесь, даже если количество света, которое падает на фотодиод D1 в соответствующих периодах измерения, является одинаковым между выходными данными схемы датчика, считываемыми вследствие импульса 2 сигнала RW считывания на фиг.30, и выходными данными схемы датчика, считываемыми вследствие импульса 3 сигнала RW считывания, нижеприведенное смещение Voff2-3 возникает вследствие паразитных емкостей. Это выражение извлекается из вышеописанного выражения (1):

Voff2-3=Cps/Ctotal·{(Vs1-Vw2)-(Vs2-Vw3)}.

Кроме того, даже если количество света, которое падает на фотодиод D1 в соответствующих периодах измерения, является одинаковым между выходными данными схемы датчика, считываемыми вследствие импульса 3 сигнала RW считывания, и выходными данными схемы датчика, считываемыми вследствие импульса 4 сигнала RW считывания, нижеприведенное смещение Voff3-4 возникает вследствие паразитных емкостей:

Voff3-4=Cps/Ctotal·{(Vs2-Vw3)-(Vs3-Vw4)}.

Как упомянуто выше, потенциал Vs1, Vw2, Vs2, ... выходных межсоединений SData зависит от потенциала непосредственно предыдущих выходных данных схемы датчика (т.е. выходных данных из схемы датчика в предыдущей строке этого столбца). Соответственно, смещение Voff2-3 и смещение Voff3-4 не обязательно являются постоянными. Как описано выше, даже если количество света, которое падает на фотодиод D1, является постоянным, выходные данные схемы датчика имеют смещение, возникающее из колебания в потенциале выходных межсоединений SData непосредственно перед сигналом RW считывания и сигналом RS сброса. Кроме того, как упомянуто выше, смещение не является постоянным и, следовательно, не может просто исключаться.

В конфигурации, в которой некоторые из линий SL истока также выступают в качестве линии Vsup питания и выходных межсоединений SData, как показано на фиг.28, смещение, возникающее из колебания в потенциале выходных межсоединений SData, а также смещение, возникающее из колебания в потенциале линии Vsup питания, накладываются на выходные данные схемы датчика. В потенциале линии Vsup питания в конфигурации, показанной на фиг.27 и 30, отсутствует колебание, при этом в конфигурации, показанной на фиг.28, линия Vsup питания также выступает в качестве линий SL истока, и, следовательно, потенциал колеблется вследствие применения видеосигнала в периоде отображения изображений.

В свете вышеописанных проблем, цель настоящего изобретения состоит в том, чтобы предоставлять дисплейное устройство с фотодатчиком, который может получать очень точные выходные данные схемы датчика посредством разрешения проблемы смещения в запоминающем узле, возникающего из паразитной емкости.

Чтобы разрешать вышеописанную проблему, дисплейное устройство согласно настоящему изобретению является дисплейным устройством, включающим в себя фотодатчик в пиксельной области подложки активной матрицы, причем фотодатчик включает в себя: фотодетекторный элемент, который принимает падающий свет; запоминающий узел, который подключается к фотодетекторному элементу, причем потенциал запоминающего узла изменяется в соответствии с выходным током из фотодетекторного элемента; межсоединения сигнала сброса, которые подают сигнал сброса в фотодатчик; межсоединения сигнала считывания, которые подают сигнал считывания в фотодатчик; и переключающий элемент датчика для считывания потенциала запоминающего узла на выходные межсоединения в качестве вывода схемы датчика, причем потенциал запоминающего узла изменяется в соответствии с количеством света, принимаемым посредством фотодетекторного элемента в периоде измерения, причем период измерения длится от момента, когда сигнал сброса подается, до момента, когда сигнал считывания подается, при этом потенциал межсоединений, имеющих паразитную емкость с запоминающим узлом, фиксируется равным предварительно определенному потенциалу, по меньшей мере, в одном из момента непосредственно перед сигналом считывания и непосредственно перед сигналом сброса.

Настоящее изобретение дает возможность предоставления дисплейного устройства с фотодатчиком, который может получать очень точные выходные данные схемы датчика посредством разрешения проблемы смещения в запоминающем узле, возникающего из паразитной емкости.

Краткое описание чертежей

Фиг.1 является блок-схемой, показывающей схематичную конфигурацию дисплейного устройства согласно варианту осуществления настоящего изобретения.

Фиг.2 является эквивалентной принципиальной схемой, показывающей конфигурацию пикселя в дисплейном устройстве согласно варианту осуществления настоящего изобретения.

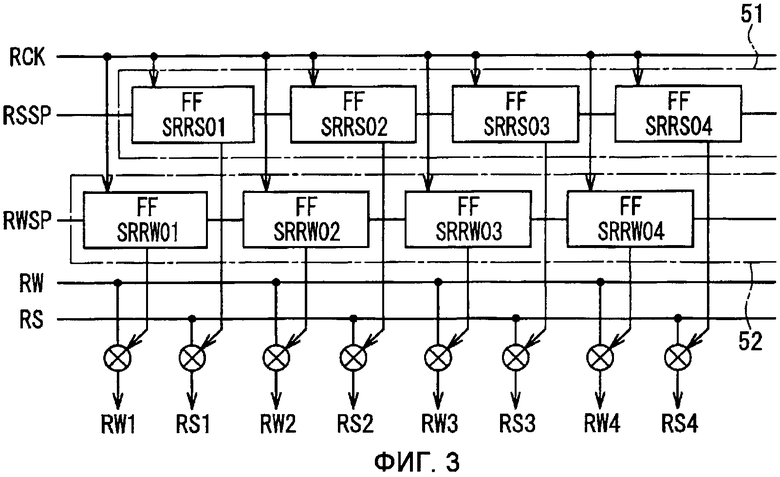

Фиг.3 является эквивалентной принципиальной схемой, показывающей пример конфигурации драйвера строк.

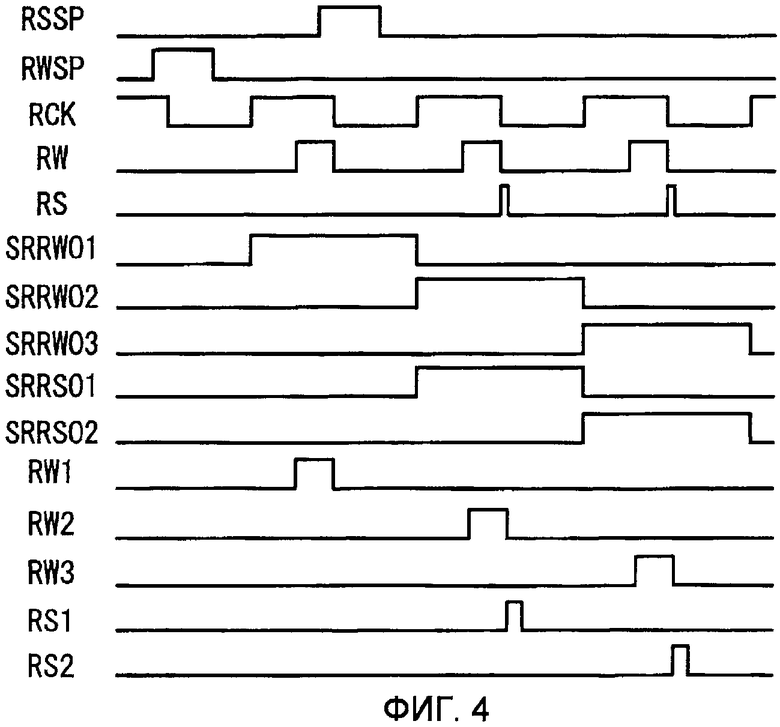

Фиг.4 является временной диаграммой, показывающей синхронизацию сигналов, связанных с возбуждением драйвера строк.

Фиг.5 является эквивалентной принципиальной схемой, показывающей пример конфигурации драйвера столбцов.

Фиг.6 является временной диаграммой, показывающей синхронизацию сигналов, связанных с возбуждением драйвера столбцов.

Фиг.7 является эквивалентной принципиальной схемой, показывающей пример конфигурации драйвера затвора.

Фиг.8 является временной диаграммой, показывающей синхронизацию сигналов, связанных с возбуждением драйвера затвора.

Фиг.9 является эквивалентной принципиальной схемой, показывающей пример конфигурации драйвера истока.

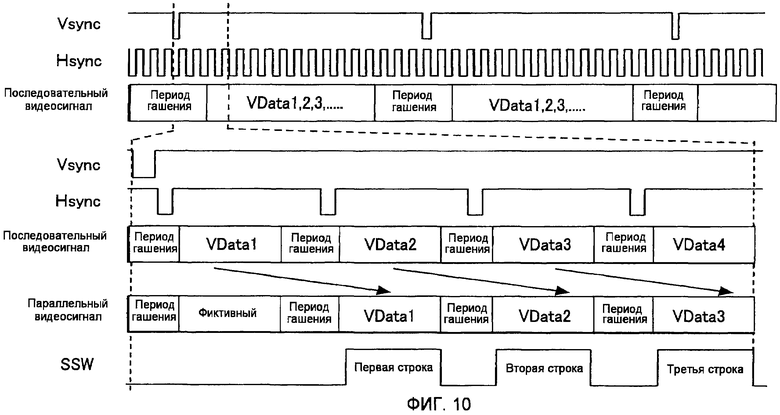

Фиг.10 является временной диаграммой, показывающей синхронизацию сигналов, связанных с возбуждением драйвера истока.

Фиг.11 является эквивалентной принципиальной схемой, показывающей пример конфигурации драйвера истока и драйвера столбцов.

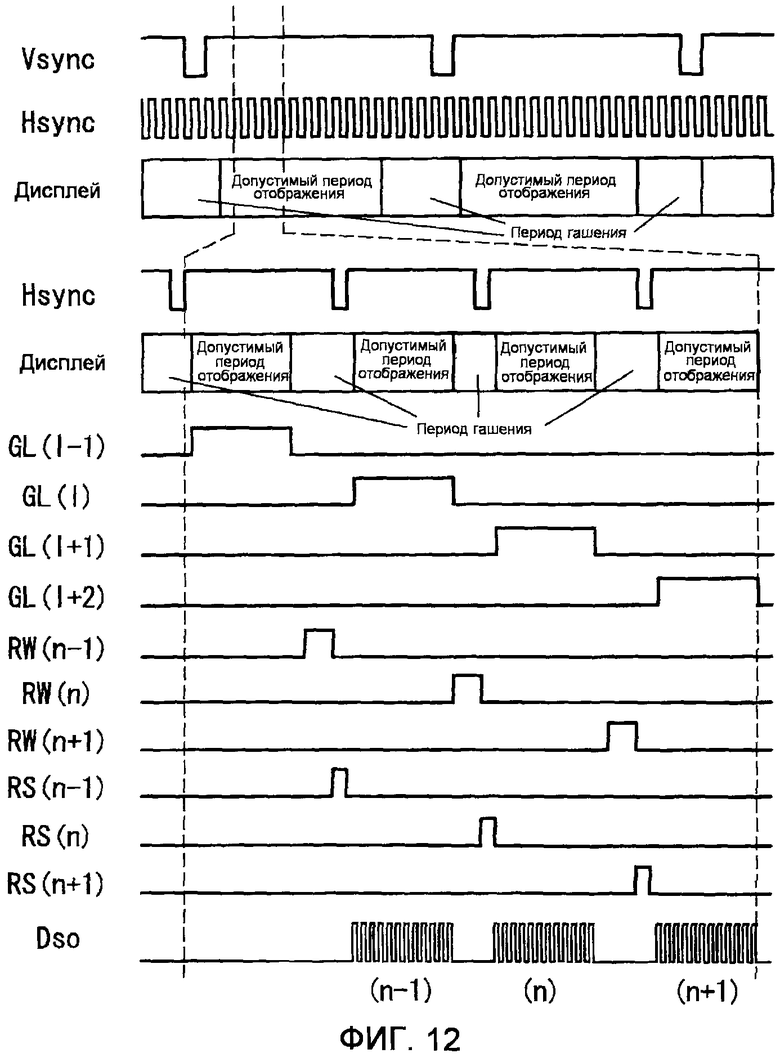

Фиг.12 является временной диаграммой, показывающей взаимосвязь между синхронизацией операции отображения и синхронизацией измерения.

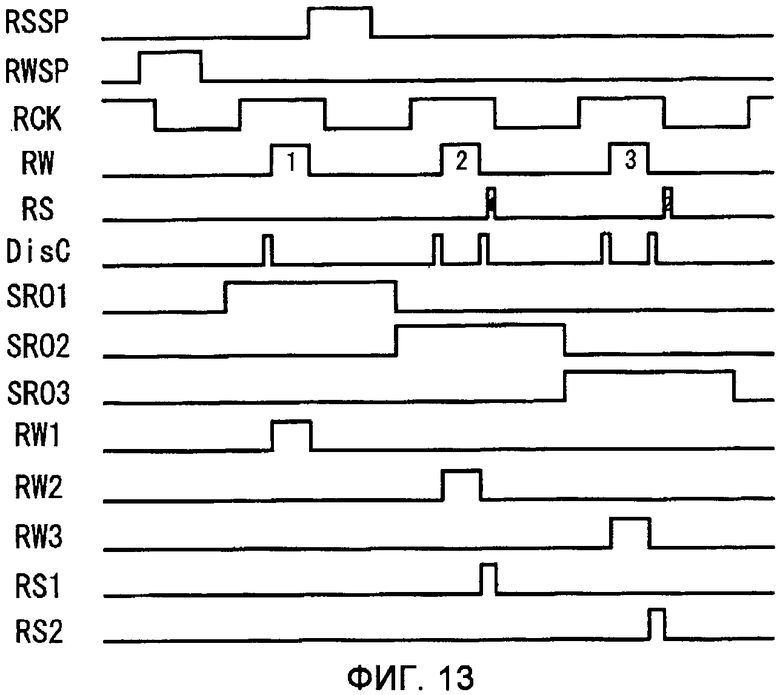

Фиг.13 является временной диаграммой, показывающей синхронизацию сигналов возбуждения датчика согласно варианту осуществления 1.

Фиг.14 является эквивалентной принципиальной схемой, показывающей конфигурацию драйвера столбцов согласно варианту осуществления 1.

Фиг.15 является временной диаграммой, показывающей взаимосвязь между сигналом считывания, сигналом сброса, сигналом разрядки и потенциалом межсоединений вывода данных.

Фиг.16 является эквивалентной принципиальной схемой, показывающей конфигурацию пикселя в дисплейном устройстве согласно варианту осуществления настоящего изобретения.

Фиг.17 является временной диаграммой, показывающей взаимосвязь между синхронизацией операции отображения и синхронизацией измерения.

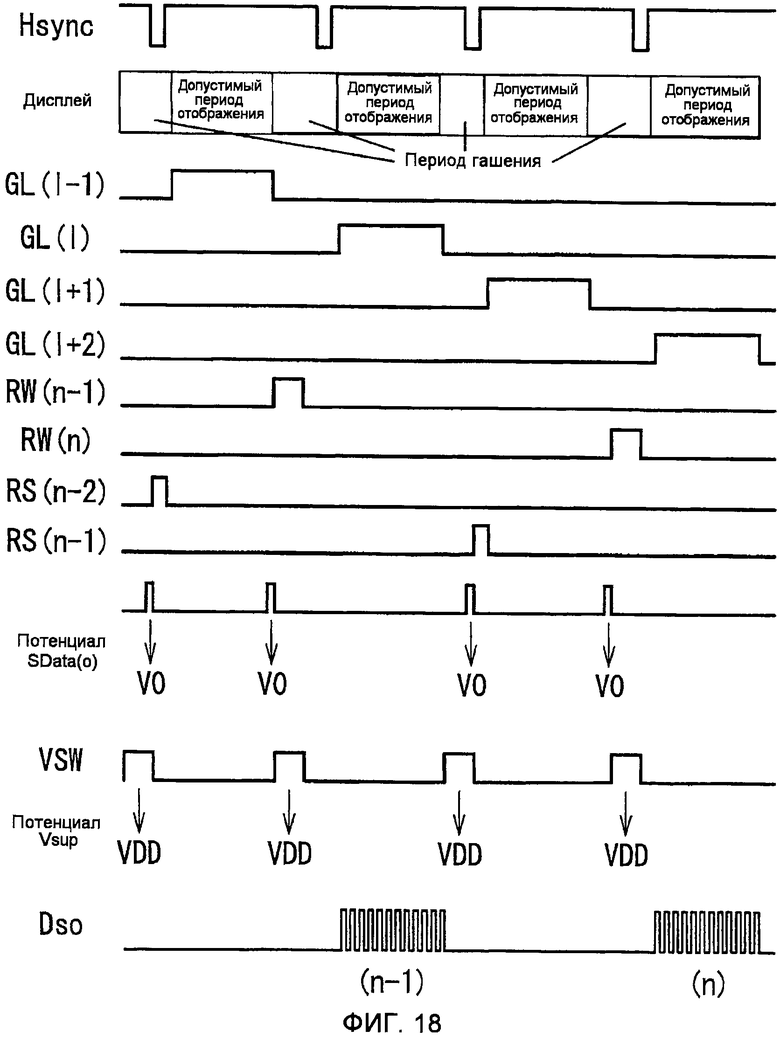

Фиг.18 является временной диаграммой, показывающей синхронизацию сигналов возбуждения датчика согласно варианту осуществления 2.

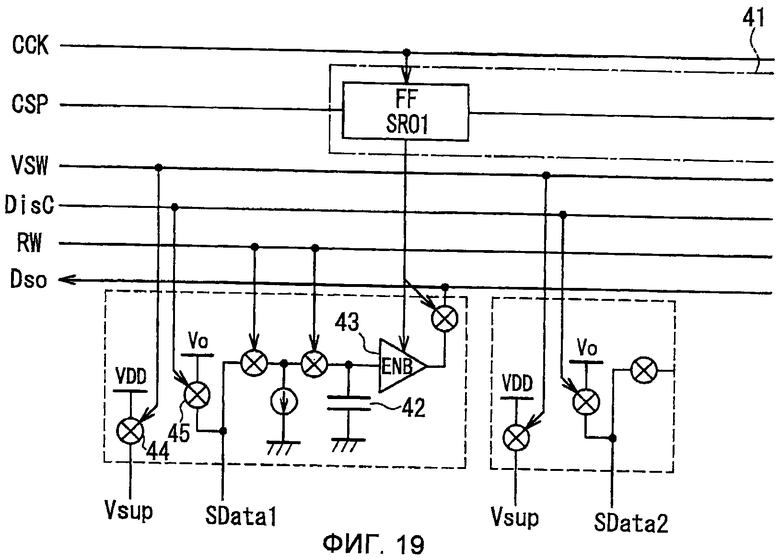

Фиг.19 является эквивалентной принципиальной схемой, показывающей конфигурацию драйвера столбцов согласно варианту осуществления 2.

Фиг.20 является временной диаграммой, показывающей синхронизацию сигналов возбуждения датчика согласно варианту осуществления 3.

Фиг.21 является эквивалентной принципиальной схемой, показывающей конфигурацию дифференциальной схемы усиления драйвера истока согласно варианту осуществления 3.

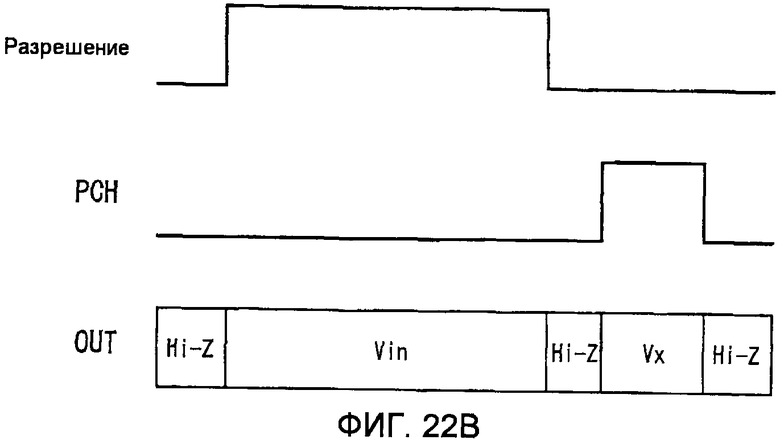

Фиг.22A является эквивалентной принципиальной схемой, показывающей конфигурацию дифференциальной схемы усиления драйвера истока согласно варианту осуществления 3, а фиг.22B является временной диаграммой, показывающей синхронизацию сигналов возбуждения схемы на фиг.22A.

Фиг.23 является временной диаграммой, показывающей синхронизацию сигналов возбуждения датчика согласно варианту осуществления 4.

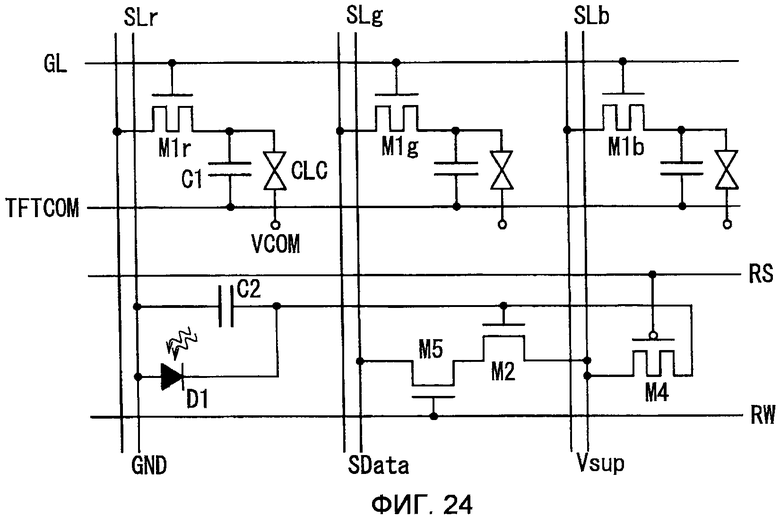

Фиг.24 является эквивалентной принципиальной схемой, показывающей другой вариант осуществления схемы датчика, к которой применимо настоящее изобретение.

Фиг.25 является эквивалентной принципиальной схемой, показывающей пример традиционного фотодатчика, сформированного на подложке активной матрицы.

Фиг.26 является временной диаграммой, показывающей формы сигналов возбуждения в традиционном фотодатчике.

Фиг.27 является иллюстративной схемой, показывающей пример межсоединений в традиционном фотодатчике.

Фиг.28 является иллюстративной схемой, показывающей другой пример межсоединений в традиционном фотодатчике.

Фиг.29 является эквивалентной принципиальной схемой, показывающей взаимосвязь соединений между схемой фотодатчика и периферийными межсоединениями.

Фиг.30 является временной диаграммой для описания случая, в котором потенциал межсоединений считывания данных колеблется непосредственно перед сигналом считывания и непосредственно перед сигналом сброса.

Описание изобретения

Дисплейное устройство согласно варианту осуществления настоящего изобретения является дисплейным устройством, включающим в себя фотодатчик в пиксельной области подложки активной матрицы, причем фотодатчик включает в себя: фотодетекторный элемент, который принимает падающий свет; запоминающий узел, который подключается к фотодетекторному элементу, причем потенциал запоминающего узла изменяется в соответствии с выходным током из фотодетекторного элемента; межсоединения сигнала сброса, которые подают сигнал сброса в фотодатчик; межсоединения сигнала считывания, которые подают сигнал считывания в фотодатчик; и переключающий элемент датчика для считывания потенциала запоминающего узла на выходные межсоединения в качестве вывода схемы датчика, причем потенциал запоминающего узла изменяется в соответствии с количеством света, принимаемым посредством фотодетекторного элемента в периоде измерения, причем период измерения длится от момента, когда сигнал сброса подается, до момента, когда сигнал считывания подается, при этом потенциал межсоединений, имеющих паразитную емкость с запоминающим узлом, фиксируется равным предварительно определенному потенциалу, по меньшей мере, в одном из момента непосредственно перед сигналом считывания и непосредственно перед сигналом сброса.

Согласно этой конфигурации, фиксация потенциала межсоединений, имеющих паразитную емкость с запоминающим узлом, равным предварительно определенному потенциалу, по меньшей мере, в одном из момента непосредственно перед сигналом считывания и непосредственно перед сигналом сброса дает возможность недопущения колебания потенциала запоминающего узла вследствие колебания в потенциале, возникающего из потенциала межсоединений непосредственно перед считыванием из фотодатчика и/или непосредственно перед сбросом. Это дает возможность предоставления дисплейного устройства с фотодатчиком, в котором разрешается смещение в запоминающем узле, возникающее из паразитной емкости, и могут получаться очень точные выходные данные схемы датчика.

Следует отметить, что предпочтительной является конфигурация, в которой межсоединения, имеющие паразитную емкость с запоминающим узлом, являются выходными межсоединениями. Потенциал выходных межсоединений колеблется в соответствии, например, с непосредственно предыдущими выходными данными схемы датчика и, в зависимости от схемной конфигурации, уровнем непосредственно предыдущего видеосигнала. Кроме того, величина колебания не может быть прогнозирована. Соответственно, фиксация потенциала этих межсоединений равным предварительно определенному потенциалу, по меньшей мере, непосредственно перед сигналом считывания или непосредственно перед сигналом сброса предоставляет разрешение смещения в запоминающем узле, возникающего из паразитной емкости. Кроме того, в этой конфигурации, предпочтительно, чтобы видеосигнал, имеющий предварительно определенный уровень, подавался в выходные межсоединения, чтобы фиксировать потенциал выходных межсоединений равным предварительно определенному потенциалу.

Кроме того, предпочтительной является конфигурация, в которой межсоединения, имеющие паразитную емкость с запоминающим узлом, являются межсоединениями питания, которые подают напряжение питания в фотодатчик в период, в который подается сигнал считывания, и межсоединения питания также выступают в качестве линии истока, которая подает видеосигнал в пиксель в пиксельной области. При этой конфигурации, потенциал межсоединений питания колеблется в соответствии с уровнем видеосигнала, подаваемого в пиксели. Кроме того, величина колебания не может быть прогнозирована. Соответственно, фиксация потенциала этих межсоединений питания равным предварительно определенному потенциалу, по меньшей мере, непосредственно перед сигналом считывания или непосредственно перед сигналом сброса предоставляет разрешение смещения в запоминающем узле, возникающего из паразитной емкости. Кроме того, в этой конфигурации, предпочтительно, чтобы фиксация потенциала межсоединений питания равным предварительно определенному потенциалу управлялась посредством сигнала, отличного от сигнала считывания.

Кроме того, предпочтительно, чтобы видеосигнал, имеющий предварительно определенный уровень, подавался в выходные межсоединения, чтобы фиксировать потенциал выходных межсоединений равным первому предварительно определенному потенциалу непосредственно перед сигналом считывания, и напряжение, имеющее предварительно определенный уровень, подавалось в выходные межсоединения, чтобы фиксировать потенциал выходных межсоединений равным второму предварительно определенному потенциалу непосредственно перед сигналом сброса.

Кроме того, дисплейное устройство настоящего изобретения может быть предпочтительно реализовано как жидкокристаллическое дисплейное устройство, дополнительно включающее в себя общую подложку, располагающуюся напротив подложки активной матрицы, и жидкий кристалл, размещаемый между подложкой активной матрицы и общей подложкой.

Ниже приводится описание более конкретных вариантов осуществления настоящего изобретения со ссылкой на чертежи. Следует отметить, что хотя следующие варианты осуществления показывают примеры конфигураций, в которых дисплейное устройство согласно настоящему изобретению реализовано как жидкокристаллическое дисплейное устройство, дисплейное устройство согласно настоящему изобретению не ограничено жидкокристаллическим дисплейным устройством и применимо к произвольному дисплейному устройству, которое использует подложку активной матрицы. Также следует отметить, что вследствие наличия фотодатчика, дисплейное устройство согласно настоящему изобретению предположительно должно использоваться, например, в качестве дисплейного устройства с сенсорной панелью, которое выполняет операции ввода посредством обнаружения объекта, который приближается к экрану, или дисплейного устройства с двусторонней связью, которое имеет функцию отображения и функцию захвата изображений.

Кроме того, для удобства в описании, чертежи, на которые ссылаются ниже, показывают упрощения, из составляющих элементов вариантов осуществления настоящего изобретения, только релевантных элементов, которые являются обязательными для описания настоящего изобретения. Соответственно, дисплейное устройство согласно настоящему изобретению может включать в себя произвольные составляющие элементы, которые не показаны на чертежах, на которые ссылаются в этом описании. Кроме того, что касается размеров элементов на чертежах, размеры фактических составляющих элементов, соотношения размеров элементов и т.п. не показаны точно.

Первый вариант осуществления

Сначала приводится описание конфигурации подложки активной матрицы, включенной в жидкокристаллическое дисплейное устройство согласно варианту осуществления 1 настоящего изобретения, со ссылкой на фиг.1 и 2.

Фиг.1 является блок-схемой, показывающей схематичную конфигурацию подложки 100 активной матрицы, включенной в жидкокристаллическое дисплейное устройство согласно варианту осуществления настоящего изобретения. Как показано на фиг.1, подложка 100 активной матрицы включает в себя, по меньшей мере, пиксельную область 1, драйвер 2 затвора, драйвер 3 истока, драйвер 4 столбцов и драйвер 5 строк на стеклянной подложке. Следует отметить, что хотя не показано на фиг.1, схема обработки сигналов для обработки сигналов изображений, снимаемых посредством фотодетекторных элементов (описаны ниже) в пиксельной области 1, подключается к подложке 100 активной матрицы через FPC 6.

В соответствии с сигналами синхронизации (Vsync и Hsync), которые введены извне, драйвер 2 затвора и драйвер 3 истока выполняют сканирование на предмет записи видеосигнала, который аналогично введен снаружи, чтобы отображать пиксели в пиксельной области 1. С другой стороны, драйвер 4 столбцов и драйвер 5 строк являются драйверами для подачи различных типов сигналов, обязательных для возбуждения датчика (нижеописанного сигнала считывания, сигнала сброса и т.п.), в фотодатчики в пиксельной области 1 и последовательного вывода выходных данных схемы датчика, которые считаны, за пределы дисплейного устройства.

Следует отметить, что компоновка различных типов драйверов, показанных на фиг.1, является просто примером, и то, как различные типы драйверов монтируются, зависит от выбранной конструкции. Кроме того, вышеописанные составляющие элементы на подложке 100 активной матрицы могут формироваться монолитно на стеклянной подложке посредством технологии производства полупроводниковых приборов. Альтернативно, возможна конфигурация, в которой усилитель и различные драйверы из вышеописанных составляющих элементов монтируются на стеклянной подложке посредством технологии COG (для монтажа на стеклянную подложку) и т.п. В качестве другой альтернативы, можно монтировать, по меньшей мере, некоторые из вышеописанных составляющих элементов, показанных на подложке 100 активной матрицы на фиг.1, на FPC. Подложка 100 активной матрицы присоединена к общей подложке (не показана), которая имеет общий электрод, сформированный на всей лицевой поверхности, и жидкокристаллический материал помещается в зазоре между ними.

Пиксельная область 1 является областью, в которой множество пикселей формируются, чтобы отображать изображение. В настоящем варианте осуществления, фотодатчик (схема 81 датчика) для снятия изображения предоставляется в каждом пикселе в пиксельной области 1. Фиг.2 является эквивалентной принципиальной схемой, показывающей компоновку пикселя и схемы 81 датчика в пиксельной области 1. В примере на фиг.2, каждый пиксель формируется посредством трех цветов элементов изображений, а именно R (красного), G (зеленого) и B (синего), и одна схема 81 датчика, выполненная посредством фотодиода D1, конденсатора C2 и тонкопленочного транзистора M2, предоставляется в каждом из пикселей, выполненных посредством этих трех элементов изображений. В частности, при конфигурации настоящего варианта осуществления, пиксельная область 1 имеет пиксели, размещенные в матрице, имеющей L строк × M столбцов, и схемы 81 датчиков, размещенные в матрице, имеющей N строк × О столбцов. Следует отметить, что в настоящем варианте осуществления, число линий GL затвора в направлении строк (L) эквивалентно числу схем 81 датчиков в направлении строк (N) и число пикселей в направлении столбцов (M) эквивалентно числу схем 81 датчиков в направлении столбцов (O). Общее число элементов изображений в пиксельной области 1 равно L×3M.

Как показано на фиг.2, пиксельная область 1 имеет, в качестве межсоединений для пикселей, линии GL затвора и линии SL истока, которые размещаются в матрице. Линии GL затвора подключаются к драйверу 2 затвора. Линии SL истока подключаются к драйверу 3 истока. Следует отметить, что L линий GL затвора предоставляются в пиксельной области 1. В дальнейшем в этом документе, линии GL затвора указываются как GL(l), когда имеется необходимость различать отдельные линии GL затвора в описании. Здесь, l - это натуральное число от 1 до L. С другой стороны, три из линий SL истока предоставляются в каждом пикселе, чтобы подавать данные изображений в три элемента изображений в каждом пикселе, как упомянуто выше. Линии SL истока указываются как SLr(m), SLg(m) и SLb(m), когда имеется необходимость различать отдельные линии SL истока в описании. Здесь, m - это натуральное число от 1 до M.

Тонкопленочные транзисторы (TFT) M1 предоставляются как переключающие элементы для пикселей на пересечениях между линиями GL затвора и линиями SL истока. Следует отметить, что на фиг.2, тонкопленочные транзисторы M1, предоставленные в красном, зеленом и синем элементах изображений, помечены как M1r, M1g и M1b, соответственно. В каждом тонкопленочном транзисторе M1, электрод затвора подключается к одной из линий GL затвора, электрод истока подключается к одной из линий SL истока, а электрод стока подключается к пиксельному электроду, который не показан. Соответственно, как показано на фиг.2, жидкокристаллический конденсатор CLC формируется между электродом стока каждого тонкопленочного транзистора M1 и общим электродом (VCOM). Кроме того, вспомогательный конденсатор C1 формируется между каждым электродом стока и TFTCOM.

На фиг.2, элемент изображения, возбуждаемый посредством тонкопленочного транзистора M1r, который подключается к пересечению между одной линией GL затвора и одной линией SLr истока, содержит красный цветной светофильтр, чтобы соответствовать этому элементу изображения, и данные изображений красного цвета подаются из драйвера 3 истока в этот элемент изображения через линию SLr истока, и тем самым этот элемент изображения выступает в качестве красного элемента изображения. Кроме того, элемент изображения, возбуждаемый посредством тонкопленочного транзистора M1g, который подключается к пересечению между линией GL затвора и линией SLg истока, содержит зеленый цветной светофильтр, чтобы соответствовать этому элементу изображения, и данные изображений зеленого цвета подаются из драйвера 3 истока в этот элемент изображения через линию SLg истока, и тем самым этот элемент изображения выступает в качестве зеленого элемента изображения. Кроме того, элемент изображения, возбуждаемый посредством тонкопленочного транзистора M1b, который подключается к пересечению между линией GL затвора и линией SLb истока, содержит синий цветной светофильтр, чтобы соответствовать этому элементу изображения, и данные изображений синего цвета подаются из драйвера 3 истока в этот элемент изображения через линию SLb истока, и тем самым этот элемент изображения выступает в качестве синего элемента изображения.

В конфигурации на фиг.2, линия Vsup питания, которая предоставляет питание в схему 81 датчика, и выходные межсоединения SData для вывода выходных данных схемы датчика предоставляются отдельно от линий SL истока. В частности, сток тонкопленочного транзистора M2 схемы 81 датчика подключается к линии Vsup питания, а его исток подключается к выходным межсоединениям SData.

Следует отметить, что в примере на фиг.2, схемы 81 датчиков предоставляются в соотношении один в расчете на пиксель (три элемента изображений) в пиксельной области 1. Тем не менее, соотношение расположения пикселей и схем 81 датчиков является произвольным и не ограничено просто этим примером. Например, одна схема 81 датчика может быть расположена в расчете на элемент изображения, и возможна конфигурация, в которой одна схема 81 датчика расположена для множества пикселей. В качестве другого примера, возможна конфигурация, в которой схемы 81 датчиков расположены в каждой второй строке.

Ниже приводится описание конфигурации и работы различных типов драйверов, показанных на фиг.1.

Сначала приводится описание конфигурации драйвера 5 строк и способа для его возбуждения со ссылкой на фиг.3 и 4. Как показано на фиг.3, драйвер 5 строк имеет сдвиговый регистр 51, состоящий из N триггеров, который, с использованием RSSP в качестве сигнала пускового импульса, последовательно формирует и переносит сигнал в синхронизации с синхросигналом RCK, и сдвиговый регистр 52, состоящий из N триггеров, который, с использованием RWSP в качестве сигнала пускового импульса, последовательно формирует и переносит сигнал в синхронизации с синхросигналом RCK. С помощью вывода SRRSOn (n=1-N), сдвиговый регистр 51 управляет размыканием и замыканием аналоговых переключателей RSn сигнала сброса (n=1-N). С помощью вывода SRRWOn (n=1-N), сдвиговый регистр 52 управляет размыканием и замыканием аналоговых переключателей RWn сигнала считывания (n=1-N).

Таким образом, аналоговые переключатели RSn сигнала сброса и аналоговые переключатели RWn сигнала считывания управляются так, чтобы последовательно размыкаться и замыкаться, и, следовательно, сигнал RS сброса и сигнал RW считывания последовательно подаются в строки схем 81 датчиков, расположенные в пиксельной области 1 (см. фиг.4). Следует отметить, что в конфигурации на фиг.3, сдвиговый регистр 51 для управления сигналом сброса и сдвиговый регистр 52 для управления сигналом считывания предоставляются независимо, тем самым предоставляя независимое управление синхронизацией считывания и синхронизацией сброса посредством изменения синхронизации пусковых импульсов RSSP и RWSP, соответственно.

Далее приводится описание конфигурации и работы драйвера 4 столбцов со ссылкой на фиг.5 и 6.

Как показано на фиг.5, драйвер 4 столбцов имеет сдвиговый регистр 41, состоящий из О триггеров, запоминающие конденсаторы 42, выходные схемы 43 и аналоговые переключатели 44. С помощью CSP в качестве пускового импульса, сдвиговый регистр 41 последовательно формирует и переносит сигнал в синхронизации с синхросигналом CCK. Запоминающие конденсаторы 42 дискретизируют выходные данные SDatao схемы датчика (o=1-O) в соответствии с сигналом RW считывания и сохраняют полученные в результате данные. Выходные схемы 43 разрешаются посредством вывода SROo (o=1-О) сдвигового регистра 41 и выводят данные в запоминающих конденсаторах 42 в выходные линии Dso (см. фиг.1). Аналоговые переключатели 44 управляются посредством сигнала RW считывания, и один из контактных выводов каждого из аналоговых переключателей 44 подключается к линии Vsup питания.

Как показано на фиг.6, согласно конфигурации на фиг.5, выходные данные SDatao схемы датчика для одной строки совместно дискретизируются посредством запоминающих конденсаторов 42 и хранятся в них в соответствии с сигналом RW считывания, и после этого сохраненные данные выводятся в выходные линии Dso в соответствующие времена в соответствии с последовательно сдвинутым выводом SROo сдвигового регистра 41. Кроме того, в соответствии с сигналом RW считывания, неизменяющееся постоянное напряжение из источников VDD питания подается в схемы 81 датчиков через линии Vsup питания.

Далее приводится описание конфигурации и работы драйвера 2 затвора со ссылкой на фиг.7 и 8. Драйвер 2 затвора имеет сдвиговый регистр 21, состоящий из L триггеров, и выходные схемы 22. С помощью GSP в качестве пускового импульса сдвиговый регистр 21 последовательно формирует и переносит сигнал в синхронизации с синхросигналом GCK. Выходные схемы 22 формируют и усиливают выходные сигналы вывода SROl (l=1-L) сдвигового регистра 21. Вывод выходных схем 22 последовательно выводится в линии GLl затвора (l=1-L) в пиксельной области 1 как сигналы выбора строки.

Ниже приводится описание конфигурации и работы драйвера 3 истока со ссылкой на фиг.9 и 10. Драйвер 3 истока имеет схему 31 преобразования из последовательной формы в параллельную, схемы 32 цифроаналогового преобразования и усилители 33. В синхронизации с сигналами синхронизации (Vsync, Hsync, CK и т.п.), которые введены снаружи, схема 31 преобразования из последовательной формы в параллельную преобразует последовательный видеосигнал, который аналогично введен снаружи как цифровые данные, в параллельные данные. Схемы 32 цифроаналогового преобразования преобразуют цифровой видеосигнал в аналоговый видеосигнал. В синхронизации с SSW, усилители 33 усиливают вывод схем 32 цифроаналогового преобразования и выводят результат в линии SLm истока (m=1-M).

Кроме того, фиг.11 показывает пример компоновки драйвера 3 истока и драйвера 4 столбцов. Конфигурация, показанная на фиг.11, по сути, является комбинацией конфигурации драйвера 4 столбцов, показанного на фиг.5, и конфигурации драйвера 3 истока, показанного на фиг.9. Число линий SL истока между триггерами, которые конфигурируют сдвиговый регистр 41 драйвера 4 столбцов и подключаются посредством каскадного соединения, зависит от компоновки схем 81 датчиков в направлении столбцов (горизонтальном направлении). В случае настоящего варианта осуществления, как показано на фиг.2, одна схема 81 датчика предоставляется в расчете на три элемента изображений (один пиксель), и, следовательно, на фиг.11, три линии SLr, SLg и SLb истока предоставляются между триггерами, которые конфигурируют сдвиговый регистр 41 драйвера 4 столбцов и подключаются посредством каскадного соединения.

Далее приводится описание синхронизации операции отображения пикселей в пиксельной области 1 и синхронизации работы фотодатчиков со ссылкой на фиг.12. В примере, показанном на фиг.12, сигнал RW считывания включается в периоде гашения периода горизонтального сканирования, и выходные данные SData схемы датчика считываются в выходную линию Dso. Следует отметить, что поскольку в дисплейном устройстве настоящего варианта осуществления, линии Vsup питания и выходные межсоединения SData для вывода выходных данных схемы датчика предоставляются отдельно от линий SL истока, как показано на фиг.2, сигнал RW считывания может применяться в активном периоде отображения. Также следует отметить, что фиг.12 показывает синхронизацию возбуждения в случае, если сигнал RW считывания и сигнал RS сброса применяются в соответствии с постоянной синхронизацией в каждом вертикальном периоде; сигнал RS(n) сброса применяется к схемам 81 датчиков в n-й строке в определенном вертикальном периоде, и выходные данные схемы датчика из этих схем 81 датчиков считываются вследствие применения сигнала RW(n) считывания в следующем вертикальном периоде. Другими словами, в примере на фиг.12, период измерения схем 81 датчиков имеет длительность, очень близкую к длительности одного вертикального периода.

Следует отметить, что признак дисплейного устройства согласно настоящему варианту осуществления заключается в том, что выходные межсоединения SData фиксируются при предварительно определенном потенциале V0 непосредственно перед сигналом RW считывания и сигналом RS сброса. По этой причине, как показано на фиг.13, сигнал DisC разрядки, который включается непосредственно перед сигналом RW считывания и сигналом RS сброса, используется как управляющий сигнал для приложения постоянного потенциала V0 к выходным межсоединениям SData. Следует отметить, что потенциал V0 является произвольным до тех пор, пока он является постоянным потенциалом, и потенциал V0 может быть, например, потенциалом земли.

Фиг.14 показывает пример схемной конфигурации для применения вышеописанного сигнала DisC разрядки к выходным межсоединениям SData. Как показано на фиг.14, признак драйвера 4 столбцов согласно настоящему варианту осуществления заключается в том, что аналоговый переключатель 45, размыкание и замыкание которого управляется посредством сигнала DisC разрядки, добавлен к базовой конфигурации, показанной на фиг.5 и 11. Один конец аналогового переключателя 45 подключается к источнику V0 неизменяющегося постоянного напряжения, а другой конец подключается к выходным межсоединениям SData.

Согласно этой конфигурации, как показано на фиг.15, потенциал выходных межсоединений SData фиксируется при постоянном потенциале V0, когда сигнал DisC разрядки включен, другими словами, непосредственно перед сигналом RW считывания и сигналом RS сброса. Соответственно, как можно видеть посредством сравнения фиг.15 и фиг.30, на которые содержатся ссылки в разделе предшествующего уровня техники, конфигурация настоящего варианта осуществления предоставляет исключение влияния, которое колебание в потенциале выходных межсоединений SData оказывает на запоминающий узел через паразитную емкость. Это дает возможность получения очень точного вывода схемы датчика, из которого удалено смещение.

Изменение 1 варианта осуществления 1

Следует отметить, что в вышеприведенном описании настоящего варианта осуществления показывается пример конфигурации, в котором линии Vsup питания и выходные межсоединения SData для выходных данных схемы датчика предоставляются отдельно от линий SL истока, как показано на фиг.2. Тем не менее, может приспосабливаться схемная конфигурация, в которой, как показано на фиг.16, линии SL истока также выступают в качестве линий Vsup питания и выходных межсоединений SData для выходных данных схемы датчика. Даже в случае этой конфигурации и, кроме того, случая выполнения возбуждения в соответствии с синхронизацией, показанной на фиг.12, фиксация потенциала выходных межсоединений SData при постоянном потенциале V0 непосредственно перед сигналом RW считывания и сигналом RS сброса дает возможность исключения смещения, возникающего из паразитной емкости, и получения очень точного вывода схемы датчика.

В частности, в схемной конфигурации, показанной на фиг.16, в случае если схемы 81 датчиков возбуждаются в соответствии с синхронизацией, показанной на фиг.12, потенциал выходных межсоединений SData непосредственно перед тем, как сигнал RW считывания применяется (Vw1, Vw2, ..., показанные на фиг.30), зависит от непосредственно предыдущих отображаемых данных. Кроме того, потенциал выходных межсоединений SData непосредственно перед тем, как сигнал RS сброса применяется (Vs1, Vs2, ..., показанные на фиг.30), зависит от непосредственно предыдущих выходных данных схемы датчика.

Соответственно, в этом случае также, даже если количество света, которое падает на фотодиод D1, является постоянным, выходные данные схемы датчика имеют смещение, возникающее из колебания в потенциале выходных межсоединений SData непосредственно перед сигналом RW считывания и сигналом RS сброса. Кроме того, как упомянуто выше, смещение не является постоянным и, следовательно, не может просто исключаться. Тем не менее, в этом случае также, фиксация потенциала выходных межсоединений SData равным постоянному потенциалу V0 в синхронизации с сигналом DisC разрядки, который включается непосредственно перед сигналом RW считывания и сигналом RS сброса, как описано выше, дает возможность исключения смещения, возникающего из паразитной емкости, и получения очень точного вывода схемы датчика.

Изменение 2 варианта осуществления 1

Кроме того, в вышеприведенном описании настоящего варианта осуществления, схема 81 датчика предоставляется в каждом пикселе в направлении строк (вертикальном направлении), и возбуждение выполняется в соответствии с синхронизацией, такой как синхронизация, показанная на фиг.12. Тем не менее, в случае если схема 81 датчика предоставляется в каждом втором пикселе в направлении строк, схемы 81 датчиков возбуждаются в соответствии с синхронизацией, показанной на фиг.17. В частности, сигнал RW считывания и сигнал RS сброса применяются к схемам 81 датчиков в каждом втором горизонтальном периоде.

Здесь, если синхронизация возбуждения на фиг.17 применяется к схемной конфигурации, в которой линии SL истока также выступают в качестве линий Vsup питания и выходных межсоединений SData для выходных данных схемы датчика, как показано на фиг.16, потенциал выходных межсоединений SData непосредственно перед тем, как сигнал RW считывания применяется (Vw1, Vw2, ..., показанные на фиг.30), зависит от непосредственно предыдущих отображаемых данных. Кроме того, потенциал выходных межсоединений SData непосредственно перед тем, как сигнал RS сброса применяется (Vs1, Vs2, ..., показанные на фиг.30), также зависит от непосредственно предыдущих отображаемых данных.

Соответственно, в этом случае также, даже если количество света, которое падает на фотодиод D1, является постоянным, выходные данные схемы датчика имеют смещение, возникающее из колебания в потенциале выходных межсоединений SData непосредственно перед сигналом RW считывания и сигналом RS сброса. Кроме того, как упомянуто выше, смещение не является постоянным и, следовательно, не может просто исключаться. Тем не менее, в этом случае также, фиксация потенциала выходных межсоединений SData равным постоянному потенциалу V0 в синхронизации с сигналом DisC разрядки, который включается непосредственно перед сигналом RW считывания и сигналом RS сброса, как описано выше, дает возможность исключения смещения, возникающего из паразитной емкости между запоминающим узлом и выходными межсоединениями SData, и получения очень точного вывода схемы датчика.

Второй вариант осуществления

Ниже приводится описание варианта осуществления 2 настоящего изобретения. Следует отметить, что составляющим элементам, имеющим функции, идентичные функциям составляющих элементов, описанных в варианте осуществления 1, присвоены ссылки с номерами, идентичные ссылкам с номерами в варианте осуществления 1, и их подробные описания опущены.

Дисплейное устройство согласно варианту осуществления 2 имеет схемную конфигурацию, показанную на фиг.16, схемы 81 датчиков предоставляются в каждом втором пикселе в направлении строк, и схемы 81 датчиков возбуждаются в соответствии с синхронизацией, показанной на фиг.17. Кроме того, хотя потенциал выходных межсоединений SData фиксируется равным постоянному потенциалу V0 непосредственно перед сигналом RW считывания и сигналом RS сброса аналогично варианту осуществления 1, вариант осуществления 2 отличается от варианта осуществления 1 в том, что напряжение питания (VDD), которое традиционно подается в схемы 81 датчиков через линии Vsup питания только во время применения сигнала RW считывания, также подается непосредственно перед сигналом RS сброса, как показано на фиг.18.

В частности, в варианте осуществления 2, напряжение питания (VDD) подается в линии Vsup питания в то время, когда сигнал VSW включен, при этом сигнал VSW включается в предварительно определенный период непосредственно перед сигналом RS сброса, и в то время, когда сигнал RW считывания включен, как показано на фиг.18. Чтобы реализовывать это, в дисплейном устройстве согласно варианту осуществления 2, аналоговые переключатели 44, которые управляют подачей напряжения питания (VDD) в линии Vsup питания в драйвере 4 столбцов, размыкаются и замыкаются в соответствии с сигналом VSW, как показано на фиг.19. Следует отметить, что в варианте осуществления 1, размыкание и замыкание аналоговых переключателей 44 для линий Vsup питания управляется в соответствии с сигналом RW считывания, как показано на фиг.5, 11 и 14.

Таким образом, потенциал линий Vsup питания фиксируется равным предварительно определенному потенциалу (напряжению VDD питания) непосредственно перед сигналом RS сброса в соответствии с сигналом VSW, который является независимым от сигнала RW считывания, тем самым давая возможность сохранения постоянным потенциала линий Vsup питания непосредственно перед сигналом RW считывания и сигналом RS сброса независимо от их предыдущего состояния, как показано на фиг.18. Это дает возможность исключения смещения, возникающего из паразитной емкости между запоминающим узлом и линиями Vsup питания, и получения очень точного вывода схемы датчика. Кроме того, аналогично варианту осуществления 1, фиксация потенциала выходных межсоединений SData равным постоянному потенциалу V0 непосредственно перед сигналом RW считывания и сигналом RS сброса дает возможность исключения смещения, возникающего из паразитной емкости между запоминающим узлом и выходными межсоединениями SData, и получения очень точного вывода схемы датчика.

Следует отметить, что в вышеприведенном описании варианта осуществления 2, описан пример, в котором дисплейное устройство имеет схемную конфигурацию, показанную на фиг.16, схемы 81 датчиков предоставляются в каждом втором пикселе в направлении строк, и схемы 81 датчиков возбуждаются в соответствии с синхронизацией, показанной на фиг.17. Тем не менее, управление линиями Vsup питания в соответствии с сигналом VSW также может применяться к схемной конфигурации, показанной на фиг.2, и получаются аналогичные эффекты. Кроме того, даже в случае возбуждения схем 81 датчиков в соответствии с синхронизацией, показанной на фиг.12, в конфигурации, в которой схемы 81 датчиков предоставляются в каждом пикселе в направлении строк, управление линиями Vsup питания в соответствии с сигналом VSW может применяться, и получаются аналогичные эффекты.

Третий вариант осуществления

Ниже приводится описание варианта осуществления 3 настоящего изобретения. Следует отметить, что составляющим элементам, имеющим функции, идентичные функциям составляющих элементов, описанных в вышеописанных вариантах осуществления, присвоены ссылки с номерами, идентичные ссылкам с номерами в вышеописанных вариантах осуществления, и их подробные описания опущены.

Дисплейное устройство согласно варианту осуществления 3 имеет схемную конфигурацию, показанную на фиг.16, схемы 81 датчиков предоставляются в каждом пикселе в направлении строк, и схемы 81 датчиков возбуждаются в соответствии с синхронизацией, показанной на фиг.12. Кроме того, потенциал выходных межсоединений SData фиксируется равным предварительно определенному потенциалу непосредственно перед сигналом RW считывания и сигналом RS сброса аналогично варианту осуществления 1. Тем не менее, вариант осуществления 3 отличается от варианта осуществления 1 в том, что предварительно определенным потенциалом является предварительно определенный уровень (Vx), вводимый как видеосигнал, как показано на фиг.20. Следует отметить, что предусмотрено два типа способов для получения этого постоянного потенциала Vx, первый из которых использует вывод повторителя напряжения, составляющего выходную схему 33 усиления (см. фиг.9 и т.п.) драйвера 3 истока, а второй из которых использует функцию фиксации потенциала сигнальной линии выходной схемы 33 усиления драйвера 3 истока.

Во-первых, в случае вышеописанного первого способа, выходная схема 33 усиления, которая усиливает вывод в линии SL истока, которые выступают в качестве межсоединений SData, реализована посредством схемы повторителя напряжения, полученной посредством применения отрицательной обратной связи к дифференциальной схеме усиления, как показано на фиг.21. Эта схема усиливает ток входного напряжения IN в активном режиме вследствие разрешающего вывода. С другой стороны, эта схема находится в состоянии высокого полного сопротивления в неактивном режиме. Соответственно, достаточно включать сигнал разрешения также в соответствии с синхронизацией сигнала PCH, показанного на фиг.20, и вводить в качестве входного напряжения IN напряжение, которое получает предварительно определенное напряжение Vx после усиления.

С другой стороны, в случае вышеописанного второго способа, достаточно для выходной схемы 33 усиления, которая усиливает вывод в линии SL истока, которые выступают в качестве межсоединений SData, использовать конфигурацию, в которой дифференциальная схема усиления, показанная на фиг.21, дополнительно содержит переключатель, как показано на фиг.22A. Согласно конфигурации на фиг.22A, неизменяющееся постоянное напряжение Vx может выводиться в линии SL истока, которые выступают в качестве межсоединений SData, только в то время, когда сигнал PCH включен, как показано на фиг.22B.

Согласно варианту осуществления 3, как описано выше, фиксация потенциала выходных межсоединений SData равным постоянному потенциалу Vx непосредственно перед сигналом RW считывания и сигналом RS сброса дает возможность исключения смещения, возникающего из паразитной емкости между запоминающим узлом и выходными межсоединениями SData, и получения очень точного вывода схемы датчика.

Кроме того, аналогично варианту осуществления 2, потенциал линий Vsup питания фиксируется равным предварительно определенному потенциалу (напряжению VDD питания) непосредственно перед сигналом RS сброса в соответствии с сигналом VSW, который является независимым от сигнала RW считывания, тем самым давая возможность сохранения постоянным потенциала линий Vsup питания непосредственно перед сигналом RW считывания и сигналом RS сброса независимо от их предыдущего состояния, как показано на фиг.18. Это дает возможность исключения смещения, возникающего из паразитной емкости между запоминающим узлом и линиями Vsup питания, и получения очень точного вывода схемы датчика.

Следует отметить, что в вышеприведенном описании варианта осуществления 3 описан пример, в котором дисплейное устройство имеет схемную конфигурацию, показанную на фиг.16, схемы 81 датчиков предоставляются в каждом втором пикселе в направлении строк, и схемы 81 датчиков возбуждаются в соответствии с синхронизацией, показанной на фиг.17. Тем не менее, даже в случае возбуждения схем 81 датчиков в соответствии с синхронизацией, показанной на фиг.12, в конфигурации, в которой схемы 81 датчиков предоставляются в каждом пикселе в направлении строк, аналогичные эффекты получаются посредством фиксации потенциала выходных межсоединений SData равным предварительно определенному потенциалу Vx непосредственно перед сигналом RW считывания и сигналом RS сброса, как описано выше.

Четвертый вариант осуществления

Ниже приводится описание варианта осуществления 4 настоящего изобретения. Следует отметить, что составляющим элементам, имеющим функции, идентичные функциям составляющих элементов, описанных в вышеописанных вариантах осуществления, присвоены ссылки с номерами, идентичные ссылкам с номерами в вышеописанных вариантах осуществления, и их подробные описания опущены.

Дисплейное устройство согласно варианту осуществления 4 имеет схемную конфигурацию, показанную на фиг.16, схемы 81 датчиков предоставляются в каждом пикселе в направлении строк, и схемы 81 датчиков возбуждаются в соответствии с синхронизацией, показанной на фиг.12. Кроме того, в дисплейном устройстве согласно варианту осуществления 4, как показано на фиг.23, предварительно определенный уровень (Vx), вводимый как видеосигнал непосредственно перед сигналом RW считывания, подается в линии SL истока, которые выступают в качестве межсоединений SData (см. вариант осуществления 3). Кроме того, предварительно определенное напряжение V0 подается в линии SL истока, которые выступают в качестве межсоединений SData, непосредственно перед сигналом RS сброса (см. вариант осуществления 1). Кроме того, как непосредственно перед сигналом RS сброса, так и в период, в который сигнал RW считывания применяется, потенциал линий Vsup питания фиксируется равным предварительно определенному потенциалу (напряжению VDD питания) в соответствии с сигналом VSW, который является независимым от сигнала RW считывания (см. вариант осуществления 2). Следует отметить, что напряжения V0 и Vx являются произвольными при условии, что они являются постоянными значениями. Кроме того, значения V0 и Vx могут быть взаимно различными.

Как описано выше, комбинирование вариантов осуществления 1-3 дает возможность исключения как смещения, возникающего из паразитной емкости между запоминающим узлом и выходными межсоединениями SData, так и смещения, возникающего из паразитной емкости между запоминающим узлом и линиями Vsup питания, и получения очень точного вывода схемы датчика.

Хотя варианты осуществления 1 и 2 настоящего изобретения описаны выше, настоящее изобретение не ограничено только вышеописанными вариантами осуществления и различные модификации могут осуществляться в рамках объема изобретения.

Например, в настоящем изобретении, предпочтительно, чтобы потенциал межсоединений, имеющих паразитную емкость с запоминающим узлом, фиксировался равным предварительно определенному потенциалу как непосредственно перед сигналом RW считывания, так и непосредственно перед сигналом RS сброса. Тем не менее, предусмотрены случаи, когда достаточный эффект получается даже посредством фиксации потенциала межсоединений, имеющих паразитную емкость с запоминающим узлом, равным предварительно определенному потенциалу только непосредственно перед сигналом RW считывания или непосредственно перед сигналом RS сброса. Соответственно, например, приложение напряжения V0 в соответствии с сигналом DisC разрядки может опускаться в варианте осуществления 4.

Кроме того, в вышеописанных вариантах осуществления, приведен пример конфигурации, в которой схема 81 датчика имеет фотодиод D1, конденсатор C2 и один тонкопленочный транзистор M2, как показано на фиг.2 и 16. Тем не менее, настоящее изобретение также применимо к конфигурации, в которой, как показано на фиг.24, схема 81 датчика включает в себя фотодиод D1, конденсатор C2 и три тонкопленочных транзистора M2, M4 и M5. В частности, в этой конфигурации, фиксация потенциала межсоединений, имеющих паразитную емкость с запоминающим узлом, равным предварительно определенному потенциалу только непосредственно перед сигналом RW считывания или непосредственно перед сигналом RS сброса дает возможность исключения смещений, возникающих из паразитной емкости между запоминающим узлом и вышеописанными межсоединениями, и получения очень точного вывода схемы датчика.

Кроме того, хотя пример, в котором схема 81 датчика включает в себя конденсатор C2 в качестве накопительного конденсатора, приведен в вышеописанных вариантах осуществления, даже если схемный элемент, соответствующий накопительному конденсатору, не предоставляется в схеме 81 датчика, можно использовать паразитную емкость, которая формируется в запоминающем узле, в качестве накопительного конденсатора. Конденсатор C2, следовательно, является несущественным.

Промышленная применимость

Настоящее изобретение промышленно применимо в качестве дисплейного устройства, имеющего фотодатчик в пиксельной области подложки активной матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2451983C1 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2457550C1 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2473937C2 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2010 |

|

RU2501067C1 |

| ДИСПЛЕЙ | 2009 |

|

RU2473110C2 |

| СХЕМА ВОЗБУЖДЕНИЯ ДИСПЛЕЯ, ДИСПЛЕЙНАЯ ПАНЕЛЬ И УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2487424C1 |

| ДИСПЛЕЙ | 2009 |

|

RU2471213C1 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО И СПОСОБ ДЛЯ ВОЗБУЖДЕНИЯ ДИСПЛЕЙНОГО УСТРОЙСТВА | 2008 |

|

RU2443071C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ | 2013 |

|

RU2649967C2 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2510931C2 |

Изобретение относится к дисплейным устройствам. Техническим результатом является повышение точности выходных данных схемы фотодатчика. Дисплейное устройство содержит фотодатчик в пиксельной области подложки активной матрицы, содержащий: фотодетекторный элемент, принимающий падающий свет; запоминающий узел, подключенный к фотодетекторному элементу, причем потенциал запоминающего узла изменяется в соответствии с выходным током из фотодетекторного элемента; средства соединения сигнала сброса, подающие сигнал сброса в фотодатчик; средства соединения сигнала считывания, подающие сигнал считывания в фотодатчик; и переключающий элемент датчика для считывания потенциала запоминающего узла на выход в качестве вывода схемы датчика. 6 з.п. ф-лы, 30 ил.

1. Дисплейное устройство, содержащее фотодатчик в пиксельной области подложки активной матрицы, причем фотодатчик содержит: фотодетекторный элемент, который принимает падающий свет; запоминающий узел, который подключается к фотодетекторному элементу, причем потенциал запоминающего узла изменяется в соответствии с выходным током из фотодетекторного элемента; межсоединения сигнала сброса, которые подают сигнал сброса в фотодатчик; межсоединения сигнала считывания, которые подают сигнал считывания в фотодатчик; и переключающий элемент датчика для считывания потенциала запоминающего узла на выходные межсоединения в качестве вывода схемы датчика, при этом потенциал запоминающего узла изменяется в соответствии с количеством света, принимаемым посредством фотодетекторного элемента в периоде измерения, причем период измерения длится от момента, когда подается сигнал сброса, до момента, когда подается сигнал считывания, при этом потенциал межсоединений, имеющих паразитную емкость с запоминающим узлом, фиксируется равным предварительно определенному потенциалу, по меньшей мере, либо непосредственно перед сигналом считывания или непосредственно перед сигналом сброса.

2. Дисплейное устройство по п.1, в котором межсоединения, имеющие паразитную емкость с запоминающим узлом, являются выходными межсоединениями.

3. Дисплейное устройство по п.2, в котором видеосигнал, имеющий предварительно определенный уровень, подается в выходные межсоединения, чтобы фиксировать потенциал выходных межсоединений равным предварительно определенному потенциалу.

4. Дисплейное устройство по п.1, в котором межсоединения, имеющие паразитную емкость с запоминающим узлом, являются межсоединениями питания, которые подают напряжение питания в фотодатчик в период, в который сигнал считывания подается, и межсоединения питания также выступают в качестве линии истока, которая подает видеосигнал в пиксель в пиксельной области.

5. Дисплейное устройство по п.4, в котором фиксация потенциала межсоединений питания равным предварительно определенному потенциалу управляется посредством сигнала, отличного от сигнала считывания.

6. Дисплейное устройство по п.1, в котором видеосигнал, имеющий предварительно определенный уровень, подается в выходные межсоединения, чтобы фиксировать потенциал выходных межсоединений равным первому предварительно определенному потенциалу непосредственно перед сигналом считывания, и напряжение, имеющее предварительно определенный уровень, подается в выходные межсоединения, чтобы фиксировать потенциал выходных межсоединений равным второму предварительно определенному потенциалу непосредственно перед сигналом сброса.

7. Дисплейное устройство по любому из пп.1-6, дополнительно содержащее: общую подложку, располагающуюся напротив подложки активной матрицы; и жидкий кристалл, размещаемый между подложкой активной матрицы и общей подложкой.

| МАТРИЧНЫЙ ДИСПЛЕЙ С АДРЕСУЕМЫМИ ЭЛЕМЕНТАМИ ДИСПЛЕЯ И СООТВЕТСТВУЮЩИЕ ЕМУ СПОСОБЫ | 2004 |

|

RU2289887C2 |

| ЖИДКОКРИСТАЛЛИЧЕСКИЙ ДИСПЛЕЙ | 2006 |

|

RU2319991C1 |

| JP 2006003857 A, 05.01.2006 | |||

| JP 9247536 A, 19.09.1997 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

2012-04-27—Публикация

2009-07-07—Подача