ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к дисплейным устройствам, а более конкретно к дисплейному устройству, в котором множество оптических датчиков размещаются в пикселной области.

УРОВЕНЬ ТЕХНИКИ

Относительно дисплейных устройств, к настоящему времени известны такие способы предоставления функций ввода, как сенсорные панели, устройства перьевого ввода и сканеры, таким образом, что множество оптических датчиков предоставляется на дисплейной панели. Чтобы адаптировать этот способ к мобильному устройству, которое должно использоваться в различных окружениях освещения, необходимо исключать влияние окружения освещения. Следовательно, также известен способ исключения компонента в зависимости от окружения освещения из сигнала, считываемого посредством оптического датчика, чтобы получать сигнал, который должен вводиться по существу.

Патентный документ 1 описывает устройство ввода-вывода, в котором светоприемные элементы предоставляются согласно отдельным дисплейным элементам. В устройстве ввода-вывода задняя подсветка включается и выключается однократно за период в один кадр, и сброс и считывание из светоприемных элементов выполняется последовательно по линиям так, что количество света в течение периода включения задней подсветки и количество света в течение периода выключения задней подсветки получается из всех светоприемных элементов за период в один кадр.

Фиг. 20 является схемой, показывающей времена включения и выключения задней подсветки, а также времена сброса и считывания светоприемных элементов в патентном документе 1. Как показано на фиг. 20, за период в один кадр задняя подсветка включается в первой половине и выключается во второй половине. В течение периода включения задней подсветки сброс для светоприемных элементов выполняется последовательно по линиям (стрелка со сплошной линией), а затем считывание из светоприемных элементов выполняется последовательно по линиям (стрелка с пунктирной линией). Также в течение периода выключения задней подсветки сброс и считывание из светоприемных элементов выполняется аналогичным образом.

Патентный документ 2 описывает твердотельное устройство формирования изображений, включающее в себя единичную светоприемную секцию, показанную на фиг. 21. Как показано на фиг. 21, единичная светоприемная секция включает в себя одну часть PD фотоэлектрического преобразования и две части C1 и C2 накопления заряда. В случае приема как внешнего света, так и света, который излучается из светоизлучающего средства и затем отражается от физического объекта, первый выборочный затвор SG1 включается, и заряд, сформированный посредством части PD фотоэлектрического преобразования, накапливается в первой части C1 накопления заряда. В случае приема только внешнего света второй выборочный затвор SG2 включается, и заряд, сформированный посредством части PD фотоэлектрического преобразования, накапливается во второй части C2 накопления заряда. Можно получать разность между величинами заряда, накопленными в этих двух частях C1 и C2 накопления заряда, тем самым получая количество света, который излучается из светоизлучающего средства и затем отражается от физического объекта.

ДОКУМЕНТЫ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

Патентные документы

Патентный документ 1. Патент (Япония) номер 4072732

Патентный документ 2. Патент (Япония) номер 3521187

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Задачи, которые должны быть решены изобретением

В типичном дисплейном устройстве, в котором множество оптических датчиков предоставляются на дисплейной панели, считывание из оптических датчиков выполняется последовательно по линиям. Кроме того, задние подсветки для мобильного устройства включаются одновременно и выключаются одновременно как один экран.

В устройстве ввода-вывода, описанном в патентном документе 1, задняя подсветка включается и выключается однократно за период в один кадр. В течение периода включения задней подсветки период для сброса не перекрывается с периодом для считывания. Также в течение периода выключения задней подсветки период для сброса не перекрывается с периодом для считывания. Следовательно, считывание из светоприемных элементов должно быть выполнено за период в 1/4 кадра (например, в течение 1/240 секунд в случае, если частота кадров составляет 60 кадров в секунду). Тем не менее, фактически очень трудно выполнять высокоскоростное считывание, описанное выше.

Кроме того, существует отклонение, соответствующее периоду в 1/2 кадра между периодом (B1, показан на фиг. 20), в течение которого светоприемный элемент считывает свет в период включения задней подсветки, и периодом (B2, показан на фиг. 20), в течение которого светоприемный элемент считывает свет в период выключения задней подсветки. Следовательно, характеристика следования входному перемещению варьируется в соответствии с направлением ввода. Кроме того, это устройство ввода-вывода начинает выполнять считывание сразу после завершения сброса и начинает выполнять сброс сразу после завершения считывания. Следовательно, невозможно свободно задавать длительность и интервал относительно периода включения задней подсветки и периода выключения задней подсветки.

Кроме того, в этом устройстве ввода-вывода количество света в течение периода включения задней подсветки и количество света в течение периода выключения задней подсветки определяются посредством идентичного светоприемного элемента. Следовательно, в случае, если определенный светоприемный элемент определяет количество света в течение периода включения задней подсветки, этот светоприемный элемент не может начинать определять количество света в течение периода выключения задней подсветки до тех пор, пока определенное количество света не считывается из этого светоприемного элемента.

Кроме того, это устройство ввода-вывода отдельно определяет количество света в течение периода включения задней подсветки и количество света в течение периода выключения задней подсветки. Следовательно, в случае, если одно из количеств света насыщается, невозможно корректно получать разность между этими двумя количествами света. В качестве способа для недопущения насыщения количества света рассматривается способ понижения чувствительности оптического датчика и способ сокращения выдержки (времени накопления). Тем не менее, когда чувствительность оптического датчика понижается, точность обнаружения количества света снижается. Кроме того, трудно регулировать выдержку, поскольку частота кадров определяется заранее во многих случаях.

Следовательно, цель настоящего изобретения заключается в том, чтобы предоставлять дисплейное устройство, которое разрешает проблемы, описанные выше, и имеет функцию ввода, которая не зависит от окружений освещения.

СРЕДСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ

Согласно первому аспекту настоящего изобретения предоставляется дисплейное устройство, в котором множество оптических датчиков размещаются в пикселной области, причем дисплейное устройство включает в себя: дисплейную панель, которая включает в себя множество пикселных схем дисплея и множество пикселных схем датчиков; и возбуждающую схему, которая выводит в пикселные схемы датчиков управляющий сигнал, указывающий, что источник света включается или источник света выключается, при этом пикселная схема датчика включает в себя: один оптический датчик; один узел накопления, накапливающий заряд, соответствующий количеству считываемого света; считывающий транзистор, имеющий управляющий контактный вывод, подключенный к узлу накопления; и множество переключающих элементов, которые включаются или выключаются в соответствии с управляющим сигналом и переключают путь для тока, протекающего через оптический датчик, и пикселная схема датчика выполнена так, что в соответствии с управляющим сигналом ток, протекающий через оптический датчик, протекает в предварительно определенном направлении относительно узла накопления, когда источник света включается, и протекает в обратном направлении относительно узла накопления, когда источник света выключается.

Согласно второму аспекту настоящего изобретения в первом аспекте настоящего изобретения пикселная схема датчика включает в себя: первый переключающий элемент, который предоставляется между линией сброса и одним из концов оптического датчика и включается, когда источник света включается; второй переключающий элемент, который предоставляется между проводом, к которому прикладывается предварительно определенный потенциал, и другим концом оптического датчика и включается, когда источник света выключается; третий переключающий элемент, который предоставляется между узлом накопления и одним из концов оптического датчика и включается, когда источник света выключается; и четвертый переключающий элемент, который предоставляется между узлом накопления и другим концом оптического датчика и включается, когда источник света включается.

Согласно третьему аспекту настоящего изобретения во втором аспекте настоящего изобретения каждый из первого и третьего переключающих элементов выполнен с помощью транзистора первого проводящего типа, каждый из второго и четвертого переключающих элементов выполнен с помощью транзистора второго проводящего типа, первый и второй переключающие элементы включаются или выключаются в соответствии с первым управляющим сигналом, третий переключающий элемент включается или выключается в соответствии со вторым управляющим сигналом, четвертый переключающий элемент включается или выключается в соответствии с третьим управляющим сигналом, и каждый из второго и третьего управляющих сигналов является инвертированным сигналом от первого управляющего сигнала и изменяется во время, которое отличается от времени первого управляющего сигнала.

Согласно четвертому аспекту настоящего изобретения во втором аспекте настоящего изобретения каждый из первого и четвертого переключающих элементов выполнен с помощью транзистора первого проводящего типа, каждый из второго и третьего переключающих элементов выполнен с помощью транзистора второго проводящего типа, первый и четвертый переключающие элементы включаются или выключаются в соответствии с первым управляющим сигналом, и второй и третий переключающие элементы включаются или выключаются в соответствии со вторым управляющим сигналом, изменяющимся в другое время в идентичном направлении с первым управляющим сигналом.

Согласно пятому аспекту настоящего изобретения во втором аспекте настоящего изобретения пикселная схема датчика дополнительно включает в себя конденсатор, предоставляемый между узлом накопления и линией считывания.

Согласно шестому аспекту настоящего изобретения во втором аспекте настоящего изобретения четвертый переключающий элемент усиливает потенциал в узле накопления, когда потенциал для считывания прикладывается к его управляющему контактному выводу.

Согласно седьмому аспекту настоящего изобретения в первом аспекте настоящего изобретения возбуждающая схема выводит, в качестве управляющего сигнала, сигнал, указывающий, что источник света включается, и источник света выключается многократно, соответственно, за период в один кадр.

Согласно восьмому аспекту настоящего изобретения предоставляется пикселная схема датчика, которая должна размещаться в пикселной области дисплейного устройства, причем пикселная схема датчика включает в себя: один оптический датчик; один узел накопления, накапливающий заряд, соответствующий количеству считываемого света; считывающий транзистор, имеющий управляющий контактный вывод, подключенный к узлу накопления; и множество переключающих элементов, которые включаются или выключаются в соответствии с управляющим сигналом, указывающим, что источник света включается или источник света выключается, и переключают путь для тока, протекающего через оптический датчик, при этом пикселная схема датчика выполнена так, что в соответствии с управляющим сигналом ток, протекающий через оптический датчик, протекает в предварительно определенном направлении относительно узла накопления, когда источник света включается, и протекает в обратном направлении относительно узла накопления, когда источник света выключается.

ПРЕИМУЩЕСТВА ИЗОБРЕТЕНИЯ

Согласно первому аспекту настоящего изобретения пикселная схема датчика включает в себя один оптический датчик и один узел накопления. Кроме того, ток протекает из/в узел накопления в обратном направлении, и потенциал в узле накопления изменяется в обратном направлении, когда источник света включается и когда источник света выключается. Соответственно, можно определять разность между количеством света, когда источник света включается, и количеством света, когда источник света выключается, посредством использования одной пикселной схемы датчика и предоставлять функцию ввода, которая не зависит от окружений освещения. Кроме того, разность между количествами света определяется посредством использования одной пикселной схемы датчика. По сравнению со случаем отдельного определения двух типов количеств света, следовательно, можно не допускать насыщения количества света и корректно получать разность между количествами света. Кроме того, по сравнению со случаем последовательного определения двух типов количества света посредством использования одной пикселной схемы датчика можно уменьшать частоту считывания из пикселных схем датчиков, снижать скорость считывания и уменьшать потребление мощности в устройстве. Кроме того, становится необязательным предоставлять запоминающее устройство, которое требуется в случае определения двух типов количеств света последовательно и используется для сохранения количества света, считываемого сначала. Кроме того, можно увеличивать степень свободы для задания времен включения и выключения источника света, а также времен сброса и считывания пикселных схем датчиков. Кроме того, в случае использования подходящего способа возбуждения можно исключать отклонение между периодом считывания, когда источник света включается, и периодом считывания, когда источник света выключается, и не допускать варьирования характеристики следования входному перемещению в соответствии с направлением ввода. Кроме того, посредством получения разности между количествами света посредством использования одной пикселной схемы датчика можно одновременно выполнять температурную компенсацию.

Согласно второму аспекту настоящего изобретения, когда источник света включается, первый и четвертый переключающие элементы включаются, и путь тока формируется так, что он проходит через оптический датчик и первый и четвертый переключающие элементы. Когда источник света выключается, второй и третий переключающие элементы включаются, и путь тока формируется так, что он проходит через оптический датчик и второй и третий переключающие элементы. Соответственно, посредством задания потенциала в линии сброса и предварительно определенного потенциала надлежащим образом можно создавать пикселную схему датчика, в который ток протекает из/в узел накопления в обратном направлении, когда источник света включается и когда источник света выключается, и которой дается возможность определять разность между количеством света, когда источник света включается, и количеством света, когда источник света выключается.

Согласно третьему аспекту настоящего изобретения, когда источник света включается, первый и четвертый переключающие элементы включаются так, что предварительно определенный путь тока формируется. Когда источник света выключается, второй и третий переключающие элементы включаются так, что другой путь тока формируется. Кроме того, второй и третий управляющие сигналы изменяются во время, которое отличается от времени управляющего сигнала. Следовательно, можно точно управлять периодом существования пути тока и повышать точность обнаружения.

Согласно четвертому аспекту настоящего изобретения, когда источник света включается, первый и четвертый переключающие элементы включаются так, что предварительно определенный путь тока формируется. Когда источник света выключается, второй и третий переключающие элементы включаются так, что другой путь тока формируется. Кроме того, посредством использования этих двух управляющих сигналов можно сокращать число управляющих сигналов, увеличивать светосилу и повышать чувствительность пикселной схемы датчика.

Согласно пятому аспекту настоящего изобретения посредством прикладывания потенциала для считывания к линии считывания можно изменять потенциал в узле накопления и считывать сигнал, соответствующий количеству считываемого света, из пикселной схемы датчика.

Согласно шестому аспекту настоящего изобретения, когда потенциал для считывания прикладывается к управляющему контактному выводу четвертого переключающего элемента, потенциал в узле накопления усиливается. Таким образом, можно повышать чувствительность пикселной схемы датчика.

Согласно седьмому аспекту настоящего изобретения посредством многократного выполнения операции считывания света, когда источник света включается, и операции считывания света, когда источник света выключается, соответственно, за период в один кадр, можно не допускать насыщения количества света и корректно получать разность между количествами света. Кроме того, можно исключать отклонение между периодом считывания, когда источник света включается, и периодом считывания, когда источник света выключается, и не допускать варьирования характеристики следования входному перемещению в соответствии с направлением ввода.

Согласно восьмому аспекту настоящего изобретения можно создавать пикселную схему датчика, которая должна быть включена в дисплейное устройство согласно первому аспекту, и предоставлять дисплейное устройство, имеющее функцию ввода, которая не зависит от окружений освещения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг. 1 является блок-схемой, показывающей конфигурацию дисплейного устройства согласно одному варианту осуществления настоящего изобретения.

Фиг. 2 является схемой, показывающей компоновку пикселных схем датчиков на дисплейной панели, включенной в дисплейное устройство, показанное на фиг. 1.

Фиг. 3 является схемой, показывающей времена включения и выключения задней подсветки, а также времена сброса и считывания пикселных схем датчиков в дисплейном устройстве, показанном на фиг. 1.

Фиг. 4 является схемой форм сигналов дисплейной панели, включенной в дисплейное устройство, показанное на фиг. 1.

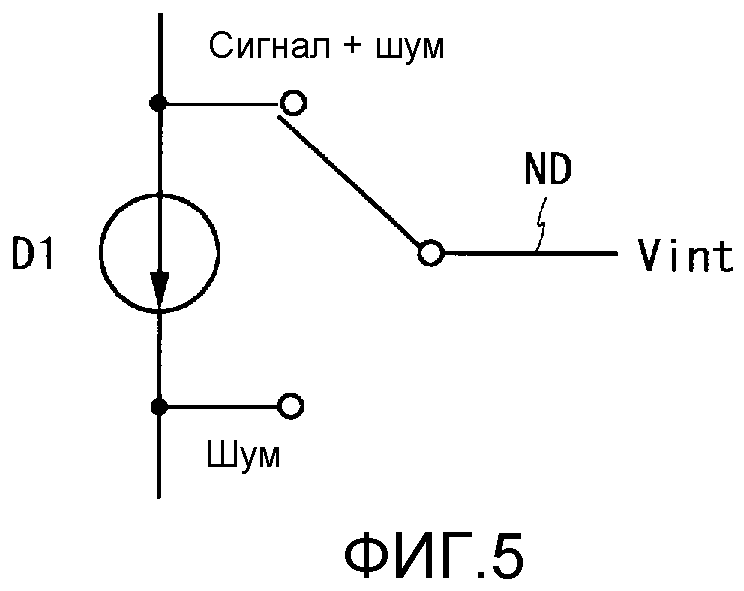

Фиг. 5 является схемой, показывающей схематичную конфигурацию пикселной схемы датчика, включенной в дисплейное устройство, показанное на фиг. 1.

Фиг. 6 является принципиальной схемой пикселной схемы датчика согласно первому варианту осуществления настоящего изобретения.

Фиг. 7A является схемой компоновки пикселной схемы датчика, показанной на фиг. 6.

Фиг. 7B является другой схемой компоновки пикселной схемы датчика, показанной на фиг. 6.

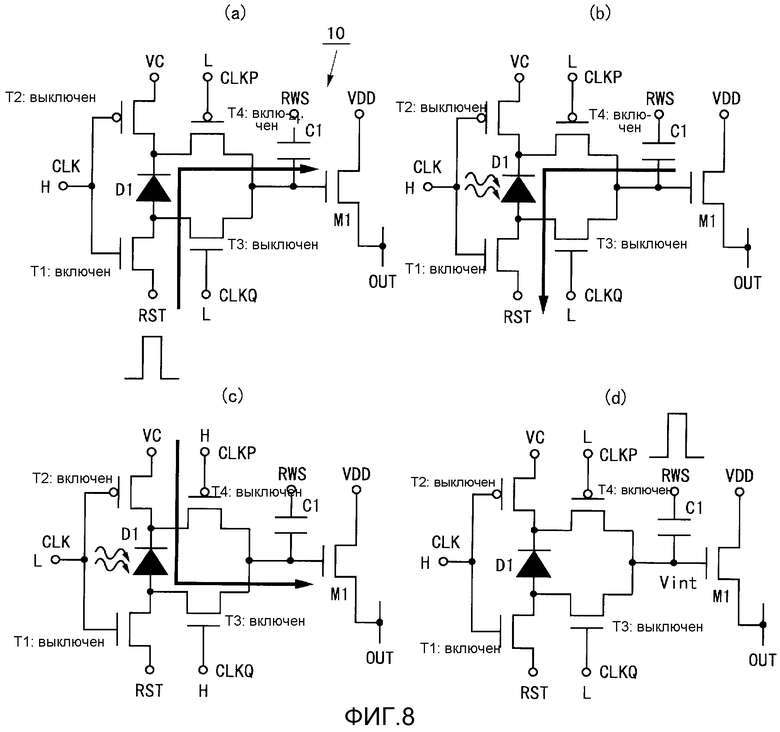

Фиг. 8 является схемой, показывающей операции пикселной схемы датчика, показанной на фиг. 6.

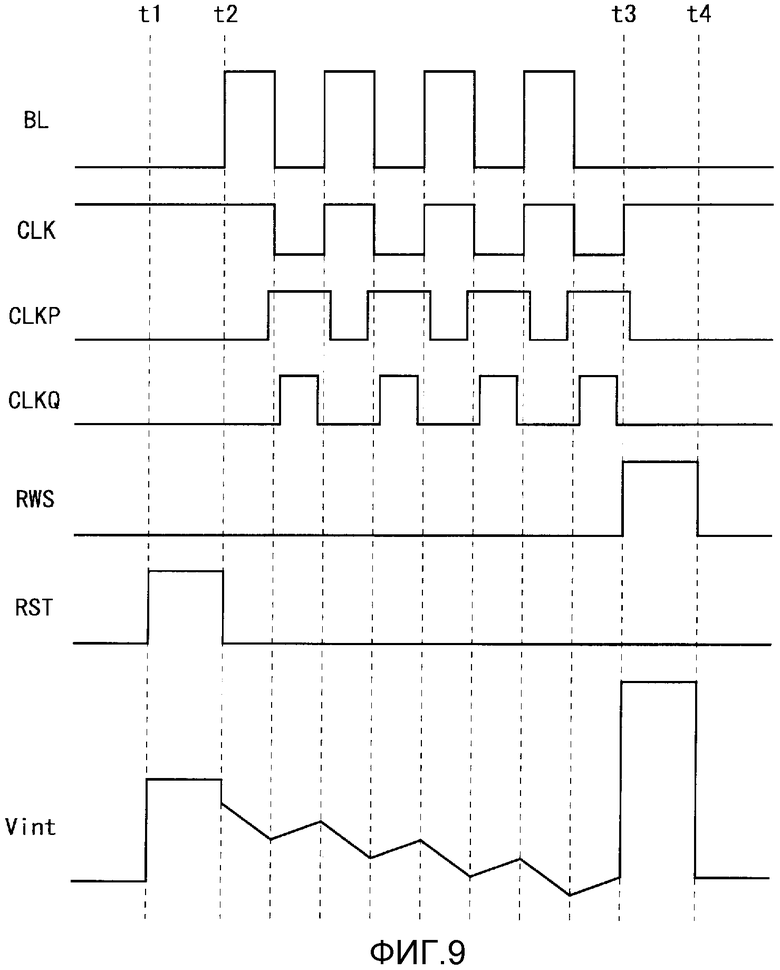

Фиг. 9 является схемой форм сигналов пикселной схемы датчика, показанной на фиг. 6.

Фиг. 10 является принципиальной схемой пикселной схемы датчика согласно второму варианту осуществления настоящего изобретения.

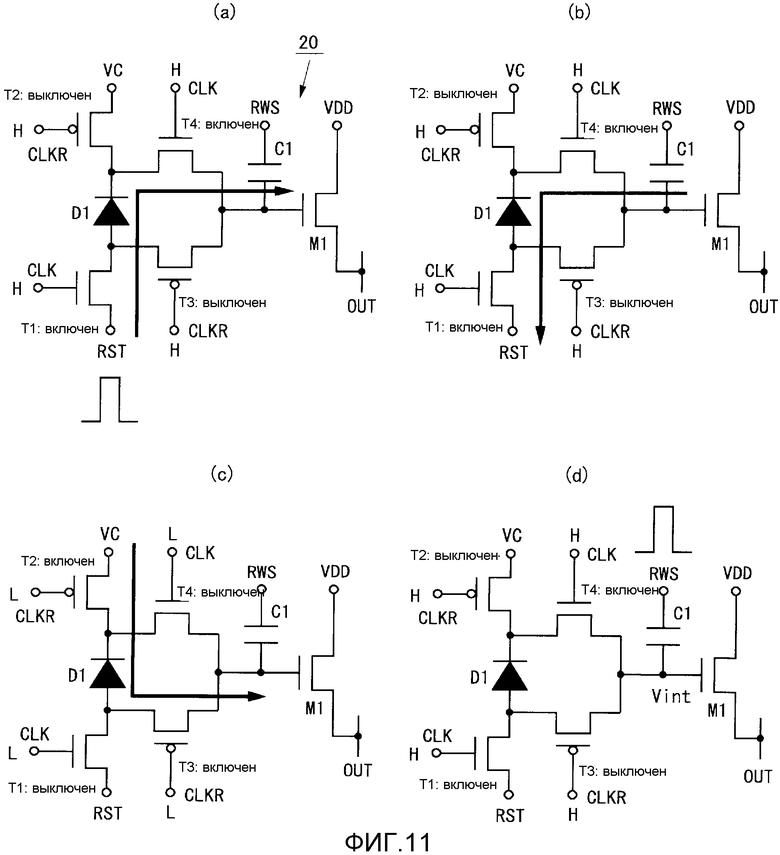

Фиг. 11 является схемой, показывающей операции пикселной схемы датчика, показанной на фиг. 10.

Фиг. 12 является схемой форм сигналов пикселной схемы датчика, показанной на фиг. 10.

Фиг. 13 является принципиальной схемой пикселной схемы датчика согласно третьему варианту осуществления настоящего изобретения.

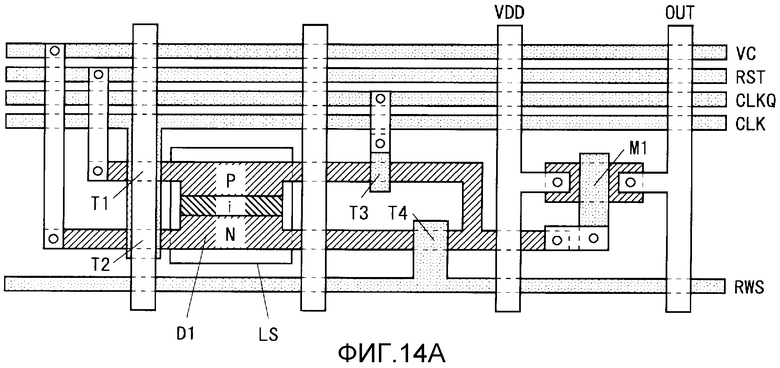

Фиг. 14A является схемой компоновки пикселной схемы датчика, показанной на фиг. 13.

Фиг. 14B является другой схемой компоновки пикселной схемы датчика, показанной на фиг. 13.

Фиг. 15 является схемой, показывающей операции пикселной схемы датчика, показанной на фиг. 13.

Фиг. 16 является схемой форм сигналов пикселной схемы датчика, показанной на фиг. 13.

Фиг. 17A является принципиальной схемой пикселной схемы датчиков согласно первому примеру модификации первого варианта осуществления.

Фиг. 17B является принципиальной схемой пикселной схемы датчика согласно второму примеру модификации первого варианта осуществления.

Фиг. 17C является принципиальной схемой пикселной схемы датчиков согласно третьему примеру модификации первого варианта осуществления.

Фиг. 17D является принципиальной схемой пикселной схемы датчика согласно четвертому примеру модификации первого варианта осуществления.

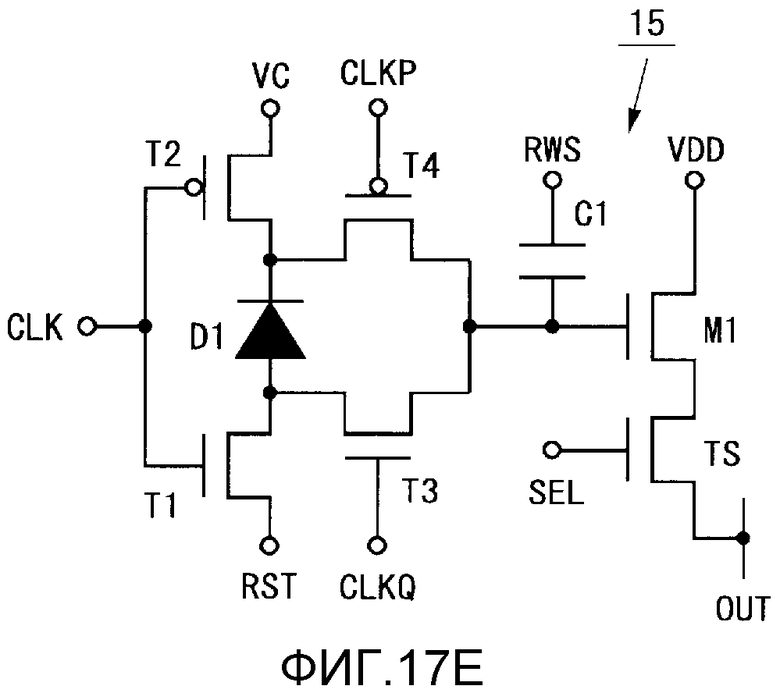

Фиг. 17E является принципиальной схемой пикселной схемы датчика согласно пятому примеру модификации первого варианта осуществления.

Фиг. 17F является принципиальной схемой пикселной схемы датчика согласно шестому примеру модификации первого варианта осуществления.

Фиг. 17G является принципиальной схемой пикселной схемы датчика согласно седьмому примеру модификации первого варианта осуществления.

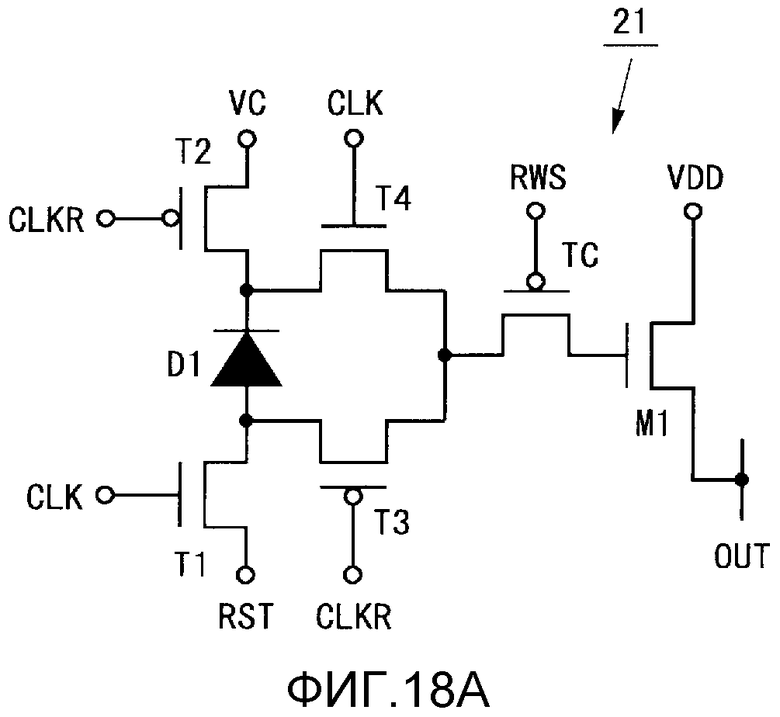

Фиг. 18A является принципиальной схемой пикселной схемы датчиков согласно первому примеру модификации второго варианта осуществления.

Фиг. 18B является принципиальной схемой пикселной схемы датчика согласно второму примеру модификации второго варианта осуществления.

Фиг. 18C является принципиальной схемой пикселной схемы датчика согласно третьему примеру модификации второго варианта осуществления.

Фиг. 18D является принципиальной схемой пикселной схемы датчика согласно четвертому примеру модификации второго варианта осуществления.

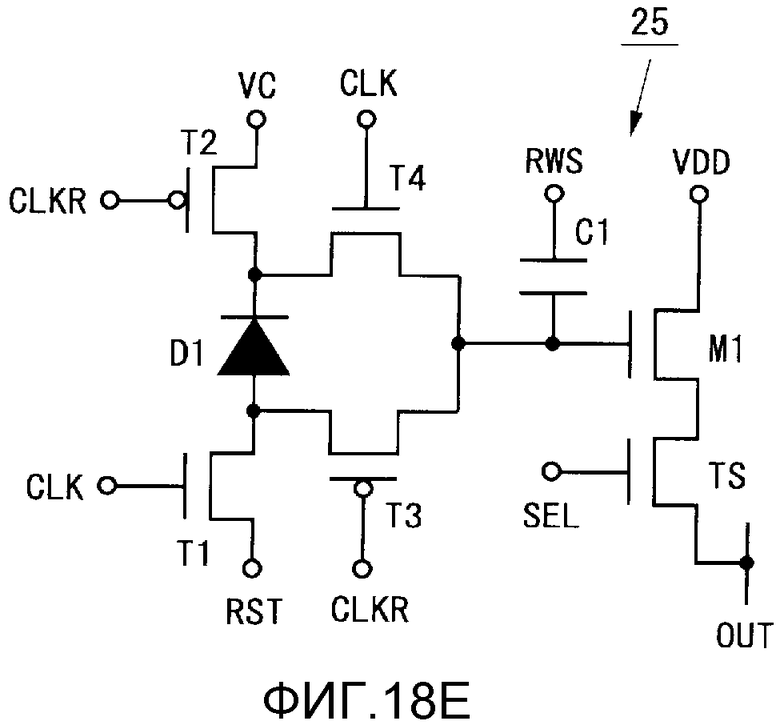

Фиг. 18E является принципиальной схемой пикселной схемы датчика согласно пятому примеру модификации второго варианта осуществления.

Фиг. 18F является принципиальной схемой пикселной схемы датчика согласно шестому примеру модификации второго варианта осуществления.

Фиг. 18G является принципиальной схемой пикселной схемы датчика согласно седьмому примеру модификации второго варианта осуществления.

Фиг. 19A является принципиальной схемой пикселной схемы датчиков согласно первому примеру модификации третьего варианта осуществления.

Фиг. 19B является принципиальной схемой пикселной схемы датчика согласно второму примеру модификации третьего варианта осуществления.

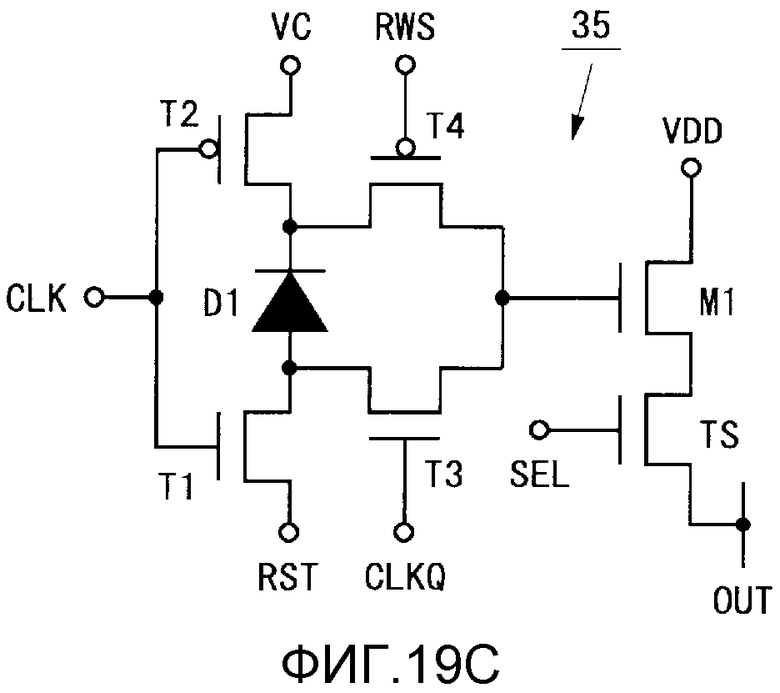

Фиг. 19C является принципиальной схемой пикселной схемы датчика согласно третьему примеру модификации третьего варианта осуществления.

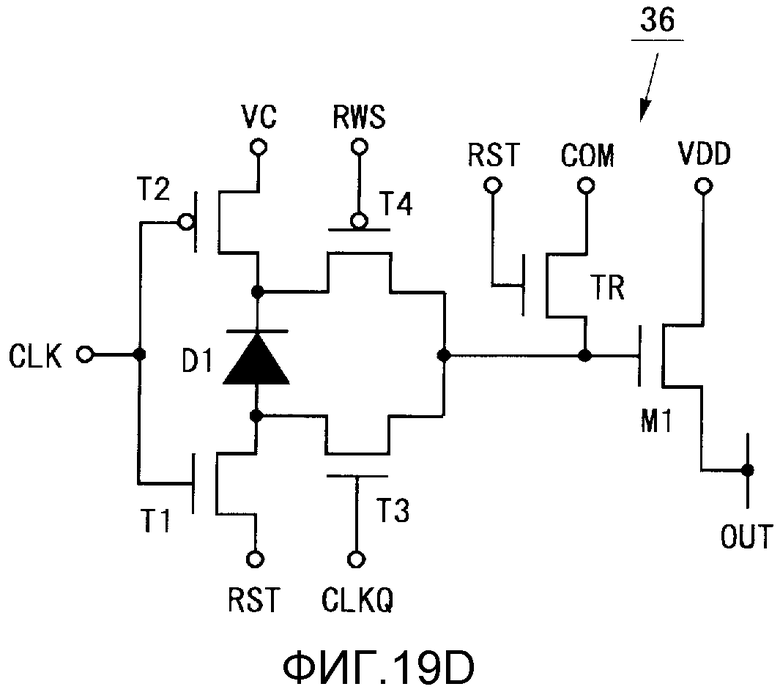

Фиг. 19D является принципиальной схемой пикселной схемы датчика согласно четвертому примеру модификации третьего варианта осуществления.

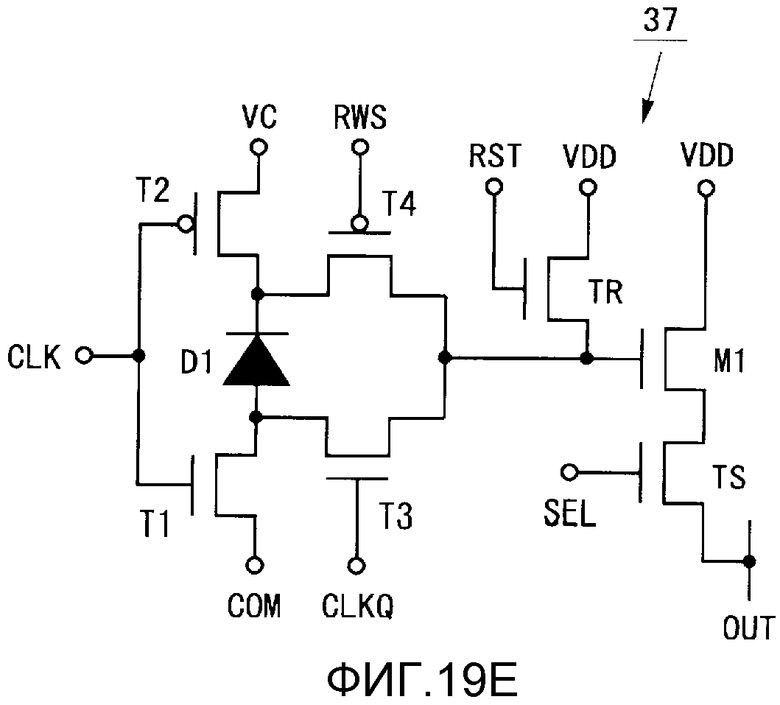

Фиг. 19E является принципиальной схемой пикселной схемы датчика согласно пятому примеру модификации третьего варианта осуществления.

Фиг. 20 является схемой, показывающей времена включения и выключения задней подсветки, а также времена сброса и считывания светоприемных элементов в традиционном устройстве ввода-вывода.

Фиг. 21 является принципиальной схемой единичной светоприемной секции, включенной в традиционное твердотельное устройство формирования изображений.

ОПТИМАЛЬНЫЕ РЕЖИМЫ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Фиг. 1 является блок-схемой, показывающей конфигурацию дисплейного устройства согласно одному варианту осуществления настоящего изобретения. Как показано на фиг. 1, дисплейное устройство включает в себя схему 1 управления дисплея, дисплейную панель 2 и заднюю подсветку 3. Дисплейная панель 2 включает в себя пикселную область 4, схему 5 драйвера затвора, схему 6 драйвера истока и схему 7 драйвера строки датчиков. Пикселная область 4 включает в себя множество пикселных схем 8 дисплея и множество пикселных схем 9 датчиков. Это дисплейное устройство имеет функцию отображения изображения на дисплейной панели 2 и функцию считывания света, падающего на дисплейную панель 2. В следующем описании x представляет целое число не меньше 2, y представляет кратное 3, m и n представляют четное число и частота кадров дисплейного устройства составляет 60 кадров в секунду.

В дисплейное устройство, показанное на фиг. 1, видеосигнал Vin и синхронизирующий управляющий сигнал Cin подаются извне. На основе этих сигналов схема 1 управления дисплея выводит видеосигнал VS и управляющие сигналы CSg, CSs и CSr на дисплейную панель 2 и выводит управляющий сигнал CSb в заднюю подсветку 3. Видеосигнал VS может быть идентичным видеосигналу Vin или может быть сигналом, соответствующим видеосигналу Vin, подвергнутому обработке сигналов.

Задняя подсветка 3 является источником света для излучения света в дисплейную панель 2. Более конкретно задняя подсветка 3 предоставляется на задней стороне дисплейной панели 2 и излучает свет в заднюю часть дисплейной панели 2. Задняя подсветка 3 включается, когда управляющий сигнал CSb имеет высокий логический уровень, и выключается, когда управляющий сигнал CSb имеет низкий логический уровень.

В пикселной области 4 дисплейной панели 2 (x*y) пикселных схем 8 дисплея и (n*m/2) пикселных схем 9 датчиков размещаются в двумерной матрице, соответственно. Более конкретно x линий GL1-GLx затвора и y линий SL1-SLy истока формируются в пикселной области 4. Линии GL1-GLx затвора размещаются параллельно друг другу, и линии SL1-SLy истока размещаются параллельно друг другу так, что они являются ортогональными к линиям GL1-GLx затвора. (X*y) пикселных схем 8 дисплея размещаются около пересечений между линиями GL1-GLx затвора и линиями SL1-SLy истока. Каждая пикселная схема 8 дисплея подключается к одной линии GL затвора и одной линии SL истока. Пикселные схемы 8 дисплея классифицируются на пикселные схемы для красного изображения, пикселные схемы для зеленого отображения и пикселные схемы для синего отображения. Эти три типа пикселных схем 8 дисплея размещаются и совмещаются в направлении прохождения линий GL1-GLx затвора так, что они формируют один цветной пиксел.

В пикселной области 4 n линий CLK1-CLKn синхросигнала, n линий RST1-RSTn сброса и n линий RWS1-RWSn считывания формируются параллельно линиям GL1-GLx затвора. Кроме того, в пикселной области 4 другие сигнальные линии и линии электропитания (не показаны) формируются параллельно линиям GL1-GLx затвора. В случае, если считывание из пикселных схем 9 датчиков выполняется, m линий истока, выбранных из числа линий SL1-SLy истока, используются в качестве линий VDD1-VDDm электропитания, и другие m линий истока используются в качестве выходных линий OUT1-OUTm.

Фиг. 2 является схемой, показывающей компоновку пикселных схем 9 датчиков в пикселной области 4. Как показано на фиг. 2, (n*m/2) пикселных схем 9 датчиков размещаются около пересечений между линиями CLK1-CLKn-1 синхросигнала с нечетным номером и выходными линиями OUT1-OUTm-1 с нечетным номером и около пересечений между линиями CLK2-CLKn синхросигнала с четным номером и выходными линиями OUT2-OUTm с четным номером.

Схема 5 драйвера затвора возбуждает линии GL1-GLx затвора. Более конкретно, на основе управляющего сигнала CSg схема 5 драйвера затвора выбирает одну линию затвора последовательно из числа линий GL1-GLx затвора, прикладывает потенциал высокого логического уровня к выбранной линии затвора и прикладывает потенциал низкого логического уровня к оставшимся линиям затвора. Таким образом, y пикселных схем 8 дисплея, подключенных к выбранной линии затвора, выбираются совместно.

Схема 6 драйвера истока возбуждает линии SL1-SLy истока. Более конкретно, на основе управляющего сигнала CSs схема 6 драйвера истока прикладывает потенциалы, соответствующие видеосигналу VS, к линиям SL1-SLy истока. Здесь схема 6 драйвера истока может выполнять последовательное возбуждение по линиям или может выполнять точечное последовательное возбуждение. Потенциалы, прикладываемые к линиям SL1-SLy истока, записываются в y пикселных схем 8 дисплея, выбранных посредством схемы 5 драйвера затвора. Как описано выше, можно записывать потенциалы, соответствующие видеосигналу VS, во все пикселные схемы 8 дисплея посредством использования схемы 5 драйвера затвора и схемы 6 драйвера истока, тем самым отображая требуемое изображение на дисплейной панели 2.

Схема 7 драйвера строки датчиков возбуждает линии CLK1-CLKn синхросигнала, линии RST1-RSTn сброса, линии RWS1-RWSn считывания и т.п. Более конкретно, на основе управляющего сигнала CSr схема 7 драйвера строки датчиков прикладывает потенциал высокого логического уровня к линиям CLK1-CLKn синхросигнала, когда задняя подсветка 3 включается и, прикладывает потенциал низкого логического уровня к линиям CLK1-CLKn синхросигнала, когда задняя подсветка 3 выключается. Кроме того, на основе управляющего сигнала CSr, схема 7 драйвера строки датчиков выбирает одну линию сброса последовательно из числа линий RST1-RSTn сброса, прикладывает потенциал высокого логического уровня для сброса к выбранной линии сброса и прикладывает потенциал низкого логического уровня к оставшимся линиям сброса. Таким образом, (m/2) пикселных схем 9 датчиков, подключенных к выбранной линии сброса, сбрасываются совместно.

Кроме того, на основе управляющего сигнала CSr схема 7 драйвера строки датчиков выбирает одну линию считывания последовательно из числа линий RWS1-RWSn считывания, прикладывает потенциал высокого логического уровня для считывания к выбранной линии считывания и прикладывает потенциал низкого логического уровня к оставшимся линиям считывания. Таким образом, (m/2) пикселных схем 9 датчиков, подключенных к выбранной линии считывания, переходят в считываемое состояние совместно. Здесь схема 6 драйвера истока прикладывает потенциал высокого логического уровня к линиям VDD1-VDDm электропитания. Таким образом, (m/2) пикселных схем 9 датчиков в считываемом состоянии выводят сигналы, соответствующие количествам света, считываемым в соответствующих пикселных схемах 9 датчиков (в дальнейшем в этом документе называемые сигналами датчиков), в выходные линии OUT1-OUTm.

Схема 6 драйвера истока усиливает сигналы датчиков, выводимые у выходные линии OUT1-OUTm, и выводит усиленные сигналы последовательно в качестве вывода Sout датчика за пределы дисплейной панели 2. Как описано выше, посредством считывания сигналов датчиков из всех пикселных схем 9 датчиков посредством использования схемы 6 драйвера истока и схемы 7 драйвера строки датчиков можно считывать свет, падающий на дисплейную панель 2. Дисплейное устройство, показанное на фиг. 1, выполняет следующее последовательное возбуждение, чтобы считывать свет, падающий на дисплейную панель 2.

Фиг. 3 является схемой, показывающей времена включения и выключения задней подсветки 3, а также времена сброса и считывания пикселных схем 9 датчиков. Как показано на фиг. 3, задняя подсветка 3 включается многократно и выключается многократно за период в один кадр. В последующем описании предполагается, что задняя подсветка 3 включается на четыре раза и выключается четыре раза за период в один кадр. Период включения имеет одинаковую длительность с периодом выключения. Сброс для пикселных схем 9 датчиков выполняется последовательно по линиям за период в один кадр (стрелка со сплошной линией). Считывание из пикселных схем 9 датчиков выполняется после истечения практически периода в один кадр от сброса (более конкретно после истечения времени, которое немного меньше периода в один кадр) (стрелка с пунктирной линией).

Фиг. 4 является схемой форм сигналов дисплейной панели 2. Как показано на фиг. 4, потенциалы в линиях GL1-GLx затвора последовательно переключаются к высокому логическому уровню однократно в течение предварительно определенного времени за период в один кадр. Потенциалы в линиях CLK1-CLKn синхросигнала изменяются одновременно и переключаются к высокому логическому уровню и низкому логическому уровню четыре раза, соответственно, за период в один кадр. Относительно потенциалов в линиях CLK1-CLKn синхросигнала период высокого логического уровня имеет одинаковую длительность с периодом низкого логического уровня. Потенциалы в линиях RST1-RSTn сброса последовательно переключаются к высокому логическому уровню один раз в течение предварительно определенного времени за период в один кадр. Потенциалы в линиях RWS1-RWSn считывания также последовательно переключаются к высокому логическому уровню один раз в течение предварительно определенного времени за период в один кадр. Сразу после того, как потенциал в линии RWS1 считывания изменяется от высокого логического уровня к низкому логическому уровню, потенциал в линии RST1 сброса изменяется от низкого логического уровня к высокому логическому уровню. Аналогичное справедливо для потенциалов в линиях RST2-RSTn сброса. Следовательно, период, в течение которого пикселная схема 9 датчика считывает свет (период от сброса до считывания: A0, показанный на фиг. 3), становится почти равным по длительности периоду в один кадр.

Фиг. 5 является схемой, показывающей схематичную конфигурацию пикселной схемы 9 датчика. Как показано на фиг. 5, пикселная схема 9 датчика включает в себя один фотодиод D1 и один узел ND накопления. Фотодиод D1 извлекает из узла ND накопления заряд, соответствующий количеству света, который должен падать, в то время как задняя подсветка 3 включается, и добавляет в узел ND накопления заряд, соответствующий количеству света, который должен падать, в то время как задняя подсветка 3 выключается. Следовательно, потенциал Vint в узле ND накопления снижается в соответствии с количеством света, который должен падать в течение периода включения задней подсветки 3 (что соответствует (сигнал+шум)), и поднимается в соответствии с количеством света, который должен падать в течение периода выключения задней подсветки 3 (что соответствует шуму). Сигнал датчика, соответствующий разности между двумя типами количеств света, считывается из пикселной схемы 9 датчика.

Следует отметить, что число пикселных схем 9 датчиков, которые должны предоставляться в пикселной области 4, может быть произвольным. Например, (n*m) пикселных схем 9 датчиков могут предоставляться в пикселной области 4. Альтернативно, пикселные схемы 9 датчиков, число которых равно числу цветных пикселов (т.е. (x*y/3)), могут предоставляться в пикселной области 4. Альтернативно, пикселные схемы 9 датчиков, число которых меньше числа цветных пикселов (например, одна из нескольких на одну из нескольких десятков цветных пикселов), могут предоставляться в пикселной области 4.

Как описано выше, дисплейное устройство согласно варианту осуществления настоящего изобретения является дисплейным устройством, в котором множество фотодиодов (оптических датчиков) размещаются в пикселной области 4. Дисплейное устройство включает в себя дисплейную панель 2, которая включает в себя множество пикселных схем 8 дисплея и множество пикселных схем 9 датчиков, и схему 7 драйвера строки датчиков (возбуждающую схему), которая выводит в пикселную схему 9 датчика синхросигналы CLK1-CLKn (управляющие сигналы), каждый из которых указывает, что задняя подсветка включается или задняя подсветка выключается. В дальнейшем в этом документе приводится описание подробностей пикселной схемы 9 датчика, включенной в это дисплейное устройство. В последующем описании, пикселная схема датчика упоминается просто как пикселная схема и сигнал на сигнальной линии обозначается с использованием обозначения сигнальной линии в целях идентификации (например, сигнал в линии CLK синхросигнала упоминается как синхросигнал CLK). Пикселная схема подключается к линии CLK синхросигнала, линии RST сброса, линии RWS считывания, линии VDD электропитания и выходной линии OUT, и в нее подаются потенциал VC и инвертированный сигнал от синхросигнала CLK. Потенциал VC является потенциалом, который выше потенциала высокого логического уровня для сброса.

ПЕРВЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

Фиг. 6 является принципиальной схемой пикселной схемы согласно первому варианту осуществления настоящего изобретения. Пикселная схема 10, показанная на фиг. 6, включает в себя транзисторы T1-T4 и M1, фотодиод D1 и конденсатор C1. Каждый из транзисторов T1, T3 и M1 является TFT (тонкопленочным транзистором) с каналом n-типа, а каждый из транзисторов T2 и T4 является TFT с каналом p-типа. Пикселная схема 10 подключается к трем линиям CLK, CLKP и CLKQ синхросигнала.

Как показано на фиг. 6, затворы транзисторов T1 и T2 подключаются к линии CLK синхросигнала, затвор транзистора T3 подключается к линии CLKQ синхросигнала и затвор транзистора T4 подключается к линии CLKP синхросигнала. В транзисторе T1 исток подключается к линии RST сброса, а сток подключается к аноду фотодиода D1 и стоку транзистора T3. В транзисторе T2 к истоку прикладывается потенциал VC и сток подключается к катоду фотодиода D1 и стоку транзистора T4. Истоки транзисторов T3 и T4 подключаются к затвору транзистора M1. В транзисторе M1 сток подключается к линии VDD электропитания, а исток подключается к выходной линии OUT. Конденсатор C1 предоставляется между затвором транзистора M1 и линией RWS считывания. В пикселной схеме 10 узел, подключенный к затвору транзистора M1, служит в качестве узла накопления, который накапливает заряд, соответствующий количеству считываемого света, и транзистор M1 выступает в качестве считывающего транзистора.

Фиг. 7A является схемой компоновки пикселной схемы 10. Как показано на фиг. 7A, пикселная схема 10 имеет такую конфигурацию, что светоэкранирующая пленка LS, полупроводниковый слой (заштрихованная часть), слой межсоединений затвора (точечная часть) и слой межсоединений истока (белые части) формируются последовательно на стеклянной подложке. Контакт (показан с помощью белого круга) предоставляется в месте, в котором соединяются полупроводниковый слой и слой межсоединений истока, и в месте, в котором соединяются слой межсоединений затвора и слой межсоединений истока. Транзисторы T1-T4 и M1 формируются посредством размещения полупроводникового слоя и слоя межсоединений затвора так, что эти два слоя пересекают друг друга. Фотодиод D1 формируется посредством размещения P-слоя, I-слоя и N-слоя, включенных в полупроводниковый слой, так что эти три слоя совмещаются. Конденсатор C1 формируется посредством размещения полупроводникового слоя и слоя межсоединений затвора так, что эти два слоя перекрываются. Светоэкранирующая пленка LS изготавливается из металла и не допускает падения света, поступающего через заднюю часть стеклянной подложки, на фотодиод D1.

Фиг. 7B является другой схемой компоновки пикселной схемы 10. Согласно компоновке, показанной на фиг. 7B, потенциал VC прикладывается к экрану SH (прозрачному электроду: показан с помощью полужирной пунктирной линии) для покрытия поверхности компоновки, и контакт (показан с помощью черного круга) предоставляется в месте, в котором соединяются экран SH и слой межсоединений истока. Следует отметить, что компоновка пикселных схем 10 может быть изменена в форме, отличной от форм, описанных выше.

Фиг. 8 является схемой, показывающей операции пикселной схемы 10. Как показано на фиг. 8, пикселная схема 10 выполняет (a) сброс, (b) накопление, когда задняя подсветка включается, (c) накопление, когда задняя подсветка выключается, и (d) считывание за период в один кадр. Накопление, когда задняя подсветка включается, и накопление, когда задняя подсветка выключается, выполняется четыре раза, соответственно, за период в один кадр.

Фиг. 9 является схемой форм сигналов пикселной схемы 10. На фиг. 9 BL представляет яркость задней подсветки 3 и Vint представляет потенциал в узле накопления (потенциал затвора в транзисторе M1). Каждый из синхросигналов CLKP и CLKQ является инвертированным сигналом от синхросигнала CLK. Тем не менее, период низкого логического уровня синхросигнала CLKP и период высокого логического уровня синхросигнала CLKQ имеют одинаковую длительность друг с другом и составляют меньше половины цикла синхросигнала CLK. На фиг. 9, период сброса соответствует диапазону от времени t1 до времени t2, период накопления соответствует диапазону от времени t2 до времени t3 и период считывания соответствует диапазону от времени t3 до времени t4.

В период сброса синхросигнал CLK переключается к высокому логическому уровню, синхросигналы CLKP и CLKQ и сигнал RWS считывания переключаются к низкому логическому уровню и сигнал RST сброса переключается к высокому логическому уровню для сброса. Здесь транзисторы T1 и T4 включаются, и транзисторы T2 и T3 выключаются. Соответственно, ток (прямой ток в фотодиоде D1) протекает из линии RST сброса во второй узел накопления через транзистор T1, фотодиод D1 и транзистор T4 (фиг. 8(a)), и потенциал Vint сбрасывается до предварительно определенного уровня.

В период накопления сигнал RST сброса и сигнал RWS считывания переключаются к низкому логическому уровню и синхросигналы CLK, CLKP и CLKQ переключаются к высокому логическому уровню и низкому логическому уровню четыре раза, соответственно. Пока синхросигнал CLK имеет высокий логический уровень и синхросигналы CLKP и CLKQ имеют низкий логический уровень, транзисторы T1 и T4 включаются и транзисторы T2 и T3 выключаются. Здесь, когда свет падает на фотодиод D1, ток (фототок в фотодиоде D1) протекает из узла накопления в линию RST сброса через транзистор T4, фотодиод D1 и транзистор T1 и заряд выходит из узла накопления (фиг. 8(b)). Соответственно, потенциал Vint снижается в соответствии с количеством света, который должен падать, пока синхросигнал CLK имеет высокий логический уровень (период включения задней подсветки 3).

С другой стороны, пока синхросигнал CLK имеет низкий логический уровень и синхросигналы CLKP и CLKQ имеют высокий логический уровень, транзисторы T1 и T4 выключаются и транзисторы T2 и T3 включаются. Здесь, когда свет падает на фотодиод D1, ток (фототок в фотодиоде D1) протекает из провода, имеющего потенциал VC, в узел накопления через транзистор T2, фотодиод D1 и транзистор T3 и заряд добавляется в узел накопления (фиг. 8(c)). Соответственно, потенциал Vint поднимается в соответствии с количеством света, который должен падать, пока синхросигнал CLK имеет низкий логический уровень (период выключения задней подсветки 3).

В период считывания синхросигнал CLK переключается к высокому логическому уровню, синхросигналы CLKP и CLKQ и сигнал RST сброса переключаются к низкому логическому уровню и сигнал RWS считывания переключается к высокому логическому уровню для считывания. Здесь транзисторы T1 и T4 включаются и транзисторы T2 и T3 выключаются. Здесь потенциал Vint поднимается посредством величины, которая в (Cq/Cp) раз (Cp: значение емкости всей пикселной схемы 10, Cq: значение емкости конденсатора C1) превышает величину подъема потенциала в сигнале RWS считывания. Транзистор M1 составляет схему усиления истокового повторителя, имеющую в качестве схемы нагрузки транзистор (не показан), включенный в схему 6 драйвера истока, и возбуждает выходную линию OUT в соответствии с потенциалом Vint (фиг. 8(d)).

Как описано выше, пикселная схема 10 согласно этому варианту осуществления включает в себя один фотодиод D1 (оптический датчик), один узел накопления, который накапливает заряд, соответствующий количеству считываемого света, транзистор M1 (считывающий транзистор), который имеет управляющий контактный вывод, подключенный к узлу накопления, и транзисторы T1-T4 (множество переключающих элементов), которые включаются или выключаются в соответствии с синхросигналом CLK и переключают путь для тока, протекающего через фотодиод D1.

Транзистор T1 предоставляется между линией RST сброса и одним из концов фотодиода D1 и включается, когда задняя подсветка включается. Транзистор T2 предоставляется между проводом, к которому прикладывается предварительно определенный потенциал, VC, и другим концом фотодиода D1 и включается, когда задняя подсветка выключается. Транзистор T3 предоставляется между узлом накопления и одним из концов фотодиода D1 и включается, когда задняя подсветка выключается. Транзистор T4 предоставляется между узлом накопления и другим концом фотодиода D1 и включается, когда задняя подсветка включается. Каждый из транзисторов T1 и T3 является транзистором с каналом n-типа (первого проводящего типа), а каждый из транзисторов T2 и T4 является транзистором с каналом p-типа (второго проводящего типа). Транзисторы T1 и T2 включаются или выключаются в соответствии с синхросигналом CLK (первым управляющим сигналом), транзистор T3 включается или выключается в соответствии с синхросигналом CLKQ (вторым управляющим сигналом) и транзистор T4 включается или выключается в соответствии с синхросигналом CLKP (третьим управляющим сигналом). Каждый из синхросигналов CLKP и CLKQ является инвертированным сигналом от синхросигнала CLK и изменяется во время, которое отличается от времени синхросигнала CLK.

Когда задняя подсветка включается, транзисторы T1 и T4 включаются, путь тока формируется так, что он проходит через оптический датчик и транзисторы T1 и T4, и ток протекает из узла накопления. Когда задняя подсветка выключается, транзисторы T2 и T3 включаются, путь тока формируется так, что он проходит через оптический датчик и транзисторы T2 и T3, и ток протекает в узел накопления. Как описано выше, поскольку ток протекает через узел накопления в обратном направлении, когда задняя подсветка включается и когда задняя подсветка выключается, потенциал в узле накопления изменяется в обратном направлении, когда задняя подсветка включается и когда задняя подсветка выключается. Согласно пикселной схеме 10, следовательно, можно определять разность между количеством света, когда задняя подсветка включается, и затем количеством света, когда задняя подсветка выключается, посредством использования одной пикселной схемы датчика и предоставлять функцию ввода, которая не зависит от окружений освещения.

Кроме того, разность между количествами света определяется посредством использования одной пикселной схемы датчика. Следовательно, по сравнению со случаем отдельного определения двух типов количеств света, можно не допускать насыщения количества света и корректно получать разность между количествами света. Кроме того, по сравнению со случаем последовательного определения двух типов количества света посредством использования одной пикселной схемы датчика, можно уменьшать частоту считывания из пикселных схем датчиков, снижать скорость считывания и уменьшать потребление мощности в устройстве. Кроме того, становится необязательным предоставлять запоминающее устройство, которое требуется в случае определения двух типов количеств света последовательно и используется для сохранения количества света, считываемого сначала. Кроме того, можно увеличивать степень свободы для задания времен включения и выключения задней подсветки, а также времен сброса и считывания пикселных схем датчиков. Кроме того, операция считывания света, когда задняя подсветка включается, и операция считывания света, когда задняя подсветка выключается, выполняются однократно, соответственно, за период в один кадр. Следовательно, можно исключать отклонение между периодом считывания, когда задняя подсветка включается, и периодом считывания, когда задняя подсветка выключается, и не допускать варьирования характеристики следования входному перемещению в соответствии с направлением ввода. Кроме того, посредством получения разности между количествами света посредством использования одной пикселной схемы датчика можно одновременно выполнять температурную компенсацию.

Кроме того, можно корректно управлять периодом существования пути тока и повышать точность обнаружения, поскольку каждый из синхросигналов CLKP и CLKQ изменяется во время, которое отличается от времени синхросигнала CLK. Кроме того, пикселная схема 10 дополнительно включает в себя конденсатор C1, предоставляемый между узлом накопления и линией RWS считывания. Соответственно, посредством прикладывания потенциала высокого логического уровня для считывания к линии RWS считывания, можно изменять потенциал в узле накопления и считывать сигнал, соответствующий количеству считываемого света, из пикселной схемы 10.

ВТОРОЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

Фиг. 10 является принципиальной схемой пикселной схемы согласно второму варианту осуществления настоящего изобретения. Пикселная схема 20, показанная на фиг. 10, включает в себя транзисторы T1-T4 и M1, фотодиод D1 и конденсатор C1. Каждый из транзисторов T1, T4 и M1 является TFT с каналом n-типа, а каждый из транзисторов T2 и T3 является TFT с каналом p-типа. Пикселная схема 20 подключается к двум линиям CLK и CLKR синхросигнала.

Как показано на фиг. 10, затворы транзисторов T1 и T4 подключаются к линии CLK синхросигнала, а затворы транзисторов T2 и T3 подключаются к линии CLKR синхросигнала. В транзисторе T1 исток подключается к линии RST сброса, а сток подключается к аноду фотодиода D1 и истоку транзистора T3. В транзисторе T2 к истоку прикладывается потенциал VC, а сток подключается к катоду фотодиода D1 и истоку транзистора T4. Стоки транзисторов T3 и T4 подключаются к затвору транзистора M1. В транзисторе M1 сток подключается к линии VDD электропитания, а исток подключается к выходной линии OUT. Конденсатор C1 предоставляется между затвором транзистора M1 и линией RWS считывания. В первой пикселной схеме 20 узел, подключенный к затвору транзистора M1, служит в качестве узла накопления и транзистор M1 выступает в качестве считывающего транзистора.

Фиг. 11 является схемой, показывающей операции пикселной схемы 20. Как показано на фиг. 11, пикселная схема 20 выполняет (a) сброс, (b) накопление, когда задняя подсветка включается, (c) накопление, когда задняя подсветка выключается, и (d) считывание за период в один кадр. Накопление, когда задняя подсветка включается, и накопление, когда задняя подсветка выключается, выполняется четыре раза, соответственно, за период в один кадр.

Фиг. 12 является схемой форм сигналов пикселной схемы 20. Как показано на фиг. 12, синхросигнал CLKR включается или выключается аналогично синхросигналу CLK. Тем не менее, период низкого логического уровня синхросигнала CLKR меньше половины цикла синхросигнала CLK. На фиг. 12 период сброса соответствует диапазону от времени t1 до времени t2, период накопления соответствует диапазону от времени t2 до времени t3 и период считывания соответствует диапазону от времени t3 до времени t4.

В период сброса синхросигналы CLK и CLKR переключаются к высокому логическому уровню, сигнал RWS считывания переключается к низкому логическому уровню и сигнал RST сброса переключается к высокому логическому уровню для сброса. Здесь транзисторы T1 и T4 включаются, а транзисторы T2 и T3 выключаются. Соответственно, ток (прямой ток в фотодиоде D1) протекает из линии RST сброса во второй узел накопления через транзистор T1, фотодиод D1 и транзистор T4 (фиг. 11(a)), и потенциал Vint сбрасывается до предварительно определенного уровня.

В период накопления сигнал RST сброса и сигнал RWS считывания переключаются к низкому логическому уровню и синхросигналы CLK и CLKR переключаются к высокому логическому уровню и низкому логическому уровню четыре раза, соответственно. Пока синхросигналы CLK и CLKR имеют высокий логический уровень, транзисторы T1 и T4 включаются, а транзисторы T2 и T3 выключаются. Здесь, когда свет падает на фотодиод D1, ток (фототок в фотодиоде D1) протекает из узла накопления в линию RST сброса через транзистор T4, фотодиод D1 и транзистор T1 и заряд выходит из узла накопления (фиг. 11(b)). Соответственно, потенциал Vint снижается в соответствии с количеством света, который должен падать, пока синхросигнал CLK имеет высокий логический уровень (период включения задней подсветки 3).

С другой стороны, пока синхросигналы CLK и CLKR имеют низкий логический уровень, транзисторы T1 и T4 выключаются, а транзисторы T2 и T3 включаются. Здесь, когда свет падает на фотодиод D1, ток (фототок в фотодиоде D1) протекает из сигнальной линии, имеющей потенциал VC, в узел накопления через транзистор T2, фотодиод D1 и транзистор T3 и заряд добавляется в узел накопления (фиг. 11(c)). Соответственно, потенциал Vint поднимается в соответствии с количеством света, который должен падать, пока синхросигнал CLK имеет низкий логический уровень (период выключения задней подсветки 3).

В период считывания синхросигналы CLK и CLKR переключаются к высокому логическому уровню, сигнал RST сброса переключается к низкому логическому уровню и сигнал RWS считывания переключается к высокому логическому уровню для считывания. Здесь транзисторы T1 и T4 включаются, а транзисторы T2 и T3 выключаются. Здесь потенциал Vint поднимается посредством величины, которая в (Cq/Cp) раз (Cp: значение емкости всей пикселной схемы 20, Cq: значение емкости конденсатора C1) превышает величину подъема потенциала в сигнале RWS считывания. Транзистор M1 составляет схему усиления истокового повторителя и возбуждает выходную линию OUT в соответствии с потенциалом Vint (фиг. 11(d)).

Как описано выше, аналогично пикселной схеме 10 согласно первому варианту осуществления пикселная схема 20 согласно этому варианту осуществления включает в себя один фотодиод D1, один узел накопления, транзистор M1 и транзисторы T1-T4. В пикселной схеме 20 каждый из транзисторов T1 и T4 является транзистором с каналом n-типа (первого проводящего типа), а каждый из транзисторов T2 и T3 является транзистором с каналом p-типа (второго проводящего типа). Транзисторы T1 и T4 включаются или выключаются в соответствии с синхросигналом CLK (первым управляющим сигналом), и транзисторы T2 и T3 включаются или выключаются в соответствии с синхросигналом CLKR (вторым управляющим сигналом). Синхросигнал CLKR изменяется в другое время и в идентичном направлении с синхросигналом CLK.

В пикселной схеме 20 аналогично пикселной схеме 10 согласно первому варианту осуществления, ток протекает в узел накопления в обратном направлении, когда задняя подсветка включается и когда задняя подсветка выключается, и потенциал в узле накопления изменяется в обратном направлении, когда задняя подсветка включается и когда задняя подсветка выключается. Согласно пикселной схеме 20, следовательно, можно определять разность между количеством света, когда задняя подсветка включается, и количеством света, когда задняя подсветка выключается, посредством использования одной пикселной схемы датчика и давать функцию ввода, которая не зависит от окружений освещения. Таким образом, можно достигать эффектов, которые являются аналогичными эффектам в первом варианте осуществления. Кроме того, можно сокращать число управляющих сигналов, увеличивать светосилу и повышать чувствительность пикселной схемы датчика посредством использования этих двух синхросигналов CLK и CLKR в качестве управляющих сигналов.

ТРЕТИЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

Фиг. 13 является принципиальной схемой пикселной схемы согласно третьему варианту осуществления настоящего изобретения. Пикселная схема 30, показанная на фиг. 13, включает в себя транзисторы T1-T4 и M1 и фотодиод D1. Каждый из транзисторов T1, T3 и M1 является TFT с каналом n-типа, а каждый из транзисторов T2 и T4 является TFT с каналом p-типа. Пикселная схема 30 подключается к двум линиям CLK и CLKQ синхросигнала.

Как показано на фиг. 13, затворы транзисторов T1 и T2 подключаются к линии CLK синхросигнала, затвор транзистора T3 подключается к линии CLKQ синхросигнала и затвор транзистора T4 подключается к линии RWS считывания. В транзисторе T1 исток подключается к линии RST сброса, а сток подключается к аноду фотодиода D1 и стоку транзистора T3. В транзисторе T2 к истоку прикладывается потенциал VC и сток подключается к катоду фотодиода D1 и стоку транзистора T4. Истоки транзисторов T3 и T4 подключаются к затвору транзистора M1. В транзисторе M1 сток подключается к линии VDD электропитания, а исток подключается к выходной линии OUT. В первой пикселной схеме 30 узел, подключенный к затвору транзистора M1, служит в качестве узла накопления и транзистор M1 выступает в качестве считывающего транзистора. Транзистор T4 усиливает потенциал в узле накопления, когда к его затвору прикладывается потенциал высокого логического уровня для считывания.

Фиг. 14A и 14B являются схемами компоновки пикселной схемы 30. Описание относительно этих чертежей является аналогичным описанию в первом варианте осуществления. Согласно компоновке, показанной на фиг. 14B, потенциал VC прикладывается к экрану SH для покрытия поверхности компоновки.

Фиг. 15 является схемой, показывающей операции пикселной схемы 30. Как показано на фиг. 15, пикселная схема 30 выполняет (a) сброс, (b) накопление, когда задняя подсветка включается, (c) накопление, когда задняя подсветка выключается, и (d) считывание за период в один кадр. Накопление, когда задняя подсветка включается, и накопление, когда задняя подсветка выключается, выполняется четыре раза, соответственно, за период в один кадр.

Фиг. 16 является схемой форм сигналов пикселной схемы 30. Как показано на фиг. 16, синхросигнал CLKQ является инвертированным сигналом от синхросигнала CLK. Кроме того, в период накопления сигнал RWS считывания является инвертированным сигналом от синхросигнала CLK. Тем не менее, период высокого логического уровня синхросигнала CLKQ и период низкого логического уровня сигнала RWS считывания в период накопления имеют одинаковую длительность друг с другом и составляют меньше половины цикла синхросигнала CLK. На фиг. 16 период сброса соответствует диапазону от времени t1 до времени t2, период накопления соответствует диапазону от времени t2 до времени t3 и период считывания соответствует диапазону от времени t3 до времени t4.

В период сброса синхросигнал CLK переключается к высокому логическому уровню, синхросигнал CLKQ и сигнал RWS считывания переключаются к низкому логическому уровню и сигнал RST сброса переключается к высокому логическому уровню для сброса. Здесь транзисторы T1 и T4 включаются, а транзисторы T2 и T3 выключаются. Соответственно, ток (прямой ток в фотодиоде D1) протекает из линии RST сброса во второй узел накопления через транзистор T1, фотодиод D1 и транзистор T4 (фиг. 15(a)), и потенциал Vint сбрасывается до предварительно определенного уровня.

В период накопления сигнал RST сброса переключается к низкому логическому уровню и синхросигналы CLK и CLKQ и сигнал RWS считывания переключаются к высокому логическому уровню и низкому логическому уровню четыре раза, соответственно. Пока синхросигнал CLK имеет высокий логический уровень и синхросигнал CLKQ и сигнал RWS считывания имеют низкий логический уровень, транзисторы T1 и T4 включаются, а транзисторы T2 и T3 выключаются. Здесь, когда свет падает на фотодиод D1, ток (фототок в фотодиоде D1) протекает из узла накопления в линию RST сброса через транзистор T4, фотодиод D1 и транзистор T1 и заряд выходит из узла накопления (фиг. 15(b)). Соответственно, потенциал Vint снижается в соответствии с количеством света, который должен падать, пока синхросигнал CLK имеет высокий логический уровень (период включения задней подсветки 3).

С другой стороны, пока синхросигнал CLK имеет низкий логический уровень и синхросигнал CLKQ и сигнал RWS считывания имеют высокий логический уровень, транзисторы T1 и T4 выключаются, а транзисторы T2 и T3 включаются. Здесь, когда свет падает на фотодиод D1, ток (фототок в фотодиоде D1) протекает из сигнальной линии, имеющей потенциал VC, в узел накопления через транзистор T2, фотодиод D1 и транзистор T3 и заряд добавляется в узел накопления (фиг. 15(c)). Соответственно, потенциал Vint поднимается в соответствии с количеством света, который должен падать, пока синхросигнал CLK имеет низкий логический уровень (период выключения задней подсветки 3).

В период считывания синхросигнал CLK переключается к высокому логическому уровню, синхросигнал CLKQ и сигнал RST сброса переключаются к низкому логическому уровню и сигнал RWS считывания переключается к высокому логическому уровню для считывания. Здесь транзисторы T1 и T4 включаются, а транзисторы T2 и T3 выключаются. Транзистор T4 усиливает потенциал Vint, когда к его затвору прикладывается потенциал высокого логического уровня для считывания. Соответственно, потенциал Vint поднимается посредством величины, которая в (Cq/Cp) раз (Cp: значение емкости всей пикселной схемы 30, Cq: значение емкости конденсатора C1) превышает величину подъема потенциала в сигнале RWS считывания. Транзистор M1 составляет схему усиления истокового повторителя и возбуждает выходную линию OUT в соответствии с потенциалом Vint (фиг. 15(d)).

Как описано выше, аналогично пикселной схеме 10 согласно первому варианту осуществления, пикселная схема 30 согласно этому варианту осуществления включает в себя один фотодиод D1, один узел накопления, транзистор M1 и транзисторы T1-T4. Эти составляющие элементы имеют одинаковые характеристики и формы соединения с пикселной схемой 10 согласно первому варианту осуществления. Соответственно, можно достигать эффектов, которые являются одинаковыми с эффектами в первом варианте осуществления.

Кроме того, в пикселной схеме 30, когда потенциал для считывания прикладывается к затвору транзистора T4, потенциал в узле накопления (потенциал затвора в транзисторе M1) усиливается. Таким образом, можно повышать чувствительность пикселной схемы датчика.

ПРИМЕРЫ МОДИФИКАЦИЙ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Соответствующие варианты осуществления настоящего изобретения могут использовать следующие примеры модификаций. Фиг. 17A-17G являются принципиальными схемами пикселных схем согласно первому-седьмому примерам модификаций первого варианта осуществления. Как показано на фиг. 17A-17G, пикселные схемы 11-17 осуществляются таким образом, что пикселная схема 10 согласно первому варианту осуществления подвергается следующим модификациям.

Пикселная схема 11, показанная на фиг. 17A, соответствует пикселной схеме 10, в которой конденсатор C1 заменяется транзистором TC, который является TFT с каналом p-типа. Относительно пикселной схемы 11, в транзисторе TC, один из проводящих контактных выводов подключается к истокам транзисторов T3 и T4, другой проводящий контактный вывод подключается к затвору транзистора M1 и затвор подключается к линии RWS считывания. Когда высокий логический уровень для считывания прикладывается к линии RWS считывания, транзистор TC, имеющий форму подключения, описанную выше, вызывает большее изменение потенциала в узле накопления по сравнению с исходной пикселной схемой. Соответственно, можно усиливать разность между потенциалом в узле накопления в случае, если падающий свет является сильным, и потенциалом в узле накопления в случае, если падающий свет является слабым, тем самым повышая чувствительность пикселной схемы 11. Пикселная схема 21, показанная на фиг. 18A, осуществляется таким образом, что аналогичные модификации выполняются для второго варианта осуществления.

Пикселная схема 12, показанная на фиг. 17B, соответствует пикселной схеме 10, в которой фотодиод D1 заменяется фототранзистором TD, а транзисторы T2 и T4 заменяются транзисторами T7 и T8, которые являются TFT с каналом n-типа. Относительно пикселной схемы 12, в транзисторе T7 к стоку прикладывается потенциал VC и исток подключается к катоду фототранзистора TD и истоку транзистора T8. Сток транзистора T8 подключается к затвору транзистора M1 в сочетании с истоком транзистора T3. Затвор транзистора T7 подключается к линии CLKB синхросигнала для распространения инвертированного сигнала от синхросигнала CLK. Затвор транзистора T8 подключается к линии CLKPB синхросигнала для распространения инвертированного сигнала от синхросигнала CLKP. Таким образом, все транзисторы, включенные в пикселную схему 12, имеют канал n-типа. Соответственно, можно изготавливать пикселную схему 12 посредством использования одноканального процесса, допускающего изготовление только транзисторов с каналом n-типа. Пикселная схема 22, показанная на фиг. 18B, и пикселная схема 32, показанная на фиг. 19A, осуществляются таким образом, что аналогичные модификации выполняются для второго и третьего вариантов осуществления.

Пикселная схема 13, показанная на фиг. 17C, соответствует пикселной схеме 10, в которой фотодиод D1 подключается наоборот. В пикселную схему 13 подается сигнал RST сброса, который имеет высокий логический уровень в нормальном состоянии и переключается к низкому логическому уровню для сброса во время сброса и потенциалу VC низкого логического уровня, который ниже потенциала низкого логического уровня для сброса. Катод фотодиода D1 подключается к истокам транзисторов T1 и T3, и анод фотодиода D1 подключается к истокам транзисторов T2 и T4. Таким образом, можно осуществлять множество пикселных схем. Пикселная схема 23, показанная на фиг. 18C, и пикселная схема 33, показанная на фиг. 19B, осуществляются таким образом, что аналогичные модификации выполняются для второго и третьего вариантов осуществления.

Пикселная схема 14, показанная на фиг. 17D, соответствует пикселной схеме 10, в которой фотодиод D1 подключается наоборот и из которой конденсатор C1 исключен. В пикселную схему 14 подается сигнал RST сброса и потенциал VC аналогично пикселной схеме 13. Тем не менее, сигнал RST сброса переключается к высокому логическому уровню для считывания во время считывания. Когда сигнал RST сброса переключается к высокому логическому уровню для считывания, потенциал в узле накопления (потенциал затвора в транзисторе M1) поднимается, и ток, соответствующий потенциалу узла накопления, протекает в транзистор M1. Как описано выше, пикселная схема 14 не включает в себя конденсатор C1. Соответственно, можно увеличивать светосилу посредством исключения конденсатора C1 и повышать чувствительность пикселной схемы. Пикселная схема 24, показанная на фиг. 18D, осуществляется таким образом, что аналогичные модификации выполняются для второго варианта осуществления.

Пикселная схема 15, показанная на фиг. 17E, соответствует пикселной схеме 10, к которой добавляется транзистор TS. Транзистор TS является TFT с каналом n-типа и выступает в качестве переключающего элемента для выбора. Относительно пикселной схемы 15, исток транзистора M1 подключается к стоку транзистора TS. В транзисторе TS исток подключается к выходной линии OUT, а затвор подключается к линии SEL выбора. Сигнал SEL выбора переключается к высокому логическому уровню во время считывания из пикселной схемы 15. Таким образом, можно осуществлять множество пикселных схем. Пикселная схема 25, показанная на фиг. 18E, и пикселная схема 35, показанная на фиг. 19C, осуществляются таким образом, что аналогичные модификации выполняются для второго и третьего вариантов осуществления.

Пикселная схема 16, показанная на фиг. 17F, соответствует пикселной схеме 10, к которой добавляется транзистор TR. Транзистор TR является TFT с каналом n-типа и выступает в качестве переключающего элемента для сброса. Относительно первой пикселной схемы 16, в транзисторе TR к стоку прикладывается потенциал COM низкого логического уровня, сток подключается к затвору транзистора M1, а затвор подключается к линии RST сброса. Кроме того, к истоку транзистора T1 прикладывается потенциал COM низкого логического уровня. Таким образом, можно осуществлять множество пикселных схем. Пикселная схема 26, показанная на фиг. 18F, и пикселная схема 36, показанная на фиг. 19D, осуществляются таким образом, что аналогичные модификации выполняются для второго и третьего вариантов осуществления.

Пикселная схема 17, показанная на фиг. 17G, соответствует пикселной схеме 10, к которой добавляются транзисторы TS и TR, описанные выше. Формы соединения транзисторов TS и TR являются одинаковыми с пикселными схемами 15 и 16. Таким образом, можно осуществлять множество пикселных схем. Пикселная схема 27, показанная на фиг. 18G, и пикселная схема 37, показанная на фиг. 19E, осуществляются таким образом, что аналогичные модификации выполняются для второго и третьего вариантов осуществления.

Кроме того, первый-третий варианты осуществления могут использовать различные примеры модификаций таким образом, что модификации, описанные выше, комбинируются произвольно без нарушения своих свойств.

Как описано выше, в дисплейных устройствах согласно вариантам осуществления настоящего изобретения и примерам модификаций вариантов осуществления можно определять разность между количеством света, когда задняя подсветка включается, и количеством света, когда задняя подсветка выключается, посредством использования пикселной схемы датчика, включающей в себя один оптический датчик, один узел накопления, транзистор для считывания и множество переключающих элементов. Следовательно, можно разрешать традиционные проблемы и предоставлять функцию ввода, которая не зависит от окружений освещения.

Следует отметить, что тип источника света, который должен предоставляться в дисплейном устройстве, не ограничен конкретным образом в настоящем изобретении. Соответственно, например, задняя подсветка в диапазоне видимого света, которая должна предоставляться для отображения, может быть включена и выключена многократно, соответственно, за период в один кадр. Альтернативно, задняя подсветка в диапазоне инфракрасного излучения для считывания света может предоставляться отдельно от задней подсветки в диапазоне видимого света для отображения на дисплейном устройстве. В таком дисплейном устройстве задняя подсветка в диапазоне видимого света может быть всегда включена, и только задняя подсветка в диапазоне инфракрасного излучения может быть включена и выключена многократно, соответственно, за период в один кадр.

ПРОМЫШЛЕННАЯ ПРИМЕНИМОСТЬ

Дисплейное устройство согласно настоящему изобретению отличается наличием функции ввода, которая не зависит от окружений освещения, и, следовательно, является применимой к различным дисплейным устройствам, в которых множество оптических датчиков предоставляются на дисплейной панели.

ПОЯСНЕНИЕ ССЫЛОЧНЫХ ПОЗИЦИЙ

1 - схема управления дисплея

2 - дисплейная панель

3 - задняя подсветка

4 - пикселная область

5 - схема драйвера затвора

6 - схема драйвера истока

7 - схема драйвера строки датчиков

8 - пикселная схема дисплея

9 - пикселная схема датчика

10-17, 20-27, 30, 32, 33, 35-37 - пикселная схема

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2473937C2 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2457550C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2507605C1 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2451983C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2510931C2 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО И СПОСОБ ДЛЯ ВОЗБУЖДЕНИЯ ДИСПЛЕЙНОГО УСТРОЙСТВА | 2008 |

|

RU2443071C1 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО И СПОСОБ ДЛЯ ЕГО ВОЗБУЖДЕНИЯ | 2009 |

|

RU2479047C2 |

| ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2449345C1 |

| ПОДЛОЖКА АКТИВНОЙ МАТРИЦЫ, ЖИДКОКРИСТАЛЛИЧЕСКАЯ ПАНЕЛЬ, ЖИДКОКРИСТАЛЛИЧЕСКОЕ ДИСПЛЕЙНОЕ УСТРОЙСТВО, МОДУЛЬ ЖИДКОКРИСТАЛЛИЧЕСКОГО ДИСПЛЕЯ И ТЕЛЕВИЗИОННЫЙ ПРИЕМНИК | 2008 |

|

RU2452989C1 |

| ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ И СПОСОБ ЕГО ВОЗБУЖДЕНИЯ | 2010 |

|

RU2496153C1 |

Изобретение относится к устройствам отображения. Технический результат заключается в обеспечении возможности свободно задавать длительность и интервал относительно периода включения задней подсветки и периода выключения задней подсветки независимо от световых сред. Устройство содержит дисплейную панель, которая включает в себя множество пиксельных схем дисплея и множество пиксельных схем датчиков, возбуждающую схему, которая выводит в пиксельные схемы датчиков управляющий сигнал, включающую в себя один оптический датчик, один узел накопления, накапливающий заряд, соответствующий количеству считываемого света, считывающий транзистор, имеющий управляющий контактный вывод, подключенный к узлу накопления, множество переключающих элементов, которые включаются или выключаются в соответствии с управляющим сигналом и переключают путь для тока, протекающего через оптический датчик, при этом пиксельная схема датчика сконфигурирована так, что в соответствии с управляющим сигналом ток, протекающий через оптический датчик, протекает в предварительно определенном направлении относительно узла накопления, когда источник света включается, и протекает в обратном направлении относительно узла накопления, когда источник света выключается. 2 н. и 6 з.п. ф-лы, 39 ил.

1. Дисплейное устройство, в котором множество оптических датчиков размещены в пикселной области, причем дисплейное устройство содержит:

- дисплейную панель, которая включает в себя множество пикселных схем дисплея и множество пикселных схем датчиков; и

- возбуждающую схему, которая выводит в пикселные схемы датчиков управляющий сигнал, указывающий, что источник света включается или источник света выключается, при этом:

- пикселная схема датчика включает в себя:

- один оптический датчик;

- один узел накопления, накапливающий заряд, соответствующий количеству считываемого света;

- считывающий транзистор, имеющий управляющий контактный вывод, подключенный к узлу накопления; и

- множество переключающих элементов, которые включаются или выключаются в соответствии с управляющим сигналом и переключают путь для тока, протекающего через оптический датчик, и

- пикселная схема датчика сконфигурирована так, что в соответствии с управляющим сигналом ток, протекающий через оптический датчик, протекает в предварительно определенном направлении относительно узла накопления, когда источник света включается, и протекает в обратном направлении относительно узла накопления, когда источник света выключается.

2. Дисплейное устройство по п. 1, в котором:

- пикселная схема датчика включает в себя:

- первый переключающий элемент, который предоставляется между линией сброса и одним из концов оптического датчика и включается, когда источник света включается;

- второй переключающий элемент, который предоставляется между проводом, к которому прикладывается предварительно определенный потенциал, и другим концом оптического датчика и включается, когда источник света выключается;

- третий переключающий элемент, который предоставляется между узлом накопления и одним из концов оптического датчика и включается, когда источник света выключается; и

- четвертый переключающий элемент, который предоставляется между узлом накопления и другим концом оптического датчика и включается, когда источник света включается.

3. Дисплейное устройство по п. 2, в котором:

- каждый из первого и третьего переключающих элементов сконфигурирован с помощью транзистора первого проводящего типа,

- каждый из второго и четвертого переключающих элементов сконфигурирован с помощью транзистора второго проводящего типа,

- первый и второй переключающие элементы включаются или выключаются в соответствии с первым управляющим сигналом,

- третий переключающий элемент включается или выключается в соответствии со вторым управляющим сигналом,

- четвертый переключающий элемент включается или выключается в соответствии с третьим управляющим сигналом и

- каждый из второго и третьего управляющих сигналов является инвертированным сигналом от первого управляющего сигнала и изменяется во время, которое отличается от времени первого управляющего сигнала.

4. Дисплейное устройство по п. 2, в котором:

- каждый из первого и четвертого переключающих элементов сконфигурирован с помощью транзистора первого проводящего типа,

- каждый из второго и третьего переключающих элементов сконфигурирован с помощью транзистора второго проводящего типа,

- первый и четвертый переключающие элементы включаются или выключаются в соответствии с первым управляющим сигналом и

- второй и третий переключающие элементы включаются или выключаются в соответствии со вторым управляющим сигналом, изменяющимся в другое время в идентичном направлении с первым управляющим сигналом.

5. Дисплейное устройство по п. 2, в котором:

- пикселная схема датчика также включает в себя конденсатор, предоставляемый между узлом накопления и линией считывания.

6. Дисплейное устройство по п. 2, в котором:

- четвертый переключающий элемент усиливает потенциал в узле накопления, когда потенциал для считывания прикладывается к его управляющему контактному выводу.

7. Дисплейное устройство по п. 1, в котором:

- возбуждающая схема выводит, в качестве управляющего сигнала, сигнал, указывающий, что источник света включается и источник света выключается многократно, соответственно, за период в один кадр.

8. Пикселная схема датчика, которая должна размещаться в пикселной области дисплейного устройства, причем пикселная схема датчика содержит:

- один оптический датчик;

- один узел накопления, накапливающий заряд, соответствующий количеству считываемого света;

- считывающий транзистор, имеющий управляющий контактный вывод, подключенный к узлу накопления; и

- множество переключающих элементов, которые включаются или выключаются в соответствии с управляющим сигналом, указывающим, что источник света включается или источник света выключается, и переключают путь для тока, протекающего через оптический датчик, при этом:

- пикселная схема датчика сконфигурирована так, что в соответствии с управляющим сигналом ток, протекающий через оптический датчик, протекает в предварительно определенном направлении относительно узла накопления, когда источник света включается, и протекает в обратном направлении относительно узла накопления, когда источник света выключается.

| Колосоуборка | 1923 |

|

SU2009A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| УСТРОЙСТВО И СПОСОБ ОТОБРАЖЕНИЯ ВРЕМЕНИ ИСПОЛЬЗОВАНИЯ ПОДСВЕТКИ ДЛЯ ЖИДКОКРИСТАЛЛИЧЕСКОГО МОНИТОРА | 1999 |

|

RU2163735C2 |

| СЕНСОРНОЕ ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2004 |

|

RU2363991C2 |

| Станок для обработки заготовок метчиков, осей и т.п. деталей малого диаметра | 1939 |

|

SU63073A1 |

Авторы

Даты

2013-12-10—Публикация

2010-06-08—Подача