2420-184876RU/085

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к устройству отображения, оснащенному оптическим датчиком, имеющим фоточувствительный элемент, например, фотодиод или фототранзистор, и, в частности, относится к устройству отображения, оснащенному оптическим датчиком в области пикселей.

УРОВЕНЬ ТЕХНИКИ

Традиционно предлагалось устройство отображения, оснащенное оптическим датчиком, которое снабжено фотоприемными элементами, такими как, например, фотодиоды в его пикселях, и которое в силу этого способно обнаруживать яркость внешней засветки и регистрировать изображение объекта, приближающегося к его панели дисплея.

Такое устройство отображения, оснащенное оптическим датчиком, предполагается использовать в качестве устройства отображения для двусторонней связи или в качестве устройства отображения с функцией сенсорной панели. В случае обычного устройства отображения, оснащенного оптическим датчиком, когда известные компоненты, такие как, например, сигнальные линии и линии сканирования, TFT (тонкопленочные транзисторы) и электроды пикселей сформированы на подложке активной матрицы с использованием технологии обработки полупроводниковых материалов, то фотодиоды и т.п. сформированы на подложке активной матрицы с использованием той же самой технологии (см. JP 2006-3857A).

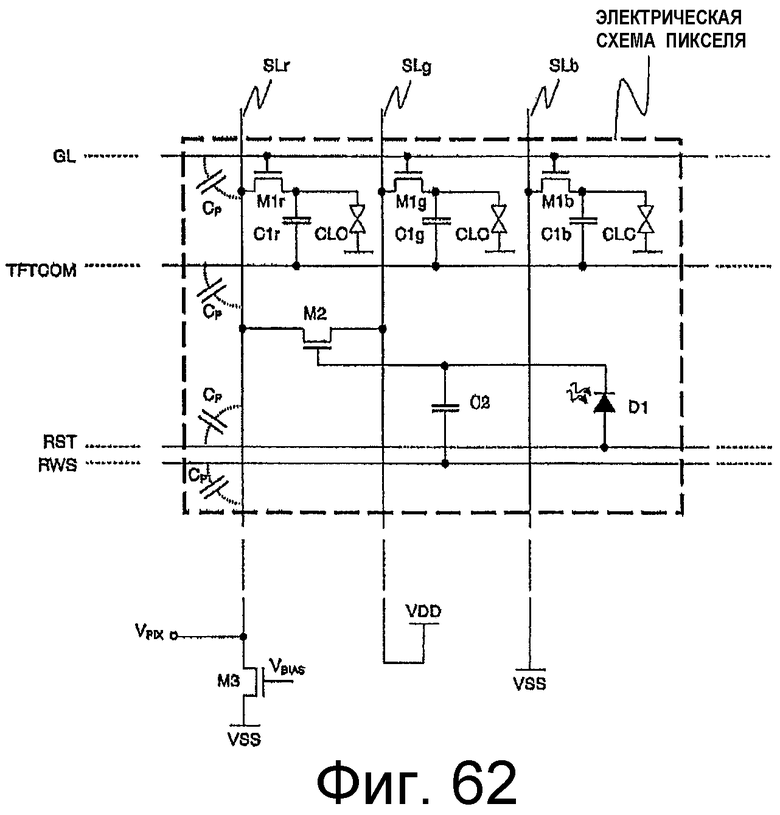

Так как на подложке активной матрицы сформирован обычный оптический датчик, то приведенная в качестве примера конфигурация, раскрытая в W0 2007/145346 и W0007/145347, показана на Фиг. 62. Обычный оптический датчик, показанный на Фиг. 62, состоит их следующих основных компонентов: фотодиода D1, конденсатора C2 и транзистора M2. С анодом D1 фотодиода соединена линия RST для подачи сигнала сброса. С катодом фотодиода D1 соединен один из электродов конденсатора C2 и затвор транзистора M2. Сток транзистора M2 соединен с линией VDD, а его исток соединен с линией OUT (выход). Другой электрод конденсатора C2 соединен с линией RWS для подачи сигнала считывания.

В этой конфигурации выходной сигнал VPIX датчика, соответствующий количеству света, принятого фотодиодом D1, может быть получен путем подачи сигнала сброса и сигнала считывания соответственно на линию RST и на линию RWS в соответствующие заданные моменты времени. Здесь функционирование обычного оптического датчика, показанного на Фиг. 62, объяснено со ссылкой на Фиг. 63. Следует отметить, что на Фиг. 63 низкий уровень (равный, например, -7 В) сигнала сброса обозначен как "VRST.L", высокий уровень (равный, например, 0 В) сигнала сброса обозначен как "VRST.H", низкий уровень (равный, например, 0 В) сигнала считывания обозначен как "VRWS.L", а высокий уровень (равный, например, 15 В) сигнала считывания обозначен как "VRWS.H".

Сначала, когда на линию RST подают сигнал VRST.H сброса с высоким уровнем, фотодиод D1 имеет прямое смещение, и, следовательно, потенциал VINT затвора транзистора M2 выражается следующей формулой (1):

VINT=VRST.H-VF, (1)

где VF - прямое напряжение фотодиода D1. Поскольку VINT здесь является более низким, чем пороговое напряжение транзистора M2, то транзистор M2 является непроводящим в течение периода сброса.

Затем сигнал сброса вновь становится имеющим низкоуровневый потенциал VRST.L (в момент времени tRST, показанный на Фиг. 63), и, следовательно, начинается период интегрирования фототока (период регистрации, который представляет собой период, обозначенный как TINT, который показан на Фиг. 63). В периоде интегрирования фототок, пропорциональный количеству света, падающего на фотодиод D1, вытекает из конденсатора C2, вследствие чего конденсатор C2 разряжается. Соответственно, потенциал VINT затвора транзистора M2 в конце периода интегрирования выражается следующей формулой (2):

VINT=VRST.H-VF-ΔVRST·CPD/CTOTAL-IPHOTO·TINT/CTOTAL, (2)

где ΔVRST - высота импульса сигнала сброса (VRST.H-VRST.L), IPHOTO - фототок фотодиода D1, а TINT - длительность периода интегрирования. CPD - емкость фотодиода D1. CTOTAL - сумма емкости конденсатора C2, емкости CPD фотодиода D1 и емкости CTFT транзистора M2. К тому же, в течение периода интегрирования, поскольку VINT является более низким, чем пороговое напряжение транзистора M2, то транзистор M2 является непроводящим.

После окончания периода интегрирования в момент времени tRWS, показанный на Фиг. 63, уровень сигнала RWS считывания повышается, и, следовательно, начинается период считывания. Следует отметить, что период считывания продолжается до тех пор, пока уровень сигнала RWS считывания остается высоким. При этом происходит инжекция зарядов в конденсатор C2. В результате, потенциал VINT затвора транзистора M2 выражается следующей формулой (3):

VINT=VRST.H-VF-ΔVRST·CPD/CTOTAL-IPHOTO·TINT/CTOTAL+ΔVRWS·CINT/CTOTAL, (3)

где ΔVRWS - высота импульса сигнала считывания (VRST.H-VRWS.L). При этом потенциал VINT затвора транзистора M2 становится более высоким, чем его пороговое напряжение, и это вызывает то, что транзистор M2 становится проводящим. Таким образом, транзистор M2, вместе с транзистором M3 смещения, обеспеченный на конце линии OUT в каждом столбце, функционируют в качестве усилителя на истоковом повторителе. Другими словами, выходное напряжение VPIX датчика из транзистора M2 является пропорциональным интегралу фототока фотодиода D1 в течение периода интегрирования.

Следует отметить, что на Фиг. 63 форма сигнала, обозначенная сплошной линией, представляет собой изменение потенциала VINT в том случае, когда количество света, падающего на фотодиод D1, мало. Форма сигнала, обозначенная пунктирной линией, представляет собой изменение потенциала VINT в том случае, когда количество света, падающего на фотодиод D1, находится на уровне насыщения. Величина ΔVSIG, показанная на Фиг. 63, представляет собой разность потенциалов, пропорциональную количеству света, падающего на фотодиод D1. Величина ΔVINT, показанная на Фиг. 63, представляет собой величину, на которую повышается потенциал VINT при подаче сигнала считывания с линии RWS на оптический датчик в течение периода считывания.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

В описанном выше устройстве отображения, имеющем оптический датчик в пикселе, разность между соответствующими потенциалами накопительного узла в случаях с различными значениями освещенности (например, в случае темного состояния и в случае, когда падает свет на уровне насыщения) в конце периода накопления равна разности между соответствующими потенциалами узла накопления в вышеизложенных соответствующих случаях после их усиления в течение периода считывания. Другими словами, разность между потенциалом (обозначенным здесь как "VINT1") накопительного узла в конце периода накопления в случае темного состояния и потенциалом (обозначенным здесь как "VINT2") накопительного узла в конце периода накопления в том случае, когда падает свет на уровне насыщения, равна разности между потенциалом (обозначенным здесь как "VINT3") накопительного узла после его усиления в течение периода считывания в случае темного состояния и потенциалом (обозначенным здесь как "VINT4") накопительного узла после его усиления в течение периода считывания в том случае, когда падает свет на уровне насыщения.

Однако поскольку описанная выше разность между VINT3 и VINT4 является большей, то может быть получен оптический датчик, имеющий превосходные характеристики, например, более высокую чувствительность и более высокое отношение сигнал/шум. Следовательно, задачей настоящего изобретения является создание устройства отображения, имеющего высокочувствительный оптический датчик, за счет установления большей разности между потенциалами (VINT3-VINT4) накопительного узла после усиления вследствие разности освещенностей на светоприемной поверхности, чем разность между его потенциалами (VINT1-VINT2) в конце периода интегрирования.

Для достижения описанной выше задачи раскрытое здесь устройство отображения представляет собой устройство отображения, которое включает в себя оптический датчик в области пикселей на подложке активной матрицы, причем этот оптический датчик включает в себя: фотоприемный элемент для приема падающего света; сигнальную линию сброса для подачи сигнала сброса в оптический датчик; сигнальную линию считывания для подачи сигнала считывания в оптический датчик; накопительный узел, имеющий потенциал, который изменяется в зависимости от количества света, полученного фотоприемным элементом в течение периода регистрации, причем период регистрации представляет собой период с момента подачи сигнала сброса до момента подачи сигнала считывания; усилительный элемент для усиления потенциала накопительного узла в соответствии с сигналом считывания; и элемент, переключающий датчик, для считывания потенциала, усиленного усилительным элементом, и вывода этого потенциала в качестве выходного сигнала из схемы датчика на выходную линию, в котором обеспечено наличие светоэкранирующей пленки на стороне, противоположной стороне светоприемной поверхности относительно фотоприемного элемента, причем эта светоэкранирующая пленка соединена с источником питания для подачи напряжения для фиксации потенциала светоэкранирующей пленки, равного постоянному потенциалу, и удовлетворяется следующая формула:

VLS≥VRST.H ,

где VLS - постоянный потенциал, а VRST.H - высокоуровневый потенциал сигнала сброса.

В описанной выше конфигурации, в которой обеспечено наличие усилительного элемента для усиления потенциала накопительного узла в соответствии с сигналом считывания, разность между потенциалами накопительного узла вследствие разности между значениями освещенности на светоприемной поверхности после усиления является большей, чем разность между его потенциалами в конце периода интегрирования. Например, разность между потенциалом накопительного узла после его усиления в течение периода считывания в случае темного состояния и потенциалом накопительного узла после его усиления в течение периода считывания в том случае, когда падает свет на уровне насыщения, является большей, чем разность между потенциалом накопительного узла в конце периода накопления в случае темного состояния и потенциалом накопительного узла в конце периода накопления в том случае, когда падает свет на уровне насыщения. Следовательно, может быть реализовано устройство отображения, включающее в себя оптический датчик с высокой чувствительностью. Кроме того, за счет установления потенциала светоэкранирующей пленки как постоянного потенциала, равного или большего, чем высокоуровневый потенциал VRST.H сигнала сброса, может быть получен выходной сигнал датчика, имеющий превосходную линейность относительно количества падающего света.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

На Фиг. 1 изображена блок-схема, на которой схематично показана конфигурация устройства отображения согласно одному из вариантов осуществления настоящего изобретения.

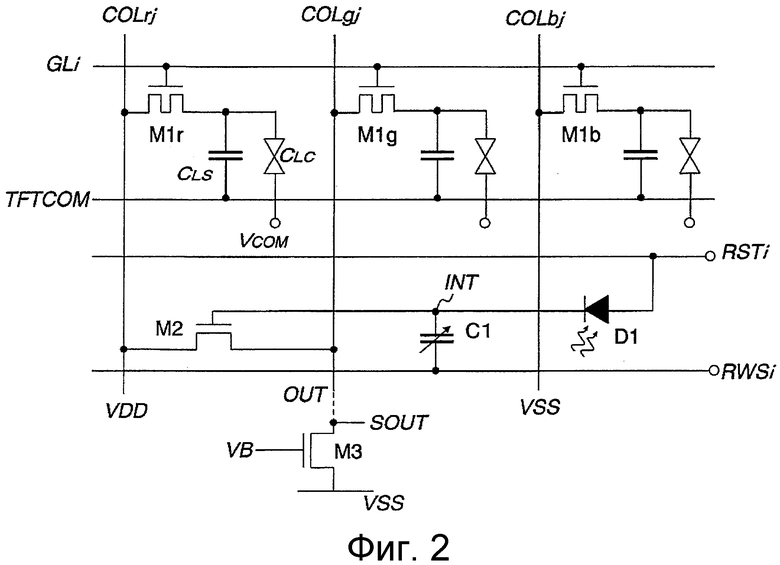

На Фиг. 2 изображена эквивалентная электрическая схема, на которой показана конфигурация одного пикселя в устройстве отображения согласно первому варианту осуществления настоящего изобретения.

На Фиг. 3 показаны вольтфарадные (CV) характеристики конденсатора, которым оснащен оптической датчик согласно первому варианту осуществления изобретения.

На Фиг. 4 изображена временная диаграмма, на которой показана форма управляющего сигнала и изменение потенциала накопительного узла в оптическом датчике согласно первому варианту осуществления изобретения.

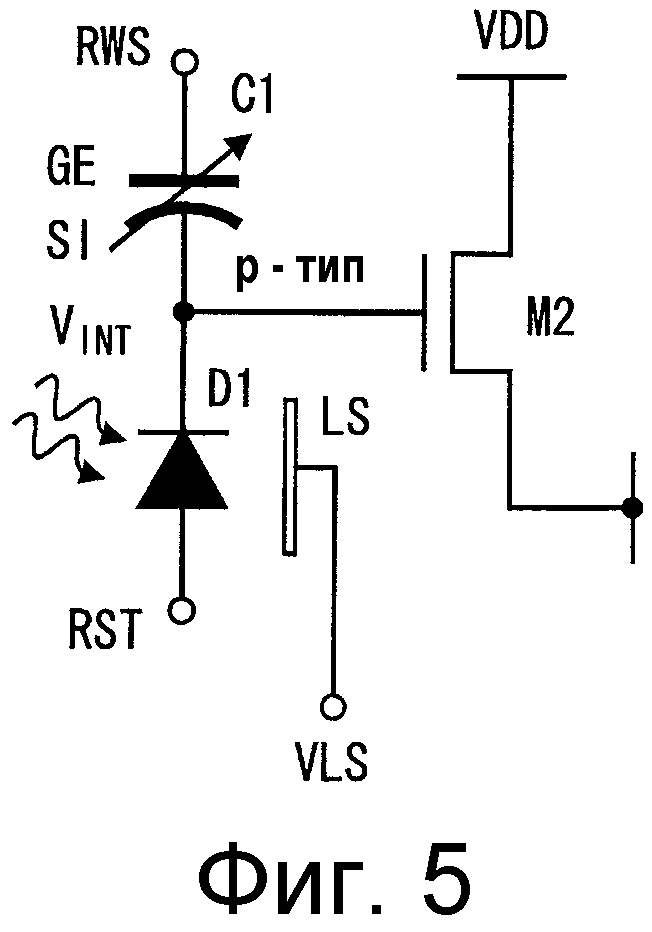

На Фиг. 5 изображена эквивалентная электрическая схема оптического датчика согласно данному варианту осуществления изобретения.

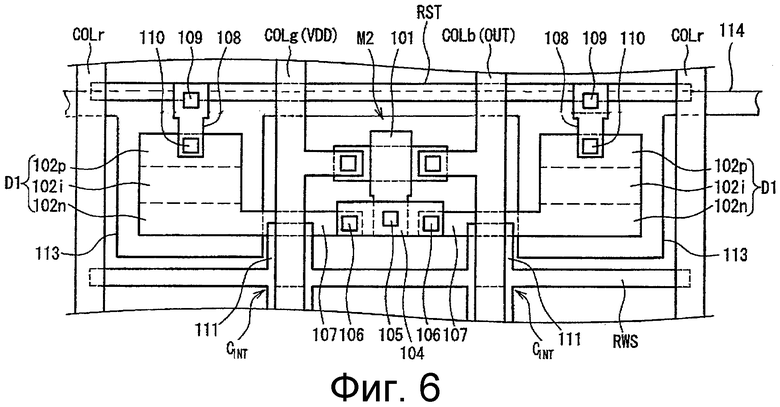

На Фиг. 6 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно данному варианту осуществления изобретения.

На Фиг. 7 на виде в увеличенном масштабе показана та область, где сформирован конденсатор C1.

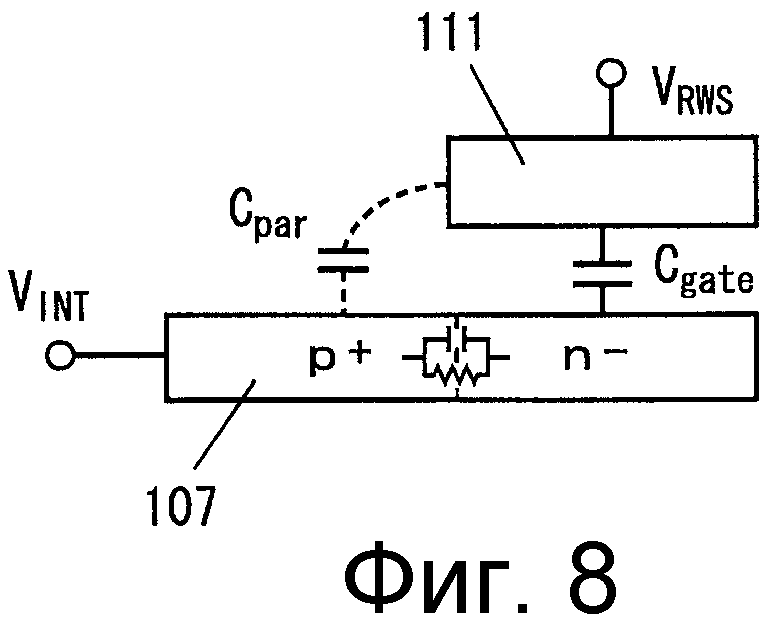

На Фиг. 8 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно данному варианту осуществления изобретения.

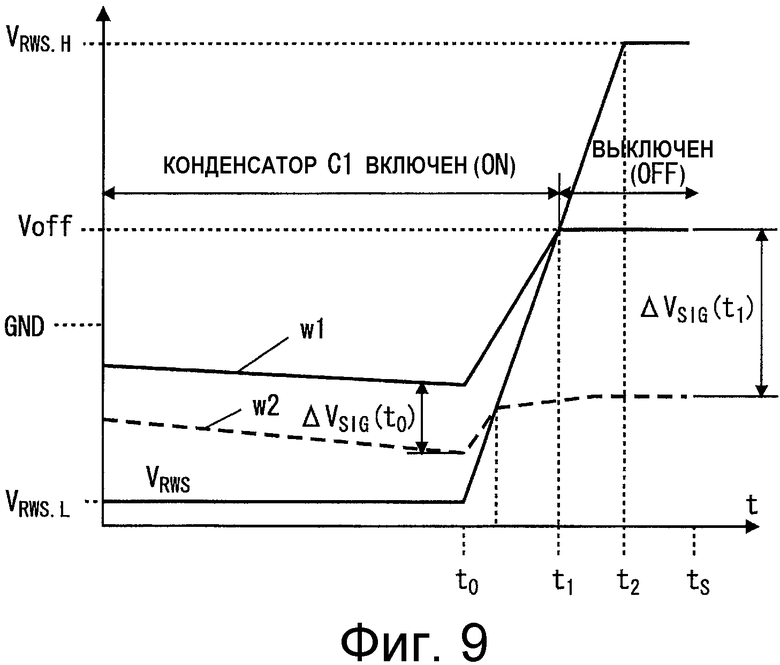

На Фиг. 9 изображена временная диаграмма сигналов, на которой показано изменение потенциала VINT накопительного узла с момента окончания периода интегрирования до периода считывания.

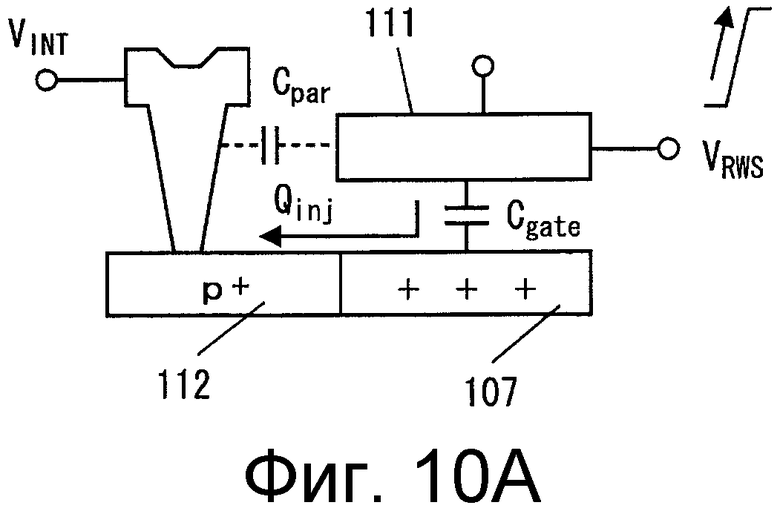

На Фиг. 10A на схематичном виде в поперечном разрезе показан перенос заряда в конденсаторе C1, когда потенциал электрода затвора является более низким, чем пороговое напряжение.

На Фиг. 10B на схематичном виде в поперечном разрезе показан перенос заряда в конденсаторе C1, когда потенциал электрода затвора является более высоким, чем пороговое напряжение.

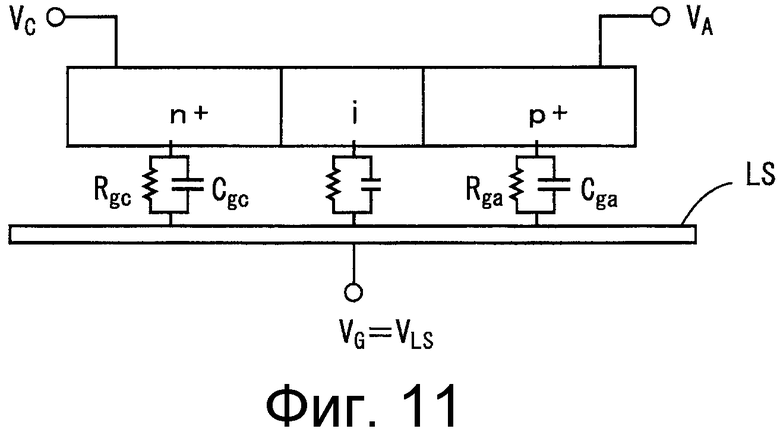

На Фиг. 11 на схематичном виде в поперечном разрезе показан pin-диод, имеющий латеральную структуру.

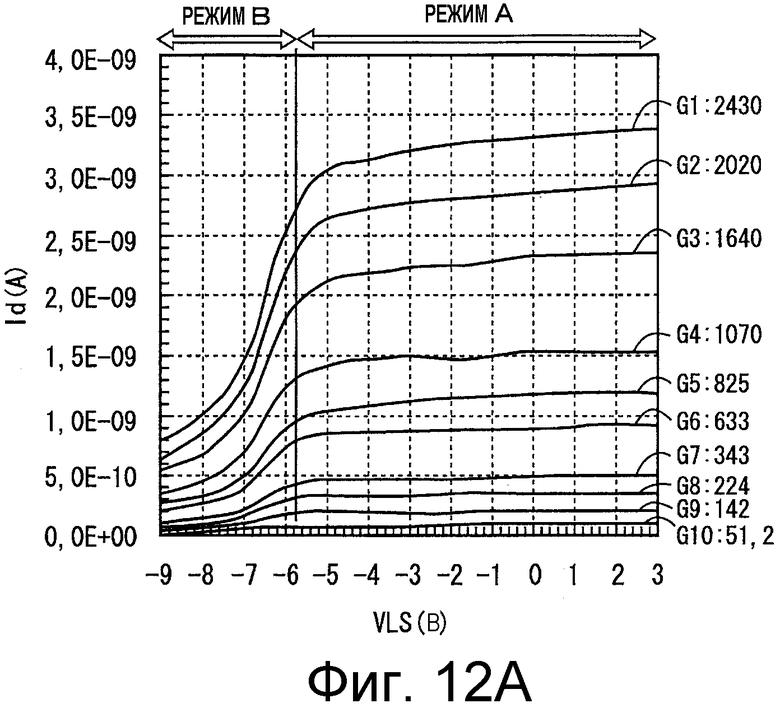

На Фиг. 12A изображен график характеристики "зависимость Id от VLS", на котором показаны различия между тремя режимами работы pin-диода.

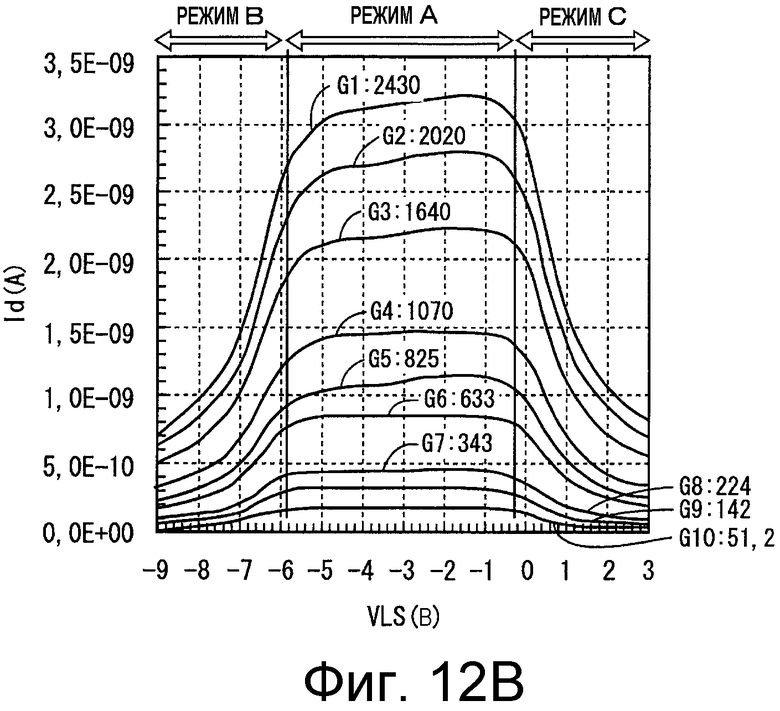

На Фиг. 12B изображен график характеристики "зависимость Id от VLS", на котором показаны различия между тремя режимами работы pin-диода.

На Фиг. 13 изображен график, на котором показана зависимость между потенциалом VA анода и потенциалом VLS светоэкранирующей пленки LS.

На Фиг. 14 изображена временная диаграмма, на которой показан момент считывания в устройстве отображения согласно первому варианту осуществления изобретения.

На Фиг. 15 изображена принципиальная электрическая схема, на которой показана внутренняя конфигурация схемы считывания пикселя, оснащенного датчиком.

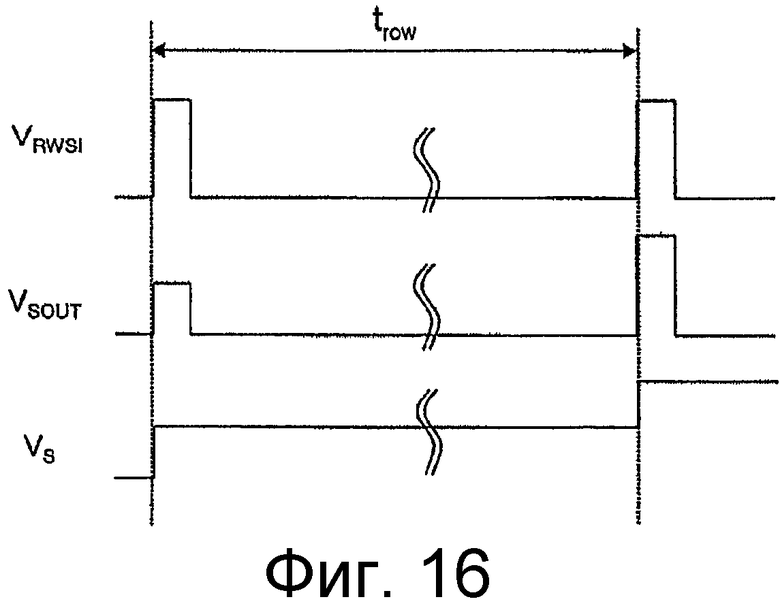

На Фиг. 16 изображена временная диаграмма сигналов, на которой показана зависимость между сигналом считывания, выходным сигналом датчика и выходным сигналом из схемы считывания пикселя, оснащенного датчиком.

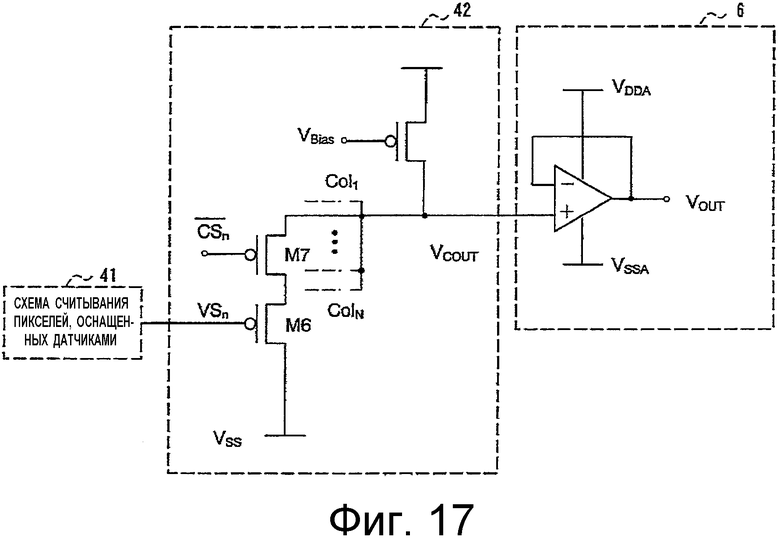

На Фиг. 17 изображена эквивалентная электрическая схема, на которой схематично показана конфигурация усилителя столбца датчиков.

На Фиг. 18 изображена эквивалентная электрическая схема оптического датчика согласно второму варианту осуществления изобретения.

На Фиг. 19 изображена временная диаграмма сигналов, на которой показаны сигнал сброса и сигнал считывания, подаваемые в оптический датчик согласно второму варианту осуществления изобретения.

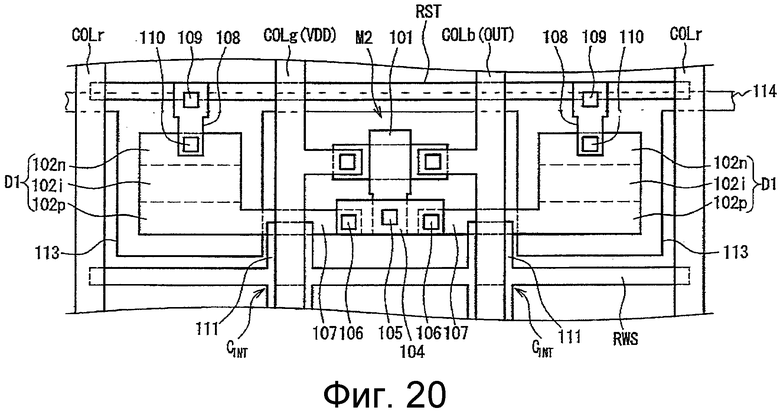

На Фиг. 20 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно второму варианту осуществления изобретения.

На Фиг. 21 на виде в увеличенном масштабе изображена та область, показанная на Фиг. 20, где сформирован конденсатор C1.

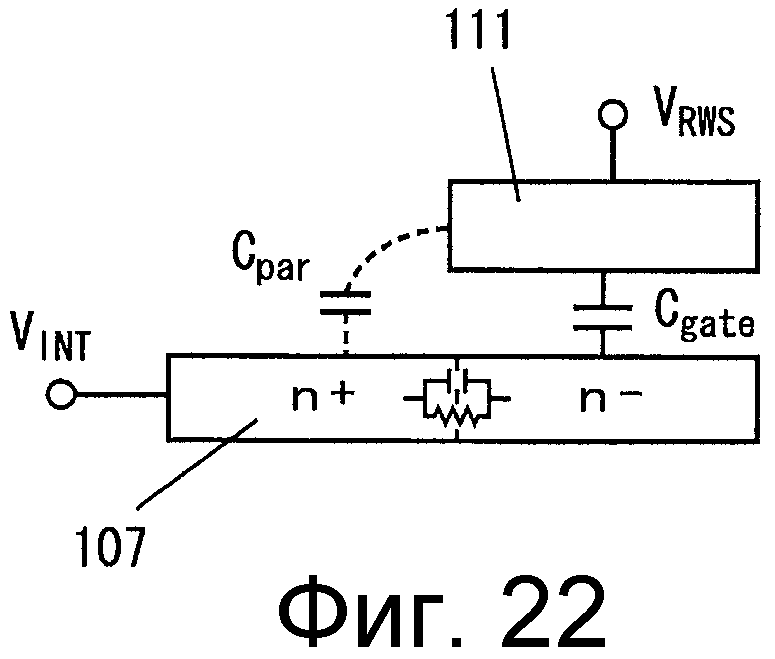

На Фиг. 22 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно второму варианту осуществления изобретения.

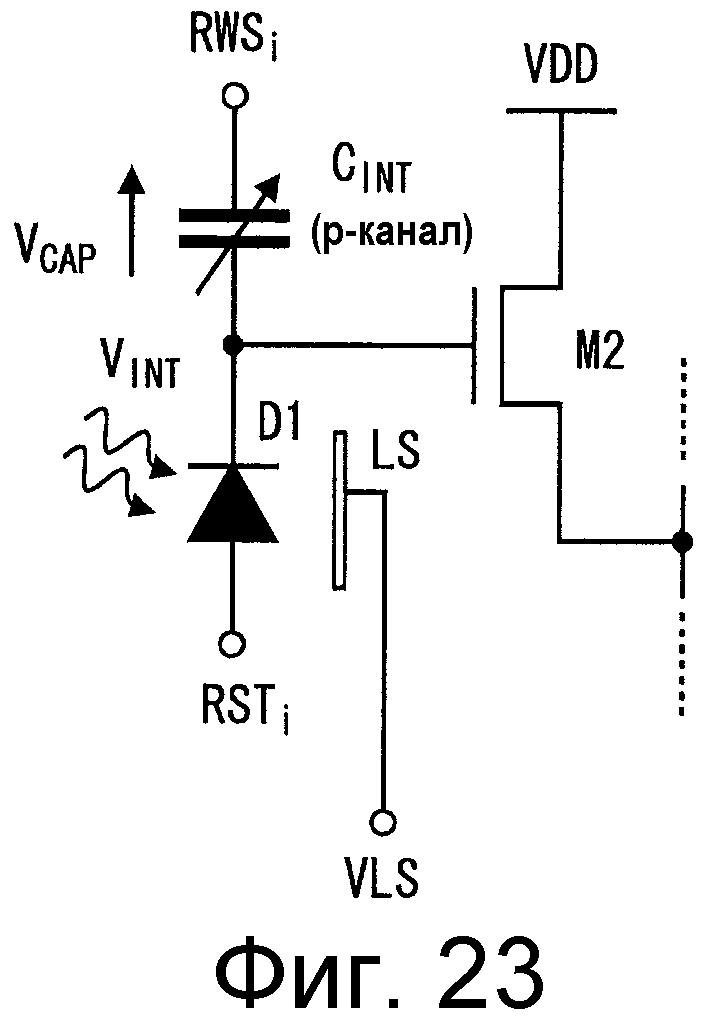

На Фиг. 23 изображена эквивалентная электрическая схема оптического датчика согласно третьему варианту осуществления изобретения.

На Фиг. 24 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно третьему варианту осуществления изобретения.

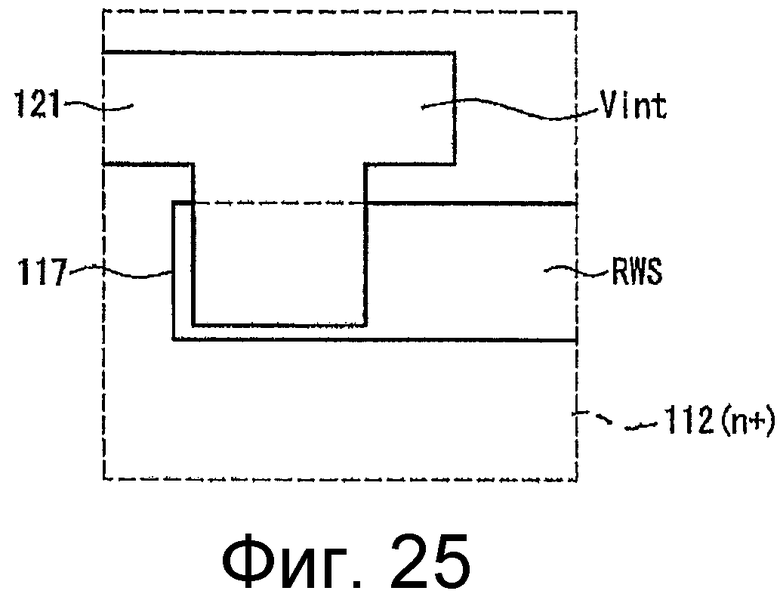

На Фиг. 25 на виде в увеличенном масштабе изображена та область, показанная на Фиг. 24, в которой сформирован конденсатор C1.

На Фиг. 26 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно третьему варианту осуществления изобретения.

На Фиг. 27 изображена эквивалентная электрическая схема оптического датчика согласно четвертому варианту осуществления изобретения.

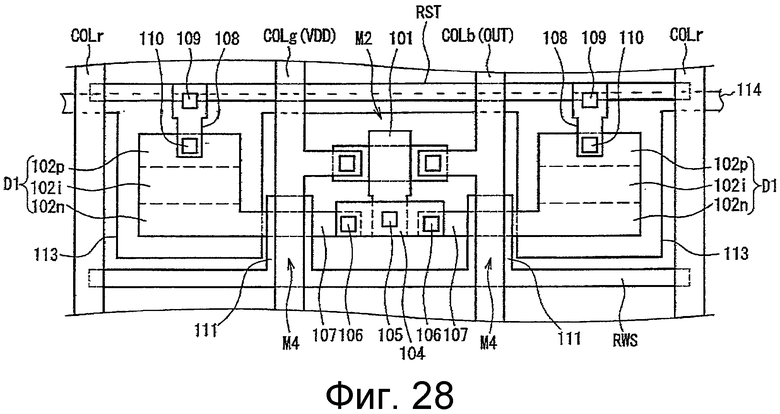

На Фиг. 28 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно четвертому варианту осуществления изобретения.

На Фиг. 29 на виде в увеличенном масштабе изображена та область, показанная на Фиг. 28, где сформирован p-канальный TFT.

На Фиг. 30 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно четвертому варианту осуществления изобретения.

На Фиг. 31 изображена эквивалентная электрическая схема p-канального TFT оптического датчика согласно четвертому варианту осуществления изобретения.

На Фиг. 32 изображена временная диаграмма сигналов, на которой показаны влияния, которые паразитная емкость и ток утечки оказывают на потенциал накопительного узла.

На Фиг. 33 на виде сверху показана приведенная в качестве примера планарная структура приведенного в качестве примера видоизмененного варианта оптического датчика согласно четвертому варианту осуществления изобретения.

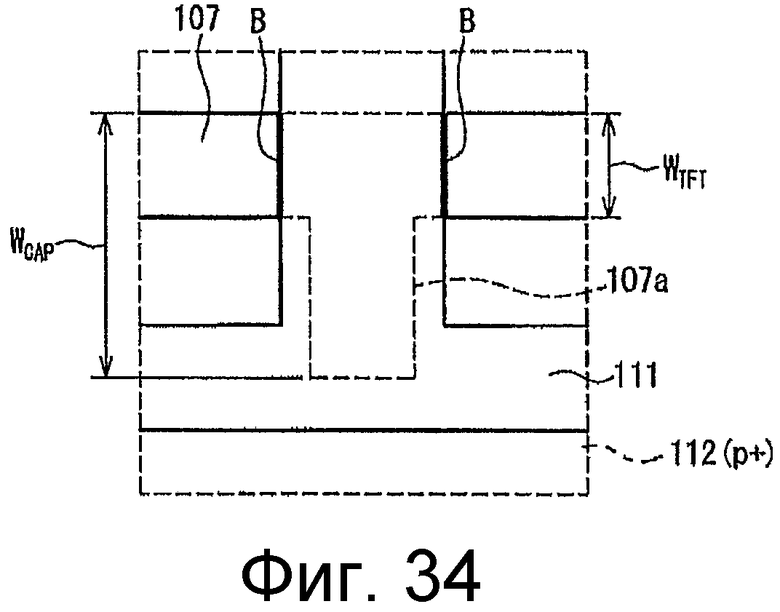

На Фиг. 34 на виде в увеличенном масштабе изображена та область, показанная на Фиг. 33, где сформирован p-канальный TFT.

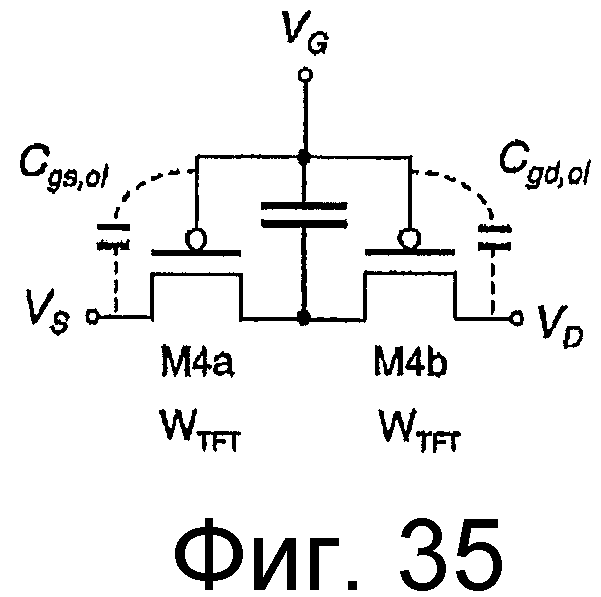

На Фиг. 35 изображена эквивалентная электрическая схема p-канального TFT, показанного на Фиг. 33.

На Фиг. 36 изображена эквивалентная электрическая схема оптического датчика согласно пятому варианту осуществления изобретения.

На Фиг. 37 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно пятому варианту осуществления изобретения.

На Фиг. 38 на виде в увеличенном масштабе показана та область, где сформирован усилительный элемент (n-канальный TFT) в пятом варианте осуществления изобретения.

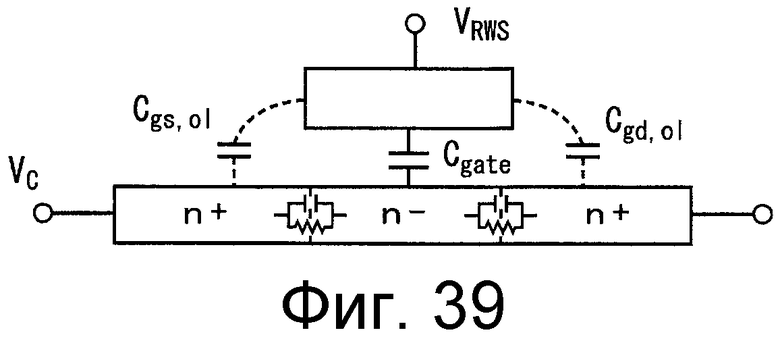

На Фиг. 39 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно пятому варианту осуществления изобретения.

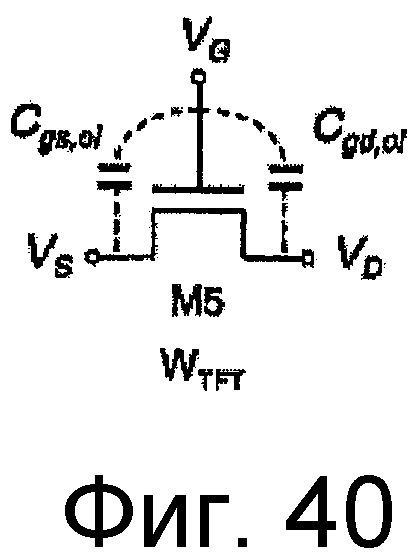

На Фиг. 40 изображена эквивалентная электрическая схема n-канального TFT, служащего в качестве усилительного элемента в пятом варианте осуществления изобретения.

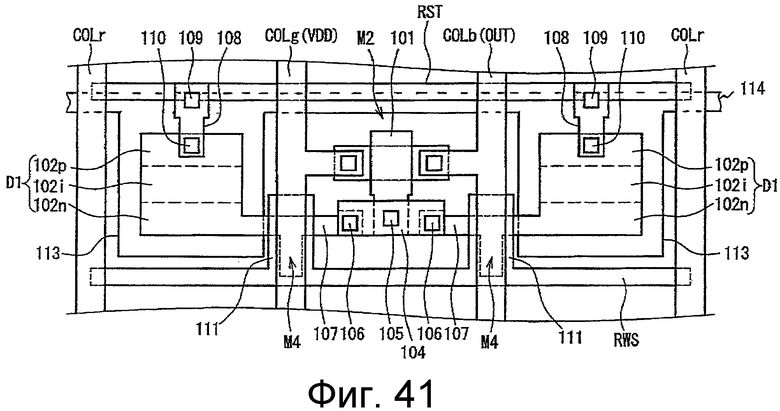

На Фиг. 41 на виде сверху показана приведенная в качестве примера планарная структура приведенного в качестве примера видоизмененного варианта оптического датчика согласно пятому варианту осуществления изобретения.

На Фиг. 42 на схематичном виде в поперечном разрезе изображена схема соединений соответствующих областей в усилительном элементе в приведенном в качестве примера видоизмененном варианте, показанном на Фиг. 41.

На Фиг. 43 изображена эквивалентная электрическая схема n-канального TFT, показанного на Фиг. 42.

На Фиг. 44 изображена эквивалентная электрическая схема оптического датчика согласно шестому варианту осуществления изобретения.

На Фиг. 45 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно шестому варианту осуществления изобретения.

На Фиг. 46 на виде в увеличенном масштабе показана та область, где сформирован усилительный элемент (диод D2) в шестом варианте осуществления изобретения.

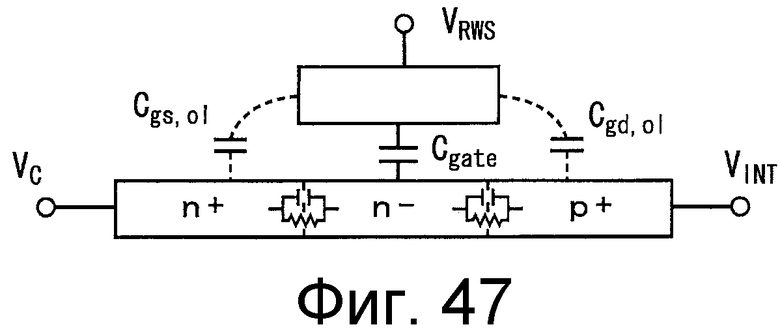

На Фиг. 47 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно шестому варианту осуществления изобретения.

На Фиг. 48 изображена эквивалентная электрическая схема диода, служащего в качестве усилительного элемента, согласно шестому варианту осуществления изобретения.

На Фиг. 49 изображена эквивалентная электрическая схема оптического датчика согласно первому видоизмененному варианту шестого варианта осуществления изобретения, который приведен в качестве примера.

На Фиг. 50 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно первому видоизмененному варианту шестого варианта осуществления изобретения, который приведен в качестве примера.

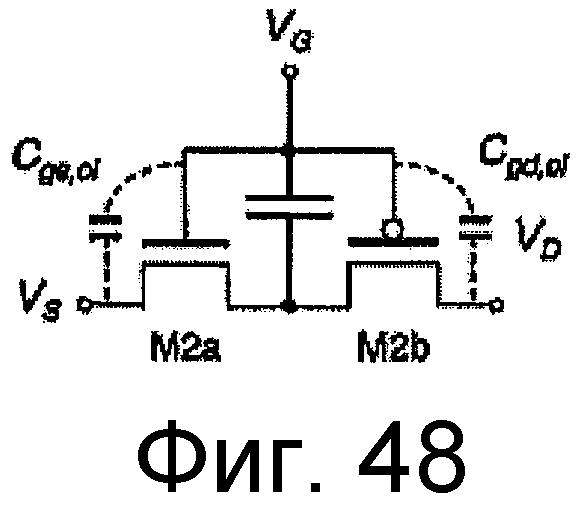

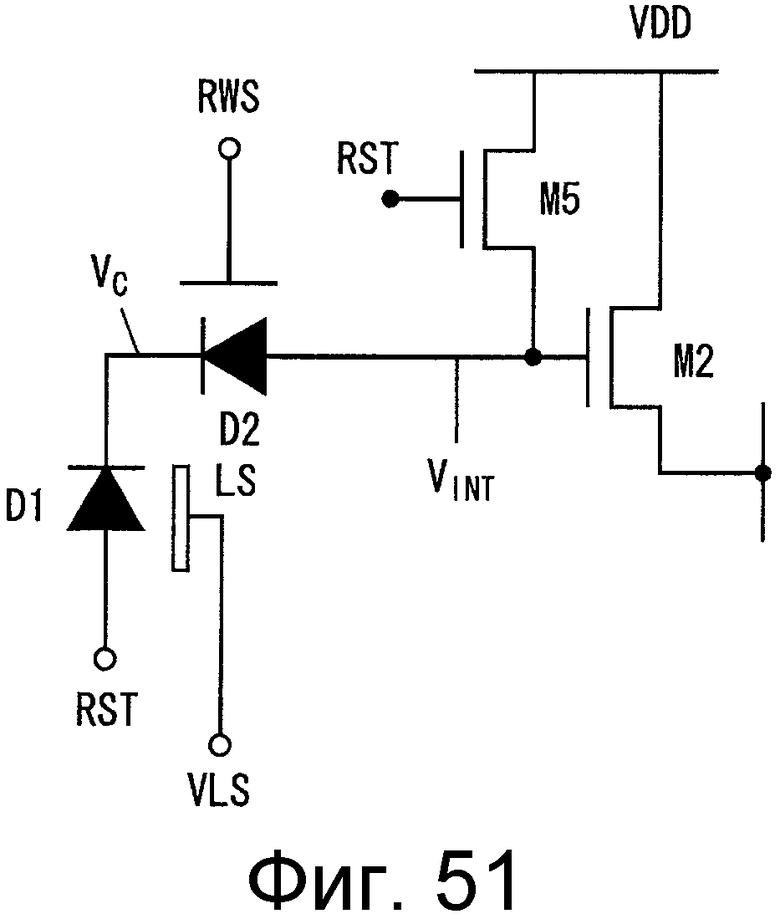

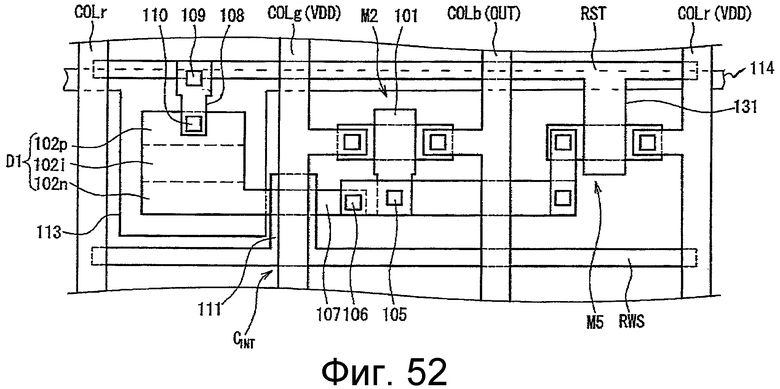

На Фиг. 51 изображена эквивалентная электрическая схема оптического датчика согласно второму видоизмененному варианту шестого варианта осуществления изобретения, который приведен в качестве примера.

На Фиг. 52 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно второму видоизмененному варианту шестого варианта осуществления изобретения, который приведен в качестве примера.

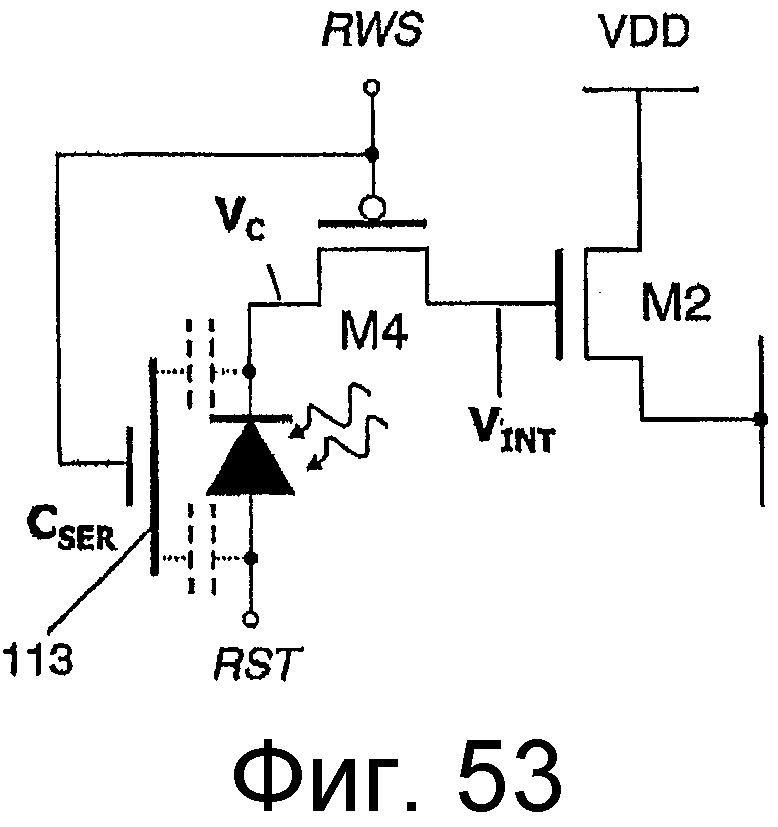

На Фиг. 53 изображена эквивалентная электрическая схема оптического датчика согласно седьмому варианту осуществления изобретения.

На Фиг. 54 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно данному варианту осуществления изобретения.

На Фиг. 55A изображена принципиальная электрическая схема, на которой показано состояние инжекции заряда в случае, когда последовательно подключенный конденсатор CSER объединен с конфигурацией, в которой усилительным элементом является конденсатор переменной емкости.

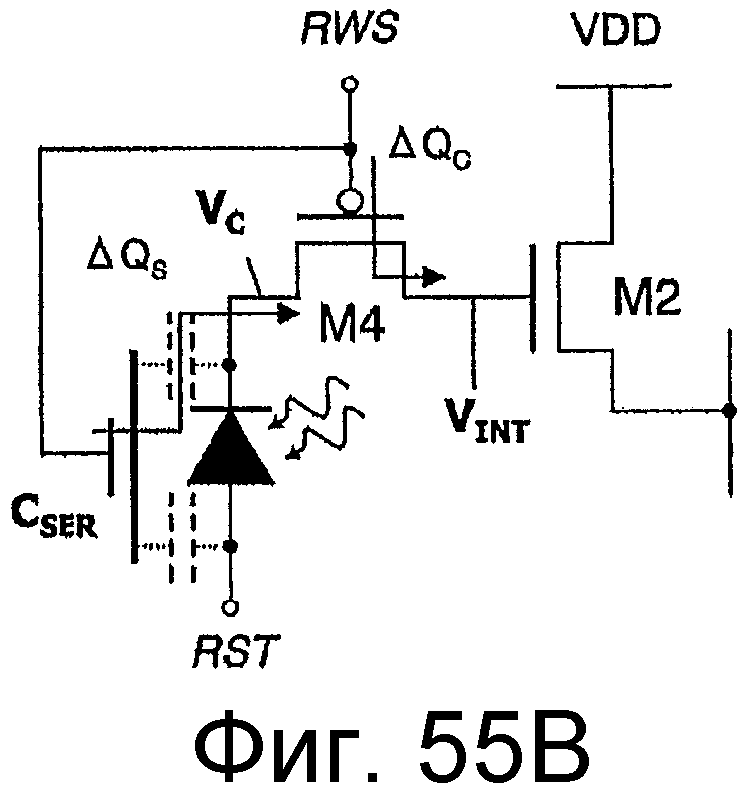

На Фиг. 55B изображена принципиальная электрическая схема, на которой показано состояние инжекции заряда в случае, когда последовательно подключенный конденсатор CSER объединен с конфигурацией, в которой усилительным элементом является p-канальный TFT.

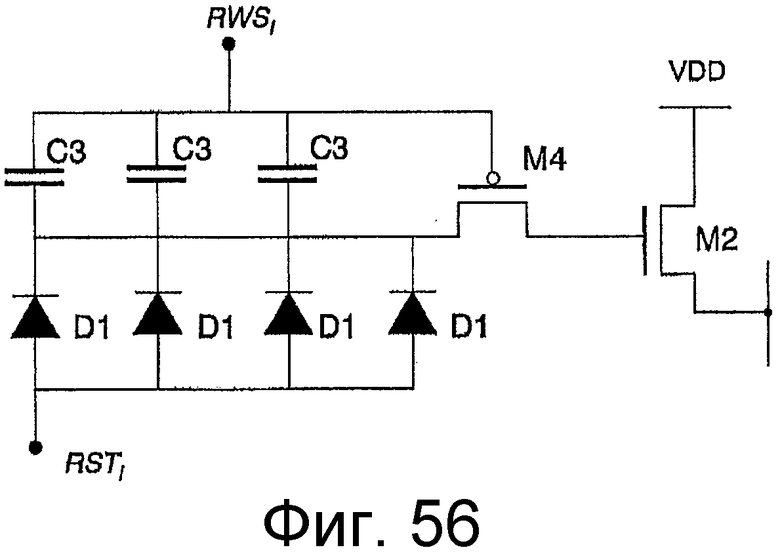

На Фиг. 56 изображена эквивалентная электрическая схема оптического датчика согласно восьмому варианту осуществления изобретения.

На Фиг. 57 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно восьмому варианту осуществления изобретения.

На Фиг. 58 изображена эквивалентная электрическая схема оптического датчика согласно девятому варианту осуществления изобретения.

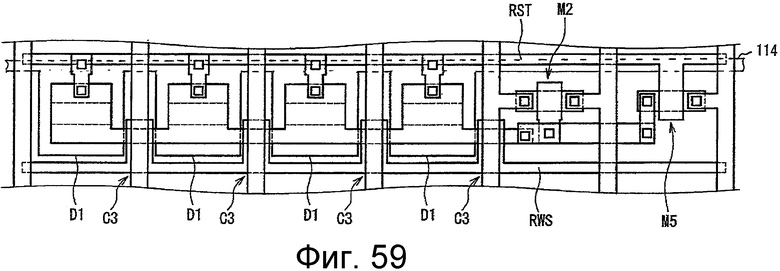

На Фиг. 59 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно девятому варианту осуществления изобретения.

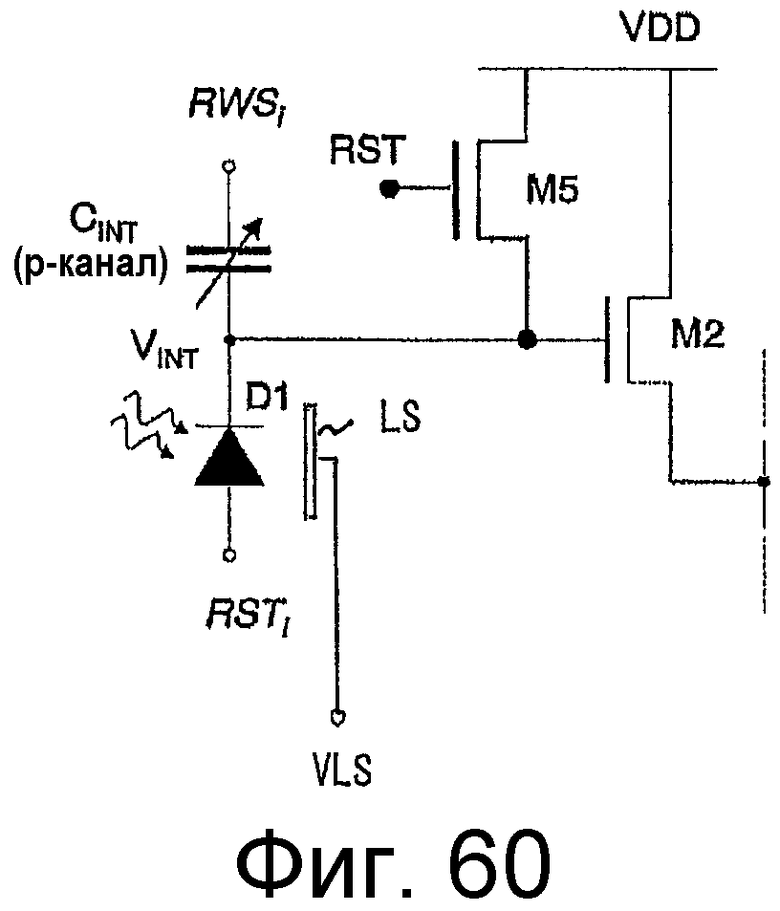

На Фиг. 60 изображена эквивалентная электрическая схема оптического датчика согласно данному варианту осуществления изобретения.

На Фиг. 61 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно данному варианту осуществления изобретения.

На Фиг. 62 изображена эквивалентная электрическая схема, на которой показан приведенный в качестве примера обычный оптический датчик, сформированный на подложке активной матрицы.

На Фиг. 63 изображена временная диаграмма, на которой показана форма управляющего сигнала и изменение потенциала накопительного узла в обычном оптическом датчике.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Устройство отображения согласно одному из вариантов осуществления настоящего изобретения представляет собой устройство отображения, включающее в себя оптический датчик в области пикселей на подложке активной матрицы, в котором оптический датчик включает в себя: фотоприемный элемент для приема падающего света; сигнальную линию сброса для подачи сигнала сброса в оптический датчик; сигнальную линию считывания для подачи сигнала считывания в оптический датчик; накопительный узел, имеющий потенциал, который изменяется в зависимости от количества света, принятого фотоприемным элементом в течение периода регистрации, причем период регистрации представляет собой период с момента подачи сигнала сброса до момента подачи сигнала считывания; усилительный элемент для усиления потенциала накопительного узла в соответствии с сигналом считывания; и элемент, переключающий датчик, для считывания потенциала, усиленного усилительным элементом, и вывода этого потенциала в качестве выходного сигнала из схемы датчика на выходную линию.

В этой конфигурации, в которой обеспечено наличие усилительного элемента для усиления потенциала накопительного узла в соответствии с сигналом считывания, разность между потенциалами накопительного узла вследствие разницы значений освещенности на светоприемной поверхности после того, как усиление больше чем разность между его потенциалами в конце периода интегрирования. Например, разность между потенциалом накопительного узла после усиления во время периода считывания в случае темного состояния и потенциалом накопительного узла после усиления во время периода считывания в том случае, когда падает свет на уровне насыщения, является большей, чем разность между потенциалом накопительного узла в конце периода накопления в случае темного состояния и потенциалом накопительного узла в конце периода накопления в том случае, когда падает свет на уровне насыщения. Следует отметить, что эта функция усиления разности потенциалов установлена между любыми значениями освещенности, а не исключительно для случая темного состояния и для того случая, когда падает свет на уровне насыщения. Таким образом, может быть создано устройство отображения, включающее в себя оптический датчик с высокой чувствительностью.

Кроме того, описанная выше конфигурация предпочтительно видоизменена так, что обеспечено наличие светоэкранирующей пленки на стороне, противоположной стороне светоприемной поверхности относительно фотоприемного элемента, причем эта светоэкранирующая пленка соединена с источником питания для подачи напряжения для фиксации потенциала светоэкранирующей пленки равным постоянному потенциалу, и удовлетворяется следующая формула:

VLS≥VRST.H ,

где VLS - постоянный потенциал, а VRST.H - высокоуровневый потенциал сигнала сброса. В этой предпочтительной конфигурации могут быть устранены флуктуации потенциала светоэкранирующей пленки, в силу чего ухудшение характеристик диода D1 может быть ослаблено.

В том случае, когда в качестве фотоприемного элемента использован pin-диод, еще более предпочтительно, чтобы удовлетворялась следующая формула:

VLS≥VRST.H+Vth_p,

где Vth_p - пороговое напряжение p-канала pin-диода. Эта предпочтительная конфигурация может вызывать работу pin-диода в состоянии, в котором в диоде на обеих границах слоя собственного полупроводника (i-слоя) со стороны p-слоя и со стороны n-слоя свободные электроны и положительные дырки имеют тенденцию к миграции. Следовательно, фототок (фотоэлектрический ток) увеличивается, и линейность изменения фототока (фотоэлектрического тока) при изменении освещенности может быть улучшена.

В описанном выше устройстве отображения в качестве усилительного элемента может быть использован, например, конденсатор переменной емкости. В этом случае в качестве конденсатора переменной емкости может быть использован, например, MOS-конденсатор (конденсатор со структурой металл-оксид-полупроводник), который включает в себя сигнальную линию считывания, изоляционную пленку и область полупроводника p-типа, сформированную в кремниевой пленке. В альтернативном варианте в качестве конденсатора переменной емкости может быть использован MOS-конденсатор, который включает в себя электрод затвора элемента, переключающего датчик, изоляционную пленку и область полупроводника n-типа, сформированную в кремниевой пленке. В описанной выше конфигурации сигнальная линия считывания может быть использована в качестве затвора конденсатора переменной емкости. Следовательно, эта конфигурация имеет преимущество, состоящее в отсутствии необходимости обеспечения наличия линии и контактов для соединения сигнальной линии считывания и электрода затвора.

Более того, в описанном выше устройстве отображения в качестве усилительного элемента может быть использован, например, p-канальный тонкопленочный транзистор. В этом случае предпочтительно, чтобы в p-канальном тонкопленочном транзисторе область канала была сформирована в широком участке кремниевой пленки, соединяющей фотоприемный элемент и накопительный узел друг с другом, и чтобы электрод затвора p-канального тонкопленочного транзистора был создан так, что перекрывает этот широкий участок. В этой конфигурации длина границы может быть уменьшена, что предотвращает сужения динамического диапазона из-за паразитной емкости или тока утечки. В альтернативном варианте в описанном выше устройстве отображения в качестве усилительного элемента может быть использован n-канальный тонкопленочный транзистор.

В альтернативном варианте в описанном выше устройстве отображения в качестве усилительного элемента может быть использован диод, имеющий электрод затвора на канале. В этой конфигурации длина границы может быть уменьшена.

Кроме того, в качестве другой предпочтительной конфигурации описанное выше устройство отображения может иметь конфигурацию, в которой обеспечено наличие электрода, противоположного светоэкранирующей пленке, для формирования последовательно подключенной емкости относительно паразитной емкости между светоэкранирующей пленкой и фотоприемным элементом, и этот электрод является электрически соединенным с сигнальной линией считывания. Эта конфигурация имеет эффект уменьшения влияния, которое оказывает паразитная емкость между светоэкранирующей пленкой и фотоприемным элементом на изменение потенциала накопительного узла в течение периода интегрирования.

Кроме того, в описанном выше устройстве отображения предпочтительно обеспечено наличие множества фотоприемных элементов в области пикселей, причем это множество фотоприемных элементов соединены параллельно, а усилительный элемент соединен с одним из фотоприемных элементов, расположенным в конце фотоприемных элементов. За счет параллельного соединения множества фотоприемных элементов таким способом может быть увеличен фотоэлектрический ток, в силу чего чувствительность может быть улучшена.

В описанном выше устройстве отображения элементом, переключающим датчик, предпочтительно является переключающий элемент с тремя выводами, причем электрод затвора, являющийся одним из этих трех выводов, соединен с накопительным узлом, а один из двух других выводов из этих трех выводов соединен с выходной линией. В этой конфигурации достаточно наличие одного элемента, переключающего датчик, и, следовательно, конфигурация схемы оптического датчика может быть упрощена. Следует отметить, что в описанном выше устройстве отображения может быть дополнительно обеспечено наличие переключающего элемента для сброса элемента, переключающего датчик.

В описанном выше устройстве отображения усилительный элемент предпочтительно имеет пороговый потенциал, при котором состояние усилительного элемента переключается между состоянием "включено" ("ВКЛ") и состоянием "выключено" ("ВЫКЛ") в интервале между низкоуровневым потенциалом и высокоуровневым потенциалом сигнала считывания.

Описанное выше устройство отображения может быть осуществлено как жидкокристаллическое устройство отображения, которое дополнительно включает в себя противоположную подложку, которая является противоположной подложке активной матрицы; и жидкий кристалл, расположенный между подложкой активной матрицы и противоположной подложкой.

Ниже приведено объяснение более конкретных вариантов осуществления настоящего изобретения со ссылкой на чертежи. Следует отметить, что в описанных ниже вариантах осуществления изобретения показаны приведенные в качестве примера конфигурации в том случае, когда устройство отображения согласно настоящему изобретению осуществлено как жидкокристаллическое устройство отображения, но устройство отображения согласно настоящему изобретению не ограничено жидкокристаллическим устройством отображения, и настоящее изобретение применимо к произвольному устройству отображения, в котором используется подложка активной матрицы. Следует отметить, что устройство отображения согласно настоящему изобретению, имеющее оптические датчики, используется в качестве устройства отображения, оснащенного сенсорной панелью, которое обнаруживает объект, приближающийся к его экрану, и выполняет операцию ввода, в качестве устройства отображения для двусторонней связи, имеющего функцию отображения и функцию захвата изображения, и т.д.

Кроме того, для удобства объяснения на чертежах, ссылки на которые приведены ниже, из составляющих элементов, входящих в состав варианта осуществления настоящего изобретения, упрощенно показаны только лишь те основные элементы, иллюстрации которых необходимы для объяснения настоящего изобретения. Следовательно, устройство отображения согласно данному варианту осуществления изобретения может включать в себя произвольные элементы, не показанные на чертежах, на которые приведены ссылки в описании настоящего изобретения. Кроме того, размеры элементов, показанных на чертежах, не точно отражают реальные размеры составляющих элементов, соотношения размеров составляющих элементов и т.д.

[Первый вариант осуществления изобретения]

Сначала приведено объяснение конфигурации подложки активной матрицы, которая обеспечена в жидкокристаллическом устройстве отображения согласно первому варианту осуществления настоящего изобретения, со ссылкой на Фиг. 1 и Фиг. 2.

На Фиг. 1 изображена блок-схема, на которой схематично проиллюстрирована конфигурация подложки 100 активной матрицы, которой оснащено жидкокристаллическое устройство отображения согласно одному из вариантов осуществления настоящего изобретения. Как показано на Фиг. 1, подложка 100 активной матрицы включает в себя, на ее стеклянной подложке, по меньшей мере, область 1 пикселей, драйвер 2 затворов устройства отображения, драйвер 3 истоков устройства отображения, драйвер 4 столбцов датчиков, драйвер 5 строк датчиков, буферный усилитель 6 и соединитель 7 для гибких печатных плат (FPC-соединитель). Кроме того, с подложкой 100 активной матрицы через FPC-соединитель 7 и гибкую печатную плату (FPC) 9 соединена схема 8 обработки сигналов для обработки сигнала изображения, регистрируемого фотоприемным элементом (описание которого приведено ниже) в области 1 пикселей.

Следует отметить, что описанные выше составляющие элементы на подложке 100 активной матрицы могут быть сформированы монолитно на стеклянной подложке посредством технологии обработки полупроводниковых материалов. В альтернативном варианте конфигурация может быть следующей: усилители и драйверы из описанных выше элементов смонтированы на стеклянной подложке, например, способами COG (монтаж микросхемы на стекло). Кроме того, в альтернативном варианте, по меньшей мере, часть вышеупомянутых элементов, показанных на подложке 100 активной матрицы на Фиг. 1, может быть установлена на гибкой печатной плате (FPC) 9. Подложка 100 активной матрицы покрыта противоположной подложкой (не показана), имеющей противоэлектрод, сформированный на всей ее поверхности, образуя многослойную структуру. Жидкокристаллическое вещество загерметизировано в пространстве между подложкой 100 активной матрицы и противоположной подложкой.

Область 1 пикселей представляет собой область, где сформировано множество пикселей для отображения изображений. В данном варианте осуществления изобретения оптический датчик для регистрации изображений обеспечен в каждом пикселе в области 1 пикселей. На Фиг. 2 изображена эквивалентная электрическая схема, на которой показана компоновка пикселей и оптических датчиков в области 1 пикселей на подложке 100 активной матрицы. В примере, показанном на Фиг. 2, один пиксель сформирован из трех подпикселей R (красного), G (зеленого) и B (синего). В одном пикселе, составленном из этих трех подпикселей, обеспечен один оптический датчик. Область 1 пикселей включает в себя пиксели, упорядоченно расположенные в виде матрицы из М строк × N столбцов, и оптические датчики, упорядоченно распложенные аналогичным образом в виде матрицы из М строк × N столбцов. Следует отметить, что количество подпикселей равно М × 3N, как описано выше.

Следовательно, как показано на Фиг. 2, области 1 пикселей имеют линии GL затворов и линии COL истоков, упорядоченно расположенные в виде матрицы в качестве линий для пикселей. Линии GL затворов соединены с драйвером 2 затворов устройства отображения. Линии COL истоков соединены с драйвером 3 истоков устройства отображения. Следует отметить, что в области 1 пикселей обеспечено М строк линий GL затворов. Ниже, когда необходимо дать описание конкретной отдельной линии GL затворов, то она обозначена как GLi (i= от 1 до M). С другой стороны, обеспечены три линии COL истоков на один пиксель для подачи данных об изображении в три подпикселя в пикселе, как описано выше. Когда необходимо дать описание конкретной отдельной линии COL истоков, то она обозначена как COLrj, COLgj или COLbj (j= от 1 до N).

В каждой из точек пересечения линий GL затворов и линий COL истоков обеспечен тонкопленочный транзистор (TFT) M1 в качестве переключающего элемента для пикселя. Следует отметить, что на Фиг. 2 тонкопленочные транзисторы M1, обеспеченные для красного, зеленого и синего подпикселей, обозначены соответственно как M1r, M1g и M1b. Электрод затвора тонкопленочного транзистора M1 соединен с линией GL затворов, его электрод истока соединен с линией COL истоков, а его электрод стока соединен с электродом пикселя, который не показан. Таким образом, как показано на Фиг. 2, между электродом стока тонкопленочного транзистора M1 и противоэлектродом (VCOM) сформирован жидкокристаллический конденсатор CLC. Кроме того, между электродом стока и TFT COM сформирован вспомогательный конденсатор CLS.

На Фиг. 2 для подпикселя, приводимого в действие тонкопленочным транзистором M1r, который соединен с точкой пересечения одной линии GLi затворов и одной линии COLrj истоков, обеспечен красный цветовой фильтр, соответствующий этому подпикселю. В этот подпиксель подают данные об изображении красного цвета из драйвера 3 истоков устройства отображения через исток COLrj, вследствие чего он функционирует как красный подпиксель. Кроме того, для подпикселя, приводимого в действие тонкопленочным транзистором M1g, который соединен с точкой пересечения линии GLi затворов и линии COLgj истоков, обеспечен зеленый цветовой фильтр, соответствующий этому подпикселю. В этот подпиксель подают данные об изображении зеленого цвета из драйвера 3 истоков устройства отображения через линию COLgj истоков, вследствие чего он функционирует как зеленый подпиксель. Помимо этого, для подпикселя, приводимого в действие тонкопленочным транзистором M1b, который соединен с точкой пересечения линии GLi затворов и линии COLbj истоков, обеспечен синий цветовой фильтр, соответствующий этому подпикселю. В этот подпиксель подают данные об изображении синего цвета из драйвера 3 истоков устройства отображения через линию COLbj истоков, вследствие чего он функционирует как синий подпиксель.

Следует отметить, что в примере, показанном на Фиг. 2, обеспечены такие оптические датчики, что один оптический датчик соответствует одному пикселю (трем подпикселям) в области 1 пикселей. Однако соотношение между пикселями и обеспеченными оптическими датчиками не ограничено этим примером, но является произвольным. Например, может быть обеспечено наличие одного оптического датчика на каждый один подпиксель, или может быть обеспечено наличие одного оптического датчика на множество пикселей.

Как показано на Фиг. 2, оптический датчик включает в себя фотодиод D1 в качестве фотоприемного элемента, конденсатор C1 (усилительный элемент) и транзистор M2. Конденсатором C1, который в данном варианте осуществления изобретения функционирует в качестве усилительного элемента, является конденсатор переменной емкости.

В примере, показанном на Фиг. 2, линия COLr истоков также функционирует в качестве линии VDD для подачи постоянного напряжения VDD на оптический датчик из драйвера 4 столбцов датчиков. Кроме того, линия COLg истоков также функционирует в качестве линии OUT для вывода выходного сигнала датчика.

С анодом фотодиода D1 соединена линия RST для подачи сигнала сброса. Один из электродов конденсатора C1 и затвор транзистора M2 соединены с катодом фотодиода D1. Сток транзистора M2 соединен с линией VDD, а его исток соединен с линией OUT. На Фиг. 2 точка соединения (накопительный узел), в которой (в котором) соединены катод фотодиода D1, один из электродов конденсатора C1 и затвор транзистора M2, обозначена как "INT". Другой электрод конденсатора C1 соединен с линией RWS для подачи сигнала считывания. Линии RST и линии RWS соединены с драйвером 5 строк датчиков. Наличие этих линий RST и RWS обеспечено для каждой строки. Следовательно, ниже, когда нужно различить эти линии, то они обозначены как RSTi и RWSi (i= от 1 до M).

Драйвер 5 строк датчиков выбирает линии RSTi и RWSi в комбинации, показанной на Фиг. 2, последовательно через заданные промежутки trow времени. Таким образом, строки оптических датчиков, с которых необходимо считывать информационные заряды, выбирают последовательно в области 1 пикселей.

Следует отметить, что, как показано на Фиг. 2, сток полевого транзистора M3 с изолированным затвором соединен с концом линии OUT. Со стоком транзистора M3 соединена выходная линия SOUT. Следовательно, потенциал VSOUT стока транзистора M3 выводят в качестве выходного сигнала из оптического датчика в драйвер 4 столбцов датчиков. Исток транзистора M3 соединен с линией VSS. Затвор транзистора M3 соединен с источником опорного напряжения (не показан) через линию VB опорного напряжения.

На Фиг. 3 показана диаграмма вольтфарадной (CV) характеристики конденсатора C1. На Фиг. 3 по горизонтальной оси показано напряжение VCAP между электродами конденсатора C1, а по вертикальной оси показана электростатическая емкость. Как показано на Фиг. 3, конденсатор C1 отличается тем, что имеет электростатическую емкость, которая является постоянной тогда, когда напряжение VCAP между электродами мало, но круто изменяется непосредственно до и после того, как напряжение VCAP между электродами достигает порогового значения. Следовательно, характеристики конденсатора C1 могут динамически изменяться при изменении потенциала сигнала считывания, подаваемого с линии RWS. Использование конденсатора C1, имеющего такие характеристики, позволяет оптическому датчику согласно данному варианту осуществления изобретения считывать усиленное значение изменения потенциала накопительного узла периода TINT интегрирования, как показано на Фиг. 4. Пример, показанный на Фиг. 4, представляет собой просто один из вариантов осуществления изобретения, в котором низкий уровень VRST.L сигнала сброса равен -1,4 В, а высокий уровень VRST.H сигнала сброса равен 0 В. Низкий уровень VRWS.L сигнала считывания равен -3 В, а высокий уровень VRWS.H сигнала считывания является 12 В. К тому же, на Фиг. 4 форма сигнала, обозначенная сплошной линией, представляет собой изменение потенциала VINT в том случае, когда количество света, падающего на фотодиод D1, мало, а форма сигнала, обозначенная пунктирной линией, представляет собой изменение потенциала VINT в том случае, когда на фотодиод D1 падает свет на уровне насыщения. ΔVSIG представляет собой разность потенциалов, пропорциональную количеству света, падающего на фотодиод D1. Из сравнения между обычным примером, показанным на Фиг. 63, и конфигурацией, показанной на Фиг. 4, ясно, что в оптическом датчике согласно данному варианту осуществления изобретения изменение потенциала накопительного узла в течение периода интегрирования TINT в том случае, когда падает свет на уровне насыщения, является меньшим, чем в обычном оптическом датчике. Однако оптический датчик согласно данному варианту осуществления изобретения усиливает потенциал накопительного узла и считывает его в течение периода считывания (периода, когда потенциал сигнала считывания имеет высокий уровень VRWS.H).

Здесь считывание выходного сигнала датчика из области 1 пикселей объяснено со ссылкой на Фиг. 4. Сначала, когда уровень сигнала сброса, подаваемого из драйвера 5 строк датчиков на линию RST, повышается с низкого уровня (VRST.L) до высокого уровня (VRST.H), фотодиод D1 имеет прямое смещение. В результате потенциал VINT точки INT соединения имеет величину, которая выражается следующей формулой (4):

VINT=VRST.H-VF, (4)

где VF - прямое напряжение фотодиода D1. Поскольку здесь VINT является более низким, чем пороговое напряжение транзистора M2, то транзистор M2 является непроводящим в течение периода сброса.

Затем, когда уровень сигнала сброса возвращается до низкого уровня VRST.L, начинается период интегрирования фотоэлектрического тока (TINT). В течение периода TINT интегрирования фотоэлектрический ток, пропорциональный количеству света, падающему на фотодиод D1, втекает в конденсатор C1, в силу чего конденсатор C1 разряжается. Это приводит к тому, что потенциал VINT точки INT соединения в конце периода TINT интегрирования имеет величину, которая выражается следующей формулой (5):

VINT=VRST.H-VF-∆VRST·CPD/CTOTAL-IPHOTO·tINT/CTOTAL (5)

где ΔVRST - высота импульса сигнала сброса (VRST.H - VRST.L); IPHOTO - фотоэлектрический ток фотодиода D1; tINT - продолжительность периода интегрирования; CPD - емкость фотодиода D1; а CTOTAL - емкость всей оптической схемы в целом, то есть, суммарная емкости точки INT соединения, равная сумме емкости CINT конденсатора C1, емкости CPD фотодиода D1 и емкости CTFT транзистора M2. К тому же, в течение периода интегрирования также, поскольку VINT является более низким, чем пороговое напряжение транзистора M2, то транзистор M2 является непроводящим.

После окончания периода интегрирования уровень сигнала считывания, подаваемого на линию RWS, повышается, и начинается период считывания. При этом происходит инжекция электрических зарядов в конденсатор C1. Когда потенциал VINT точки INT соединения становится более высоким, чем пороговое напряжение транзистора M2, то транзистор M2, становится проводящим. Следовательно, транзистор M2 вместе с транзистором M3 смещения, наличие которого обеспечено на конце линии OUT в каждом столбце, функционирует в качестве усилителя на истоковом повторителе. В оптическом датчике согласно данному варианту осуществления изобретения напряжение выходного сигнала с выходной линии SOUT со стока транзистора M3 является эквивалентным значению, полученному путем усиления интеграла фотоэлектрического тока фотодиода D1 в течение периода интегрирования. Описание принципов этого приведено ниже.

Как описано выше, в данном варианте осуществления изобретения инициализацию импульсом сброса, интегрирование фотоэлектрического тока в течение периода интегрирования и считывание выходного сигнала датчика в течение периода считывания, которые, как предполагают, составляют один цикл, выполняют циклически.

Ниже объяснена конкретная конфигурация оптического датчика согласно данному варианту осуществления изобретения со ссылкой на чертежи. На Фиг. 5 изображена эквивалентная электрическая схема оптического датчика согласно пятому варианту осуществления изобретения. На Фиг. 6 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно данному варианту осуществления изобретения. На Фиг. 7 на виде в увеличенном масштабе показана та область, где сформирован конденсатор C1. На Фиг. 8 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно данному варианту осуществления изобретения.

Как показано на Фиг. 5, оптический датчик согласно данному варианту осуществления изобретения включает в себя конденсатор C1, которым является конденсатор переменной емкости, в качестве усилительного элемента. В данном варианте осуществления изобретения конденсатор C1 представляет собой p-канальный MOS-конденсатор. Следует отметить, что на Фиг. 6 обеспечено наличие транзистора M2 в области между линиями COLg и COLb истоков, и обеспечено наличие двух наборов из конденсатора C1 и диода D1, соответственно, с обеих их сторон. В альтернативном варианте может быть обеспечено наличие только лишь одного набора из конденсатора C1 и диода D1. На задней стороне диода D1 обеспечено наличие светоэкранирующей пленки LS, предотвращающей падение света от задней подсветки на диод D1. Светоэкранирующая пленка LS имеет потенциал, который зафиксирован равным постоянному потенциалу VLS, по меньшей мере, во время работы оптического датчика.

За счет фиксации потенциала светоэкранирующей пленки LS равным постоянному потенциалу VLS может быть улучшена надежность фотодиода. В том случае, когда потенциал светоэкранирующей пленки LS является плавающим, возможны отклонения потенциала светоэкранирующей пленки LS от исходного значения вследствие переноса носителей заряда или инжекции, в силу чего может происходить изменение и ухудшение характеристик диода D1. Однако, эта проблема может быть решена путем фиксации потенциала светоэкранирующей пленки LS равным постоянному потенциалу VLS.

Помимо этого, могут быть уменьшены различия в характеристиках между множеством диодов D1. Это объясняется тем, что если потенциал светоэкранирующей пленки LS является плавающим, то светоэкранирующие пленки LS могут иметь различные плавающие потенциалы вследствие неравномерной зарядки ионов плазмы и т.п. в процессе обработки. В отличие от этого, эта задача может быть решена путем фиксации потенциала светоэкранирующей пленки LS равным постоянному потенциалу VLS.

Кроме того, могут быть уменьшены взаимные шумы различных сигналов для устройства отображения. Это объясняется следующим: поскольку светоэкранирующая пленка LS имеет емкостную связь с линиями COL истоков, электродами пикселей и т.д., то в случае, когда потенциал светоэкранирующей пленки LS является плавающим, на потенциал светоэкранирующей пленки LS влияют флуктуации потенциала различных сигналов для устройства отображения (потенциалы линий истоков, потенциалы электродов пикселей и т.д.). Такие флуктуации потенциала светоэкранирующей пленки LS дополнительно добавляют шумы к оптическому датчику. В отличие от этого, за счет фиксации потенциала светоэкранирующей пленки LS равным постоянному потенциалу VLS могут быть устранены флуктуации потенциала светоэкранирующей пленки LS, посредством чего может быть решена описанная выше задача.

Следует отметить, что предпочтительно удовлетворяется следующее соотношение:

VLS≥VRST.H ,

где VLS - постоянный потенциал светоэкранирующей пленки LS, а VRST.H - высокоуровневый потенциал сигнала сброса. Кроме того, более предпочтительно удовлетворяется следующее соотношение:

VLS≥VRST.H+Vth_p,

где Vth_p - пороговое напряжение p-канала диода D1. Причина этого будет подробно описана ниже.

Как показано на Фиг. 6, оптический датчик согласно данному варианту осуществления изобретения включает в себя транзистор M2 в области между линиями COLg и COLb истоков. Диод D1 представляет собой pin-диод с латеральной структурой, в котором на кремниевой пленке, служащей в качестве основы, последовательно сформированы следующие области: область полупроводника p-типа 102p, область 102i собственного полупроводника и область 102n полупроводника n-типа. Область 102p полупроводника p-типа функционируют в качестве анода фотодиода D1 и соединена с линией RST через линию 108 и контакты 109 и 110. Область 102n полупроводника n-типа функционирует в качестве катода фотодиода D1 и соединена с электродом 101 затвора транзистора M2 через продленный участок 107 кремниевой пленки, контакты 105 и 106, и линию 104.

В этой конфигурации линии RST и RWS сформированы из того же самого металла, что и металл электрода 101 затвора транзистора M2, и на том же самом слое тем же самым способом, что слой и способ, примененные для электрода 101 затвора. Кроме того, линии 104 и 108 сформированы из того же самого металла, что и металл линии COL истоков, и на том же самом слое тем же самым способом, что слой и способ, примененные для линии COL истоков. На задней стороне фотодиода D1 обеспечена металлическая пленка 113, которая функционирует в качестве светоэкранирующей пленки LS (см. Фиг. 5). Как описано выше, потенциал металлической пленки 113, служащей в качестве светоэкранирующей пленки, зафиксирован равным постоянному потенциалу VLS. Следовательно, металлическая пленка 113 соединена с линией 114. Линия 114 соединена с источником питания с постоянным напряжением (не показан), который расположен вне области 1 пикселей. Следует отметить, что показанная на Фиг. 6 конфигурация, в которой обеспечено наличие линии 114 для подачи постоянного потенциала VLS на металлическую пленку 113, функционирующую в качестве светоэкранирующей пленки LS, параллельно с линией сброса RST, приведена в качестве примера, но конфигурация относительно линии 114 не ограничена этим конкретным примером.

Кроме того, как показано на Фиг. 6 по Фиг. 8, конденсатор C1 сформирован посредством широкого участка 111, сформированного в линии RWS, продленного участка 107 кремниевой пленки и изоляционной пленки (не показана), обеспеченной между широким участком 111 и продленным участком 107. Другими словами, широкий участок 111, имеющий тот же самый потенциал, что и потенциал линии RWS, функционирует в качестве электрода затвора конденсатора C1. Область 112, показанная на Фиг. 7, представляет собой область p+, сформированную путем легирования кремниевой пленки n-типа примесью p-типа, например, бором. Следует отметить, что когда выполнено легирование примесью p-типа, то широкий участок 111 функционирует в качестве маски. Следовательно, как показано на Фиг. 8, продленный участок 107 становится областью p+, а участок кремниевой пленки ниже широкого участка 111 образует область n-.

Операция считывания с оптического датчика согласно данному варианту осуществления изобретения объяснена здесь ниже. На Фиг. 9 изображена временная диаграмма сигналов, на которой показано изменение потенциала VINT накопительного узла с момента окончания периода интегрирования до периода считывания. На Фиг. 9, форма w1 сигнала, обозначенная сплошной линией, отображает изменение потенциала VINT в том случае, когда количество света, падающего на фотодиод D1, мало. Форма сигнала w2, обозначенная пунктирной линией, отображает изменение потенциала VINT в том случае, когда свет падает на фотодиод D1. Момент времени t0 представляет собой момент времени, в который уровень сигнала считывания, подаваемого с линии RWS, начинает повышаться с низкого уровня VRWS.L. Момент времени t2 представляет собой момент времени, в который уровень сигнала считывания доходит до высокого уровня VRWS.H. Момент времени tS представляет собой момент времени, в который включается транзистор M2 и производится выборка выходного сигнала датчика. Момент времени t1 представляет собой момент времени, в который сигнал считывания достигает порогового напряжения Voff конденсатора C1. Другими словами, конденсатор, C1 имеет рабочие характеристики, которые изменяются в соответствии с количественным соотношением между потенциалом, который подают с сигнальной линии RWS считывания на широкий участок 111, и пороговым напряжением Voff.

На Фиг. 10A и Фиг. 10B изображены принципиальные схемы в разрезе, на которых показана разница в переносе зарядов вследствие потенциала электрода затвора (широкий участок 111) в конденсаторе C1. Как показано на Фиг. 9, Фиг. 10A и Фиг. 10B, до момента времени t1 конденсатор C1 всегда находится в состоянии "включен" (ON), а после момента времени t1 конденсатор C1 находится в состоянии "выключен" (OFF). Другими словами, когда потенциал линии RWS является равным пороговому напряжению Voff или более низким, то происходит перенос зарядов Qinj под электродом затвора (широким участком 111,) как показано на Фиг. 10A. Однако когда потенциал линии RWS превышает пороговое напряжение Voff, то перенос зарядов Qinj под электродом затвора (широким участком 111) не происходит, как показано на Фиг. 10B. Как описано выше, потенциал VINT(tS) накопительного узла в момент времени tS выборки после того, как потенциал сигнала считывания, поданный с сигнальной линии RWS считывания, достигает высокого уровня VRWS.H, выражается формулой (6), приведенной ниже. Следует отметить, что разность ΔVINT, показанная на Фиг. 4, эквивалентна разности между VINT(t0) и VINT(tS), которая равна Qinj/CINT.

[Математическая формула 1]

(6)

(6)

где

Как показано на Фиг. 9, в оптическом датчике согласно данному варианту осуществления изобретения разность потенциалов накопительного узла, вследствие разности освещенности на светоприемной поверхности после усиления, является большей, чем его разность потенциалов в конце периода интегрирования. Например, разность между потенциалом накопительного узла после усиления в течение периода считывания в случае темного состояния и потенциалом накопительного узла после усиления в течение периода считывания в том случае, когда падает свет на уровне насыщения, является более высокой, чем разность между потенциалом накопительного узла в конце периода накопления в случае темного состояния и потенциалом накопительного узла в конце периода накопления в том случае, когда падает свет на уровне насыщения. Следовательно, может быть реализован оптический датчик, имеющий высокую чувствительность и высокое отношение сигнал/шум.

Здесь объяснены преимущества оптического датчика согласно данному варианту осуществления изобретения со ссылкой на Фиг. 11 - Фиг. 13. Как описано выше, оптический датчик согласно данному варианту осуществления изобретения включает в себя светоэкранирующую пленку LS (см. Фиг. 5) для предотвращения падения света от задней подсветки на поверхность фотодиода D1 на стороне, противоположной стороне светоприемной поверхности, и потенциал светоэкранирующей пленки зафиксирован равным постоянному потенциалу VLS. Постоянный потенциал VLS удовлетворяет приведенному ниже соотношению с высокоуровневым потенциалом VRST.H сигнала сброса и пороговым напряжением Vth_p p-канала диода D1:

VLS≥VRST.H+Vth_p.

За счет установления постоянного потенциала VLS светоэкранирующей пленки LS, таким образом, может быть улучшена линейность фотодиода D1 в диапазоне низких значений освещенности. Объяснение принципов этого приведено ниже.

На Фиг. 11 на схематичном виде в поперечном разрезе показан pin-диод, имеющий латеральную структуру. Как показано на Фиг. 11, в том случае, когда обеспечено наличие светоэкранирующей пленки LS в окрестности pin-диода, имеющего латеральную структуру, что имеет место в оптическом датчике согласно данному варианту осуществления изобретения, паразитная емкость, созданная между диодом и этой светоэкранирующей пленкой LS, вызывает то, что диод функционирует как элемент с тремя выводами. В частности, светоэкранирующая пленка LS, p-слой и n-слой функционируют соответственно как затвор, анод и катод, и предполагают, что диод имеет три различных режима работы в зависимости от соотношения между потенциалом VLS затвора, то есть светоэкранирующей пленки LS, потенциалом VA анода и потенциалом VC катода.

На Фиг. 12A и Фиг. 12B изображены графики характеристики "зависимость Id от VLS", на которых показаны различия между тремя описанными выше режимами работы. Следует отметить, что Id представляет собой фототок диода. Следует отметить, что фототок представляет собой ток, генерируемый при падении света на диод в соответствии с количеством падающего света, и его также именуют фототоком. На Фиг. 12A изображен график, на котором показана зависимость между потенциалом VLS светоэкранирующей пленки LS и фототоком Id в том случае, когда потенциал VA анода равен -7 В, а потенциал VC катода равен 0 В. В примере, показанном на Фиг. 12A, характер поведения фототока Id в зависимости от потенциала VLS светоэкранирующей пленки LS меняется вблизи точки VLS=VC+Vth_p как точки разграничения. Здесь режим работы в интервале VLS≤VA+Vth_p именуют "режимом B", а режим работы в интервале VLS≥VA+Vth_p именуют "режимом A".

Кроме того, на Фиг. 12B изображен график, на котором показана зависимость между потенциалом VLS светоэкранирующей пленки LS и фототоком Id в том случае, когда потенциал VA анода равен -7 В, а потенциал VC катода равен -3 В. В примере, показанном на Фиг. 12B, характер поведения фототока Id в зависимости от потенциала VLS светоэкранирующей пленки LS меняется вблизи точки VLS=VA+Vth_p как точки разграничения, а также характер поведения фототока Id в зависимости от потенциала VLS светоэкранирующей пленки LS меняется вблизи точки VLS=VC+Vth_n как точки разграничения. Здесь режим работы в интервале VLS≤VA+Vth_p именуют "режимом B", режим работы в интервале VA+Vth_p≤VLS≤VC+Vth_n именуют "режимом A", а режим работы в диапазоне VC+Vth_n≤VLS именуют "режимом C".

Из Фиг. 12A и Фиг. 12B ясно, что в режиме A может быть получено стабильно высокое значение фототока Id, и линейность фототока относительно освещенности является превосходной. Следовательно, в данном варианте осуществления изобретения диод D1 предпочтительно работает в режиме A. В частности, в случае VA+Vth_p≤VLS≤VC+Vth_n (режим A) предполагают, что обе границы i-слоя в диоде со стороны p-слоя и со стороны n-слоя находятся в состоянии, в котором свободные электроны и положительные дырки имеют тенденцию к миграции. Следовательно, в режиме A фотоэлектрический ток стремится беспрепятственно протекать через диод, и имеет место тенденция уменьшения темнового тока. Следовательно, получено превосходное отношение сигнал/шум, и улучшена линейность фототока относительно освещенности.

С другой стороны, в случае VLS≤VA+Vth_p (режим B) предполагают, что граница i-слоя в диоде со стороны n-слоя находится в состоянии, в котором свободные электроны и положительные дырки имеют тенденцию к миграции, тогда как на границе i-слоя в диоде со стороны p-слоя i-слой препятствует протеканию электрического тока. В отличие от этого, в случае VC+Vth_n≤VLS (режим C) предполагают, что граница i-слоя в диоде со стороны p-слоя находится в состоянии, в котором свободные электроны и положительные дырки имеют тенденцию к миграции, тогда как на его границе со стороны n-слоя i-слой препятствует протеканию электрического тока. Следовательно, в случаях режимов B и C фотоэлектрический ток не может беспрепятственно протекать через диод, и имеет место тенденция увеличения темнового тока. Следовательно, превосходное отношение сигнал/шум не может быть получено.

Здесь распределение режимов A, B и C может быть представлено соотношением между потенциалом VA анода и потенциалом VLS светоэкранирующей пленки LS, которое показано на Фиг. 13. На Фиг. 13 незаштрихованная область является областью режима A, область, заштрихованная линиями справа вниз по диагонали, является областью режима B, а область, заштрихованная линиями слева вниз по диагонали, является областью режима C. Как описано выше, область режима A может быть выражена следующим образом:

VA+Vth_p≤VLS≤VC+Vth_n.

Область режима B может быть выражена следующим образом:

VLS≤VA+Vth_p.

Область режима C может быть выражена следующим образом:

VC+Vth_n≤VLS.

Среди точек T1, T2 и T3, показанных на Фиг. 13, T1 представляет собой координатную точку, отображающую VLS и VA в момент времени, в который уровень сигнала сброса, показанного на Фиг. 4, повышается до высокого уровня. Точка T2 соответствует моменту времени tRST, показанному на Фиг. 4 (то есть, моменту времени, когда уровень сигнала сброса переключают с высокого уровня на низкий уровень), а точка T3 соответствует моменту времени tRWS, показанному на Фиг. 4 (то есть моменту времени, когда уровень сигнала сброса переключают с низкого уровня на высокий уровень).

Здесь треугольник, образованный линиями, продолжающимися между точками T1 и T2, T2 и T3 и T3 и T1, предпочтительно находится в пределах области режима A. Следовательно, предпочтительно удовлетворяется приведенное ниже условие как необходимое условие, которое должно удовлетворяться для того, чтобы значение VLS в T1 не находилось в пределах области режима B, а находилось в пределах области режима A:

VLS≥VA+Vth_p.

Следует отметить, что потенциал VA анода в начале сброса равен высокоуровневому потенциалу VRST.H сигнала сброса, и, следовательно, вышеописанная формула может быть выражена следующим образом:

VLS≥VRST.H+Vth_p.

Следует отметить, что значение VLS не изменяется в течение периода от T1 до T2. Когда сигнал сброса переключают на низкий уровень в момент времени TRST, показанный на Фиг. 4, то начинается период накопления (T2 на Фиг. 13). Затем до тех пор, пока уровень сигнала считывания не будет переключен на высокий уровень в момент времени tRWS, показанный на Фиг. 4 (T3 на Фиг. 13), фотоэлектрический ток, соответствующий количеству принятого света, течет непрерывно, и значение VLS увеличивается. После того как сигнал считывания переключен на высокий уровень в точке T3, значение VLS возвращается к исходному состоянию (T1).

Поскольку в данном варианте осуществления изобретения в качестве конденсатора C1 использован конденсатор переменной емкости, то флуктуации потенциала VC катода в течение периода накопления ослаблены по сравнению с тем случаем, в котором используется обычный конденсатор (не являющийся конденсатором переменной емкости). Следовательно, VLS не сильно увеличивается в течение периода накопления (от точки T2 до точки T3 на Фиг. 13), что позволяет добиться работы в области режима A.

Чтобы заставить диод D1 не работать в области режима C в точке T3, желательно, чтобы коэффициент AAC усиления конденсатора C1 удовлетворял соотношению, представленному следующим выражением:

AAC≥VDD/(Vth_n-Vth_p),

где VDD - напряжение источника питания выходного транзистора M2. Если выполняется это соотношение, то можно добиться соответствия диапазона изменения потенциала VINT накопительного узла, выраженного как ΔVth=Vth_n -Vth_p, диапазону выходного напряжения от 0 В до VDD.

Как описано выше, за счет установления значения потенциала VLS светоэкранирующей пленки равным постоянному потенциалу, при котором должно удовлетворяться условие VLS≥VRST.H+Vth_p, можно добиться работы фотодиода D1 в режиме A с момента начала сброса до, по меньшей мере, начальной стадии периода накопления. Если диод работает в режиме B близко к началу сброса, то заметно явление ухудшения линейности, в особенности, в области низкой освещенности, что показано на Фиг. 12A и Фиг. 12B. Однако, как здесь объяснено, за счет того, что добиваются работы диода в режиме A после начала сброса, величина выходного сигнала датчика с высоким отношением сигнал/шум и превосходной линейностью при изменении освещенности также может быть получена даже в течение периода после начала сброса на протяжении начальной стадии периода накопления.

Несмотря на то, что в наиболее предпочтительном варианте потенциал светоэкранирующей пленки LS установлен равным постоянному потенциалу VLS, который удовлетворяет условию VLS≥VRST.H+Vth_p, может быть достигнут эффект улучшения характеристик диода D1, даже если постоянный потенциал VLS имеет величину, удовлетворяющую условию VLS≥VRST.H. Кроме того, даже если постоянный потенциал VLS имеет величину, которая не удовлетворяет условию VLS≥VRST.H, может быть достигнут эффект улучшения характеристик диода D1 по сравнению с тем случаем, когда потенциал светоэкранирующей пленки LS является плавающим.

Поскольку в данном варианте осуществления изобретения линии COLr, COLg и COLb истоков служат также и в качестве соответственно линий VDD, OUT и VSS, то для описанного выше оптического датчика необходимо отличать те моменты времени, когда сигналы данных об изображении для устройства отображения вводят через линии COLr, COLg и COLb истоков, с момента времени, когда производят считывание выходных сигналов с датчиков, что показано на Фиг. 14. В примере, показанном на Фиг. 14, выходной сигнал датчика считывают, используя период горизонтального гашения после окончания ввода данных об изображении для отображения в течение периода горизонтального сканирования.

Как показано на Фиг. 1, драйвер 4 столбцов датчиков включает в себя схему 41 считывания пикселей, оснащенных датчиками, усилитель 42 столбцов датчиков и схему 43 сканирования столбцов датчиков. Со схемой 41 считывания пикселей, оснащенных датчиками, соединена линия SOUT (см. Фиг. 2) для вывода выходного сигнала VSOUT датчика из области 1 пикселей. На Фиг. 1 выходной сигнал датчика с линии SOUTj (j= от 1 до N) обозначен как VSOUTj. Схема 41 считывания пикселей, оснащенных датчиками, выводит зарегистрированное пиковое напряжение VSj выходного сигнала VSOUTj датчика в усилитель 42 столбцов датчиков. Усилитель 42 столбцов датчиков включает в себя N усилителей столбцов, которые соответствуют соответственно N столбцам оптических датчиков в области 1 пикселей. Усилитель 42 столбцов датчиков усиливает зарегистрированное пиковое напряжение VSj (j= от 1 до N) усилителем для каждого столбца, в силу чего его выводят как VCOUT в буферный усилитель 6. Схема 43 сканирования столбцов датчиков выводит сигнал CSj (j= от 1 до N) выбора столбца в усилитель 42 столбцов датчиков для последовательного подключения усилителей столбцов из усилителя 42 столбцов датчиков к выходному сигналу буферного усилителя 6.

Здесь ниже объяснено функционирование драйвера 4 столбцов датчиков и буферного усилителя 6 после считывания выходного сигнала VSOUT датчика из области 1 пикселей со ссылкой на Фиг. 15 и Фиг. 16. На Фиг. 15 изображена принципиальная электрическая схема, на которой проиллюстрирована внутренняя конфигурация схемы 41 считывания пикселей, оснащенных датчиками. На Фиг. 16 изображена временная диаграмма сигналов, на которой показана зависимость между сигналом VRWS считывания, выходным сигналом VSOUT датчика и выходным сигналом VS из схемы считывания пикселей, оснащенных датчиками. Как описано выше, когда уровень сигнала считывания повышается до высокого уровня VRWS.H, то транзистор M2 становится проводящим, в силу чего транзисторы M2 и M3 образуют усилитель на истоковом повторителе. Это позволяет накапливать выходной сигнал VSOUT датчика в конденсаторе CSAM для выборок, входящем в состав схемы 41 считывания пикселей, оснащенных датчиками. Следовательно, как показано на Фиг. 16, после того как уровень сигнал считывания падает до низкого уровня VRWS.L, выходное напряжение VS из схемы 41 считывания пикселей, оснащенных датчиками, подаваемое в усилитель 42 столбцов датчиков, сохраняется на уровне, равном максимальному значению выходного сигнала VSOUT датчика в течение некоторого периода (trow) во время выбора соответствующей строки.

Ниже приведено объяснение функционирования усилителя 42 столбцов датчиков со ссылкой на Фиг. 17. Как показано на Фиг. 17, соответствующие выходные напряжения VSj (j= от 1 до N) столбцов вводят из схемы 41 считывания пикселей, оснащенных датчиками, в N усилителей столбцов, входящих в состав усилителя 42 столбцов датчиков. Как показано на Фиг. 17, каждый усилитель столбца составлен из транзисторов M6 и M7. Сигналы CSj выбора столбца, сгенерированные схемой 43 сканирования столбцов датчиков, становятся последовательно включенными (ON) относительно соответственно N столбцов в течение периода выбора (trow) для одной строки, в результате чего включается транзистор M6 соответствующего одного из N усилителей столбцов в усилителе 42 столбцов датчиков. Затем выводят только соответствующее одно из выходных напряжений VSj (j= от 1 до N) столбцов через соответствующий транзистор M6 в качестве выходного сигнала VCOUT из усилителя 42 столбцов датчиков. Буферный усилитель 6 дополнительно усиливает сигнал VCOUT, выведенный из усилителя 42 столбцов датчиков, и выводит его в качестве выходного сигнала VOUT панели (сигнала оптического датчика) в схему 8 обработки сигналов.

Следует отметить, что схема 43 сканирования столбцов датчиков может сканировать столбцы оптического датчика один за другим, как описано выше, но конфигурация не ограничена этим вариантом. Схема 43 сканирования столбцов датчиков может иметь конфигурацию для выполнения чересстрочного сканирования столбцов оптических датчиков. В альтернативном варианте схема 43 сканирования столбцов датчиков может быть сформирована как сканирующая схема многофазной адресации, например четырехфазной адресации.

В описанной выше конфигурации устройство отображения согласно данному варианту осуществления изобретения получает выходной сигнал VOUT панели в соответствии с количеством света, принятого фотодиодом D1, сформированным в каждом пикселе в области 1 пикселей. Выходной сигнал VOUT панели передают в схему 8 обработки сигналов, подвергают в ней аналого-цифровому преобразованию и накапливают в запоминающем устройстве (не показано) в качестве данных, выведенных из панели. Это означает, что в этом запоминающем устройстве накапливают то же самое количество наборов данных, выведенных из панели, что и количество пикселей (количество оптических датчиков) в области 1 пикселей. Схема 8 обработки сигналов выполняет операции обработки сигналов различных типов, например, захват изображения и обнаружение области, к которой прикоснулись, с использованием данных, выведенных из панели, которые накоплены в запоминающем устройстве. Следует отметить, что в данном варианте осуществления изобретения в запоминающем устройстве схемы 8 обработки сигналов накапливают то же самое количество наборов данных, выведенных из панели, что и количество пикселей (количество оптических датчиков) в области 1 пикселей, но с учетом ограничений, таких как, например, емкость запоминающего устройства, количество накопленных в нем наборов данных, выведенных из панели, не обязательно является тем же самым, что и количество пикселей.

Поскольку широкий участок 111 линии RWS служит также в качестве электрода затвора конденсатора C1, то конфигурация согласно первому варианту осуществления изобретения имеет преимущества, состоящие в том, что количество контактов (контактов 118, 119, показанных на Фиг. 24 применительно к описанию третьего варианта осуществления изобретения) является меньшим, в силу чего размер схемы оптического датчика может быть уменьшен по сравнению с третьим вариантом осуществления изобретения, описание которого приведено ниже. Кроме того, в конфигурации согласно первому варианту осуществления изобретения широкий участок 111 линии RWS расположен так, что экранирует накопительный узел INT от линии COL истоков. Следовательно, эта конфигурация имеет преимущество, состоящее в ослаблении шумовых помех в накопительном узле INT от линии COL истоков по сравнению с конфигурацией, в которой линия COL истоков расположена в слое над накопительным узлом INT, что имеет место, например, в конфигурации из третьего варианта осуществления изобретения, описание которой приведено ниже.

[Второй вариант осуществления изобретения]

Ниже приведено объяснение второго варианта осуществления настоящего изобретения. Элементы, имеющие те же самые функции, что и элементы из первого варианта осуществления изобретения, объяснение которого приведено выше, обозначены теми же самыми номерами позиций, что и соответствующие элементы в первом варианте осуществления изобретения, и их подробные объяснения опущены.

На Фиг. 18 изображена эквивалентная электрическая схема оптического датчика согласно данному варианту осуществления изобретения. На Фиг. 19 изображена временная диаграмма сигналов, на которой показаны сигнал сброса и сигнал считывания, подаваемые в оптический датчик согласно данному варианту осуществления изобретения. На Фиг. 20 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно данному варианту осуществления изобретения. На Фиг. 21 на виде в увеличенном масштабе изображена та область, где сформирован конденсатор C1. На Фиг. 22 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно данному варианту осуществления изобретения.

Как показано на Фиг. 18, оптический датчик согласно данному варианту осуществления изобретения отличается от оптического датчика из первого варианта осуществления изобретения тем, что конденсатором C1 является n-канальный MOS-конденсатор. Кроме того, диод D1 подключен в обратном направлении по сравнению с первым вариантом осуществления изобретения. В частности, катод диода D1 соединен с линией RST, а его анод соединен с накопительным узлом INT. Более того, транзистором M2 для считывания является p-канальный TFT. Помимо этого, как показано на Фиг. 19, предполагают, что высокие уровни и низкие уровни потенциалов сигнала сброса и сигнала считывания являются обратными по сравнению с первым вариантом осуществления изобретения.

Как показано на Фиг. 20, диод D1 представляет собой pin-диод с латеральной структурой, в котором на кремниевой пленке, служащей в качестве основы, последовательно сформированы область 102p полупроводника p-типа, область 102i собственного полупроводника и область 102n полупроводника n-типа, как и в первом варианте осуществления изобретения. Однако область 102n полупроводника n-типа (катод) соединена с линией RST через линию 108 и контакты 109 и 110. Область 102p полупроводника p-типа (анод) соединена с электродом 101 затвора транзистора M2 через продленный участок 107 кремниевой пленки, контакты 105 и 106 и линию 104.

Как показано на Фиг. 21 и Фиг. 22, конденсатор C1 сформирован посредством широкого участка 111, сформированного в линии RWS, продленного участка 107 кремниевой пленки и изоляционной пленки (не показана), обеспеченной между широким участком 111 и продленным участком 107. Другими словами, широкий участок 111, имеющий тот же самый потенциал, что и линия RWS, функционирует в качестве электрода затвора конденсатора C1. В данном варианте осуществления изобретения область 112, показанная на Фиг. 21, представляет собой область n+, сформированную путем легирования кремниевой пленки n-типа примесью n-типа, например фосфором. Когда выполнено легирование примесью n-типа, то широкий участок 111 функционирует в качестве маски. Следовательно, как показано на Фиг. 22, продленный участок 107 становится областью n+, а участок кремниевой пленки под широким участком 111 образует область n-.

В оптическом датчике данного варианта осуществления изобретения, имеющем описанную выше конфигурацию, соотношение между потенциалами является обратным по сравнению с первым вариантом осуществления изобретения. Следовательно, изменение потенциала накопительного узла INT в течение периода интегрирования и периода считывания предполагает наличие состояния, полученного путем обращения состояния, показанного на Фиг. 9 по вертикали в сочетании с описанием первого варианта осуществления изобретения. Следовательно, в оптическом датчике данного варианта осуществления изобретения разность потенциалов накопительного узла вследствие разности освещенности светоприемной поверхности после усиления также является большей, чем эта разность в конце периода интегрирования. Например, разность между потенциалом накопительного узла после усиления в течение периода считывания в случае темного состояния и потенциалом накопительного узла после усиления в течение периода считывания в том случае, когда падает свет на уровне насыщения, является большей, чем разность между потенциалом накопительного узла в конце периода накопления в случае темного состояния и потенциалом накопительного узла в конце периода накопления в том случае, когда падает свет на уровне насыщения. В результате может быть реализован оптический датчик, имеющий высокую чувствительность и высокое отношение сигнал/шум.

Помимо этого, посредством оптического датчика данного варианта осуществления изобретения также может быть получен выходной сигнал оптического датчика, имеющий превосходную линейность при изменении освещенности, как и в первом варианте осуществления изобретения, за счет фиксации потенциала светоэкранирующей пленки LS диода D1 равным постоянному потенциалу VLS и за счет установления значения постоянного потенциала VLS, удовлетворяющего следующему условию:

VLS≥VRST.H

или предпочтительно

VLS≥VRST.H+Vth_p.

[Третий вариант осуществления изобретения]

Ниже приведено объяснение третьего варианта осуществления настоящего изобретения. Элементы, имеющие те же самые функции, что и элементы из объясненных выше вариантов осуществления изобретения, обозначены теми же самыми номерами позиций, что и соответствующие элементы в описанных выше вариантах осуществления изобретения, и их подробные объяснения опущены.

На Фиг. 23 изображена эквивалентная электрическая схема оптического датчика согласно данному варианту осуществления изобретения. На Фиг. 24 на виде сверху показана приведенная в качестве примера планарная структура оптического датчика согласно данному варианту осуществления изобретения. На Фиг. 25 на виде в увеличенном масштабе изображена та область, в которой сформирован конденсатор C1. На Фиг. 26 на схематичном виде в поперечном разрезе показана схема соединений соответствующих областей в оптическом датчике согласно данному варианту осуществления изобретения.