Предлагаемое изобретение относится к области радиотехники и связи и может использоваться в структуре радиоприемных устройств ВЧ и СВЧ диапазонов.

В современных системах телекоммуникаций в качестве смесителей двух сигналов находят применение различные модификации перемножающей ячейки Джильберта [1-24] (термин «ячейка Джильберта» широко используется в микроэлектронике, см., например, патент №7.054.609 и обозначает «перемножающую» архитектуру на основе двух дифференциальных каскадов с перекрестным включением коллекторов входных транзисторов).

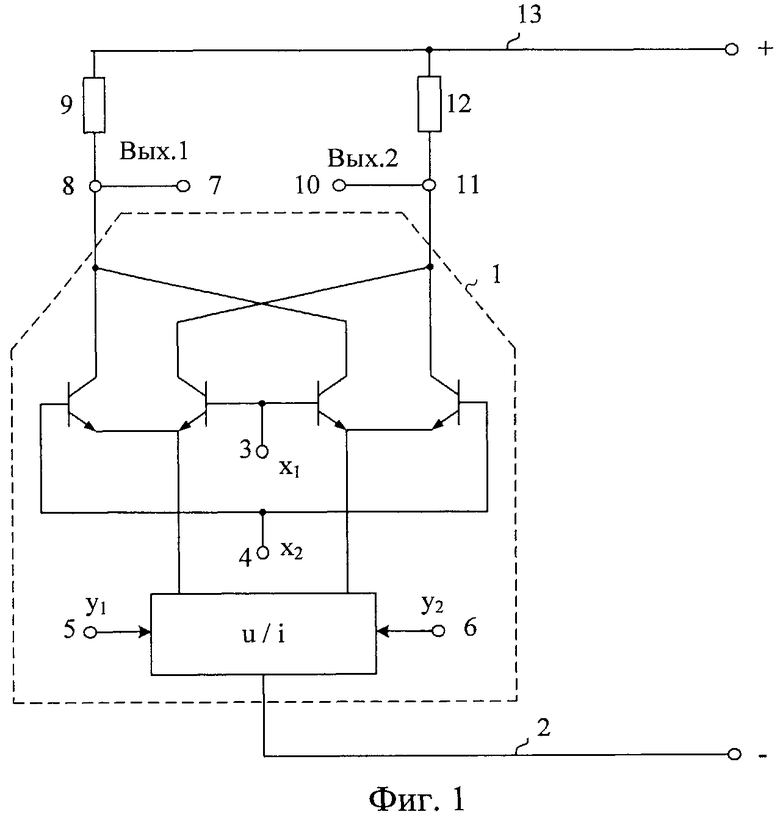

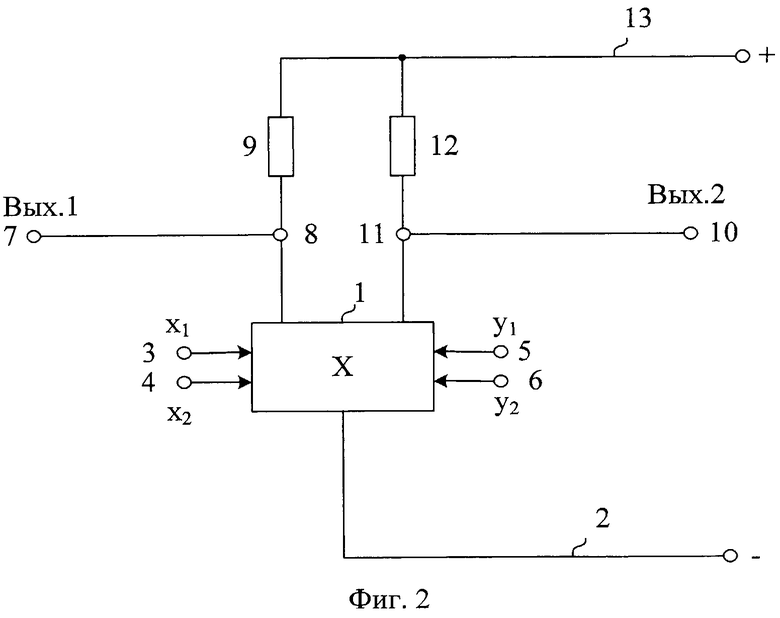

Ближайшим прототипом заявляемого устройства является аналоговый смеситель сигналов фиг.1, представленный в патентной заявке США №2008/113644, fig.2 (данная архитектура присутствует также в патентной заявке US 2006/0164149, fig.5, патенте US 7.812.775 fig.16 и др. [1-24]). Он содержит входную перемножающую ячейку Джильберта 1, эмиттерная цепь которой согласована с первой 2 шиной источника питания, первый 3 и второй 4 входы канала «X» перемножающей ячейки Джильберта 1, первый 5 и второй 6 входы канал «Y» перемножающей ячейки Джильберта 1, первый 7 выход устройства, соединенный с первым 8 токовым выходом перемножающей ячейки Джильберта 1 и первым выводом первого 9 резистора нагрузки, второй 10 выход устройства, соединенный со вторым 11 токовым выходом перемножающей ячейки Джильберта 1 и первым выводом второго 12 резистора нагрузки, причем второй вывод первого 9 резистора нагрузки и второй вывод второго 12 резистора нагрузки связаны со второй 13 шиной источника питания.

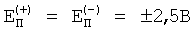

Существенный недостаток известного смесителя состоит в том, что он имеет малый коэффициент преобразования по напряжению (Ку), характеризующий уровень его основных выходных гармоник с частотами fx+fy и fx-fy при заданных значениях амплитуд и частот входных сигналов ux(fx) и uy(fy). Небольшие значения Ку АС-прототипа обусловлены ограничениями на численные значения сопротивлений резисторов нагрузки 9 и 12, которые при малых напряжениях питания (например,  ) должны выбираться сравнительно низкоомными.

) должны выбираться сравнительно низкоомными.

Основная задача предлагаемого изобретения состоит в повышении коэффициента преобразования Ку смесителя для его основных fx+fy, fx-fy выходных гармоник при низковольтном питании.

Поставленная задача решается тем, что в аналоговом смесителе двух сигналов, содержащем входную перемножающую ячейку Джильберта 1, эмиттерная цепь которой согласована с первой 2 шиной источника питания, первый 3 и второй 4 входы канала «X» перемножающей ячейки Джильберта 1, первый 5 и второй 6 входы канала «Y» перемножающей ячейки Джильберта 1, первый 7 выход устройства, соединенный с первым 8 токовым выходом перемножающей ячейки Джильберта 1 и первым выводом первого 9 резистора нагрузки, второй 10 выход устройства, соединенный со вторым 11 токовым выходом перемножающей ячейки Джильберта 1 и первым выводом второго 12 резистора нагрузки, причем второй вывод первого 9 резистора нагрузки и второй вывод второго 12 резистора нагрузки связаны со второй 13 шиной источника питания, предусмотрены новые элементы и связи - второй вывод первого 9 резистора нагрузки связан со второй 13 шиной источника питания через первый 14 дополнительный резистор и через первый 15 двухполюсник с малым дифференциальным сопротивлением по переменному току связан с эмиттером первого 16 дополнительного транзистора, коллектор которого подключен к первому 8 токовому выходу перемножающей ячейки Джильберта 1, второй вывод второго 12 резистора нагрузки связан со второй 13 шиной источника питания через второй 17 дополнительный резистор и через второй 18 двухполюсник с малым дифференциальным сопротивлением по переменному току связан с эмиттером второго 19 дополнительного транзистора, коллектор которого подключен ко второму 11 токовому выходу перемножающей ячейки Джильберта 1, эмиттер первого 16 дополнительного транзистора связан с первой 2 шиной источника питания через первый 20 дополнительный токостабилизирующий двухполюсник, эмиттер второго 19 дополнительного транзистора связан с первой 2 шиной источника питания через второй 21 дополнительный токостабилизирующий двухполюсник, причем база первого 16 дополнительного транзистора соединена с выходом 22 первой цепи установления статического режима, а база второго 19 дополнительного транзистора соединена с выходом 23 второй цепи установления статического режима.

На чертеже фиг.1 представлена схема АС-прототипа, который содержит конкретное выполнение входной перемножающей ячейки Джильберта 1, а на чертежах фиг.2 схема АС-прототипа фиг.1, на которой входная перемножающая ячейка Джильберта 1 обозначена в виде функционального узла 1.

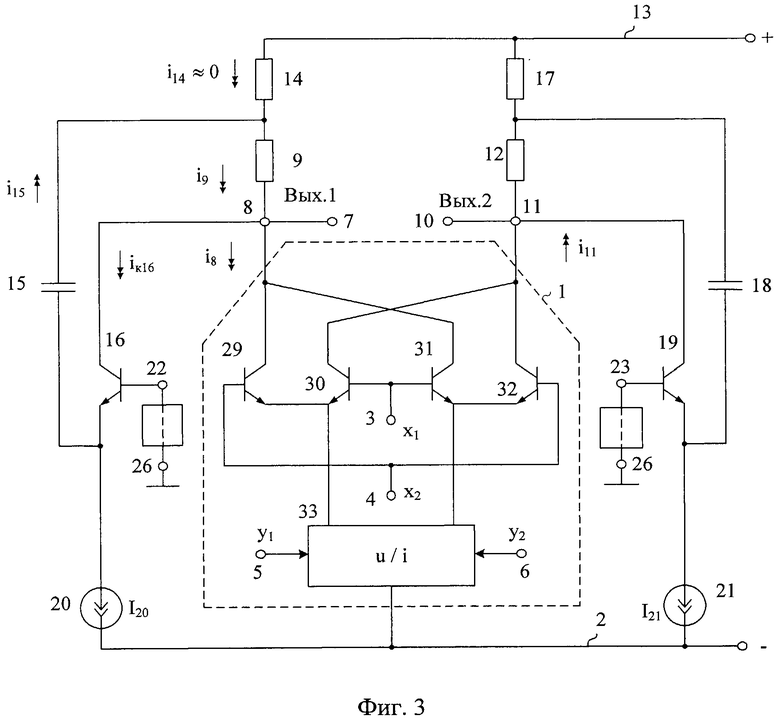

На чертеже фиг.3 представлена схема заявляемого АС в соответствии с п.1 формулы изобретения.

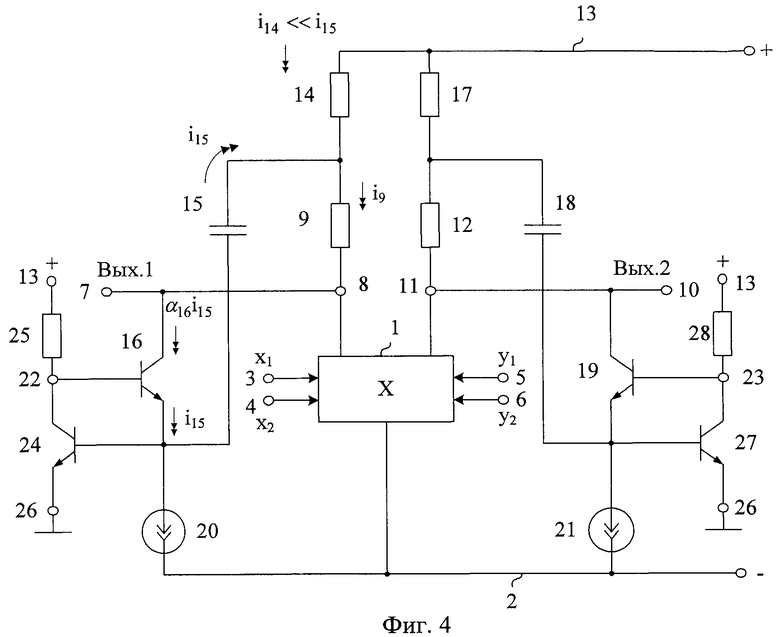

На чертеже фиг.4 приведена заявляемая схема АС, соответствующая п.2 и п.3 формулы изобретения.

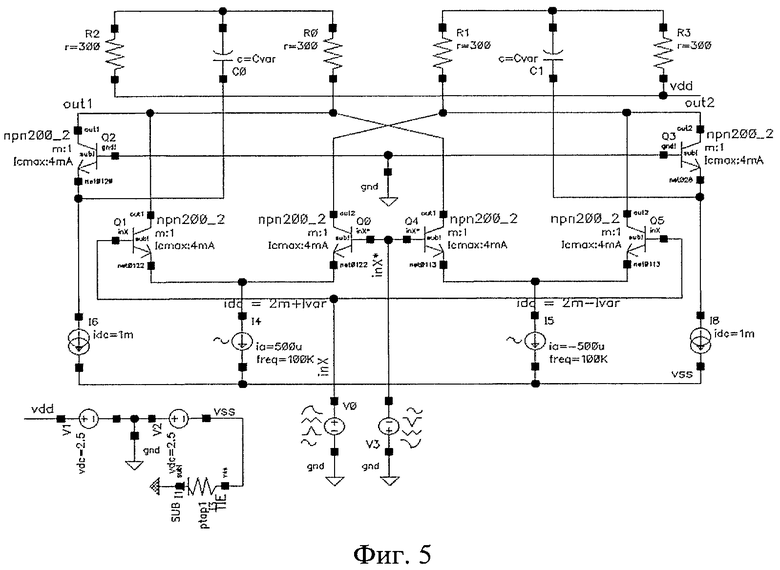

На чертеже фиг.5 представлена схема предлагаемого смесителя в среде Cadence на моделях SiGe интегральных транзисторов при Ivar=500 мкА (управление по каналу «Y»: I4=2 мА+Ivar; I5=2 мА-Ivar).

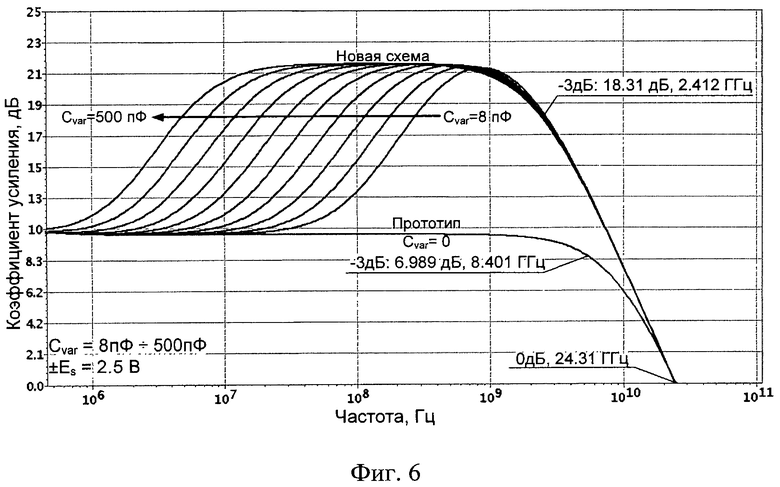

На чертеже фиг.6 показаны логарифмические амплитудно-частотные характеристики коэффициента усиления по напряжению АС фиг.5 при Ivar=500 мкА и изменении емкости конденсаторов 15 и 18 в диапазоне 0-500 пФ (двухполюсников 15 и 18 с малым дифференциальным сопротивлением для переменного тока).

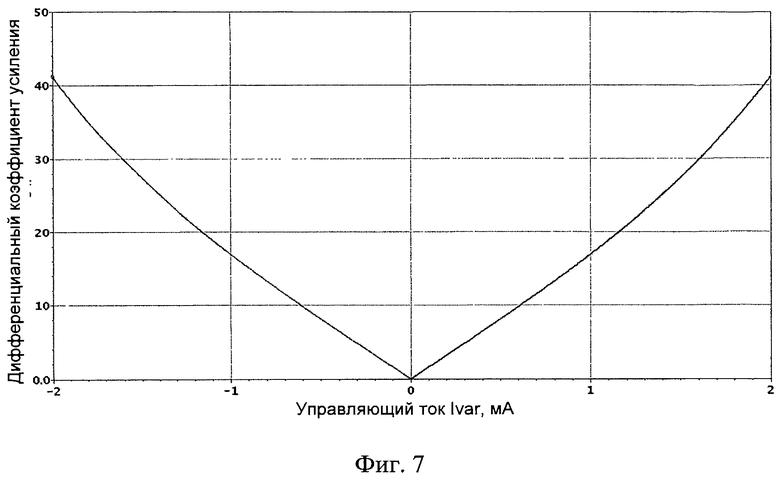

На чертеже фиг.7 показана зависимость модуля коэффициента усиления по напряжению Ку смесителя фиг.5 от тока управления (Ivar) по каналу «Y».

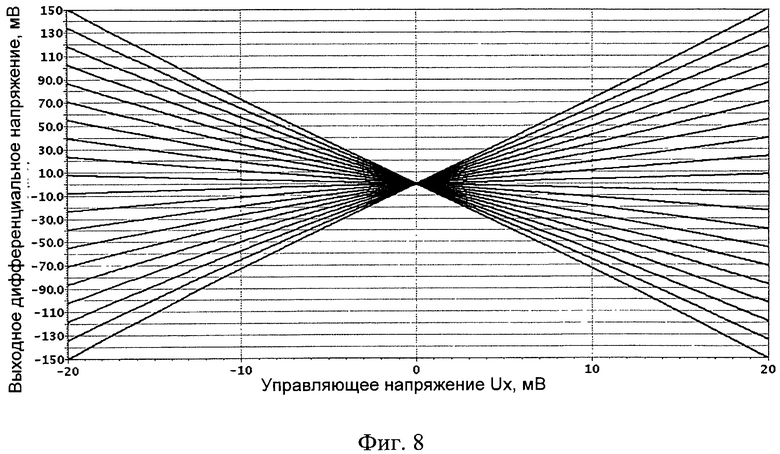

На чертеже фиг.8 приведена зависимость выходного дифференциального напряжения смесителя фиг.5 от напряжения по каналу «X» при разных напряжениях (токах управления Ivar) канала «Y».

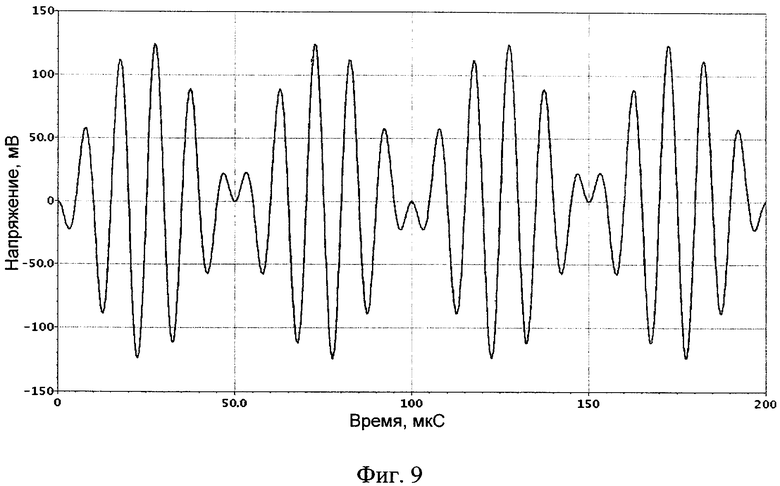

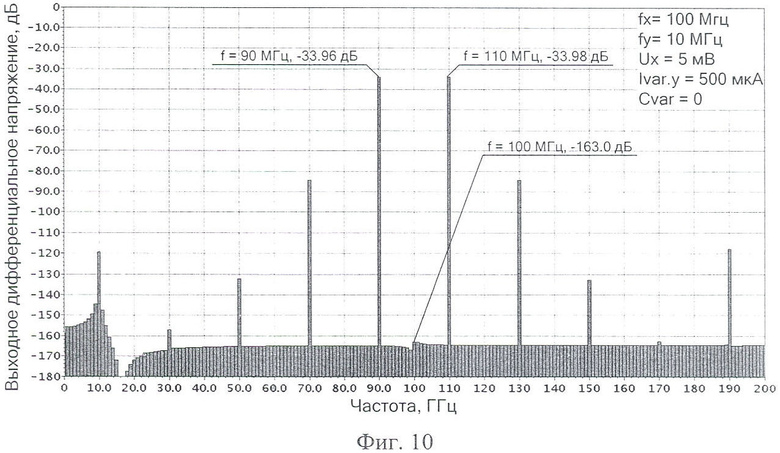

На чертеже фиг.9 представлена осциллограмма выходного сигнала смесителя фиг.5, а на чертеже фиг.10 - спектр выходного сигнала смесителя-прототипа при Cvar=0 и fx=100 МГц, fy=10 МГц, Ux=5 мВ, Iy=Ivar=500 мкА.

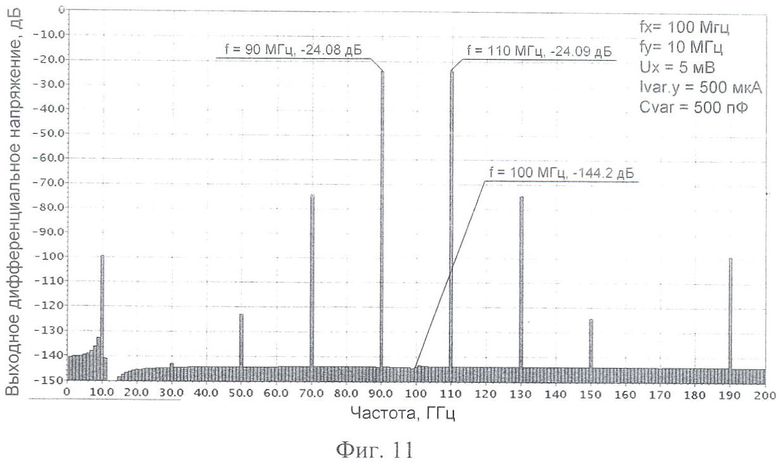

На чертеже фиг.11 показан спектр выходных сигналов заявляемого АС фиг.5, в котором емкость конденсаторов 15 и 18 (двухполюсников 15 и 18 с малым дифференциальным сопротивлением для переменного тока) равна 500 пФ.

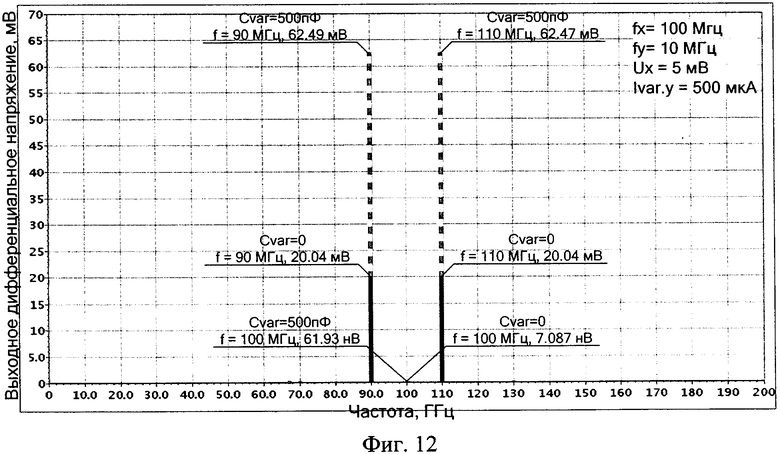

На чертеже фиг.12 показан спектр выходных сигналов сравниваемых смесителей (новая схема - Cvar=500 пФ, прототип - Cvar=0).

Заявляемый смеситель двух сигналов фиг.3 содержит входную перемножающую ячейку Джильберта 1, эмиттерная цепь которой согласована с первой 2 шиной источника питания, первый 3 и второй 4 входы канала «X» перемножающей ячейки Джильберта 1, первый 5 и второй 6 входы канала «Y» перемножающей ячейки Джильберта 1, первый 7 выход устройства, соединенный с первым 8 токовым выходом перемножающей ячейки Джильберта 1 и первым выводом первого 9 резистора нагрузки, второй 10 выход устройства, соединенный со вторым 11 токовым выходом перемножающей ячейки Джильберта 1 и первым выводом второго 12 резистора нагрузки, причем второй вывод первого 9 резистора нагрузки и второй вывод второго 12 резистора нагрузки связаны со второй 13 шиной источника питания. Второй вывод первого 9 резистора нагрузки связан со второй 13 шиной источника питания через первый 14 дополнительный резистор и через первый 15 двухполюсник с малым дифференциальным сопротивлением по переменному току связан с эмиттером первого 16 дополнительного транзистора, коллектор которого подключен к первому 8 токовому выходу перемножающей ячейки Джильберта 1, второй вывод второго 12 резистора нагрузки связан со второй 13 шиной источника питания через второй 17 дополнительный резистор и через второй 18 двухполюсник с малым дифференциальным сопротивлением по переменному току связан с эмиттером второго 19 дополнительного транзистора, коллектор которого подключен ко второму 11 токовому выходу перемножающей ячейки Джильберта 1, эмиттер первого 16 дополнительного транзистора связан с первой 2 шиной источника питания через первый 20 дополнительный токостабилизирующий двухполюсник, эмиттер второго 19 дополнительного транзистора связан с первой 2 шиной источника питания через второй 21 дополнительный токостабилизирующий двухполюсник, причем база первого 16 дополнительного транзистора соединена с выходом 22 первой цепи установления статического режима, а база второго 19 дополнительного транзистора соединена с выходом 23 второй цепи установления статического режима.

На чертеже фиг.4, в соответствии с п.2 формулы изобретения, первая цепь установления статического режима содержит третий 24 дополнительный транзистор, коллектор которого связан с выходом 22 первой цепи установления статического режима и через третий 25 дополнительный резистор подключен ко второй 13 шине источника питания, причем эмиттер третьего 24 дополнительного транзистора соединен с третьей 26 шиной источников питания, а его база подключена к эмиттеру первого 16 дополнительного транзистора.

Кроме этого, на чертеже фиг.4, в соответствии с п.3 формулы изобретения, вторая цепь установления статического режима содержит четвертый 27 дополнительный транзистор, коллектор которого связан с выходом 23 второй цепи установления статического режима и через четвертый 28 дополнительный резистор подключен ко второй 13 шине источника питания, причем эмиттер четвертого 27 дополнительного транзистора соединен с третьей 26 шиной источников питания, а его база подключена к эмиттеру второго 19 дополнительного транзистора.

В качестве первого 15 и второго 18 двухполюсников с малым дифференциальным сопротивлением по переменному току авторы рекомендуют использовать конденсаторы, стабилитроны, цепочки прямосмещенных p-n-p переходов или более сложные транзисторные схемы (диоды Видлара и т.п.).

В частном случае фиг.3 перемножающая ячейка Джильберта 1 выполнена на транзисторах 29-32 и преобразователе «напряжение-ток» 33, который реализуется по традиционным схемам. Для ряда вариантов построения АС фиг.3 в качестве первой и второй цепей установления статического режима с выходами 22 и 23 может использоваться третья 26 (общая) шина источников питания (2, 13).

Рассмотрим работу АС фиг.3.

Синусоидальные напряжения первого смешиваемого сигнала ux (на входах канала «X» 3, 4) и второго смешиваемого сигнала uy (на входах канала «Y» 5, 6) «перемножаются» традиционным образом в ячейке Джильберта 1. При этом переменный выходной ток i8 (i11) ячейки Джильберта 1 имеет спектр, совпадающий по форме со спектром, представленным на чертеже фиг.11.

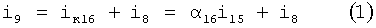

Приращение тока i9 через первый 9 резистор нагрузки определяется суммой переменного выходного тока i8 ячейки Джильберта 1 и коллекторного тока (iк16) транзистора 16:

где α16≤1 - коэффициент усиления по току эмиттера транзистора 16;

i15 - ток двухполюсника 15.

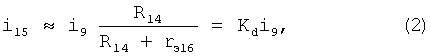

Причем для диапазона частот, в котором можно пренебречь сопротивлением двухполюсника 15 на переменном токе

где R14 - сопротивление первого 14 дополнительного резистора (R14<<R9);

rэ16 - дифференциальное сопротивление эмиттерного перехода транзистора 16 (rэ16<<R14);

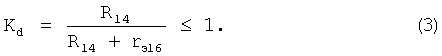

Kd - коэффициент деления тока i9 между резистором 14 (R14) и входным сопротивлением транзистора 16 (rэ16) в схеме с общей базой:

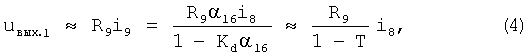

Таким образом, в рабочем диапазоне частот, когда влиянием сопротивления двухполюсника 15 можно пренебречь, переменное напряжение uвых.1 на выходе 7 АС фиг.3

где  ≈1.

≈1.

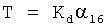

Таким образом, если обеспечить Т≈1 (Kd≈1, α16≈1), то амплитуда выходного напряжения для основных гармоник с частотами fx-fy и fx+fy в АС фиг.3 будет в Nc - раз больше, чем в АС-прототипе фиг.1, где

Данные выводы подтверждаются результатами компьютерного моделирования АС фиг.5, показанными на чертежах фиг.6, а также фиг.10, фиг.11 и фиг.12. Заявляемый АС имеет более высокий коэффициент преобразования Ку, характеризующий уровень преобразования сигналов ux и uy в амплитуды выходных гармоник fx+fy и fx-fy.

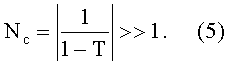

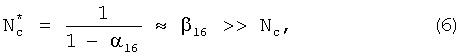

Дальнейшее повышение Ку в схеме фиг.3 связано с уменьшением отношения rэ16/R14→0. В этом (предельном) случае выигрыш  по Ку будет достигать значения

по Ку будет достигать значения

где β16=50÷150 - коэффициент усиления по току базы транзистора 16.

В тех случаях, когда отношение R14/rэ16 получается небольшим, выигрыш по Кy, соответствующий (6), реализуется в схеме фиг.4 (п.2, п.3 формулы изобретения), в которой за счет местной отрицательной обратной связи (транзисторы 24, 25) обеспечивается близкая к единице передача тока i15(i18) в коллектор транзистора 16 (19).

Если стоит задача расширения диапазона рабочих частот АС в сторону более низких частот fx, fy, то в качестве двухполюсников 15 и 18 целесообразно применять, например, цепочки из нескольких p-n переходов.

Таким образом, заявляемый смеситель двух сигналов имеет существенные преимущества в сравнении с прототипом, а также другими АС с малым напряжением питания.

Предлагаемое техническое решение существенно улучшает основной технический параметр (коэффициент преобразования) большого класса низковольтных смесителей сигналов Джильберта, защищенных более 300 патентами ведущих микроэлектронных фирм мира.

Библиографический список

1. Патентная заявка US №2008/113644

2. Патентная заявка US №2006/0232334, fig.1

3. Патент US №4.965.528, fig.2

4. Патент US №6.744.308

5. Патент US №7.633.328

6. Патент US №7.110.740

7. Патентная заявка US №2009/0085663, fig.2

8. Патент US №7.514.981, fig.1

9. А.св. СССР №642843

10. Патент US №5.933.771, fig.2

11. Патент US №6.016.079, fig.4

12. Патент US №5.057.784

13. Патент US №4.286.226

14. Патентная заявка US №2008/0261552, fig.1

15. Патент US №6.373.345, fig.2

16. Патентная заявка US №2010/0164595, fig.2

17. Патентная заявка US №2010/0141325

18. Патент US №4.344.188, fig.1, fig.3

19. Патент ЕР 1455441

20. Патент US №7.812.775, fig.20, fig.16

21. Патент ЕР 2235559, fig.3

22. Патент US №7.676.212, fig.2

23. Патентная заявка US №2008/0180156, fig.1, fig.5

24. Патент US №5.825.231, fig.1

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ ДВУХ СИГНАЛОВ С ВЫХОДНЫМ КАСКОДОМ | 2011 |

|

RU2450353C1 |

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ ДВУХ СИГНАЛОВ | 2011 |

|

RU2458456C1 |

| СМЕСИТЕЛЬ СИГНАЛОВ | 2011 |

|

RU2452010C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419188C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2010 |

|

RU2419145C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419190C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419189C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2013 |

|

RU2530259C1 |

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2012 |

|

RU2504072C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

Изобретение относится к области радиотехники и связи и может использоваться в структуре радиоприемных устройств ВЧ и СВЧ диапазонов. Технический результат заключается в повышении коэффициента преобразования Ку смесителя для его основных fx+fy, fx-fy выходных гармоник при низковольтном питании. Аналоговый смеситель двух сигналов содержит входную перемножающую ячейку Джильберта, первый и второй дополнительные транзисторы, первый и второй резисторы нагрузки, первый и второй дополнительные резисторы, первый и второй двухполюсники с малым дифференциальным сопротивлением по переменному току, первая и вторая цепи установления статического режима, первый и второй дополнительные токостабилизирующие двухполюсники. 2 з.п. ф-лы, 12 ил.

1. Аналоговый смеситель двух сигналов, содержащий входную перемножающую ячейку Джильберта (1), эмиттерная цепь которой согласована с первой (2) шиной источника питания, первый (3) и второй (4) входы канала «X» перемножающей ячейки Джильберта (1), первый (5) и второй (6) входы канал «Y» перемножающей ячейки Джильберта (1), первый (7) выход устройства, соединенный с первым (8) токовым выходом перемножающей ячейки Джильберта (1) и первым выводом первого (9) резистора нагрузки, второй (10) выход устройства, соединенный со вторым (11) токовым выходом перемножающей ячейки Джильберта (1) и первым выводом второго (12) резистора нагрузки, причем второй вывод первого (9) резистора нагрузки и второй вывод второго (12) резистора нагрузки связаны со второй (13) шиной источника питания, отличающийся тем, что второй вывод первого (9) резистора нагрузки связан со второй (13) шиной источника питания через первый (14) дополнительный резистор и через первый (15) двухполюсник с малым дифференциальным сопротивлением по переменному току связан с эмиттером первого (16) дополнительного транзистора, коллектор которого подключен к первому (8) токовому выходу перемножающей ячейки Джильберта (1), второй вывод второго (12) резистора нагрузки связан со второй (13) шиной источника питания через второй (17) дополнительный резистор и через второй (18) двухполюсник с малым дифференциальным сопротивлением по переменному току связан с эмиттером второго (19) дополнительного транзистора, коллектор которого подключен ко второму (11) токовому выходу перемножающей ячейки Джильберта (1), эмиттер первого (16) дополнительного транзистора связан с первой (2) шиной источника питания через первый (20) дополнительный токостабилизирующий двухполюсник, эмиттер второго (19) дополнительного транзистора связан с первой (2) шиной источника питания через второй (21) дополнительный токостабилизирующий двухполюсник, причем база первого (16) дополнительного транзистора соединена с выходом (22) первой цепи установления статического режима, а база второго (19) дополнительного транзистора соединена с выходом (23) второй цепи установления статического режима.

2. Аналоговый смеситель двух сигналов по п.1, отличающийся тем, что первая цепь установления статического режима содержит третий (24) дополнительный транзистор, коллектор которого связан с выходом (22) первой цепи установления статического режима и через третий (25) дополнительный резистор подключен ко второй (13) шине источника питания, причем эмиттер третьего (24) дополнительного транзистора соединен с третьей (26) шиной источников питания, а его база подключена к эмиттеру первого (16) дополнительного транзистора.

3. Аналоговый смеситель двух сигналов по п.2, отличающийся тем, что вторая цепь установления статического режима содержит четвертый (27) дополнительный транзистор, коллектор которого связан с выходом (23) второй цепи установления статического режима и через четвертый (28) дополнительный резистор подключен ко второй (13) шине источника питания, причем эмиттер четвертого (27) дополнительного транзистора соединен с третьей (26) шиной источников питания, а его база подключена к эмиттеру второго (19) дополнительного транзистора.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2389071C1 |

| НИЗКОВОЛЬТНЫЙ АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2009 |

|

RU2394358C1 |

Авторы

Даты

2012-05-10—Публикация

2011-04-20—Подача