Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления канала «Y». Аналоговый смеситель сигналов (АСС) является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов.

Аналоговые смесители сигналов реализуются в основном в виде перемножающей ячейки Гильберта, которая совершенствовалась в более чем 50 патентах ведущих микроэлектронных фирм. В этом смысле АСС является базовым функциональным узлом современной микроэлектроники, определяющим качественные показатели многих систем связи. Предлагаемое изобретение относится к данному классу устройств.

Среди известных АСС можно выделить подкласс устройств, в которых один из перемножаемых сигналов (как правило, канала «Y») подается в эмиттерные цепи входных дифференциальных каскадов АСС через последовательно соединенные резисторы и конденсаторы [1-10].

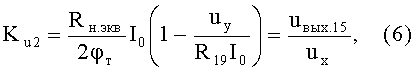

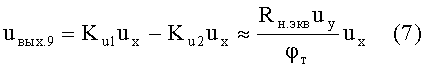

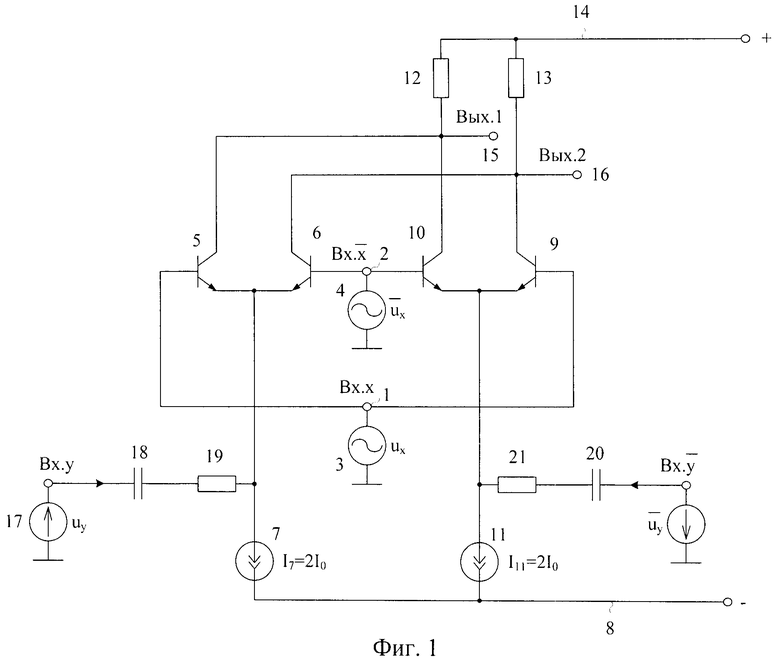

Ближайшим прототипом заявляемого устройства, архитектура которого присутствует также и в других АСС [1-10], является аналоговый смеситель сигналов фиг.1 по патентной заявке US №2010/0327939, fig 4, содержащий первый 1 и второй 2 противофазные входы, к которым подключены соответствующие первый 3 и второй 4 источники сигналов канала «X», первый 5 и второй 6 входные транзисторы, базы которых подключены к соответствующим первому 1 и второму 2 противофазным входам, а объединенные эмиттеры через первый 7 токостабилизирующий двухполюсник соединены с первой 8 шиной источника питания, третий 9 и четвертый 10 входные транзисторы, базы которых подключены к соответствующим первому 1 и второму 2 противофазным входам, а эмиттеры соединены с первым выводом второго 11 токостабилизирующего двухполюсника, первый 12 и второй 13 двухполюсники нагрузки, включенные между второй 14 шиной источника питания и соответствующими первым 15 и вторым 16 выходами устройства, связанными с коллекторами соответствующих первого 5 и второго 6 входных транзисторов, источник входного напряжения канала «Y» 17, связанный с эмиттерами первого 5 и второго 6 входных транзисторов через последовательно соединенные первый 18 конденсатор и первый 19 вспомогательный резистор, последовательно соединенные второй 20 конденсатор и второй 21 вспомогательный резистор.

Существенный недостаток известного смесителя состоит в том, что для обеспечения его работоспособности необходимо иметь два противофазных сигнала по каналу «Y», что требует применения специальных фазорасщепителей - так называемых «балунов» (bulun). В конечном итоге введение фазорасщепителей и их фазовая погрешность отрицательно сказываются на качестве смешения (перемножения) двух сигналов канала «X» и канала «Y».

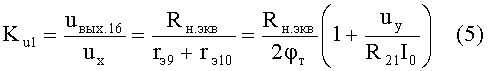

Основная задача предлагаемого изобретения состоит в обеспечении работоспособности смесителя сигналов при однофазном управлении по каналу «Y».

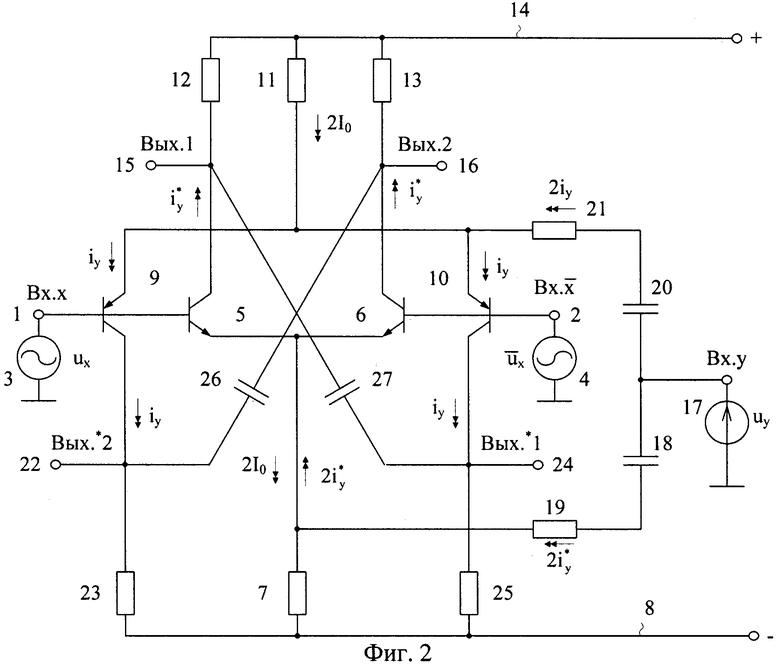

Поставленная задача решается тем, что в АСС фиг.1, содержащем первый 1 и второй 2 противофазные входы, к которым подключены соответствующие первый 3 и второй 4 источники сигналов канала «X», первый 5 и второй 6 входные транзисторы, базы которых подключены к соответствующим первому 1 и второму 2 противофазным входам, а объединенные эмиттеры через первый 7 токостабилизирующий двухполюсник соединены с первой 8 шиной источника питания, третий 9 и четвертый 10 входные транзисторы, базы которых подключены к соответствующим первому 1 и второму 2 противофазным входам, а эмиттеры соединены с первым выводом второго 11 токостабилизирующего двухполюсника, первый 12 и второй 13 двухполюсники нагрузки, включенные между второй 14 шиной источника питания и соответствующими первым 15 и вторым 16 выходами устройства, связанными с коллекторами соответствующих первого 5 и второго 6 входных транзисторов, источник входного напряжения канала «Y» 17, связанный с эмиттерами первого 5 и второго 6 входных транзисторов через последовательно соединенные первый 18 конденсатор и первый 19 вспомогательный резистор, последовательно соединенные второй 20 конденсатор и второй 21 вспомогательный резистор, предусмотрены новые элементы и связи - второй 11 токостабилизирующий двухполюсник включен между объединенными эмиттерами третьего 9 и четвертого 10 входных транзисторов и второй 14 шиной источников питания, источник входного напряжения канала «Y» 17 соединен с объединенными эмиттерами третьего 9 и четвертого 10 входных транзисторов через последовательно соединенные второй 20 конденсатор и второй 21 вспомогательный резистор, коллектор третьего 9 входного транзистора, соединенный с третьим 22 выходом устройства, связан с первой 8 шиной источника питания через третий 23 двухполюсник нагрузки, коллектор четвертого 10 входного транзистора связан с четвертым 24 выходом устройства и подключен к первой 8 шине источника питания через четвертый 25 двухполюсник нагрузки, причем второй 16 выход устройства связан с третьим 22 выходом устройства через третий 26 конденсатор, а первый 15 выход устройства соединен с четвертым 24 выходом устройства через четвертый 27 конденсатор.

На чертеже фиг.1 показана схема АСС-прототипа, а на чертеже фиг.2 - схема заявляемого АСС в соответствии с формулой изобретения.

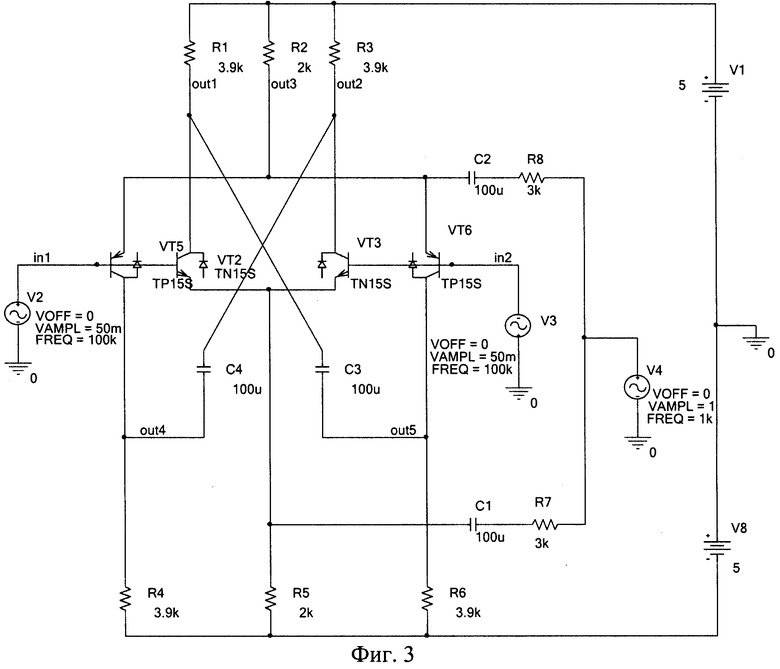

На чертеже фиг.3 представлена схема заявляемого АСС в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

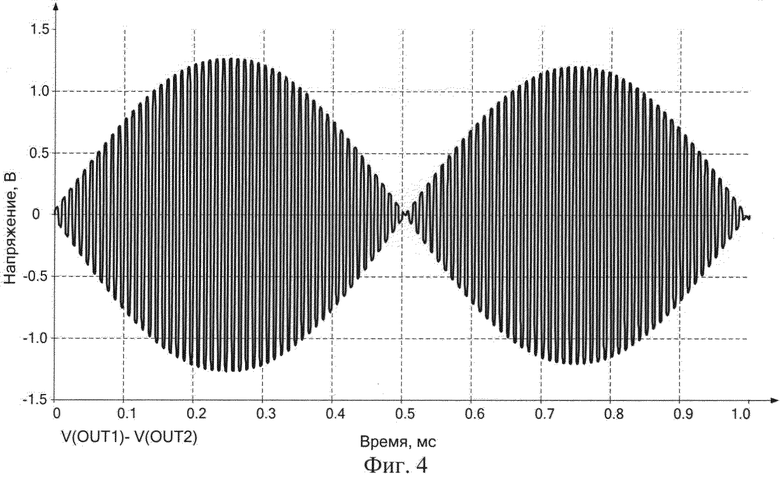

На чертеже фиг.4 приведена осциллограмма выходного напряжения АСС фиг.3 при Ux=150 мВ, fx=100 КГц, Uy=1 В, fy=1 КГц.

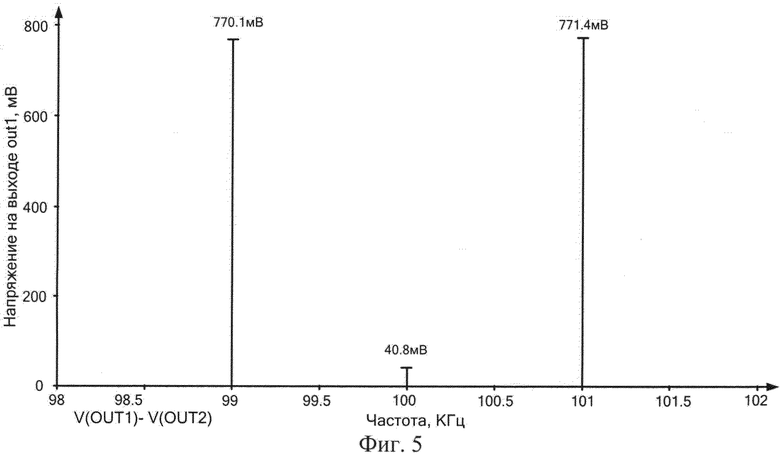

На чертеже фиг.5 показан спектр выходного сигнала АСС фиг.3 при Ux=150 мВ, fx=100 КГц, Uy=1 В, fy=1 КГц. При этом из графиков следует, что схема фиг.3 обеспечивает подавление центральной гармоники в 19 раз.

Заявляемый АСС фиг.2 содержит первый 1 и второй 2 противофазные входы, к которым подключены соответствующие первый 3 и второй 4 источники сигналов канала «X», первый 5 и второй 6 входные транзисторы, базы которых подключены к соответствующим первому 1 и второму 2 противофазным входам, а объединенные эмиттеры через первый 7 токостабилизирующий двухполюсник соединены с первой 8 шиной источника питания, третий 9 и четвертый 10 входные транзисторы, базы которых подключены к соответствующим первому 1 и второму 2 противофазным входам, а эмиттеры соединены с первым выводом второго 11 токостабилизирующего двухполюсника, первый 12 и второй 13 двухполюсники нагрузки, включенные между второй 14 шиной источника питания и соответствующими первым 15 и вторым 16 выходами устройства, связанными с коллекторами соответствующих первого 5 и второго 6 входных транзисторов, источник входного напряжения канала «Y» 17, связанный с эмиттерами первого 5 и второго 6 входных транзисторов через последовательно соединенные первый 18 конденсатор и первый 19 вспомогательный резистор, последовательно соединенные второй 20 конденсатор и второй 21 вспомогательный резистор. Второй 11 токостабилизирующий двухполюсник включен между объединенными эмиттерами третьего 9 и четвертого 10 входных транзисторов и второй 14 шиной источников питания, источник входного напряжения канала «Y» 17 соединен с объединенными эмиттерами третьего 9 и четвертого 10 входных транзисторов через последовательно соединенные второй 20 конденсатор и второй 21 вспомогательный резистор, коллектор третьего 9 входного транзистора, соединенный с третьим 22 выходом устройства, связан с первой 8 шиной источника питания через третий 23 двухполюсник нагрузки, коллектор четвертого 10 входного транзистора связан с четвертым 24 выходом устройства и подключен к первой 8 шине источника питания через четвертый 25 двухполюсник нагрузки, причем второй 16 выход устройства связан с третьим 22 выходом устройства через третий 26 конденсатор, а первый 15 выход устройства соединен с четвертым 24 выходом устройства через четвертый 27 конденсатор.

Рассмотрим работу АСС фиг.2 в диапазоне средних частот, когда влиянием конденсаторов 18, 20 и 26, 27 можно пренебречь из-за малого сопротивления на переменном токе.

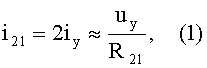

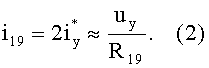

Увеличение напряжения uy (17) канала «Y» (положительная «полуволна») приводит к появлению синфазных токов через резисторы 21 и 19, которые «втекают» в общие эмиттерные цепи транзисторов 9, 10 и 5, 6:

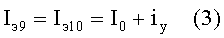

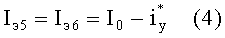

При этом токи эмиттеров транзисторов 9 и 10 увеличиваются от статического уровня I0 на величину iy, а токи эмиттеров транзисторов 5 и 6 уменьшаются на величину

При увеличении суммарного тока эмиттерной цепи транзисторов 9 и 10 их коэффициент усиления по напряжению со входов 1 и 2 увеличивается

а транзисторов 5 и 6 уменьшается

где φт≈26 мВ - температурный потенциал;

Rн.экв - эквивалентное сопротивление нагрузки в цепи выходов 16, 22 и 15, 24.

Поэтому дифференциальное выходное напряжение АСС между выходами 15 и 16 пропорционально произведению ux и uy:

Из (7) следует, что заявляемое устройство обеспечивает смешение (перемножение) двух сигналов при однофазном управлении по каналу «Y», что подтверждается результатами моделирования фиг.4, фиг.5.

В СВЧ-смесителях сигналов фиг.2 резисторы 21 и 19 могут выполнять функции устройств согласования источника входного напряжения канала «Y» 17 uy и АСС с заданным волновым сопротивлением, например 50 Ом.

Замечательная особенность заявляемого устройства фиг.2 - возможность работы при малых напряжениях питания (например,±1 В), что позволяет рекомендовать его схему для использования в системах СВЧ-связи, реализуемых на основе SiGe техпроцессов.

Таким образом, предлагаемое техническое решение является дальнейшим развитием широко распространенного смесителя Гильберта [1-10] и характеризуется отсутствием фазорасщепителя сигнала по каналу «Y» - одного из основных источников погрешности АСС.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент DE 10351115, fig. 4.

2. Патент US №7.356.317, fig. 2.

3. Патент US №6.178.320, fig. 2.

4. Патент US №4.912.520 fig. 2.

5. Патент US №6.871.057, fig. 1.

6. Патент WO 2010062702.

7. Патент US №6.396.330, fig. 10.

8. Патент EP 1480333, fig. 17.

9. Патентная заявка US №2010/0164595, fig. 2.

10. Патент JP 2010-206263 (P2010-206263A).

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2013 |

|

RU2530259C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419190C1 |

| СМЕСИТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ | 2011 |

|

RU2439777C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И СМЕСИТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ НА БАЗЕ ДИФФЕРЕНЦИАЛЬНОГО КАСКАДА ДАРЛИНГТОНА | 2013 |

|

RU2519348C1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2436227C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2012 |

|

RU2487466C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419188C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩИЙ ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ДИФФЕРЕНЦИАЛЬНЫМ ВХОДОМ | 2013 |

|

RU2536377C1 |

| ФАЗОРАСЩЕПИТЕЛЬ ВЫСОКОЧАСТОТНОГО СИГНАЛА | 2011 |

|

RU2439782C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2468502C1 |

Изобретение относится к области радиотехники и связи. Техническим результатом является обеспечение работоспособности смесителя сигналов при однофазном управлении по каналу «Y». Аналоговый смеситель сигналов содержит противофазные входы с источниками сигналов канала «X», первый, второй, третий и четвертый входные транзисторы, базы которых подключены к противофазным входам, а объединенные эмиттеры первого и второго входных транзисторов через первый токостабилизирующий двухполюсник соединены с первой шиной источника питания, двухполюсники нагрузки, включенные между второй шиной источника питания и первым и вторым выходами устройства. Второй токостабилизирующий двухполюсник включен между объединенными эмиттерами третьего и четвертого входных транзисторов и второй шиной источников питания, источник входного напряжения канала «Y» соединен с эмиттерами входных транзисторов через последовательно соединенные конденсаторы и вспомогательные резисторы, коллектор третьего и четвертого входных транзисторов соединены с третьим и четвертым выходами устройства соответственно и связаны с первой шиной источника питания через двухполюсники нагрузки, причем второй выход устройства связан через конденсатор с третьим выходом устройства, а первый выход устройства через конденсатор соединен с четвертым выходом устройства. 5 ил.

Аналоговый смеситель сигналов, содержащий первый (1) и второй (2) противофазные входы, к которым подключены соответствующие первый (3) и второй (4) источники сигналов канала «X», первый (5) и второй (6) входные транзисторы, базы которых подключены к соответствующим первому (1) и второму (2) противофазным входам, а объединенные эмиттеры через первый (7) токостабилизирующий двухполюсник соединены с первой (8) шиной источника питания, третий (9) и четвертый (10) входные транзисторы, базы которых подключены к соответствующим первому (1) и второму (2) противофазным входам, а эмиттеры соединены с первым выводом второго (11) токостабилизирующего двухполюсника, первый (12) и второй (13) двухполюсники нагрузки, включенные между второй (14) шиной источника питания и соответствующими первым (15) и вторым (16) выходами устройства, связанными с коллекторами соответствующих первого (5) и второго (6) входных транзисторов, источник входного напряжения канала «Y» (17), связанный с эмиттерами первого (5) и второго (6) входных транзисторов через последовательно соединенные первый (18) конденсатор и первый (19) вспомогательный резистор, последовательно соединенные второй (20) конденсатор и второй (21) вспомогательный резистор, отличающийся тем, что второй (11) токостабилизирующий двухполюсник включен между объединенными эмиттерами третьего (9) и четвертого (10) входных транзисторов и второй (14) шиной источников питания, источник входного напряжения канала «Y» (17) соединен с объединенными эмиттерами третьего (9) и четвертого (10) входных транзисторов через последовательно соединенные второй (20) конденсатор и второй (21) вспомогательный резистор, коллектор третьего (9) входного транзистора, соединенный с третьим (22) выходом устройства, связан с первой (8) шиной источника питания через третий (23) двухполюсник нагрузки, коллектор четвертого (10) входного транзистора связан с четвертым (24) выходом устройства и подключен к первой (8) шине источника питания через четвертый (25) двухполюсник нагрузки, причем второй (16) выход устройства связан с третьим (22) выходом устройства через третий (26) конденсатор, а первый (15) выход устройства соединен с четвертым (24) выходом устройства через четвертый (27) конденсатор.

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| УСТРОЙСТВО ДЛЯ ФИЛЬТРАЦИИ ВОЗДУХА | 2009 |

|

RU2458729C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| СХЕМА СМЕСИТЕЛЯ И СПОСОБ | 2006 |

|

RU2437205C2 |

Авторы

Даты

2014-01-10—Публикация

2012-10-09—Подача