Уровень техники изобретения

Область техники, к которой относится изобретение

Настоящее изобретение относится к дельта-сигма модулятору, более подробно к дельта-сигма модулятору и способу дизеринга, включающим в себя способность дизеринга для устранения неактивных тонов.

Постановка задачи

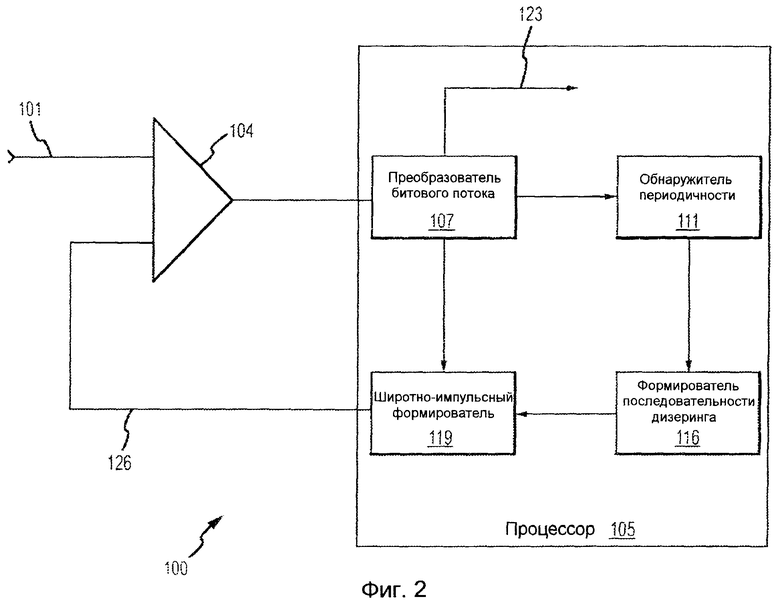

Дельта-сигма модулятор содержит электронное устройство или схему, которая оцифровывает аналоговый вход, и содержит широко используемый аналого-цифровой преобразователь (ADC). Фиг.1 показывает дельта-сигма модулятор согласно предшествующему уровню техники. Дельта-сигма модулятор предшествующего уровня техники включает в себя интегратор на аналоговом входе, и выход интегратора подается в процессор битового потока. Процессор битового потока принимает аналоговый вход и формирует соответствующий (последовательный) цифровой выходной битовый поток. Выход процессора битового потока содержит цифровой выход дельта-сигма модулятора.

Общий и известный недостаток дельта-сигма модулятора предшествующего уровня техники состоит в том, что выход обычно включает в себя нежелательный шум. Дельта-сигма модулятор предшествующего уровня техники, как следствие, включает в себя сигнал дизеринга, который подается обратно во вход, чтобы, по меньшей мере, некоторым образом придать случайный характер аналоговому входному сигналу. У сигнала дизеринга может быть низкая амплитуда так, чтобы дизеринг был эффективен только на низких амплитудах входного сигнала или в неактивное время.

Один недостаток дельта-сигма модулятора предшествующего уровня техники состоит в том, что могут быть сформированы выходы с ошибками, когда вход является неактивным, включая в себя неактивные тоны, которые сформированы, когда аналоговый вход содержит сигналы или значения с постоянным током (DC). Во время такой периодичности выход дельта-сигма модулятора предшествующего уровня техники производит неактивные тоны, содержащие шумовые выбросы на выходе. Эти шумовые выбросы могут быть ошибочно интерпретированы как цифровые значения.

Другой недостаток в предшествующем уровне техники состоит в том, что дизеринг выполняется всегда и не активируется по необходимости.

Аспекты изобретения

В одном аспекте изобретения, дельта-сигма модулятор, включающий в себя способность дизеринга для устранения неактивных тонов, содержит:

преобразователь битового потока, сконфигурированный с возможностью формирования выхода цифрового сигнала, по существу соответствующего входу аналогового сигнала;

обнаружитель периодичности, соединенный с преобразователем битового потока и сконфигурированный с возможностью обнаружения периодичности на выходе цифрового сигнала;

формирователь последовательности дизеринга, соединенный с и активируемый обнаружителем периодичности, когда периодичность обнаруживается, причем формирователь последовательности дизеринга формирует последовательность дизеринга; и

формирователь широтно-импульсной модуляции (PWM), соединенный с формирователем последовательности дизеринга и принимающий последовательность дизеринга, причем формирователь PWM модулирует последовательность дизеринга на вход аналогового сигнала дельта-сигма модулятора в качестве сигнала дизеринга.

Предпочтительно, формирователь последовательности дизеринга формирует по существу случайную последовательность дизеринга.

Предпочтительно, дельта-сигма модулятор дополнительно содержит интегратор, сконфигурированный с возможностью ввода входа аналогового сигнала и сигнала дизеринга в преобразователь битового потока.

Предпочтительно, обнаружитель периодичности сравнивает окно стробирования выхода цифрового сигнала с одним или более предварительно определенными шаблонами, и периодичность обнаруживается, если окно стробирования совпадает с, по меньшей мере, одним шаблоном из одного или более предварительно определенных шаблонов.

Предпочтительно, обнаружитель периодичности маскирует одну или более частей выхода цифрового сигнала одной или более предварительно определенными масками, чтобы сформировать одну или более маскированных частей, и сравнивает оставшееся цифровое содержимое одной или более маскированных частей с предварительно определенной пороговой величиной маски, причем периодичность обнаруживается, если оставшееся цифровое содержимое превышает предварительно определенную пороговую величину маски.

Предпочтительно, обнаружитель периодичности фильтрует одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более отфильтрованных частей, обрабатывает одну или более отфильтрованных частей, чтобы определить присутствие гармоник, и сравнивает гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

Предпочтительно, гребенка обнаружителей периодичности фильтрует одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более гребенчато-отфильтрованных частей, обрабатывает одну или более гребенчато-отфильтрованных частей, чтобы определить присутствие гармоник, и сравнивает гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

В одном аспекте изобретения, способ дизеринга дельта-сигма модулятора, включающий в себя способность дизеринга для устранения неактивных тонов, содержит этапы, на которых:

обнаруживают периодичность на выходе цифрового сигнала дельта-сигма модулятора;

активируют сигнал дизеринга, направленный на вход дельта-сигма модулятора в течение периодов, когда периодичность обнаружена;

формируют по существу случайную последовательность в качестве последовательности дизеринга; и

модулируют последовательность дизеринга на вход дельта-сигма модулятора в качестве широтно-импульсного модулированного (PWM) цифрового сигнала дизеринга, причем этап формирования и этап модуляции активируют в течение периодов, когда периодичность обнаружена.

Предпочтительно, этап обнаружения периодичности дополнительно содержит этап, на котором сравнивают окно стробирования выхода цифрового сигнала с одним или более предварительно определенными шаблонами, и периодичность обнаруживается, если окно стробирования совпадает с, по меньшей мере, одним шаблоном из одного или более предварительно определенных шаблонов.

Предпочтительно, этап обнаружения периодичности дополнительно содержит этапы, на которых маскируют одну или более частей выхода цифрового сигнала одной или более предварительно определенными масками, чтобы сформировать одну или более маскированных частей, и сравнивают оставшееся цифровое содержимое одной или более маскированных частей с предварительно определенной пороговой величиной маски, причем периодичность обнаруживается, если оставшееся цифровое содержимое превышает предварительно определенную пороговую величину маски.

Предпочтительно, этап обнаружения периодичности дополнительно содержит этапы, на которых фильтруют одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более отфильтрованных частей, обрабатывают одну или более отфильтрованных частей, чтобы определить присутствие гармоник, и сравнивают гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

Предпочтительно, этап обнаружения периодичности дополнительно содержит этапы, на которых гребенчато фильтруют одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более гребенчато-отфильтрованных частей, обрабатывают одну или более гребенчато-отфильтрованных частей, чтобы определить присутствие гармоник, и сравнивают гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

Описание чертежей

Одна и та же ссылочная позиция представляет один и тот же элемент на всех чертежах. Нужно понимать, что чертежи не должны обязательно масштабироваться.

Фиг.1 показывает дельта-сигма модулятор согласно предшествующему уровню техники.

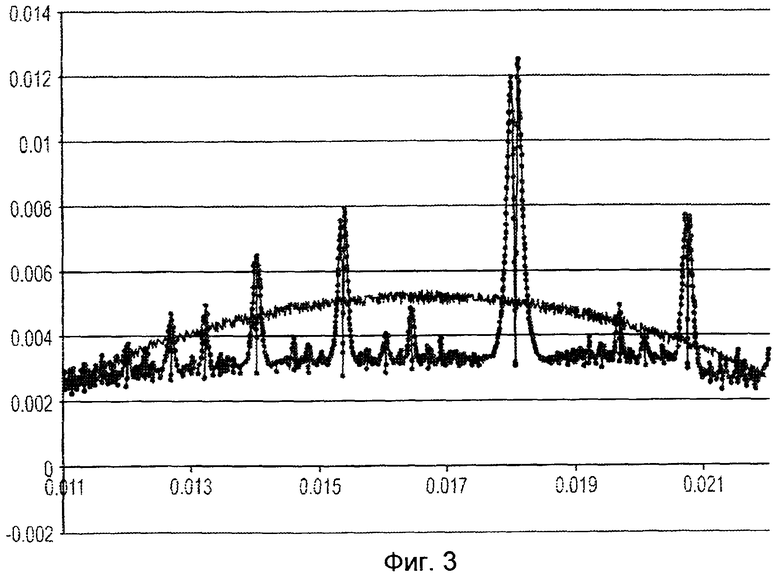

Фиг.2 показывает дельта-сигма модулятор согласно варианту осуществления изобретения.

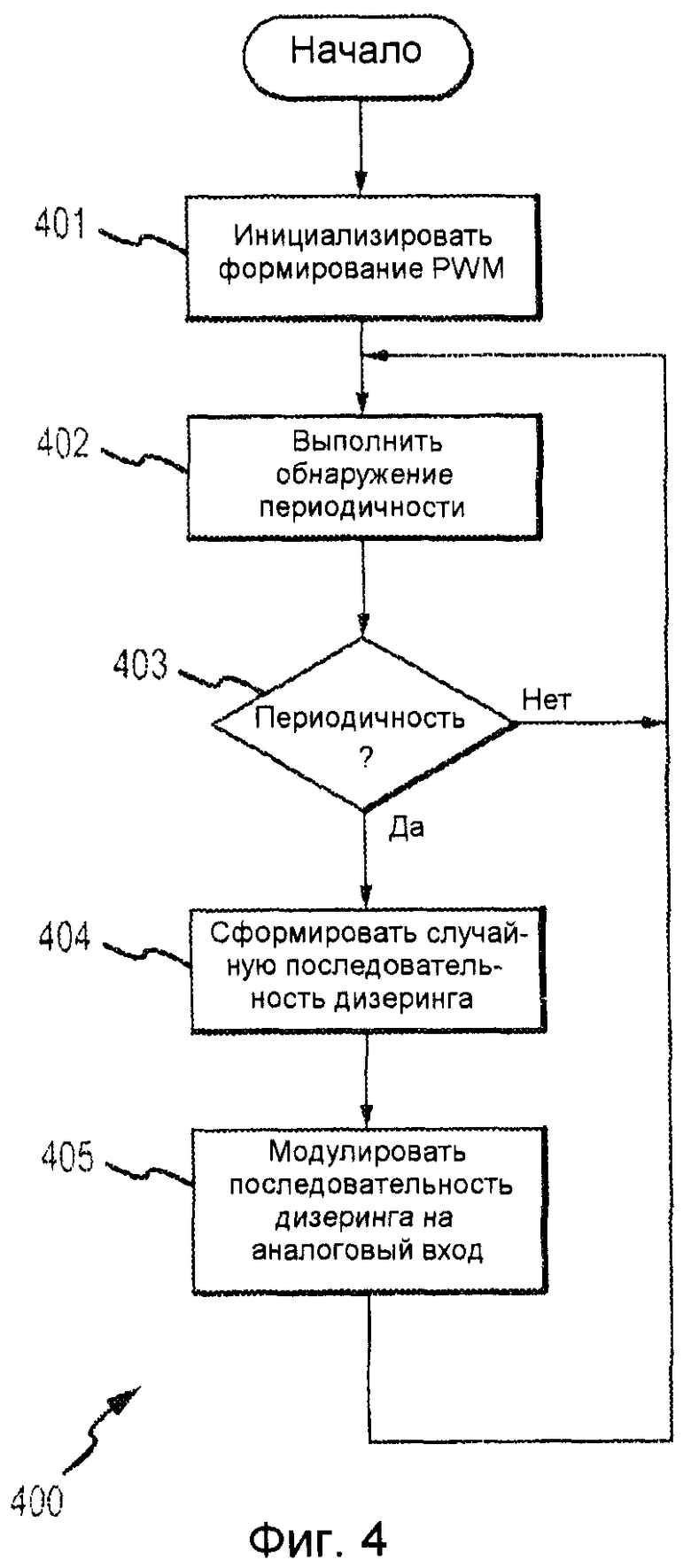

Фиг.3 является графиком дельта-сигма выхода как с, так и без дизеринга согласно изобретению.

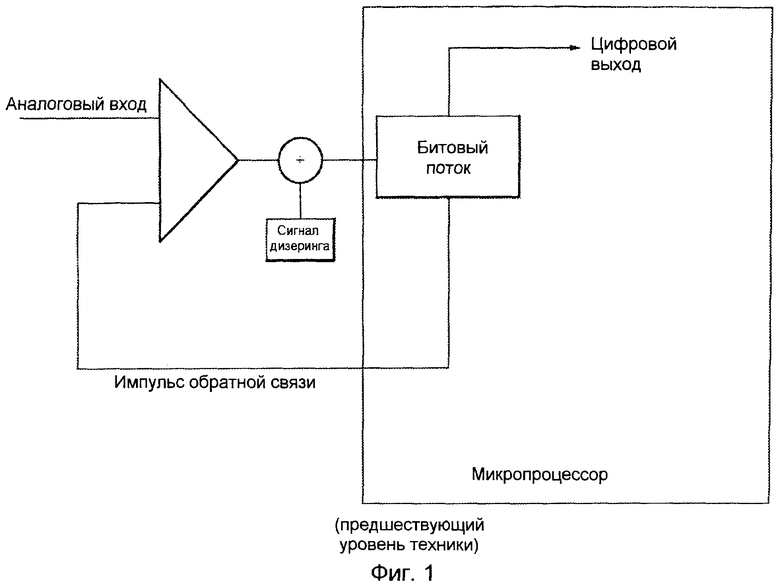

Фиг.4 является блок-схемой последовательности операций способа дизеринга дельта-сигма модулятора согласно варианту осуществления изобретения.

Подробное описание изобретения

Фиг.2-4 и последующее описание изображают конкретные примеры, чтобы научить специалистов в данной области техники, как сделать и использовать самый лучший вариант изобретения. С целью раскрытия принципов изобретения, некоторые стандартные аспекты были упрощены или опущены. Специалисты в данной области техники примут во внимание изменения от этих примеров, которые попадут в пределы объема изобретения. Специалисты в данной области техники примут во внимание, что признаки, описанные ниже, могут сочетаться различными способами, чтобы сформировать множественные изменения изобретения. В результате изобретение не ограничивается конкретными примерами, описанными ниже, а только пунктами формулы изобретения и их эквивалентами.

Фиг.2 показывает дельта-сигма модулятор 100 согласно одному варианту осуществления изобретения. Дельта-сигма модулятор 100 содержит аналого-цифровой преобразователь (ADC), способный к преобразованию аналогового сигнала напряжения в соответствующее последовательное цифровое представление.

Дельта-сигма модулятор 100 включает в себя процессор 105, соединенный с интегратором 104. Интегратор 104 включает в себя аналоговый вход 101, который принимает сигнал аналогового входа для преобразования в выход цифрового сигнала. В некоторых вариантах осуществления интегратор 104 может включать в себя множество состояний (то есть, порядков). Например, интегратор 104 может содержать два интегратора, где дельта-сигма модулятор 100 содержит модулятор второго порядка. Однако нужно понимать, что дельта-сигма модулятор 100 может содержать модулятор любого порядка. Процессор 105 дополнительно включает в себя цифровой выход 123, который может быть соединен любым образом с другим устройством и цепью 126 обратной связи, которая соединена с интегратором 104. Цепь 128 обратной связи подает выход цифрового сигнала от преобразователя 107 битового потока назад на вход преобразователя 107 битового потока.

Цепь 126 обратной связи также подает сигнал дизеринга назад интегратору 104, и интегратор 104 объединяет сигнал дизеринга с сигналом аналогового входа. Сигнал дизеринга содержит преднамеренно примененный, по существу случайный сигнал, который используется, чтобы придать случайный характер или минимизировать присутствие неактивных тонов/периодичности на выходе преобразования A/D.

Процессор 105 может реализовать процессы, которые выполняют преобразование A/D. Процессы включают в себя преобразователь 107 битового потока, обнаружитель 111 периодичности, формирователь 116 последовательности дизеринга и формирователь 119 широтно-импульсной модуляции (PWM). Процессор 105 может содержать компьютер общего назначения, микропроцессорную систему, логическую схему или специализированную интегральную схему, или некоторое другое заказное устройство обработки либо устройство обработки общего назначения. Процессор 105 может включать в себя одно или более устройств обработки. Процессор 105 может включать в себя любой вид встроенного или независимого электронного носителя хранения информации. Однако нужно понимать, что процессор 105 может альтернативно быть заменен или включать в себя дискретную схему, разработанную, чтобы выполнять процессы.

Преобразователь 107 битового потока принимает сигнал аналогового входа плюс любой наложенный сигнал дизеринга. Преобразователь 107 битового потока выполняет преобразование A/D и формирует последовательный цифровой поток битов на цифровом выходе 123. Последовательный цифровой поток битов содержит цифровое представление аналогового сигнала на аналоговом входе 101.

Кроме того, преобразователь 107 битового потока соединен с обнаружителем 111 периодичности. Цифровой выход преобразователя 107 битового потока используется, чтобы обнаружить периодичность. Кроме того, преобразователь 107 битового потока дополнительно соединен с формирователем 119 PWM.

Последовательный цифровой поток битов обеспечивает коэффициент усиления, который используется, чтобы управлять или устанавливать выход PWM от формирователя 119 PWM. Преобразователь 107 битового потока может обеспечить коэффициент усиления для формирователя 119 PWM без потребности в любых внешних устанавливающих усиление или определяющих усиление внешних элементах (то есть резисторах и конденсаторах), поскольку внешние элементы могли бы ввести температурный дрейф или другой шум.

Обнаружитель 111 периодичности соединен с преобразователем 107 битового потока и с формирователем 116 последовательности дизеринга. Обнаружитель 111 периодичности сконфигурирован с возможностью обнаружения периодичности на цифровом выходе битового потока дельта-сигма модулятора 100. Когда обнаружитель 111 периодичности обнаруживает периодичность в цифровом выходе битового потока, обнаружитель 111 периодичности может изменить свое выводимое значение и может соответственно активировать и деактивировать формирователь 116 последовательности дизеринга. Способность обнаружителя 111 периодичности активировать и деактивировать формирователь 116 последовательности дизеринга позволяет обнаружителю 111 периодичности активировать и деактивировать сигнал дизеринга.

Обнаружитель 111 периодичности может обнаружить периодичность различными способами. В одном варианте осуществления обнаружитель 111 периодичности использует поиск по таблице. Обнаружитель (111) периодичности сравнивает окно стробирования выхода цифрового сигнала с одним или более предварительно определенными шаблонами, и периодичность обнаруживается, если окно стробирования совпадает с, по меньшей мере, одним шаблоном из одного или более предварительно определенных шаблонов. Окно может быть предварительно определенного размера, сконструированного, чтобы захватить требуемую периодичность. Окно перемещается в течение долгого времени, и многократно выполняются повторные сравнения с таблицей. В некоторых вариантах осуществления единственное табличное соответствие может быть достаточным для того, чтобы обнаружить периодичность, но альтернативно в других вариантах осуществления, возможно, нужно найти множественные соответствия.

Дополнительно, возможно, нужно выполнить обработку над найденными записями таблицы. Например, можно выполнить некоторую разновидность усреднения или интегрирования над соответствующими записями таблицы, чтобы окончательно определить периодичность.

В другом варианте осуществления обнаружитель 111 периодичности выполняет маскирование, чтобы обнаружить периодичность. Обнаружитель (111) периодичности маскирует одну или более частей выхода цифрового сигнала одной или более предварительно определенными масками, чтобы сформировать одну или более маскированных частей, и сравнивает остающееся цифровое содержимое одной или более маскированных частей с предварительно определенной пороговой величиной маски, причем периодичность обнаруживается, если остающееся цифровое содержимое превышает предварительно определенную пороговую величину маски. Альтернативно, маскирование может быть выполнено над множеством окон. Маскирующий результат (то есть, любые остающиеся цифровые значения) усредняется или суммируется некоторым образом, таким как взятие среднеквадратичного (RMS) значения результатов, затем остающееся цифровое содержимое сравнивается с предварительно определенной пороговой величиной маски. Если остающееся цифровое содержимое превышает предварительно определенную пороговую величину маски, то обнаружитель 111 периодичности определяет, что периодичность была обнаружена.

В еще одном варианте осуществления обнаружитель 111 периодичности фильтрует сигнал цифрового выхода, чтобы обнаружить периодичность. Фильтрация может быть направлена на обнаружение/квантификацию гармоник, например. Обнаружитель (111) периодичности фильтрует одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более отфильтрованных частей, обрабатывает одну или более отфильтрованных частей, чтобы определить присутствие гармоник, и сравнивает гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник. В некоторых вариантах осуществления фильтрация содержит цифровой гребенчатый фильтр, который характеризует множество провалов, которые лежат между ожидаемыми гармониками частоты дискретизации дельта-сигма модулятора 100. Выходы гребенчатого фильтра могут впоследствии быть обработаны, чтобы определить присутствие гармоник, например, усреднением, взятием значения RMS, интегрированием или в противном случае квантификацией выхода фильтра.

Должно быть понято, что обнаружитель 111 периодичности не ограничивается выполнением одного из вышеупомянутых типов обнаружения. Обнаружение периодичности может включать в себя одну или более вышеупомянутых схем обнаружения. Например, обнаружитель 111 периодичности может выполнить фильтрацию и затем может выполнить операцию соответствия шаблона/поиска по таблице над результатами фильтрации.

Формирователь 116 последовательности дизеринга предоставляет последовательность дизеринга формирователю 119 PWM. Формирователь 116 последовательности дизеринга активируется и деактивируется обнаружителем 111 периодичности. Последовательность дизеринга может содержать предварительно определенную последовательность. В некоторых вариантах осуществления формирователь 116 последовательности дизеринга формирует по существу случайную последовательность дизеринга. Альтернативно, формирователь 116 последовательности дизеринга может реализовать предварительно определенный шаблон или шаблоны, разработанные, чтобы иметь низкий уровень повторения.

Формирователь 119 PWM соединен с и управляется формирователем 116 последовательности дизеринга. Использование дизеринга PWM делает возможной более высокую частоту дизеринга. Формирователь 119 PWM принимает последовательность дизеринга от формирователя 116 последовательности дизеринга и формирует оттуда сигнал дизеринга PWM. Широты импульсов сигнала дизеринга в цепи 126 обратной связи поэтому являются достаточно случайными по содержанию энергии, чтобы расформироваться или существенно предотвратить неактивные тоны (или другие ошибки квантования) на цифровом выходе 123.

Формирователь 119 PWM в некоторых вариантах осуществления может выполнить обрезку, уменьшение ширины импульса сигнала дизеринга/обратной связи, предоставленного на аналоговый вход. В результате обрезки импульсы сигнала дизеринга/обратной связи являются более узкими, чем в предшествующем уровне техники. Преимущественно, это дает усиление ADC. Дополнительно, использование сигнала PWM формирует хаотический поток импульсов, который не имеет доминирующей частоты и вместо этого характеризует широкий спектр частот. Однако сигнал дизеринга/обратной связи не содержит значений постоянного тока (DC). Отсутствие составляющей DC в сигнале дизеринга/обратной связи не оказывает влияния на точность оцифрованного результата.

Фиг.3 является графиком дельта-сигма выхода как с, так и без дизеринга согласно изобретению. Более низкая кривая содержит выход без дизеринга согласно изобретению. Выбросы внутри содержат неактивные тоны, которые появляются на выходе дельта-сигма модулятора в течение неактивных периодов. Должным образом, там, где аналоговый вход должен формировать цифровые нулевые выходные значения, выход цифрового сигнала теперь включает в себя выбросы. Выбросы могут быть ошибочно интерпретированы последующей схемой как значения цифровой "единицы". Этот шум может повредить дальнейшее измерение или действие, выполняемое над или посредством выхода цифрового сигнала. Если шум сильный, то он может быть излучен и подхвачен электронными составляющими, которые даже не являются нисходящим потоком устройства дельта-сигма модулятора.

Верхняя кривая на графике содержит выход сглаженного дельта-сигма модулятора согласно изобретению. Верхняя кривая линия отклоняется от плоской линии, которая была бы идеальным выходом дельта-сигма модулятора, где аналоговый вход к дельта-сигма модулятору является по существу статическим. Однако сглаженный дельта-сигма модулятор не показывает амплитуду напряжения выбросов, поэтому гораздо менее вероятно, что будет ошибочно интерпретирован как значение цифровой единицы. Энергия выбросов стала рассредоточенной и оказалась безвредной.

Фиг.4 является блок-схемой 400 последовательности операций способа дизеринга дельта-сигма модулятора согласно варианту осуществления изобретения. На этапе 401 инициализируется сигнал широтно-импульсной модуляции (PWM), например, в течение включения питания или инициализации устройства, которое включает в себя дельта-сигма модулятор, например. Инициализация может включать в себя инициализацию начинающей ширины импульса, инициализацию периода импульсов и т.д.

На этапе 402 выполняется обнаружение периодичности. Обнаружение периодичности может включать в себя обнаружение неактивных тонов в течение периодов, когда значения DC присутствуют на входе аналогового сигнала. Сформированный цифровой выход битового потока (и обратная связь) будет часто содержать периодические части, когда аналоговый вход будет содержать значения DC. Неактивные тоны видятся как шумовые выбросы на цифровом выходе.

Периодичность можно обнаружить посредством использования поиска по таблице, маскирования или фильтрации, как было обсуждено ранее. Окно (окна) стробирования может быть захвачено и обработано в процессе обнаружения.

На этапе 403, если периодичность обнаруживается, то способ продолжается до этапа 404. В противном случае, способ ответвляется назад вверх к этапу 402 и продолжает отслеживать периодичность.

На этапе 404, когда периодичность обнаруживается на цифровом выходе, тогда активируется способность дизеринга. Активация может содержать формирование случайной последовательности дизеринга.

На этапе 405 случайная последовательность дизеринга модулируется на сигнал обратной связи PWM, который в свою очередь модулируется на аналоговый вход в качестве сигнала дизеринга. По существу случайная природа сигнала дизеринга разрушает и/или предотвращает периодичность и неактивные тоны на цифровом выходе дельта-сигма модулятора.

Согласно настоящему изобретению предоставлен дельта-сигма модулятор, включающий в себя способность дизеринга для устранения неактивных тонов. Технический результат заключается в формировании сигнала дизеринга в необходимое время, что улучшает качество сигнала. Дельта-сигма модулятор включает в себя преобразователь битового потока, сконфигурированный с возможностью формирования выхода цифрового сигнала, по существу соответствующего входу аналогового сигнала, обнаружитель периодичности, соединенный с преобразователем битового потока и сконфигурированный с возможностью обнаружения периодичности на выходе цифрового сигнала, и формирователь последовательности дизеринга, соединенный с обнаружителем периодичности и активируемый им. Формирователь последовательности дизеринга формирует последовательность дизеринга. Дельта-сигма модулятор дополнительно включает в себя формирователь широтно-импульсной модуляции (PWM), соединенный с формирователем последовательности дизеринга и принимающий последовательность дизеринга. Формирователь PWM модулирует последовательность дизеринга на вход аналогового сигнала дельта-сигма модулятора в качестве сигнала дизеринга. 2 н. и 10 з.п. ф-лы, 4 ил

1. Дельта-сигма модулятор (100), включающий в себя способность дизеринга для устранения неактивных тонов, при этом дельта-сигма модулятор (100) содержит:

преобразователь (107) битового потока, сконфигурированный с возможностью формирования выхода цифрового сигнала, по существу, соответствующего входу аналогового сигнала;

обнаружитель (111) периодичности, соединенный с преобразователем (107) битового потока и сконфигурированный с возможностью обнаружения периодичности на выходе цифрового сигнала;

формирователь (116) последовательности дизеринга, соединенный с обнаружителем (111) периодичности и активируемый им, когда периодичность обнаруживается, причем формирователь (116) последовательности дизеринга формирует последовательность дизеринга; и

формирователь (119) широтно-импульсной модуляции (PWM), соединенный с формирователем (116) последовательности дизеринга и принимающий последовательность дизеринга, причем формирователь (119) PWM модулирует последовательность дизеринга на вход аналогового сигнала дельта-сигма модулятора (100) в качестве сигнала дизеринга.

2. Дельта-сигма модулятор (100) по п.1 с формирователем (116) последовательности дизеринга, формирующим, по существу, случайную последовательность дизеринга.

3. Дельта-сигма модулятор (100) по п.1, дополнительно содержащий интегратор (104), сконфигурированный с возможностью ввода входа аналогового сигнала и сигнала дизеринга в преобразователь (107) битового потока.

4. Дельта-сигма модулятор (100) по п.1, в котором обнаружитель (111) периодичности сравнивает окно стробирования выхода цифрового сигнала с одним или более предварительно определенными шаблонами, и периодичность обнаруживается, если окно стробирования совпадает с, по меньшей мере, одним шаблоном из одного или более предварительно определенных шаблонов.

5. Дельта-сигма модулятор (100) по п.1, в котором обнаружитель (111) периодичности маскирует одну или более частей выхода цифрового сигнала одной или более предварительно определенными масками, чтобы сформировать одну или более маскированных частей, и сравнивает оставшееся цифровое содержимое одной или более маскированных частей с предварительно определенной пороговой величиной маски, причем периодичность обнаруживается, если оставшееся цифровое содержимое превышает предварительно определенную пороговую величину маски.

6. Дельта-сигма модулятор (100) по п.1, в котором обнаружитель (111) периодичности фильтрует одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более отфильтрованных частей, обрабатывает одну или более отфильтрованных частей, чтобы определить присутствие гармоник, и сравнивает гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

7. Дельта-сигма модулятор (100) по п.1, в котором гребенка обнаружителей (111) периодичности фильтрует одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более гребенчато-отфильтрованных частей, обрабатывает одну или более гребенчато-отфильтрованных частей, чтобы определить присутствие гармоник, и сравнивает гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

8. Способ дизеринга дельта-сигма модулятора, включающий в себя способность дизеринга для устранения неактивных тонов, содержащий этапы, на которых:

обнаруживают периодичность на выходе цифрового сигнала дельта-сигма модулятора;

активируют сигнал дизеринга, направленный на вход дельта-сигма модулятора в течение периодов, когда периодичность обнаружена;

формируют, по существу, случайную последовательность в качестве последовательности дизеринга; и

модулируют последовательность дизеринга на вход дельта-сигма модулятора в качестве широтно-импульсного модулированного (PWM) цифрового сигнала дизеринга, причем этап формирования и этап модуляции активируют в течение периодов, когда периодичность обнаружена.

9. Способ по п.8 с этапом обнаружения периодичности, дополнительно содержащим этап, на котором сравнивают окно стробирования выхода цифрового сигнала с одним или более предварительно определенными шаблонами, и периодичность обнаруживается, если окно стробирования совпадает с, по меньшей мере, одним шаблоном из одного или более предварительно определенных шаблонов.

10. Способ по п.8, в котором этап обнаружения периодичности дополнительно содержит этапы, на которых:

маскируют одну или более частей выхода цифрового сигнала одной или более предварительно определенными масками, чтобы сформировать одну или более маскированных частей; и

сравнивают оставшееся цифровое содержимое одной или более маскированных частей с предварительно определенной пороговой величиной маски, причем периодичность обнаруживается, если оставшееся цифровое содержимое превышает предварительно определенную пороговую величину маски.

11. Способ по п.8, в котором этап обнаружения периодичности дополнительно содержит этапы, на которых:

фильтруют одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более отфильтрованных частей;

обрабатывают одну или более отфильтрованных частей, чтобы определить присутствие гармоник; и

сравнивают гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

12. Способ по п.8, в котором этап обнаружения периодичности дополнительно содержит этапы, на которых:

гребенчато фильтруют одну или более частей выхода цифрового сигнала, чтобы сформировать одну или более гребенчато-отфильтрованных частей;

обрабатывают одну или более гребенчато-отфильтрованных частей, чтобы определить присутствие гармоник; и

сравнивают гармоники с предварительно определенной пороговой величиной гармоник, причем периодичность обнаруживается, если гармоники превышают предварительно определенную пороговую величину гармоник.

| WO 2008036140 А, 27.03.2008 | |||

| US 7345607 B1, 18.03.2008 | |||

| WO 2007040989 A1, 12.04.2007. |

Авторы

Даты

2012-07-27—Публикация

2008-07-30—Подача