Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и решающих усилителях с управляемыми параметрами, а также аналоговых микросхемах (AM) с цепями частотной коррекции коэффициента усиления или программируемых AM).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ с двухканальной активной нагрузкой, обеспечивающей непосредственное управление двухтактным выходным буферным усилителем [1-10]. Такие ОУ имеют двухканальную передачу сигнала через управляемую активную нагрузку (АН) и характеризуются более высоким диапазоном рабочих частот благодаря наличию каскодной структуры и наибольшим быстродействием, которое обеспечивается исключением нелинейных режимов в данной АН.

Предлагаемое изобретение относится также к классу ОУ на базе несимметричных входных каскадов [1÷10], которые до сих пор находили применение только в устройствах с низкими требованиями к стабильности нулевого уровня.

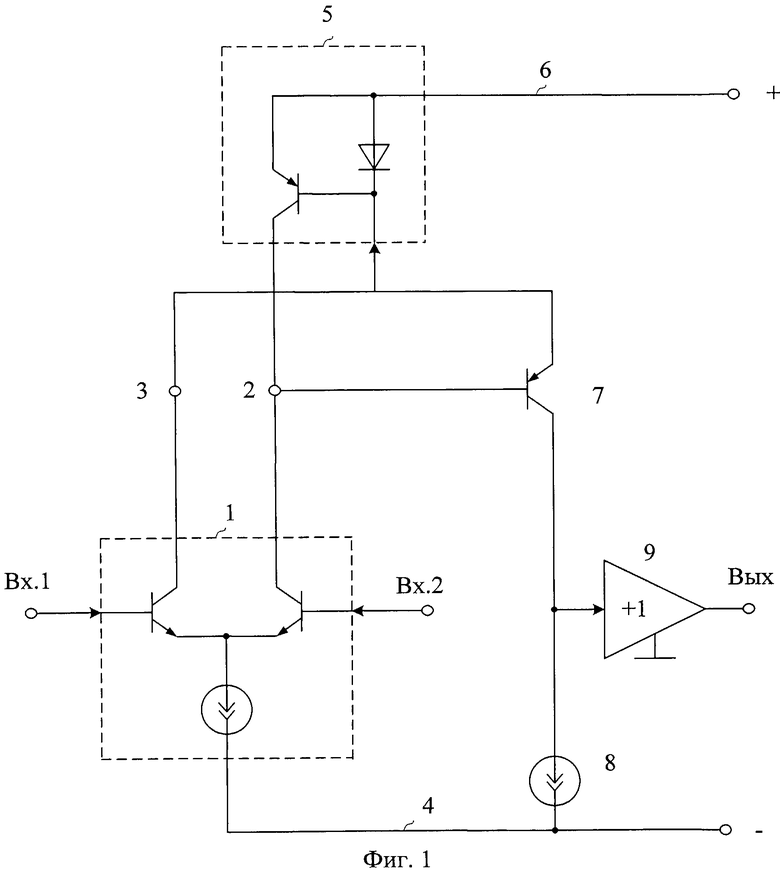

Наиболее близким по технической сущности к заявляемому схемотехническому решению является классическая схема ОУ фиг.1, представленная в патенте US 3.697.882, fig.2 (или SE 362177, fig.2), которая также присутствует в большом числе других патентов и монографий, например [1÷10], имеющих в качестве цепи нагрузки входных транзисторов двухканальные токовые зеркала с несимметричным включением (по отношению к входному каскаду). Это одна из перспективных архитектур ОУ, так как она обеспечивает (при минимально возможной сложности) получение двуполярных амплитуд выходного напряжения, близких к напряжениям питания, и имеет хорошие показатели по частотному диапазону благодаря каскодной структуре.

Существенный недостаток известного ОУ фиг.1 состоит в том, что в нем не предусмотрена (физически не реализуется) «опережающая» коррекция коэффициента усиления (Ку) в частотной области, что не позволяет увеличивать Ку с повышением частоты и компенсировать таким образом отрицательное влияние на частотную характеристику и на показатели устойчивости ОУ физических инерционностей схемы (емкостей на подложку транзисторов, емкостей коллектор-база, паразитных емкостей и т.п.).

Кроме этого, в известном ОУ изменение Ку возможно только путем управления статическим режимом транзисторов, т.е. величиной потребляемого тока от источника питания, что не всегда допустимо.

Основная задача предлагаемого изобретения состоит в создании условий для введения в ОУ элементов «опережающей» частотной коррекции с целью формирования заданных амплитудно-частотных характеристик ОУ и обеспечения запаса устойчивости по амплитуде и фазе, а также управления величиной Ку в тех случаях, когда заявляемая архитектура используется в качестве устройства с программируемыми параметрами.

Поставленная задача решается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, эмиттерная цепь которого связана с первой 4 шиной источника питания, токовое зеркало 5, согласованное со второй 6 шиной источника питания, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, а выход подключен к первому 2 токовому выходу входного дифференциального каскада 1 и базе выходного транзистора 7, двухполюсник коллекторной нагрузки 8, включенный между коллектором выходного транзистора 7 и первой 4 шиной источника питания, выходной буферный усилитель 9, вход которого соединен с коллектором выходного транзистора 7, причем эмиттер выходного транзистора 7 связан со входом токового зеркала 5, предусмотрены новые элементы и связи - эмиттер выходного транзистора 7 связан со входом токового зеркала 5 через цепь коррекции коэффициента усиления 10 и соединен со второй 6 шиной источника питания через дополнительный двухполюсник обратной связи 11.

Схема ОУ-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого ОУ в соответствии с п.1, п.3 формулы изобретения.

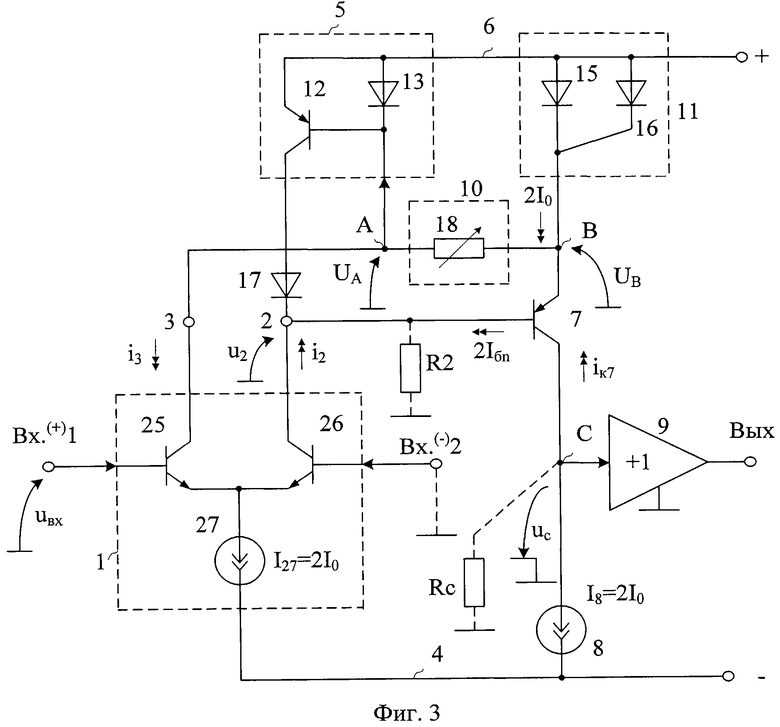

На чертеже фиг.3 показана схема ОУ фиг.2 с конкретным выполнением токового зеркала 5 (п.2 формулы изобретения), цепи коррекции коэффициента усиления 10 (п.6 формулы изобретения), дополнительного двухполюсника обратной связи 11 (п.4 формулы изобретения), а также п.5 формулы изобретения, характеризующего включение согласующего p-n перехода 17.

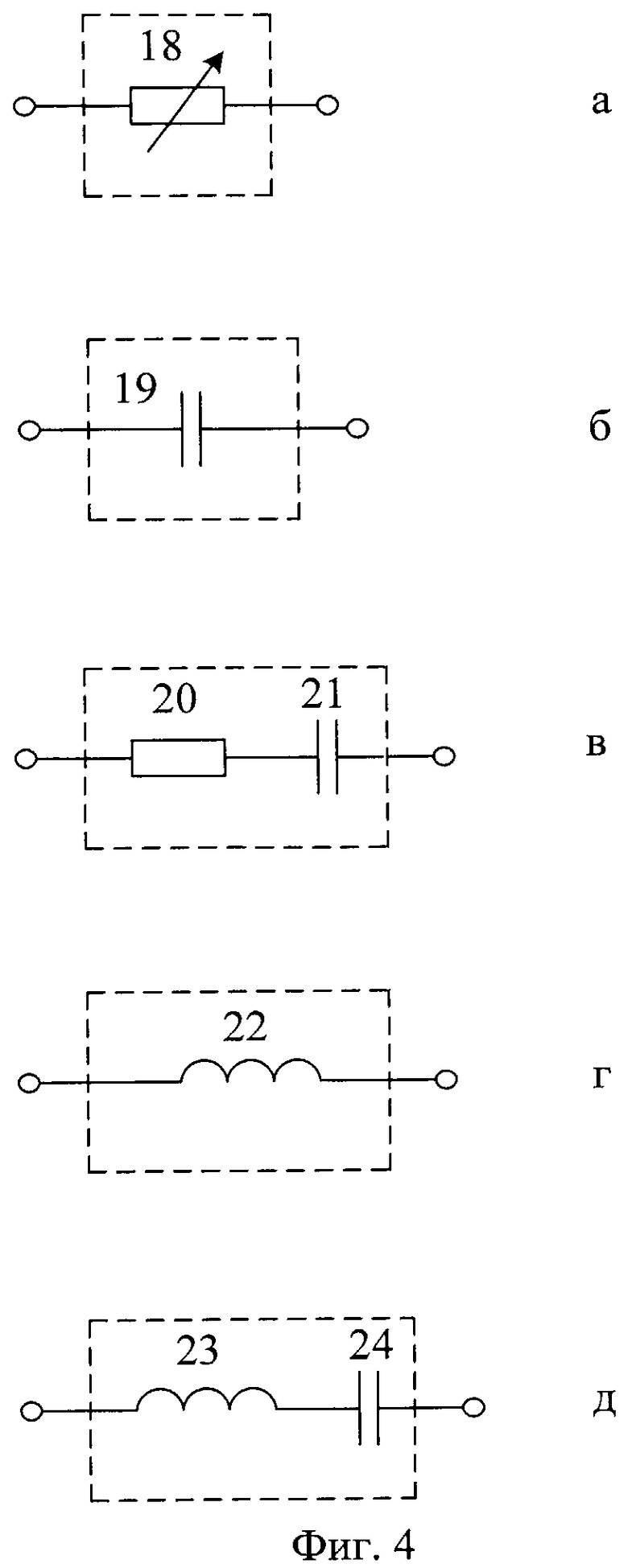

На чертежах фиг.4 приведены частные варианты построения цепи коррекции коэффициента усиления 10, которые соответствуют:

- фиг.4а - п.6 формулы изобретения,

- фиг.4б - п.7 формулы изобретения,

- фиг.4в - п.8 формулы изобретения,

- фиг.4г - п.9 формулы изобретения,

- фиг.4д - п.10 формулы изобретения.

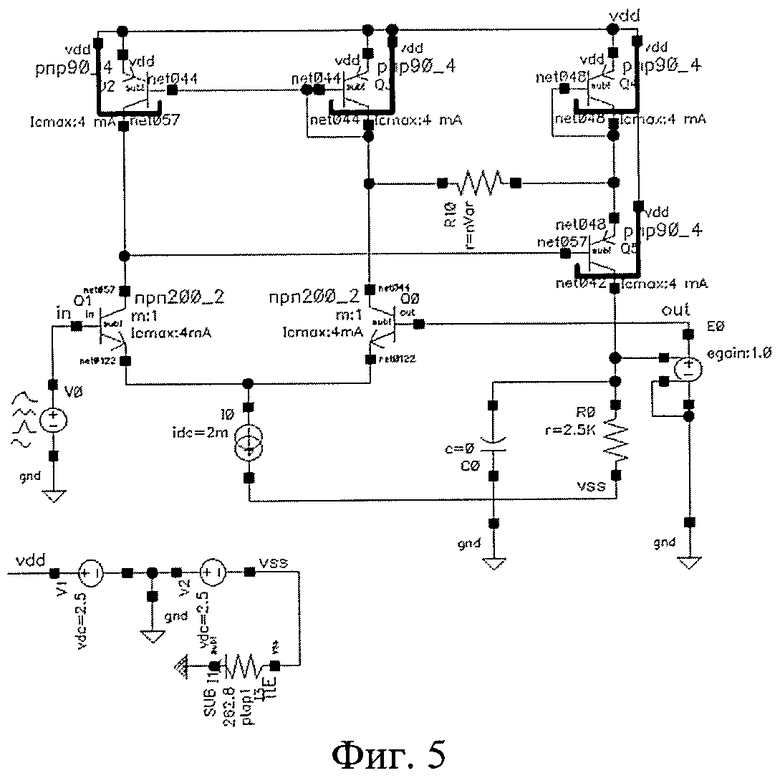

На чертеже фиг.5 представлена схема предлагаемого ОУ (п.6, п.3 формулы изобретения) в среде Cadence на моделях SiGe интегральных транзисторов. В частном случае, при выборе сопротивления дополнительного резистора 18 R18=R10=n var=0, данная схема соответствует схеме ОУ-прототипа фиг.1.

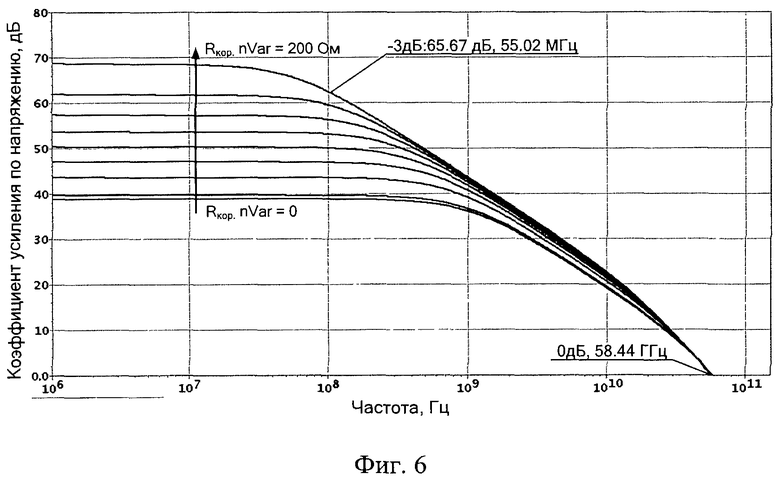

На чертеже фиг.6 показаны логарифмические амплитудно-частотные характеристики коэффициента усиления по напряжению ОУ фиг.5 при разных значениях сопротивления резистора R10 данной схемы (резистора 18 фиг.3 цепи коррекции коэффициента усиления 10: R18=R10=r=n var).

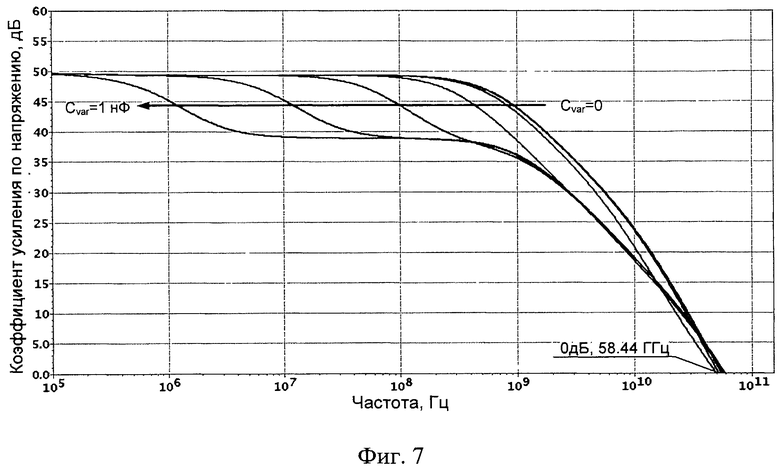

На чертеже фиг.7 показаны логарифмические амплитудно-частотные характеристики коэффициента усиления по напряжению ОУ фиг.5 при разных значениях параметров цепи коррекции 10, реализованной в соответствии с п.7 формулы изобретения и чертежом фиг.4б в виде конденсатора.

На чертеже фиг.8 показаны логарифмические амплитудно-частотные характеристики коэффициента усиления ОУ фиг.5 при разных значениях сопротивления резистора R10=Rкорn var (резистора цепи коррекции

коэффициента усиления 10, соответствующей фиг.4а и п.6 формулы изобретения).

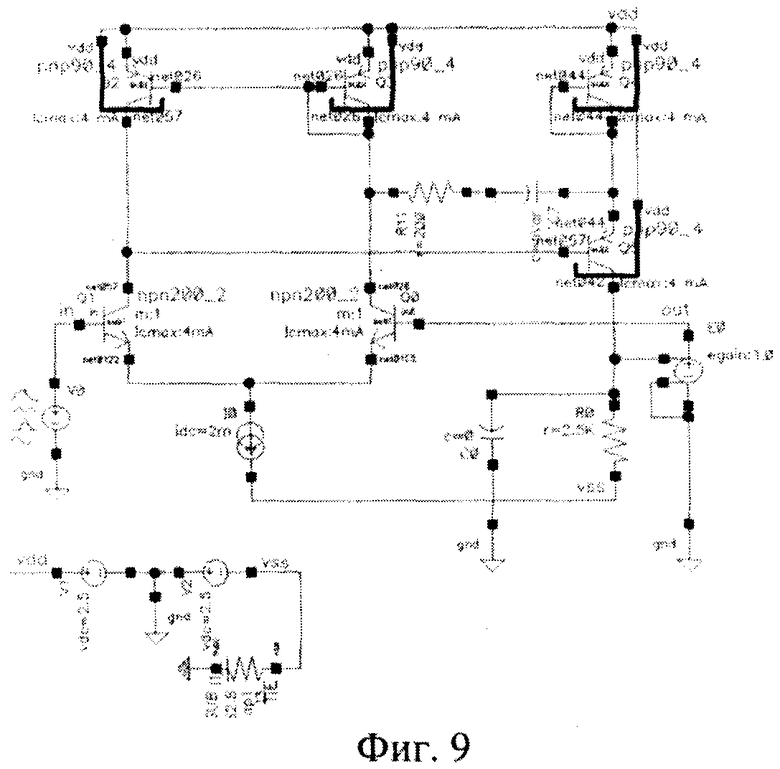

На чертеже фиг.9 приведена схема предлагаемого ОУ в среде Cadence на моделях SiGe интегральных транзисторов при реализации цепи коррекции коэффициента усиления 10 в соответствии с чертежом фиг.4в и п.8 формулы изобретения.

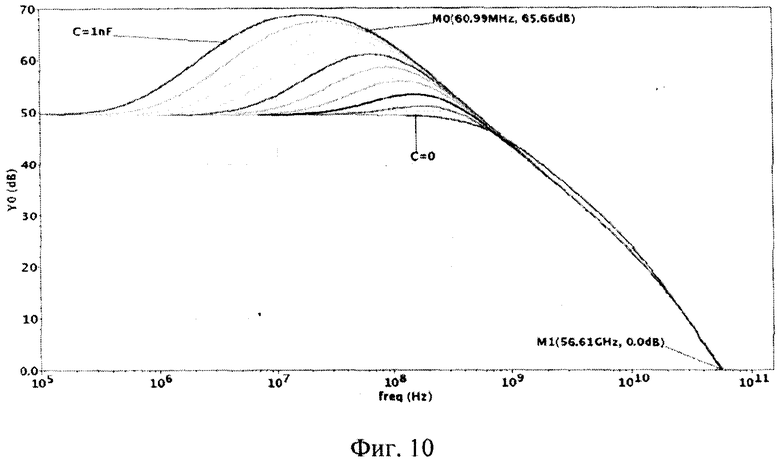

На чертеже фиг.10 приведены амплитудно-частотные характеристики коэффициента усиления схемы фиг.9 при разных значениях емкости конденсатора С=Cvar входящего в структуру цепи коррекции коэффициента усиления 10.

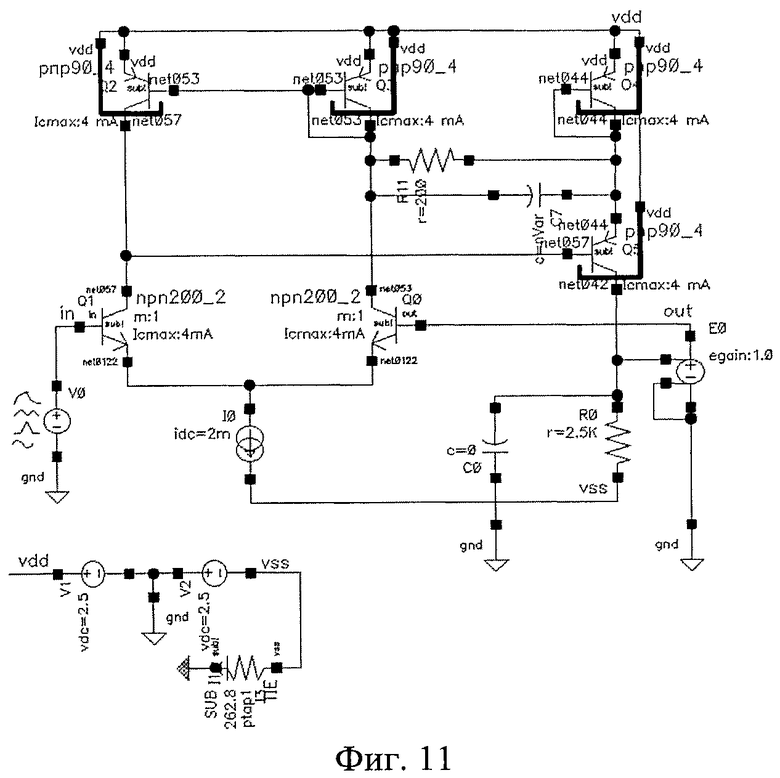

На чертеже фиг.11 приведена схема предлагаемого ОУ в среде Cadence на моделях SiGe интегральных транзисторов при реализации цепи коррекции коэффициента усиления 10 в соответствии с чертежом фиг.2. В частном случае при выборе сопротивления резистора R11=0 данная схема соответствует схеме ОУ-прототипа.

На чертеже фиг.12 приведены логарифмические амплитудно-частотные характеристики коэффициента усиления по напряжению схемы фиг.11 при разных значениях емкости конденсатора Cvar, входящего в цепь коррекции коэффициента усиления 10, соответствующую фиг.2.

Операционный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, эмиттерная цепь которого связана с первой 4 шиной источника питания, токовое зеркало 5, согласованное со второй 6 шиной источника питания, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, а выход подключен к первому 2 токовому выходу входного дифференциального каскада 1 и базе выходного транзистора 7, двухполюсник коллекторной нагрузки 8, включенный между коллектором выходного транзистора 7 и первой 4 шиной источника питания, выходной буферный усилитель 9, вход которого соединен с коллектором выходного транзистора 7, причем эмиттер выходного транзистора 7 связан со входом токового зеркала 5. Эмиттер выходного транзистора 7 связан со входом токового зеркала 5 через цепь коррекции коэффициента усиления 10 и соединен со второй 6 шиной источника питания через дополнительный двухполюсник обратной связи 11.

Кроме этого, на чертеже фиг.2, в соответствии с п.3 формулы изобретения, дополнительный двухполюсник обратной связи 11 выполнен в виде второго 14 дополнительного прямосмещенного p-n перехода.

На чертеже фиг.3, в соответствии с п.2 формулы изобретения, токовое зеркало 5 содержит первый 12 вспомогательный транзистор, эмиттер которого подключен ко второй 6 шине источника питания, база соединена со входом токового зеркала 5, коллектор - с его выходом, а между базой первого 12 вспомогательного транзистора и второй 6 шиной источника питания включен первый 13 дополнительный p-n переход.

На чертеже фиг.3, в соответствии с п.4 формулы изобретения, дополнительный двухполюсник обратной связи 11 выполнен в виде двух параллельно включенных третьего 15 и четвертого 16 дополнительных прямосмещенных p-n переходов. Такое решение обеспечивает одинаковые потенциалы между узлами, к которым подключается цепь коррекции коэффициента усиления 10.

Кроме этого, на чертеже фиг.3, в соответствии с п.5 формулы изобретения, выход токового зеркала 5 подключен к первому 2 токовому выходу входного дифференциального каскада 1 и базе выходного транзистора 7 через согласующий p-n переход 17. Это обеспечивает идентичность статических режимов по напряжению коллектор-база входных транзисторов 25, 26 дифференциального каскада 1 и минимизирует напряжение смещения нуля ОУ.

Кроме этого, на чертежах фиг.3 и фиг.4а, в соответствии с п.6 формулы изобретения, цепь коррекции коэффициента усиления 10 выполнена в виде первого 18 дополнительного резистора.

На чертеже фиг.4б, в соответствии с п.7 формулы изобретения, цепь коррекции коэффициента усиления 10 выполнена в виде первого 19 дополнительного конденсатора, который формирует желаемую амплитудно-частотную характеристику ОУ.

На чертеже фиг.4в, в соответствии с п.8 формулы изобретения, цепь коррекции коэффициента усиления 10 выполнена в виде последовательно соединенных второго 20 дополнительного резистора и второго 21 дополнительного конденсатора. Такое решение позволяет «выключить» влияние конденсатора 21 на высоких частотах.

На чертеже фиг.4г, в соответствии с п.9 формулы изобретения, цепь коррекции коэффициента усиления 10 выполнена в виде первой дополнительной индуктивности 22. В этом случае с повышением частоты суммарный Ку операционного усилителя повышается.

На чертеже фиг.4д, в соответствии с п.10 формулы изобретения, цепь коррекции коэффициента усиления 10 выполнена в виде последовательно соединенных второй дополнительной индуктивности 23 и третьего 24 дополнительного конденсатора.

Во всех рассматриваемых схемах ОУ входной дифференциальный каскад 1 выполнен на транзисторах 25, 26 и источнике тока 27.

Рассмотрим факторы, определяющие зависимость коэффициента усиления по напряжению от параметров цепи коррекции 10 при ее выполнении в виде резистора 18.

Определим два предельных значения коэффициента усиления (Ку) ОУ фиг.3, которые реализуются при двух крайних значениях сопротивления резистора 18 цепи коррекции коэффициента усиления 10: R18=0 и R10=∞.

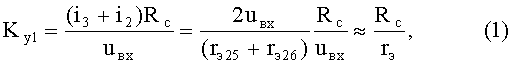

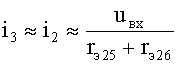

При R18=0 схема фиг.3 совпадает со схемой ОУ-прототипа и ее коэффициент усиления Ку1 определяется по формуле

где i3≈i2 - приращения выходных токов узлов 3 и 2 входного каскада 1, обусловленные изменением uвх;

Rc - эквивалентное сопротивление в узле «C»;

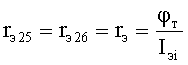

- дифференциальные сопротивления эмиттерных переходов входных транзисторов 25, 26 входного дифференциального каскада 1 при токе эмиттера Iэi=I0;

- дифференциальные сопротивления эмиттерных переходов входных транзисторов 25, 26 входного дифференциального каскада 1 при токе эмиттера Iэi=I0;

φт≈25 мВ - температурный потенциал.

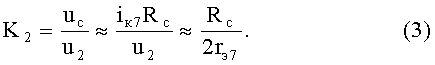

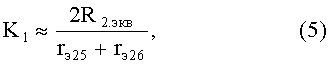

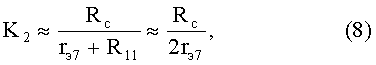

Если R18=∞, то коэффициент усиления схемы ОУ фиг.3 (Kу.2) существенно возрастает и определяется произведением Kу2=K1K2,

где K1 - коэффициент усиления по напряжению подсхемы, образованный входным дифференциальным каскадом 1 и токовым зеркалом 5

K2 - коэффициент усиления по напряжению от узла 2 к узлу «C» (входу буферного усилителя 9)

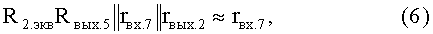

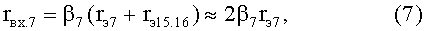

Если учесть, что  , а эквивалентное сопротивление R2 в узле 2 при R18=0 определяется входным сопротивлением транзистора 7 (rвх.7), то суммарный коэффициент усиления ОУ в рассматриваемом режиме:

, а эквивалентное сопротивление R2 в узле 2 при R18=0 определяется входным сопротивлением транзистора 7 (rвх.7), то суммарный коэффициент усиления ОУ в рассматриваемом режиме:

где

где rвых.2 - выходное сопротивление входного каскада 1 относительно узла 2;

Rвых.5 - выходное сопротивление токового зеркала 5;

rэ7 - сопротивление эмиттерного перехода транзистора 7;

rэ15.16 - эквивалентное сопротивление в эмиттере транзистора 7.

Таким образом

Из последних уравнений можно найти диапазон перестройки Ку:

Таким образом, при изменении сопротивления двухполюсника 10 (для фиг.3 - резистора R18) в диапазоне 0÷∞, коэффициент усиления ОУ изменяется в β7 раз (50÷100 раз или на 25÷40 дБ).

Следует заметить, что узлы «A» и «B» в схеме фиг.3 эквипотенциальны, т.е. через двухполюсник 18 протекает нулевой статический ток. Это обеспечивается (при I8=2I0) параллельным включением p-n переходов 15 и 16 (фиг.3).

В качестве переменного резистора 18 (R18, фиг.3) в заявляемых схемах могут применяться полевые транзисторы. Это позволяет выполнять ОУ с программируемым коэффициентом усиления.

Авторы рекомендуют выбирать ток двухполюсника 8 на уровне I8=2I0. При этом статический ток базы транзистора 7 будет равен величине 2Iбn, что обеспечивает в схеме фиг.3 близкое к нулю напряжение смещения нуля (Uсм). При других значениях I8 и других вариантах реализации двухполюсника обратной связи Uсм≠0.

Для минимизации влияния напряжения Эрли входных транзисторов 25 и 26 входного дифференциального каскада 1 вводится согласующий p-n переход 17 (фиг.3), который обеспечивает равенство UA=U2, что также уменьшает Uсм.

Компьютерное моделирование схем фиг.5, фиг.9, фиг.11 подтверждает данные теоретические выводы (фиг.6, фиг.7, фиг.8, фиг.10, фиг.12).

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU №2193293, fig.2, АООТ завод «Микрон» г.Зеленоград.

2. Патент США №4.250.460.

3. Патент США №3.843.935, fig.2.

4. Патент США №4.366.442.

5. Патент США №3.569.848, fig.7 (А2-В2).

6. Патент Японии JP 52-149946.

7. Полонников, Д.Е. Операционные усилители: Принципы построения, теория, схемотехника [Текст] / Д.Е.Полонников. - М., 1983. - стр.141, рис.4.14.

8. Операционные усилители и компараторы. - М.: Издательский дом «Додэка-XXI», 2001, стр.259 (микросхема 1450УД1, ТАА 2761).

9. Журнал «Схемотехника» №3, 2001, стр.3.

10. Справочник «Electronics information series: Linear integrated circuit D.A.T.A. bock», Edition 21, 1979, Condura Company, US, New Jersey, P212, fig.A358, HA1-4625, HA1-4605, www.datasheetarchive.com/HA-4625-5-datasheet.html - США.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2455756C1 |

| ИЗМЕРИТЕЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМИ ПАРАМЕТРАМИ АМПЛИТУДНО-ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ | 2013 |

|

RU2519429C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2616573C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2400924C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416146C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2589323C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2604684C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и решающих усилителях с управляемыми параметрами, а также аналоговых микросхемах (AM) с цепями частотной коррекции коэффициента усиления или программируемых AM). Технический результат: создание условий для введения в ОУ элементов «опережающей» частотной коррекции с целью формирования заданных амплитудно-частотных характеристик ОУ и обеспечение запаса устойчивости по амплитуде и фазе, а также управления величиной Ку в тех случаях, когда заявляемая архитектура используется в качестве устройства с программируемыми параметрами. Операционный усилитель с цепью коррекции коэффициента усиления содержит входной дифференциальный каскад, токовое зеркало, выходной транзистор, двухполюсник коллекторной нагрузки, выходной буферный усилитель, цепь коррекции коэффициента усиления, дополнительный двухполюсник обратной связи. 9 з.п. ф-лы, 12 ил.

1. Операционный усилитель с цепью коррекции коэффициента усиления, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, эмиттерная цепь которого связана с первой (4) шиной источника питания, токовое зеркало (5), согласованное со второй (6) шиной источника питания, вход которого соединен со вторым (3) токовым выходом входного дифференциального каскада (1), а выход подключен к первому (2) токовому выходу входного дифференциального каскада (1) и базе выходного транзистора (7), двухполюсник коллекторной нагрузки (8), включенный между коллектором выходного транзистора (7) и первой (4) шиной источника питания, выходной буферный усилитель (9), вход которого соединен с коллектором выходного транзистора (7), причем эмиттер выходного транзистора (7) связан со входом токового зеркала (5), отличающийся тем, что эмиттер выходного транзистора (7) связан со входом токового зеркала (5) через цепь коррекции коэффициента усиления (10) и соединен со второй (6) шиной источника питания через дополнительный двухполюсник обратной связи (11).

2. Операционный усилитель с цепью коррекции коэффициента усиления по п.1, отличающийся тем, что токовое зеркало (5) содержит первый (12) вспомогательный транзистор, эмиттер которого подключен ко второй (6) шине источника питания, база соединена со входом токового зеркала (5), коллектор - с его выходом, а между базой первого (12) вспомогательного транзистора и второй (6) шиной источника питания включен первый (13) дополнительный р-n переход.

3. Операционный усилитель с цепью коррекции коэффициента усиления по п.2, отличающийся тем, что дополнительный двухполюсник обратной связи (11) выполнен в виде второго (14) дополнительного прямосмещенного р-n перехода.

4. Операционный усилитель с цепью коррекции коэффициента усиления по п.2, отличающийся тем, что дополнительный двухполюсник обратной связи (11) выполнен в виде двух параллельно включенных третьего (15) и четвертого (16) дополнительных прямосмещенных р-n переходов.

5. Операционный усилитель с цепью коррекции коэффициента усиления по п.4, отличающийся тем, что выход токового зеркала (5) подключен к первому (2) токовому выходу входного дифференциального каскада (1) и базе выходного транзистора (7) через согласующий р-n переход (17).

6. Операционный усилитель с цепью коррекции коэффициента усиления по п.1, отличающийся тем, что цепь коррекции коэффициента усиления (10) выполнена в виде первого (18) дополнительного резистора.

7. Операционный усилитель с цепью коррекции коэффициента усиления по п.1, отличающийся тем, что цепь коррекции коэффициента усиления (10) выполнена в виде первого (19) дополнительного конденсатора.

8. Операционный усилитель с цепью коррекции коэффициента усиления по п.1, отличающийся тем, что цепь коррекции коэффициента усиления (10) выполнена в виде последовательно соединенных второго (20) дополнительного резистора и второго (21) дополнительного конденсатора.

9. Операционный усилитель с цепью коррекции коэффициента усиления по п.1, отличающийся тем, что цепь коррекции коэффициента усиления (10) выполнена в виде первой дополнительной индуктивности (22).

10. Операционный усилитель с цепью коррекции коэффициента усиления по п.1, отличающийся тем, что цепь коррекции коэффициента усиления (10) выполнена в виде последовательно соединенных второй дополнительной индуктивности (23) и третьего (24) дополнительного конденсатора.

| US 3697882 А, 10.10.1972 | |||

| Колосоуборка | 1923 |

|

SU2009A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402154C1 |

Авторы

Даты

2012-08-20—Публикация

2011-05-19—Подача