Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в быстродействующих аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков, в том числе работающих в тяжелых условиях эксплуатации (низкая температура, радиация и т.п.).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ, реализованные на основе «перегнутых» каскодов и BJT, BiJFet или КМОП транзисторах [1-32], имеющие простейшую архитектуру и содержащие небольшое число элементов. Схемы ОУ данного класса характеризуются расширенным частотным диапазоном. Предполагаемое изобретение относится к данному типу устройств.

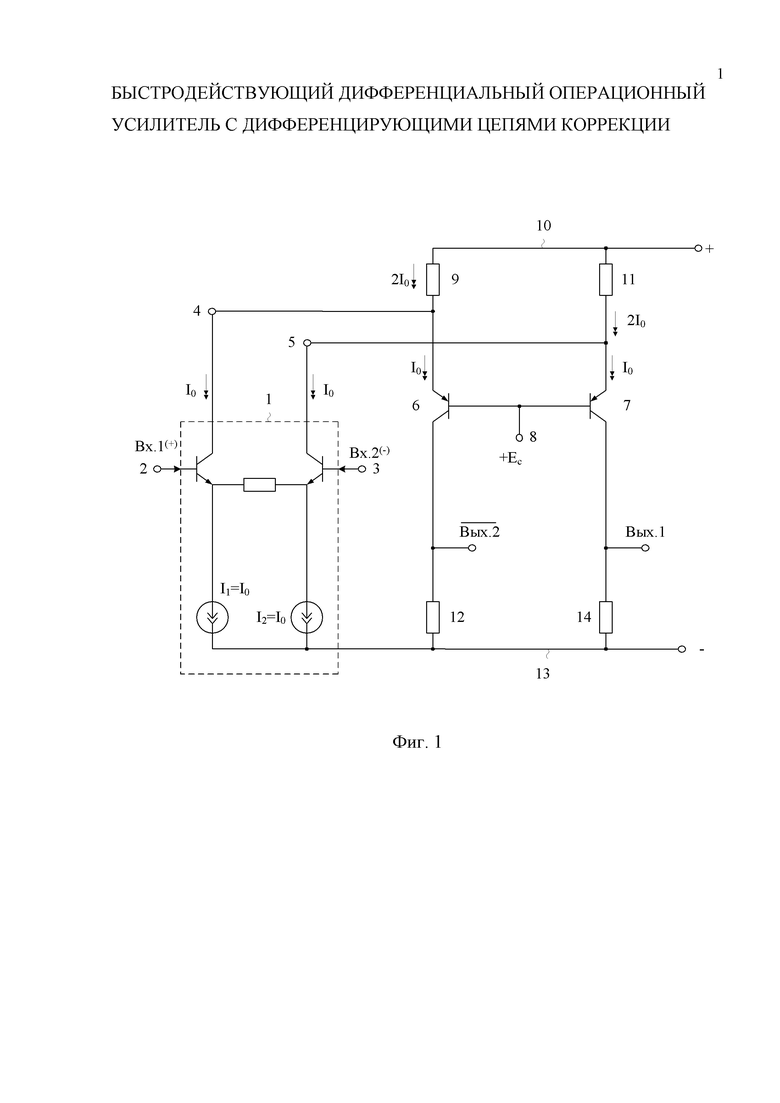

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ по патенту US № 4.600.893, fig. 4, 1986 г. Он содержит (фиг. 1) входной дифференциальный каскад 1 с дифференциальными входами 2 и 3, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора подключен к первому 4 токовому выходу входного дифференциального каскада 1 и через первый 9 токостабилизирующий двухполюсник связан с первой 10 шиной источника питания, эмиттер второго 7 выходного транзистора подключен ко второму 5 выходу входного дифференциального каскада 1 и через второй 11 токостабилизирующий двухполюсник связан с первой 10 шиной источника питания, первый 12 резистор коллекторной нагрузки, включенный между коллектором первого 6 выходного транзистора и второй 13 шиной источника питания, второй 14 резистор коллекторной нагрузки, включенный между коллектором второго 7 выходного транзистора и второй 13 шиной источника питания, токовый выход устройства 15.

Существенный недостаток известного ОУ состоит в том, что он имеет сравнительно небольшие значения максимальной скорости нарастания выходного напряжения (Slew rate – SR), что обусловлено неспособностью схемы обеспечить быстрый перезаряд корректирующего конденсатора, формирующего частоту единичного усиления ОУ на основе «перегнутого» каскода.

Основная задача предполагаемого изобретения состоит в повышении SR без ухудшения энергетических параметров ОУ на основе «перегнутого» каскода в статическом режиме, а также создании условий раздельного регулирования SR для переднего SR(+) и заднего SR(-) фронтов выходного напряжения при импульсных входных сигналах в типовых схемах включения. Дополнительная задача – повышение коэффициента усиления по напряжению ОУ.

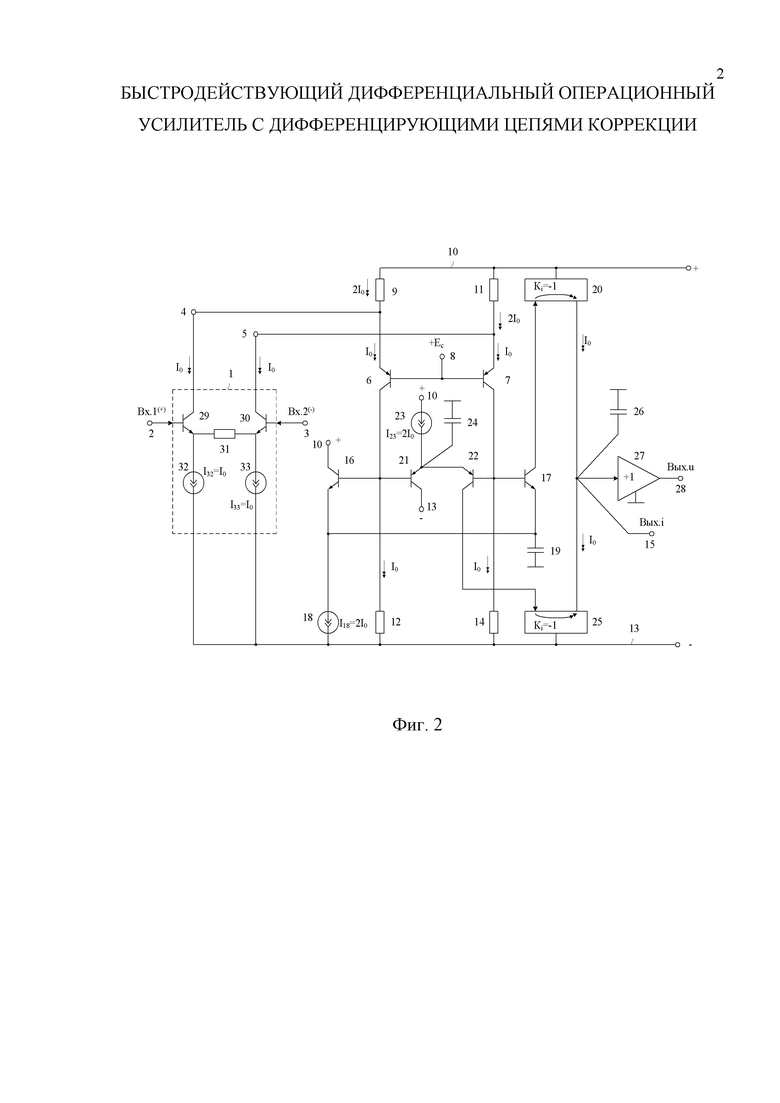

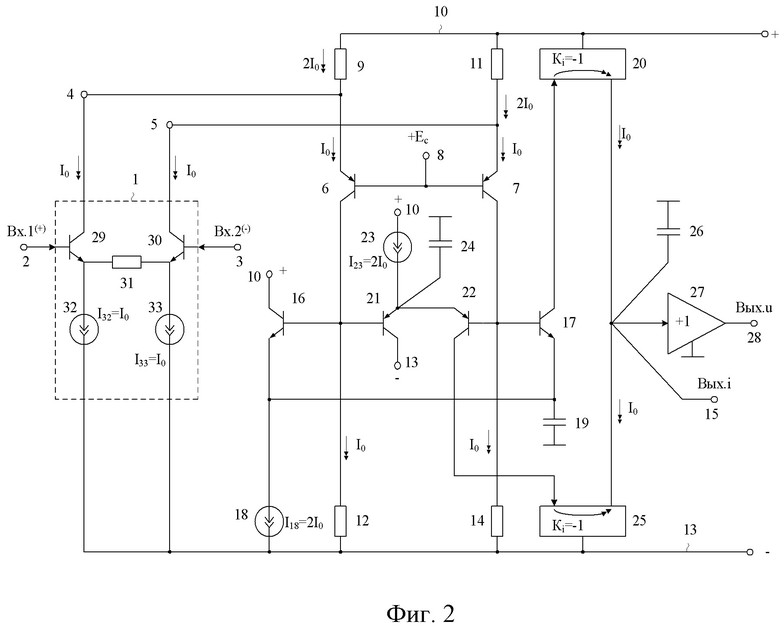

Поставленные задачи достигаются тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с дифференциальными входами 2 и 3, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора подключен к первому 4 токовому выходу входного дифференциального каскада 1 и через первый 9 токостабилизирующий двухполюсник связан с первой 10 шиной источника питания, эмиттер второго 7 выходного транзистора подключен ко второму 5 выходу входного дифференциального каскада 1 и через второй 11 токостабилизирующий двухполюсник связан с первой 10 шиной источника питания, первый 12 резистор коллекторной нагрузки, включенный между коллектором первого 6 выходного транзистора и второй 13 шиной источника питания, второй 14 резистор коллекторной нагрузки, включенный между коллектором второго 7 выходного транзистора и второй 13 шиной источника питания, токовый выход устройства 15, предусмотрены новые элементы и связи – в схему введены первый 16 и второй 17 вспомогательные транзисторы, объединенные эмиттеры которых связаны со второй 13 шиной источника питания через параллельно включенные по переменному току первый 18 токостабилизирующий двухполюсник и первый 19 корректирующий конденсатор, база первого 16 вспомогательного транзистора соединена с коллектором первого 6 выходного транзистора, коллектор первого 16 вспомогательного транзистора соединен с первой 10 шиной источника питания, база второго 17 вспомогательного транзистора подключена к коллектору второго 7 выходного транзистора, коллектор второго 17 вспомогательного транзистора соединен со входом первого 20 дополнительного токового зеркала, согласованного с первой 10 шиной источника питания, база третьего 21 вспомогательного транзистора соединена с базой первого 16 вспомогательного транзистора, эмиттер третьего 21 вспомогательного транзистора соединен с эмиттером четвертого 22 вспомогательного транзистора и через параллельно включенные по переменному току второй 23 токостабилизирующий двухполюсник и второй 24 корректирующий конденсатор связан с первой 10 шиной источника питания, коллектор третьего 21 вспомогательного транзистора подключен ко второй 13 шине источника питания, база четвертого 22 вспомогательного транзистора соединена с базой второго 17 вспомогательного транзистора, а коллектор соединен со входом второго 25 токового зеркала, согласованного со второй 13 шиной источника питания, причем токовые выходы первого 20 и второго 25 токовых зеркал подключены к токовому выходу устройства 15 и связаны с третьим 26 корректирующим конденсатором.

На чертеже фиг. 1 показана схема ОУ-прототипа. На чертеже фиг. 2 представлена схема заявляемого ОУ в соответствии с п.1 и п.2 формулы изобретения.

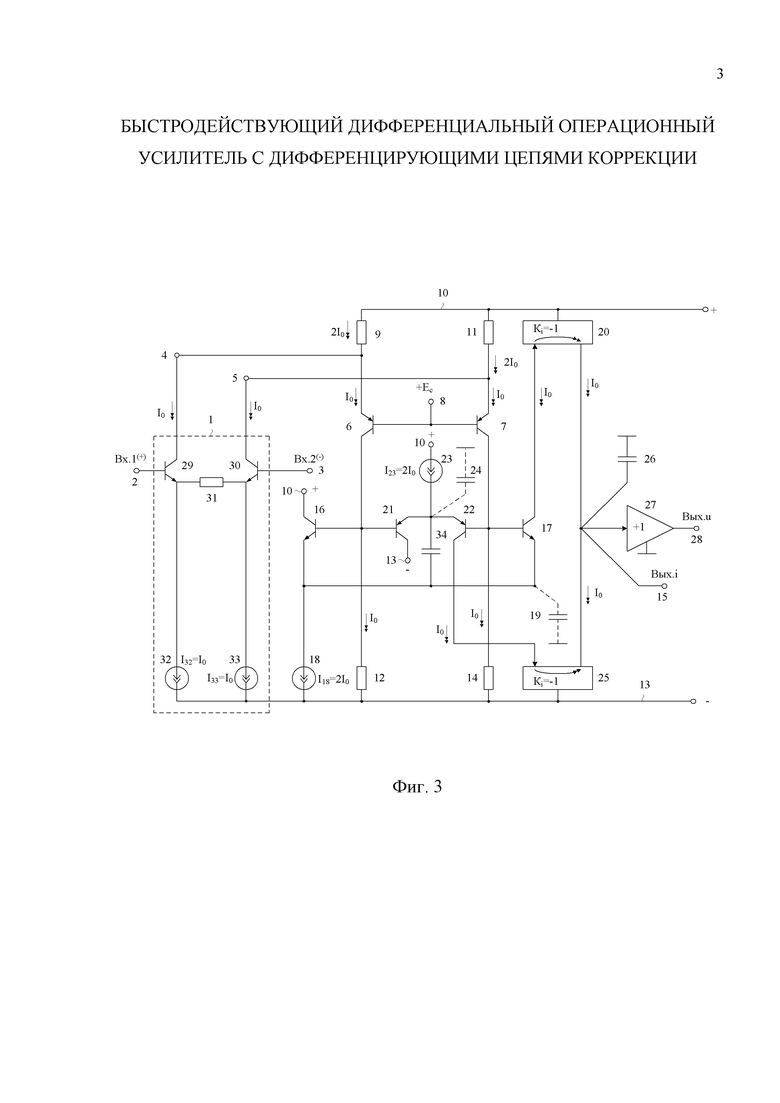

На чертеже фиг. 3 изображена схема заявляемого ОУ в соответствии с п.3 формулы изобретения.

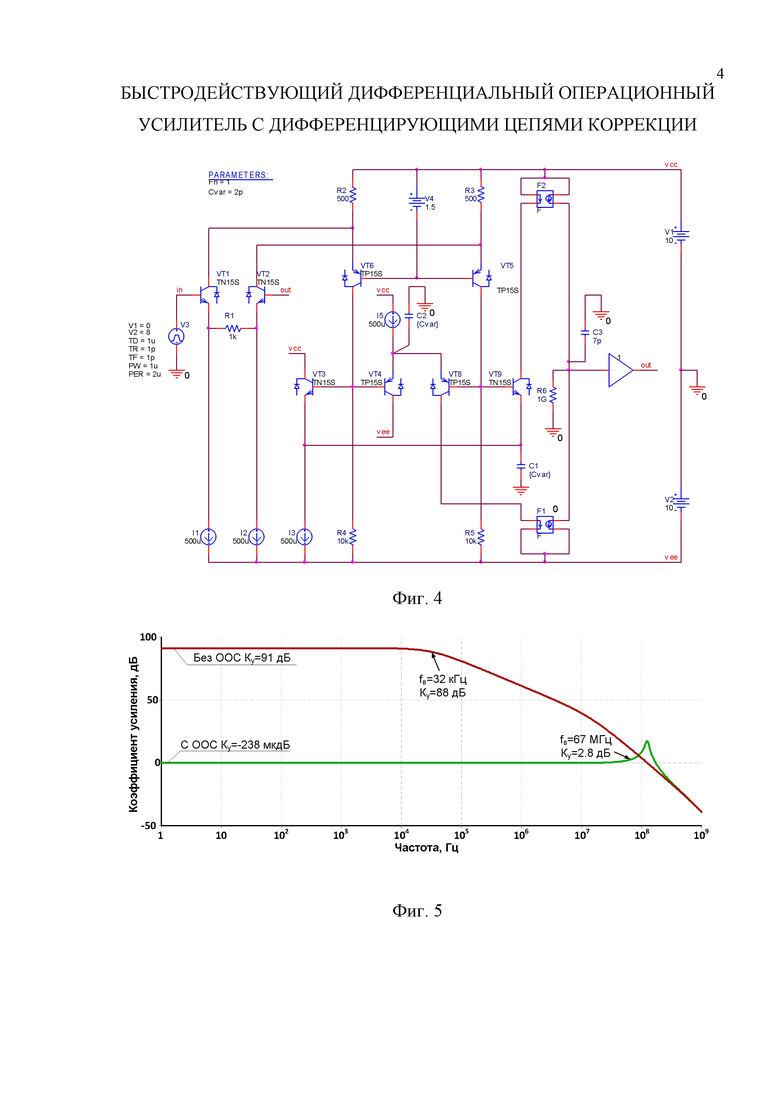

На чертеже фиг. 4 приведена схема ОУ фиг. 2 при 100% отрицательной обратной связи в среде PSpice на моделях комплементарных интегральных транзисторов АО «НПП «Пульсар» (г. Москва).

На чертеже фиг. 5 представлены амплитудно-частотные характеристики коэффициента усиления в ОУ фиг. 4 со 100% ООС и без 100% ООС, рассчитанные в среде PSpice на моделях комплементарных транзисторов АО «НПП «Пульсар» (г. Москва).

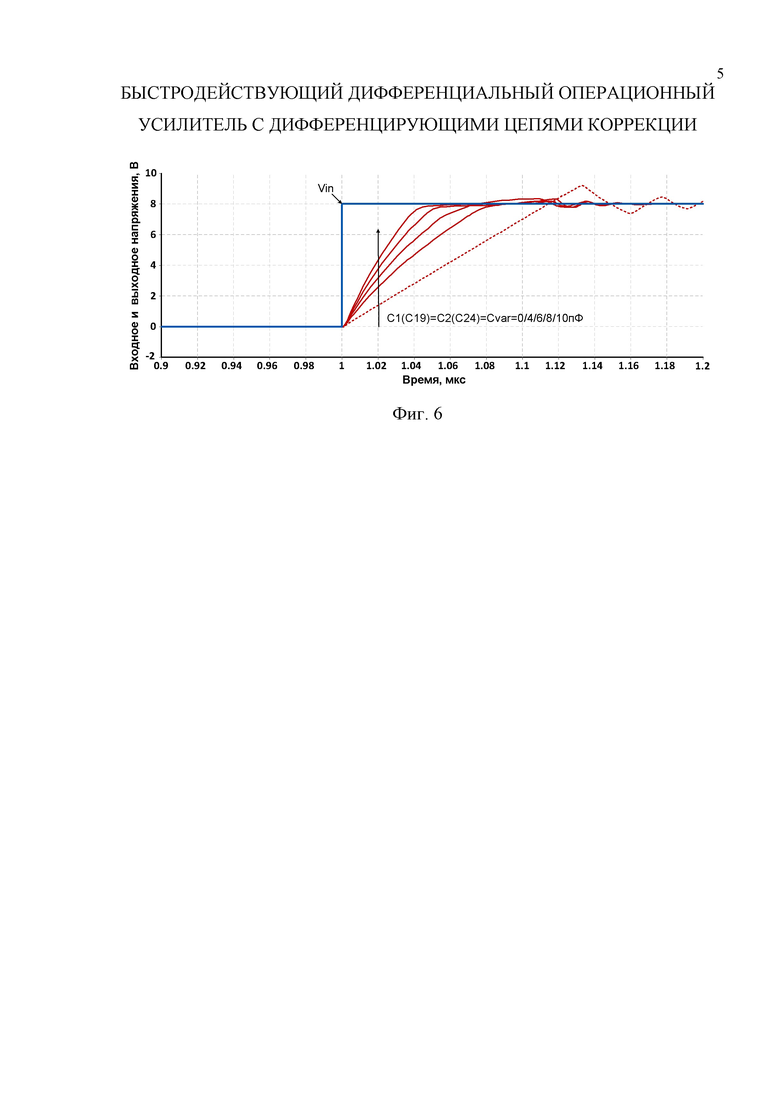

На чертеже фиг. 6 изображен передний фронт выходного напряжения ОУ фиг. 4 при амплитуде входного импульса напряжения Uвх(+)=8В, емкости третьего 26 корректирующего конденсатора С3(С26)=7пФ и разных значениях емкостей первого 19 и второго 24 корректирующих конденсаторов С1(С19)=С2(С24)=Сvar=0/4/6/8/10 пФ.

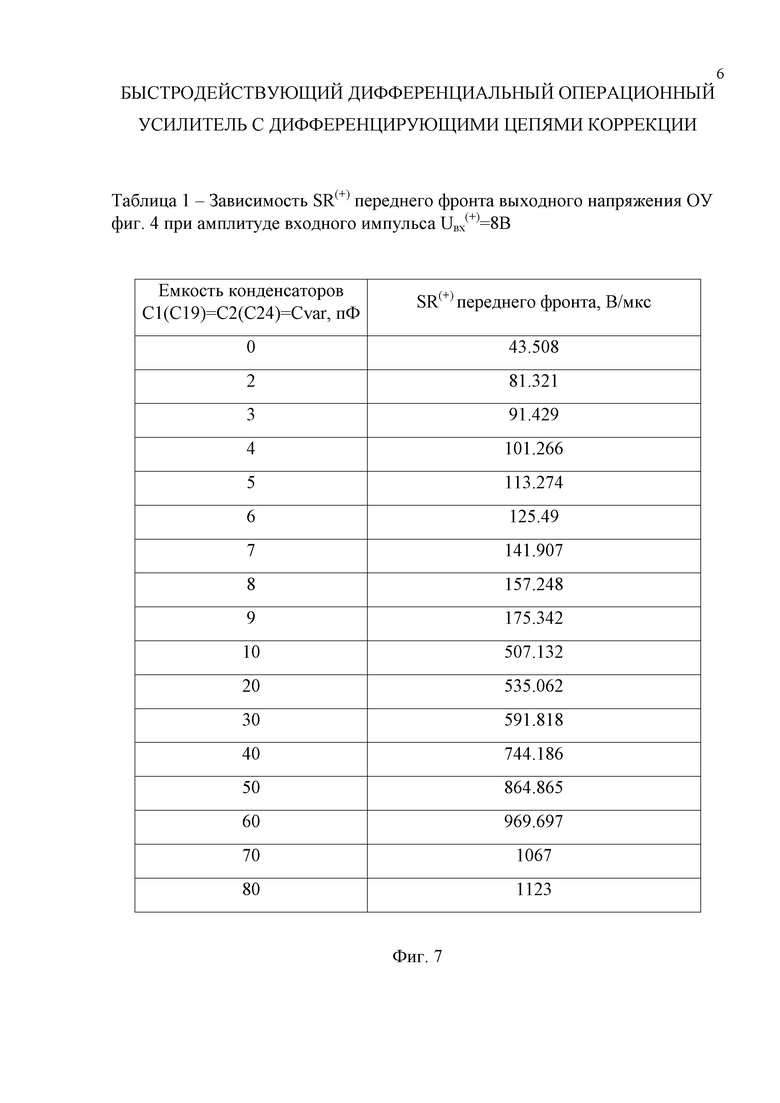

На чертеже фиг. 7 показана таблица зависимости SR(+) переднего фронта выходного напряжения ОУ фиг. 4 при амплитуде входного импульса напряжения Uвх(+)=8В, емкости третьего 26 корректирующего конденсатора С3(С26)=7пФ и разных значениях емкостей первого 19 и второго 24 корректирующих конденсаторов, изменяющихся в диапазоне С1(С19)=С2(С24)=Сvar=0÷80пФ.

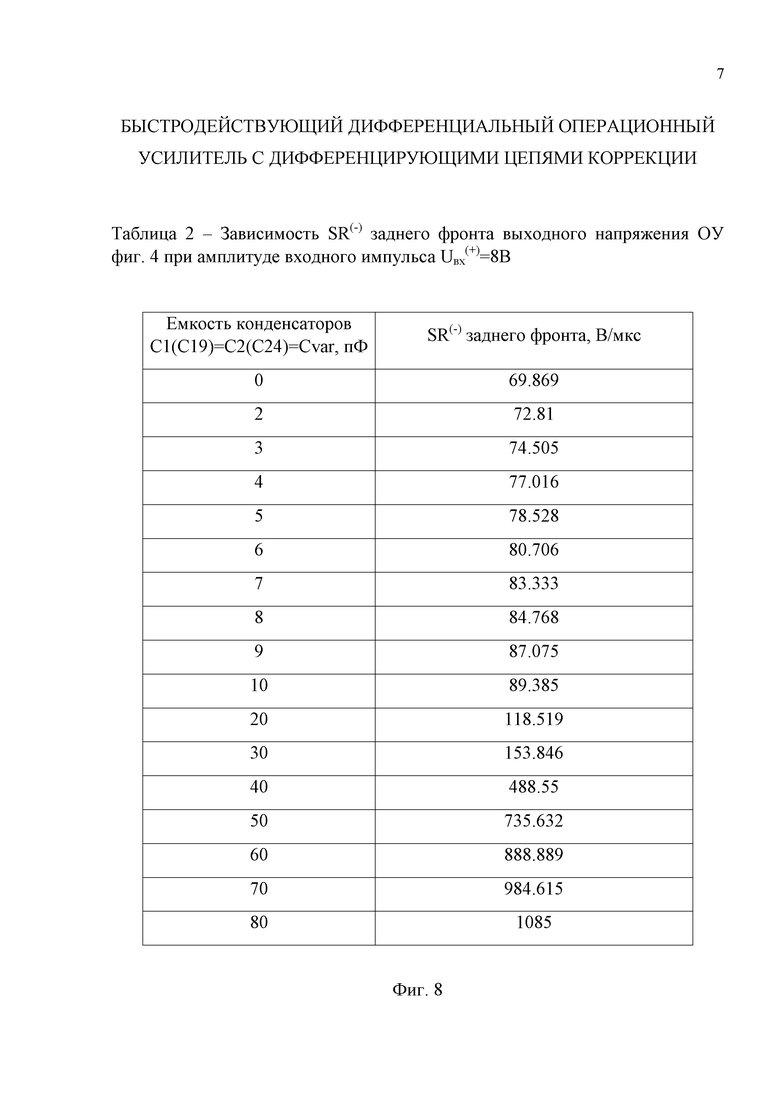

На чертеже фиг. 8 приведена таблица зависимости SR(-) заднего фронта выходного напряжения ОУ фиг. 4 при амплитуде входного импульса напряжения Uвх(+)=8В, емкости третьего 26 корректирующего конденсатора С3(С26)=7пФ и разных значениях емкостей первого 19 и второго 24 корректирующих конденсаторов, изменяющихся в диапазоне С1(С19)=С2(С24)=Сvar=0÷80пФ.

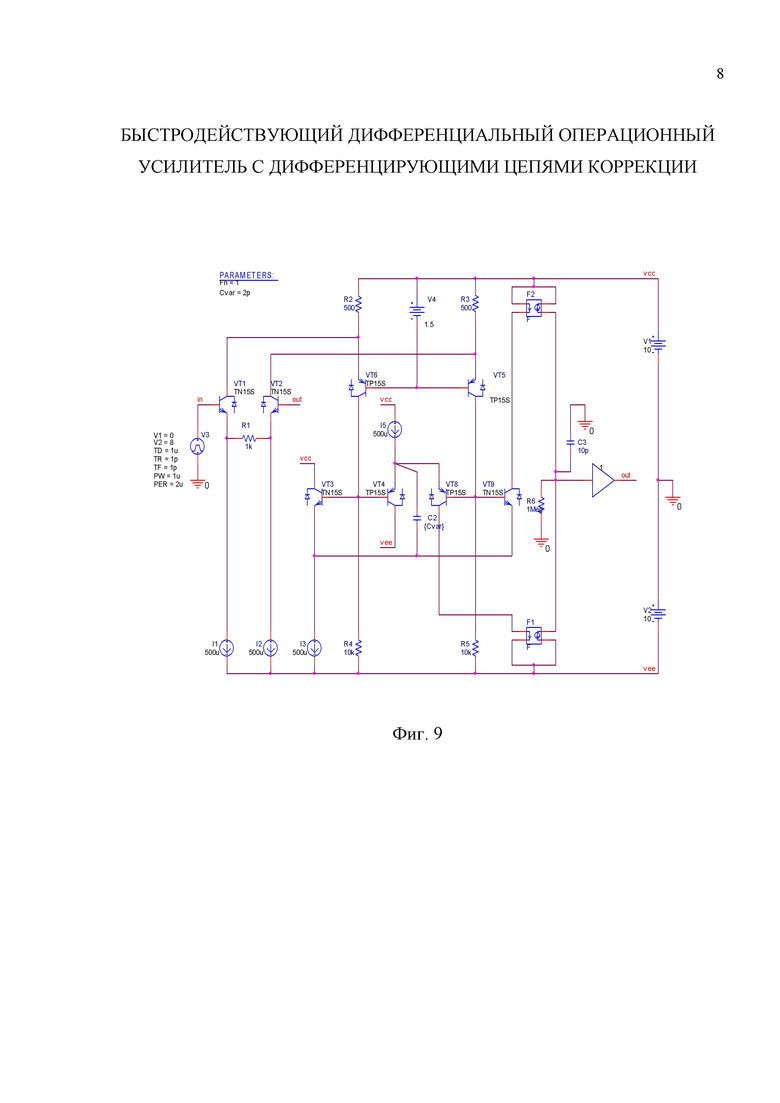

На чертеже фиг. 9 представлена схема заявляемого ОУ фиг. 3 в среде PSpice на моделях интегральных транзисторов АО «НПП «Пульсар» для измерений SR(+) и SR(-).

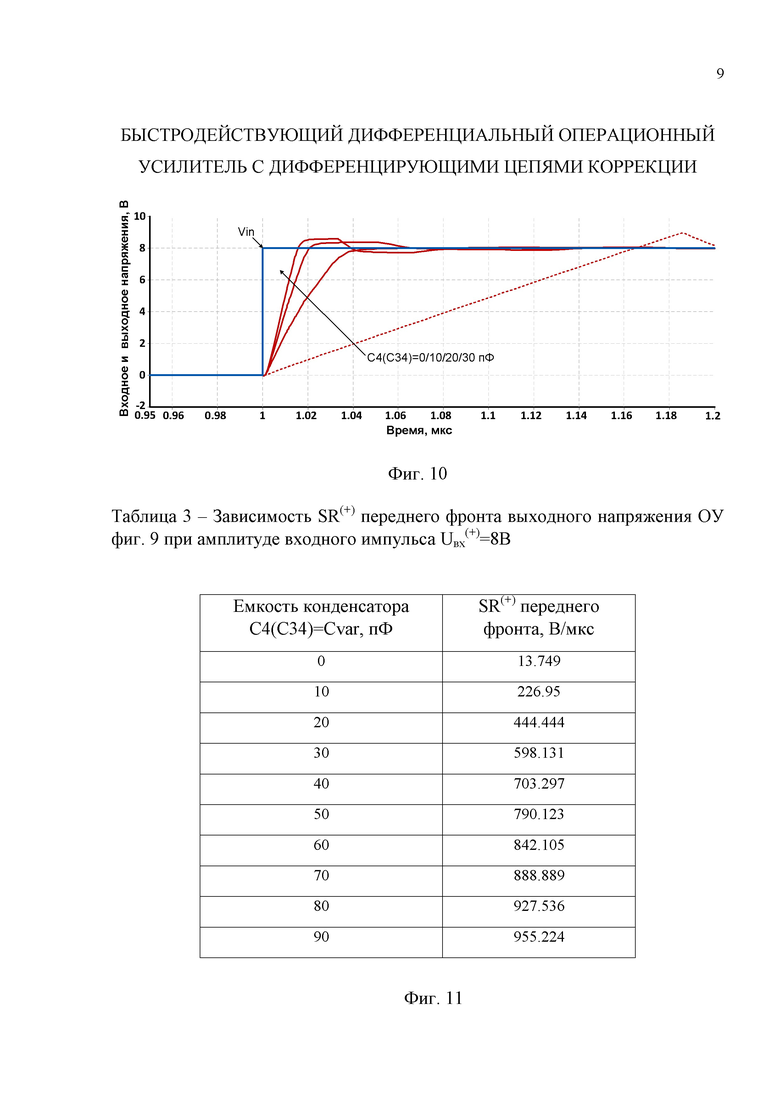

На чертеже фиг. 10 показан передний фронт импульса выходного напряжения ОУ фиг. 9 при емкости третьего 26 корректирующего конденсатора С3(С26)=10пФ и разных значениях емкости четвертого 34 корректирующего конденсатора, изменяющейся в диапазоне С4(С34)=0ч30 пФ.

На чертеже фиг. 11 показана таблица зависимости SR(+) переднего фронта импульса выходного напряжения ОУ фиг. 9 при амплитуде входного напряжения Uвх(+)=8В, емкости третьего 26 корректирующего конденсатора С3(С26)=10пФ и разных значениях емкости четвертого 34 корректирующего конденсатора, изменяющейся в диапазоне С4(С34)=0ч90 пФ.

Быстродействующий дифференциальный операционный усилитель с дифференцирующими цепями коррекции фиг. 2 содержит входной дифференциальный каскад 1 с дифференциальными входами 2 и 3, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора подключен к первому 4 токовому выходу входного дифференциального каскада 1 и через первый 9 токостабилизирующий двухполюсник связан с первой 10 шиной источника питания, эмиттер второго 7 выходного транзистора подключен ко второму 5 выходу входного дифференциального каскада 1 и через второй 11 токостабилизирующий двухполюсник связан с первой 10 шиной источника питания, первый 12 резистор коллекторной нагрузки, включенный между коллектором первого 6 выходного транзистора и второй 13 шиной источника питания, второй 14 резистор коллекторной нагрузки, включенный между коллектором второго 7 выходного транзистора и второй 13 шиной источника питания, токовый выход устройства 15. В схему введены – первый 16 и второй 17 вспомогательные транзисторы, объединенные эмиттеры которых связаны со второй 13 шиной источника питания через параллельно включенные по переменному току первый 18 токостабилизирующий двухполюсник и первый 19 корректирующий конденсатор, база первого 16 вспомогательного транзистора соединена с коллектором первого 6 выходного транзистора, коллектор первого 16 вспомогательного транзистора соединен с первой 10 шиной источника питания, база второго 17 вспомогательного транзистора подключена к коллектору второго 7 выходного транзистора, коллектор второго 17 вспомогательного транзистора соединен со входом первого 20 дополнительного токового зеркала, согласованного с первой 10 шиной источника питания, база третьего 21 вспомогательного транзистора соединена с базой первого 16 вспомогательного транзистора, эмиттер третьего 21 вспомогательного транзистора соединен с эмиттером четвертого 22 вспомогательного транзистора и через параллельно включенные по переменному току второй 23 токостабилизирующий двухполюсник и второй 24 корректирующий конденсатор связан с первой 10 шиной источника питания, коллектор третьего 21 вспомогательного транзистора подключен ко второй 13 шине источника питания, база четвертого 22 вспомогательного транзистора соединена с базой второго 17 вспомогательного транзистора, а коллектор соединен со входом второго 25 токового зеркала, согласованного со второй 13 шиной источника питания, причем токовые выходы первого 20 и второго 25 токовых зеркал подключены к токовому выходу устройства 15 и связаны с третьим 26 корректирующим конденсатором.

На чертежах фиг. 2 и фиг. 3, в соответствии с п. 2 формулы изобретения, токовый выход устройства 15 соединен со входом буферного усилителя напряжения 27, выход которого является низкоомным потенциальным выходом устройства 28.

На схеме фиг. 2 входной дифференциальный каскад 1 реализован в частном случае на транзисторах 29, 30, резисторе местной отрицательной обратной связи 31 и источниках опорного тока 32, 33.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, между объединенными эмиттерами третьего 21 и четвертого 22 вспомогательных транзисторов и объединенными эмиттерами первого 16 и второго 17 вспомогательных транзисторов включен четвертый 34 корректирующий конденсатор.

Рассмотрим работу предлагаемого ОУ фиг. 2 в схеме со 100% отрицательной обратной связью с низкоомного потенциального выхода устройства 28 на дифференциальный вход 3 при импульсном положительном изменении напряжения на неинвертирующем входе 2.

Особенность ОУ фиг. 2 состоит в том, что входной дифференциальный каскад 1 имеет небольшую крутизну преобразования входного дифференциального напряжения в его выходные токи для первого 4 и второго 5 токовых выходов. Это обеспечивается соответствующим выбором резистора 31. Однако, входной дифференциальный каскад 1, имея небольшое усиление (1ч5 раз), обеспечивает подавление входного синфазного сигнала ОУ, что является обязательным условием повышения SR в заявленном устройстве.

Импульсное изменение напряжения на дифференциальном входе 2 вызывает увеличение коллекторного тока транзистора 29 и уменьшение коллекторного тока транзистора 30. В результате коллекторный ток второго 7 выходного транзистора увеличивается, а первого 6 выходного транзистора уменьшается. Как следствие, коллекторные токи второго 17 и третьего 21 вспомогательных транзисторов увеличиваются, а эмиттерные токи первого 16 и четвертого 22 вспомогательных транзисторов уменьшаются. Это приводит к импульсному увеличению тока через первый 19 корректирующий конденсатор и его передачу через второй 17 вспомогательный транзистор на вход первого 20 дополнительного токового зеркала и далее на его выход, который связан с третьим 26 корректирующим конденсатором. Как следствие, скорость перезаряда третьего 26 корректирующего конденсатора существенно увеличивается, что повышает быстродействие ОУ фиг. 2.

При отрицательном импульсном изменении напряжения на дифференциальном входе 2 запирается транзистор 29, увеличивается коллекторный ток первого 6 выходного транзистора и уменьшается коллекторный ток второго 7 выходного транзистора, что приводит к формированию импульса тока через второй 24 корректирующий конденсатор, его передачу в эмиттер четвертого 22 вспомогательного транзистора и, далее, на вход второго 25 токового зеркала. В результате третий 26 корректирующий конденсатор перезаряжается быстрее, что повышает быстродействие ОУ в режиме большого сигнала.

Особенность схемы фиг. 3 состоит в том, что здесь кроме первого 19 и второго 24 корректирующих конденсаторов имеется четвертый 34 корректирующий конденсатор, который в конечном итоге также форсирует перезаряд третьего 26 корректирующего конденсатора и повышает быстродействие ОУ.

В практических схемах ОУ фиг. 3 могут применяться одновременно как первый 19 и второй 24 корректирующие конденсаторы, так и четвертый 34 корректирующий конденсатор. За счет выбора оптимальных значений емкости этих конденсаторов можно получить существенный выигрыш по максимальной скорости нарастания ОУ фиг. 3 на основе «перегнутого» каскода.

Чертежи фиг. 6 и таблицы 1 и 2 (фиг. 7, фиг. 8) показывают эффективность применения только первого 19 и второго 24 корректирующих конденсаторов в схеме фиг. 4.

Графики фиг. 10 и таблица 3 (фиг. 11) иллюстрирую эффект повышения быстродействия в ОУ фиг. 9 только за счет четвертого 34 корректирующего конденсатора.

Введение дополнительных элементов в исходную схему в соответствии с формулой изобретения позволяет повысить коэффициент усиления по напряжению разомкнутого ОУ (фиг. 2, фиг. 3).

Заявляемые положительные эффекты реализуется также при низкотемпературных BiJFet [33] и классических КМОП технологических процессах.

Таким образом, в сравнении с ОУ-прототипом предлагаемые схемотехнические решения ОУ обладают существенными преимуществами по динамическим параметрам в режиме большого сигнала.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 4.600.893, fig. 4, 1986 г.

2. Патент US 3.979.689, fig. 2, 1976 г.

3. Патент US RE 30.587, 1981 г.

4. Патент US 4.151.483, fig. 4, 1979 г.

5. Патент US 4.151.484, fig. 4, 1979 г.

6. Патент US 4.406.990, fig. 3, 1983 г.

7. Патент US 4.463.319, 1984 г.

8. Патент US 7.791.414, fig. 6, 2010 г.

9. Патент US 6.924.701, , fig. 1А, 2005 г.

10. Патент US 5.455.535, 1995 г.

11. Патент US 6.788.143, fig. 2, 2004 г.

12. Патент US 5.153.529, 1995 г.

13. Патентная заявка US 2003/0090321, fig. 8, 2007 г.

14. Патентная заявка US 2007/0069815, fig. 1, 2007 г.

15. Патент US 6.696.894, 2004 г.

16. Патент US 5.455.536, 1995 г.

17. Патент US 5.963.085, 1999 г.

18. Патент US 5.966.050, fig. 4, 1999 г.

19. Патент US 5.166.637, fig. 3, 1992 г.

20. Патент US 6.529.076, 2003 г.

21. Патент US 6.483.382, fig.2, fig.1, 2002 г.

22. Патент US 5.627.495, fig. 2, 1997 г.

23. Патент US 5.327.100, fig. 1, 1994 г.

24. Патент US 4.390.850, fig. 1, 1983 г.

25. Патент US 5.610.557, fig. 2A, 1997 г.

26. Патент US 8.350.622, 2013 г.

27. Патент US 5.418.491, fig.1, 1995 г.

28. Патент US 4.783.637, fig. 2, 1988 г.

29. Патент US 5.091.701, fig. 1, 1992 г.

30. Патент US 5.140.280, 1992 г.

31. Патент US 5.786.729, 1998 г.

32. I.M. Filanovsky, V.V. Ivanov, “Operational Amplifier Speed and Accuracy Improvement: Analog Circuit Design with Structural Methodology,” Kluwer Academic Publishers, New York, Boston, Dordrecht, London, 2004, 194 p.

33. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ВЫСОКОЧАСТОТНОЙ КОРРЕКЦИЕЙ | 2010 |

|

RU2423778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2011 |

|

RU2439783C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| Быстродействующий дифференциальный операционный усилитель | 2018 |

|

RU2688227C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2475942C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2441315C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

Изобретение относится к дифференциальным операционным усилителям. Технический результат заключается в повышении максимальной скорости нарастания выходного напряжения без ухудшения энергетических параметров. Дифференциальный операционный усилитель содержит входной дифференциальный каскад с дифференциальными входами, а также первым и вторым токовыми выходами, первый и второй выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения, первый токостабилизирующий двухполюсник, второй токостабилизирующий двухполюсник, первый резистор коллекторной нагрузки, второй резистор коллекторной нагрузки, токовый выход устройства, первый и второй вспомогательные транзисторы, первый токостабилизирующий двухполюсник и первый корректирующий конденсатор, первое дополнительное токовое зеркало, третий вспомогательный транзистор, четвертый вспомогательный транзистор, второй токостабилизирующий двухполюсник и второй корректирующий конденсатор, второе токовое зеркало, третий корректирующий конденсатор. 2 з.п. ф-лы, 11 ил.

1. Быстродействующий дифференциальный операционный усилитель с дифференцирующими цепями коррекции, содержащий входной дифференциальный каскад (1) с дифференциальными входами (2) и (3), а также первым (4) и вторым (5) токовыми выходами, первый (6) и второй (7) выходные транзисторы, объединенные базы которых подключены к источнику напряжения смещения (8), эмиттер первого (6) выходного транзистора подключен к первому (4) токовому выходу входного дифференциального каскада (1) и через первый (9) токостабилизирующий двухполюсник связан с первой (10) шиной источника питания, эмиттер второго (7) выходного транзистора подключен ко второму (5) выходу входного дифференциального каскада (1) и через второй (11) токостабилизирующий двухполюсник связан с первой (10) шиной источника питания, первый (12) резистор коллекторной нагрузки, включенный между коллектором первого (6) выходного транзистора и второй (13) шиной источника питания, второй (14) резистор коллекторной нагрузки, включенный между коллектором второго (7) выходного транзистора и второй (13) шиной источника питания, токовый выход устройства (15), отличающийся тем, что в схему введены первый (16) и второй (17) вспомогательные транзисторы, объединенные эмиттеры которых связаны со второй (13) шиной источника питания через параллельно включенные по переменному току первый (18) токостабилизирующий двухполюсник и первый (19) корректирующий конденсатор, база первого (16) вспомогательного транзистора соединена с коллектором первого (6) выходного транзистора, коллектор первого (16) вспомогательного транзистора соединен с первой (10) шиной источника питания, база второго (17) вспомогательного транзистора подключена к коллектору второго (7) выходного транзистора, коллектор второго (17) вспомогательного транзистора соединен с входом первого (20) дополнительного токового зеркала, согласованного с первой (10) шиной источника питания, база третьего (21) вспомогательного транзистора соединена с базой первого (16) вспомогательного транзистора, эмиттер третьего (21) вспомогательного транзистора соединен с эмиттером четвертого (22) вспомогательного транзистора и через параллельно включенные по переменному току второй (23) токостабилизирующий двухполюсник и второй (24) корректирующий конденсатор связан с первой (10) шиной источника питания, коллектор третьего (21) вспомогательного транзистора подключен ко второй (13) шине источника питания, база четвертого (22) вспомогательного транзистора соединена с базой второго (17) вспомогательного транзистора, а коллектор соединен с входом второго (25) токового зеркала, согласованного со второй (13) шиной источника питания, причем токовые выходы первого (20) и второго (25) токовых зеркал подключены к токовому выходу устройства (15) и связаны с третьим (26) корректирующим конденсатором.

2. Быстродействующий дифференциальный операционный усилитель с дифференцирующими цепями коррекции по п. 1, отличающийся тем, что токовый выход устройства (15) соединен с входом буферного усилителя напряжения (27), выход которого является низкоомным потенциальным выходом устройства (28).

3. Быстродействующий дифференциальный операционный усилитель с дифференцирующими цепями коррекции по п. 1, отличающийся тем, что между объединенными эмиттерами третьего (21) и четвертого (22) вспомогательных транзисторов и объединенными эмиттерами первого (16) и второго (17) вспомогательных транзисторов включен четвертый (34) корректирующий конденсатор.

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2640744C1 |

| US 7701291 B2, 20.04.2010 | |||

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390916C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С КОМПЛЕМЕНТАРНЫМ ВХОДНЫМ КАСКАДОМ | 2012 |

|

RU2475941C1 |

Авторы

Даты

2019-04-09—Публикация

2018-07-17—Подача