Предлагаемое изобретение относится к технике электросвязи и может быть использовано в системах передачи данных по KB и УКВ радиоканалам.

Уже известны радиомодемы, описанные, например, в работах [1, 2] и основанные на последовательной передаче данных по радиоканалу с замираниями. Наличие в таких каналах эффекта многолучевости, при котором задержка распространения отдельных лучей достигает нескольких миллисекунд, приводит к существенной межсимвольной интерференции (МСИ). Для борьбы с этим явлением используются адаптивные корректоры, основанные на периодическом оценивании характеристик канала путем тестирования его специальной последовательностью. Эта последовательность должна быть достаточно длинной, чтобы отразить все особенности характеристик канала, обусловленные наличием МСИ. Это приводит к снижению скорости передачи (также при этом уменьшается полезная мощность передаваемого сигнала). Поэтому как отмечается в работе [3], подобные устройства обладают относительно низкой информационной скоростью.

Известны параллельные радиомодемы [4], построенные с использованием нескольких десятков пилот-сигналов, параметры которых зависят только от состояния среды распространения и могут быть определены и использованы в процессе демодуляции на приемной стороне радиолинии. Наличие большого числа неинформативных сигналов существенно снижает как энергетическую эффективность подобных устройств, так и эффективность использования ими выделенной полосы частот, что в конечном итоге приводит к уменьшению помехоустойчивости.

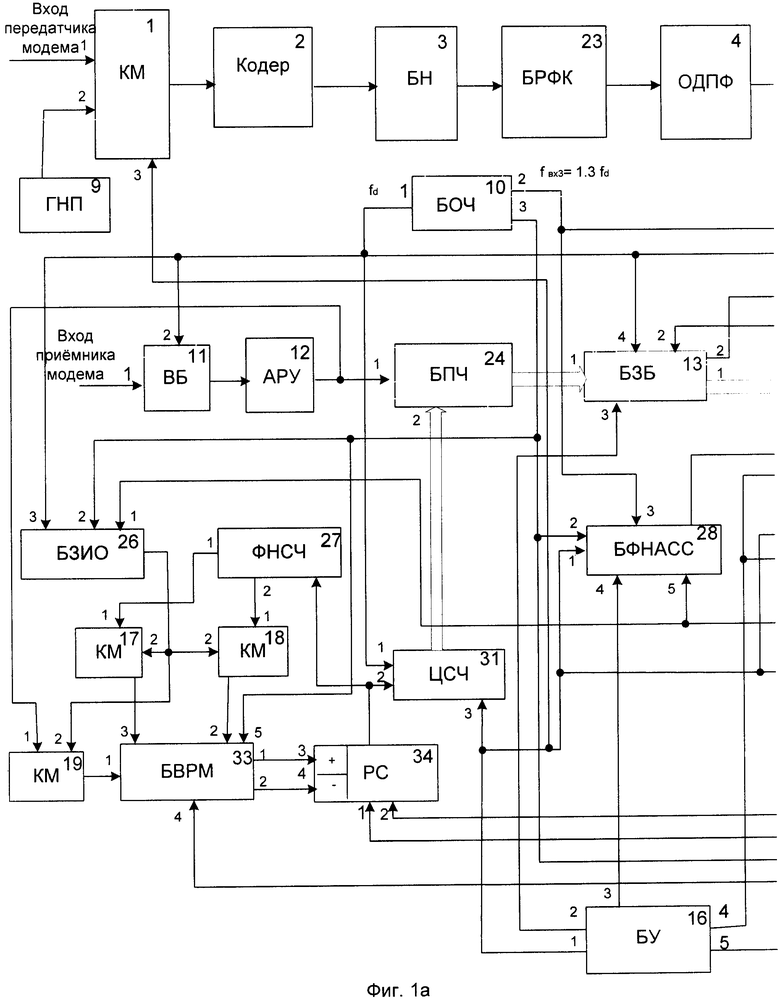

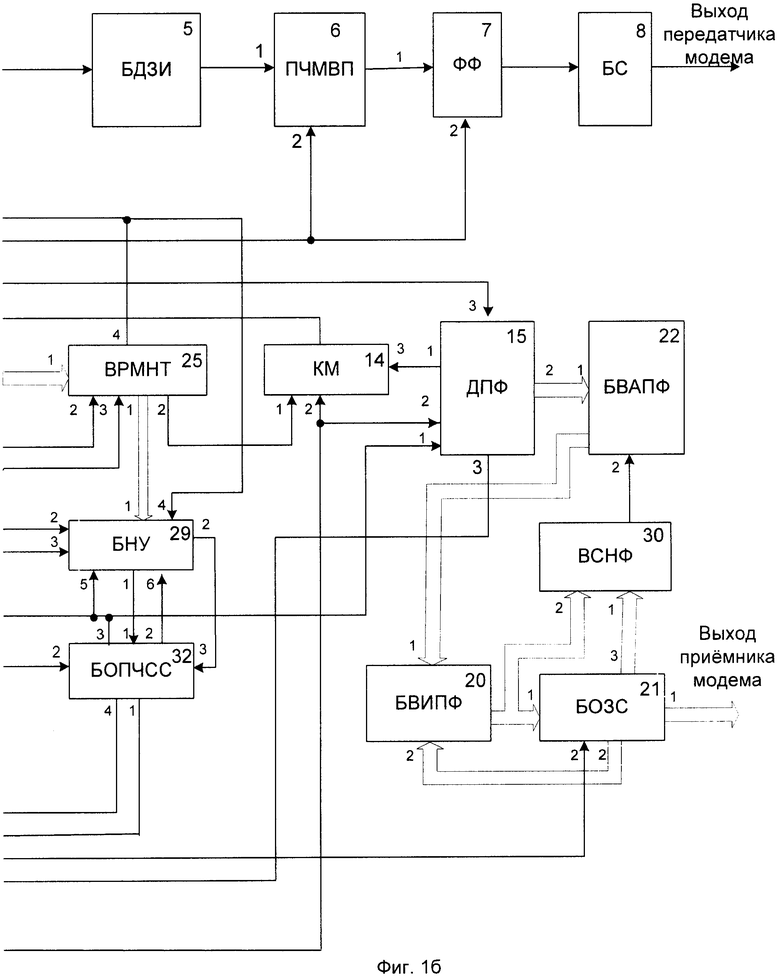

Известен параллельный радиомодем [5], наиболее близкий к предлагаемому изобретению. Структурная схема этого устройства приведена на фиг.1. Отметим, что с целью обеспечения возможности выявления существенных отличительных признаков заявляемого объекта на фиг.1 представлена функциональная схема устройства, построенная в строгом соответствии с приводимым в тексте работы [5] описанием принципов реализации и взаимодействия отдельных узлов данного устройства. Представленная функциональная схема является более полной и подробной, чем на фиг.12-17 вышеупомянутой работы [5]. Радиомодем содержит пять коммутаторов (КМ) 1, 14, 17, 18 и 19, кодер 2, буферный накопитель (БН) 3, блок 23 распределения и формирования кадров (БРФК), блок 4 вычисления обратного дискретного преобразования Фурье (ОДПФ), блок 5 добавления защитного интервала (БДЗИ), преобразователь числового массива во временную последовательность (ПЧМВП) 6, формирующий фильтр (ФФ) 7, блок 8 согласования (БС), генератор настроечной последовательности (ГНП) 9, блок 10 опорных частот (БОЧ), входной блок (ВБ) 11, блок 12 автоматической регулировки усиления (АРУ), блок 24 преобразователей частоты (БПЧ), буферный запоминающий блок 13 (БЗБ), вычислитель разностной мощности несигнального тона 25 (ВРМНТ), блок 15 дискретного преобразования Фурье (ДПФ), блок 22 вычисления аргумента и поворота фазы (БВАПФ), блок 26 задания интервала ортогональности (БЗИО), формирователь 27 отсчетов несущих со смещенными частотами (ФНСЧ), блок 28 формирования начального адреса при тестировании символьной синхронизации (БФНАСС), блок 29 накопления и усреднения (БНУ), блок 30 вычисления среднего набега фазы (ВСНФ), блок 31 цифровых синтезаторов частот (ЦСЧ), блок 32 определения оптимальных положений частотной и символьной синхронизации (БОПЧСС), блок 20 вычисления информативного приращения фазы (БВИПФ), блок 21 оценки значений символов и эталонной фазы (БОЗС), блок 33 вычисления разностной мощности и усреднения (БВРМ), реверсивный счетчик (PC) 34 и блок 16 управления (БУ), причем первый вход коммутатора 1 соединен со входом передатчика модема, второй вход этого коммутатора подключен к генератору настроечной последовательности 9, третий вход коммутатора 1 соединен с первым выходом БУ 16, третьим входом блока 31 цифровых синтезаторов частот, первым входом блока 28 формирования начального адреса, вторыми входами блока 29 усреднения и блока 32 определения оптимальных положений частотной и символьной синхронизации; выход коммутатора 1 подключен ко входу кодера 2, выход кодера 2 связан со входом буферного накопителя 3, выход буферного накопителя 3 соединен со входом блока 23 распределения и формирования кадров, выход которого подключен ко входу блока 4 вычисления ОДПФ, выход блока 4 вычисления ОДПФ связан со входом блока 5 добавления защитного интервала 5, выход которого соединен с первым входом преобразователя числового массива во временную последовательность 6, второй вход которого связан с первым выходом БОЧ 10, со вторыми входами формирующего фильтра 7 и входного блока 11, с четвертым входом буферного запоминающего блока 13, третьим входом блока 26 задания интервала ортогональности и первым входом блока 31 цифровых синтезаторов частот, выход преобразователя числового массива во временную последовательность 6 подключен к первому входу формирующего фильтра 7, выход которого соединен со входом блока 8 согласования, выход блока согласования связан со входом канала; выход канала связи подключен к первому входу входного блока 11, выход которого соединен со входом АРУ 12, выход АРУ связан с первыми входами блока 24 преобразователей частоты и коммутатора 19, второй вход блока 24 подключен к выходу блока 31 цифровых синтезаторов частот, выход блока 24 преобразователей частоты соединен с первым входом буферного запоминающего блока 13, второй вход которого связан с выходом второго коммутатора 14, третий вход буферного запоминающего блока 13 подключен ко второму выходу блока управления 16; первый и второй выходы буферного запоминающего блока 13 соединены соответственно с первым входом вычислителя разностной мощности несигнального тона 25 и третьим входом блока 15 ДПФ, второй вход вычислителя разностной мощности несигнального тона 25 связан с выходом блока 28 формирования начального адреса при тестировании символьной синхронизации, третий вход вычислителя разностной мощности несигнального тона 25 соединен с третьим входом блока 29 накопления и усреднения и четвертым выходом блока управления 16; четвертый вход вычислителя 25 разностной мощности несигнального тона подключен к четвертому входу блока 29 накопления и усреднения, третьему входу блока 28 формирования начального адреса при тестировании символьной синхронизации и второму выходу БОЧ 10, первый выход вычислителя разностной мощности несигнального тона 25 связан с первым входом блока 29 накопления и усреднения, второй выход вычислителя 25 соединен с первым входом коммутатора 14, второй вход коммутатора 14 подключен к пятому выходу БУ 16 и второму входу блока ДПФ 15, третий вход коммутатора 14 связан с первым выходом блока ДПФ 15, первый вход блока 15 ДПФ соединен с пятыми входами блока 28 формирования начального адреса при тестировании символьной синхронизации и блока 29 накопления и усреднения, первым входом блока 26 задания интервала ортогональности и третьим выходом блока 32 определения оптимальных положений частотной и символьной синхронизации, второй выход блока ДПФ 15 подключен к первому входу блока 22 вычисления аргумента и поворота фазы, третий выход блока ДПФ 15 соединен с четвертым входом блока 33 вычисления разностной мощности и усреднения, второй вход блока 22 вычисления аргумента и поворота фазы связан с выходом блока 30 вычисления среднего набега фазы, выход блока 22 вычисления аргумента и поворота фазы подключен к первому входу блока 20 вычислителей информативного приращения фазы, второй вход блока 26 задания интервала ортогональности соединен с третьим выходом БОЧ 10, вторыми входами блока 28 формирования начального адреса при тестировании символьной синхронизации, блока 21 оценки значений символов и эталонной фазы и пятым входом блока 33 преобразования частоты, выход блока 26 задания интервала ортогональности связан со вторыми входами коммутаторов 17, 18 и 19, вход формирователя 27 отсчетов несущих со смещенными частотами подключен к выходу реверсивного счетчика 34 и второму входу блока 31 цифровых синтезаторов частот, первый и второй выходы формирователя отсчетов несущих со смещенными частотами 27 соединены с первыми входами соответственно коммутаторов 17 и 18, четвертый вход блока 28 формирования начального адреса при тестировании символьной синхронизации связан с третьим выходом блока управления 16; шестой вход блока 29 накопления и усреднения подключен ко второму выходу блока 32 определения оптимальных положений частотной и символьной синхронизации; первый и второй выходы блока 29 усреднения соединены соответственно с первым и третьим входами блока 32 определения оптимальных положений частотной и символьной синхронизации; первый вход блока 30 вычисления среднего набега фазы связан с третьим выходом блока 31 оценки значений символов и эталонной фазы, второй вход блока 30 вычисления среднего набега фазы подключен к выходу блока 20 вычислителей информативного приращения фазы, соединенному с первым входом блока 21 оценки значений символов и эталонной фазы, выходы коммутаторов 17 и 18 связаны соответственно с третьим и вторым входами блока 33 вычисления разностной мощности и усреднения, второй вход блока 20 вычислителей информативного приращения фазы соединен со вторым выходом блока 26 оценки значений символов и эталонной фазы, первый выход которого является выходом модема, выход коммутатора 19 связан с первым входом блока 33 вычисления разностной мощности и усреднения, первый и второй выходы блока 33 вычисления разностной мощности и усреднения подключены соответственно к последовательным входам сложения 3 и вычитания 4 реверсивного счетчика 34, первый и второй входы параллельной записи кода которого соединены соответственно с первым и четвертым выходами блока 32 определения оптимальных положений частотной и символьной синхронизации.

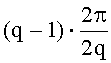

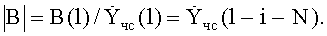

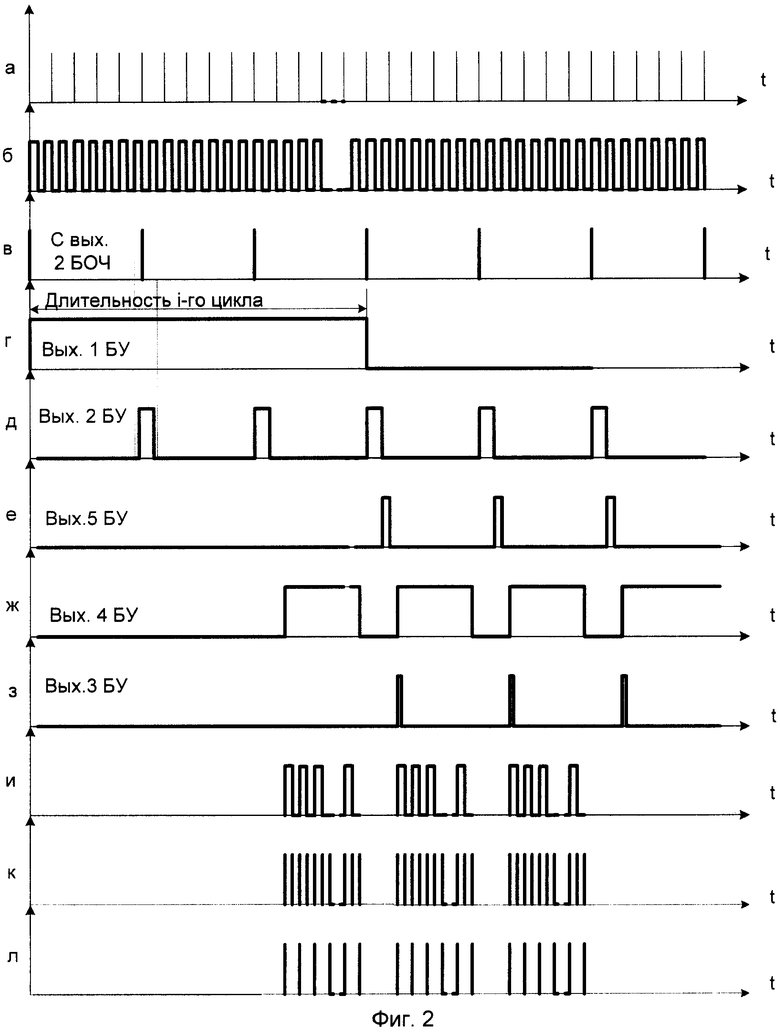

Работа устройства осуществляется следующим образом. Подлежащие передаче данные поступают на первый вход коммутатора 1, на второй вход которого подается цифровой сигнал с выхода генератора настроечной последовательности 9. На третий вход коммутатора 1 с первого выхода блока 22 управления подается сигнал, изображенный на строке в временной диаграммы, представленной на фиг.2. Как будет показано ниже, в процессе работы модема можно выделить 2 режима (цикла): режим вхождения в связь (1-й цикл) и режим передачи данных (2-й цикл). В течение 1-го цикла под воздействием единичного уровня на управляющем входе 3 к выходу коммутатора 1 подключается выходной сигнал генератора настроечной последовательности 9, а в течение 2-го цикла («0» на входе 3) - подлежащие передаче данные. Выходной сигнал коммутатора поступает на вход кодера 2. В модеме предполагается использование дифференциальной многократной фазовой модуляции с квадратурной реализацией модулятора и демодулятора [6], возможно применение квадратурно-амплитудной модуляции. В кодере 2 последовательность символов данных разбивается на группы по q бит (значение q выбирается из условия применения 2q - кратной модуляции). Каждой из возможных m-разрядных двоичных кодовых комбинаций ставится в соответствие определенный фазовый сдвиг, выбираемый из ряда 0,  ,…,

,…,  ,…,

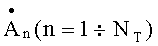

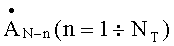

,…,  . При этом i-й фазовый сдвиг φi может быть представлен на плоскости с помощью единичного радиус-вектора, образующего угол φi с осью абсцисс. Координаты этого вектора: абсцисса a

сn (синфазная составляющая) и ордината a

кв n (квадратурная составляющая). Анализируя состав образованной q-битной группы из поступивших данных, кодер 3 выбирает соответствующие группе данных значения a

сn и a

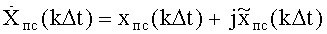

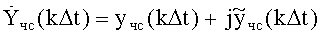

кв n и передает их в буферный накопитель 3. Отметим, что для дальнейшего описания работы схемы удобно ввести в рассмотрение комплексный сигнал:

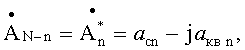

. При этом i-й фазовый сдвиг φi может быть представлен на плоскости с помощью единичного радиус-вектора, образующего угол φi с осью абсцисс. Координаты этого вектора: абсцисса a

сn (синфазная составляющая) и ордината a

кв n (квадратурная составляющая). Анализируя состав образованной q-битной группы из поступивших данных, кодер 3 выбирает соответствующие группе данных значения a

сn и a

кв n и передает их в буферный накопитель 3. Отметим, что для дальнейшего описания работы схемы удобно ввести в рассмотрение комплексный сигнал:

содержащий одновременно информацию и об a

сn и a

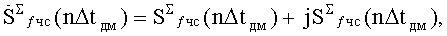

кв n; при этом мнимая единица j в данном случае выполняет роль метки, отличающей квадратурную составляющую от синфазной. В буферном накопителе 3 осуществляется накопление NT последовательно поступающих на его вход символов сигнала  , что необходимо для реализации параллельного способа передачи данных с использованием метода уплотнения с ортогонально-частотным разделением (OFDM - Orthogonal Frequency Division Multiplexing). Для обеспечения высокой скорости передачи данных число параллельных подканалов, а следовательно, и число поднесущих в спектре сигнала должно быть большим. Однако такую систему сложно реализовать по классической схеме с числом модуляторов, равным числу несущих. Вместе с тем существует возможность выполнить операцию модуляции во всех подканалах одновременно с гораздо меньшими реализационными затратами на основе эффективных методов цифровой обработки сигналов, а именно вычисляя ОДПФ с использованием алгоритма ОБПФ [7]. Если N/2 символов модулирующего сигнала

, что необходимо для реализации параллельного способа передачи данных с использованием метода уплотнения с ортогонально-частотным разделением (OFDM - Orthogonal Frequency Division Multiplexing). Для обеспечения высокой скорости передачи данных число параллельных подканалов, а следовательно, и число поднесущих в спектре сигнала должно быть большим. Однако такую систему сложно реализовать по классической схеме с числом модуляторов, равным числу несущих. Вместе с тем существует возможность выполнить операцию модуляции во всех подканалах одновременно с гораздо меньшими реализационными затратами на основе эффективных методов цифровой обработки сигналов, а именно вычисляя ОДПФ с использованием алгоритма ОБПФ [7]. Если N/2 символов модулирующего сигнала  дополнить N/2 комплексно сопряженными символами

дополнить N/2 комплексно сопряженными символами

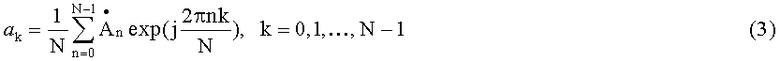

то после вычисления N-точечного ОДПФ получаем массив вещественных чисел:

Элементы массива {а k, k=0÷{N-1)} можно рассматривать как дискретные отчеты суммы выходов всех модуляторов параллельных каналов, взятые в моменты времени:

kΔt=kTopm/N,

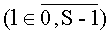

где Тopm - длительность интервала ортогональности. Отметим, что размер ОДПФ N равен числу дискретных отсчетов модулированного сигнала на интервале ортогональности. Эффективное вычисление суммы (3) возможно с помощью алгоритма БПФ, при этом желательно, чтобы размер ОДПФ N был целой степенью числа 2. При этом число NT накопленных в узле 2 символов сигнала  по разным соображениям [5, §3.3.2, 3.3.3] выбирается меньшим N/2, т.е.

по разным соображениям [5, §3.3.2, 3.3.3] выбирается меньшим N/2, т.е.

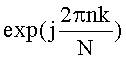

Это означает, что в передаваемом сигнале модема имеются неиспользуемые частоты. В блоке 23 производится дополнение NT накопленных блоком 3 символов до N/2 нулевыми значениями (соответствующими неиспользуемым частотам) и дополнение полученного массива еще N/2 символами  , вычисляемыми по правилу (2). Сформированный таким образом N-точечный массив комплексных данных подается на вход блока 4. В блоке 4 формируется совокупность значений фигурирующих в сумме (3) комплексных экспонент

, вычисляемыми по правилу (2). Сформированный таким образом N-точечный массив комплексных данных подается на вход блока 4. В блоке 4 формируется совокупность значений фигурирующих в сумме (3) комплексных экспонент  . Эти сигналы образуются аналогично комплексному символу

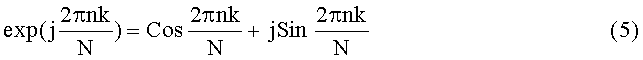

. Эти сигналы образуются аналогично комплексному символу  , задаваемому (1), в соответствии с формулой Эйлера:

, задаваемому (1), в соответствии с формулой Эйлера:

Реализация этой операции может быть выполнена таким образом: в запоминающем устройстве записаны N равноудаленных отсчетов периода гармонического колебания. Меняя адреса считываемых отсчетов в соответствии со значениями n и k, предписываемыми формулой (3) (или алгоритмом БПФ), и учитывая, что адреса отсчетов синусоиды задержаны на N/4 относительно адресов косинусоиды с той же фазой, получают значения колебаний, объединение которых в соответствии с (5) дает  С использованием этих значений и отсчетов

С использованием этих значений и отсчетов  входного сигнала в соответствии с выражением (3) (либо непосредственно по этой формуле либо с использованием алгоритма БПФ) в блоке 4 осуществляется вычисление ОДПФ. В результате по окончании вычисления ОДПФ на выходе блока 4 получается массив из N действительных чисел, равных отсчетам последовательности a(kΔt)=a

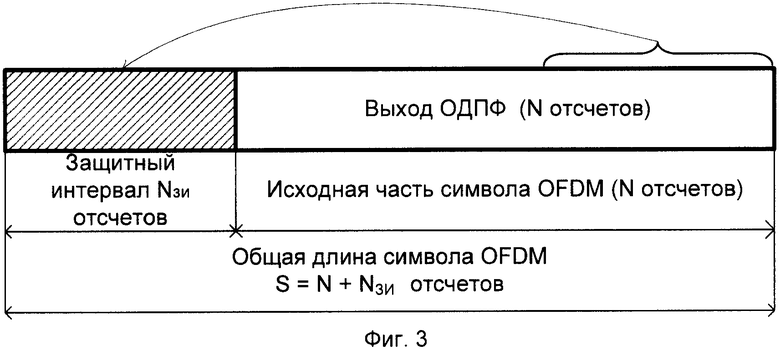

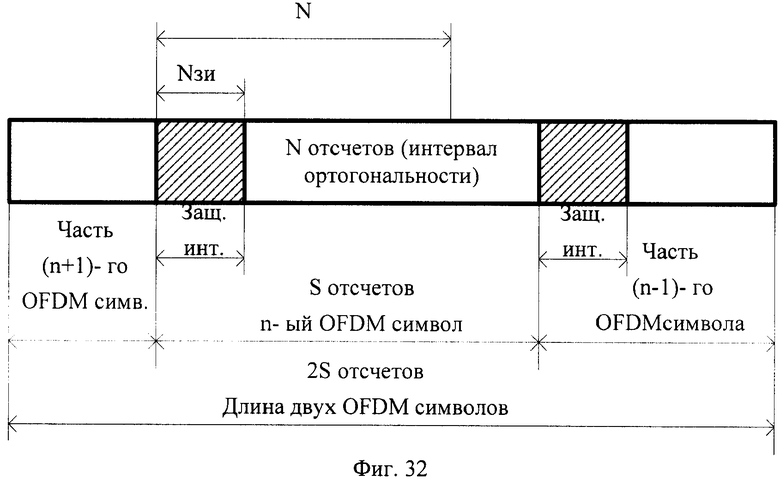

k, определяемой (3). В блоке 5 добавления защитного интервала длина этого массива увеличивается путем его циклического расширения до S=N+NЗИ отсчетов, где NЗИ - количество отсчетов, содержащихся в защитном интервале OFDM-символа длительностью

входного сигнала в соответствии с выражением (3) (либо непосредственно по этой формуле либо с использованием алгоритма БПФ) в блоке 4 осуществляется вычисление ОДПФ. В результате по окончании вычисления ОДПФ на выходе блока 4 получается массив из N действительных чисел, равных отсчетам последовательности a(kΔt)=a

k, определяемой (3). В блоке 5 добавления защитного интервала длина этого массива увеличивается путем его циклического расширения до S=N+NЗИ отсчетов, где NЗИ - количество отсчетов, содержащихся в защитном интервале OFDM-символа длительностью

где Δt - шаг дискретизации, определяемый соотношением (4).

Механизм формирования циклического расширения иллюстрируется фиг.3 и заключается в помещении копии NЗИ оконечных отсчетов выхода ОДПФ в начало OFDM-символа (формирование префикса).

Наличие защитного интервала необходимо для устранения межсимвольной интерференции, обусловленной многолучевостью, вследствие которой первые NЗИ отсчетов очередного OFDM-символа оказываются искаженными и при демодуляции просто отбрасываются. Восстановление принятой информации осуществляется по N отсчетам исходной части символа OFDM (фиг.3) с использованием для демодуляции N-точечного ДПФ.

Выходной массив блока 5 добавления защитного интервала, содержащий S отсчетов, поступает на первый вход преобразователя числового массива во временную последовательность 6, на второй вход которого с первого выхода блока опорных частот 8 поступают импульсы частоты дискретизации (строка а временной диаграммы, изображенной на фиг.2):

Выходной сигнал блока 6 поступает на формирующий фильтр (ФФ) 7, представляющий собой цифровой полосовой фильтр, который ограничивает спектр общего OFDM сигнала в соответствии с эффективной полосой пропускания телефонного канала. Выходной сигнал блока 7 поступает в блок согласования 8, где осуществляется цифроаналоговое преобразование и нормирование по уровню сформированного сигнала, после чего сигнал передается по каналу связи.

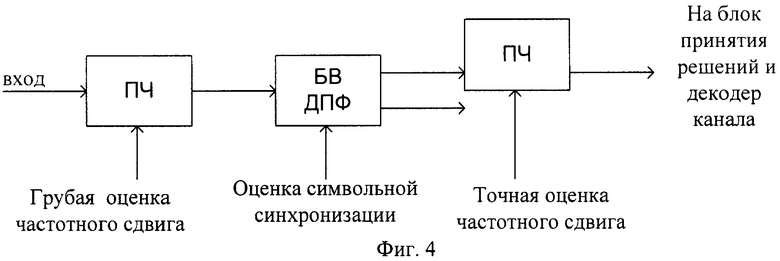

Прежде чем приступить к описанию работы структурной схемы приемника модема, изображенной на фиг.1, отметим, что задачей приемника является демодуляция принимаемого сигнала OFDM. Она может достаточно просто решена на основе вычисления дискретного преобразования Фурье (ДПФ) с использованием алгоритмов БПФ [7]. Однако при этом необходимо наличие совершенной символьной синхронизации и устранение частотного сдвига, вносимого радиоканалом.

Поскольку в KB модемах возможен значительный сдвиг частоты несущих передаваемого сигнала, который к тому же непрерывно изменяется во времени, оценка этого сдвига, необходимая для его устранения, обычно осуществляется в 2 этапа: вначале производиться грубая оценка, а затем точная. Таким образом, укрупненная структурная схема приемника модема имеет вид, показанный фиг.4 (в описании прототипа [5] она приведена на фиг.14). Обозначения узлов, приведенных фиг.4, расшифровываются следующим образом: ПЧ - преобразователь частоты, БВ - блок вычисления ДПФ.

В процессе работы системы синхронизации обычно выделяют 2 этапа: первоначальная оценка синхропараметров, имеющая место на этапе вхождения в связь, и слежение за изменяющимися значениями синхропараметров, производимое в процессе работы модема.

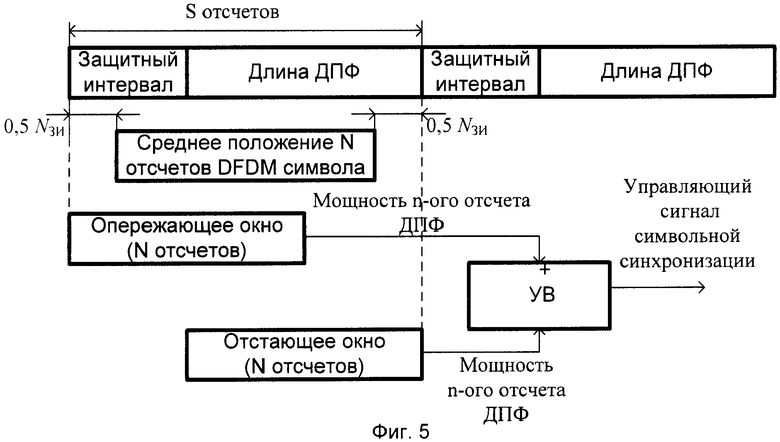

В устройстве-прототипе для установления символьной синхронизации используется метод «отстающего и опережающего окна», сущность которого иллюстрируется фиг.5.

На фиг.5 показано временное расположение двух последовательно поступивших OFDM-символов, содержащих по S отсчетов принимаемого сигнала (верхняя строка), а также соответствующее правильно установленной символьной синхронизации среднее положение блока из N отсчетов OFDM-символа и 2 его смещенных на NЗИ/2 отсчетов положения, причем первое смещено в сторону опережения (опережающее окно), а второе - отставания (отстающее окно).

Как отмечалось при описании передатчика в передаваемом сигнале имеются тоны, не используемые для передачи данных. Положим, что один из таких тонов находится в подканале с номером n.

Изображенная на фиг.5 ситуация характеризуется тем, что все отсчеты опережающего и отстающего окон принадлежат одному и тому же OFDM символу. При этом мощность n-го отсчета ДПФ, вычисленного по N отсчетам входного сигнала, входящим в опережающее окно, будет равна мощности n-го отсчета ДПФ, вычисленного по N отсчетам, принадлежащим отстающему окну. В итоге выходной сигнал узла вычитания УВ на фиг.5 будет равен нулю, что и говорит о наличии установленной символьной синхронизации. При нарушенной символьной синхронизации, отсчеты одного из окон выйдут за пределы одного OFDM-символа, баланс мощностей неиспользуемых отсчетов ДПФ, вычисленных на основе отстающего и опережающего окон, будет нарушен, и выходной сигнал узла вычитания будет отличен от нуля. Таким образом, по сигналу на выходе УВ можно судить о наличии символьной синхронизации.

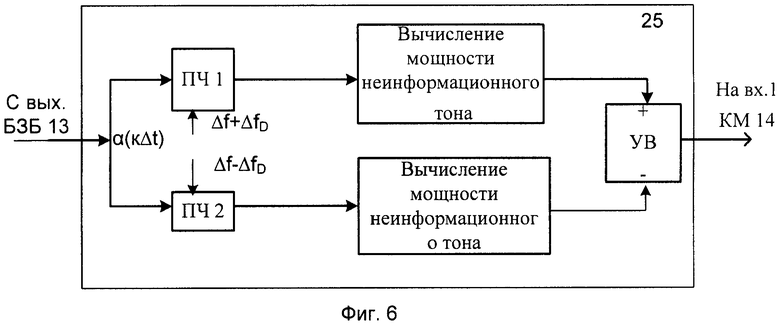

Грубая оценка частотного сдвига в прототипе осуществляется методом, похожим на вышеописанный метод «опережающего» и «отстающего» окна, но реализуемым в частотной области. Идея метода иллюстрируется блок-схемой, представленной на фиг.6.

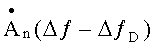

Эта схема включает в себя 2 преобразователя частоты ПЧ1 и ПЧ2, осуществляющих перенос спектра входного сигнала на частоты соответственно Δƒ+ΔƒD и Δƒ-ΔƒD, где Δƒ - значение тестируемой величины частотной расстройки, а ΔƒD - девиация частотной расстройки, необходимая для реализации данного метода (в работе [5] рекомендуется выбирать ΔƒD=0,1ΔFOFDM, где ΔFOFDM - ширина полосы пропускания одного подканала при OFDM передаче).

Вычислению мощности, например, выбранного для установления синхронизации, n-го неинформационного отсчета ДПФ должно предшествовать его выделение, осуществляемое путем вычисления n-го отсчета ДПФ входного сигнала.

При нулевой частотной расстройке, мощности, вычисленные в нижней и верхней ветвях схемы, являются одинаковыми и на выходе узла вычитания УВ присутствует нулевой сигнал, при наличии ухода частоты баланс мощностей нарушается и знак выходного сигнала УВ указывает знак частотной расстройки.

Идея выполнения точной оценки частотного сдвига основана на использовании решений о значении символа, переданного по i-му подканалу, и будет подробнее пояснена при описании реализации устройства-прототипа.

Необходимо отметить, что рассмотренный метод посимвольной синхронизации предполагает, что вносимый каналом частотный сдвиг спектра принимаемого сигнала полностью устранен. Аналогично иллюстрируемый на фиг.6 метод оценки частотного сдвига является корректным лишь при наличии установленной посимвольной синхронизации.

Вместе с тем, на этапе вхождения в связь оба названных условия не выполняются. В этой ситуации в прототипе реализуется алгоритм совместного оценивания посимвольной синхронизации и частотного сдвига, основанный на Nуср-кратном тестировании всех возможных сочетаний положений символьной синхронизации и значений частотного сдвига, усреднении и запоминании результатов и последующем отыскании оптимальных положений синхропараметров как координат ячейки таблицы с минимальным значением усредненного результата тестирования.

Рассмотрим далее, как все изложенное реализуется в схеме прототипа, представленной на фиг.1.

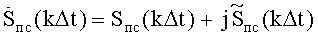

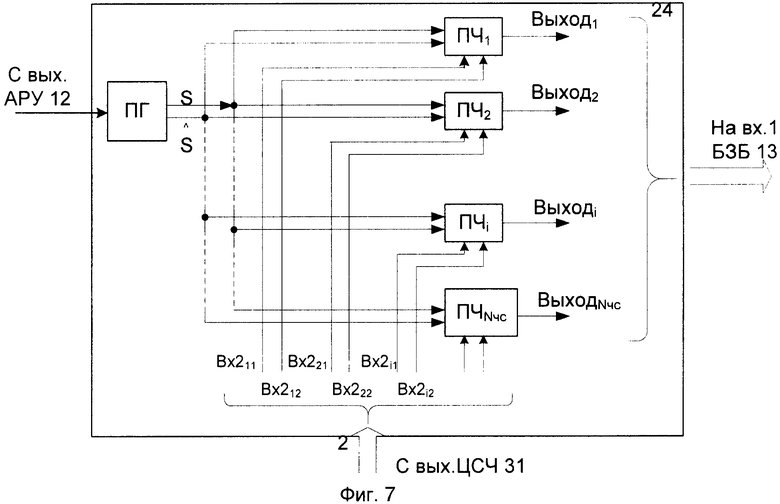

Сигнал, поступающий из канала связи, подается на первый вход входного блока 11, на второй вход которого с выхода БОЧ 10 подаются тактирующие импульсы, следующие с частотой дискретизации ƒd (строка а временной диаграммы фиг.2). В входном блоке 11 осуществляется фильтрация и аналого-цифровое преобразование. Далее отсчеты цифрового сигнала поступают на вход блока 12 АРУ, который нормализует уровень принимаемого сигнала. После этого отсчеты принятого цифрового сигнала s(kΔt) подаются на первый вход блока преобразователей частоты 24. Структурная схема блока 24 показана на фиг.7. Она представляет собой последовательное соединение преобразователя Гильберта ПГ и набора из Nчс параллельно включенных идентичных по построению преобразователей частоты ПЧ1, ПЧ2,…, ПЧNчс, где Nчc - число тестируемых на этапе вхождения в связь значений оценки частотного сдвига, вносимого каналом.

Необходимость параллельного включения такого большого числа преобразователей частоты обусловлена тем, что ввиду достаточно быстрого изменения во времени параметров радиоканала выбранный в прототипе алгоритм совместного оценивания посимвольной синхронизации и частотного сдвига, основанный на переборе всех возможных комбинаций и последующем усреднении, имеет практический смысл лишь в том случае, когда оценка всех тестируемых значений частотного сдвига выполняется одновременно. При этом в течение одной посылки OFDM символа появится возможность (при достаточном быстродействии выбранной элементной базы) оценки методом «отстающего» и «опережающего» окна всех Nпс тестируемых положений посимвольной синхронизации, и общее время вхождения в синхронизм будет определяться лишь числом Nуcp OFDM-посылок, на которых производится усреднение результатов тестирования. Попытка реализовать данный алгоритм путем последовательного тестирования разных значений частотного сдвига сделает данную процедуру бессмысленной, поскольку за время ее выполнения параметры канала изменятся столь существенным образом, что результат оценивания окажется недостоверным.

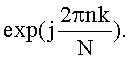

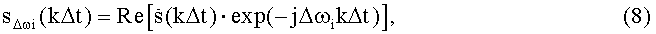

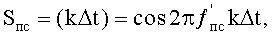

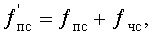

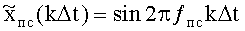

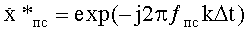

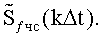

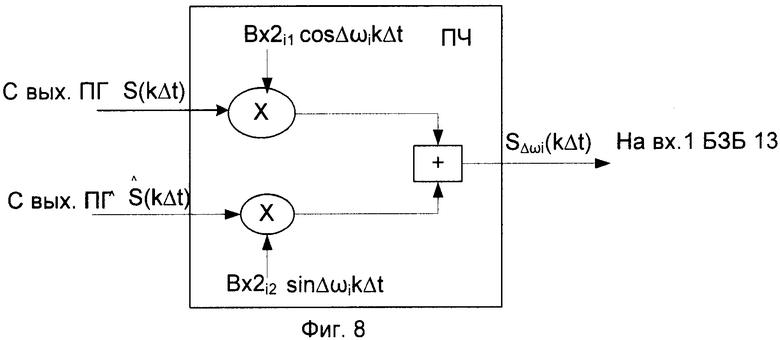

Схема конкретной реализации i-го преобразователя частоты ПЧi представлена на фиг.8. Она включает в себя два перемножителя и узел сложения. Выходной сигнал ПЧi sΔωi (kΔt) описывается выражением:

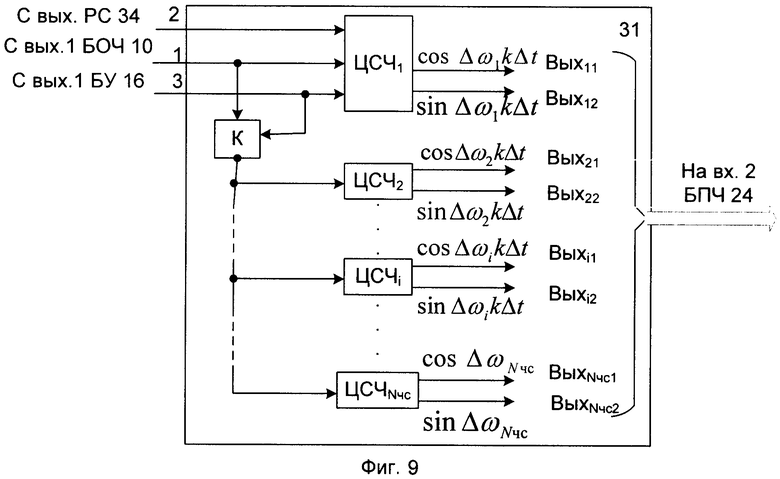

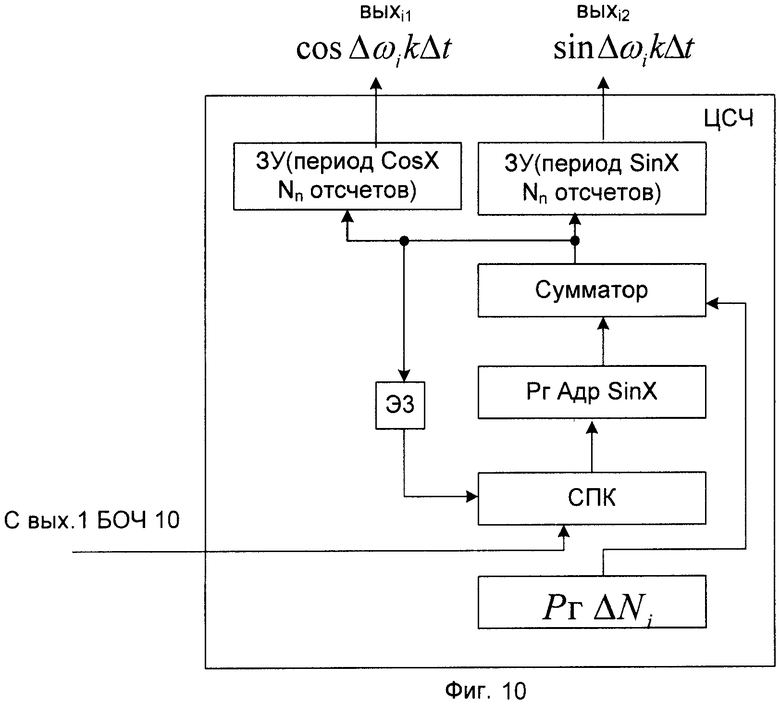

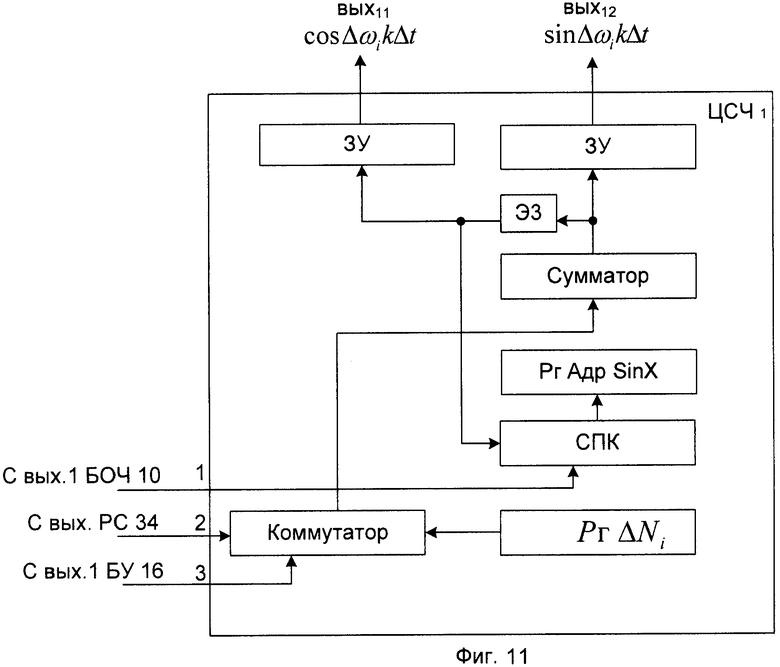

где  Сигналы cos ΔωikΔt и sin ΔωikΔt, поступающие на вторые входы перемножителей схемы фиг.8, подаются на входы блока 24 с соответствующих выходов блока 31 цифровых синтезаторов частот. Структурная схема блока 31 представлена на фиг.9 и включает в себя ключ K и Nчс цифровых синтезаторов частоты ЦСЧ1, ЦСЧ2,…, ЦСЧNчс. Отметим, что схема ЦСЧ1 несколько отличается от схем остальных ЦСЧi, i≠1, поэтому на фиг.10 отдельно изображена структура ЦСЧi, i≠1, а на фиг.11 - ЦСЧ1.

Сигналы cos ΔωikΔt и sin ΔωikΔt, поступающие на вторые входы перемножителей схемы фиг.8, подаются на входы блока 24 с соответствующих выходов блока 31 цифровых синтезаторов частот. Структурная схема блока 31 представлена на фиг.9 и включает в себя ключ K и Nчс цифровых синтезаторов частоты ЦСЧ1, ЦСЧ2,…, ЦСЧNчс. Отметим, что схема ЦСЧ1 несколько отличается от схем остальных ЦСЧi, i≠1, поэтому на фиг.10 отдельно изображена структура ЦСЧi, i≠1, а на фиг.11 - ЦСЧ1.

Как уже отмечалось, в процессе работы модема можно выделить 2 режима: режим вхождения в связь, в котором осуществляется первоначальная оценка синхропараметров и режим работы, в котором осуществляется прием передаваемых данных и необходимое для этого отслеживание изменений синхропараметров (положения посимвольной синхронизации и частотного сдвига), обусловленных изменением во времени параметров канала.

В режиме вхождения в связь по сигналу с первого выхода блока управления 22, поступающему на третий вход блока 31, открывается ключ К в схеме фиг.9, и импульсы с частотой дискретизации ƒd, подаваемые на первый вход блока 31 с первого выхода блока опорных частот 10, поступают на входы всех ЦСЧi, i=1÷Nчс. Функциональная схема одного узла ЦСЧi, i≠1 (фиг.10) включает в себя два ЗУ, в одном из которых записаны Nп отсчетов дискретизированного периода косинусоиды, а в другом - синусоиды. Адрес считываемого на k-м шаге дискретизации отсчета определяется кодом на выходе соответствующего сумматора, этот код представляет собой сумму по модулю Nп числа, зарегистрированного в регистре адреса (Рг Адр) и некоторого числа ΔNi, хранящегося в регистре Pг ΔNi, и определяющего частоту Δωi, считываемых с ЦСЧ; дискретизированных гармонических колебаний cos ΔωikΔt и sin ΔωikΔt. Значение ΔNi определяется из соотношения:

где Δƒi=Δωi/2π. Через элемент задержки ЭЗ (см. фиг.10) выходной код сумматора подается на вход схемы переписи кода (СПК), посредством которой с приходом на первый вход ЦСЧ 31 очередного импульса дискретизации переписывается в Рг Адр. Элемент задержки ЭЗ обеспечивает возможность считывания отсчетов ЦСЧ (до их изменения), подготовленных аналогичным образом на предыдущем шаге дискретизации, соответствующим ПЧi (см. фиг.7).

Отличие схемы ЦСЧ1, изображенной на фиг.11, от рассмотренной схемы заключается в том, что посредством коммутатора, управляемого поступающим на третий вход блока 31 сигналом с первого выхода блока управления 16, в течение первого режима работы модема к одному из входов сумматоров подключается выход регистра Рг ΔN1 (так же как и в схеме фиг, 10), а во втором режиме - выход реверсивного счетчика 34, связанный со вторым входом блока 31 синтезатора частот.

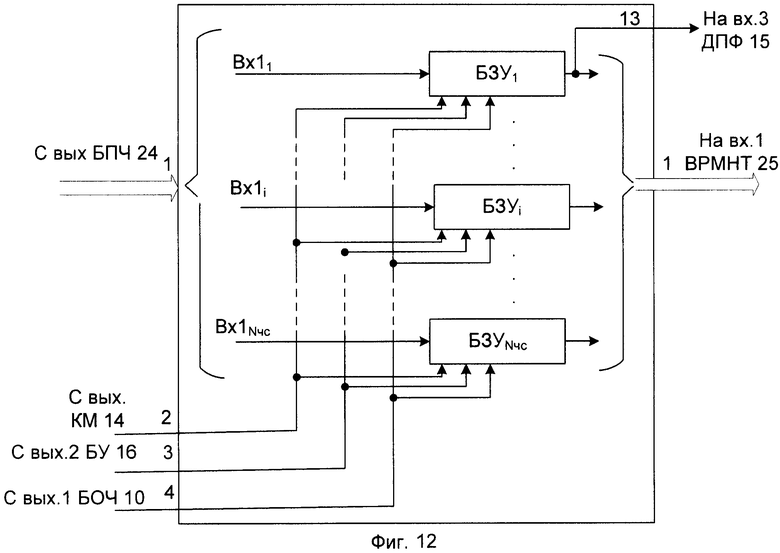

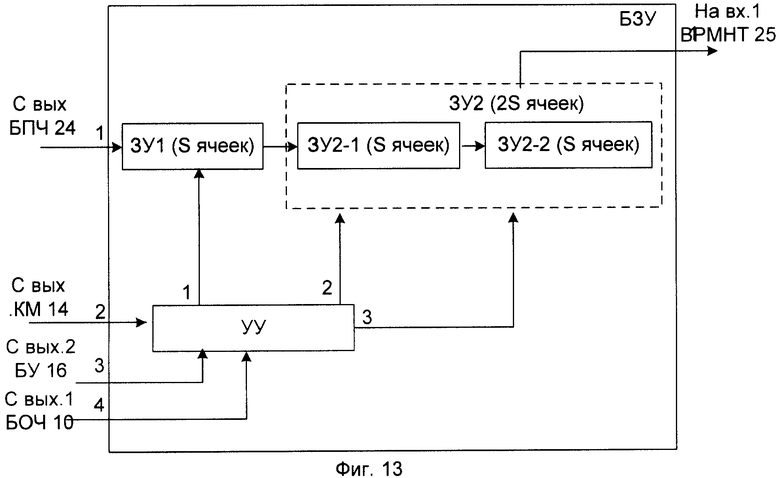

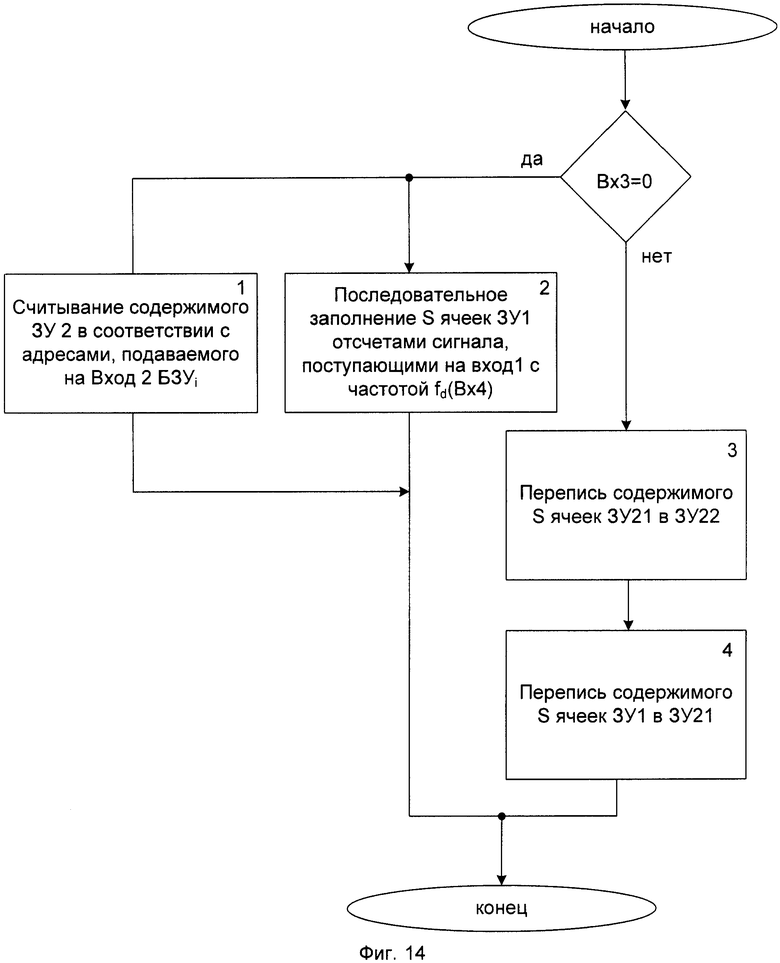

Таким образом, в первом режиме работы модема на Nчс выходах блока 31 формируются Nчс вариантов дискретизированного выходного сигнала с устраненным в разной степени влиянием оцениваемого частотного сдвига, вносимого радиоканалом. Эти сигналы поступают через блок 24 преобразователей частот на Nчс входов Вх1,…, ВхNчс буферного запоминающего блока 13 (все они обозначены как первый вход). Функциональная схема буферного запоминающего блока 13 изображена на фиг.12. Она включает в себя Nчc идентичных буферных запоминающих узлов БЗУi… Блок-схема узла БЗУi показана на фиг.13, а алгоритм его работы - на фиг.14. Узел БЗУi изображенный на фиг.13, состоит из ЗУ1, содержащего S ячеек памяти, и ЗУ2, включающего 2 S ячеек. Для описания алгоритма работы БЗУi удобно в составе ЗУ2 выделить ЗУ2-1, включающее первые S ячеек памяти с адресами 0÷(S-1) и ЗУ2-2, включающее оставшиеся S ячеек с адресами S÷(2S-1). Процессами записи и считывания информации в БЗУi управляет узел управления УУ БЗУi. Поскольку форма реализации описываемого модема и входящих в его состав блоков предполагает использование программируемого многофункционального средства, на фиг.14 представлен алгоритм функционирования блока БЗУi, из которого становятся ясными функции, выполняемые узлом УУ БЗУi. В результате анализа сигнала, поступающего на третий вход буферного запоминающего блока 13 (фиг.12, фиг.13) со второго выхода блока управления 16 фиг.1 (см. строку д временной диаграммы работы устройства, изображенной на фиг.2), УУ БЗУi фиг.13 обеспечивает выполнение действий, предписываемых либо блоками 1 и 2 алгоритма фиг.14 (эти процедуры выполняются параллельно во времени) либо блоками 3 и 4 алгоритма фиг.14, реализуемыми последовательно во времени. Как видно из временной диаграммы, при этом в течение почти всей длительности TS=1/ƒS OFDM-символа (строка в диаграммы фиг.2) осуществляется считывание информации, зафиксированной в ЗУ2 и необходимой для тестирования различных положений посимвольной синхронизации, выполняемого в соответствии с описанным выше алгоритмом «отстающего» и «опережающего» окна (блок 1 алгоритма), и последовательная во времени запись в ЗУ1 новых отсчетов сигнала с выхода блока 10 преобразования частот, поступающих с частотой дискретизации ƒd (блок 2 алгоритма). Последовательность тактирующих запись импульсов с частотой ƒd подается на второй вход буферного запоминающего блока 13 фиг.1.

Для реализации использованного в данном устройстве и изложенного выше метода синхронизации необходимо на этапе вхождения в связь (т.е. в 1-м режиме работы модема) S раз в течение одного OFDM-символа обеспечить считывание N отсчетов, поступивших на буферный запоминающий блок 13 с блока 24 преобразования частоты сигнала, при этом начальный адрес каждой партии из N отсчетов должен последовательно инкрементироваться. Аналогичная ситуация имеет место и во втором (рабочем) режиме функционирования модема, в котором осуществляется слежение за оптимальным положением посимвольной синхронизации. Отличие от 1-го режима здесь состоит лишь в том, что число тестируемых положений может быть уменьшено с S вариантов до ±Nгр вокруг номинального (определенного в 1 цикле и в процессе предыдущего слежения).

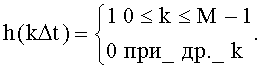

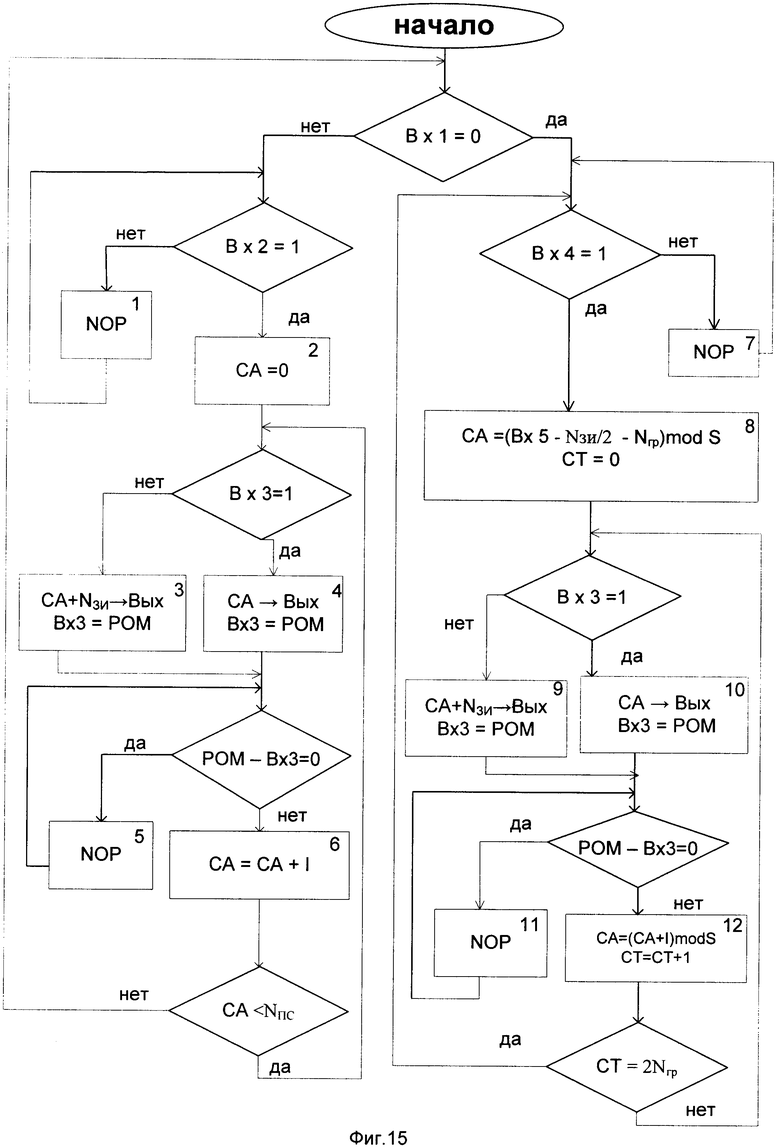

Задачу формирования начальных адресов считываемых партий отсчетов в прототипе выполняет блок 28 фиг.1 формирования начального адреса при тестировании символьной синхронизации, алгоритм работы которого представлен на фиг.15. Алгоритм запускается при включении модема. В алгоритме показано «начало» и отсутствует «конец», поскольку его выполнение прекращается лишь с выключением модема. На вход 1 блока 28 фиг.1 с первого выхода блока управления 16 подается сигнал, показанный на строке г временной диаграммы фиг.2, который равен 1 в течение длительности 1-го режима и 0 - в течение 2-го.

Таким образом, левая часть алгоритма фиг.15 иллюстрирует функционирование блока 28 формирования начального адреса при тестировании символьной синхронизации в режиме вхождения в связь, а правая - в рабочем режиме. На второй вход блока 28 с третьего выхода БОЧ 10 (фиг.1) подаются короткие единичные импульсы с частотой ƒS (частотой следования OFDM-символов), показанные на строке в временной диаграммы (фиг.2). Появление каждого импульса на втором входе блока 28 фиг.1 соответствует началу очередного цикла тестирования положения посимвольной синхронизации, осуществляемого в течение длительности OFDM-символа при положительном результате проверки условия Вх.2=1. При отрицательном результате этого анализа (Вх.2=0) с помощью блока 1 алгоритма (фиг.15) «NOP» или «нет операции» производится ожидание прихода очередного единичного импульса на втором входе блока 28. При этом в блоке 2 алгоритма фиг.15 обнуляется значение переменной СА (счетчик адреса), затем анализируется сигнал, поступающий на третий вход блока 28 с второго выхода БОЧ (строка б временной диаграммы фиг.2). Этот сигнал представляет собой последовательность двухуровневых прямоугольных импульсов типа меандр (то есть со скважностью равной 2). Частота следования этих импульсов ƒвх3 незначительно превышает ƒd:ƒвх3=1,3 ƒd, что позволяет за время, меньшее длительности OFDM-символа Тc=S/ƒd, выполнять S тестирований.

В зависимости от того, какой из полупериодов описанного сигнала присутствует в данный момент на третьем входе блока 28 фиг.1 (в одном из полупериодов Вх.3=0, в другом - Вх.3=1), выполняется блок 3 или 4 алгоритма фиг.15. В каждом из этих блоков на первый выход блока 28 фиг.1 выдается значение начального адреса для тестирования в соответствии с правилом, иллюстрируемым фиг.5. Кроме того, вспомогательной переменной РОМ в каждом из блоков 3, 4 алгоритма фиг.15 присваивается значение, равное значению сигнала на Вх3. Это необходимо для того, чтобы с помощью последующего условного перехода (РОМ-Вх3=0) обеспечить ожидание момента смены сигналом на Вх.3 своего значения и сохранить неизменным в течение полупериода сигнала Вх3 начальное значение адреса на выходе. Процедура ожидания реализуется с помощью блока 5 алгоритма фиг.15. Далее в алгоритме осуществляется инкрементирование переменной СА и производится проверка количества тестирований. Если оно меньше предусмотренного числа тестов на данной посылке OFDM-символа Nпс=S, то вновь анализируется состояние Вх.3 и цикл повторяется. По окончании тестирования на очередном OFDM-символе (СА=-Nпс), вновь осуществляется проверка состояния сигнала на Вх1. По окончании первого цикла начинается второй, на Вх1 появляется «0» и работает правая часть алгоритма фиг.15. Напомним, что во втором цикле задачей блока 28 фиг.1 является формирование начальных адресов кадров из N отсчетов, извлекаемых из блока 13 фиг.1 в процессе тестирования положений посимвольной синхронизации, осуществляемого в рамках слежения за изменением параметров радиоканала в рабочем режиме. При этом первоначально осуществляется анализ состояния четвертого входа блока 28 фиг.1, на который с третьего выхода БУ 16 подается сигнал, изображенный на строке з временной диаграммы фиг.2 и представляющий собой короткие единичные импульсы, соответствующие началам допустимого интервала тестирования положений посимвольной синхронизации в рабочем режиме (строка ж временной диаграммы, фиг.2). Этот интервал во 2-м режиме начинается спустя время Δt после прихода очередного импульса с частотой ƒS и заканчивается на Δt раньше прихода последующего импульса ƒS. Блок 7 алгоритма «NOP» (фиг.15) используется для ожидания прихода очередного единичного импульса на вход 4 блока 28 фиг.1. Далее работа правой части алгоритма фиг.15 осуществляется аналогично его левой части, с той лишь разницей, что в блоке 8 алгоритма переменной СА присваивается значение:

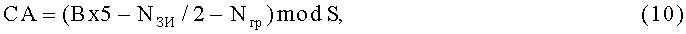

а для подсчета числа тестирований вводится дополнительная переменная СТ, инициализируемая в том же блоке 8 фиг.14 нулевым значением. На вход 5 блока 28 фиг.1 подается «оптимальный» начальный адрес, используемый для демодуляции кадра из N отсчетов ЗУ2 буферного запоминающего блока 13 фиг.1, который был определен в течение 1-го режима и предшествовавших шагов коррекции во 2-м режиме. В соответствии с правилом тестирования, иллюстрируемым фиг.5, для определения начального значения СА из него необходимо вычесть NЗИ/2, что и делается в блоке 8 алгоритма фиг.15. При слежении за оптимальным положением Nопт посимвольной синхронизации можно сузить диапазон тестирования по сравнению с режимом вхождения в связь, сохранив его в границах Nопт±Nгp. Поэтому начальное значения переменной СА вычисляется по формуле (10) (вычитание осуществляется по модулю S, что позволяет учесть случай, когда Nопт<Nгр). Очевидно, что при таком выборе начального значения СА для подсчета числа тестирований целесообразно ввести дополнительную переменную СТ.

В результате работы данного фрагмента алгоритма в течение временных интервалов, соответствующих единичным значениям сигнала на строке ж временной диаграммы фиг.2, на выходе блока 28 фиг.1 будут появляться начальные адреса кадров из N отсчетов, необходимых для тестирования положений посимвольной синхронизации в рабочем режиме.

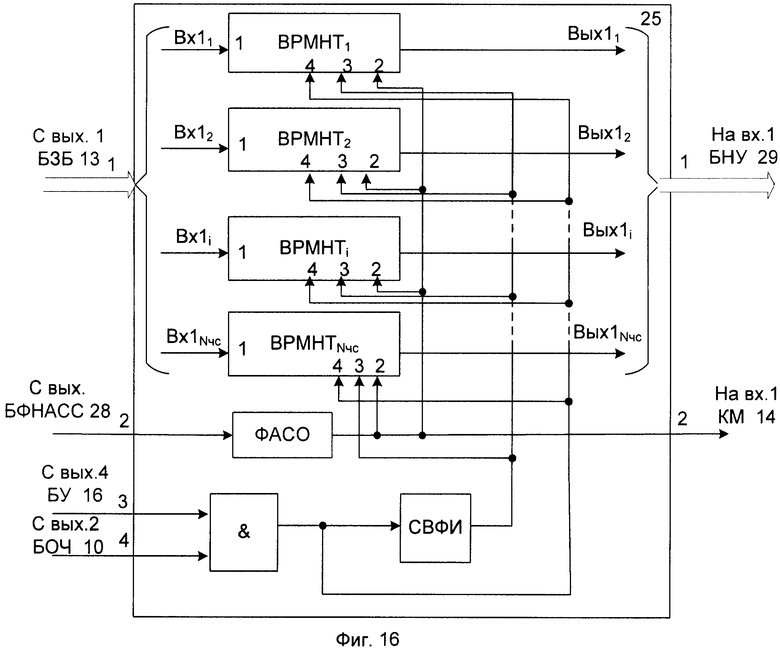

Формируемые на выходе блока 28 начальные адреса кадров из N отсчетов подаются на второй вход блока 25 вычислителей разностной мощности несигнального тона, структурная схема которого изображена на фиг.16. Схема включает Nчc параллельно включенных вычислителей разностной мощности несигнального тона ВРМНТi, первые входы которых, объединенные на схеме фиг.1 в один общий первый вход, связаны с выходами ЗУ2 соответствующих БЗУi буферного запоминающего блока, изображенного на фиг.12. Алгоритм функционирования отдельного блока ВРМНТi представлен на фиг.17. Очередной запуск этого алгоритма осуществляется импульсами, формируемыми изображенными на фиг.16 элементом И и схемой выделения фронта импульса СВФИ. Диаграммы сигналов на третьем и четвертом входах блока 25 (на входах схемы И фиг.16), выходе схемы И и выходе СВФИ представлены соответственно на строках ж, б, и и к временной диаграммы фиг.2.

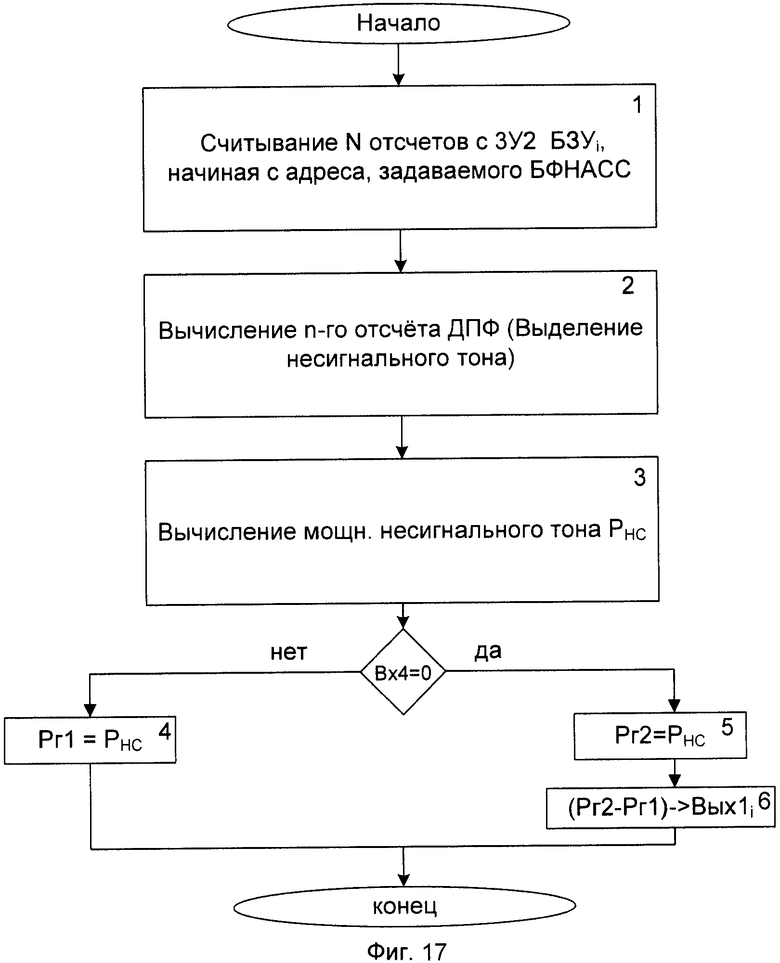

Первый блок алгоритма (фиг.17) предписывает считывание с ЗУ2 БЗУi фиг.13 кадров из N отсчетов, начальный адрес которых поступает на второй вход блока 25 с выхода блока 28 фиг.1. Адреса последовательно считываемых отсчетов формируются изображенным на схеме фиг.16 формирователем адресов считываемых отсчетов (ФАСО) и подаются как на второй вход блока 13 через коммутатор 14 фиг.1, так и на второй вход каждого ВРМНТi (фиг.16). Последнее необходимо для синхронизации ячеек внутренней памяти ВРМНТi, принимающих значения считываемых отсчетов, с адресацией считывания.

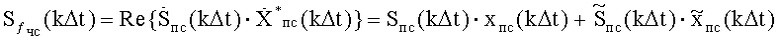

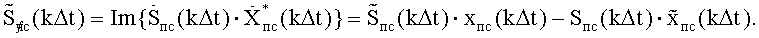

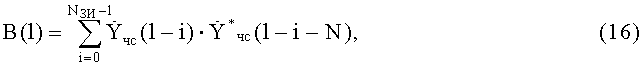

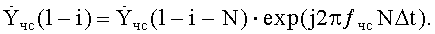

Во втором блоке алгоритма фиг.17 производится вычисление n-го отсчета ДПФ (что эквивалентно выделению n-го неиспользуемого для передачи тона), осуществляемое по N считанным отсчетам в соответствии с выражением:

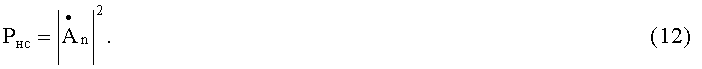

В третьем блоке определяется мощность несигнального тона Pнс, рассчитываемая как:

На четвертый вход каждого блока ВРМНТi фиг.16 подается сигнал с выхода схемы И, иллюстрируемой строкой и временной диаграммы фиг.2. При этом, как видно из сопоставления строк и и к временной диаграммы, каждому нечетному запуску на четвертом входе соответствует наличие 1, а четному - 0. Поэтому при каждом нечетном запуске ВРМНТi будет выполняться левая ветвь алгоритма по условию Вх.4=0 фиг.17, что соответствует фиксации в Рг1 фиг.17 мощности отсчета ДПФ, вычисленного на основе «опережающего» окна (см. фиг.5), а при каждом четном - правая ветвь, фиксирующая аналогичный результат для «отстающего» окна и определяющая модуль разностной мощности, значение которого и выдается на выход 1i ВРМНТi. На фиг.16 выходы 1i всех ВРМНТi условно объединяются в первый выход блока 25, который изображен в виде шины на схеме фиг.1.

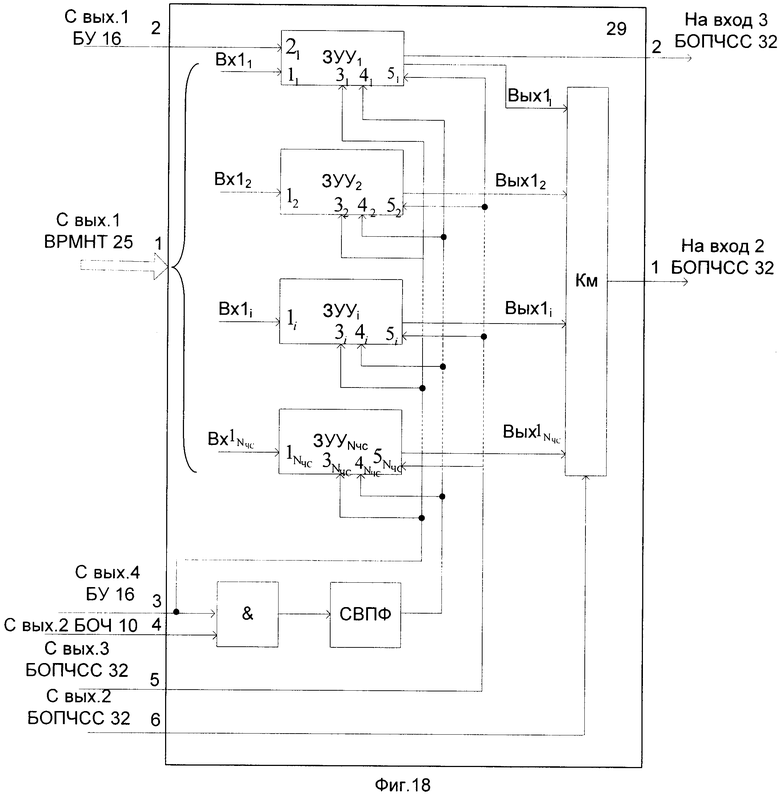

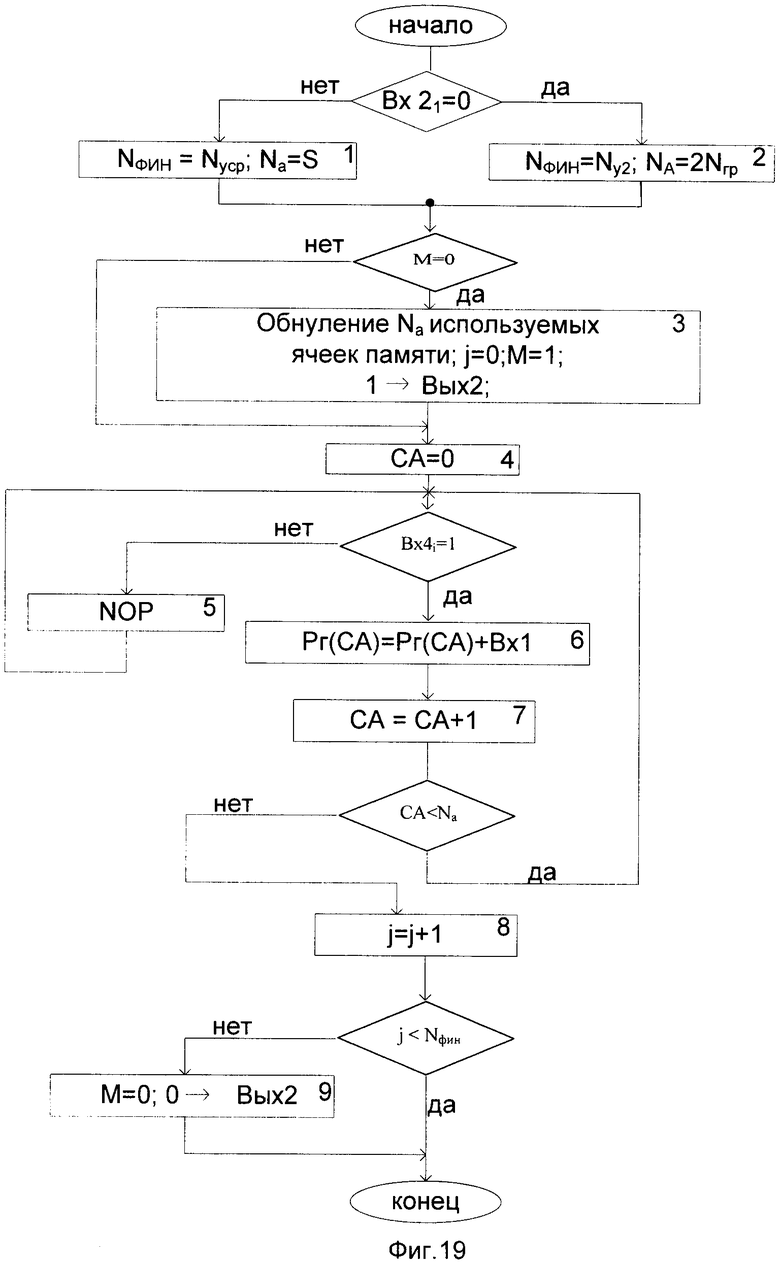

Выходной сигнал блока 25 фиг.1 поступает на вход блока накопления и усреднения 19, схема которого изображена на фиг.18. В состав блока 29 входят Nчc запоминающих и усредняющих узлов ЗУУi. Задачей каждого из этих узлов является запоминание и усреднение разностных мощностей, вычисленных в блоке 25 в первом цикле работы модема при Nчс разных значениях компенсируемого в блоке 24 (фиг.1) частотного сдвига, кроме того ЗУУi используется и во втором цикле работы модема для слежения за оптимальным положением посимвольной синхронизации. Алгоритм работы ЗУУi иллюстрируется фиг.19. Запуск данного алгоритма осуществляется передним фронтом сигнала, поступающего на третий вход блока 29 накопления и усреднения (входы 3i ЗУУi) и изображенного на строке ж временной диаграммы фиг.2.

Как уже отмечалось, представленный на фиг.19 алгоритм реализуется в ЗУУ1, которое отличается от остальных ЗУУi тем, что используется и в 1-м и во 2-м режимах работы модема. Поэтому на второй вход этого узла (у остальных ЗУУi данный вход отсутствует) подается сигнал с первого выхода блока управления 16, изображенный на строке г временной диаграммы фиг.2 и содержащий информацию о том, какой из циклов работы имеет место. Сразу после запуска алгоритма ЗУУ1 проверяется условие Bx21=0 и по результатам проверки устанавливаются значения переменных Nфин и Na, определяющих количество символов (посылок) OFDM сигнала, на которых осуществляется усреднение (Nфин) и число тестируемых положений посимвольной синхронизации (Na). В ЗУУi при i≠1 данная проверка отсутствует и всегда устанавливает присущие 1-му режиму значение Nфин=Nуcp, Na=S.

Далее осуществляется проверка условия М=0, где М - переменная, устанавливаемая в ноль либо по окончании цикла усреднения, либо при первоначальном включении модема (этот случай в алгоритме не показан). При выполнении условия М=0 осуществляется подготовка к новому циклу усреднения, заключающаяся в обнулении всех Na ячеек памяти ЗУУi; нулевой инициализации счетчика j усредняемых посылок, и установке в 1 значения М и сигнала на Вых2 (только для ЗУУ1). Далее в блоке 4 алгоритма фиг.19 обнуляется счетчик адреса ячеек памяти ЗУУi в которых хранятся усредняемые значения разностных мощностей. На входы 4i всех ЗУУi (i=1÷Nчс) подаются короткие единичные импульсы (строка л временной диаграммы фиг.2), формируемые конъюнктором и схемой выделения переднего фронта (СВПФ), изображенного в нижней части рисунка на фиг.18. На входы конъюнктора (третий и четвертый входы блока 29) поступают сигналы, изображенные на временной диаграмме (фиг.2, строки ж и б), при этом на выходе образуется сигнал, изображенный на строке и временной диаграммы. Отметим, что аналогичный сигнал имеет место и на выходе конъюнктора в схеме вычислителя разностной мощности несигнального тона (фиг.16). Однако в данном случае импульсы на выходе СВФИ (фиг.16) формируются не по каждому, а лишь по переднему фронту этого сигнала (строка л временной диаграммы фиг.2). В результате значения Вх4i=1 имеют место лишь в те моменты времени, когда на первом выходе блока 29 фиг.1 оказывается вычисленной разностная мощность «отстающего» и «опережающего» окон. Если условие Вх4i=1 не выполняется, с использованием блока 5 «NOP» («нет операции») в алгоритме фиг.19 реализуется ожидание прихода очередного импульса на Вх4i. Далее в блоке 6 алгоритма выполняется суммирование с накоплением в ячейке памяти с адресом СА (Рг(СА)), а затем в блоке 7 инкрементируется значение адреса СА. Выполнение операций блоков 6 и 7 алгоритма (фиг.19) циклически продолжается до тех пор, пока не будет изменено содержимое всех Nа ячеек памяти, что гарантируется проверкой условия CA<Na. Затем инкрементируется значение счетчика числа усреднений j. При достижении этой переменной значения Nфин (что говорит о том, что описываемый алгоритм уже запускался Nфин раз, т.е. цикл усреднения завершен), посредством блока 9 алгоритма устанавливаются значения М=0 и Вых2=0.

Сигналы с пятого и шестого входов (фиг.18), поступающие соответственно на входы 5i ЗУУi и на управляющий (нижний) вход коммутатора КМ (см. фиг.18), выдаются по окончании описанного цикла работы ЗУУi блоком 32 (фиг.1) и необходимы для подключения к первому выходу блока 29 определенных ячеек памяти (фиг.18).

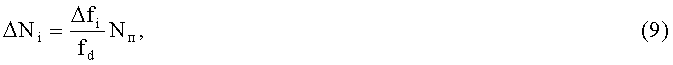

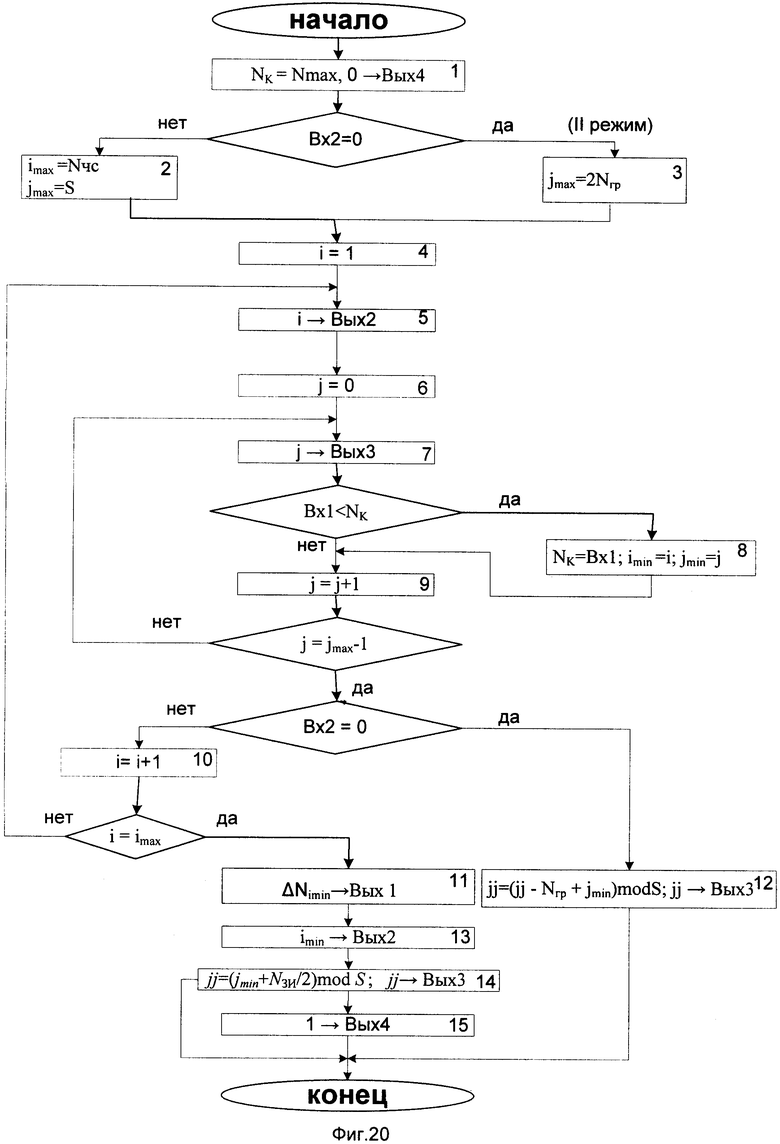

Наличие на втором выходе блока 29 накопления и усреднения нулевого сигнала говорит о том, что в ячейках этого блока зафиксирована информация, анализ которой позволит сделать вывод об оптимальных значении частотного сдвига и положении посимвольной синхронизации. Этот сигнал поступает на третий вход блока 32 определения оптимальных положений частотной и символьной синхронизации, алгоритм работы которого представлен на фиг.20, и запускает этот алгоритм. Задачей блока 32 является определение адреса ячейки памяти в блоке 29 с минимальным значением усредненной разностной мощности. По этому адресу в 1-м режиме устанавливаются оптимальные значения корректирующего частотного сдвига (по номеру i ЗУУi в блоке 29, которому принадлежит найденная ячейка) и положение посимвольной синхронизации (по номеру этой ячейки в ЗУУi). Во втором режиме, когда используется лишь ЗУУ1, определяется лишь адрес ячейки с минимальным содержимым в этом блоке, по которому корректируется положение посимвольной синхронизации. В блоке 1 алгоритма (фиг.20) контрольной переменной NK присваивается значение Nмах, заведомо большее максимально ожидаемого значения усредненной разностной мощности, кроме того, устанавливается 0 на выходе 4 блока 32 фиг.1. Затем анализируется состояние второго входа блока 32, на который с первого выхода БУ 16 подается сигнал, определяющий длительность 1-го режима (строка г временной диаграммы на фиг.2). В 1-м цикле (левое ветвление) в блоке 2 алгоритма (фиг.20) определяются значения переменных imax=Nчс и jmax=S, определяющих диапазон поиска ячейки с минимальным содержимым, а во 2-м цикле (правое ветвление), когда используется только первое ЗУУ1, в блоке 3 принимается jmax=2 Nгp<S, так как в режиме слежения границы поиска должны быть меньше, чем в режиме вхождения в связь. Затем в блоке 4 инициализируется единицей (так как нумерация ЗУУi в блоке 29 начинается с i=1) значение i. В блоке 5 алгоритма (фиг.20) на второй выход блока 32 фиг.1 подается значение i, которое, поступая на шестой вход блока 29, посредством коммутатора КМ (см. фиг.18) подключает к первому входу блока 32 выход ЗУУi. Далее в блоке 6 алгоритма инициализируется нулем (так как адресация ячееек памяти ЗУУi в блоке 29 начинается j=0) переменная j, а затем (блок 7 алгоритма) значение передается на третий выход блока 32 фиг.1. Поскольку третий выход блока 32 соединен через пятый вход блока 29 со входом адресации 5i ЗУУi (см. фиг.18), значение j определяет адрес ячейки памяти ЗУУi, подключаемой к первому входу блока 32. Таким образом, по окончании выполнения операции, предписываемой блоком 7 алгоритма (фиг.20), к первому входу блока 24 фиг.1 оказывается подключенным содержимое j-й ячейки памяти i-го ЗУУi. Далее осуществляется сравнение числа на первом входе (Вх1) с контрольной переменной NK, при Вх1<NK в блоке 8 алгоритма (фиг.20) переменной NK присваивается новое значение NK=Вх1, и переменными imin и jmin фиксируются значения i и j, при которых это событие имело место. Затем в блоке 9 алгоритма инкрементируется значение j, проверяется условие незавершенности цикла по j (j=jmax-1) и в 1-м режиме работы модема (Вх2≠0) аналогичные процедуры производятся с переменной i (блок 10 и проверка условия i=imax). Так реализуется алгоритм поиска ячейки памяти блока 29 фиг.1 с минимальным значением средней разностной мощности. По окончании процедуры поиска в блоках 11, 13 и 14 алгоритма (фиг.20) в 1-м режиме работы модема на первый, второй и третий выходы блока 32 фиг.1 соответственно выдаются значения ΔNi min (определяемое по формуле (9) при i=imin и соответствующее наилучшему компенсирующему частотному сдвигу), imin (определяющее наилучший компенсирующий частотный сдвиг), и вычисленное через jmin значение jj (определяющее начальный адрес Nна в ЗУ2 блока 13 среднего положения кадра из N отсчетов (см. фиг.5), соответствующий оптимальной посимвольной синхронизации). Затем в блоке 15 алгоритма (фиг.20) на четвертом выходе блока 32 (фиг.1) устанавливается 1. Это говорит о том, что определение ΔNmin (блок 11 алгоритма) завершено и значение, присутствующее на первом выходе, может быть переписано в блок 34 (фиг.1), что осуществляется по положительному фронту сигнала, поступающего на второй вход реверсивного счетчика с четвертого вывода блока 32. Значение ΔNmin на первый вход реверсивного счетчика подается с первого выхода блока 32 фиг.1. Во втором режиме (режиме слежения) с третьего выхода блока 32 фиг.1 передается определенный через jmin в блоке 12 алгоритма начальный адрес jj, соответствующий оптимальной посимвольной синхронизации. (Записанная в блоке 12 формула позволяет пересчитать jmin, определенное в диапазоне 0÷2 Nгp., в вычисляемое на данном этапе работы алгоритма значение jj, соответствующее диапазону 0÷S-1).

Таким образом, посредством взаимодействия описанной совокупности блоков в прототипе решаются 2 задачи: первоначальная оценка синхропараметров на этапе вхождения в связь (1-й режим) и слежение за оптимальным положением посимвольной синхронизации в процессе работы модема (2-й режим). Как отмечалось выше, для правильной демодуляции принятых данных необходимо в процессе работы модема (2-й режим) также обеспечить слежение за величиной вносимого каналом частотного сдвига.

Данное слежение, реализуемое на основе метода, иллюстрируемого фиг.6, осуществляется с использованием блоков 26, 27, 17, 18, 19, 33 и 34 схемы, изображенной на фиг.1.

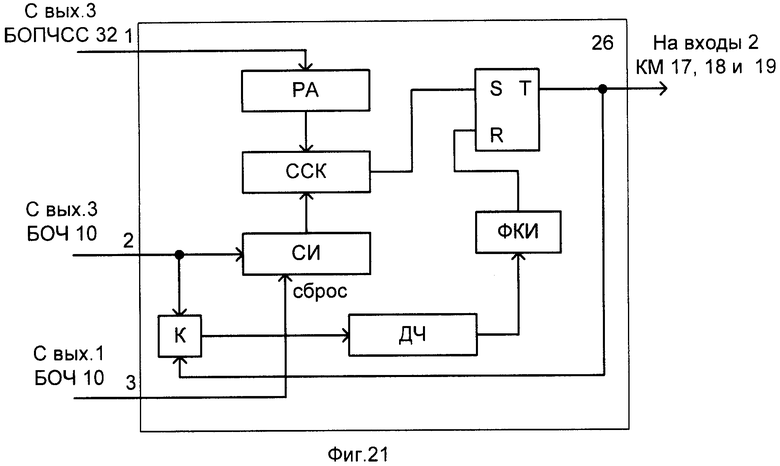

В блоке 26 задания интервала ортогональности с использованием поступающего на его первый вход определенного в блоке 32 начального адреса Nна, соответствующего оптимальной посимвольной синхронизации, осуществляется формирование временного интервала, в течение которого на вход приемника поступают отсчеты канального сигнала, сформированные в передатчике в течение интервала ортогональности.

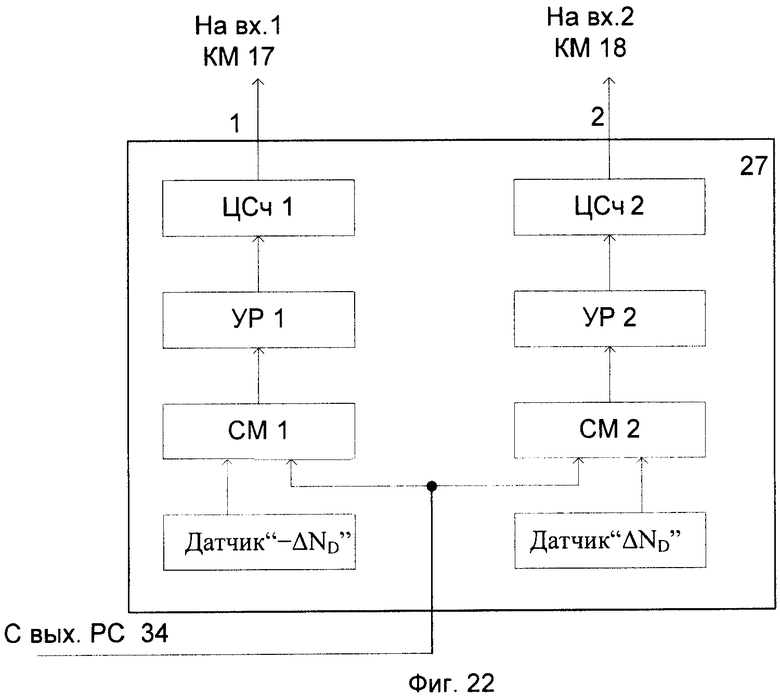

Функциональная схема блока 26 задания интервала ортогональности показана на фиг.21. Значение Nнa, поступающее на первый вход, записывается в регистр адреса РА. На второй вход с БОЧ 10 поступают прямоугольные импульсы с частотой ƒd (строка а временной диаграммы фиг.2), а на третий вход - импульсы с частотой ƒS (строка в временной диаграммы фиг.2), каждый из которых устанавливает счетчик импульсов СИ в ноль. Каждый раз в момент накопления в СИ числа, равного Nна, срабатывает схема совпадения кодов ССК и устанавливает выходной RS-триггер в единичное состояние. При этом открывается ключ К, и импульсы поступают на вход делителя частоты (ДЧ) с коэффициентом деления N (напомним, что N - число импульсов с частотой ƒd, укладывающихся в интервале ортогональности). При появлении положительного фронта на выходе ДЧ посредством формирователя короткого импульса RS-триггер переводится в состояние «0» и тем самым закрывается ключ К. Таким образом на выходе триггера формируется сигнал, соответствующий синхронизированному интервалу ортогональности. Этот сигнал поступает на вторые (управляющие) входы коммутаторов (КМ) 17, 18 и 19 (фиг.1). На первый вход КМ 19 с выхода АРУ 12 поступают отсчеты принимаемого сигнала, а на первые входы КМ 17 и КМ 18 - отчеты несущих со смещенными частотами с первого и второго выходов формирователя отсчетов несущих со смещенными частотами 27, функциональная схема которого показана на фиг.22.

Входящие в состав этой схемы цифровые синтезаторы частоты ЦСч1 и ЦСч2 имеют структуру, аналогичную показанной на фиг.9, с той лишь разницей, что роль Рг ΔNi на фиг.22 выполняют управляющие регистры УР1 и УР2. Коды NУР1 и NУР2, записанные в эти регистры, формируются с помощью сумматоров См1 и См2 и датчиков положительного и отрицательного приращений ±ΔND. При этом NУР1=ΔN-ΔND и NУР2=ΔN+ΔND, где ΔN - число, зафиксированное в реверсивном счетчике 29 (фиг.1) и соответствующее отслеженному в приемнике значению частотного сдвига, вносимого радиоканалом. В результате на первом и втором выходах блока 27 (выходах ЦСч1 и ЦСч2 фиг.22) появляются отсчеты опорных гармонических колебаний с частотами Δƒ±ΔƒD, необходимые для реализации алгоритма слежения за частотным сдвигом, иллюстрируемого фиг.6.

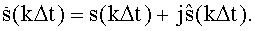

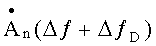

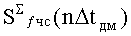

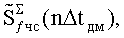

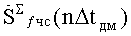

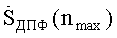

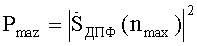

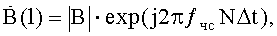

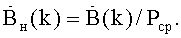

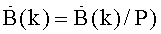

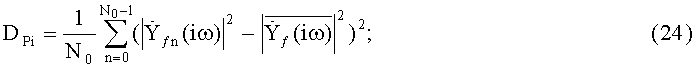

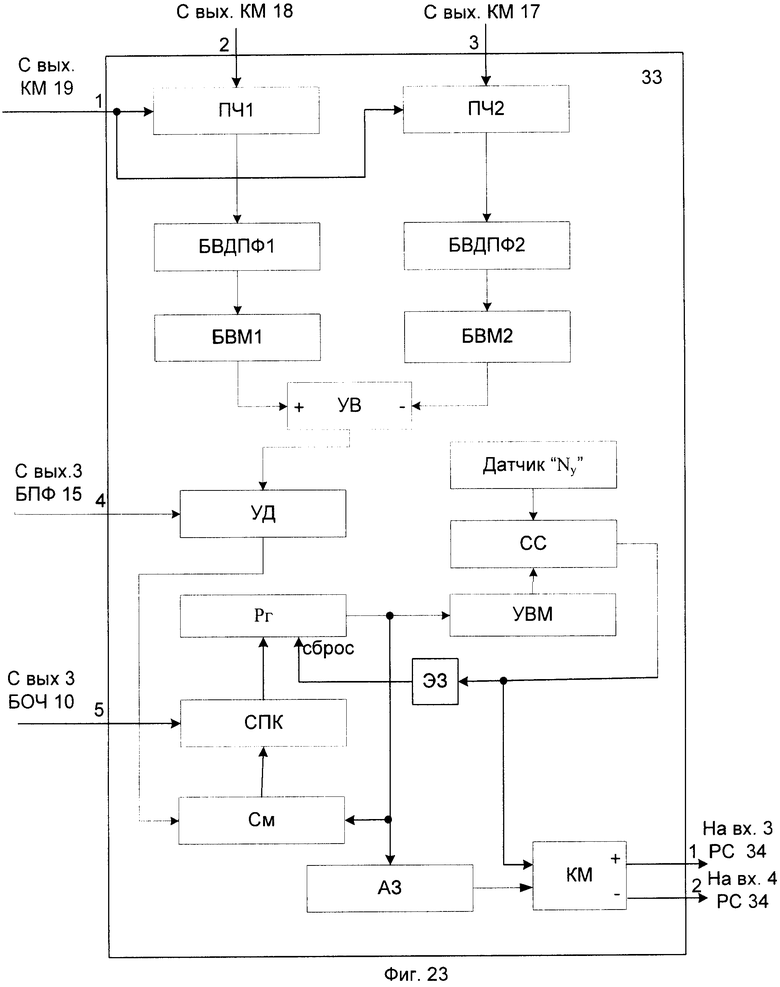

Выходные сигналы коммутаторов 19, 17 и 18 поступают на первый, второй и третий входы блока 33 вычисления разностной мощности и усреднения, функциональная схема которого представлена на фиг.23. В преобразователях частоты ПЧ1 и ПЧ2 осуществляется перенос спектра принимаемого сигнала на частоты Δƒ+ΔƒD и Δƒ-ΔƒD. В блоках БВДПФ1 и БВДПФ2 в соответствии с формулой (11) вычисляются n-е отсчеты ДПФ  и

и  этих сигналов (т.е. выделяется несигнальный тон). После этого в блоках вычисления мощности БВМ1 и БВМ2 по правилу (12) вычисляются мощности Р(Δƒ+ΔƒD) и Р(Δƒ-ΔƒD) смещенного по частоте несигнального тона, а в узле вычитания УВ в соответствии с алгоритмом, иллюстрируемым фиг.6, вычисляется разностная мощность РΔ=Р(Δƒ+ƒD)-Р(Δƒ-ƒD). В узле деления УД определяется нормированная разностная мощность РΔН=PΔ/Рcp, где Pcp - значение средней мощности сигнальных тонов, поступающих на четвертый вход блока 33 с блока 15 (фиг.1). В моменты времени, определяемые поступлением на пятый вход импульсов с третьего выхода БОЧ 10, следующих с частотой ƒS тактирования OFDM-символов, посредством схемы перелиси кода СПК в регистр Рг с выхода сумматора См записывается алгебраическая сумма числа, накопленного в Рг ранее, и поступающего с выхода УД значения PΔН. Таким образом, в регистре (Рг) осуществляется накопление суммарного значения разностной мощности (при включении модема Рг инициализируется нулем). В узле вычисления модуля (УВМ) определяется модуль числа, накопленного в Рг, который посредством схемы сравнения (СС) сравнивается с некоторым порогом Ny, выдаваемым датчиком «Ny» и задающим объем усреднения. При превышении выходным сигналом УВМ значения Ny СС выдает короткий импульс, поступающий на сигнальный вход коммутатора КМ. На управляющий вход этого узла поступает сигнал с анализатора знака (A3), определяющего знак числа, накопленного в Рг. В зависимости от уровня (ноль или единица) на выходе A3 коммутатор КМ подключает выходной импульс СС к первому выходу или второму выходу блока 33 фиг.1. Кроме того, через элемент задержки ЭЗ, обеспечивающий возможность четкого срабатывания A3 и КМ, выходной импульс СС сбрасывает регистр Рг в ноль. Сигналы с первого и второго выходов блока 33 поступают соответственно на третий и четвертый входы сложения и вычитания реверсивного счетчика 34 фиг.1 и корректируют тем самым хранящееся в нем значение ΔN1, определяющее частоту компенсируемого частотного сдвига радиоканала.

этих сигналов (т.е. выделяется несигнальный тон). После этого в блоках вычисления мощности БВМ1 и БВМ2 по правилу (12) вычисляются мощности Р(Δƒ+ΔƒD) и Р(Δƒ-ΔƒD) смещенного по частоте несигнального тона, а в узле вычитания УВ в соответствии с алгоритмом, иллюстрируемым фиг.6, вычисляется разностная мощность РΔ=Р(Δƒ+ƒD)-Р(Δƒ-ƒD). В узле деления УД определяется нормированная разностная мощность РΔН=PΔ/Рcp, где Pcp - значение средней мощности сигнальных тонов, поступающих на четвертый вход блока 33 с блока 15 (фиг.1). В моменты времени, определяемые поступлением на пятый вход импульсов с третьего выхода БОЧ 10, следующих с частотой ƒS тактирования OFDM-символов, посредством схемы перелиси кода СПК в регистр Рг с выхода сумматора См записывается алгебраическая сумма числа, накопленного в Рг ранее, и поступающего с выхода УД значения PΔН. Таким образом, в регистре (Рг) осуществляется накопление суммарного значения разностной мощности (при включении модема Рг инициализируется нулем). В узле вычисления модуля (УВМ) определяется модуль числа, накопленного в Рг, который посредством схемы сравнения (СС) сравнивается с некоторым порогом Ny, выдаваемым датчиком «Ny» и задающим объем усреднения. При превышении выходным сигналом УВМ значения Ny СС выдает короткий импульс, поступающий на сигнальный вход коммутатора КМ. На управляющий вход этого узла поступает сигнал с анализатора знака (A3), определяющего знак числа, накопленного в Рг. В зависимости от уровня (ноль или единица) на выходе A3 коммутатор КМ подключает выходной импульс СС к первому выходу или второму выходу блока 33 фиг.1. Кроме того, через элемент задержки ЭЗ, обеспечивающий возможность четкого срабатывания A3 и КМ, выходной импульс СС сбрасывает регистр Рг в ноль. Сигналы с первого и второго выходов блока 33 поступают соответственно на третий и четвертый входы сложения и вычитания реверсивного счетчика 34 фиг.1 и корректируют тем самым хранящееся в нем значение ΔN1, определяющее частоту компенсируемого частотного сдвига радиоканала.

Демодуляция и оценка значений принятых символов, а также точное слежение за величиной вносимого радиоканалом частотного сдвига осуществляются в прототипе в результате взаимодействия блоков 15, 20, 21, 22 и 30 (фиг.1). Как известно [7], одновременная демодуляция во всех параллельных подканалах в системе с OFDM может быть выполнена путем вычисления ДПФ от совокупности N отсчетов {a k}, поступивших в течение интервала ортогональности. При этом вычисление n-го отчета ДПФ осуществляется по формуле (11), а всего таких образом вычисляется N отсчетов (при n=0÷N-1). Каждый из этих отсчетов представляется комплексным числом, реальная и мнимая чисти которого содержат информацию о синфазной а сп и квадратурной a кв n составляющих, переданных по данному подканалу. Для уменьшения реализационных затрат процедура вычисления ДПФ выполняется с использованием алгоритма быстрого преобразования Фурье (БПФ) [7]. Описанные операции в устройстве-прототипе реализуются в блоке ДПФ 15. На первый вход блока ДПФ с третьего выхода блока 32 фиг.1 подается значение начального адреса отсчета, зафиксированного в ЗУ2 блока 13 буферной памяти, соответствующего оптимальной посимвольной синхронизации. На второй вход блока с пятого выхода блока управления 16 подается сигнал, задающий временной интервал работы блока ДПФ (интервал ортогональности) и изображенный на строке е временной диаграммы на фиг.2 в виде прямоугольного единичного импульса. С приходом уровня «I» на второй вход блок ДПФ осуществляет последовательную во времени выдачу на первый выход адресов N отсчетов, хранящихся в ЗУ2 блока 13. Эти адреса представляют собой результат последовательной инкрементации (т.е. увеличения на 1) значения начального адреса, поступившего на первый вход. Формируемые таким образом адреса с первого выхода блока 15 через коммутатор 14, управляемый сигналом с пятого выхода БУ 16, поступают на второй вход блока 13, вследствие чего на его втором выходе появляются (и подаются на вход 3 блока ДПФ 15) необходимые для демодуляции (то есть вычисления ДПФ) отсчеты принятого сигнала. Отметим, что связь второго выхода блока 13 с третьим входом блока 15 на фиг.1 показана тонкой, а не составной линей потому, что передача информации по этому соединению осуществляется лишь во втором цикле работы модема, когда к первому выходу блока 13 оказывается подключенным лишь выход одного БЗУ1 (см. фиг.12). При этом составная линия показывает соединение нескольких выходов одного блока с несколькими соответствующими входами другого блока (например, соединение первого выхода блока 13 с первым входом блока 25).

В блоке ДПФ 15 на основе считанных описанным образом N отсчетов принятого сигнала осуществляется вычисление ДПФ, производимое на основе алгоритма БПФ. Результаты вычисления ДПФ подаются на второй выход блока 15. Поскольку эти результаты представляют собой набор N комплексных чисел, второй выход блока 15 и ряд других аналогичных соединений на фиг.1 показаны составными линиями. Также в блоке ДПФ 15 по правилу (12) вычисляется мощность каждого сигнального тона, а затем определяется их среднее арифметическое значение, которое и представляет собой значение Pcp, подаваемое на третий выход блока ДПФ.

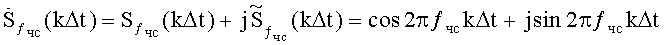

С второго выхода блока 15 комплексные значения отсчетов ДПФ, определяемые выражением (1), поступают на первый вход блока вычисления аргумента и поворота фазы БВАПФ 22. В этом блоке с каждым i-м отсчетом ДПФ  (выходом i-го подканала в системе с OFDM при приеме n-го OFDM символа), последовательно выполняются две следующие операции:

(выходом i-го подканала в системе с OFDM при приеме n-го OFDM символа), последовательно выполняются две следующие операции:

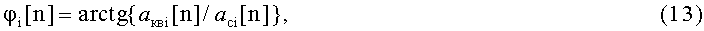

1) вычисляется его аргумент

2) определяется уточненное значение аргумента символа φоi[n], в котором с доступной данному устройству точностью скорректировано влияние неотслеживаемого описанной выше инерционной системой слежения за частотным сдвигом набега фазы, обусловленного быстрым допплеровским изменением частоты в радиоканале. Коррекция осуществляется в соответствии с выражением:

где Δφcp[n-1] - среднее по всем принимаемым OFDM символам значение «быстрого» набега фазы, вычисленное на (n-1)-м OFDM такте в блоке вычисления среднего набега фазы ВСНФ 30, подаваемое на второй вход блока вычисления аргумента и поворота фазы 22.

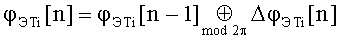

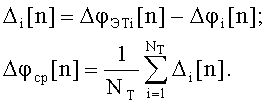

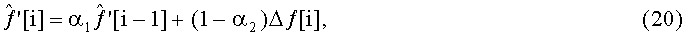

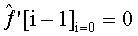

Величины φ0i[n], (i=1÷NT) являются выходным сигналом блока 22 фиг.1 и подаются на первый вход блока вычисления информативного приращения фазы БВИПФ 20. На второй вход этого блока со второго выхода блока оценки значений символов и эталонной фазы БОЗС 21 поступают вычисленные в этом блоке в предыдущем такте значения φЭТi[n-1], (i=1÷NT) эталонной фазы (т.е. фазы, определяемой целым числом использованных при кодировании в блоке 2 фазовых сдвигов, кратных 2π/2q, где q - кратность используемой фазовой модуляции). В блоке 20 фиг.1 оцениваются информативные приращения фазы Δφi[n] демодулированного сигнала в i-м подканале на n-м OFDM такте. Эти величины вычисляются как:

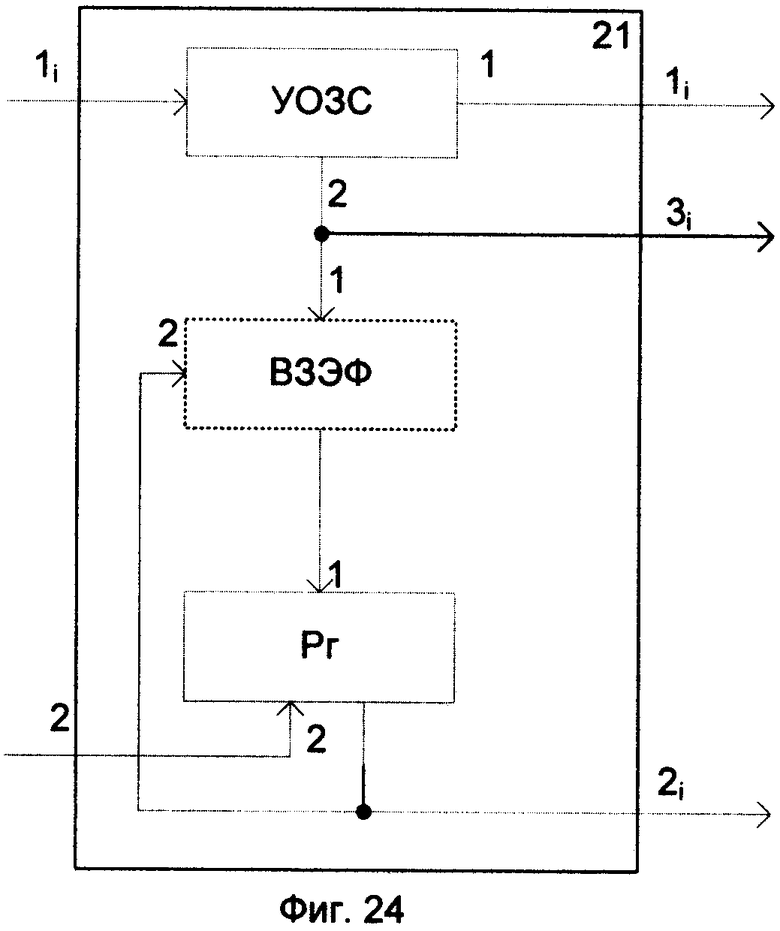

Выходной сигнал блока 20 (совокупность величин Δφi[n], (i=1÷NT) подается на вход блока 21 оценки значений символов и эталонной фазы и на второй вход блока вычисления среднего набега фазы ВСНФ 30. Блок 21 включает в себя NT параллельно включенных идентичных узлов, каждый из которых имеет структурную схему, представленную на фиг.24. Сигнал, действующий на входе 1i i-го узла Δφi[n] поступает на вход узла оценки значений символов (УОЗС) (см. фиг.24). В этом узле осуществляется сопоставление величины Δφi[n] с фазовыми сдвигами, кратными 2π/2q. Выявленный в результате этого сопоставления эталонный фазовый сдвиг ΔφЭТi[n], наименее отличающийся от Δφi[n], и принимается за оценку истинного фазового сдвига, а соответствующие ему двоичные символы на выходе 1i УОЗС подаются на выход модема для дальнейшей обработки в декодере канала. Со второго выхода УОЗС на первый вход вычислителя значений эталонной фазы (ВЗЭФ) и на третий выход блока 21 (см. фиг.24) подается величина ΔφЭТi[n]. На второй вход ВЗЭФ с выхода регистра Рг подается задержанное на один OFDM-такт значение эталонной фазы ΔφЭТi[n-1] и в соответствии с выражением

в узле ВЗЭФ вычисляется новое значение эталонной фазы, подаваемой далее на первый вход регистра Рг. Запись же этой величины в Рг (а следовательно, и выдача ее значения на выход 2i) осуществляется лишь в начале каждого OFDM-такта с приходом на второй вход регистра Рг коротких единичных импульсов с частотой ƒS (строка в временной диаграммы фиг.2). В результате на втором выходе БОЗС 21 формируется величина ΔφЭТi[n], в конечном итоге необходимая для формирования фигурирующей в (14) оценки «быстрого» допплеровского набега фазы Δφcp[n]. В качестве начального условия при n=0 в приемнике и передатчике может быть использовано ΔφЭТi[-1]=0.

в узле ВЗЭФ вычисляется новое значение эталонной фазы, подаваемой далее на первый вход регистра Рг. Запись же этой величины в Рг (а следовательно, и выдача ее значения на выход 2i) осуществляется лишь в начале каждого OFDM-такта с приходом на второй вход регистра Рг коротких единичных импульсов с частотой ƒS (строка в временной диаграммы фиг.2). В результате на втором выходе БОЗС 21 формируется величина ΔφЭТi[n], в конечном итоге необходимая для формирования фигурирующей в (14) оценки «быстрого» допплеровского набега фазы Δφcp[n]. В качестве начального условия при n=0 в приемнике и передатчике может быть использовано ΔφЭТi[-1]=0.

В блоке ВСНФ 30 (фиг.1) определяется среднее арифметическое Δφcp[n] фазовой ошибки Δi[n], вычисляемой как разность поступающих на его входы величин ΔφЭТi[n] и Δφi[n]:

Значение Δφcp[n] задерживается на один OFDM такт и подается на выход блока 30 (фиг.1). Таким образом на второй вход блока 22 поступает величина Δφcp[n-1], которая и фигурирует в формуле (14).

Недостатком рассмотренного модема является низкая помехоустойчивость, обусловленная следующими обстоятельствами:

1. Как видно из приведенного описания, точность первоначальной оценки канального частотного сдвига в данном устройстве определяется количеством параллельных каналов обработки информации, организованных в блоках 13, 24, 25 и 31. Так, для оценки с точностью до 1 Гц частотного сдвига в диапазоне ±100 Гц необходима организация 200 параллельных каналов. Реальный реализационный ресурс ограничивает возможность получения точной оценки частотного сдвига. Это усложняет условия функционирования инерционной системы слежения за частотным сдвигом: она должна обладать достаточно широкой полосой захвата. В результате в качестве такой системы используется устройство фазовой автоподстройки низкого порядка, не способное отслеживать флуктуации частотного сдвига, возникающие при связи между движущимися с изменяющимися скоростями объектами, что в конечном итоге снижает помехоустойчивость модема при работе в таких условиях.

2. Критерий, на основании которого выявляется информация о степени подстроенности синхропараметров (как посимвольной синхронизации в методе «отстающего» и «опережающего» окна фиг.5, так и частотного сдвига в методе, иллюстрируемом фиг.6), базируется на сравнении мощностей, содержащихся в единственном отсчете ДПФ принимаемого сигнала, соответствующем несигнальному тону при тех или иных модификациях значений оцениваемых синхропараметров. При этом шум, действующий в канале, непосредственно влияет на получаемую таким образом информацию. Используемая в прототипе возможность уменьшения влияния шума за счет усреднения результатов анализа степени подстроенности синхропараметров является ограниченной, поскольку вследствие быстрого изменения во времени параметров радиоканала длительность усреднения не может быть выбрана достаточно большой. Вследствие этого ухудшается качество посимвольной синхронизации, а также снижается эффективность инерционной системы слежения за частотным сдвигом, что снижает помехоустойчивость модема.

3. В процессе точного слежения за быстрым допплеровским сдвигом, осуществляемым посредством блоков 20, 21, 22 и 30 схемы, приведенной на фиг.1, коррекция фазы i-го принятого тона в соответствии с выражением (11) осуществляется за счет использования среднего по всем NT принятым тонам фазового сдвига Δφcp[n-1], вычисленного в узле 20. Ввиду того, что усредненное значение Δφcp не совпадает с конкретным значением фазового сдвига в отдельном i-м подканале, точность слежения за быстрым допплеровским сдвигом снижается, что тоже в конечном итоге ухудшает помехоустойчивость устройства.

4. Вследствие неизбежной неидеальности синхронизации при наличии распространенной в радиоканалах мощной узкополосной сосредоточенной по спектру помехи (расположенной в полосе одного из подканалов системы с OFDM) ее мешающее влияние не только не позволит принять информацию в данном подканале (что может быть исправлено с помощью помехоустойчивого кода в декодере канала), но и окажется весьма существенным в других подканалах и приведет к неисправляемым ошибкам. Это также снижает помехоустойчивость устройства.

В предлагаемом изобретении решается задача повышения помехоустойчивости модема.

Технический результат предлагаемого изобретения заключается в повышении помехоустойчивости устройства, обусловленном более эффективной реализацией процедур первоначальной оценки и отслеживания вносимого каналом частотного сдвига и посимвольной синхронизации и принятия решений о значении принимаемых символов, а также устранением влияния сосредоточенной по спектру помехи, попадающей в полосу частот одного из параллельных подканалов, на сигналы, передаваемые по остальным подканалам.

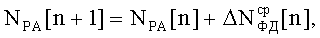

Указанный технический результат достигается тем, что в радиомодем, включающий четыре коммутатора, кодер, буферный накопитель, блок обратного дискретного преобразования Фурье, блок добавления защитного интервала, преобразователь числового массива во временную последовательность, формирующий фильтр, блок согласования, генератор настроечной последовательности, блок опорных частот, входной блок, блок автоматической регулировки усиления, буферный запоминающий блок, блок дискретного преобразования Фурье, блок вычислителей информативного приращения фазы, блок оценки значений символов и эталонной фазы и блок управления, причем первый вход первого коммутатора подключен ко входу передатчика модема, второй вход первого коммутатора соединен с выходом генератора настроечной последовательности, третий вход первого коммутатора связан с первым выходом блока управления, а выход первого коммутатора подключен ко входу кодера, выход которого соединен со входом буферного накопителя; выход блока обратного дискретного преобразования Фурье связан со входом блока добавления защитного интервала; выход блока добавления защитного интервала подключен к первому входу преобразователя числового массива во временную последовательность, второй вход которого соединен с первым выходом блока опорных частот, вторым входом формирующего фильтра, вторым входом входного блока, четвертым входом буферного запоминающего блока; выход преобразователя числового массива во временную последовательность связан с первым входом формирующего фильтра; выход блока согласования соединен с выходом передатчика модема, второй вход второго коммутатора подключен к пятому выходу блока управления и ко второму входу блока дискретного преобразования Фурье, третий вход второго коммутатора связан с первым выходом блока дискретного преобразования Фурье, выход второго коммутатора соединен со вторым входом буферного запоминающего блока, третий вход блока опорных частот подключен ко второму входу блока оценки значений символов и эталонной фазы; первый вход входного блока связан со входом приемника модема; второй выход блока управления соединен с третьим входом буферного запоминающего блока; третий вход блока дискретного преобразования Фурье связан с первым выходом буферного запоминающего блока; второй вход блока вычислителей информативного приращения фазы соединен со вторым выходом блока оценки значений символов и эталонной фазы, первый выход которого является выходом приемника модема, дополнительно введены блок распределения и формирования кадров с внесением избыточности, два сумматора, генератор пилот-сигнала, блок режекторных фильтров, узкополосный полосовой фильтр, два преобразователя частоты с комплексным выходом, блок накапливающих сумматоров, дециматор, блок накопления отсчетов и вычисления дискретного преобразования Фурье, анализатор частотного сдвига, фильтр, блок группирования, синхронизации и вычисления аргумента, формирователь частоты переноса спектра сигнала, блок вычисления и обработки синхросуммы, регистр адреса, фазовый дискриминатор посимвольной синхронизации, блок вычисления и анализа дисперсии мощности тонов, коммутационный блок и кодер-накопитель настроечной последовательности, причем выход буферного накопителя подключен ко входу блока распределения и формирования кадров с внесением избыточности, выход которого соединен со входом блока обратного дискретного преобразования Фурье, второй вход преобразователя числового массива во временную последовательность связан со входом генератора пилот-сигнала, первым входом блока управления, вторыми входами обоих преобразователей частоты с комплексным выходом, узкополосного полосового фильтра, блока режекторных фильтров и фильтра, третьим входом формирователя частоты переноса спектра сигнала и первым выходом блока опорных частот, выход формирующего фильтра подключен к первому входу первого сумматора, второй вход которого соединен с первым выходом генератора пилот-сигнала и третьим входом первого преобразователя частоты с комплексным выходом, выход первого сумматора связан со входом блока согласования, второй выход блока опорных частот подключен к вторым входам блока накапливающих сумматоров, дециматора, блока накопления отсчетов и вычисления дискретного преобразования Фурье и анализатора частотного сдвига, третий выход блока опорных частот соединен со вторыми входами формирователя частоты переноса спектра сигнала, регистра адреса, блока управления и блока оценки значений символов и эталонной фазы и четвертым входом блока группирования, синхронизации и вычисления аргумента, второй выход генератора пилот-сигнала связан с четвертым входом первого преобразователя частоты с комплексным выходом, выход входного блока подключен к первому входу блока режекторных фильтров, третий вход которого соединен с выходом блока вычисления и анализа дисперсии мощности тонов, выход блока режекторных фильтров связан со входом блока автоматической регулировки усиления, выход блока автоматической регулировки усиления подключен к первым входам узкополосного полосового фильтра и фильтра, выход узкополосного полосового фильтра соединен с первым входом первого преобразователя частоты с комплексным выходом, выход которого связан с первым входом блока накапливающих сумматоров, выход блока накапливающих сумматоров подключен к первому входу дециматора, выход дециматора соединен с первым входом узла накопления отсчетов и вычисления дискретного преобразования Фурье, первый выход которого связан с первым входом анализатора частотного сдвига, второй выход блока накопления отсчетов и вычисления дискретного преобразования Фурье подключен к третьему входу анализатора частотного сдвига, первый выход анализатора частотного сдвига соединен с четвертым входом формирователя частоты переноса спектра сигнала, а второй - с третьим входом блока управления, выход фильтра связан с первым входом второго преобразователя частоты с комплексным выходом, третий и четвертый входы которого подключены соответственно к первому и второму выходам формирователя частоты переноса спектра, выход второго преобразователя частоты с комплексным выходом соединен с первым входом третьего коммутатора, второй вход третьего коммутатора связан с шестым выходом блока управления, выход третьего коммутатора подключен к первому входу буферного запоминающего блока, первый выход буферного запоминающего блока связан с первым входом узла вычисления и обработки синхросуммы, второй выход буферного запоминающего блока подключен ко второму входу блока вычисления и обработки синхросуммы, первый вход второго коммутатора соединен с первым выходом блока вычисления и обработки синхросуммы, первый вход четвертого коммутатора соединен с третьим выходом блока вычисления и обработки синхросуммы, второй вход четвертого коммутатора связан с выходом второго сумматора, третий вход четвертого коммутатора подключен к третьему выходу блока управления, третьему входу блока вычисления и обработки синхросуммы и пятому входу формирователя частоты переноса спектра сигнала, выход четвертого коммутатора соединен с первым входом регистра адреса, первый вход блока дискретного преобразования Фурье связан со вторыми входами второго сумматора и фазового дискриминатора посимвольной синхронизации, четвертым входом блока вычисления и обработки синхросуммы и выходом регистра адреса, второй выход блока дискретного преобразования Фурье подключен к первому входу блока группирования, синхронизации и вычисления аргумента и входу блока вычисления и анализа дисперсии мощности тонов, третий выход блока дискретного преобразования Фурье соединен с пятым входом блока вычисления и обработки синхросуммы, второй вход блока группирования, синхронизации и вычисления аргумента связан с пятым выходом блока вычисления и обработки синхросуммы и первым входом формирователя частоты переноса спектра сигнала, третий вход блока группирования, синхронизации и вычисления аргумента подключен ко второму входу блока вычислителей информативного приращения фазы, выход блока группирования, синхронизации и вычисления аргумента соединен с первым входом блока вычислителей информативного приращения фазы, первый вход блока оценки значений символов и эталонной фазы связан с выходом коммутаторного блока, второй выход блока вычисления и обработки синхросуммы подключен к первому входу фазового дискриминатора посимвольной синхронизации, четвертый выход блока вычисления и обработки синхросуммы соединен с четвертым входом блока управления, первый вход второго сумматора связан с выходом фазового дискриминатора посимвольной синхронизации, выход блока вычислителей информативного приращения фазы соединен с первым входом коммутационного блока, второй вход коммутационного блока связан с выходом кодера-накопителя настроечной последовательности, третий вход коммутационного блока подключен к первому выходу блока управления, вход кодера-накопителя настроечной последовательности соединен с выходом генератора настроечной последовательности.

Описание изобретения включает 38 фигур.

На фигуре 1 изображена функциональная схема устройства-прототипа.

На фигуре 2 представлены временные диаграммы, иллюстрирующие работу прототипа.

На фигурах 3-24 приведены алгоритмы работы и функциональные схемы отдельных узлов, входящих в состав устройства-прототипа.

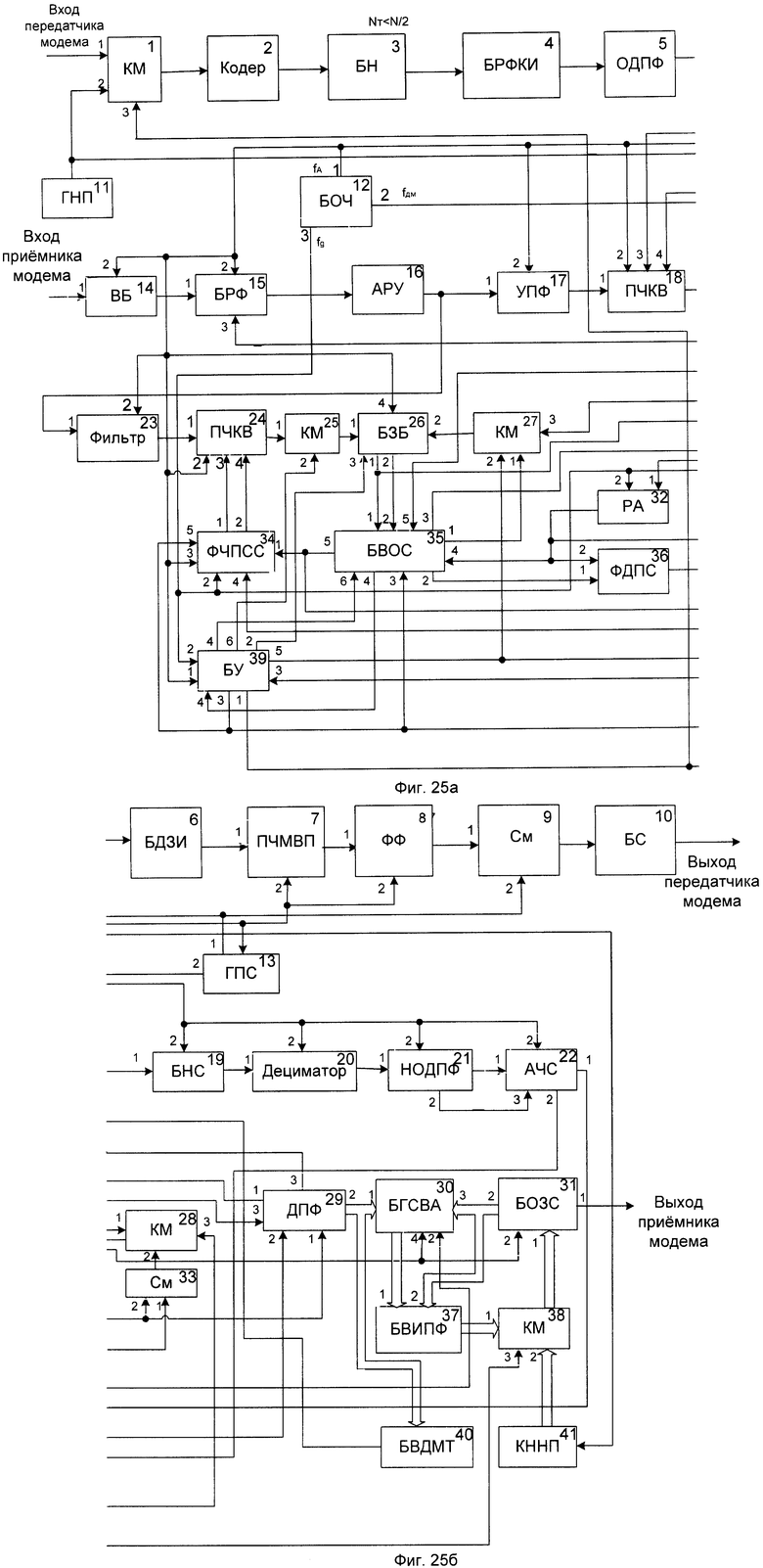

На фигуре 25 изображена функциональная схема предлагаемого изобретения.

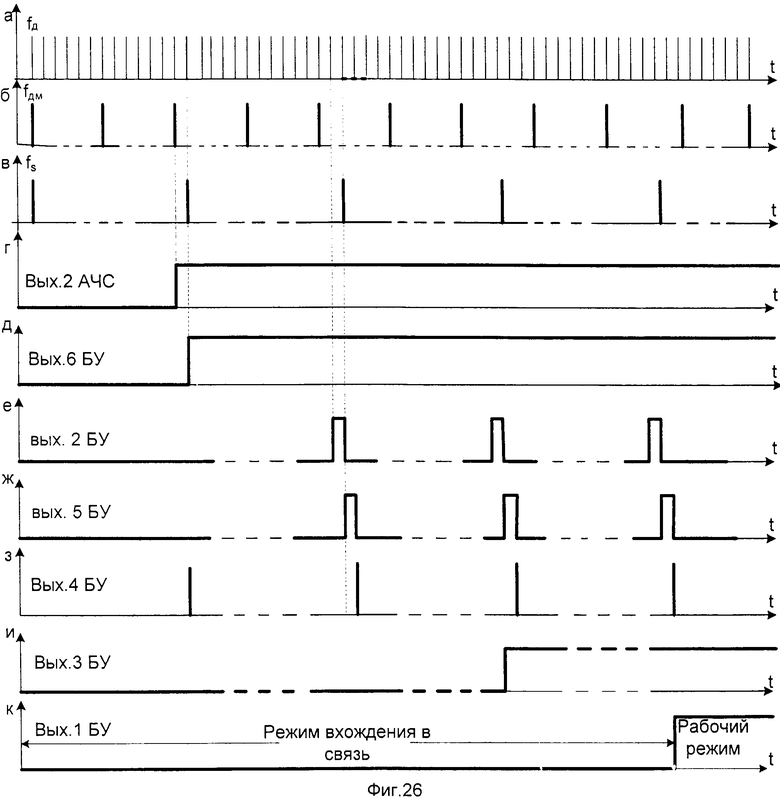

На фигуре 26 представлены временные диаграммы, иллюстрирующие работу предлагаемого изобретения.

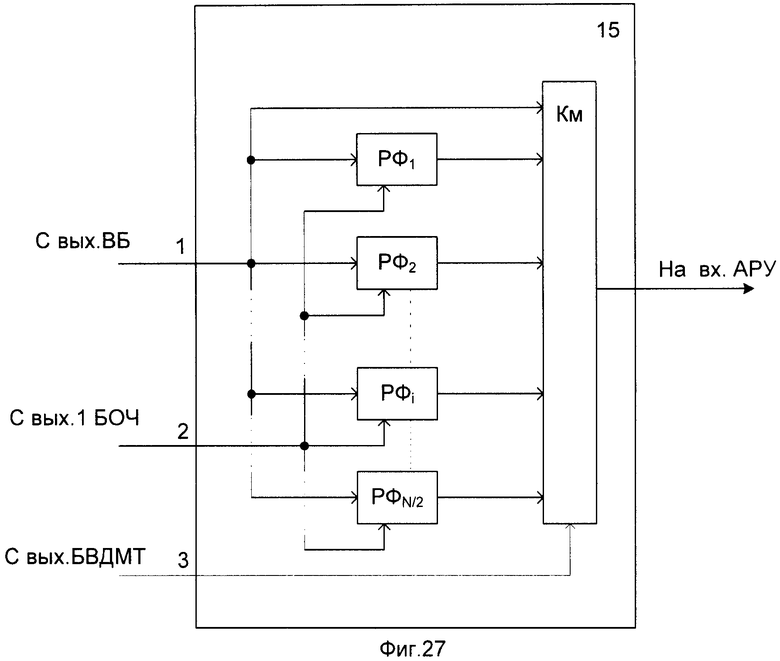

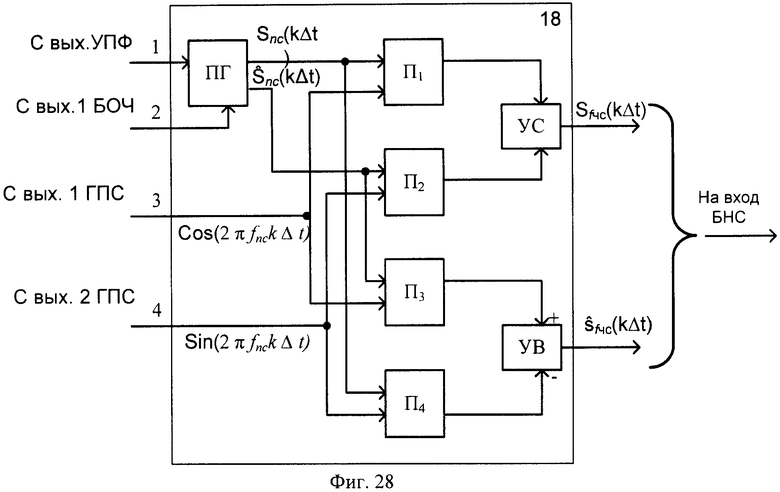

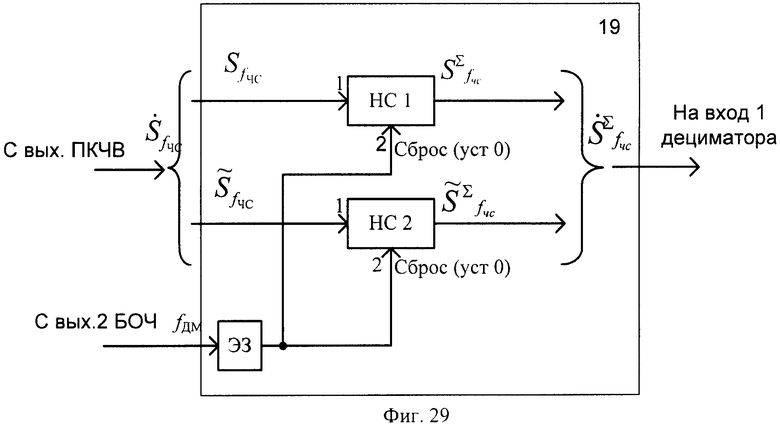

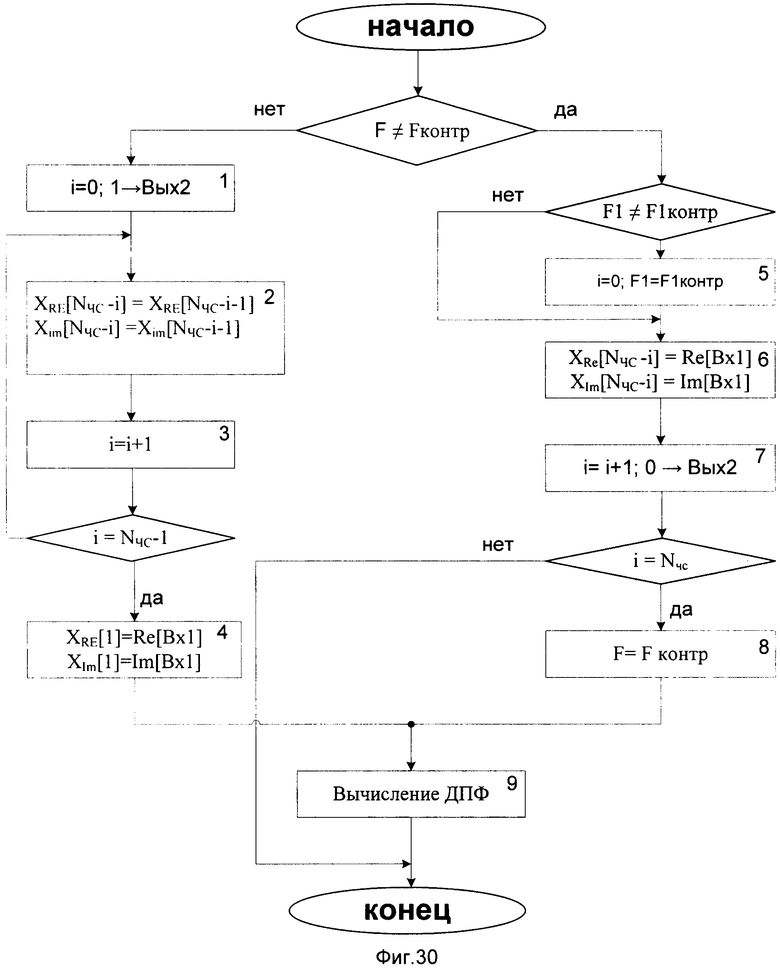

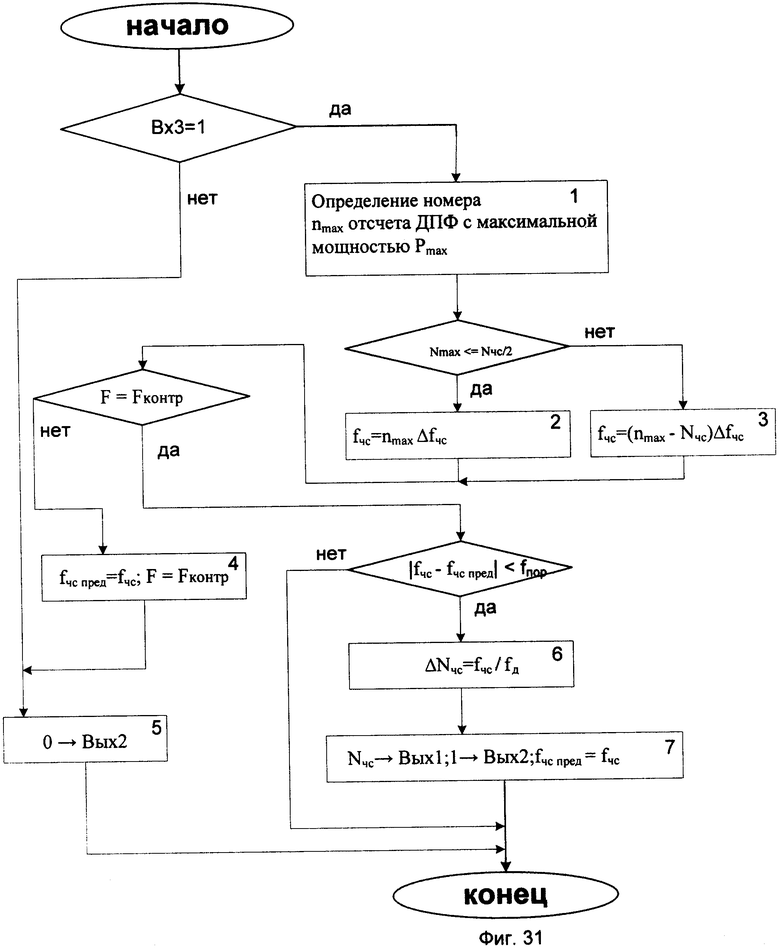

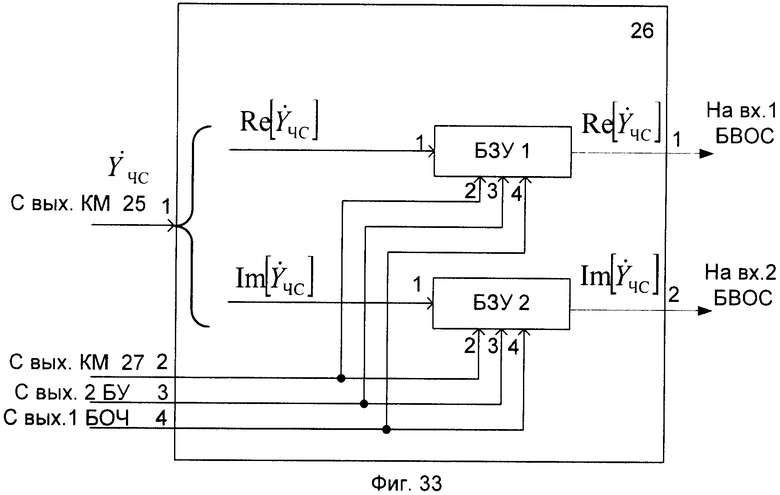

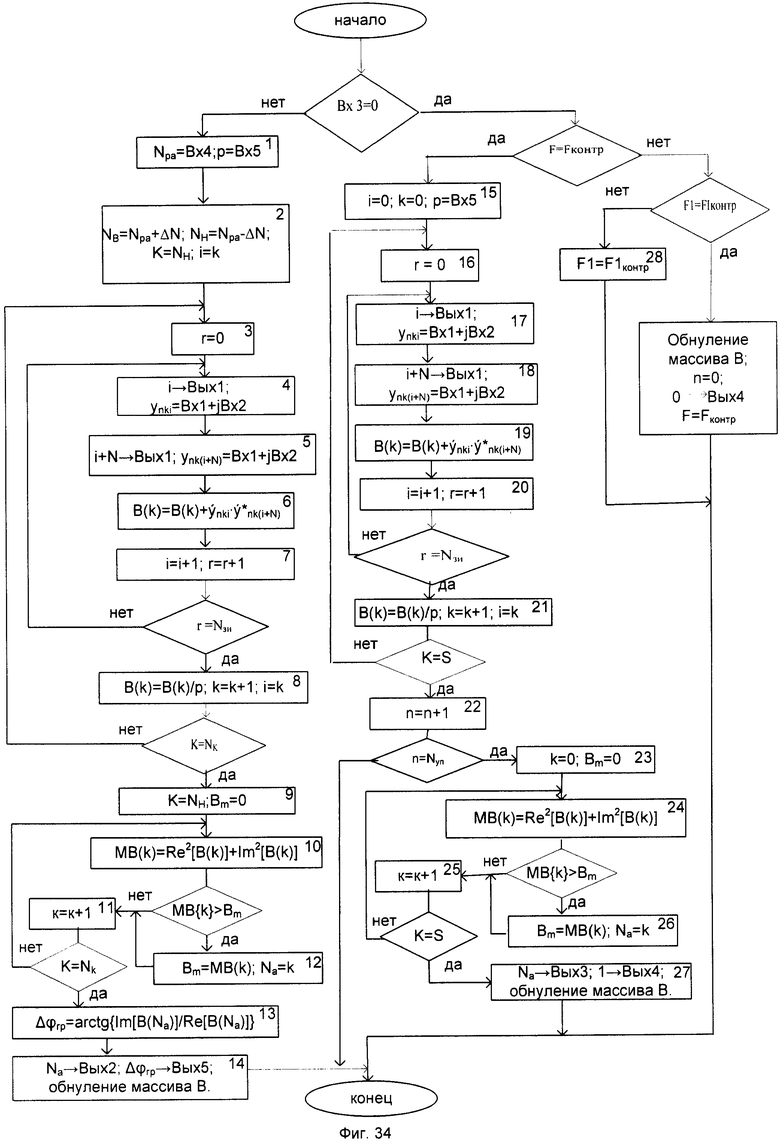

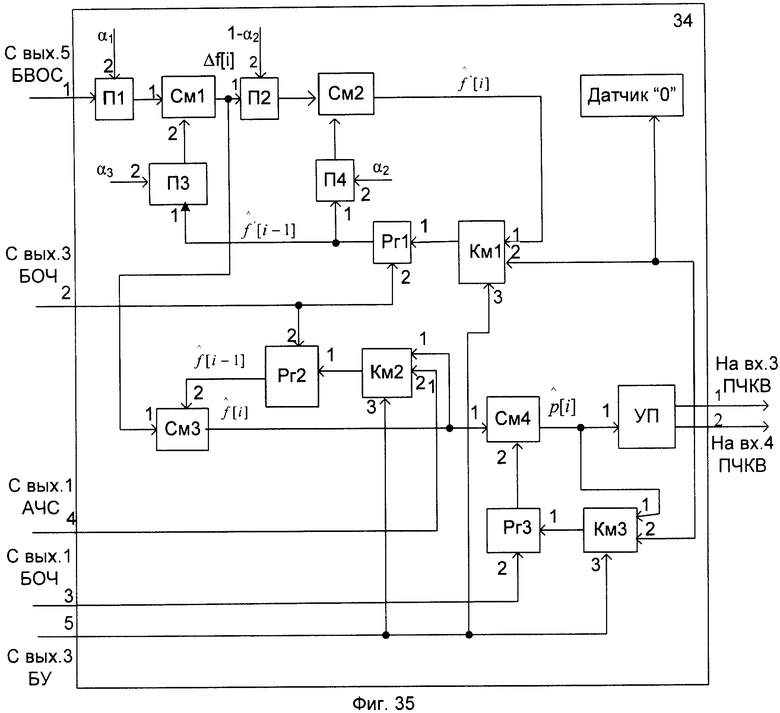

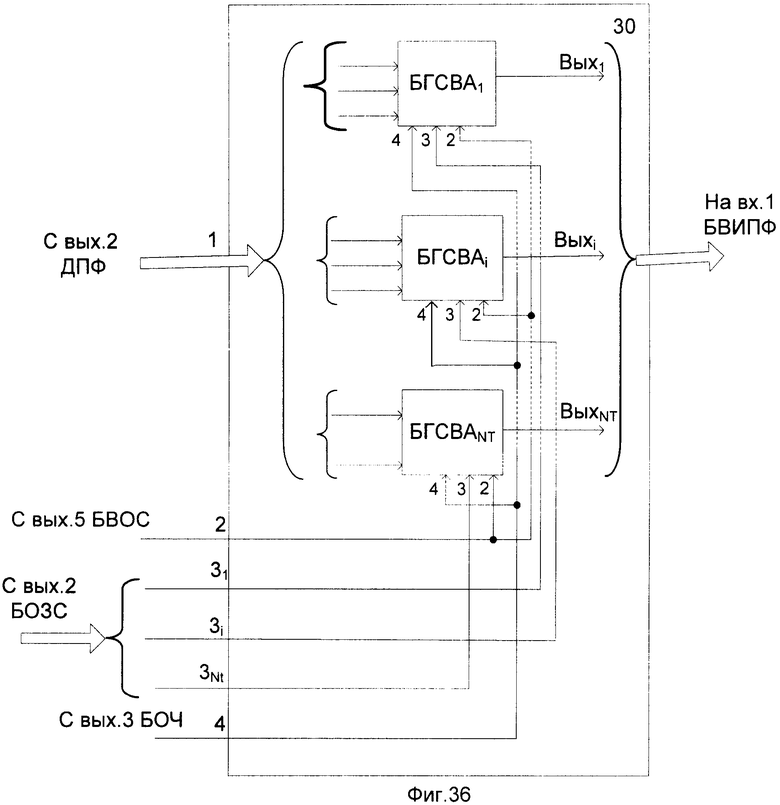

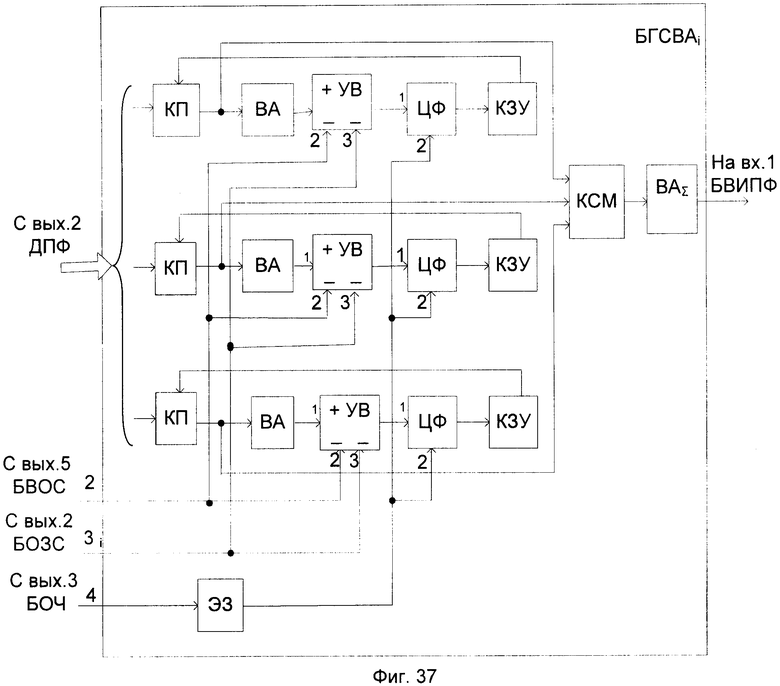

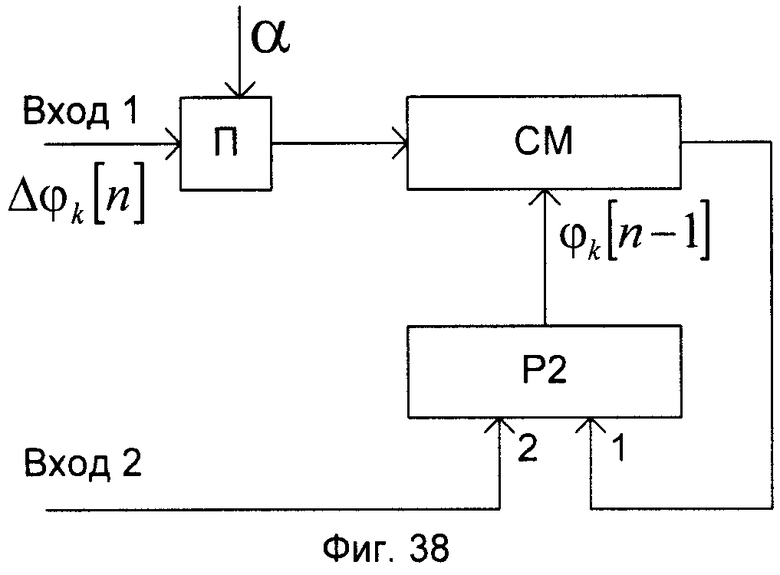

На фигурах 27-38 приведены алгоритмы работы и функциональные схемы отдельных узлов, входящих в состав предлагаемого изобретения.