Родственные заявки

[0001] По настоящей патентной заявке испрашивается приоритет Предварительной заявки США № 61/040,540, озаглавленной «Architecture to Handle Concurrent Multiple Channels», которая была подана 28 марта 2008, которая явным образом во всей своей полноте включена в настоящее описание посредством ссылки.

УРОВЕНЬ ТЕХНИКИ

Область техники

[0002] Это изобретение относится к системам беспроводной связи. Более конкретно, это изобретение относится к системам и способам для обеспечения улучшенной пропускной способности для обработки информации в нисходящей линии связи.

УРОВЕНЬ ТЕХНИКИ

[0003] Системы беспроводной связи широко развернуты для предоставления различного контента связи, такого как голос, данные и т.д. Такие системы могут быть системами с множественным доступом, выполненные с возможностью поддержки связи с многочисленными пользователями посредством совместного использования доступных ресурсов системы (например, полосы пропускания и мощности передачи). Примеры таких систем с множественным доступом включают в себя системы множественного доступа с кодовым разделением каналов (CDMA), системы множественного доступа с временным разделением каналов (TDMA), системы множественного доступа с частотным разделением каналов (FDMA), системы 3GPP LTE и системы множественного доступа с ортогональным частотным разделением каналов (OFDMA).

[0004] В целом, беспроводная система связи с множественным доступом может одновременно поддерживать связь для множества беспроводных терминалов, которые осуществляют связь с одной или более базовыми станциями посредством передач по прямой и обратной линиям связи. Прямая линия связи (или нисходящая линия связи) относится к линии связи от базовых станций к терминалам, а обратная линия связи (или восходящая линия связи) относится к линии связи от терминалов к базовым станциям. Эта линия связи может быть установлена через систему с одним-входом-одним-выходом (SISO), систему с многими-входами-одним-выходом или систему с многими-входами-многими-выходами (MIMO).

[0005] Система MIMO использует множество (N T) передающих антенн и множество (N R) принимающих антенн для передачи данных. Канал MIMO, образованный N T передающими и N R принимающими антеннами, может быть разбит на N S независимых каналов, которые также именуются как пространственные каналы, где N S≤min{N T, N R}. Каждый из N S независимых каналов соответствует размерности. Система MIMO может обеспечить улучшенное функционирование (например, большую пропускную способность и/или большую надежность), если используются дополнительные размерности, созданные множеством передающих и принимающих антенн.

[0006] Система MIMO поддерживает системы с дуплексом с временным разделением каналов (TDD) и дуплексом с частотным разделением каналов (FDD). В системе TDD передачи по прямой и обратной линии связи находятся в одной и той же области частоты так, что принцип обратимости позволяет оценивать канал прямой линии связи по каналу обратной линии связи. Это дает возможность точке доступа извлекать выгоду из диаграммы направленности при передаче по прямой линии связи, когда на точке доступа доступны многочисленные антенны.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0007] Настоящее изобретение содержит в себе описания, относящиеся к координированию многочисленных систем для улучшенной обработки данных в нисходящей линии связи.

[0008] В одном из разнообразных аспектов изобретения предоставлено устройство для улучшенной обработки нисходящей линии связи принятых каналов в системе мобильной связи, причем устройство содержит: буфер, выполненный с возможностью содержать в себе, по меньшей мере, демодулированные данные управления и демодулированные данные трафика; механизм блока обратного преобразования, содержащий в себе, по меньшей мере, два блока обратного преобразования, выполненные с возможностью независимо работать с, по меньшей мере, данными управления и данными трафика из буфера; буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти, доступных посредством механизма блока обратного преобразования; механизм декодера, содержащий в себе множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и схему разрешения конфликтов, обеспечивающую управление, по меньшей мере, одним из: механизм обратного преобразователя, буфером LLR и механизм декодера, причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика.

[0009] В другом аспекте изобретения предоставлен способ для улучшенной обработки нисходящей линии связи принятых каналов в системе мобильной связи, причем способ содержит этапы, на которых: в буфер вводят демодулированные данные управления и демодулированные данные трафика; обратно преобразуют данные управления и данные трафика из буфера, используя, по меньшей мере, два блока обратного преобразования, выполненные с возможностью работать независимо; загружают данные, подвергнутые обратному преобразованию, в буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти; декодируют данные в буфере LLR, используя множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и управляют работой, по меньшей мере, одного из: обратного преобразования, доступа к буферу LLR и декодирования, причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика.

[0010] В другом аспекте изобретения предоставлено устройство для улучшенной обработки в нисходящей линии связи принятых каналов в системе мобильной связи, причем устройство содержит: средство для хранения, по меньшей мере, демодулированных данных управления и демодулированных данных трафика; множество средств для независимого обратного преобразования данных управления и данных трафика из средства для хранения; средство для хранения логарифмического отношения правдоподобия (LLR), выполненное с возможностью поддержки множества сегментов памяти, доступных посредством множества средств для независимого обратного преобразования; множество средств для декодирования, работающих с данными из выбранного сегмента памяти средства для хранения LLR; и средство для обеспечения управления, по меньшей мере, одним из: множеством средств для обратного преобразования, средством для хранения LLR и множеством средств для декодирования, причем, по меньшей мере, одно из множества средств для декодирования приспособлено для декодирования данных управления и, по меньшей мере, другое одно из множества средств для декодирования приспособлено для декодирования данных трафика.

[0011] В другом аспекте изобретения предоставлен компьютерный программный продукт, который содержит: машиночитаемый носитель, который содержит: код для ввода в буфер демодулированных данных управления и демодулированных данных трафика; код для обратного преобразования данных управления и данных трафика из буфера, используя, по меньшей мере, два блока обратного преобразования, выполненные с возможностью работать независимо; код для загрузки данных, подвергнутых обратному преобразованию в буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти; код для декодирования данных в буфере LLR, используя множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и код для управления работой, по меньшей мере, одного из: обратное преобразование, доступ к буферу LLR и декодирование, причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика.

[0012] В другом аспекте изобретения предоставлено устройство для улучшенной обработки нисходящей линии связи принятых каналов в системе мобильной связи, причем устройство содержит: процессор, выполненный с возможностью управлять работой по: вводу в буфер демодулированных данных управления и демодулированных данных трафика; обратному преобразованию данных управления и данных трафика из буфера, используя, по меньшей мере, два блока обратного преобразования, выполненные с возможностью работать независимо; загрузке данных, подвергнутых обратному преобразованию в буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти; декодированию данных в буфере LLR, используя множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и управлению работой, по меньшей мере, одного из: обратное преобразование, доступ к буферу LLR и декодирование, причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика; и памяти, объединенной с процессором для хранения данных.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0013] Признаки, сущность и преимущества настоящего изобретения станут более очевидными из подробного описания изложенного ниже при совместном рассмотрении с чертежами, в которых одинаковые ссылочные позиции обозначают соответствующие элементы на всех чертежах и причем:

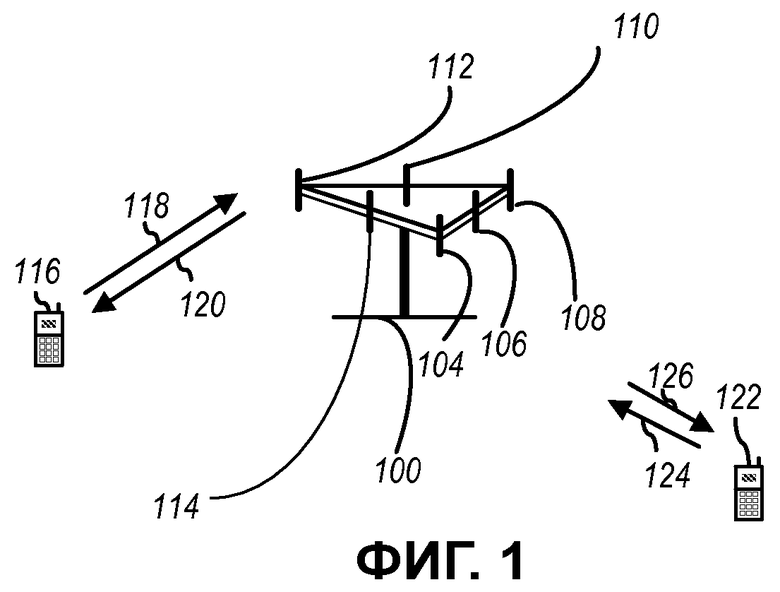

[0014] Фиг.1 иллюстрирует систему беспроводной связи с множественным доступом в соответствии с одним вариантом осуществления.

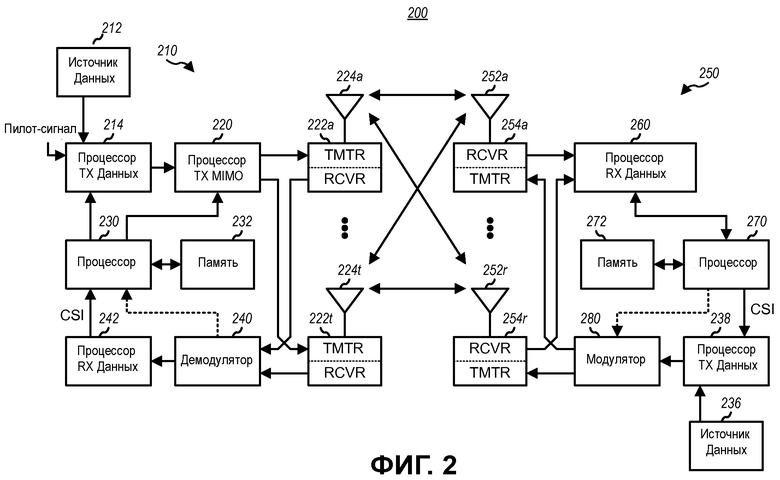

[0015] Фиг.2 является структурной схемой системы связи.

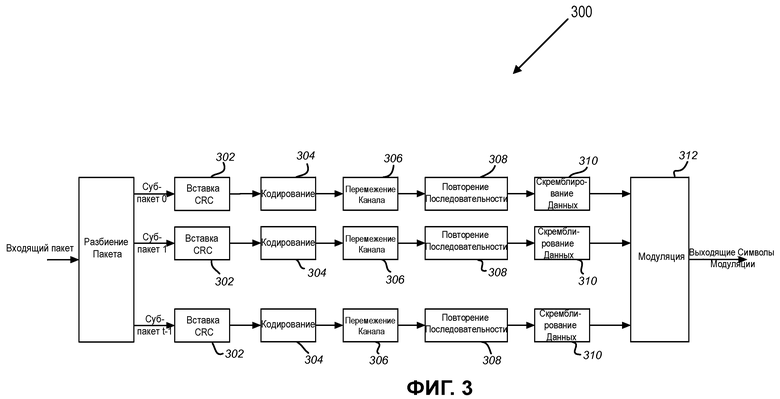

[0016] Фиг.3 является структурной схемой архитектуры передачи для компоновки пакетов данных.

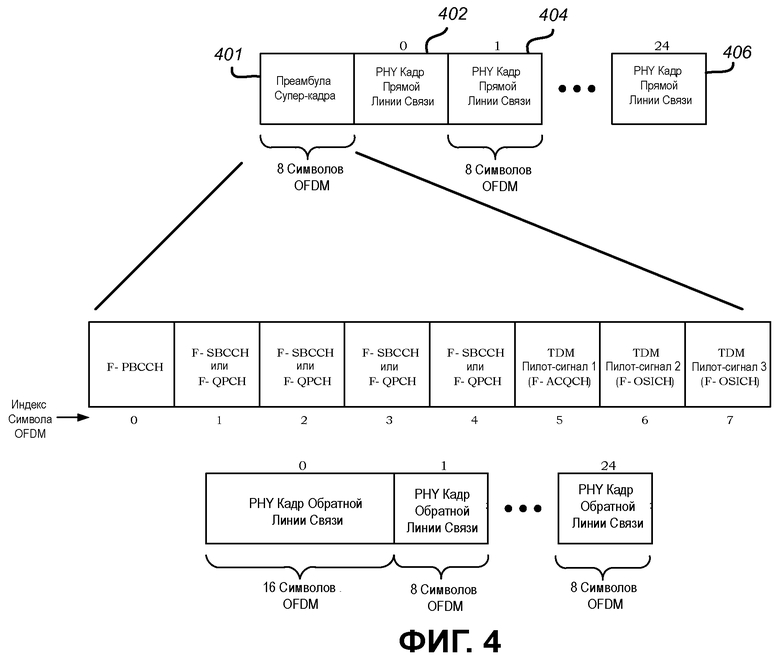

[0017] Фиг.4 является примерной архитектурой передачи кадра/супер-кадра.

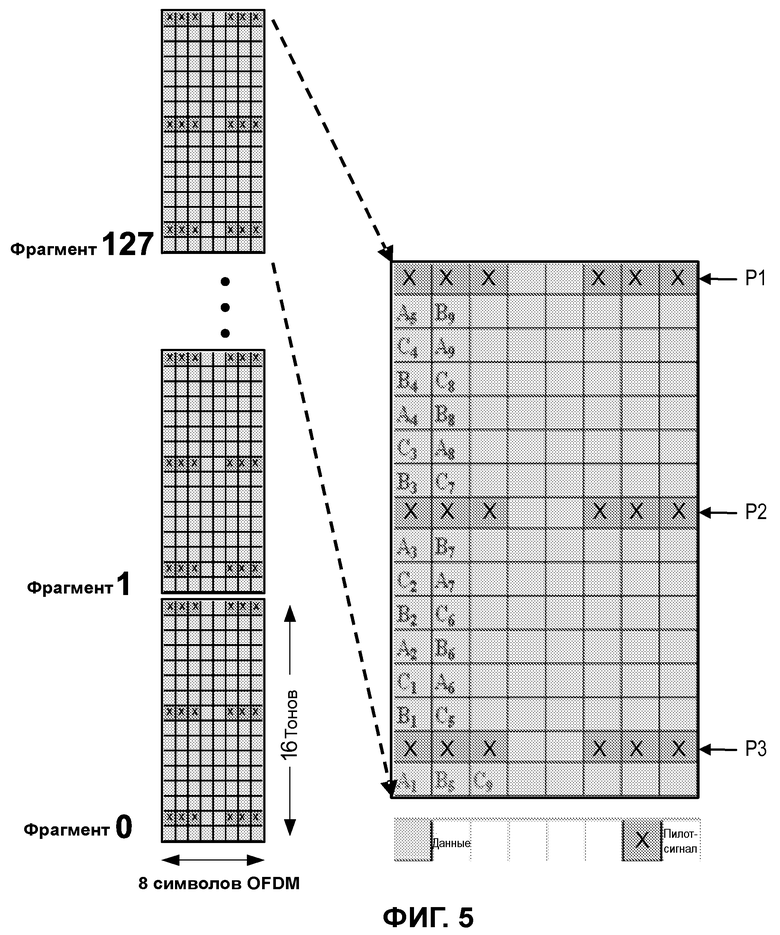

[0018] Фиг.5 изображает логическую компоновку данных OFDM.

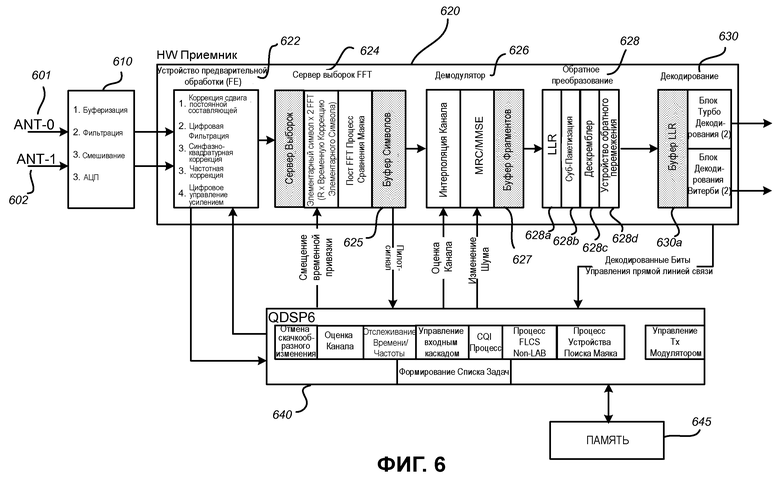

[0019] Фиг.6 изображает примерную архитектуру аппаратно реализованного приемника с поддерживающим процессором.

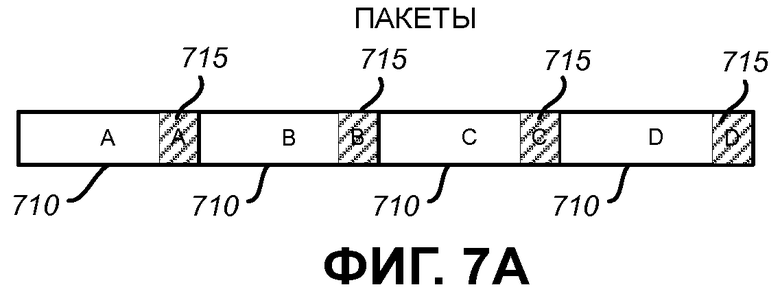

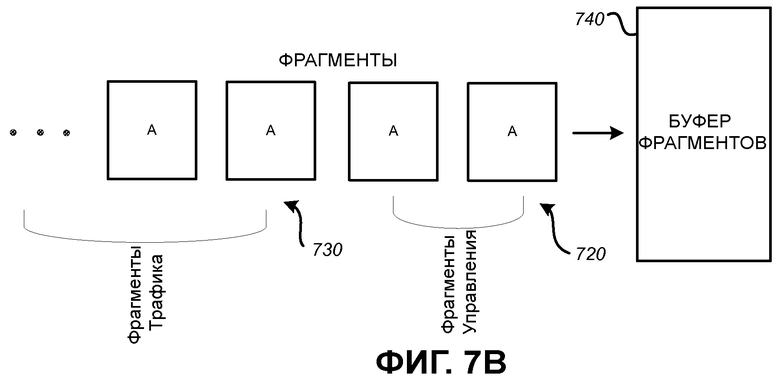

[0020] Фиг.7A-B изображают компоновку пакетов/суб-пакетов и их соответствующий порядок фрагментов.

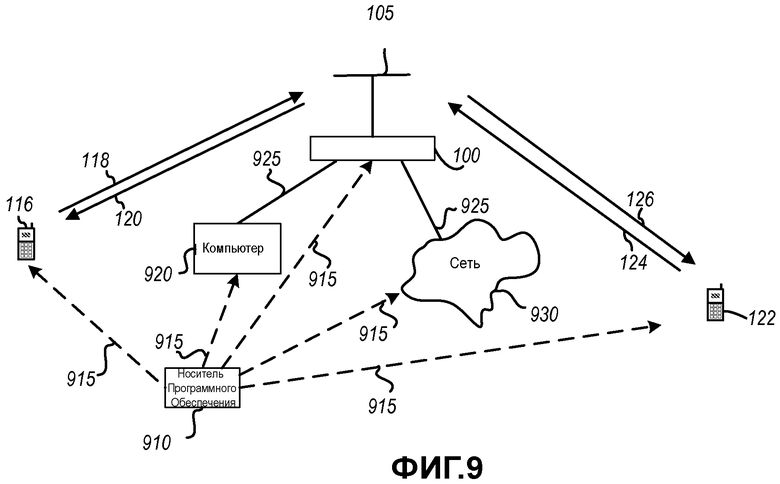

[0021] Фиг.8 изображает часть примерного аппаратно реализованного приемника с Фиг.6.

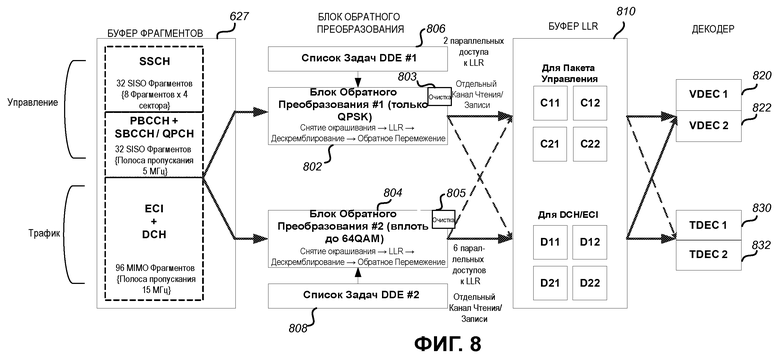

[0022] Фиг.9 изображает примерную систему с носителем программного обеспечения.

ПОДРОБНОЕ ОПИСАНИЕ

[0023] В целях настоящего документа используются нижеследующие сокращения, пока не указано иное:

AM Режим с Подтверждением Передачи

AMD Данные Режима с Подтверждением Передачи

ARQ Автоматический Запрос Повторной Передачи

BCCH Широковещательный Канал Управления

BCH Широковещательный Канал

C- Управление-

CCCH Общий Канал Управления

CCH Канал Управления

CCTrCH Составной Кодовый Транспортный Канал

CP Циклический Префикс

CRC Контроль Циклическим Избыточным Кодом

CTCH Общий Канал Трафика

DCCH Выделенный Канал Управления

DCH Выделенный Канал

DL Нисходящая Линия Связи

DSCH Совместно Используемый Канал Нисходящей Линии Связи

DTCH Выделенный Канал Трафика

ECI Расширенная Информация Канала

FACH Канал Доступа Прямой Линии Связи

FDD Дуплекс с Частотным Разделением Каналов

L1 Уровень 1 (физический уровень)

L2 Уровень 2 (уровень управления передачей данных)

L3 Уровень 3 (сетевой уровень)

LI Индикатор Длины

LSB Младший Значащий Бит

MAC Управление Доступом к Среде

MBMS Служба Мультимедийного Многоадресного Широковещания

MCCH Канал Управления MBMS при соединении "точка-множество точек"

MRW Окно Приема Перемещения

MSB Старший Значащий Бит

MSCH Канал Планирования MBMS при соединении "точка-множество точек"

MTCH Канал Трафика MBMS при соединении "точка-множество точек"

PBCCH Первичный Широковещательный Канал Управления

PCCH Канал Управления Поисковым Вызовом

PCH Канал Поискового Вызова

PDU Протокольная Единица Данных

PHY Физический Уровень

PhyCH Физические Каналы

QPCH Канал Быстрого Поискового Вызова

RACH Канал Произвольного Доступа

RLC Управление Радиосвязью

RRC Управление Радиоресурсами

SAP Точка Доступа к Службе

SBCCH Вторичный Широковещательный Канал Управления

SDU Модуль Данных Службы

SHCCH Канал Управления Совместно Используемого Канала

SN Номер Последовательности

SSCH Совместно Используемый Канал Сигнализации

SUFI Супер Поле

TCH Канал Трафика

TDD Дуплекс с Временным Разделением каналов

TFI Индикатор Транспортного Формата

TM Прозрачный Режим

TMD Данные Прозрачного Режима

TTI Интервал Времени Передачи

U- Пользователь-

UE Оборудование Пользователя

UL Восходящая Линия Связи

UM Режим Без Подтверждения Передачи

UMD Данные Режима Без Подтверждения Передачи

UMTS Универсальная Система Мобильной Связи

UTRA UMTS Наземного Радиодоступа

UTRAN UMTS Сети Наземного Радиодоступа

MBSFN Многоадресное Широковещание по Одночастотной Сети

MCE Координирующий Объект MBMS

MCH Многоадресный Канал

DL-SCH Совместно Используемый Канал Нисходящей Линии Связи

MSCH Канал Управления MBMS

PDCCH Физический Канал Управления Нисходящей Линии Связи

PDSCH Физический Совместно Используемый Канал Нисходящей Линии Связи

[0024] Описанные здесь технологии могут использоваться для различных сетей беспроводной связи, таких как сети Множественного Доступа с Кодовым Разделением (CDMA), сети Множественного Доступа с Временным Разделением (TDMA), сети Множественного Доступа с Частотным Разделением (FDMA), сети FDMA с Ортогональным разделением(OFDMA), сети FDMA с Единственной Несущей (SC-FDMA) и т.д. Термины «сети» и «системы» часто используются взаимозаменяемо. Сеть CDMA может реализовывать радиотехнологию, такую как Универсальный Наземный Радиодоступ (UTRA), cdma2000 и т.д. UTRA включает в себя Широкополосный-CDMA (W-CDMA) и Низкоскоростную Передачу Сигнала (LCR). cdma2000 охватывает стандарты IS-2000, IS-95 и IS-856. Сеть TDMA может реализовывать радиотехнологию, такую как Глобальная Система Связи с Подвижными Объектами (GSM). Сеть OFDMA может реализовывать радиотехнологию, такую как Развитый UTRA (E-UTRA), IEEE 802.11, IEEE 802.16, IEEE 802.20, Flash-OFDM® и т.д. UTRA, E-UTRA и GSM являются частями Универсальной Системы Мобильной Связи (UMTS). Проект Долговременного Развития (LTE) является предстоящим выпуском UMTS, которая использует E-UTRA. UTRA, E-UTRA, GSM, UMTS и LTE описаны в документах от организации, именуемой «Проектом Партнерства Третьего Поколения» (3GPP). cdma2000 описан в документах от организации, именуемой «Второй Проект Партнерства Третьего Поколения» (3GPP2). Эти различные радиотехнологии и стандарты являются известными в соответствующей области техники. Для ясности, некоторые аспекты технологии описаны ниже применительно к LTE, и в большей части нижеследующего описания используется терминология LTE.

[0025] Технологией является множественный доступ с частотным разделением и одной несущей (SC-FDMA), которая использует модуляцию с одной несущей и коррекцию частотной области. SC-FDMA имеет похожую производительность и, по существу, такую же сложность, как и у системы OFDMA. Сигнал SC-FDMA имеет меньшее отношение пиковой к средней мощности (PAPR) благодаря присущей ему структуре с одной несущей. На SC-FDMA обращают большое внимание, в особенности в связи по восходящей линии связи, в которой меньшее PAPR дает мобильному терминалу значительное преимущество в отношении эффективности мощности передачи. На сегодняшний день это является рабочим предположением для схемы множественного доступа в восходящей линии связи в Проекте Долгосрочного Развития (LTE) 3GPP или Развитом UTRA.

[0026] Ссылаясь на Фиг.1, проиллюстрирована система беспроводной связи с множественным доступом в соответствии с одним вариантом осуществления. Точка 100 доступа (AP) включает в себя многочисленные группы антенн, одна из которых включает в себя 104 и 106, другая включает 108 и 110 и добавочная включает в себя 112 и 114. На Фиг.1 для каждой группы антенн показаны только две антенны, тем не менее, для каждой группы антенн может использоваться большее или меньшее число антенн. Терминал 116 доступа (AT) находится на связи с антеннами 112 и 114, причем антенны 112 и 114 передают информацию терминалу 116 доступа по прямой линии 120 связи и принимают информацию от терминала 116 доступа по обратной линии 118 связи. Терминал 122 доступа находится на связи с антеннами 106 и 108, причем антенны 106 и 108 передают информацию терминалу 122 доступа по прямой линии 126 связи и принимают информацию от терминала 122 доступа по обратной линии 124 связи. В системе FDD линии 118, 120, 124 и 126 связи могут использовать для связи отличные частоты. Например, прямая линия 120 связи может использовать частоту, отличную от той, что используется обратной линией 118 связи.

[0027] Каждая группа антенн и/или область, в которой они предназначены осуществлять связь, часто именуется как сектор точки доступа. В варианте осуществления каждая из групп антенн предназначена для осуществления связи с терминалами доступа в секторе областей, охватываемых точкой 100 доступа.

[0028] Для связи по прямым линиям 120 и 126 связи передающие антенны точки 100 доступа используют формирование диаграммы направленности для того, чтобы улучшить отношение сигнала к шуму по прямым линиям связи для отличных терминалов 116 и 122 доступа. Также точка доступа, использующая формирование диаграммы направленности для передачи терминалам доступа, произвольно размещенным в зоне ее охвата, создает меньше помех для терминалов доступа в соседних ячейках, нежели точка доступа, передающая всем ее терминалам доступа через одну антенну.

[0029] Точка доступа может быть фиксированной станцией, используемой для связи с терминалами, и также может именоваться как Узел В или в соответствии с некоторой другой терминологией. Терминал доступа также может именоваться оборудованием пользователя (UE), устройством беспроводной связи, терминалом, терминалом доступа или в соответствии с некоторой другой терминологией.

[0030] Фиг.2 является структурной схемой варианта осуществления системы 210 передатчика (также известного как точка доступа) и системы 250 приемника (также известной как терминал) в системе 200 MIMO. В системе 210 передатчика данные трафика для нескольких потоков данных предоставляются источником 212 данных процессору 214 передачи (TX) данных.

[0031] В варианте осуществления каждый поток данных передается через соответствующую передающую антенну или группу антенн. Процессор 214 TX данных форматирует, кодирует и перемежает данные трафика для каждого потока данных на основании конкретной схемы кодирования, выбранной для потока данных, для того чтобы предоставить закодированные данные.

[0032] Закодированные данные для каждого потока данных могут быть мультиплексированы с данными пилот-сигнала, используя технологии OFDM. Данные пилот-сигнала, как правило, являются известным шаблоном данных, который обрабатывается известным образом и может быть использован в системе приемника для того, чтобы оценить отклик канала. Мультиплексированные пилот-сигнал и закодированные данные для каждого потока данных затем подвергаются модуляции (например, преобразуются в символ) на основании конкретной схемы модуляции (например, BPSK, QSPK, M-PSK, M-QAM и т.д.), выбранной для этого потока данных для того, чтобы предоставить символы модуляции. Скорость передачи данных, кодирование и модуляция для каждого потока данных могут быть определены инструкциями, выполняемыми процессором 230.

[0033] Затем символы модуляции для всех потоков данных предоставляются процессору 220 TX MIMO, который может далее обработать символы модуляции (например, для OFDM). Затем процессор 220 TX MIMO предоставляет N T потоков символов модуляции, N T передатчикам с 222а по 222t (TMTR). В некоторых вариантах осуществления процессор 220 TX MIMO применяет весовые коэффициенты формирования диаграммы направленности к символам потоков данных и к антенне, по которой будут переданы символы.

[0034] Каждый передатчик 222 принимает и обрабатывает соответствующий поток символов для того, чтобы предоставить один или более аналоговые сигналы, и дополнительно приводит к заданным условиям (например, усиливает, фильтрует или преобразует с повышением частоты) аналоговые сигналы для того, чтобы предоставить сигнал, модулированный сигнал, подходящий для передачи по каналу MIMO. N T модулированных сигналов от передатчиков с 222a по 222t затем соответственно передаются через N T антенн с 224a по 224t.

[0035] В системе 250 приемника переданные подвергнутые модуляции сигналы принимаются N R антеннами с 252a по 252r и сигнал, принятый от каждой антенны 252, предоставляется соответствующему приемнику с 254a по 254r (RCVR). Каждый приемник 254 приводит к заданным условиям (например, фильтрует, усиливает и преобразует с понижением частоты) соответствующий принятый сигнал, оцифровывает приведенный к заданным условиям сигнал, чтобы предоставить выборки и дополнительно обрабатывает выборки для того, чтобы предоставить соответствующий «принятый» поток символов.

[0036] Затем процессор 260 RX (принятых) данных принимает и обрабатывает, принятые N R потоков символов от N R приемников 254, на основании конкретной технологии обработки приемника для того, чтобы предоставить «обнаруженные» N T потоков символов. Затем процессор 260 RX данных демодулирует, осуществляет обратное перемежение и декодирует каждый обнаруженный поток символов, для того чтобы восстановить данные трафика для потока данных. Обработка, выполняемая процессором 260 RX данных, является добавочной к той, что выполнена процессором 220 TX MIMO и процессором 214 TX данных в системе 210 передатчика.

[0037] Процессор 270 периодически определяет, какую матрицу предварительного кодирования использовать (обсуждается ниже). Процессор 270 формулирует сообщение обратной линии связи, содержащее часть индекса матрицы и часть значения ранга.

[0038] Сообщение обратной линии связи может содержать в себе различные типы информации относительно линии связи и/или принятого потока данных. Затем сообщение обратной линии связи обрабатывается процессором 238 TX данных, который также принимает данные трафика для некоторого количества потоков данных от источника 236 данных, подвергнутые модуляции модулятором 280, приведенные к заданным условиям передатчиками с 254a по 254r и переданные обратно системе 210 передатчика.

[0039] В системе 210 передатчика сигналы, подвергнутые модуляции от системы 250 приемника, принимаются антеннами 224, приводятся к заданным условиям приемниками 222, демодулируются демодулятором 240 и обрабатываются процессором 242 RX данных для того, чтобы извлечь сообщение обратной линии связи, переданное системой 250 приемника. Затем процессор 230 определяет, какую матрицу предварительного кодирования использовать для определения весовых коэффициентов формирования диаграммы направленности, и затем обрабатывает извлеченное сообщение.

[0040] Фиг.3 изображает примерную архитектуру 300 передачи. Как предложено на Фиг.3, пакет информации может быть разбит на некоторое число суб-пакетов {0, 1, 2, … t-1}, причем каждый суб-пакет, получая контрольную сумму 302 CRC, затем подвергается некоторому числу стандартных обработок, таким как кодированию 304, перемежению 306, повторению 308 последовательности и скремблированию 310. Затем полученные в результате обработки суб-пакеты могут быть объединены в большую архитектуру (описана далее ниже), затем модулированы 312 и переданы в соответствии со схемой OFDM и в соответствии с временной архитектурой кадров и супер-кадров, как той, что показана на Фиг.4

[0041] Фиг.4 изображает компоновку кадров, приспособленную для OFDM, показывая упорядочение пакета/суб-пакета для прямой и обратной линии связи. Упорядочение в верхней части Фиг.4 показывает серию суб-пакетов 402, 404 и 406, добавленную к Преамбуле 401 Супер-Кадра прямой линии связи. Для различных блоков в архитектуре кадра/супер-кадра сигналы OFDM и данные могут быть организованы в под-блоки, называемые в целях настоящего изобретения «фрагменты». Каждый из суб-пакетов будет иметь структуру фрагментов OFDM-на-Тон, подобную той, что показана на Фиг.5, причем один или более фрагментов ассоциированы с различными пользователями в секторе и/или сети. Суб-пакеты, содержащие данные трафика, будут вложены в данные Управления, которые используются для того, чтобы определить, где в суб-пакете размещены данные трафика, как впрочем и то, как много данных трафика находится в суб-пакете, и прочую соответствующую информацию. Так как данные трафика могут быть помещены в различные местоположения в фрагменте, необходимо прежде обработать данные Управления до попытки обрабатывать данные трафика. Принимая во внимание это требование, ниже рассматриваются примерные подходы для повышения пропускной способности.

[0042] Фиг.5 показывает пример сигнала OFDM разбитого на 128 фрагментов, причем каждый фрагмент состоит из 16 отдельных тонов (или суб-каналов) по 8-ми символам OFDM так, что каждый фрагмент может состоять из целых 128 символов. Формат Фиг.5 показывает физический уровень OFDM, который предоставляет трехмерную сетку с осями время-частота-пространство, которая может использоваться в соответствии с Режимом Скачкообразного изменения Блоков, где некоторые из этих фрагментов могут быть присвоены AT.

[0043] Как показано на Фиг.5, каждый из различных фрагментов может иметь как символы данных (обозначенные индексами A, B, C), так и символы пилот-сигнала (обозначенные X), причем символы данных используются для переноса информации, а символы пилот-сигнала используются для выполнения широкого многообразия задач, некоторые из которых могут быть объяснены далее ниже, причем отметим, что последовательность ортогонального пилот сигнала от Tx антенны AP может позволить оценить канал и помехи из расчета на уровень.

[0044] С другой стороны символы, не принадлежащие пилот-сигналу, могут быть заняты данными от нескольких суб-пакетов, причем символы из подмножества суб-пакетов «окрашены» в тона, не принадлежащие пилот-сигналу циклическим образом по одному или более фрагментам.

[0045] В зависимости от желаемого назначения фрагментов данным данные полезной нагрузки могут быть эффективно скомпонованы. Например, на Фиг.5, фрагмент 127 показан как назначенный, чтобы содержать три суб-пакета информации {A, B, C}, причем суб-пакет {A} содержит в себе символы данных (A0, A1, A2, A3, …), суб-пакет {B} содержит в себе символы данных (B0, B1, B2, B3, …), а суб-пакет {C} содержит в себе символы данных (C0, C1, C2, C3, …). Отметим, что различные символы совместно разбросаны в процессе/формате, который может именоваться как «окрашивание». Шаблоны окрашивания позволяют конвейерную обработку операций Демодулирования (Demod) и Декодирования (Decode) для различных суб-пакетов.

[0046] Фиг.6 изображает примерную архитектуру аппаратно реализованного приемника с поддерживающим процессором. Как показано на Фиг.6, две антенны ANT-0 601 и ANT-1 602 показаны как ведущие к аналоговому устройству 610 предварительной обработки, которое может выполнять различные процессы над принятыми сигналами, такие как буферизацию, фильтрацию, смешивание и аналого-цифровое преобразование, для того чтобы предоставить два потока оцифрованных данных цифровому устройству 622 предварительной обработки архитектуры аппаратного обеспечения 620 приемника. Отметим, что каждая антенна 601, 602 может принимать многочисленные сигналы от многочисленных AT, причем каждая AT имеет одну или более антенны и имеет возможности передачи по множеству каналов данных. Соответственно аналоговый входной каскад 610 и аппаратное обеспечение 620 приемника могут быть предназначены, чтобы обеспечивать любые и все такие принятые каналы.

[0047] Оцифрованные данные после того, как были приняты, обработаны и оцифрованы, могут быть обработаны в соответствии с некоторым числом требуемых процессов, таких как: коррекция сдвига постоянной составляющей, цифровая фильтрация, синфазно-квадратурная коррекция, частотная коррекция, цифровое управление усилением и т.д., в цифровом входном каскаде 622. Затем цифровой входной каскад 622 предварительной обработки может предоставить обработанные цифровым образом данные как два или более потока для сервера/механизма 624 выборок FFT (Быстрого Преобразования Фурье).

[0048] Сервер 624 выборок FFT может быть выполнен с возможностью буферизовать принятые данные от цифрового входного каскада 622 предварительной обработки, затем выполнять параллельные операции FFT над, по меньшей мере, двумя отдельными потоками, причем отметим, что каждый поток может быть обработан независимо друг от друга в такой степени, что могут быть независимыми размеры FFT и пост-FFT обработка, также может выполняться независимо, так что временные смещения и искажение в фильтре могут обрабатываться независимо. Например, если два параллельных потока данных приняты со смещением первого принятого потока в 1 микросекунду и смещением второго принятого потока в 5 микросекунд, то пост-FFT обработка может быть обеспечена таким образом, что каждое смешение правильно учитывается/корректируется. Отметим, что сервер 624 выборок FFT, подобно прочим различным модулям в аппаратном обеспечении 620 приемника, может динамически конфигурироваться под управлением процессора, обозначенного здесь как Модель QDSP6 640, который может быть любым видом машины последовательной обработки инструкций, выполняющей программное обеспечение/встроенное программное обеспечение, имеющее либо внутреннюю, либо внешнюю память (не показана). Следовательно, в соответствии с предпочтением исполнения могут использоваться процессоры, отличные от QDSP6 640. Объединенной с процессором 640 является необязательная память 645 для хранения данных/инструкций и т.д. В некоторых процессорах память 645 может быть внутри процессора, а не вне процессора.

[0049] Продолжая, скорректированные пост-FFT данные затем могут сохраняться в буфере 625 символов FFT, которые затем могут быть предоставлены механизму 626 Demod, который может выполнять любое число операций демодуляции, таких как операции c MMSE (Минимальная Среднеквадратическая Ошибка) или c MRC (Объединение с Максимальным Отношением), для того чтобы создать сдвоенные демодулированные выходные данные (независимые друг от друга), причем каждые выходные данные логически скомпонованы способом, согласующимся с фрагментами на Фиг.5. Отметим, что каждая точка входа каждого фрагмента может включать в себя три компонента, включая: реальную часть (I), составную часть (Q) и соответствующее SNR (отношение сигнала к шуму). Затем демодулированные данные могут сохраняться в Буфере 627 Фрагмента и могут быть далее обработаны Механизмом 628 Demap (Обратного Преобразования) и Механизмом 630 Decode (Декодирования), способами более полно рассматриваемыми ниже.

[0050] Примерный Механизм 628 Demap может быть разделен на четыре функциональных компонента, включающих в себя Механизм 628a логарифмического отношения правдоподобия (LLR), механизм 628b суб-пакетирования, дескремблер 628c и обратный перемежитель 628d. Вновь, как и в случае с ранее описанными модулями, Механизм 628 Demap может параллельно обрабатывать множество каналов.

[0051] Механизм 628a LLR может отвечать за формирование логарифмических отношений правдоподобия, которые могут выражать случайную информацию, необходимую/используемую декодером. В настоящем варианте осуществления LLR могут формироваться независимо для двух уровней в компоновках MIMO. Входные данные могут включать в себя данные I, Q, SNR - из расчета на уровень для каждого тона и Порядка Модуляции. Выходные данные могут включать в себя логарифмические отношения правдоподобия (LLR) для 2-битных данных в Квадратурной Фазовой Манипуляции (QPSK), 3-битные данные в Фазовой Манипуляции (8PSK), 4-битные данные в Квадратурной Амплитудной Модуляции (16 QAM) и/или 6-битные данные (64 QAM), как впрочем и для прочих доступных или применимых схем.

[0052] Механизм 628b суб-пакетизации может отвечать за преобразования данных OFDM, основанных на фрагментах, в данные, организованные как суб-пакеты. Дескремблер 628c может отвечать за дескремблирование данных суб-пакетов, а механизм 628d снятия перемежения может отвечать за сохранение данных в буфере 630a LLR Декодера 630 с минимальной вероятностью конфликта данных. Данные LLR затем могут передаваться Декодерам 630, показанным на Фиг.6. Отметим, что вопрос переноса всех данных, требуемых Декодерами 630, на Фиг.6 эффективным образом является нетривиальным.

[0053] Эта проблема лучше всего может быть проиллюстрирована Фиг.7A, которая, в общем, изображает пакет в передаче по прямой линии связи, который впервые рассматривался на Фиг.4. Здесь данные для пользователей A, B, C и D разделены на их суб-пакеты, имеющие данные 710 трафика, дополненные данными 715 управления. Приемники, используя подход, показанный на Фиг.6, обрабатывают пакеты/суб-пакеты для того, чтобы сформировать последовательность фрагментов для хранения в Буфере 740 Фрагментов, как показано на Фиг.7B. В примере Фиг.7B фрагменты пользователя A скомпонованы так, что первым фрагментом(ами) 720 являются данные управления для пользователя A, а последующие фрагменты 730 являются данными трафика для пользователя A. Подобным образом, будут скомпонованы и фрагменты пользователей B, C и D для того, чтобы содержать в себе первыми фрагменты данных управления, за которыми следуют фрагменты данных трафика (не показаны). Тем не менее, данные управления могут быть эффективно декодированы, используя декодер Витерби, а данные трафика могут быть эффективно декодированы, используя Турбо декодер. Следовательно, увеличение пропускной способности может быть получено посредством наличия отдельного декодера Витерби, в основном используемого для данных управления, и Турбо декодера, в основном используемого для данных трафика, которые могут персонально обрабатывать соответствующие части фрагментов для увеличения эффективности. Несмотря на то, что описанные здесь декодеры описаны как декодеры Витерби и Турбо, должно быть понятно, что могут использоваться прочие типы декодеров, например, декодер с Контролем Четности с Низкой Плотностью (LDPC) и т.д., в соответствии с предпочтением исполнения.

[0054] Если используются два декодера Витерби и два Турбо декодера, то возникает проблема исполнения архитектуры памяти, отвечающей одному или более следующих свойств: (1) Позволять 2 Механизмам Demap, 2 Турбо Декодера, 2 Декодера Витерби и одному DSP (Цифровой Сигнальный Процессор) процессору работать параллельно в архитектуре памяти. (2) Архитектура памяти должна обеспечивать DSP прозрачный доступ ко всей памяти во время работы прочих механизмов. (3) Каждый механизм Demap должен быть способен записывать вплоть до 6 LLR и считывать вплоть до 6 LLR за такт, параллельно и с минимальными конфликтами. Адреса LLR обратно перемежены в соответствии со способом PBRI (Pruned Bit Reversal Interleaving) (Перемежения с Усеченным Битовым Реверсированием). Пакетам DCH/ECI требуется вплоть до 6 параллельных доступов к LLR. Пакеты управления могут иметь вплоть до 2 параллельных доступов к LLR. (4) Для каждого из 2 Турбо Декодеров, каждого из 2 механизмов MAP должна существовать возможность производить выборку 2 наборов (U, V0, V0', V1, V1') за такт, с минимальными конфликтами в режиме 1/5 Скорости. Каждый механизм MAP должен иметь возможность производить выборку 2 наборов (U, V0, V0') за такт в режиме 1/3 Скорости. (5) Каждый из 2 Декодеров Витерби должен иметь возможность производить выборку 2 наборов (U, V0, V1) за такт с минимальными конфликтами. (6) Пакеты 1/3 и 1/5 Скорости для каждого из 8 Перемежения должны иметь возможность совместного существования в архитектуре памяти. (7) Архитектура памяти должна обеспечивать механизм задания приоритетов параллельным доступам в случае возникновения конфликта. (8) Архитектура памяти должна обеспечивать механизм, предотвращающий несанкционированный доступ ведущих элементов к сегментам, которые принадлежат другим ведущим элементам.

[0055] Несмотря на то, что вышеописанные свойства в целом охватывают непосредственно вопросы обработки в нисходящей линии связи, используя многочисленные механизмы, работающие независимо или параллельно, должно быть понятно, что в некоторых случаях различные одно или более свойств могут быть опущены или расширены в соответствии с замыслом реализации. Например, в некоторых вариантах осуществления может использоваться большее или меньшее число параллельных считываний/записей (например, операций), чем 6. Также, при необходимости, для увеличения пропускной способности могут быть реализованы предварительная выборка и конвейерная обработка данных. Соответственно понятно, что разновидности и изменения предоставленных выше «свойств» находятся в рамках знаний специалиста в области техники и, следовательно, могут быть сделаны, не отступая от сущности этого изобретения.

[0056] Как будет показано ниже, признаки настоящего подхода включают в себя: (1) Он отвечает ранее упомянутым свойствам. (2) Однородная архитектура предоставляет возможность присвоения 6 ведущих интерфейсов любой комбинации Блоков Обратного Преобразования, Турбо Декодеров и Декодеров Витерби. Подход включает в себя высокоуровневое разрешение конфликтов, правильное выделение банков памяти, высокоуровневое разрешение конфликтов и мультиплексирование для различных ведущих элементов.

[0057] Ссылаясь на Буфер 810 LLR на Фиг.8, вся память логически разбита на 8 сегментов памяти для обслуживания 6 ведущих элементов, включая два механизма 802, 804 обратного преобразования слева и четыре декодера 820, 822, 830, 832 справа. Буфер 810 LLR может быть многосегментированной, высокопараллельной памятью с разрешением конфликтов, который может обрабатывать запросы для различных частей своей памяти.

[0058] Во время функционирования каждый ведущий элемент может получать управление над одним из 8 сегментов через первый уровень разрешения конфликтов, названный в этом изобретении частью «высокоуровневого разрешения конфликтов».

[0059] Как только ведущий элемент получил управление над сегментом, он может управлять вплоть до 6 каналами записи и 6 каналами чтения параллельно в отношении этого сегмента. Такой ведущий элемент может быть выполняющим операции Demap, Турбо Декодирования или Декодирования Витерби.

[0060] Каждый сегмент разбит внутри на некоторое число банков памяти (например, C11, C12, C21, C22, D11, D12, D21, D22) для того, чтобы поддерживать доступ LLR с нулевым конфликтом, когда механизмы 802, 804 Demap получают доступ к LLR в соответствии с различными способами PBRI. Отметим, что 6 каналов записи и 6 каналов чтения являются каналами с внутренним разрешением конфликтов в случае, когда один или более ведущих элементов пытаются получить доступ к некоторой части памяти, используя шаблон, отличный от PBRI.

[0061] Для того чтобы добиться нулевого конфликта при параллельной работе 6 каналов, выделение банков памяти основано на определенных свойствах PBRI алгоритма. Структура памяти также может обеспечивать сигнал ожидание в том же цикле для упрощения исполнения интерфейса для каждого из ведущих элементов. Высокоуровневое разрешение конфликтов может предотвратить получение доступа различными ведущими элементами к сегменту памяти, который в текущий момент находится под управлением другого ведущего элемента. Отметим, что высокоуровневое разрешение конфликтов может быть программируемым в жестком режиме, что может обеспечить порядок, в котором ведущие элементы получают доступ к сегменту памяти. Разрешение конфликтов может управляться посредством Списка(ов) 806, 808 Задач DDE (Динамического Обмена Данных).

[0062] Для того чтобы избежать ненужных операций чтения-изменения-записи, каждый канал записи для каждого ведущего элемента может быть обеспечен сигналом управления записью на каждый LLR. Эта особенность значительно упрощает исполнение.

[0063] Должно быть принято во внимание, что для различных стандартов телекоммуникации, таких как UMB (Ультрамобильный Широкополосный Доступ), не все LLR для заданного суб-пакета будут приняты внутри той же передачи. Отсюда, до того как суб-пакет может быть доставлен декодерам, все значения LLR, которые не были приняты для этого суб-пакета, должны быть обнулены.

[0064] Обычный способ очистки этих LLR, которые еще не были приняты, состоит в продолжении заполнения нулями LLR одного за другим. Этот способ требует затраты времени и усложняет аппаратное обеспечение.

[0065] В противоположность, настоящее изобретение предоставляет быстрый способ очистки всех значений LLR, который сокращает число циклов HW (Аппаратного Обеспечения). Этот подход основывается на структуре Буфера 810 LLR, описанной выше, посредством чего возможны 6 параллельных записей одним из механизмов 802, 804 блока обратного преобразования, как, впрочем, и на общей, основанной на задачах (806, 808) структуре переноса данных.

[0066] То есть посредством размещения выделенного «Устройства Очистки LLR» 803, 805 в одном или обоих обратных преобразователях 802, 804, устройство 803, 805 Очистки LLR может использовать для Буфера 810 LLR все доступные 6 каналов для того, чтобы обнулять ячейки LLR за минимальное время. Эта структура Буфера 810 LLR позволяет производить очистку LLR для более чем одного суб-пакета за раз, что, в свою очередь, может в дальнейшем сократить временную линию обработки.

[0067] Во время функционирования должно быть принято во внимание, что устройство 803, 805 Очистки LLR может работать в конкретной памяти в Буфере 810 LLR в те периоды времени, когда его соответствующий Обратный Преобразователь 802, 804 не обращается к памяти.

[0068] Как должно быть видно из этого изобретения, увеличение пропускной способности по нисходящей линии связи становится возможным посредством разделения различных фрагментов в Буфере 627 Фрагментов для различных Обратных Преобразователей 802, 804. При множестве Обратных Преобразователей 802, 804, работающих с различными фрагментами, результаты от множества Обратных Преобразователей 802, 804 могут сохраняться/записываться в выбранные области памяти примерного Буфера 810 LLR и в дальнейшем обрабатываться множеством Декодеров 820, 822, 830, 832 посредством соответствующего разрешения конфликтов и выбора областей памяти Буфера 810 LLR. Посредством «разъединения» данных управления и данных трафика Множество Обратных Преобразователей 802, 804 и Декодеры 820, 822, 830, 832 могут, когда требуется, эффективно использоваться в параллельном виде. Соответствующим образом обрабатывая информацию нисходящей линии связи и используя многочисленные потоки обработки, может быть достигнут значительный прирост для операций по нисходящей линии связи.

[0069] Фиг.9 изображает одну возможную конфигурацию для инструктирования, описанному выше аппаратному обеспечению для того, чтобы выполнить описанные процессы, используя, в качестве одного примера, инструкции программного обеспечения, закодированные на носителе данных. Фиг.9 показывает антенну(ы) 105 на точке 100 доступа, которая передает и принимает данные от терминалов 116, 122 доступа по беспроводным нисходящим линиям 120, 126 связи и беспроводным восходящим линиям 118, 124 связи. Программное обеспечение 910, содержащее в себе инструкции для описанных выше процессов, может быть загружено или встроено как частично, так и полностью в точку 100 доступа, терминалы 116, 122 доступа, компьютер 920 и/или сеть 930 (то есть подсоединено к точке 100 доступа через канал(ы) 925 связи), используя любую из линий 915 связи для того, чтобы добраться до терминалов 116, 122 доступа. Инструкции программного обеспечения также могут быть закодированы в памяти, размещенной в терминалах 116, 122 доступа, такой как возможная память RAM, ROM, программируемая память или любой доступный механизм для кодирования инструкций для использования процессором.

[0070] Различные описанные здесь способы и системы могут быть применимы к LTE, UMB и прочим протоколам, которые требуют обратного преобразования и декодирования сигнала нисходящей линии связи.

[0071] Понятно, что конкретный порядок или иерархия этапов в раскрытых процессах является примером типичного подхода. Понятно, что на основании предпочтений исполнения конкретный порядок или иерархия этапов в процессах могут быть трансформированы, оставаясь при этом в объеме настоящего изобретения. Сопровождающая способ формула изобретения представляет элементы различных этапов в простом порядке и не намерена ограничиваться конкретным представленным порядком или иерархией.

[0072] Специалист в соответствующей области должен понимать, что информация и сигналы могут быть представлены, используя любую из разнообразия различных технологий и способов. Например, данные, инструкции, команды, информация, сигналы, биты, символы и элементарные сигналы, которые могли быть упомянуты на протяжении описания выше, могут быть представлены напряжениями, токами, электромагнитными волнами, магнитными полями или частицами, оптическими полями или частицами, или любыми их сочетанием.

[0073] Специалист в соответствующей области дополнительно должен принимать во внимание, что различные иллюстративные логические блоки, модули, схемы и этапы алгоритма, описанные здесь применительно к раскрытым здесь вариантам осуществления, могут быть реализованы как электронное аппаратное обеспечение, компьютерное программное обеспечение или их сочетания. Для того чтобы однозначно проиллюстрировать эту взаимозаменяемость аппаратного и программного обеспечения, различные иллюстративные компоненты, блоки, модули, схемы и этапы, в целом, были описаны выше, в основном в терминах их функциональных возможностей. Будут ли такие функциональные возможности реализованы в аппаратном или программном обеспечении, зависит от конкретного приложения и ограничений исполнения, наложенных на всю систему. Специалисты могут реализовать описанные функциональные возможности различными способами для каждого конкретного приложения, но такие решения реализации не должны интерпретироваться как вызывающие отступление от объема настоящего изобретения.

[0074] Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми здесь вариантами осуществления, могут быть реализованы или выполнены универсальным процессором, цифровым сигнальным процессором (DSP), специализированной интегральной микросхемой (ASIC), программируемой вентильной матрицей (FPGA) или другим программируемым логическим устройством, схемой на дискретных компонентах или транзисторной логикой, дискретными компонентами аппаратного обеспечения или любыми их сочетаниями, разработанными для выполнения, описанных здесь функций. Процессор общего назначения может быть микропроцессором, но в качестве альтернативы процессор может быть любым обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован как комбинация вычислительных устройств, например комбинация DSP и микропроцессора, множество микропроцессоров, один или более микропроцессор, объединенные с ядром DSP, или любое подобное сочетание.

[0075] Этапы способа или алгоритм, описанные в отношении раскрытых здесь вариантов осуществления, могут быть реализованы непосредственно в аппаратном обеспечении, модуле программного обеспечения, выполняемом процессором или сочетанием двух. Модуль программного обеспечения может размещаться в памяти RAM, флэш-памяти, памяти ROM, памяти EPROM, памяти EEPROM, регистрах, жестком диске, съемном диске, CD-ROM или любом другом виде носителя данных известного в данной области техники. Типичный носитель данных соединен с процессором таким образом, чтобы процессор мог считывать информацию с и записывать информацию на носитель данных. В качестве альтернативы носитель данных может быть интегрирован с процессором. Процессор и носитель данных могут размещаться в ASIC. ASIC может размещаться в терминале доступа. В качестве альтернативы процессор и носитель данных могут размещаться в терминале доступа как отдельные компоненты.

[0076] Предшествующее описание раскрытых вариантов осуществления предоставлено для того, чтобы позволить любому специалисту в соответствующей области реализовать или использовать настоящее изобретение. Различные модификации этих вариантов осуществления будут очевидны специалисту в соответствующей области техники, а определенные здесь основные принципы могут быть применены к другим вариантам осуществления, не отступая от сущности и объема изобретения. Таким образом, настоящее изобретение не предназначено ограничиваться показанными здесь вариантами осуществления, а должно соответствовать самому широкому объему, совместимому с раскрытыми здесь принципами и признаками новизны.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТУРБО-ПЕРЕМЕЖИТЕЛЬ ДЛЯ ВЫСОКИХ СКОРОСТЕЙ ПЕРЕДАЧИ ДАННЫХ | 2007 |

|

RU2435298C2 |

| ПРОВЕРКА ПРАВИЛЬНОСТИ ОБНАРУЖЕНИЯ ПОДТВЕРЖДЕНИЯ ПРИЕМА ПО СХЕМЕ Н-АRQ ПОСРЕДСТВОМ КОМБИНИРОВАНИЯ ДАННЫХ И ПОВТОРНОГО ДЕКОДИРОВАНИЯ | 2008 |

|

RU2477004C2 |

| ОТОБРАЖЕНИЕ ПОДПАКЕТОВ В РЕСУРСЫ В СИСТЕМЕ СВЯЗИ | 2008 |

|

RU2427965C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБЕСПЕЧЕНИЯ КАСКАДНЫХ КОДОВ ДЛЯ КАНАЛОВ РАДИОМАЯКА | 2009 |

|

RU2444138C1 |

| ПОДАВЛЕНИЕ ПОМЕХ В ТРАФИКЕ | 2005 |

|

RU2369964C2 |

| ОЦЕНКА КАНАЛА ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ | 2005 |

|

RU2364023C2 |

| СПОСОБ ВЫБОРА ДЕМОДУЛЯТОРА MIMO-OFDM В ЗАВИСИМОСТИ ОТ ФОРМАТА ПАКЕТА | 2007 |

|

RU2419993C2 |

| СТРУКТУРА ПЕРЕМЕЖЕНИЯ КАНАЛОВ ДЛЯ СИСТЕМЫ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2446589C2 |

| СТРУКТУРА ПЕРЕДАЧИ, ПОДДЕРЖИВАЮЩАЯ МНОГОПОЛЬЗОВАТЕЛЬСКОЕ ПЛАНИРОВАНИЕ И MIMO ПЕРЕДАЧУ | 2008 |

|

RU2454798C2 |

| АДАПТАЦИЯ ПРИРОСТА ПОДКАНАЛА ПЕРЕДАЧИ В СИСТЕМЕ С НЕЙТРАЛИЗАЦИЕЙ ВЗАИМНОЙ ПОМЕХИ | 2005 |

|

RU2373646C2 |

Изобретение относится к системам беспроводной связи, более конкретно к системам и способам улучшения обработки информации в нисходящей линии связи. Описаны устройство и способ для обработки в нисходящей линии связи принятых каналов в системе мобильной связи, которые содержат буфер для данных управления и данных графика, механизм блока обратного преобразования с, по меньшей мере, двумя работающими независимо блоками обратного преобразования для обратного преобразования данных управления и графика, буфер логарифмического отношения правдоподобия (LLR) для поддержки сегментов памяти доступных посредством механизма блока обратного преобразования, механизм декодера, содержащий в себе декодеры, причем каждый из декодеров работает с данными из выбранного сегмента(ов) памяти буфера LLR, и схему разрешения конфликтов, обеспечивающую управление, по меньшей мере, одним из: механизм блока обратного преобразования, буфер LLR и механизм декодера. По меньшей мере, один из декодеров приспособлен для декодирования данных управления и другой один из декодеров приспособлен для декодирования данных трафика. Технический результат - обеспечение увеличения пропускной способности нисходящей линии связи. 5 н. и 42 з.п. ф-лы, 9 ил.

1. Устройство для улучшенной обработки принятых каналов в нисходящей линии связи в системе мобильной связи, причем устройство содержит:

буфер, выполненный с возможностью содержать, по меньшей мере, демодулированные данные управления и демодулированные данные трафика;

механизм блока обратного преобразования, содержащий, по меньшей мере, два блока обратного преобразования, выполненные с возможностью независимо работать с, по меньшей мере, данными управления и данными трафика из буфера;

буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти, доступных посредством механизма блока обратного преобразования;

механизм декодера, содержащий множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и

схему разрешения конфликтов, обеспечивающую управление, по меньшей мере, одним из: механизма блока обратного преобразования, буфера LLR и механизма декодера,

причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика.

2. Устройство по п.1, в котором демодулированные данные управления и данные трафика хранятся в буфере как OFDM-отформатированные фрагменты.

3. Устройство по п.1, в котором механизм блока обратного преобразования содержит, по меньшей мере, одно из: механизма LLR, механизма дескремблера и механизма обратного перемежителя.

4. Устройство по п.1, в котором, по меньшей мере, один из множества декодеров является отличного типа от, по меньшей мере, другого одного из множества декодеров.

5. Устройство по п.4, в котором, по меньшей мере, один из множества декодеров является декодером Витерби.

6. Устройство по п.1, причем сегменты памяти в буфере LLR назначены в качестве сегментов управления и сегментов трафика.

7. Устройство по п.1, в котором схема разрешения конфликтов содержит список задач для назначения задач управления, по меньшей мере, одному из: механизма блока обратного преобразования, буфера LLR и механизма декодера.

8. Устройство по п.1, в котором схема разрешения конфликтов обеспечивает управление элементами, по меньшей мере, одного из:

механизма блока обратного преобразователя, буфера LLR и механизма декодера в конфигурации ведущий-ведомый.

9. Устройство по п.8, в котором ведущий элемент может управлять доступом к сегментам памяти буфера LLR.

10. Устройство по п.8, в котором может существовать вплоть до 6 отличных ведущих элементов.

11. Устройство по п.8, в котором ведущий элемент может управлять, по меньшей мере, одной операцией из: обратного преобразования, турбо декодирования и декодирования Витерби.

12. Устройство по п.1, в котором запись и чтение в сегментах памяти может производиться параллельно.

13. Устройство по п.1, в котором один из, по меньшей мере, двух блоков обратного преобразования содержит устройство очистки LLR, которое может очищать назначенную память в буфере LLR, используя множество каналов с доступом к памяти, работающих параллельно.

14. Устройство по п.1, в котором один из, по меньшей мере, двух блоков обратного преобразования работает с данными, подвергнутыми Квадратурной Фазовой Манипуляции, а другой из, по меньшей мере, двух блоков обратного преобразования работает с данными, подвергнутыми Квадратурной Амплитудной Модуляции.

15. Способ для улучшенной обработки принятых каналов в нисходящей линии связи в системе мобильной связи, при этом способ содержит этапы, на которых:

в буфер вводят демодулированные данные управления и демодулированные данные трафика;

обратно преобразуют данные управления и данные трафика из буфера, используя, по меньшей мере, два блока обратного преобразования, выполненные с возможностью работать независимо;

загружают данные, подвергнутые обратному преобразованию, в буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти;

декодируют данные в буфере LLR, используя множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и

управляют работой, по меньшей мере, одного из: обратного преобразования, поддерживающего множество сегментов памяти, и декодирования,

причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика.

16. Способ по п.15, в котором демодулированные данные управления и данные трафика хранятся в буфере как OFDM-отформатированные фрагменты.

17. Способ по п.15, в котором, по меньшей мере, один из множества декодеров является отличного типа от, по меньшей мере, другого одного из множества декодеров.

18. Способ по п.15, в котором сегменты памяти в буфере LLR загружены как сегменты управления и сегменты трафика.

19. Способ по п.15, в котором управление основано на задачах, представленных в списке задач.

20. Способ по п.15, в котором управление имеет схему разрешения конфликтов в соответствии с конфигурацией ведущий-ведомый.

21. Способ по п.20, в котором ведущий элемент управляет доступом к сегментам памяти буфера LLR.

22. Способ по п.20, в котором в управлении может быть вплоть до 6 отличных ведущих элементов.

23. Способ по п.20, в котором ведущий элемент может управлять, по меньшей мере, одним из: обратного преобразования и декодирования.

24. Способ по п.15, в котором загрузка выполняется параллельно.

25. Способ по п.15, причем загрузка включает в себя операцию очистки LLR, которая очищает назначенную память в буфере LLR, используя множество каналов с доступом к памяти, работающих параллельно.

26. Способ по п.15, в котором один из, по меньшей мере, двух блоков обратного преобразования работает с данными, подвергнутыми Квадратурной Фазовой Манипуляции, а другой из, по меньшей мере, двух блоков обратного преобразования работает с данными, подвергнутыми Квадратурной Амплитудной Модуляции.

27. Устройство для улучшенной обработки принятых каналов в нисходящей линии связи в системе мобильной связи, причем устройство содержит:

средство для хранения, по меньшей мере, демодулированных данных управления и демодулированных данных трафика;

множество средств для независимого обратного преобразования данных управления и данных трафика из средства для хранения;

средство для хранения логарифмического отношения правдоподобия (LLR), выполненное с возможностью поддержки множества сегментов памяти, доступных посредством множества средств для независимого обратного преобразования;

множество средств для декодирования, работающих с данными из выбранного сегмента памяти средства для хранения LLR; и

средство для обеспечения управления, по меньшей мере, одним из: множества средств для обратного преобразования, средства для хранения LLR и множества средств для декодирования,

причем, по меньшей мере, одно из множества средств для декодирования приспособлено для декодирования данных управления и, по меньшей мере, другое одно из множества средств для декодирования приспособлено для декодирования данных трафика.

28. Устройство по п.27, в котором демодулированные данные управления и данные трафика хранятся в средстве для хранения как OFDM-отформатированные фрагменты.

29. Устройство по п.27, в котором средство для обеспечения управления содержит список задач для назначения задач управления, по меньшей мере, одному из: множеству средств обратного преобразования, средству для хранения LLR и множеству средств декодирования.

30. Устройство по п.27, в котором одно из множества средств для обратного преобразования содержит средство для очистки назначенной памяти в средстве для хранения LLR, используя множество каналов с доступом к памяти, работающих параллельно.

31. Носитель данных, содержащий реализуемые компьютером инструкции, которые при выполнении компьютером вынуждают компьютер выполнять способ, содержащий:

ввод в буфер демодулированных данных управления и демодулированных данных трафика;

обратное преобразование данных управления и данных трафика из буфера, используя, по меньшей мере, два блока обратного преобразования, выполненные с возможностью работать независимо;

загрузку данных, подвергнутых обратному преобразованию, в буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти;

декодирование данных в буфере LLR, используя множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и

управление работой, по меньшей мере, одного из: обратного преобразования, доступа к буферу LLR и декодирования,

причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика.

32. Носитель данных по п.31, в котором демодулированные данные управления и данные трафика вводятся в буфер как OFDM-отформатированные фрагменты.

33. Носитель данных по п.31, в котором, по меньшей мере, один из множества декодеров является отличного типа от, по меньшей мере, другого одного из множества декодеров.

34. Носитель данных по п.31, в котором сегменты памяти в буфере LLR загружаются как сегменты управления и сегменты трафика.

35. Носитель данных по п.31, в котором управление основано на задачах, представленных в списке задач.

36. Носитель данных по п.31, в котором управление осуществляется в соответствии с конфигурацией ведущий-ведомый.

37. Носитель данных по п.36, в котором ведущий элемент управляет доступом к сегментам памяти буфера LLR.

38. Носитель данных по п.36, в котором в управлении может быть вплоть до 6 отличных ведущих элементов.

39. Носитель данных по п.36, в котором ведущий элемент может управлять, по меньшей мере, одним из: обратного преобразования и декодирования.

40. Носитель данных по п.31, в котором загрузка выполняется параллельно.

41. Носитель данных по п.31, в котором загрузка включает в себя операцию очистки LLR, которая очищает назначенную память в буфере LLR, используя множество каналов с доступом к памяти, работающих параллельно.

42. Носитель данных по п.31, в котором один из, по меньшей мере, двух блоков обратного преобразования работает с данными, подвергнутыми Квадратурной Фазовой Манипуляции, а другой из, по меньшей мере, двух блоков обратного преобразования работает с данными, подвергнутыми Квадратурной Амплитудной Модуляции.

43. Устройство для улучшенной обработки в нисходящей линии связи принятых каналов в системе мобильной связи, причем устройство содержит:

процессор, выполненный с возможностью управлять работой по:

вводу в буфер демодулированных данных управления и демодулированных данных трафика;

обратному преобразованию данных управления и данных трафика из буфера, используя, по меньшей мере, два блока обратного преобразования, выполненные с возможностью работать независимо;

загрузке данных, подвергнутых обратному преобразованию в буфер логарифмического отношения правдоподобия (LLR), выполненный с возможностью поддержки множества сегментов памяти;

декодированию данных в буфере LLR, используя множество декодеров, причем каждый из множества декодеров работает с данными из выбранного сегмента памяти буфера LLR; и

управлению работой, по меньшей мере, одного из: обратного преобразования, доступа к буферу LLR и декодирования,

причем, по меньшей мере, один из множества декодеров приспособлен для декодирования данных управления и, по меньшей мере, другой один из множества декодеров приспособлен для декодирования данных трафика; и

память, соединенную с процессором для хранения данных.

44. Устройство по п.43, в котором демодулированные данные управления и данные трафика хранятся в буфере как OFDM-отформатированные фрагменты.

45. Устройство по п.43, в котором управление основано на задачах, представленных в списке задач.

46. Устройство по п.43, в котором управление осуществляется в соответствии с конфигурацией ведущий-ведомый.

47. Устройство по п.43, в котором загрузка включает в себя операцию очистки LLR, которая очищает назначенную память в буфере LLR, используя множество каналов с доступом к памяти, работающих параллельно.

| US 6947501 B2, 20.09.2005 | |||

| WO 2008014473 A2, 31.01.2008 | |||

| RU 2006111472 A, 27.10.2007 | |||

| US 2007011593 A1, 11.01.2007. |

Авторы

Даты

2012-09-10—Публикация

2009-03-28—Подача