Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству отображения, в котором напряжения на накопительных конденсаторах подают в линии шин запоминающих конденсаторов через соответствующее множество магистральных линий CS.

Уровень техники

Жидкокристаллическое устройство отображения с использованием многопиксельного управления является примером жидкокристаллического устройства отображения, лучше справляющегося с проблемой зависимости γ-характеристики от угла обзора. В соответствии с многопиксельным управлением каждый пиксел выполнен из двух или более субпикселов различной яркости. Такой подход позволяет лучше справляться с проблемой зависимости характеристики угла обзора, т.е. γ-характеристики, от угла обзора.

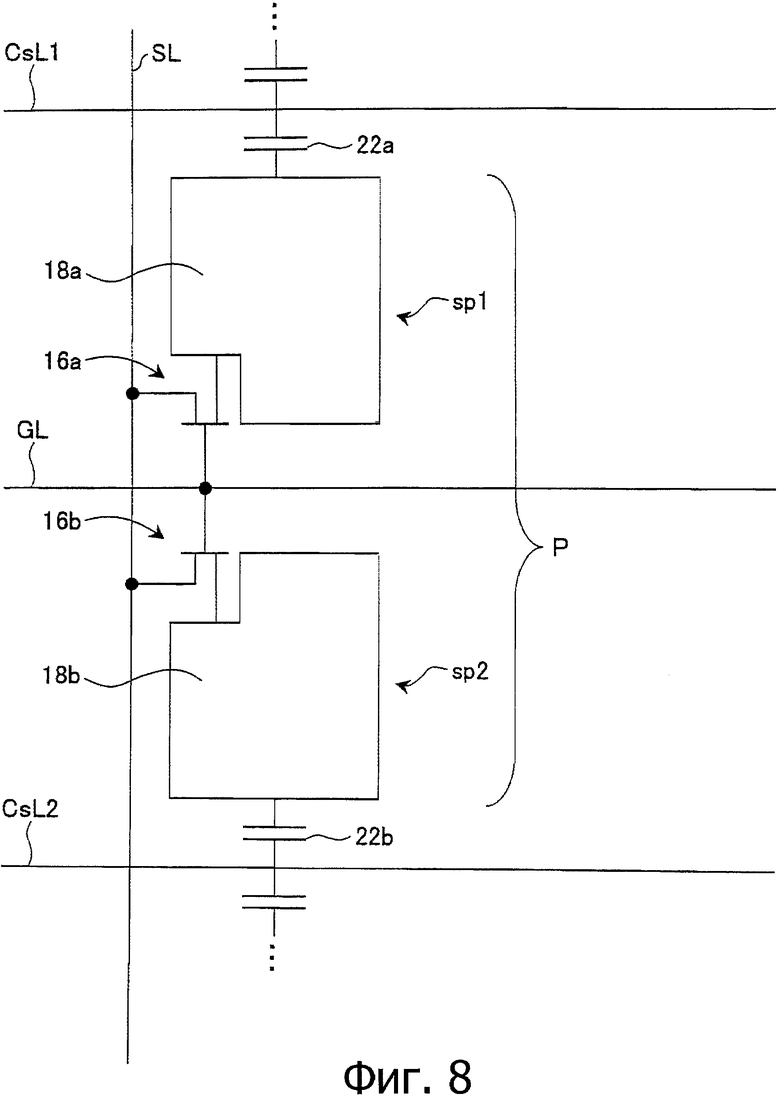

На фиг.8 показан пример конфигурации пиксела в жидкокристаллическом дисплее, использующем многопиксельное управление (см., например, Патентную литературу 1).

Пиксел Р разделен на два субпиксела sp1 и sp2. Субпиксел sp1 включает тонкопленочный транзистор (TFT) 16а, электрод 18а субпиксела и запоминающую емкость 22а. Субпиксел sp2 включает транзистор TFT 16b, электрод 18b субпиксела и запоминающую емкость 22b.

Транзисторы TFT 16а и 16b имеют: соответствующие электроды затворов, соединенные оба с общей шиной GL затворов, и соответствующие электроды истоков, соединенные оба с общей шиной SL истоков. Запоминающая емкость 22а образована между электродом 18а субпиксела и шиной CsL1 запоминающих конденсаторов. Запоминающая емкость 22b образована между электродом 18b субпиксела и шиной CsL2 запоминающих конденсаторов. Шина CsL1 запоминающих конденсаторов проходит параллельно шине GL затворов, будучи отделена от шины GL субпикселом sp1. Шина CsL2 запоминающих конденсаторов проходит параллельно шине GL затворов, будучи отделена от шины GL субпикселом sp2.

Шина CsL1 запоминающих конденсаторов пиксела Р служит также шиной CsL2 запоминающих конденсаторов соседнего пиксела Р, расположенного рядом с рассматриваемым пикселом Р через шину CsL1 запоминающих конденсаторов, так что субпиксел sp2 соседнего пиксела Р образует запоминающую емкость 22b с шиной CsL1 запоминающих конденсаторов. С другой стороны, шина CsL2 запоминающих конденсаторов пиксела Р служит также шиной CsL1 запоминающих конденсаторов соседнего пиксела Р, расположенного рядом с рассматриваемым пикселом Р через шину CsL2 запоминающих конденсаторов, так что субпиксел sp1 соседнего пиксела Р образует запоминающую емкость 22а с шиной CsL2 запоминающих конденсаторов.

В дальнейшем описании рассмотрен со ссылками на фиг.9 и 10 способ управления шинами CsL1 и CsL2 запоминающих конденсаторов в панели отображения с многопиксельным управлением.

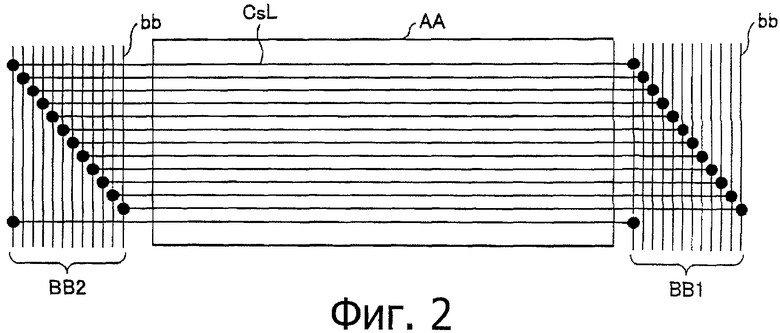

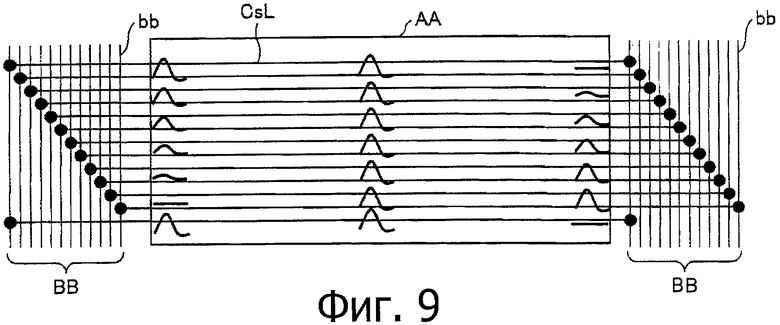

Как показано на фиг.9, шины CsL (шины CsL1 и CsL2 запоминающих конденсаторов совместно именуются шинами CsL запоминающих конденсаторов), запоминающих конденсаторов, расположенные поочередно в активной области АА, представляющей собой область отображения, соединены с соответствующими магистральными CS-линиями bb, расположенными в области, прилегающей к активной области АА. Магистральные CS-линии bb составляют группу BB магистральных CS-линий. Эта группа BB магистральных CS-линий расположена в области, граничащей с одним концом, т.е. с данным концом, активной области АА в направлении, в котором проходят шины CsL запоминающих конденсаторов. В альтернативном варианте группы BB магистральных CS-линий могут быть расположены в соответствующих областях, одна из которых граничит с одним концом, т.е. данным концом, активной области АА в направлении, в котором проходят шины CsL запоминающих конденсаторов, а другая группа граничит с другим концом активной области АА в этом направлении.

Если группа BB магистральных CS-линий создана только в области, граничащей с одним концом активной области АА, шины CsL запоминающих конденсаторов соединены только одним концом с соответствующими магистральными CS-линиями bb. С другой стороны, если группы BB магистральных CS-линий расположены в соответствующих областях, граничащих с концами активной области АА, шины CsL запоминающих конденсаторов имеют (i) первые концы, соединенные с соответствующими магистральными CS-линиями bb, расположенными в области, граничащей с данным концом активной области АА, и (ii) вторые концы, соединенные с соответствующими магистральными CS-линиями bb, расположенными в области, граничащей с другим концом активной области АА. Магистральные CS-линии bb проходят в одном направлении, а именно в направлении, в котором проходят шины SL истоков и которое перпендикулярно направлению шин CsL1 и CsL2 запоминающих конденсаторов.

На фиг.9 показан пример, когда в соответствующих областях созданы группы BB магистральных CS-линий, каждая из которых составлена из двенадцати магистральных CS-линий bb. Шина CsL запоминающих конденсаторов соединена с одной из магистральных CS-линий bb в каждой группе BB магистральных CS-линий. Двенадцать (что равно числу n (n четное число) магистральных CS-линий bb в каждой группе BB магистральных CS-линий) шин CsL запоминающих конденсаторов, выполненных последовательно, соединены с соответствующими различными магистральными CS-линиями bb в каждой группе BB магистральных CS-линий, причем такой характер соединения сохраняется для каждой группы из двенадцати (т.е. по числу n) шин запоминающих конденсаторов.

Если группа BB магистральных CS-линий расположена только в области, граничащей с одним концом активной области АА, n шин CsL запоминающих конденсаторов, выполненных последовательно, соединены с соответствующими различными магистральными CS-линиями bb в этой группе BB магистральных CS-линий, причем такой характер соединения сохраняется для каждой группы из n линий шин запоминающих конденсаторов.

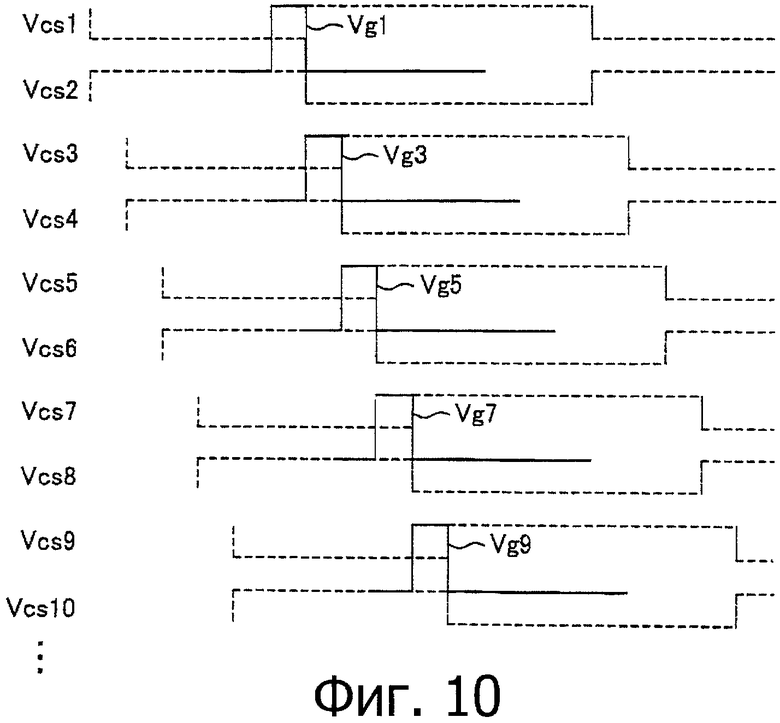

В обоих случаях, и когда группа BB магистральных CS-линий расположена только в области, граничащей с одним концом активной области АА, и когда группы BB магистральных CS-линий расположены в соответствующих областях, граничащих с одним и с другим концами активной области АА, в соответствующие n линий CsL шин запоминающих конденсаторов, расположенных последовательно, подают напряжения Vcs запоминающих конденсаторов, как показано на фиг.10 (на фиг.10 напряжения Vsc1, Vcs2 и т.д.). Те из этих напряжений Vcs запоминающих конденсаторов (на фиг.10, Vcs1, Vcs2 и т.д.), которые подают в соответствующие субпикселы sp1 и sp2 каждого пиксела Р в нечетной строке через шины CsL1 и CsL2 запоминающих конденсаторов, имеют соответствующие двоичные формы и изменяются в одни и те же моменты времени и с одинаковыми периодами, но в разных диапазонах. Совокупность напряжений Vcs запоминающих конденсаторов включает в себя n/2 пар напряжений Vcs запоминающих конденсаторов, так что эти n/2 пар напряжений Vcs запоминающих конденсаторов поступают в соответствующие нечетные строки пикселов Р. Указанные n/2 пар напряжений Vcs для запоминающих конденсаторов, которые нужно подать в соответствующие нечетные строки пикселов Р, устанавливают с постепенным сдвигом по фазе одно от другого. В каждой нечетной строке пикселов Р импульс Vg (на фиг.10, Vg1, Vg3 и т.д.), поступающий на затвор, имеет период в пределах данного периода соответствующей одной из n/2 пар напряжений Vcs для запоминающих конденсаторов. Период импульса оканчивается в момент, когда соответствующая одна из n/2 пар напряжений Vcs для запоминающих конденсаторов растет или падает.

В результате происходит запись сигналов данных сначала в нечетные строки пикселов Р. После того как произойдет запись этих сигналов данных, напряжения Vcs запоминающих конденсаторов изменяются таким образом, что различные величины ΔV электрических потенциалов (i) поступают к субпикселам sp1 и sp2 пиксела Р, которые получают идентичный сигнал данных, и (ii) добавляются к соответствующим электрическим потенциалам электродов пикселов в субпикселах sp1 и sp2. Это приводит к изменению яркостей субпикселов sp1 и sp2 друг относительно друга. Средняя яркость, обусловленная реальными величинами напряжений, поступающих на жидкие кристаллы в течение одного периода кадра, в результате влияния напряжений Vcs для запоминающих кадров, делает γ-характеристики полных пикселов Р приемлемыми в широком диапазоне углов взгляда.

После завершения сканирования нечетных строк пикселов Р сканируют четные строки пикселов Р. Однако в отличие от случая сканирования нечетных строк пикселов Р в паре напряжений на запоминающих конденсаторах, которые должны быть поданы на соответствующие субпикселы sp1 и sp2 одного и того же пиксела Р, не происходит одновременного изменения уровней этих напряжений. Тем не менее, первые изменения электрических потенциалов электродов пикселов, которые должны происходить по окончании периода импульса на затворе, совпадают с изменениями, получаемыми при сканировании нечетных строк пикселов Р. Таким образом, по-прежнему можно улучшить γ-характеристику.

Главным техническим результатом настоящего изобретения является улучшение γ-характеристик полных пикселов Р путем использования изменений соответствующих различных напряжений Vcs запоминающих конденсаторах для варьирования яркостей субпикселов sp1 и sp2 в пикселах Р.

Напряжения Vcs для запоминающих конденсаторов поступают по соответствующим магистральным CS-линиям bb. Таким образом, схема организована так, что различные напряжения Vcs для запоминающих конденсаторов приходят по соответствующим магистральным CS-линиям bb из группы магистральных CS-линий. Для достижения этого задающая схема CS (не показана) подает в соответствующую группу магистральных CS-линий напряжения для запоминающих конденсаторов, число фаз которых равно числу магистральных CS-линий bb. На фиг.10 показан пример, в котором задающая схема CS передает напряжения для запоминающих конденсаторов, имеющие 12 фаз. В случае, когда группы магистральных CS-линий созданы на обоих концах активной области АА, как показано на фиг.10, идентичные напряжения Vcs для запоминающих конденсаторов поступают через две магистральные CS-линии bb в соответствующих группах магистральных CS-линий, так что эти две магистральные CS-линии bb соединены с одной и той же шиной CsL запоминающих конденсаторов. Подача напряжений для запоминающих конденсаторов с обоих концов активной области АА таким образом позволяет предотвратить изменение формы сигнала напряжения Vcs для запоминающих конденсаторов от одной точки к другой в активной области АА из-за влияния задержки в соединительных проводниках.

Список литературы

Патентная литература 1

Публикация патентной заявки Японии, Tokukai, No. 2004-62146 А (Дата публикации: 26 февраля 2004)

Патентная литература 2

Публикация патентной заявки Японии, Tokukai, No. 2007-72033 А (Дата публикации: 22 марта 2007)

Патентная литература 3

Публикация патентной заявки Японии, Tokukai, No. 2005-338595 А (Дата публикации: 8 декабря 2005)

Патентная литература 4

Публикация патентной заявки Японии, Tokukaihei, No. 10-10572 А (Дата публикации: 16 января 1998)

Патентная литература 5

Публикация патентной заявки Японии, Tokukaihei, No. 7-325317 А (Дата публикации: 12 декабря 1995)

Сущность изобретения

Техническая задача

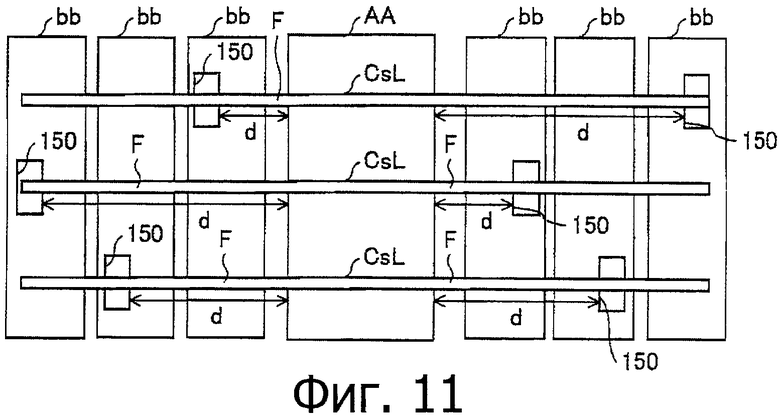

Однако в жидкокристаллическом устройстве отображения, применяющем многопиксельное управление с использованием обычных магистральных CS-линий bb, группа BB магистральных CS-линий включает несколько магистральных CS-линий bb, как показано на фиг.11. В то же время, в такой конструкции расстояния d между соответствующими магистральными CS-линиями bb и активной областью АА оказываются различными. Магистральные CS-линии bb и линии CsL запоминающих конденсаторов изготовлены в разных металлических слоях, выполненных на разных уровнях, таким образом, что (i) магистральные CS-линии bb изготовлены из металла истоков, a (ii) шины CsL запоминающих конденсаторов изготовлены из металла затворов.

Каждая из шин CsL запоминающих конденсаторов проходит через область, изолированную от группы ВВ магистральных CS-линий слоем диэлектрика, созданным поверх группы ВВ магистральных CS-линий, так что каждая из этих линий шин соединяется с соответствующей магистральной CS-линией bb через контактное отверстие 150, выполненное в слое диэлектрика.

Таким образом, если предположить, что каждое расстояние d от активной области до точки соединения (контактное отверстие 150), в которой шина CsL запоминающих конденсаторов соединяется с соответствующей магистральной CS-линией bb, представлено длиной подающего участка, то шина запоминающих конденсаторов, соединенная с магистральной CS-линией bb, проходящей дальше от активной области АА, имеет подающий участок большей длины и потому более высокое сопротивление соединения. Даже если число магистральных CS-линий всего 12, число шин CsL запоминающих конденсаторов очень велико, например порядка тысяч. Следовательно, необходимо, чтобы шины CsL запоминающих конденсаторов имели очень маленькую ширину по сравнению с шириной магистральных CS-линий bb.

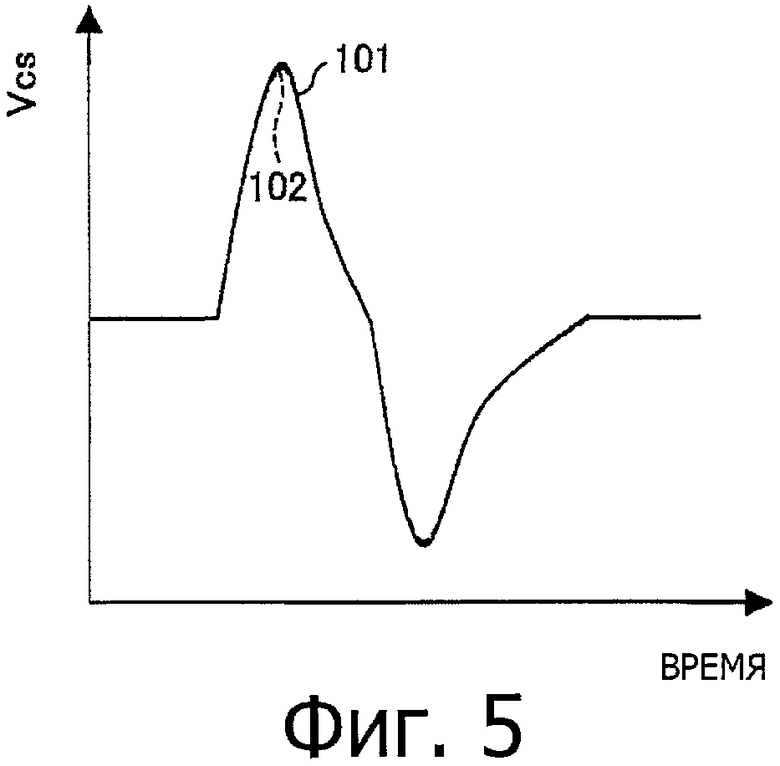

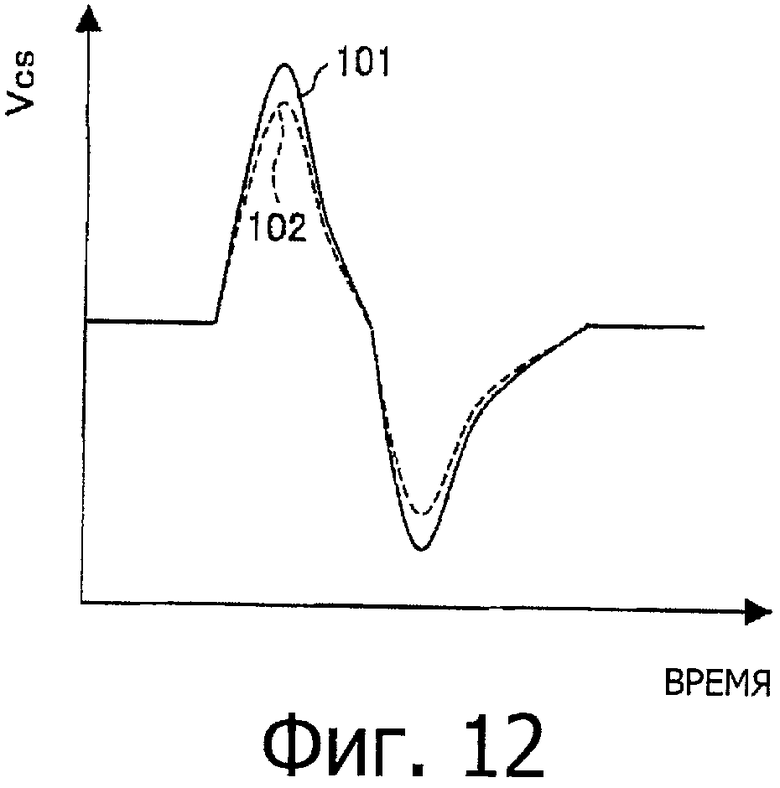

Напряжения Vcs для запоминающих конденсаторов, поступающие по соответствующим шинам CsL запоминающих конденсаторов, подлежат изменениям под влиянием электрических потенциалов электродов пикселов. Если имеет место разница длин подающих участков, напряжения Vcs для запоминающих конденсаторов, поступающие по соответствующим шинам CsL запоминающих конденсаторов, отличаются друг от друга по величине, на которую импульсные напряжения ослабевают к концу области АА. Разность, на которую ослабевают импульсные напряжения, показана на фиг.12. Кривая 101, показанная сплошной линией, представляет собой сигнал напряжения Vcs для запоминающих конденсаторов на участке шины CsL запоминающих конденсаторов, подающий участок F которой соединен с магистральной CS-линией, расположенной дальше от активной области (т.е. шины CsL запоминающих конденсаторов, имеющей подающий участок F, длина которого указывает, что расстояние d от активной области до магистральной CS-линии bb велико), так что этот участок шины соответствует концу активной области АА, расположенному ближе к подающему участку F. Кривая 102, показанная штриховой линией, представляет собой сигнал напряжения Vcs для запоминающих конденсаторов на участке шины CsL запоминающих конденсаторов, подающий участок F которой соединен с магистральной CS-линией bb, расположенной ближе к активной области (т.е. шины CsL запоминающих конденсаторов, имеющей подающий участок F, длина которого указывает, что расстояние d от активной области до магистральной (S-линии bb мало), так что этот участок шины соответствует концу активной области АА, расположенному ближе к подающему участку F. Импульсное напряжение в сигнале 101 больше, чем в сигнале 102.

Если импульсные напряжения в напряжениях для запоминающих конденсаторов, поступающих по соответствующим шинам CsL запоминающих конденсаторов, отличаются по величине друг от друга, распределение этих импульсных напряжений в составе напряжений для запоминающих конденсаторов на конце активной области АА зависит от положений этих шин CsL запоминающих конденсаторов (см. фиг.9). Это приводит к некоторому неравномерному распределению яркости субпикселов sp1 и sp2, т.е. пикселов Р, расположенных возле конца активной области АА, и тем самым создает проблему, например, появление видимых горизонтальных полос на экране.

Настоящее изобретение разработано с учетом этих проблем, так что целью настоящего изобретения является реализация устройства отображения, в котором по существу отсутствует неравномерное распределение импульсных напряжений в составе напряжений для запоминающих конденсаторов на конце активной области.

Решение задачи

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающий в себя: множество шин запоминающих конденсаторов, первую группу магистральных CS-линий в первой области, граничащей с одним концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем первая группа магистральных CS-линий образована первыми магистральными CS-линиями; и вторую группу магистральных CS-линий во второй области, граничащей с другим концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем вторая группа магистральных CS-линий образована вторыми магистральными CS-линиями, причем каждая из множества шин запоминающих конденсаторов соединена одним концом с одной или более первых магистральных CS-линий через контактное отверстие, а другим концом соединена с одной или более вторых магистральных CS-линий через контактное отверстие, при этом на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанные одну или более первых магистральных CS-линий, а на другой конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанные одну или более вторых магистральных CS-линий, при этом одна или более из множества шин запоминающих конденсаторов имеет изгибающий отрезок в пределах своего подающего участка, проходящего от активной области к точке соединения указанной шины запоминающих конденсаторов с соответствующей ей магистральной CS-линией, причем указанный изгибающийся отрезок представляет собой отрезок, оттянутый и отклоняющийся от прямой линии, вдоль которой проходит указанная шина запоминающих конденсаторов от активной области к точке соединения.

Согласно настоящему изобретению подбирают соответствующие длины изгибающихся отрезков. Таким образом, становится возможным обеспечить, чтобы множество шин запоминающих конденсаторов имели идентичные или подобные сопротивления соединения своих подающих участков независимо от конкретных магистральных CS-линий, принадлежащих к одной и той же группе магистральных CS-линий. Следовательно, напряжения для запоминающих конденсаторов, поступающие через множество шин запоминающих конденсаторов, имеют идентичные или подобные импульсные напряжения на концах активной области АА независимо от конкретных линий шин запоминающих конденсаторов. Это делает возможным избежать проявления проблемы, встречающейся в устройствах отображения, и в частности в устройствах отображения с экраном большого размера, где активная область получает напряжения для запоминающих конденсаторов с обоих концов, и заключающейся в том, что при этом возникает неравномерное распределение яркости пикселов, расположенных возле концов активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсного напряжения в составе напряжений для запоминающих конденсаторов на концах активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающий в себя: множество шин запоминающих конденсаторов; первую группу магистральных CS-линий в первой области, граничащей рядом с одним концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем первая группа магистральных CS-линий образована первыми магистральными CS-линиями; и вторую группу магистральных CS-линий во второй области, граничащей с другим концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем вторая группа магистральных CS-линий образована вторыми магистральными CS-линиями, причем каждая из множества шин запоминающих конденсаторов соединена одним концом с одной из первых магистральных CS-линий через контактное отверстие, а другим концом с одной из вторых магистральных CS-линий через контактное отверстие, при этом на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанную одну из первых магистральных CS-линий, а на другой конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанную одну из вторых магистральных CS-линий, при этом по меньшей мере та из множества шин запоминающих конденсаторов, которая соединена с другой магистральной CS-линией первой или второй групп магистральных CS-линий, отличной от магистральной CS-линии, расположенной дальше всего от активной области, имеет изгибающийся отрезок в пределах своего подающего участка, проходящий от активной области к точке соединения указанной шины запоминающих конденсаторов с указанной другой магистральной CS-линией, причем указанный изгибающийся отрезок представляет собой отрезок, оттянутый и отклоняющийся от прямой линии, вдоль которой проходит указанная шина запоминающих конденсаторов от активной области к точке соединения, и длина изгибающегося отрезка тем больше, чем меньше расстояние от активной области до точки соединения.

Согласно настоящему изобретению соответствующие длины меандровых отрезков изменяются от одного подающего участка к другому. Таким образом, можно обеспечить, чтобы множество шин запоминающих конденсаторов имели одинаковые или близкие сопротивления соединений в своих подающих участках, независимо от того, к какой из магистральных CS-линий, принадлежащих к одной группе магистральных CS-линий, присоединена конкретная шина. В результате напряжения для запоминающих конденсаторов имеют одинаковые или близкие импульсные напряжения на концах активной области. Это позволяет избежать проявления проблемы, встречающейся в устройстве отображения, и в частности в устройствах отображения с экраном большого размера, где активная область получает напряжения для запоминающих конденсаторов с обоих концов, и заключающейся в том, что при этом возникает неравномерное распределение яркости пикселов, расположенных возле концов активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсного напряжения в составе напряжений для запоминающих конденсаторов на концах активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, чтобы соотношение между (i) расстоянием от активной области до одной точки соединения и (ii) длиной соответствующего изгибающегося участка в первой группе магистральных CS-линий было идентично аналогичному соотношению во второй группе магистральных CS-линий.

Согласно настоящему изобретению изгибающиеся участки имеют одинаковую длину независимо от группы магистральных CS-линий. Таким образом, становится возможным, чтобы подающие участки шин запоминающих конденсаторов имели одинаковые сопротивления независимо от групп магистральных CS-линий.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающий в себя: множество шин запоминающих конденсаторов; и группу магистральных CS-линий в области, граничащей с одним концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем группа магистральных CS-линий образована магистральными CS-линиями, каждая из множества шин запоминающих конденсаторов соединена одним концом с одной или более магистральными CS-линиями через контактное отверстие, так что на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанные одну или более магистральных CS-линий, при этом одна или более из множества шин запоминающих конденсаторов имеет изгибающийся отрезок в пределах своего подающего участка, проходящего от активной области до точки соединения указанной шины запоминающих конденсаторов с соответствующей магистральной CS-линией, причем указанный изгибающийся отрезок представляет собой отрезок, оттянутый и отклоняющийся от прямой линии, вдоль которой проходит указанная шина запоминающих конденсаторов от активной области к точке соединения.

Согласно настоящему изобретению подбирают длины изгибающихся отрезков. Это позволяет добиться, чтобы шины запоминающих конденсаторов имели одинаковые или близкие сопротивления соединений в своих подающих участках независимо от того, с какой из магистральных CS-линий, принадлежащих одной группе магистральных CS-линий, соединена эта шина. В результате импульсные напряжения в составе напряжений для запоминающих конденсаторов, поступающих через соответствующие шины запоминающих конденсаторов, становятся одинаковыми или близкими друг другу на конце активной области. Это позволяет избежать проявления проблемы, встречающейся в устройствах отображения, и в частности в устройствах отображения с экраном большого размера, когда активная область получает напряжения для запоминающих конденсаторов с обоих концов, и заключающейся в том, что при этом возникает неравномерное распределение яркости пикселов, расположенных возле концов активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсных напряжений в составе напряжений для запоминающих конденсаторов на конце активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающий в себя: множество шин запоминающих конденсаторов; и группу магистральных CS-линий в области, граничащей с одним концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества линий запоминающих конденсаторов, причем группа магистральных CS-линий образована магистральными CS-линиями, при этом каждая из множества шин запоминающих конденсаторов соединена одним концом с одной из магистральных CS-линий через контактное отверстие, причем на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанную одну из магистральных CS-линий, при этом по меньшей мере та из множества шин запоминающих конденсаторов, которая соединена с другой магистральной CS-линией в указанной группе магистральных CS-линий, отличной от магистральной CS-линии, расположенной дальше всего от активной области, имеет изгибающийся отрезок в пределах своего подающего участка, проходящего от активной области до точки соединения указанной шины запоминающих конденсаторов с указанной другой магистральной CS-линией, причем указанный изгибающийся отрезок представляет собой отрезок, удлиненный и отклоняющийся от прямой линии, вдоль которой проходит указанная линия шины запоминающих конденсаторов от активной области к точке соединения, при этом длина изгибающегося отрезка тем больше, чем меньше расстояние от активной области до точки соединения.

Согласно настоящему изобретению соответствующая длина линий изгибающихся отрезков изменяется от одного подающего участка к другому. Это позволяет обеспечить, чтобы шины запоминающих конденсаторов имели одинаковые или близкие сопротивления соединений своих подающих участков независимо от того, с какой из магистральных CS-линий, принадлежащих одной группе магистральных CS-линий, соединена рассматриваемая шина. В результате импульсные напряжения в составе напряжений для запоминающих конденсаторов, поступающих через соответствующие шины запоминающих конденсаторов, становятся одинаковыми или близкими друг другу на конце активной области. Это позволяет избежать проявления проблемы, встречающейся в устройствах отображения, и в частности в устройствах отображения с экраном большого размера, где активная область получает напряжения для запоминающих конденсаторов через один конец, и заключающейся в том, что при этом возникает неравномерное распределение яркостей пикселов, расположенных возле конца активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсных напряжений в составе напряжений для запоминающих конденсаторов на конце активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что интервал, в котором каждый изгибающийся отрезок присутствует на соответствующем подающем участке, находится в области, накладывающейся на соответствующую магистральную CS-линию, соединенную с соответствующей шиной запоминающих конденсаторов из множества шиной запоминающих конденсаторов.

Согласно настоящему изобретению изгибающийся участок имеет по существу такой же электрический потенциал, что и соответствующая магистральная CS-линия. Следовательно, емкость, образующаяся между изгибающимся отрезком и соответствующей магистральной CS-линией, становится несущественной. Таким образом, появляется возможность пропорционально несущественности указанной емкости не допустить возникновение задержки межсоединения, вызываемой шиной запоминающего конденсатора.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что каждая из множества шин запоминающих конденсаторов, соединенных с соответствующей магистральной CS-линией или с соответствующими магистральными CS-линиями, отличными от магистральной CS-линии одной из групп магистральных CS-линий, расположенной дальше всего от активной области, доходит до области, накладывающейся на магистральную CS-линию, расположенную дальше всего от активной области.

Согласно настоящему изобретению емкости, образованные между какой-либо шиной запоминающих конденсаторов и магистральными CS-линиями, отличными от магистральной CS-линии, соединенной с указанной шиной запоминающих конденсаторов, могут быть сделаны одинаковыми с емкостями, образованными между другой шиной запоминающих конденсаторов и магистральными CS-линиями, отличными от магистральной CS-линии, соединенной с указанной шиной запоминающих конденсаторов. Таким образом, можно обеспечить одинаковую задержку межсоединения для всех шин запоминающих конденсаторов и тем самым можно улучшить равномерность яркости пикселов.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено так, что каждая магистральная CS-линия составлена из первой магистральной CS-сублинии, расположенной ближе к активной области, и второй магистральной CS-сублинии, расположенной дальше от активной области; а каждое контактное отверстие составлено из первого контактного суботверстия над первой магистральной CS-сублинией и второго контактного суботверстия над второй магистральной CS-сублинией, причем первое и второе контактные суботверстия соединены друг с другом посредством соединительной линии.

Согласно настоящему изобретению каждая магистральная CS-линия выполнена из двух магистральный CS-сублиний, а эти две магистральные CS-сублинии соединены друг с другом посредством соединительной линии. Поэтому даже если одна из этих магистральных CS-сублиний окажется оборвана, напряжение для запоминающих конденсаторов может проходить через другую из этих магистральных CS-сублиний. Следовательно, это позволяет предотвратить разъединение всей магистральной CS-линии.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что каждый изгибающийся отрезок составлен из первого изгибающегося участка, обеспеченного в области наложения на первую магистральную CS-сублинию, и второго изгибающегося участка, обеспеченного в области наложения на вторую магистральную CS-сублинию.

Настоящее изобретение облегчает подстройку длин изгибающихся отрезков посредством (i) обеспечения первого изгибающегося участка и/или второго изгибающегося участка и (ii) подбора соответствующих длин первого изгибающегося участка и второго изгибающегося участка.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что каждый из первого и второго изгибающихся участков согнут один или несколько раз в направлении, перпендикулярном направлению прямой линии, вдоль которой проходит соответствующая шина запоминающих конденсаторов от активной области.

Настоящее изобретение позволяет легко подстраивать длину изгибающегося отрезка путем изменения длины изгибающегося отрезка и числа изгибающихся участков в составе изгибающегося отрезка.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что в первой магистральной CS-сублинии первый изгибающийся участок расположен ближе к активной области, чем первое контактное суботверстие, а во второй магистральной CS-сублинии второй изгибающийся участок расположен ближе к активной области, чем второе контактное суботверстие.

Согласно настоящему изобретению длину изгибающегося отрезка всегда можно подстроить в области между контактным суботверстием и активной областью. Таким образом, можно зафиксировать взаимное расположение между областью изгибающегося отрезка и контактным суботверстием.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что в подающем участке, где расположены и первый, и второй изгибающиеся участки, первый изгибающийся участок имеет задний конец, соединенный с передним концом второго изгибающегося участка, а задний конец второго изгибающегося участка соединен со вторым контактным суботверстием.

Согласно настоящему изобретению изгибающийся отрезок соединен с ближайшим контактным суботверстием таким образом, что длина изгибающегося отрезка равна сумме соответствующих длин первого изгибающегося участка и второго изгибающегося участка. Это позволяет в большей степени изменять длину изгибающегося отрезка.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что две или более из множества шин запоминающих конденсаторов имеют изгибающиеся отрезки в составе своих подающих участков, соответственно; и в подающем участке той из двух или более из множества шин запоминающих конденсаторов, которая соединена с какой-либо магистральной CS-линией из группы магистральных CS-линий или групп магистральных CS-линий, расположенной дальше всего от активной области, второй изгибающийся участок имеет меньшую длину.

Настоящее изобретение облегчает постепенное укорочение длины изгибающегося отрезка при сохранении длины первого изгибающегося участка.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что подающий участок имеет только первый изгибающийся участок, задний конец которого соединен с первым контактным суботверстием.

Настоящее изобретение облегчает образование короткого изгибающегося отрезка путем соединения первого изгибающегося участка с первым контактным суботверстием и при этом без использования второго изгибающегося участка.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что две или более из множества шин запоминающих конденсаторов имеют изгибающиеся отрезки в составе своих подающих участков соответственно; причем в подающем участке той из указанных двух или более из множества шин запоминающих конденсаторов, которая соединена с магистральной CS-линией в группе магистральных CS-линий или в группах магистральных CS-линий, находящейся дальше от активной области, первый изгибающийся участок имеет меньшую длину.

Настоящее изобретение позволяет постепенно уменьшать длину изгибающегося отрезка.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающее в себя: множество шин запоминающих конденсаторов, первую группу магистральных CS-линий в первой области, граничащей с одним концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем первая группа магистральных CS-линий образована первыми магистральными CS-линиями; и вторую группу магистральных CS-линий во второй области, граничащей с другим концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, так что указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем вторая группа магистральных CS-линий образована вторыми магистральными CS-линиями, при этом каждая из множества шин запоминающих конденсаторов соединена одним концом с одной или более первыми магистральными CS-линиями через контактное отверстие, а другим концом с одной или более вторыми магистральными CS-линиями через контактное отверстие, причем на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанные одну или более первые магистральные CS-линии, а на другой конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанные одну или более вторые магистральные CS-линии, при этом две или более из множества линий шин запоминающих конденсаторов имеют соответственно подающие участки, каждый из которых проходит от активной области к точке соединения указанной шины запоминающих конденсаторов с соответствующей ей магистральной CS-линией, причем указанные подающие участки имеют разную ширину.

Согласно настоящему изобретению подбирают соответствующую ширину подающих участков. Таким образом, становится возможным обеспечить, чтобы шины запоминающих конденсаторов имели одинаковые или близкие сопротивления межсоединений своих подающих участков независимо от того, с какими конкретными магистральными CS-линиями, принадлежащими к одной группе магистральных CS-линий, эти шины соединены. Следовательно, напряжения для запоминающих конденсаторов, поступающие через множество шин запоминающих конденсаторов, имеют одинаковые или близкие импульсные напряжения на концах активной области. Это позволяет избежать проявления проблемы, встречающейся в устройствах отображения и, в частности, в устройствах отображения с экраном большого размера, где активная область получает напряжения для запоминающих конденсаторов с обоих концов, и заключающейся в том, что при этом возникает неравномерное распределение яркости пикселов, расположенных возле концов активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсного напряжений в составе напряжений для запоминающих конденсаторов на концах активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающий в себя: множество шин запоминающих конденсаторов; первую группу магистральных CS-линий в первой области, граничащей с одним концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем первая группа магистральных CS-линий образована первыми магистральными CS-линиями; и вторую группу магистральных CS-линий во второй области, граничащей с другим концом активной области секции отображения в направлении, в котором проходят указанное множество линий шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем вторая группа магистральных CS-линий образована вторыми магистральными CS-линиями, при этом каждая из множества шин запоминающих конденсаторов соединена одним концом с одной из первых магистральных CS-линий, а другим концом с одной из вторых магистральных CS-линий через контактное отверстие, причем на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанную одну из первых магистральных CS-линий, а на другой конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанную одну из вторых магистральных CS-линий, при этом по меньшей мере та из множества шин запоминающих конденсаторов, которая соединена с какой-либо другой магистральной CS-линией из первой и/или второй групп магистральных CS-линий, отличной от магистральной CS-линии, расположенная ближе всего к активной области, имеет подающий участок, проходящий от активной области к точке соединения указанной шины запоминающих конденсаторов с соответствующей ей магистральной CS-линией, ширина подающего участка тем больше, чем больше расстояние от активной области до соответствующей точки соединения.

Согласно настоящему изобретению ширина соответствующих подающих участков меняется от одного участка к другому. Таким образом, становится возможным обеспечить, чтобы шины запоминающих конденсаторов имели одинаковые или близкие сопротивления соединений своих подающих участков независимо от того, с какими конкретными магистральными CS-линиями, принадлежащими одной группе магистральных CS-линий, эти шины соединены. Это позволяет избежать проявления проблемы, встречающейся в устройствах отображения и, в частности, в устройствах отображения с экраном большого размера, где активная область получает напряжения для запоминающих конденсаторов с обоих концов, и заключающейся в том, что при этом возникает неравномерное распределение яркости пикселов, расположенных возле концов активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсных напряжений в составе напряжений для запоминающих конденсаторов на концах активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающее в себя: множество шин запоминающих конденсаторов; и группу магистральных CS-линий в области, граничащей с одним концом активной области секции отображения в направлении, в котором проходят указанное множество линий шин запоминающих конденсаторов, при этом указанные магистральные линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем группа магистральных CS-линий образована несколькими магистральными CS-линиями; при этом каждая из множества шин запоминающих конденсаторов соединена одним концом с одной или более магистральными CS-линиями через контактное отверстие, причем на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанные одну или более магистральных CS-линий, и две или более из множества шин запоминающих конденсаторов имеют подающие участки соответственно, каждый из которых проходит от активной области и точки соединения указанной шины запоминающих конденсаторов с соответствующей ей магистральной CS-линией, при этом линии подающих участков имеют различную ширину.

Согласно настоящему изобретению подбирают длины соответствующих подающих участков. Таким образом, становится возможным добиться, чтобы шины запоминающих конденсаторов имели одинаковые или близкие сопротивления соединений своих подающих участков независимо от того, с какими конкретными магистральными CS-линиями, принадлежащими одной группе магистральных CS-линий, эти шины соединены. Следовательно, напряжения для запоминающих конденсаторов, поступающие через несколько шин запоминающих конденсаторов, имеют одинаковые или близкие импульсные напряжения на концах активной области. Это позволяет избежать проявления проблемы, встречающейся в устройствах отображения, и, в частности, в устройствах отображения с экраном большого размера, где активная область получает напряжения для запоминающих конденсаторов с обоих концов, и заключающейся в том, что при этом возникает неравномерное распределение яркости пикселов, расположенных возле концов активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсных напряжений в составе напряжений для запоминающих конденсаторов на концах активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой устройство отображения с активной матрицей, включающее в себя: множество шин запоминающих конденсаторов; и группу магистральных CS-линий в области, граничащей с одним концом активной области секции отображения в направлении, в котором проходят указанное множество шин запоминающих конденсаторов, при этом указанные магистральные CS-линии проходят перпендикулярно направлению множества шин запоминающих конденсаторов, причем группа магистральных CS-линий образована несколькими магистральными CS-линиями; при этом каждая из множества шин запоминающих конденсаторов соединена одним концом с одной из магистральных CS-линий через контактное отверстие, причем на указанный один конец каждой из множества шин запоминающих конденсаторов подается напряжение для запоминающих конденсаторов через указанную одну из магистральных CS-линий, и по меньшей мере для той из множества шин запоминающих конденсаторов, которая соединена с какой-либо другой магистральной CS-линией в группе магистральных CS-линий, отличной от магистральной CS-линии той же группы, расположенной ближе всего к активной области, имеет подающий участок, проходящий от активной области до точки соединения указанной шины запоминающих конденсаторов с указанной другой магистральной CS-линией, причем ширина подающего участка тем больше, чем больше расстояние от активной области до соответствующей точки соединения.

Согласно настоящему изобретению длины соответствующих подающих участков выполнены отличными друг от друга, как описано выше. Таким образом, это позволяет обеспечить, чтобы шины запоминающих конденсаторов имели одинаковые или близкие сопротивления соединений своих подающих участков независимо от того, с какими конкретными магистральными CS-линиями, принадлежащими одной группе магистральных CS-линий, эти линии шин соединены. Следовательно, напряжения для запоминающих конденсаторов, поступающие через несколько шин запоминающих конденсаторов, имеют одинаковые или близкие импульсные напряжения на концах активной области. Это позволяет избежать проявления проблемы, встречающейся в устройствах отображения, и, в частности, в устройствах отображения с экраном большого размера, где активная область получает напряжения для запоминающих конденсаторов с одного конца, и заключающейся в том, что при этом возникает неравномерное распределение яркости пикселов, расположенных возле этого конца активной области, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Это позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсных напряжений в составе напряжений для запоминающих конденсаторов на концах активной области.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что каждый пиксел выполнен из нескольких субпикселов, а запоминающие емкости образуются между множеством субпикселов и множеством соответствующих этим субпикселам шин запоминающих конденсаторов.

Настоящее изобретение делает менее вероятным возникновение неравномерного распределения яркости пикселов, расположенных возле конца активной области в устройстве отображения, использующем многопиксельное управление.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что напряжение для запоминающих конденсаторов, подаваемое на множество субпикселов соответствующего пиксела, имеет вид двухуровневого сигнала с одинаковыми моментами изменения уровня, одинаковым периодом и колебанием с разной амплитудой.

Настоящее изобретение позволяет точно установить разницу яркостей свечения субпикселов в составе пикселов на устройстве отображения с использованием многопиксельного управления.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что в каждую магистральную CS-линию, соединенную с соответствующей одной из шин запоминающих конденсаторов для соответствующих разных пикселов, подают свое напряжение для запоминающих конденсаторов, моменты изменения уровня которого отличаются от соответствующих моментов изменения уровня напряжений в других линиях.

Настоящее изобретение позволяет в устройстве отображения с многопиксельным управлением варьировать яркость между субпикселами в составе пикселов в порядке сканирования линий пикселов.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что между пикселом и соответствующей одной из шин запоминающих конденсаторов образована запоминающая емкость.

Согласно настоящему изобретению в устройстве отображения, не использующем многопиксельное управление, две или более шин запоминающих конденсаторов имеют одинаковые сопротивления соединений.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что на множество шин запоминающих конденсаторов подают одинаковое напряжение для запоминающих конденсаторов.

Согласно настоящему изобретению подают одинаковое напряжение во все соответствующие шины запоминающих конденсаторов с использованием множества магистральных CS-линий.

Для достижения этой цели устройство отображения согласно настоящему изобретению представляет собой жидкокристаллическое устройство отображения.

Настоящее изобретение реализует жидкокристаллическое устройство отображения, не имеющее неравномерного распределения яркости.

Для достижения этой цели устройство отображения согласно настоящему изобретению выполнено таким образом, что каждая магистральная CS-линия выполнена из металла истоков, а каждая из шин запоминающих конденсаторов выполнена из металла затворов.

Настоящее изобретение использует существующие материалы для создания магистральных CS-линий и шин запоминающих конденсаторов.

Результаты изобретения

Как рассмотрено выше, устройство отображения согласно настоящему изобретению выполнено таким образом, что одна или более из множества шин запоминающих конденсаторов имеет изгибающийся отрезок в составе своего подающего участка, проходящего между активной областью и точкой соединения этой шины запоминающих конденсаторов с соответствующей магистральной CS-линией, при этом изгибающийся отрезок удлиняется и отклоняется от прямой линии, вдоль которой проходит указанная одна или более из множества шин запоминающих конденсаторов от активной области к указанной точке соединения.

Как рассмотрено выше, устройство отображения согласно настоящему изобретению выполнено таким образом, что по меньшей мере та из множества шин запоминающих конденсаторов, которая соединена с какой-либо другой магистральной CS-линией из первой и/или второй группы магистральных CS-линий, отличной от магистральной CS-линии той же группы, расположенной дальше всего от активной области, имеет изгибающийся отрезок в составе своего подающего участка, проходящего между активной областью и точкой соединения указанной шины запоминающих конденсаторов с указанной другой магистральной CS-линией, при этом изгибающийся отрезок удлиняется и отклоняется от прямой линии, вдоль которой проходит указанная из множества шин запоминающих конденсаторов от активной области к указанной точке соединения, причем длина изгибающегося участка тем больше, чем меньше расстояние от активной области до точки соединения.

Как рассмотрено выше, устройство отображения согласно настоящему изобретению выполнено таким образом, что одна или более из множества шин запоминающих конденсаторов содержит изгибающийся отрезок в составе своего подающего участка, проходящего между активной областью и точкой соединения указанной шины запоминающих конденсаторов с соответствующей магистральной CS-линией, при этом указанный изгибающийся отрезок удлиняется и отклоняется от прямой линии, вдоль которой проходит указанная одна или более из множества шин запоминающих конденсаторов от активной области к указанной точке соединения.

Как рассмотрено выше, устройство отображения согласно настоящему изобретению выполнено таким образом, что по меньшей мере та из множества шин запоминающих конденсаторов, которая соединена с любой другой магистральной CS-линией из группы магистральных CS-линий, отличной от магистральной CS-линии той же группы, расположенной дальше всех от активной области, имеет изгибающийся отрезок в составе своего подающего участка, проходящего между активной областью и точкой соединения указанной шины запоминающих конденсаторов с указанной любой другой магистральной CS-линией, при этом изгибающийся отрезок удлиняется и отклоняется от прямой линии, вдоль которой проходит указанная одна или более из множества шин запоминающих конденсаторов от активной области к указанной точке соединения, причем длина изгибающегося участка тем больше, чем меньше расстояние от активной области до точки соединения.

Как рассмотрено выше, устройство отображения согласно настоящему изобретению выполнено таким образом, что две или более из множества шин запоминающих конденсаторов имеют подающие участки, каждый из которых проходит между активной областью и точкой соединения шины запоминающих конденсаторов с соответствующей магистральной CS-линией, при этом подающие участки имеют различную ширину.

Как рассмотрено выше, устройство отображения согласно настоящему изобретению выполнено таким образом, что по меньшей мере та из множества шин запоминающих конденсаторов, которая соединена с любой другой магистральной CS-линией первой и/или второй группы магистральных CS-линий, отличной от магистральной CS-линии той же группы, расположенной ближе всего к активной области, содержит подающий участок, проходящий между активной областью и точкой соединения укапанной шины запоминающих конденсаторов с соответствующей магистральной CS-линией, при этом ширина подающего участка тем больше, чем больше расстояние от активной области до точки соединения.

Как рассмотрено выше, устройство отображения согласно настоящему выполнено таким образом, что две или более из множества шин запоминающих конденсаторов содержат соответствующие подающие участки, каждый из которых проходит от активной области к точке соединения этой шины запоминающих конденсаторов с соответствующей магистральной CS-линией, при этом подающие участки имеют различную ширину линий.

Как рассмотрено выше, устройство отображения согласно настоящему изобретению выполнено таким образом, что по меньшей мере та из множества линий шин запоминающих конденсаторов, которая соединена с любой другой магистральной CS-линией из группы магистральных CS-линий, отличной от магистральной CS-линии той же группы, расположенной ближе всех к активной области, содержит подающий участок, проходящий между активной областью и точкой соединения указанной шины запоминающих конденсаторов с указанной любой другой магистральной CS-линией, при этом ширина линии подающего участка тем больше, чем больше расстояние от активной области до точки соединения.

Настоящее изобретение в целом позволяет реализовать устройство отображения, в котором менее вероятно возникновение неравномерного распределения импульсных напряжений в составе напряжений для запоминающих конденсаторов на конце активной области.

Краткое описание чертежей

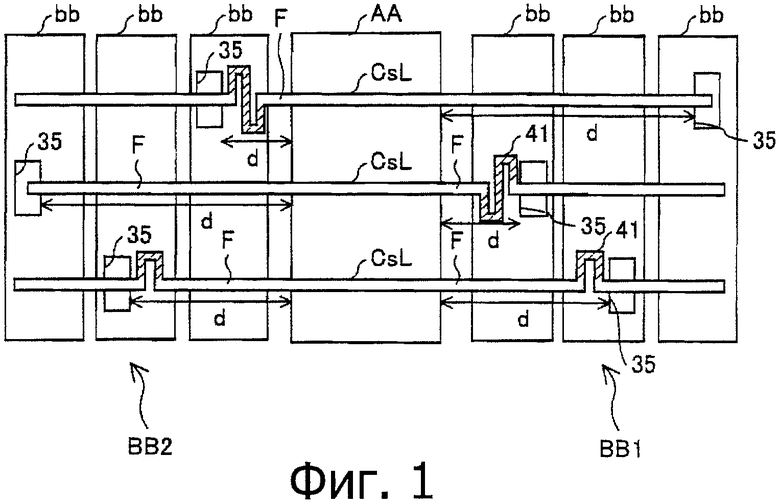

Фиг.1 представляет вид в плане, показывающий конфигурацию шин запоминающих конденсаторов и магистральных CS-линий согласно одному варианту настоящего изобретения.

Фиг.2 представляет вид в плане, показывающий размещение шины запоминающих конденсаторов и магистральной CS-линии.

Фиг.3 представляет вид в плане, показывающий примеры конфигурации подающего участка.

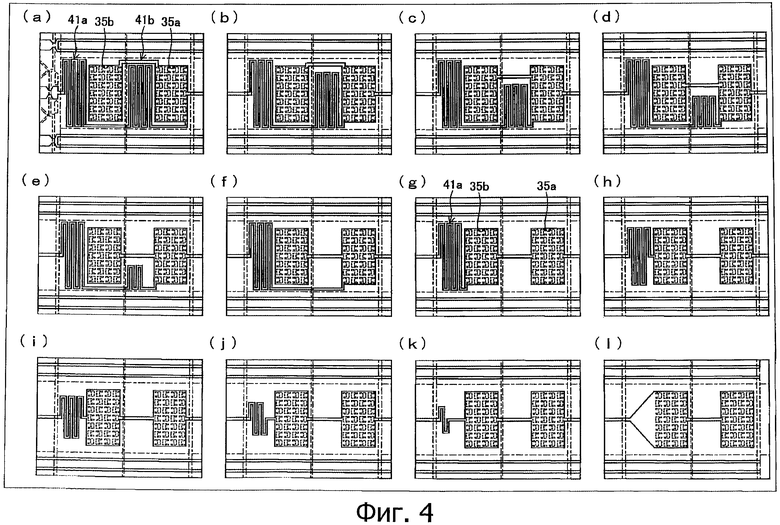

Фиг 4 (а) - (1) представляет виды в плане, показывающие примеры конфигурации подающих участков, соединенных с соответствующими различными магистральными CS-линиями.

Фиг.5 представляет временную диаграмму, показывающую форму импульсного напряжения в составе напряжения для запоминающих конденсаторов.

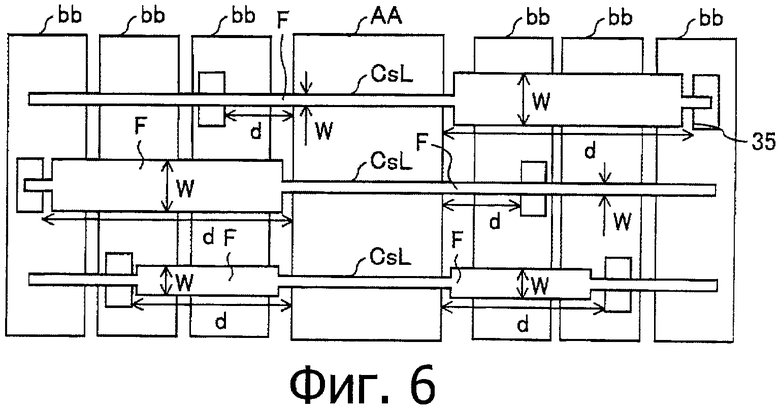

Фиг.6 представляет вид в плане, показывающий конфигурацию шин запоминающих конденсаторов и магистральных CS-линий согласно другому варианту настоящего изобретения.

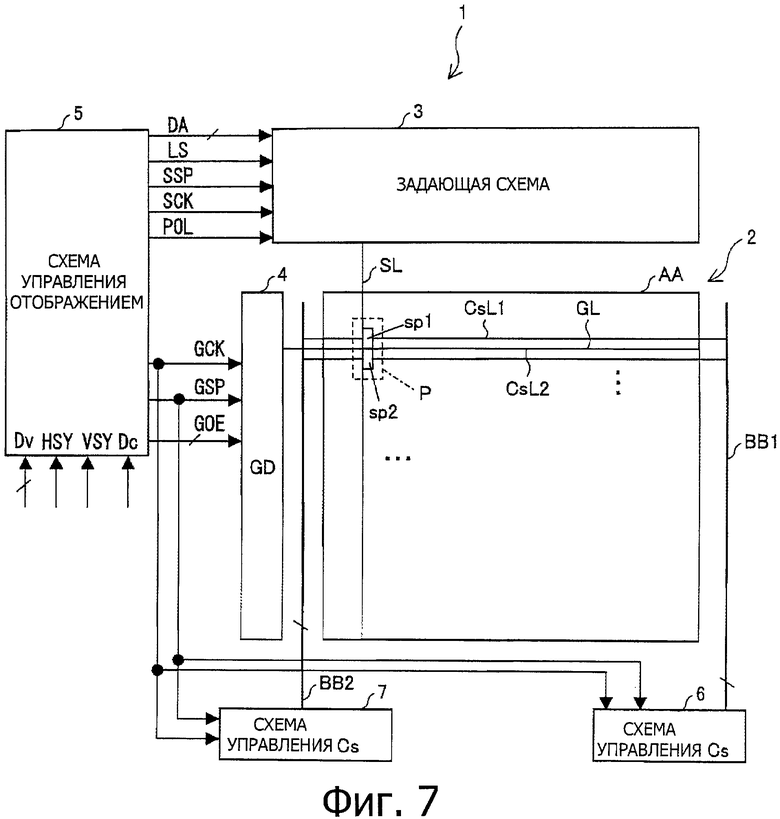

Фиг.7 представляет блок-схему, показывающую конфигурацию устройства отображения.

Фиг.8 представляет принципиальную схему, показывающую конфигурацию пиксела в системе с многопиксельным управлением.

Фиг.9 представляет вид в плане, показывающий размещение шины запоминающих конденсаторов и магистральной CS-линии в соответствии с обычным способом.

Фиг.10 представляет временную диаграмму, показывающую примеры сигналов напряжений для запоминающих конденсаторов, поступающих к пикселу, изображенному на фиг.8.

Фиг.11 представляет вид в плане, показывающий конфигурацию шин запоминающих конденсаторов и магистральных CS-линий.

Фиг.12 представляет временную диаграмму, показывающую форму сигнала напряжения пульсаций в составе напряжения для запоминающих конденсаторов, полученную для случая, изображенного на фиг.9.

Описание вариантов

Один вариант настоящего изобретения описан ниже со ссылками на фиг.1-7. Фиг.7 показывает конфигурацию жидкокристаллического устройства 1 отображения согласно настоящему изобретению. Как показано на фиг.7, жидкокристаллическое устройство отображения 1 включает в себя секцию 2 отображения, задающую схему 3 истоков, задающую схему 4 затворов, схему 5 управления отображением и схемы 6 и 7 управления CS. Эти компоненты жидкокристаллического устройства отображения 1 могут быть встроены в одну панель. В альтернативном варианте конструкция может быть такой, что некоторые или все из компонентов - задающая схема 3 истоков, задающая схема 4 затворов, схемы 6 и 7 управления Cs, могут быть выполнены на внешней подложке, такой как гибкая печатная плата, соединенная с панелью, на которой выполнена секция 2 отображения. Таким образом, настоящее изобретение не ограничивается конкретными компоновкой и конфигурацией.

Секция 2 отображения имеет активную область АА матрицы, в которой в виде матрицы расположены пикселы Р, показанные на фиг.8, каждый из пикселов Р имеет субпикселы sp1 и sp2. Секция 2 отображения включает в себя: множество линий GL затворных шин; множество линий SL истоковых шин; множество линий CsL1, CsL2,… шин запоминающих конденсаторов; и две группы ВВ1 и ВВ2 магистральных CS-линий. Аналогично конфигурации, показанной на фиг.8, каждый из пикселов Р соединен с (i) соответствующей одной из множества линий GL затворных шин и (ii) соответствующей одной из множества линий SL истоковых шин, пересекающих одна другую. Субпикселы sp1 и sp2 соединены соответственно с линиями CsL1 и CsL2 шин запоминающих конденсаторов. Группа ВВ1 магистральных CS-линий выполнена в области, граничащей с одним концом активной области АА в направлении, в котором проходят линии CsL1 и CsL2 шин запоминающих конденсаторов (совместно именуемые шинами CsL шин запоминающих конденсаторов). Группа ВВ2 магистральных CS-линий выполнена в области, граничащей с другим концом активной области АА в направлении, в котором проходят линии CsL шин запоминающих конденсаторов. Линии CsL шин запоминающих конденсаторов соединены с магистральными CS-линиями обеих групп ВВ1 и ВВ2.

Схема 5 управления отображением управляет задающей схемой 3 истоков, задающей схемой 4 затворов и схемами 6 и 7 управления Cs. Схема 5 управления отображением принимает от внешнего источника сигнала (например, тюнера): цифровой видеосигнал Dv, несущий изображение, которое нужно отобразить; горизонтальный синхросигнал HSY и вертикальный синхросигнал VSY, причем оба синхросигнала соответствуют цифровому видеосигналу Dv; и сигнал Dc управления, на основе которого управляют работой устройства отображения. Схема 5 управления отображением в ответ на принятые таким образом сигналы генерирует сигналы с (i) no (vii), в ответ на которые секция 2 отображения представляет изображение, задаваемое цифровым видеосигналом Dv. А именно, (i) занимающий импульсный сигнал SSP данных, (ii) тактовый сигнал SCK данных, (iii) стробирующий сигнал LS защелки, (iv) цифровой сигнал DA изображения (соответствующий видеосигналу Dv), задающий изображение для отображения, (v) запускающий импульсный сигнал GSP затвора, (vi) тактовый сигнал GCK затвора и (vii) и выходной сигнал GOE управления задающей схемой затворов (выходной сигнал управления сигналом развертки). Затем схема 5 управления отображения выводит сигналы с (i) по (vii).

Ниже все это будет описано более подробно. После того как будет выполнена соответствующая подстройка синхронизации или иная подобная обработка видеосигнала Dv во внутренней памяти, схема 5 управления отображением выводит видеосигнал Dv в качестве цифрового сигнала DA изображения. Затем схема 5 управления отображением генерирует тактовый сигнал SCK данных в качестве сигнала, образованного импульсами, соответствующими пикселам изображения, характеризуемого цифровым сигналом DA изображения. Схема 5 управления отображением в ответ на горизонтальный синхросигнал HSY генерирует импульсный старт-сигнал SSP данных, который переходит на высокий уровень (Н-уровень) на время заданного интервала в каждом периоде горизонтальной развертки. Схема 5 управления отображением в ответ на вертикальный синхросигнал VSY генерирует импульсный старт-сигнал GSP затвора, который переходит на высокий уровень (Н-уровень) на время заданного интервала в каждом периоде кадра (в каждом периоде вертикальной развертки). Схема 5 управления отображением генерирует тактовый сигнал GCK затвора в ответ на горизонтальный синхросигнал HSY и генерирует стробирующий сигнал LS защелки и выходной сигнал GOE управления задающей схемой затворов в ответ на горизонтальный синхросигнал HSY и сигнал управления Dc.

Схема 5 управления отображением передает задающей схеме 3 истоков цифровой сигнал DA изображения, стробирующий сигнал LS защелки, сигнал POL, на основе которого управляют полярностью электрического потенциала сигнала (электрического потенциала сигнала данных), импульсный старт-сигнал SSP данных и тактовый сигнал SCK данных из числа указанных сигналов с (i) no (vii). Схема 5 управления отображением подает на задающую схему 4 затворов импульсный старт-сигнал GSP затвора, тактовый сигнал GCK затвора и выходной сигнал GOE управления задающей схемой затворов из числа указанных сигналов с (i) по (vii).

Задающая схема 3 истоков последовательно генерирует сигналы данных для каждого периода горизонтальной развертки в ответ на принятые цифровой сигнал DA, тактовый сигнал SCK данных, стробирующий сигнал LS защелки, импульсный старт-сигнал SSP данных и сигнал POL инверсии полярности, где сигналы данных представляют собой аналоговые электрические потенциалы, соответствующие величинам пикселов на соответствующих строках сигнала развертки изображения, передаваемого цифровым сигналом DA изображения. Затем задающая схема 3 истоков передает сигналы данных в соответствующее множество линий SL шин истоков.

С другой стороны, задающая схема 4 затворов генерирует сигналы развертки в ответ на принятые импульсный старт-сигнал GSP затвора, тактовый сигнал GCK затвора и выходной сигнал GOE управления задающей схемой затворов. Затем задающая схема 4 затворов подает сигналы развертки в множество линий GL шин затворов с целью избирательного управления этим множеством линий GL шин затворов.

Задающая схема 3 истоков и задающая схема 4 затворов таким образом управляют множеством линий SL шин истоков и множеством линий GL шин затворов секции 2 отображения. В результате происходит запись электрических потенциалов сигналов из множества линий SL шин истоков на электроды субпикселов через соответствующие транзисторы TFT, соединенные с выбранной одной из множества линий GL шин затворов. Отсюда следует, что напряжения, изменяющиеся в зависимости от цифрового сигнала DA изображения, оказываются поданы через жидкокристаллический слой на субпикселы в каждом пикселе. Это приводит к управлению количеством света от источника подсветки сзади, проходящего сквозь жидкокристаллический слой, таким образом, чтобы отобразить посредством пикселов изображение, характеризуемое цифровым видеосигналом Dv.

Каждая из схем 6 и 7 управления Cs осуществляет управление электрическими потенциалами линий CsL шин запоминающих конденсаторов в ответ на импульсный старт-сигнал GSP затвора и тактовый сигнал GCK затвора, принимаемые от схемы 5 управления отображением. Это позволяет управлять фазой, периодом и другими параметрами каждого напряжения Vcs для запоминающих конденсаторов. Схема 6 управления Cs передает напряжения Vcs для запоминающих конденсаторов в группу ВВ1 магистральных CS-линий, схема 7 управления Cs передает напряжения Vcs для запоминающих конденсаторов в группу ВВ2 магистральных CS-линий.

На фиг.1 и 2 показана конфигурация линий CsL шин запоминающих конденсаторов и магистральных CS-линий bb.

Магистральные CS-линии bb выполнены так, как это обсуждалось ранее со ссылками на фиг.9 и 11. Группы ВВ1 и ВВ2 магистральных CS-линий, показанные на фиг.2, соответствуют подобным группам ВВ магистральных CS-линий, изображенным на фиг.9. Контактные отверстия 35, показанные на фиг.1, соответствуют контактным отверстиям 150, изображенным на фиг.11. Можно обеспечить только одну из групп магистральных CS-линий - ВВ1 или ВВ2. Однако если созданы обе группы, ВВ1 и ВВ2, магистральных CS-линий, напряжения Vcs для запоминающих конденсаторов поступают в активную область АА от обоих концов активной области АА. В этом случае можно не допустить изменения от точки к точке величины задержки в соединениях, вызванной влиянием сопротивления и емкости линии CsL шины запоминающих конденсаторов, через которые текут большие зарядные и разрядные токи. Схемы 6 и 7 управления Cs передают в магистральные CS-линии bb групп ВВ1 и ВВ2 магистральных CS-линий аналогично тому, как это обсуждалось ранее со ссылками на фиг.10.

Согласно настоящему изобретению, как показано на фиг.1, по меньшей мере та из линий CsL шин запоминающих конденсаторов, которая соединена с любой другой магистральной CS-линией bb из состава группы ВВ магистральных CS-линий, отличной от магистральной CS-линии той же группы, которая расположена дальше всего от активной области АА, имеет изгибающийся отрезок 41 (показан заштрихованным на фиг.1) в составе подающего участка F, проходящего от активной области АА к точке соединения этой линии CsL шины запоминающих конденсаторов с магистральной CS-линией bb группы ВВ магистральных CS-линий. Длина изгибающего отрезка 41 выбрана в соответствии с расстоянием d от активной области АА до точки соединения. Отметим что расстояние d обычно считают равным длине линии, полученной в случае, когда изгибающийся отрезок 41 проходит к точке соединения по прямой линии, вдоль которой проходит линия CsL шины запоминающих конденсаторов от активной области АА.

Изгибающийся отрезок 41 представляет собой отрезок, удлиненный и отклоняющийся от прямой линии, вдоль которой проходит рассматриваемая шина CsL шины запоминающих конденсаторов от активной области АА к точке соединения. Длина D изгибающегося отрезка 41 может быть найдена путем вычитания расстояния d из длины подающего участка F линии CsL шины запоминающих конденсаторов. В такой ситуации, если длина D больше нуля, очевидно, что изгибающийся отрезок 41 существует. Если шина CsL шины запоминающих конденсаторов имеет по всей длине одинаковую ширину, длина D линии изгибающегося отрезка 41 увеличивается при уменьшении расстояния d. Отметим, что для одновременной подстройки полной емкости соединения можно сделать так, чтобы шина CsL шины запоминающих конденсаторов, соединенная с магистральной CS-линией bb, расположенной дальше всех от активной области АА, имела изгибающийся отрезок 41 в составе своего подающего участка F. Кроме того, для достижения дополнительной цели, такой как подстройка общей емкости линии, можно также сделать чтобы шина CsL шины запоминающих конденсаторов имела изгибающийся отрезок 41 в области с внешней стороны от точки соединения.

В таких конфигурациях можно сделать так, чтобы линии CsL шин запоминающих конденсаторов имели одинаковые сопротивления соединений или имели соответствующие близкие сопротивления соединений своих подающих участков F независимо от того, с какой из магистральных CS-линий bb в одной и той же группе BB магистральных СS-линий соединена эта шина шины. Изгибающийся отрезок 41, принадлежащий к группе ВВ1 магистральных CS-линий, вовсе не обязательно имеет длину D линии, идентичную длине линии изгибающегося отрезка 41, принадлежащего к группе ВВ2 магистральных CS-линий. Однако предпочтительно, чтобы изгибающийся отрезок 41, принадлежащий к группе ВВ1 магистральных CS-линий, имел длину D линии, идентичную длине линии изгибающегося отрезка 41, принадлежащего к группе ВВ2 магистральных CS-линий, поскольку это позволяет сделать сопротивления участков соответствующих линий CsL шин запоминающих конденсаторов, проходящих от активной области АА к соответствующим точкам соединения, одинаковыми независимо от того, с какой группой, ВВ1 или ВВ2, магистральных CS-линий соединена эта линия шины.

В такой конфигурации напряжения Vcs для запоминающих конденсаторов. поступающие через соответствующие линии CsL шин запоминающих конденсаторов, могут иметь на концах активной области АА идентичные или аналогичные импульсные напряжения. Это позволяет избежать возникновения проблемы, такой как неравномерное распределение яркостей субпикселов sp1 и sp2, т.е. пикселов Р, расположенных на концах активной области АА, что в свою очередь приводит к появлению видимой горизонтальной полосы на экране.

Если каждая шина CsL запоминающих конденсаторов имеет изгибающийся отрезок 41 в диапазоне, попадающем в область наложения на соответствующую магистральную CS-линию bb, соединенную с указанной каждой из линий CsL шин запоминающих конденсаторов, тогда этот изгибающийся отрезок 41 имеет такой же электрический потенциал, что и соответствующая магистральная CS-линия bb. Таким образом, емкость, образованная между меандровым отрезком 41 и соответствующей магистральной CS-линией bb, не функционирует.Такая нефункционирующая емкость позволяет не допустить появление задержки соединения, вызванной линией CsL шины запоминающих конденсаторов.

Кроме того, как показано на фиг.1, шина CsL запоминающих конденсаторов, соединенная с магистральной CS-линией bb, отличной от магистральной CS-линии bb, расположенной дальше всего от активной области АА, проходит в область, которая накладывается на магистральную CS-линию bb, расположенную дальше всех от активной области АА. Это позволяет образовать одинаковые емкости между соответствующими шинами CsL запоминающих конденсаторов и соответствующими магистральными CS-линиями bb, отличными от магистральной CS-линии bb, соединенной с рассматриваемой шиной CsL запоминающих конденсаторов. Таким образом, можно сделать так, чтобы все шины CsL запоминающих конденсаторов имели одинаковую задержку соединения, и вследствие этого все пикселы Р могут иметь улучшенную равномерность яркости.

На фиг.3 показан подробный пример формирования изгибающегося отрезка 41.

На фиг.3 магистральные CS-линии с bb1 no bb12 показаны в качестве магистральных CS-линий bb в этом порядке от активной области АА. Каждая из магистральных CS-линий bb составлена из двух магистральных CS-сублиний bbx и bby, расположенных друг рядом с другом. На обе магистральные CS-сублинии bbx и bby одной и той же магистральной CS-линии bb поступает одно и то же напряжение для запоминающих конденсаторов. Магистральная CS-сублиния bbx (первая магистральная CS-сублиния) расположена ближе к активной области АА, а магистральная CS-сублиния bby (вторая магистральная CS-сублиния) расположена дальше от активной области АА.

Каждое из контактных отверстий 35 для соответствующих магистральных CS-линий bb составлено из: контактного суботверстия 35а (второе контактное суботверстие) для магистральной CS-сублинии bby; и контактного суботверстия 35b (первое контактное суботверстие) для магистральной CS-сублинии bbx. Магистральные CS-сублинии bbx и bby, составляющие одну (1) пару, соединены одна с другой через контактные суботверстия 35а и 35b посредством соединительной линии 35L. Соединительная линия 35L выполнена из того же самого металла затвора, из которого изготовлены линии CsL шин запоминающих конденсаторов.

(i) Каждая магистральная CS-линия bb составлена из магистральных CS-сублиний bbx и bby, и (ii) эти магистральные CS-сублинии bbx и bby соединены одна с другой посредством соединительной линии 35L. В такой конфигурации даже при обрыве одной из этих магистральных CS-сублиний bbx и bby напряжение Vcs для запоминающих конденсаторов может быть передано через другую из магистральных CS-сублиний bbx и bby. Это позволяет предотвратить обрыв всей магистральной CS-линии bb.

По меньшей мере один из изгибающихся участков 41а и 41b (первый изгибающийся участок и второй изгибающийся участок), предусмотренных для получения требуемой длины изгибающегося отрезка, служит меандровым отрезком 41. Первый изгибающийся участок 41а может быть предусмотрен в области наложения на магистральную CS-сублинию bbx, а второй изгибающийся участок 41b может быть предусмотрен в области наложения на магистральную CS-сублинию bby. Эти изгибающиеся участки 41а и 41b изогнуты один или более раз в направлении, перпендикулярном направлению, в котором шина CsL шины запоминающих конденсаторов проходит от активной области АА. Для магистральной CS-сублинии bbx изгибающийся участок 41а расположен ближе к активной области АА, чем контактное суботверстие 35b. Для магистральной CS-сублинии bby изгибающийся участок 41b расположен ближе к активной области АА, чем контактное суботверстие 35а.

В подающем участке F, содержащем оба изгибающихся участка 41а и 41b, (см. соответствующие магистральные CS-линии bb1 и bb2 на фиг.3), задний конец изгибающегося участка 41а соединен с передним концом изгибающегося участка 41b, а задний конец изгибающегося участка 41b соединен с контактным суботверстием 35а. В таком подающем участке F длина изгибающегося участка 41b становится тем меньше, чем дальше магистральная CS-линия bb от активной области АА. В подающем участке F, в котором создан только один изгибающийся участок 41а в качестве изгибающегося участка 41 (см. магистральную CS-линию bb11 на фиг.3), задний конец этого изгибающегося участка 41 соединен с контактным суботверстием 35b. В таком подающем участке F длина изгибающегося участка 41а становится тем меньше, чем дальше соответствующая магистральная CS-линия bb от активной области АА. В подающем участке F, в котором вообще нет изгибающихся участков 41 (см. магистральную CS-линию bb12 на фиг.3, наиболее удаленную от активной области АА), подающий участок F соединен с контактным суботверстием 35b через электрод 45, ширина которого плавно увеличивается. Отметим, что поскольку такой электрод 45 участвует в уменьшении сопротивления соединения линии CsL шины запоминающих конденсаторов, подобный электрод 45 может быть создан при необходимости, когда требуется уменьшить сопротивление соединения.

Когда контактное отверстие 35 составлено из контактных суботверстий 35а и 35b, предполагается, что расстояние d от активной области АА до точки соединения представляет расстояние от активной области АА до конца контактного суботверстия 35а, которое расположено дальше от активной области АА. В этом случае подающий участок F располагается в пределах диапазона расстояния d, а соотношение размеров между соответствующими расчетными длинами D изгибающихся отрезков 41 согласовано с соотношением размеров между соответствующими фактическими длинами D линий меандровых отрезков 41.

На фиг.4 от (а) до (1) показаны примеры конфигурации изгибающихся отрезков для соответствующих магистральных CS-линий от bb1 до bb12.

На фиг.4 от (а) до (f) выполнены оба изгибающихся участка 41а и 41b. Длина изгибающегося участка 41b постепенно уменьшается при переходе от фиг.4 (а) до фиг.4 (f). Отметим, что длину каждого из изгибающихся участков 41а можно подбирать, изменяя амплитуду изгиба и/или число изгибов в составе изгибающегося участка 41b. Контактные суботверстия 35а и 35b соединены одно с другим посредством соединительной линии 35L, как показано на фиг.3, вследствие чего можно подобрать положение этой соединительной линии 35L в соответствии с длиной изгибающегося отрезка 41. В такой структуре можно с высокой степенью свободы установить размеры области для образования изгибающегося отрезка 41 между контактными суботверстиями 35а и 35b.

На фиг.4 от (g) до (k) выполнен только один изгибающийся участок 41а. Длина изгибающегося отрезка 41 постепенно уменьшается при переходе от фиг.4 (g) до фиг.4 (k). Отметим, что длину каждого изгибающегося отрезка 41 можно подбирать, изменяя амплитуду изгиба и/или число изгибов в составе изгибающегося участка 41а. Задний конец изгибающегося участка 41а соединен с контактным суботверстием 35b. Область для контактного суботверстия 35а, соединительная шина 35L и область для контактного суботверстия 35b составляют участок подающего участка F, где отсутствуют изгибы.

На фиг.5 представлен (i) сигнал 101 (показанный сплошной линией) напряжения Vcs для запоминающих конденсаторов на отрезке линии CsL шины запоминающих конденсаторов, подающий участок F которой соединен с магистральной CS-линией bb, расположенной дальше от активной области АА, это отрезок соответствует концу активной области АА, который ближе расположен к подающему участку F, и (ii) сигнал 102 (показанный штриховой линией) напряжения Vcs для запоминающих конденсаторов на отрезке линии CsL шины запоминающих конденсаторов, подающий участок F которой соединен с магистральной CS-линией bb, расположенной ближе к активной области АА, это отрезок соответствует концу активной области АА, который расположен ближе к подающему участку F. Как ясно из фиг.5, сигналы 101 и 102 по существу идентичны друг другу, а импульсные напряжения в их составе также идентичны друг другу.