Область техники, к которой относится изобретение

Настоящее раскрытие относится к области технологии дисплеев и, в частности, относится к подложке дисплея и способу ее изготовления и к устройству дисплея.

Уровень техники

Подложка дисплея органического светоизлучающего устройства (Organic Light-Emitting Device, OLED) является подложкой дисплея, отличающейся от традиционного жидкокристаллического дисплея (Liquid Crystal Display, LCD), и обладает такими преимуществами, как активное свечение, хорошие температурные характеристики, низкое потребление энергии, быстрая реакция, гибкость, ультратонкость и низкая цена. Поэтому она стала одной из важных разработок и открытий для устройств дисплеев нового поколения и привлекает все больше и больше внимания.

Чтобы реализовать управление подложкой дисплея OLED на высокой частоте, на предшествующем уровне техники предложена подложка дисплея OLED с двойными линиями передачи данных, то есть, пиксели одного столбца соединяются с двумя линиями передачи данных. Однако, хотя подложка дисплея OLED на предшествующем уровне техники может реализовывать управление с высокой частотой, разрешающая способность обычно бывает низкой, что не может удовлетворить потребности в отношении высокой разрешающей способности дисплеев, предлагаемых на рынке.

Раскрытие сущности изобретения

Ниже приводится раскрытие сущности предмета изобретения, описанного здесь подробно. Это раскрытие сущности изобретения не предназначено ограничивать объем защиты формулы изобретения.

Предоставляется подложка дисплея. Подложка дисплея содержит в плоскости, параллельной подложке дисплея, множество затворных шин, множество линий передачи данных, множество шин электропитания и множество субпикселей, расположенных на базовой подложке. По меньшей мере один субпиксель содержит светоизлучающее устройство и схему управления, выполненную с возможностью управления светоизлучающим устройством для излучения света. Схема управления содержит множество транзисторов и накопительный конденсатор. Подложка дисплея в плоскости, перпендикулярной подложке дисплея, содержит базовую подложку и множество функциональных слоев, расположенных на базовой подложке. Множество функциональных слоев содержит полупроводниковый слой, первый проводящий слой, второй проводящий слой, третий проводящий слой и четвертый проводящий слой, расположенные последовательно. Первый изоляционный слой, второй изоляционный слой, третий изоляционный слой и четвертый изоляционный слой соответственно располагаются между множеством функциональных слоев. В направлении прохождения затворных шин шины электропитания соединяются друг с другом по меньшей мере через один функциональный слой.

В примерной реализации в направлении прохождения линий передачи данных шины электропитания содержат множество сублиний электропитания, соединенных последовательно, и по меньшей мере одна сублиния электропитания располагается в одном субпикселе; и сублиния электропитания по меньшей мере одного субпикселя содержит множество частей источника электропитания, соединенных последовательно, и между по меньшей мере одной частью источника электропитания и частью источника электропитания, соединенной с указанной частью источника электропитания, существует прилежащий угол более 90 градусов и меньше 180 градусов.

В примерной реализации одна часть источника электропитания из указанной по меньшей мере одной части источника электропитания и часть источника электропитания, соединенная с указанной частью источника электропитания, располагаются параллельно линиям передачи данных.

В примерной реализации сублиния электропитания содержит первую часть источника электропитания, вторую часть источника электропитания и третью часть источника электропитания; вторая часть источника электропитания выполнена с возможностью соединения первой части источника электропитания и третьей части источника электропитания, первая часть источника электропитания и третья часть источника электропитания располагаются параллельно линиям передачи данных, прилежащий угол между второй частью источника электропитания и первой частью источника электропитания больше 90 градусов и меньше 180 градусов, и прилежащий угол между второй частью источника электропитания и третьей частью источника электропитания больше 90 градусов и меньше 180 градусов.

В примерной реализации первая часть источника электропитания соединяется с третьей частью источника электропитания в субпикселе, расположенном в предыдущей строке в столбце, и третья часть источника электропитания соединяется с первой частью источника электропитания в субпикселе, расположенном в следующей строке в том же самом столбце.

В примерной реализации длина прохождения первой части источника электропитания в направлении прохождения линий передачи данных больше, чем средняя ширина первых частей источника электропитания, длина прохождения второй части источника электропитания в косом направлении больше, чем средняя ширина вторых частей источника электропитания, и длина прохождения третьей части источника электропитания в направлении прохождения линий передачи данных больше, чем средняя ширина третьих частей источника электропитания. Косое направление является направлением, в котором вторая часть источника электропитания и первая часть источника электропитания имеют прилежащий угол между ними.

В примерной реализации средняя ширина третьих частей источника электропитания меньше, чем средняя ширина первых частей источника электропитания.

В примерной реализации расстояние между краем первой части источника электропитания, ближним к стороне третьей части источника электропитания в направлении прохождения затворных шин, и краем третьей части источника электропитания, ближним к стороне первой части источника электропитания в направлении прохождения затворных шин, эквивалентно средней ширине третьих частей источника электропитания.

В примерной реализации подложка дисплея дополнительно содержит первую соединительную часть, причем второй электрод накопительного конденсатора по меньшей мере в одном субпикселе и второй электрод накопительного конденсатора в смежном субпикселе в направлении прохождения затворных шин соединяются друг с другом через первую соединительную часть; по меньшей мере в одном субпикселе между ортогональной проекцией второй части источника электропитания на базовую подложку и ортогональной проекцией второго электрода накопительного конденсатора на базовую подложку существует зона перекрытия, или между ортогональной проекцией второй части источника электропитания на базовую подложку и ортогональной проекцией первой соединительной части на базовую подложку существует зона перекрытия.

В примерной реализации между ортогональной проекцией второй части источника электропитания на базовую подложку и ортогональной проекцией первого электрода накопительного конденсатора на базовую подложку существует зона перекрытия.

В примерной реализации между ортогональной проекцией второй части источника электропитания на базовую подложку и ортогональной проекцией затворных шин на базовую подложку существует зона перекрытия.

В примерной реализации множество транзисторов содержит второй транзистор, причем между ортогональной проекцией первой части источника электропитания на базовую подложку и ортогональной проекцией второго транзистора на базовую подложку существует зона перекрытия.

В примерной реализации подложка дисплея дополнительно содержит пятый изоляционный слой, расположенный на четвертом проводящем слое, и пятый проводящий слой, расположенный на пятом изоляционном слое. В пятом изоляционном слое обеспечивается пятое сквозное отверстие, выполненное с возможностью соединения пятого проводящего слоя с четвертым проводящим слоем. Между ортогональной проекцией пятого сквозного отверстия на базовую подложку и ортогональной проекцией сублинии электропитания на базовую подложку нет зоны перекрытия.

В примерной реализации по меньшей мере в одном субпикселе между ортогональной проекцией пятого сквозного отверстия на базовую подложку и ортогональной проекцией виртуальной проходящей линии первой части источника электропитания в сублинии электропитания в направлении прохождения линий передачи данных на базовой подложке существует зона перекрытия.

В примерной реализации в первом изоляционном слое, втором изоляционном слое и третьем изоляционном слое обеспечивается восьмое сквозное отверстие, выполненным с возможностью разрешения линии передачи данных записывать сигнал данных на полупроводниковый слой. Между ортогональной проекцией восьмого сквозного отверстия на базовую подложку и ортогональными проекциями первой части источника электропитания и второй части источника электропитания в сублинии электропитания на базовую подложку нет зоны перекрытия.

В примерной реализации по меньшей мере в одном субпикселе между ортогональной проекцией восьмого сквозного отверстия на базовую подложку и ортогональной проекцией виртуальной линии прохождения третьей части источника электропитания в сублинии электропитания в направлении прохождения линий передачи данных на базовую подложку существует зона перекрытия.

В примерной реализации шины электропитания располагаются на третьем проводящем слое или на четвертом проводящем слое, и шины электропитания располагаются на том же самом слое, что и линии передачи данных.

В примерной реализации шины электропитания располагаются на третьем проводящем слое, а линии передачи данных располагаются на четвертом проводящем слое, или линии передачи данных располагаются на третьем проводящем слое, а шины электропитания располагаются на четвертом проводящем слое.

В примерной реализации подложка дисплея дополнительно содержит первую соединительную часть. Второй электрод накопительного конденсатора по меньшей мере в одном субпикселе и второй электрод накопительного конденсатора в смежном субпикселе в направлении прохождения затворных шин соединяются друг с другом через первую соединительную часть.

В примерной реализации существует по меньшей мере одна зона, содержащая 2*4 субпикселей. В одной строке второй электрод накопительного конденсатора в первом субпикселе и второй электрод накопительного конденсатора во втором субпикселе соединяются друг с другом через первую соединительную часть, второй электрод накопительного конденсатора во втором первом субпикселе напрямую соединяется со вторым электродом накопительного конденсатора в третьем субпикселе, и второй электрод накопительного конденсатора в третьем субпикселе и второй электрод накопительного конденсатора в четвертом субпикселе соединяются друг с другом через первую соединительную часть. В другой строке второй электрод накопительного конденсатора в первом субпикселе напрямую соединяется со вторым электродом накопительного конденсатора во втором субпикселе, второй электрод накопительного конденсатора во втором субпикселе и второй электрод накопительного конденсатора в третьем субпикселе соединяются друг с другом через первую соединительную часть, и второй электрод накопительного конденсатора в третьем субпикселе напрямую соединяется со вторым электродом накопительного конденсатора в четвертом субпикселе.

В примерной реализации полупроводниковый слой в первом субпикселе располагается с интервалом относительно полупроводникового слоя во втором субпикселе, полупроводниковый слой во втором субпикселе располагается с интервалом относительно полупроводникового слоя в третьем субпикселе, и полупроводниковый слой в третьем субпикселе располагается с интервалом относительно полупроводникового слоя в четвертом субпикселе.

В примерной реализации третий проводящий слой содержит первый вывод пятого транзистора. Первый вывод пятого транзистора в первом субпикселе располагается с интервалом относительно первого вывода пятого транзистора во втором субпикселе, первый вывод пятого транзистора во втором субпикселе располагается с интервалом относительно первого вывода пятого транзистора в третьем субпикселе, и первый вывод пятого транзистора в третьем субпикселе располагается с интервалом относительно первого вывода пятого транзистора в четвертом субпикселе.

В примерной реализации существует по меньшей мере одна зона, содержащая 2*4 субпикселей. В одной строке второй электрод накопительного конденсатора в первом субпикселе и второй электрод накопительного конденсатора во втором субпикселе соединяются друг с другом через первую соединительную часть, второй электрод накопительного конденсатора во втором субпикселе отсоединен от второго электрода накопительного конденсатора в третьем субпикселе, и второй электрод накопительного конденсатора в третьем субпикселе и второй электрод накопительного конденсатора в четвертом субпикселе соединяются друг с другом через первую соединительную часть. В другой строке второй электрод накопительного конденсатора в первом субпикселе отсоединен от второго электрода накопительного конденсатора во втором субпикселе, второй электрод накопительного конденсатора во втором субпикселе и второй электрод накопительного конденсатора в третьем субпикселе соединяются друг с другом через первую соединительную часть, и второй электрод накопительного конденсатора в третьем субпикселе отсоединен от второго электрода накопительного конденсатора в четвертом субпикселе.

В примерной реализации третий проводящий слой содержит первый вывод пятого транзистора и вторую соединительную часть. В одной строке первый вывод пятого транзистора в первом субпикселе отсоединен от первого вывода пятого транзистора во втором субпикселе, первый вывод пятого транзистора во втором субпикселе, первый вывод пятого транзистора в третьем субпикселе соединяются друг с другом через вторую соединительную часть, и первый вывод пятого транзистора в третьем субпикселе отсоединен от первого вывода пятого транзистора в четвертом субпикселе. В другой строке первый вывод пятого транзистора в первом субпикселе и первый вывод пятого транзистора во втором субпикселе соединяются друг с другом через вторую соединительную часть, первый вывод пятого транзистора во втором субпикселе отсоединен от первого вывода пятого транзистора в третьем субпикселе, и первый вывод пятого транзистора в третьем субпикселе и первый вывод пятого транзистора в четвертом субпикселе соединяются друг с другом через вторую соединительную часть.

В примерной реализации в направлении прохождения затворных шин шины электропитания соединяются друг с другом через вторые электроды накопительных конденсаторов и первые выводы пятых транзисторов.

В примерной реализации в четвертом изоляционном слое обеспечиваются первые сквозные отверстия, обеспечивающие доступ к первым выводам пятых транзисторов, в третьем изоляционном слое обеспечиваются вторые сквозные отверстия, обеспечивающие доступ ко вторым электродам накопительных конденсаторов, шины электропитания соединяются с первыми выводами пятых транзисторов через первые сквозные отверстия и первые выводы пятых транзисторов соединяются со вторыми электродами накопительных конденсаторов через вторые сквозные отверстия.

В примерной реализации по меньшей мере в одном субпикселе существует одно сквозное отверстие и множество вторых сквозных отверстий и множество вторых сквозных отверстий располагаются в направлении прохождения линий передачи данных. Ортогональная проекция шин электропитания на базовую подложку содержит ортогональную проекцию первого сквозного отверстия на базовую подложку и ортогональная проекция первого вывода пятого транзистора на базовую подложку содержит ортогональную проекцию вторых сквозных отверстий на базовую подложку.

В примерной реализации полупроводниковый слой содержит третью соединительную часть. В одной строке полупроводниковый слой в первом субпикселе отсоединен от полупроводникового слоя во втором субпикселе, полупроводниковый слой во втором субпикселе и полупроводниковый слой в третьем субпикселе соединяются друг с другом через третью соединительную часть, и полупроводниковый слой в третьем субпикселе отсоединен от полупроводникового слоя в четвертом субпикселе. В другой строке полупроводниковый слой в первом субпикселе и полупроводниковый слой во втором субпикселе соединяются друг с другом через третью соединительную часть, полупроводниковый слой во втором субпикселе отсоединен от полупроводникового слоя в третьем субпикселе и полупроводниковый слой в третьем субпикселе, и полупроводниковый слой в четвертом субпикселе соединяются друг с другом через третью соединительную часть.

В примерной реализации в направлении прохождения затворных шин шины электропитания соединяются друг с другом через третью соединительную часть полупроводникового слоя и вторые электроды накопительных конденсаторов.

В примерной реализации в третьем изоляционном слое обеспечиваются одиннадцатые сквозные отверстия, обеспечивающие доступ ко вторым электродам накопительных конденсаторов, и в первом изоляционном слое, втором изоляционном слое и третьем изоляционном слое обеспечиваются двенадцатые сквозные отверстия, обеспечивающие доступ к третьей соединительной части полупроводникового слоя. Шины электропитания соединяются со вторыми электродами накопительных конденсаторов через одиннадцатые сквозные отверстия, и шины электропитания соединяются с третьей соединительной частью полупроводникового слоя через двенадцатые сквозные отверстия.

В примерной реализации, по меньшей мере в одном субпикселе существуют одно одиннадцатое сквозное отверстие и множество двенадцатых сквозных отверстий. Множество двенадцатых сквозных отверстий располагаются в направлении прохождения линий передачи данных. Ортогональная проекция шин электропитания на базовую подложку содержит ортогональные проекции одиннадцатого сквозного отверстия и двенадцатых сквозных отверстий на базовую подложку.

В примерной реализации множество транзисторов содержит первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, пятый транзистор, шестой транзистор и седьмой транзистор. По меньшей мере в одном субпикселе полупроводниковый слой по меньшей мере содержит первую активную область в месте, в котором располагается первый транзистор, вторую активную область в месте, в котором располагается второй транзистор, третью активную область в месте, в котором располагается третий транзистор, четвертую активную область в месте, в котором располагается четвертый транзистор, пятую активную область в месте, в котором располагается пятый транзистор, шестую активную область в месте, в котором располагается шестой транзистор, и седьмую активную область в месте, в котором располагается седьмой транзистор. Первая активная область, вторая активная область, третья активная область, четвертая активная область, пятая активная область, шестая активная область и седьмая активная область являются интегрированной структурой.

В примерной реализации расстояние между второй активной областью и первой активной областью в направлении прохождения затворных шин меньше, чем расстояние между второй активной областью и седьмой активной областью в направлении прохождения затворных шин.

В примерной реализации седьмая активная область и первая активная область последовательно располагаются в направлении от линий передачи данных к шинам электропитания, на которые записываются сигналы данных.

В примерной реализации по меньшей мере один субпиксель содержит первую область, вторую область и третью область, которые располагаются последовательно в направлении прохождения линий передачи данных. Первая активная область и седьмая активная область располагаются на стороне первой области, дальней от второй области, вторая активная область и четвертая активная область располагаются на стороне первой области, ближней ко второй области, третья активная область располагается во второй области, а пятая активная область и шестая активная область располагаются в третьей области.

В примерной реализации первый вывод первого транзистора соединяется с линией сигнала инициирования, второй вывод первого транзистора T1 соединяется с первым электродом накопительного конденсатора, первый вывод второго транзистора соединяется с первым электродом накопительного конденсатора, второй вывод второго транзистора соединяется со вторым выводом шестого транзистора, первый вывод третьего транзистора соединяется со вторым выводом четвертого транзистора, второй вывод третьего транзистора соединяется со вторым выводом шестого транзистора, первый вывод четвертого транзистора соединяется с линией передачи данных, первый вывод пятого транзистора соединяется с шиной электропитания, второй вывод пятого транзистора соединяется с первым выводом третьего транзистора, второй вывод шестого транзистора соединяется с анодом светоизлучающего устройства, первый вывод седьмого транзистора соединяется с линией сигнала инициирования, второй вывод седьмого транзистора соединяется с анодом светоизлучающего устройства; первая активная область соответственно соединяется со второй активной областью и седьмой активной областью, вторая активная область соответственно соединяется с третьей активной областью и шестой активной областью, и четвертая активная область соответственно соединяется с третьей активной областью и пятой активной областью.

В примерной реализации полупроводниковые слои смежных субпикселей симметричны друг другу в направлении прохождения затворных шин.

В примерной реализации существует по меньшей мере одна зона, содержащая 2*2 субпикселей. Форма полупроводникового слоя в первом субпикселе в одной строке является такой же, как форма полупроводникового слоя во втором субпикселе в другой строке, и форма полупроводникового слоя во втором субпикселе в одной строке является такой же, как форма полупроводникового слоя в первом субпикселе в другой строке.

В примерной реализации полупроводниковый слой содержит третью соединительную часть. Полупроводниковый слой по меньшей мере в одном субпикселе соединяется с полупроводниковым слоем в смежном субпикселе в направлении прохождения затворных шин через третью соединительную часть.

В примерной реализации третья соединительную часть соединяется с активной областью пятого транзистора.

В примерной реализации между ортогональной проекцией третьей соединительной части на базовую подложку и ортогональной проекцией шин электропитания на базовую подложку существует зона перекрытия.

В примерной реализации в первом изоляционном слое, втором изоляционном слое и третьем изоляционном слое обеспечиваются двенадцатые сквозные отверстия, обеспечивающие доступ к третьей соединительной части, и шины электропитания соединяются с третьей соединительной частью через двенадцатые сквозные отверстия.

В примерной реализации существует по меньшей мере одна зона, содержащая 2*4 субпикселей. В одной строке полупроводниковый слой в первом субпикселе отсоединен от полупроводникового слоя во втором субпикселе, полупроводниковый слой во втором субпикселе и полупроводниковый слой в третьем субпикселе соединяются друг с другом через третью соединительную часть, и полупроводниковый слой в третьем субпикселе отсоединен от полупроводникового слоя в четвертом субпикселе. В другой строке полупроводниковый слой в первом субпикселе и полупроводниковый слой во втором субпикселе соединяются друг с другом через третью соединительную часть, полупроводниковый слой во втором субпикселе отсоединен от полупроводникового слоя в третьем субпикселе, и полупроводниковый слой в третьем субпикселе и полупроводниковый слой в четвертом субпикселе соединяются друг с другом через третью соединительную часть.

В примерной реализации существует по меньшей мере один пиксельный столбец, и в направлении прохождения линий передачи данных линия передачи данных содержит множество сублиний передачи данных, соединенных последовательно; и существует по меньшей мере один субпиксель, так что две сублинии передачи данных располагаются между субпикселем и смежным субпикселем в направлении прохождения затворных шин.

В примерной реализации эти две сублинии передачи данных параллельны друг другу.

В примерной реализации, по меньшей мере в одном субпикселе в первом изоляционном слое, втором изоляционном слое и третьем изоляционном слое обеспечиваются восьмые сквозные отверстия, обеспечивающие доступ к полупроводниковому слою, в четвертом изоляционном слое обеспечиваются третьи сквозные отверстия, обеспечивающие доступ к первому выводу четвертого транзистора, линия передачи данных соединяется с первым выводом четвертого транзистора через третье сквозное отверстие, и первый вывод четвертого транзистора соединяется с полупроводниковым слоем через восьмое сквозное отверстие.

В примерной реализации в направлении прохождения затворных шин восьмые сквозные отверстия смежных субпикселей симметричны друг другу.

В примерной реализации линии передачи данных располагаются на третьем проводящем слое, и шины электропитания располагаются на третьем проводящем слое.

В примерной реализации линии передачи данных располагаются на четвертом проводящем слое, и шины электропитания располагаются на третьем проводящем слое или на четвертом проводящем слое.

В примерной реализации по меньшей мере в одном столбце субпикселей линия передачи данных содержит первую сублинию передачи данных и вторую сублинию передачи данных, которые располагаются на двух сторонах столбца субпикселей соответственно.

В примерной реализации шина электропитания располагается между первой сублинией передачи данных и второй сублинией передачи данных.

В примерной реализации пиксельные структуры смежных субпикселей симметричны друг другу в направлении прохождения затворных шин.

В примерной реализации существует по меньшей мере одна зона, содержащая 2*2 субпикселей, в которой пиксельная структура первого субпикселя в одной строке является такой же, что и пиксельная структура второго субпикселя в другой строке, и пиксельная структура второго субпикселя в одной строке является такой же, что и пиксельная структура первого субпикселя в другой строке.

В примерной реализации подложка дисплея дополнительно содержит линию сигнала сброса, линию управления светоизлучением и линию сигнала инициирования; полупроводниковый слой содержит по меньшей мере активные области множества транзисторов, первый проводящий слой содержит по меньшей мере затворную шину, линию управления светоизлучением, линию сигнала сброса, первый электрод накопительного конденсатора и электроды затворов множества транзисторов, второй проводящий слой содержит по меньшей мере линию сигнала инициирования и второй электрод накопительного конденсатора; и третий проводящий слой содержит по меньшей мере электроды истока и стока множества транзисторов, и четвертый проводящий слой содержит по меньшей мере линию передачи данных и шину электропитания.

В примерной реализации по меньшей мере один субпиксель содержит первую область, вторую область и третью область, которые последовательно располагаются в направлении прохождения линии передачи данных; и затворная шина, линия сигнала инициирования и линия сигнала сброса располагаются в первой области, первый электрод и второй электрод накопительного конденсатора располагаются во второй области и линия управления светоизлучением располагается в третьей области.

В примерной реализации второй проводящий слой дополнительно содержит экранный электрод, и по меньшей мере в одном субпикселе между ортогональной проекцией экранного электрода на базовую подложку и ортогональной проекцией шин электропитания на базовую подложку существует зона перекрытия.

В примерной реализации шина электропитания соединяется с экранным электродом через сквозное отверстие.

В примерной реализации экранный электрод располагается между затворной шиной и линией сигнала сброса в направлении прохождения линий передачи данных.

В примерной реализации экранный электрод содержит первую часть, проходящую в направлении прохождения затворных шин, и вторую часть, проходящую в направлении прохождения линий передачи данных, и конец первой части вблизи второй части соединяется с концом второй части вблизи первой части.

В примерной реализации первый проводящий слой дополнительно содержит блок затворов, проходящий в направлении прохождения линий передачи данных. Блок затворов соединяется с затворной шиной. В направлении прохождения линий передачи данных блок затворов и вторая часть экранного электрода имеют зоны, расположенные между ними напротив друг друга.

В примерной реализации электроды истока и стока множества транзисторов содержат первый вывод второго транзистора. Во втором изоляционном слое и третьем изоляционном слое обеспечиваются седьмые сквозные отверстия, обеспечивающие доступ к первому электроду накопительного конденсатора. В первом изоляционном слое, втором изоляционном слое и третьем изоляционном слое обеспечиваются девятые сквозные отверстия, обеспечивающие доступ к активной областивторого транзистора. Один конец первого вывода второго транзистора соединяется с первым электродом накопительного конденсатора через седьмое сквозное отверстие, а другой конец первого вывода второго транзистора соединяется с активной областью второго транзистора через девятое сквозное отверстие.

В примерной реализации между ортогональной проекцией первого вывода второго транзистора на базовую подложку и ортогональной проекцией затворной шины на базовую подложку существует зона перекрытия, и между ортогональной проекцией первого вывода второго транзистора на базовую подложку и ортогональными проекциями линии управления светоизлучением, линии сигнала сброса и линии сигнала инициирования на базовую подложку не существует зоны перекрытия.

В примерной реализации электроды истока и стока множества транзисторов содержат первый вывод первого транзистора. В третьем изоляционном слое обеспечиваются шестые сквозные отверстиям, обеспечивающие доступ к линии сигналаинициирования. В первом изоляционном слое, втором изоляционном слое и третьем изоляционном слое обеспечиваются десятые сквозные отверстия, обеспечивающие доступ к активной области первого транзистора. Один конец первого вывода первого транзистора соединяется с линией сигнала инициирования через шестое сквозное отверстие, а другой конец первого вывода первого транзистора соединяется с активной областью первого транзистора через десятое сквозное отверстие.

В примерной реализации между ортогональной проекцией первого вывода первого транзистора на базовую подложку и ортогональной проекцией линии сигнала сброса на базовую подложку существует зона перекрытия, а между ортогональной проекцией первого вывода первого транзистора на базовую подложку и ортогональными проекциями затворной шины и линии управления светоизлучением на базовую подложку нет зоны перекрытия.

В примерной реализации подложка дисплея дополнительно содержит пятый изоляционный слой, расположенный на четвертом проводящем слое, и пятый проводящий слой, расположенный на пятом изоляционном слое. Четвертый проводящий слой дополнительно содержит соединительный электрод, и электроды истока и стока множества транзисторов содержат второй вывод шестого транзистора. В четвертом изоляционном слое обеспечиваются четвертые сквозные отверстия, обеспечивающие доступ ко второму выводу шестого транзистора, и в пятом изоляционном слое обеспечиваются пятые сквозные отверстия, обеспечивающие доступ к соединительному электроду. Соединительный электрод соединяется со вторым выводом шестого транзистора через четвертое сквозное отверстие, и пятый проводящий слой соединяется с соединительным электродом через пятое сквозное отверстие.

В примерной реализации существует между ортогональной проекцией соединительного электрода на базовую подложку и ортогональной проекцией первого вывода второго транзистора на базовую подложку существует зона перекрытия.

В примерной реализации по меньшей мере один субпиксель содержит по меньшей мере: первое сквозное отверстие, обеспечивающее доступ к первому выводу пятого транзистора, причем первое сквозное отверстие выполнено с возможностью соединения первого вывода пятого транзистора с шиной электропитания; второе сквозное отверстие, обеспечивающее доступ ко второму электроду накопительного конденсатора, причем второе сквозное отверстие выполнено с возможностью соединения второго электрода с первым выводом пятого транзистора; третье сквозное отверстие, обеспечивающее доступ к первому выводу четвертого транзистора, причем третье сквозное отверстие выполнено с возможностью соединения первого вывода четвертого транзистора с линией передачи данных; четвертое сквозное отверстие, обеспечивающее доступ ко второму выводу шестого транзистора, причем четвертое сквозное отверстие выполнено с возможностью соединения второго вывода шестого транзистора с соединительным электродом; пятое сквозное отверстие, обеспечивающее доступ к соединительному электроду, причем пятое сквозное отверстие выполнено с возможностью соединения соединительного электрода с анодом пятого проводящего слоя; шестое сквозное отверстие, обеспечивающее доступ к линии сигнала инициирования, причем шестое сигнальное отверстие выполнено с возможностью соединения линии сигнала инициирования с первым выводом первого транзистора; седьмое сквозное отверстие, обеспечивающее доступ к первому электроду накопительного конденсатора, причем седьмое сквозное отверстие выполнено с возможностью соединения первого электрода с первым выводом второго транзистора; восьмое сквозное отверстие, обеспечивающее доступ к активной области четвертого транзистора, причем восьмое сквозное отверстие выполнено с возможностью соединения активной области четвертого транзистора с первым выводом четвертого транзистора; девятое сквозное отверстие, обеспечивающее доступ к активной области второго транзистора, причем девятое сквозное отверстие выполнено с возможностью соединения активной области второго транзистора с первым выводом второго транзистора; и десятое сквозное отверстие, обеспечивающее доступ к активной области первого транзистора, причем десятое сквозное отверстие выполнено с возможностью соединения активной области первого транзистора с первым выводом первого транзистора.

В примерной реализации по меньшей мере один субпиксель содержит, по меньшей мере: одиннадцатое сквозное отверстие, обеспечивающее доступ ко второму электроду накопительного конденсатора, причем одиннадцатое сквозное отверстие выполнено с возможностью соединения второго электрода с шиной электропитания; и двенадцатое сквозное отверстие, обеспечивающее доступ к третьей соединительной части, причем двенадцатое соединительное отверстие выполнено с возможностью соединения третьей соединительной части с шиной электропитания.

Представляется устройство дисплея, содержащее вышеупомянутую подложку дисплея.

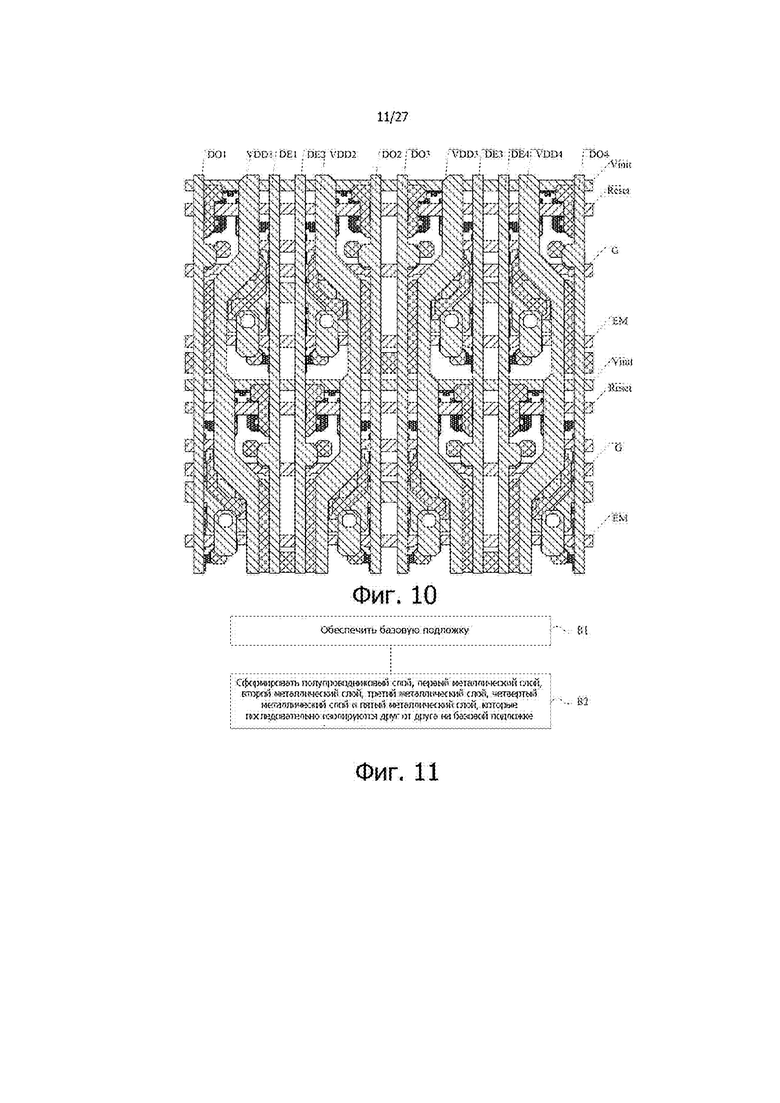

Обеспечивается способ изготовления подложки дисплея, выполненный с возможностью изготовления подложки дисплея в соответствии с любым из пп. 1-69 формулы изобретения. Подложка дисплея содержит в плоскости, параллельной подложке дисплея, затворные шины, линии передачи данных, шины электропитания и множество субпикселей, расположенных на базовой подложке. По меньшей мере один субпиксель содержит светоизлучающее устройство и схему управления, выполненную с возможностью управления светоизлучающим устройством для излучения света, и схема управления содержит множество транзисторов и накопительный конденсатор.

Способ содержит этапы, на которых: обеспечивают базовую подложку; и формируют на базовой подложке множество функциональных слоев, причем множество функциональных слоев содержит полупроводниковый слой, первый проводящий слой, второй проводящий слой, третий проводящий слой и четвертый проводящий слой, располагающиеся последовательно, причем первый изоляционный слой, второй изоляционный слой, третий изоляционный слой и четвертый изоляционный слой располагаются соответственно между множеством функциональных слоев и в направлении прохождения затворных шин, причем шины электропитания соединяются друг с другом по меньшей мере через один функциональный слой.

Другие варианты станут очевидны после прочтения и понимания сопроводительных чертежей и подробного описания.

Краткое описание чертежей

Сопроводительные чертежи используются для обеспечения понимания технических решений настоящего раскрытия и составляют часть описания. Вместе с вариантами осуществления настоящего раскрытия, они используются для объяснения технических решений настоящего раскрытия и не составляют ограничения технических решений настоящего раскрытия.

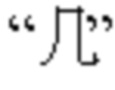

Фиг. 1 - структурная схема подложки дисплея, соответствующей настоящему раскрытию.

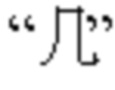

Фиг. 2 - вид сбоку субпикселя в подложке дисплея, соответствующей настоящему раскрытию.

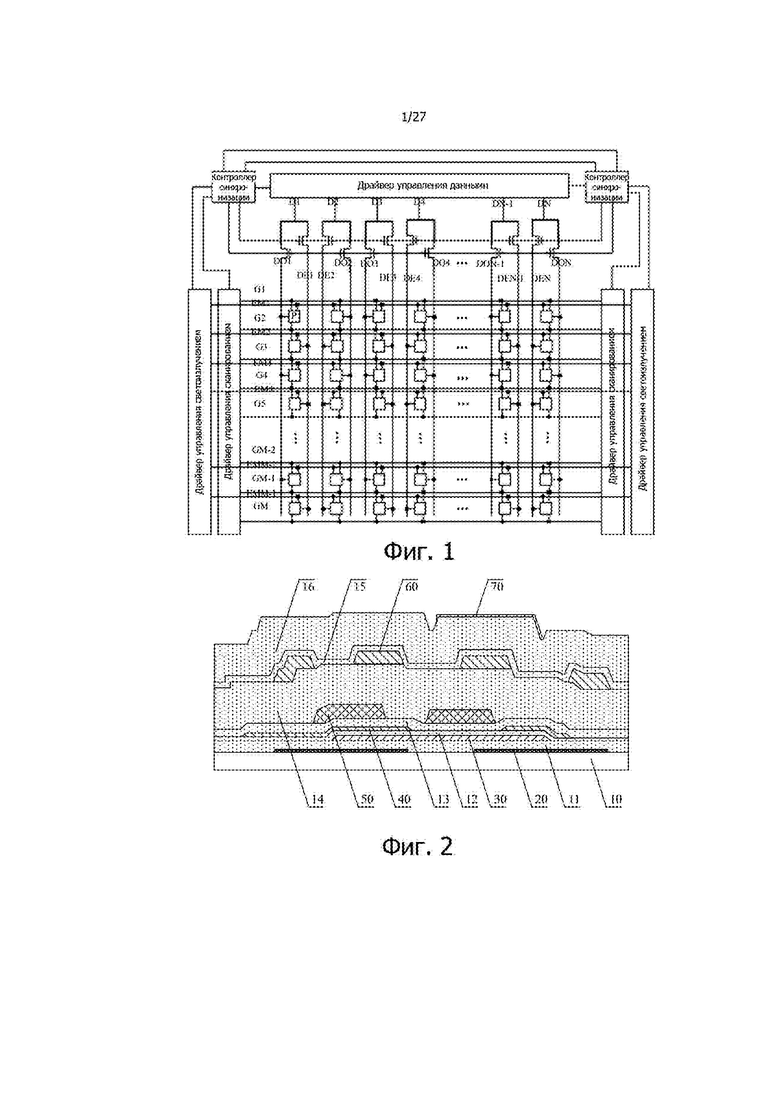

Фиг. 3 – вид сверху субпикселя в подложке дисплея, соответствующей настоящему раскрытию.

Фиг. 4A – эквивалентная диаграмма схемы управления, соответствующей настоящему раскрытию.

Фиг. 4B – диаграмма работы синхронизации схемы управления, соответствующей настоящему раскрытию.

Фиг. 5 - вид сверху множества субпикселей в подложке дисплея, соответствующей настоящему раскрытию.

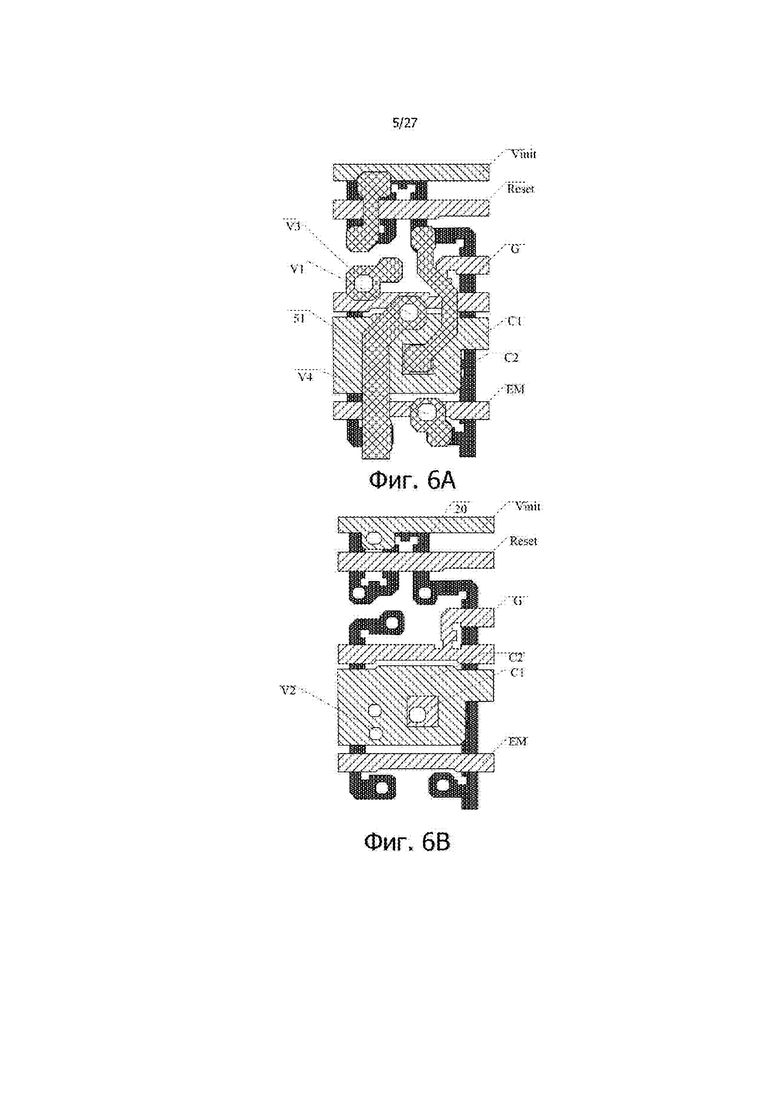

Фиг. 6A – вид сверху субпикселя, соответствующего реализации I.

Фиг. 6B - другой вид сверху субпикселя, соответствующего реализации I.

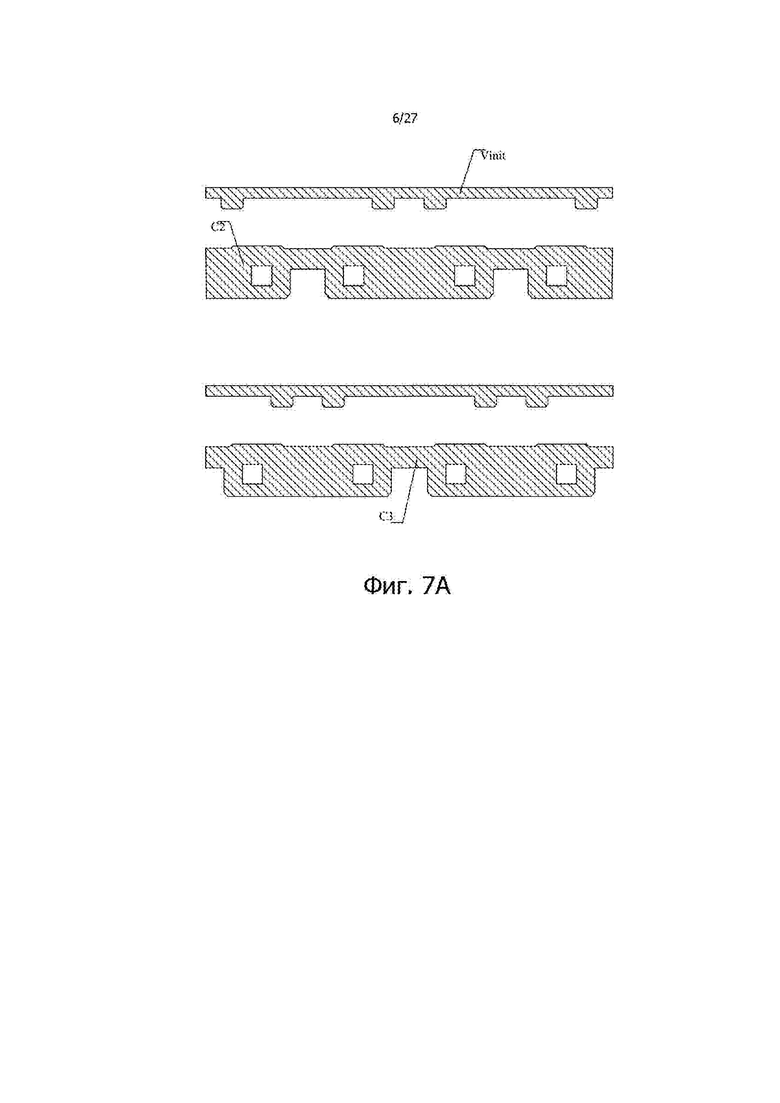

Фиг. 7A – вид сверху второго металлического слоя, соответствующего реализации I.

Фиг. 7B – вид сверху третьего металлического слоя, соответствующего реализации I.

Фиг. 8A - вид сверху субпикселя, соответствующего реализации II .

Фиг. 8B - другой вид сверху субпикселя, соответствующего реализации II.

Фиг. 9A - вид сверху второго металлического слоя, соответствующего реализации II.

Фиг. 9B - вид сверху третьего металлического слоя, соответствующего реализации II.

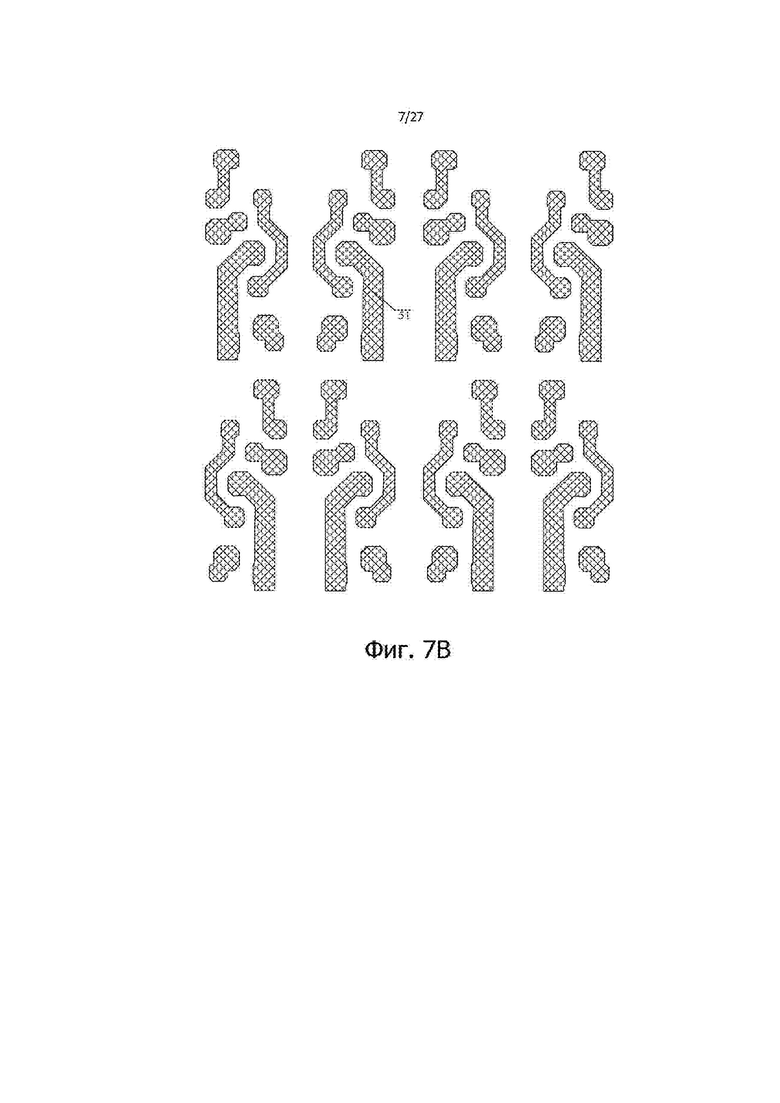

Фиг. 10 - другой вид сверху множества субпикселей в подложке дисплея, соответствующей настоящему раскрытию.

Фиг. 11 - блок-схема последовательности выполнения операций способа изготовления подложки дисплея, соответствующей настоящему раскрытию.

Фиг. 12 – первая технологическая диаграмма изготовления подложки дисплея, соответствующей настоящему раскрытию.

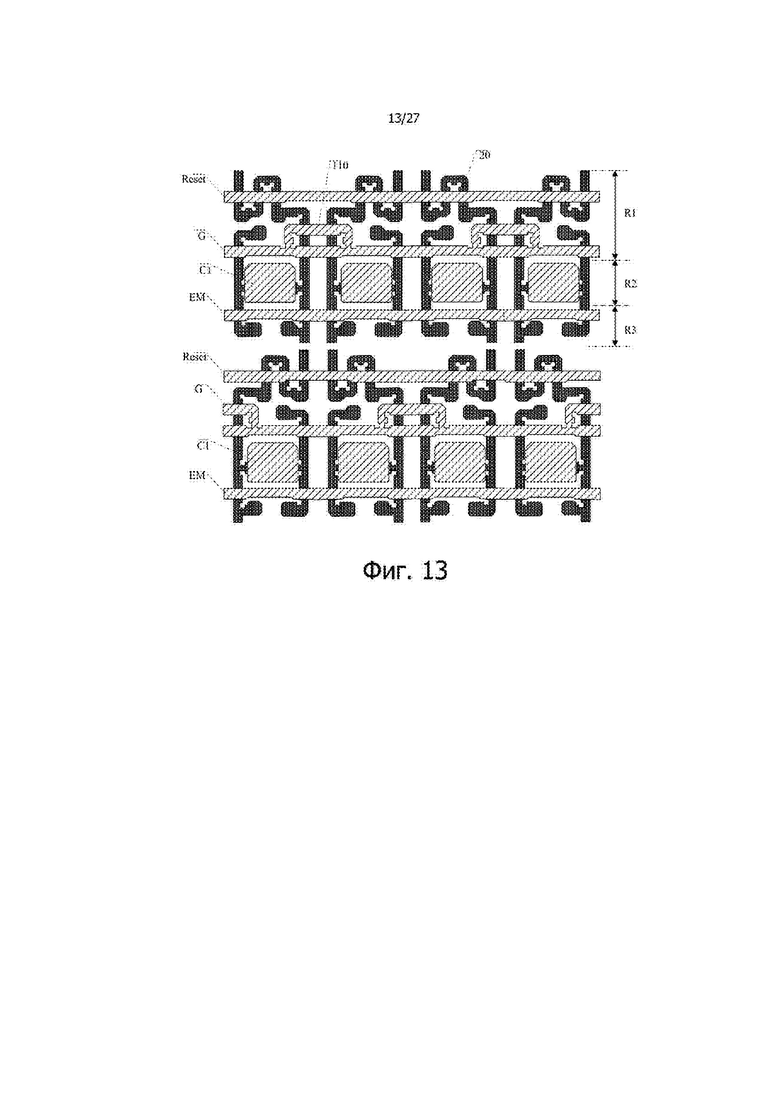

Фиг. 13 – вторая технологическая диаграмма изготовления подложки дисплея, соответствующей согласно настоящему раскрытию.

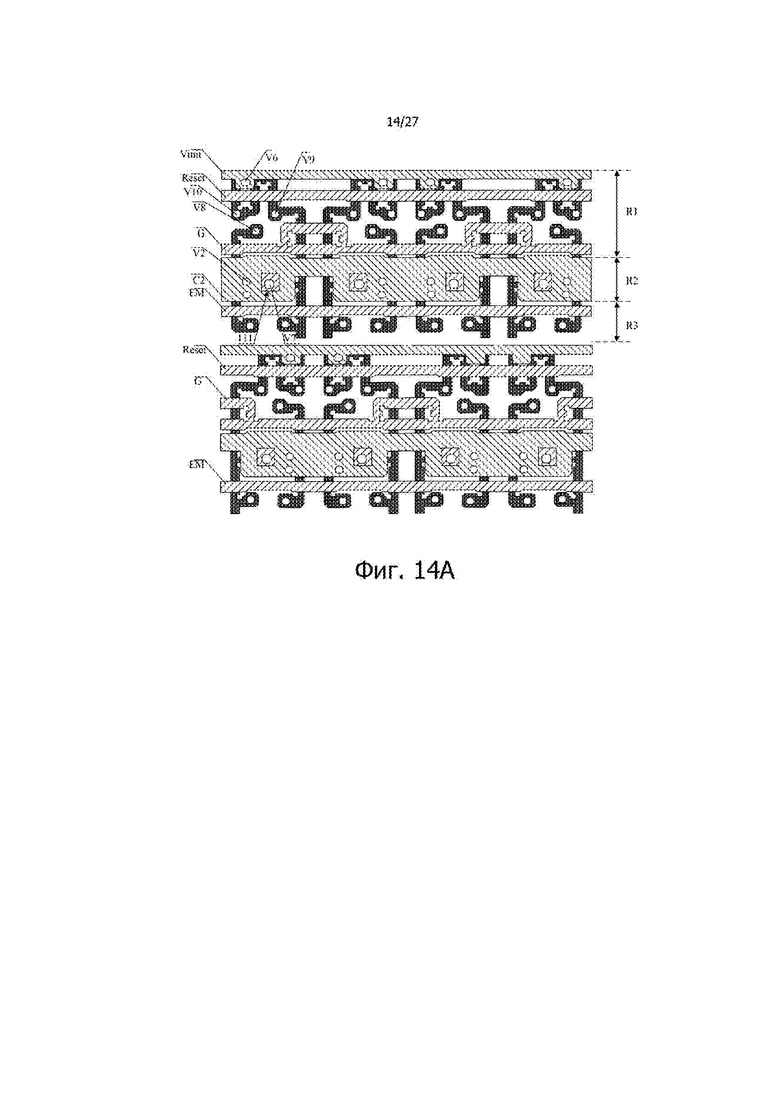

Фиг. 14A - третьей технологическая диаграмма изготовления подложки дисплея, соответствующей настоящему раскрытию.

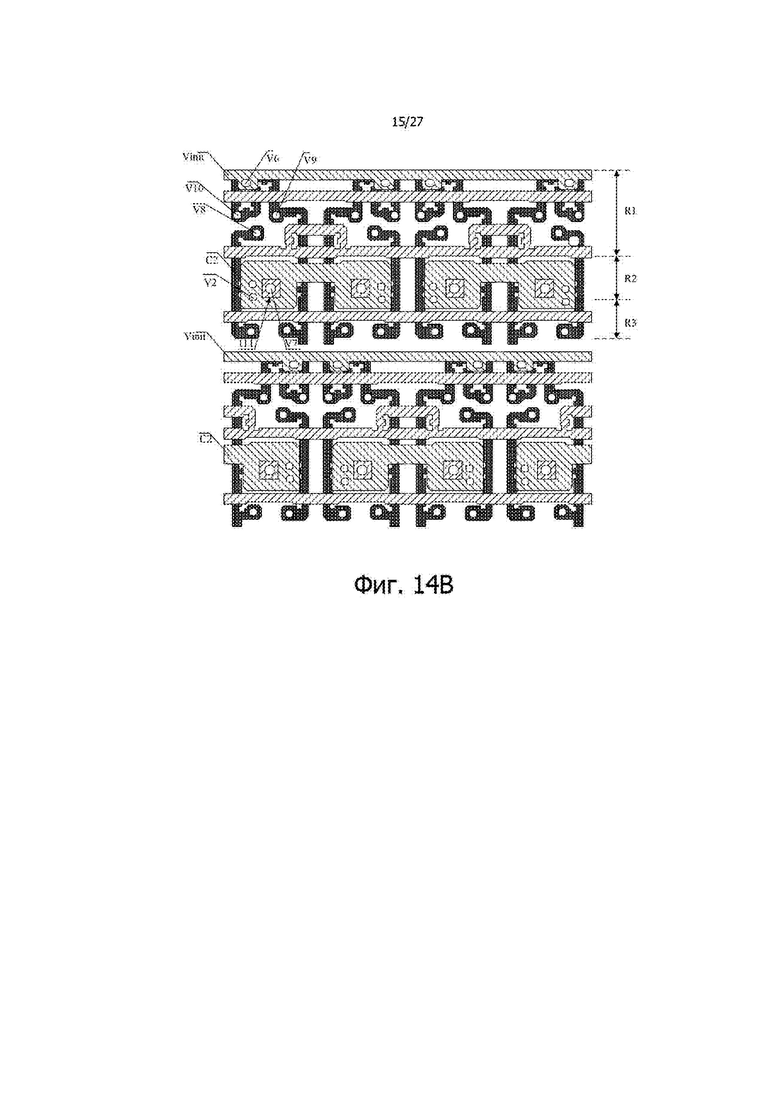

Фиг. 14B - другая третья технологическая диаграмма изготовления подложки дисплея, соответствующей настоящему раскрытию.

Фиг. 15A - четвертая технологическая диаграмма изготовления подложки дисплея, соответствующей настоящему раскрытию.

+Фиг. 15B - другая четвертая технологическая диаграмма изготовления подложки дисплея, соответствующей настоящему раскрытию.

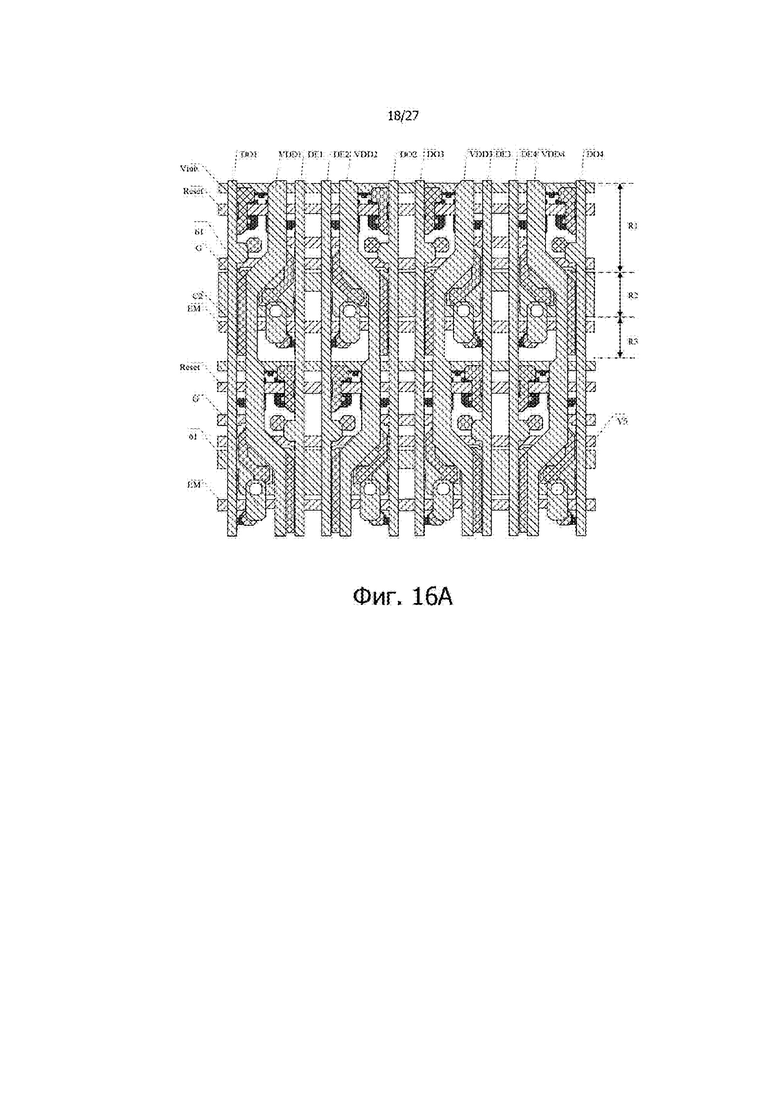

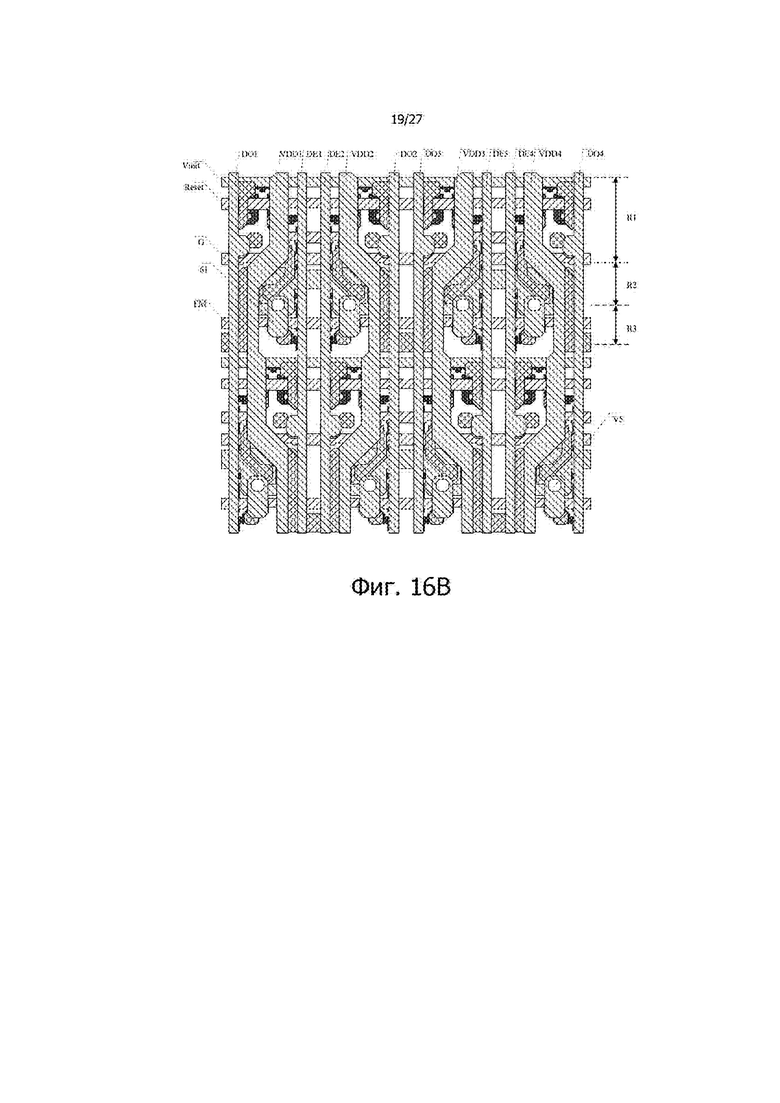

Фиг. 16A – пятая технологическая диаграмм изготовления подложки дисплея, соответствующей настоящему раскрытию.

Фиг. 16B - другая пятая технологическая диаграмма изготовления подложки дисплея, соответствующей настоящему раскрытию.

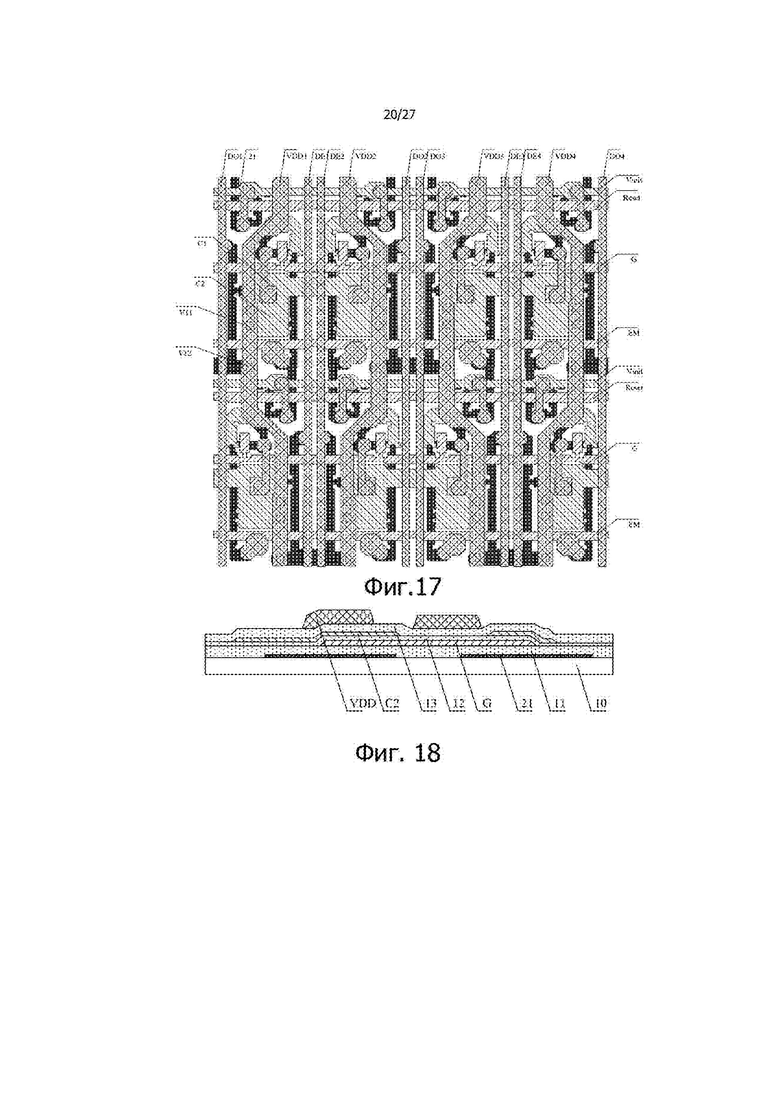

Фиг. 17 - вид сверху множества субпикселей в другой подложке дисплея, соответствующей настоящему раскрытию.

Фиг. 18 - вид в разрезе множества субпикселей в другой подложке дисплея, соответствующей настоящему раскрытию.

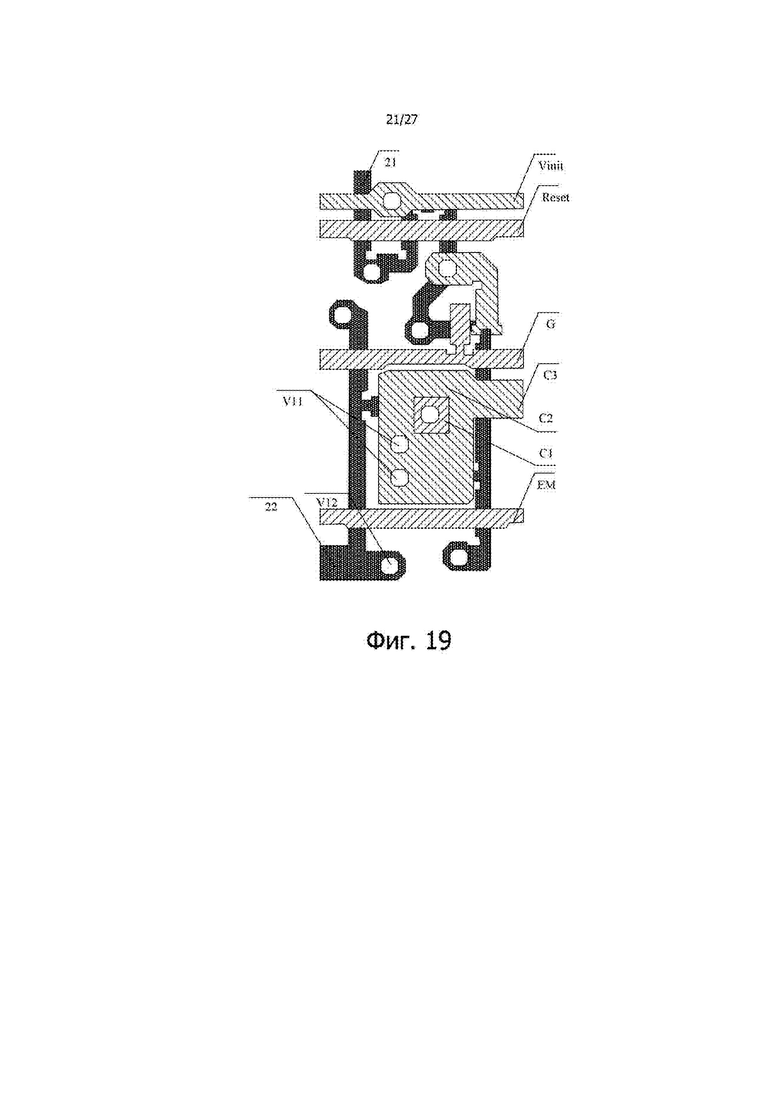

Фиг. 19 - частичный вид сверху субпикселя в другой подложке дисплея, соответствующей настоящему раскрытию.

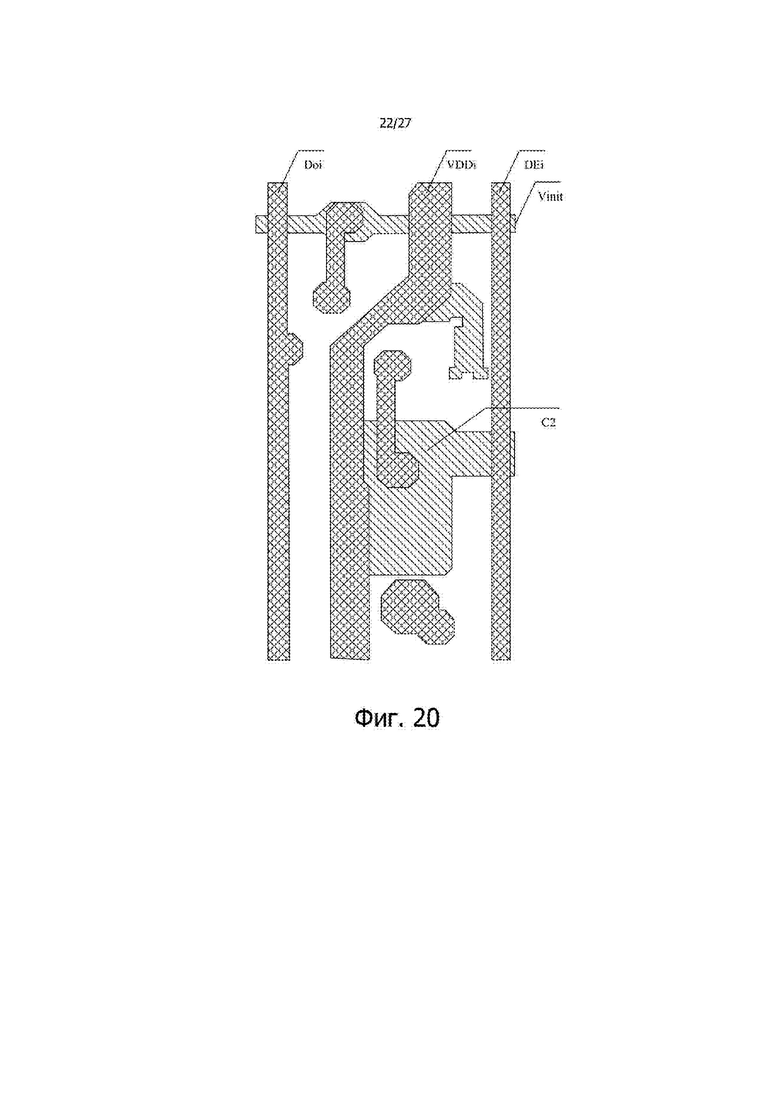

Фиг. 20 - другой частичный вид сверху субпикселя в другой подложке дисплея, соответствующей настоящему раскрытию.

Фиг. 21 - дополнительный частичный вид сверху субпикселя в другой подложке дисплея, соответствующей настоящему раскрытию.

Фиг. 22 - блок-схема последовательности выполнения операций способа изготовления другой подложки дисплея, соответствующей настоящему раскрытию.

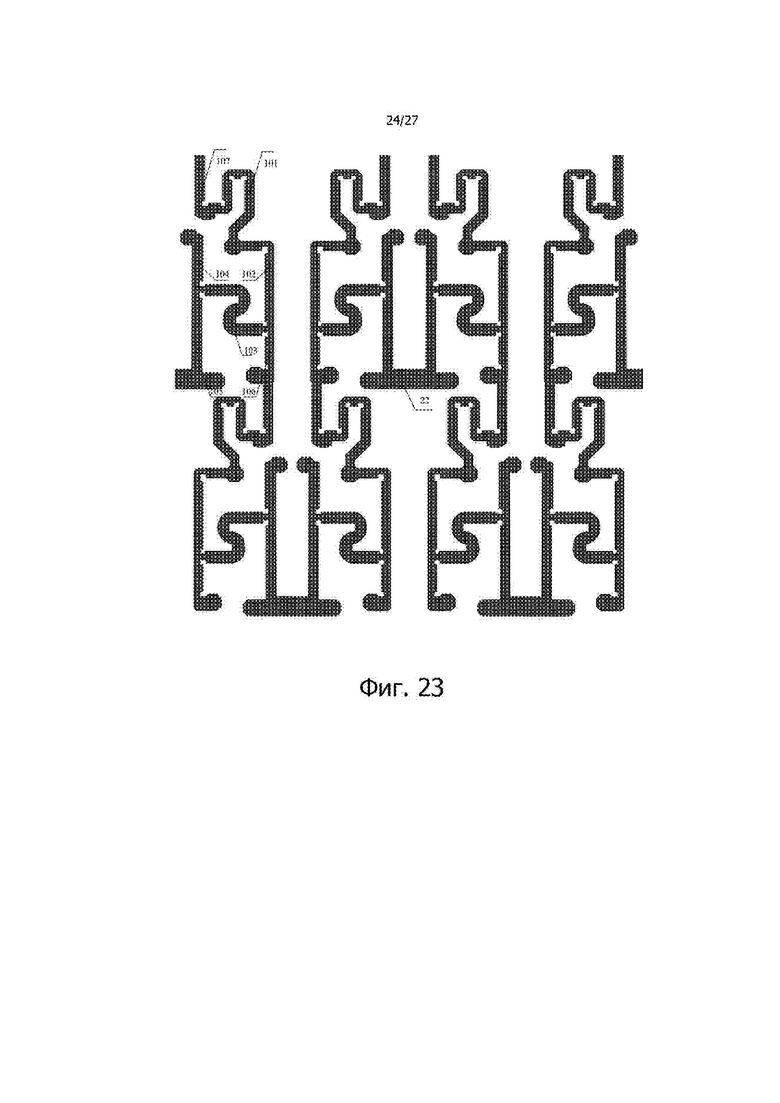

Фиг. 23 - схема изготовления активной области другой подложки дисплея, соответствующей настоящему раскрытию.

Фиг. 24 - схема изготовления первого изоляционного слоя и первого металлического слоя другой подложки дисплея, соответствующей настоящему раскрытию.

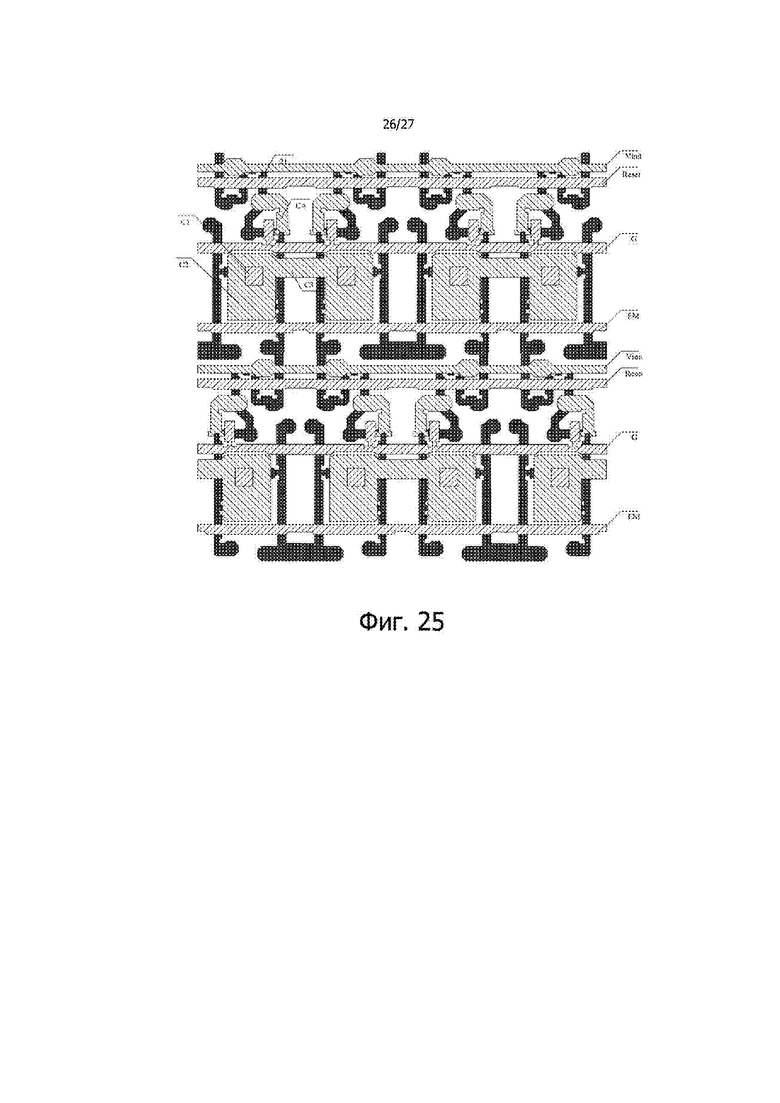

Фиг. 25 - схема изготовления второго изоляционного слоя и второго металлического слоя другой подложки дисплея, соответствующей настоящему раскрытию.

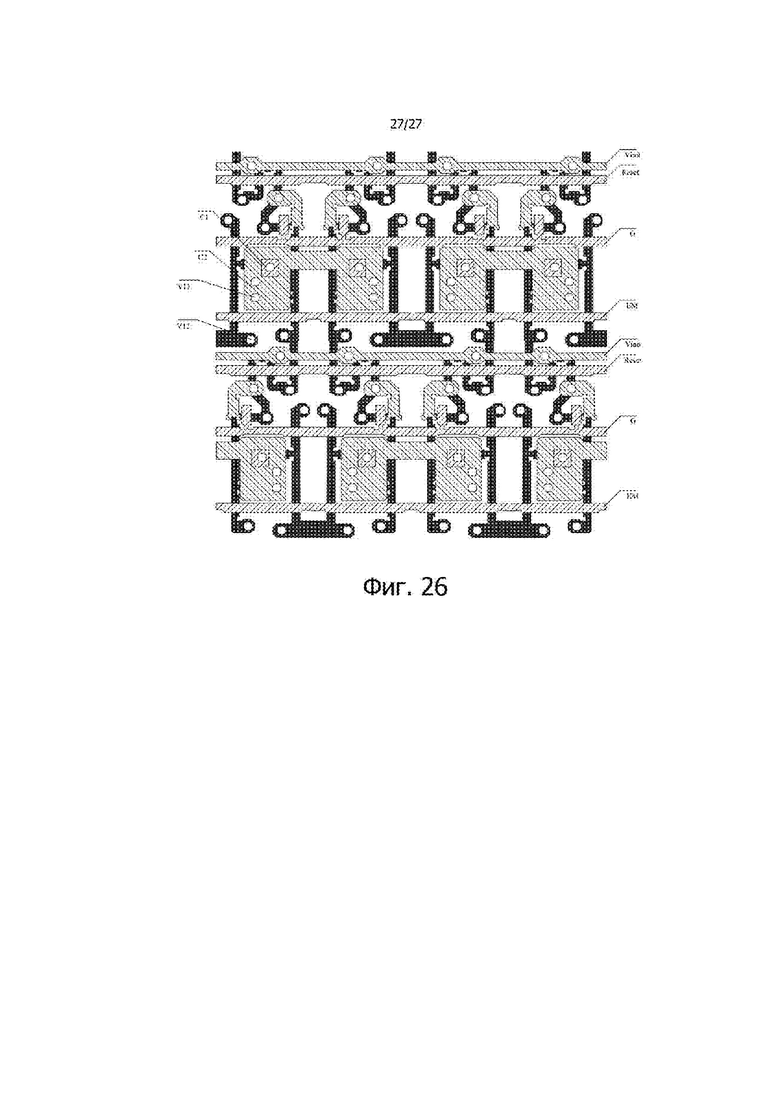

Фиг. 26 - схема изготовления третьего изоляционного слоя другой подложки дисплея, соответствующей настоящему раскрытию.

Осуществление изобретения

В настоящем раскрытии описано множество вариантов осуществления, но описание является примерным, но не ограничительным, и специалистам в данной области техники должно быть очевидным, что в рамках объема вариантов осуществления, описанных в настоящем раскрытии, возможно большее количество вариантов осуществления и решений реализации. Хотя многие возможные сочетания признаков показаны на чертежах и обсуждаются в разделе «Подробное описание», также возможны и многие другие сочетания раскрытых признаков. Если нет конкретного ограничения, то любой признак или элемент любого варианта осуществления может использоваться в сочетании или вместо любого другого признака или элемента любого другого варианта осуществления.

Настоящее раскрытие содержит и подробно рассматривает сочетания признаков и элементов, известные специалистам в данной области техники. Варианты осуществления, признаки и элементы, уже раскрытые в этом раскрытии, могут также объединяться с любыми стандартными признаками или элементами, чтобы формировать уникальное изобретательное решение, определяемое формулой изобретения. Любой признак или элемент любого варианта осуществления могут также быть объединены с признаками или элементами других изобретательских решений, чтобы сформировать другое уникальное изобретательское решение, определяемое формулой изобретения. Поэтому следует понимать, что любые из признаков, показанных и/или обсуждаемых в настоящем раскрытии, могут быть реализованы индивидуально или в любом соответствующем сочетании. Поэтому варианты осуществления ничем не ограничиваются, кроме как соответствующей приложенной формулой изобретения и ее эквивалентами. Кроме того, в пределах объема защиты добавленной формулы изобретения могут делаться различные модификации и изменения.

Кроме того, при описании репрезентативных вариантов осуществления описание может представлять способ и/или процесс в виде конкретной последовательности этапов. Однако, в том случае, когда способ или процесс не зависят от определенного порядка описанных здесь этапов, способ или процесс не должны ограничиваться определенным порядком описанных этапов. Как должны понимать специалисты в данной области техники, другие порядки этапов также возможны. Поэтому, конкретный порядок этапов, установленный в описании, не должен интерпретироваться как ограничение формулы изобретения. Кроме того, формула изобретения способа и/или процесса не должна ограничиваться выполнением этих этапов в записанном порядке и специалисты в данной области техники могут легко понять, что эти порядки могут быть различными и при этом все еще оставаться в рамках сущности и объема настоящего раскрытия.

Если не определено иначе, технические термины или научные термины, используемые в вариантах осуществления настоящего изобретения, должны иметь общий смысл, как они трактуются специалистами в данной области техники, к которой относится настоящее изобретение. Слова "первый", "второй" и т. п., используемые в вариантах осуществления настоящего изобретения, не представляют какого-либо порядка, количества или значения, а просто используются для различения разных компонентов. Подобные слова, такие как "включает" или "содержит" означают, что элементы или описания, предшествующие словам, охватывают элементы или описания, перечисленные после слов и их эквивалентов, и не исключают другие элементы или описания. Подобные слова, такие как "соединять" или "связывать" не ограничиваются физическими или механическими соединениями, а могут содержать электрические соединения, прямые или косвенные. “Верхний”, "нижний", "левый", "правый" и т. д. используются только для представления относительного позиционного соотношения, которое может соответственно изменяться, когда изменяется абсолютное положение описываемого объекта.

Термин "примерно" здесь означает, что предел строго не устанавливается и допускается значение в пределах диапазона погрешностей процесса и измерений. Термин "эквивалентный" здесь относится к состоянию, в котором отношение одного размера к другому составляет от 0,8 до 1,2.

Некоторые варианты осуществления настоящего раскрытия упоминают подложку дисплея. Подложка дисплея содержит в плоскости, параллельной подложке дисплея, затворные шины, линии передачи данных, шины электропитания и множество субпикселей, расположенных на базовой подложке. По меньшей мере один субпиксель содержит светоизлучающее устройство и схему управления, выполненную с возможностью управления светоизлучающим устройством для излучения света. Схема управления содержит множество транзисторов и накопительный конденсатор. Подложка дисплея содержит в плоскости, перпендикулярной подложке дисплея, базовую подложку и множество функциональных слоев, расположенных на базовой подложке. Множество функциональных слоев содержит полупроводниковый слой, первый проводящий слой, второй проводящий слой, третий проводящий слой и четвертый проводящий слой, располагающиеся последовательно. Первый изоляционный слой, второй изоляционный слой, третий изоляционный слой и четвертый изоляционный слой соответственно располагаются между множеством функциональных слоев и в направлении прохождения затворных шин, шины электропитания соединяются друг с другом по меньшей мере через один функциональный слой. В примерном варианте осуществления подложка дисплея дополнительно содержит пятый изоляционный слой, расположенный на четвертом проводящем слое, и пятый проводящий слой, расположенный на пятом изоляционном слое.

На фиг. 1 схематично показана структурная схема подложки дисплея, соответствующей согласно настоящему раскрытию, на фиг. 2 показан вид сбоку субпикселя в подложке дисплея, соответствующей настоящему раскрытию, и на фиг. 3 показан вид сверху субпикселя в подложке дисплея, соответствующей настоящему раскрытию. Как показано на фиг. 1-3, в плоскости, параллельной подложке дисплея, на подложке дисплея, соответствующей настоящему раскрытию, обеспечиваются затворная шина G, линия D передачи данных, шина VDD электропитания, линии Reset сигнала сброса, линия EM управления светоизлучением, линия Vinit сигнала инициирования и множество субпикселей P. Каждый субпиксель содержит светоизлучающее устройство и схему управления, выполненную с возможностью управления светоизлучающим устройством для излучения света. Схема управления содержит множество транзисторов и накопительный конденсатор. В плоскости, перпендикулярной подложке дисплея, подложка дисплея содержит: базовую подложку 10 и полупроводниковый слой 20, первый металлический слой 30, второй металлический слой 40, третий металлический слой 50, четвертый металлический слой 60 и пятый металлический слой 70, которые располагаются на базовой подложке 10 и изолируются друг от друга. Первый металлический слой 30 служит первым проводящим слоем, второй металлический слой 40 служит вторым проводящим слоем, третий металлический слой 50 служит третьим проводящим слоем, четвертый металлический слой 60 служит четвертым проводящим слоем и пятый металлический слой 70 служит пятым проводящим слоем. В примерном варианте осуществления подложка дисплея содержит зону отображения (display area, AA) и зону кадра, расположенную на периферии зоны отображения. Зона отображения содержит множество субпикселей дисплея, а зона кадра содержит множество фиктивных (Dummy) субпикселей. Субпиксели, описанные здесь, относятся к субпикселям дисплея в зоне отображения.

В примерном варианте осуществления полупроводниковый слой 20 может содержать активные области множества транзисторов. Первый металлический слой 30 может содержать затворную шину G, линию EM управления светоизлучением, линию Reset сброса сигнала, первый электрод C1 накопительного конденсатора и электроды затвора множества транзисторов. Второй металлический слой 40 может содержать линию Vinit сигнала инициирования и второй электрод C2 накопительного конденсатора. Третий металлический слой 50 может содержать первые выводы и вторые выводы множества транзисторов. Четвертый металлический слой 60 может содержать линию D передачи данных и шину VDD электропитания. Пятый металлический слой 70 может содержать анод светоизлучающего устройства.

В примерном варианте осуществления в направлении прохождения линии передачи данных, линия передачи данных может содержать множество сублиний передачи данных, соединенных последовательно, и множество сублиний передачи данных соответствует множеству субпикселей. Существует по меньшей мере один субпиксель, такой, что две сублинии передачи данных располагаются между субпикселем и смежным субпикселем в направлении прохождения затворной шины. В примерном варианте осуществления эти две сублинии передачи данных параллельны друг другу.

Как показано на фиг. 1, в примерном варианте осуществления, на подложке дисплея могут быть расположены М строк*N столбцов субпикселей, N столбцов линий D1-DN передачи данных, N столбцов шин VDD1-VDDN электропитания, М строк затворных шин G1-GM, строки M-1 линий EM1-EMM-1 управления светоизлучением, линия Reset сигнала сброса и линия Vinit сигнала инициирования. Подложка дисплея может дополнительно содержать: драйвер управления данными, выполненный с возможностью обеспечения сигналов данных для линий передачи данных, драйвер сканирования, выполненный с возможностью обеспечения сигналов сканирования для затворных шин, драйвер управления светоизлучением, выполненный с возможностью обеспечения сигналов управления светоизлучением для линий управления светоизлучением, и контроллер синхронизации, выполненный с возможностью обеспечения сигналов управления для драйверов управления данных, драйверов сканирования и драйверов светоизлучения.

В некоторых возможных реализациях, как показано на фиг. 1, схемы управления в i-ом столбце субпикселей соединяются с i-ым столбцом линии передачи данных. Каждый столбец линии передачи данных содержит первую сублинию DO передачи данных и вторую сублинию DE передачи данных. Первая сублиния DOi передачи данных и вторая сублиния DEi передачи данных i-ом столбце линии передачи данных располагаются с двух сторон i-ого столбца субпикселей, соответственно, и 1 ≤ i ≤ N, где N – общее количество столбцов субпикселей.

В некоторых возможных реализациях две сублинии передачи данных располагаются между двумя смежными столбцами субпикселей, то есть, первая сублиния DO передачи данных одного столбца субпикселей и вторая сублиния DE передачи данных смежного столбца субпикселей располагаются между двумя смежными столбцами субпикселей, или вторая сублиния DE передачи данных одного столбца субпикселей и первая сублиния DO передачи данных смежного столбца субпикселей располагаются между двумя смежными столбцами субпикселей.

Например, первая сублиния Doi передачи данных i-ого столбца линии передачи данных располагается на стороне i-ого столбца субпикселей вблизи i+1-ого столбца субпикселей, и первая сублиния DOi+1 передачи данных i+1-ого столбца линии передачи данных, располагается на стороне i+1-ого столбца субпикселей вблизи i-ого столбца субпикселей. Альтернативно, вторая сублиния DEi передачи данных i-ого столбца линии передачи данных располагается на стороне i-ого столбца субпикселей вблизи i+1-ого столбца субпикселей, и вторая сублиния DEi+1 передачи данных i+1-ого столбца линии передачи данных располагается на стороне i+1-ого столбца субпикселей вблизи i-ого столбца субпикселей.

В некоторых возможных реализациях базовая подложка 10 может быть твердой подстилающей подложкой или гибкой подстилающей подложкой. Твердая подстилающая подложка может быть, но не ограничиваясь этим, одним или более слоями стекла и металлической фольги. Гибкая подстилающая подложка может быть, но не ограничиваясь только этим, одним или более слоями терефталата полиэтилена, терефталата этилена, эфирным кетоном полиэфира, полистирола, поликарбоната, полиарилата, полиарилэфира, полиамидом, поливиниловым хлоридом, полиэтилен и текстильными волокнами.

В некоторых возможных реализациях материал для изготовления полупроводникового слоя 20 может быть поликристаллическим кремнием или металлическими оксидами, что не ограничивается в настоящем раскрытии.

В некоторых возможных реализациях материалом для изготовления первого металлического слоя могут быть такие металлические материалы, как серебро, алюминий или медь, что не ограничивается в настоящем раскрытии.

В некоторых возможных реализациях материалом для изготовления второго металлического слоя могут быть такие металлические материалы, как серебро, алюминий или медь, что не ограничивается в настоящем раскрытии.

В некоторых возможных реализациях материалом для изготовления третьего металлического слоя могут быть такие металлические материалы, как серебро, алюминий или медь, что не ограничивается в настоящем раскрытии.

В некоторых возможных реализациях материалом для изготовления четвертого металлического слоя могут быть такие металлические материалы, как серебро, алюминий или медь, что не ограничивается в настоящем раскрытии.

В некоторых возможных реализациях материалом для изготовления пятого металлического слоя могут быть такие металлические материалы, как серебро, алюминий или медь, что не ограничивается в настоящем раскрытии.

На фиг. 4A показана эквивалентная схема схемы управления, соответствующей настоящему раскрытию, и на фиг. 4B приведена диаграмма работы синхронизации схемы управления, соответствующей настоящему раскрытию. Как показано на фиг. 4A и 4B, фиг. 4A поясняет пример схем управления, содержащихся в i-ом столбце субпикселей и i+1-ом столбце субпикселей. Схема управления, соответствующая настоящему раскрытию, может иметь структуру 7T1C и может содержать: первый-седьмой транзисторы T1-T7 и накопительный конденсатор C, где накопительный конденсатор C содержит первый электрод C1 и второй электрод C2.

В примерной реализации, конкретно, электрод затвора первого транзистора T1 соединяется с линией Reset сигнала сброса, первый вывод первого транзистора T1 соединяется с линией Vinit сигнала инициирования и второй вывод первого транзистора T1 соединяется с первым электродом C1 накопительного конденсатора C. Электрод затвора второго транзистора T2 соединяется с затворной шиной G, первый вывод второго транзистора T2 соединяется с первым электродом C1 накопительного конденсатора C, и второй вывод второго транзистора T2 соединяется со вторым выводом шестого транзистора T6. Электрод затвора третьего транзистора T3 соединяется с первым электродом C1 накопительного конденсатора C, первый вывод третьего транзистора T3 соединяется со вторым выводом четвертого транзистора T4 и второй вывод третьего транзистора T3 соединяется со вторым выводом шестого транзистора T6. Электрод затвора четвертого транзистора T4 соединяется с затворной шиной G, и первый вывод четвертого транзистора T4 соединяется с линией D передачи данных. Электрод затвора пятого транзистора T5 соединяется с линией EM управления светоизлучением, первый вывод пятого транзистора T5 соединяется с шиной VDD электропитания, и второй вывод пятого транзистора T5 соединяется с первым выводом третьего транзистора T3. Электрод затвора шестого транзистора T6 соединяется с линией EM управления светоизлучением и второй вывод шестого транзистора T6 соединяется с анодом светоизлучающего устройства. Электрод затвора седьмого транзистора T7 соединяется с линией Reset линии сигнала сброса, первый вывод седьмого транзистора T7 соединяется с линией Vinit сигнала инициирования и второй вывод седьмого транзистора T7 соединяется с анодом светоизлучающего устройства. Второй электрод C2 накопительного конденсатора соединяется с шиной VDD электропитания и катод светоизлучающего устройства OLED соединяется с выводом источника VSS электропитания нижнего слоя.

В примерном варианте осуществления третий транзистор T3 является управляющим транзистором, другие транзисторы, кроме третьего транзистора T3, все являются коммутационными транзисторами и первым-седьмой транзисторы T1-T7 все могут быть транзисторами p-типа или транзисторами n-типа, что не ограничивается в настоящем раскрытии.

Рассматривая в качестве примера случай, в котором первый-седьмой транзисторы T1-T7 все являются транзисторами p-типа, рабочий процесс схемы управления может содержать первый этап P1 (этап сброса), второй этап P2 (этап записи) и третий этап P3 (этап светоизлучения).

На первом этапе P1 (этап сброса), линия Reset сигнала сброса обеспечивает уровень включения, первый-седьмой транзисторы T1-T7 включаются и сигнал инициирования, обеспечиваемый линией Vinit сигнала инициирования, инициирует сигнал на втором выводе шестого транзистора T6 и сигнал на первом электроде C1.

На втором этапе P2 (этап записи), линия G затвора обеспечивает уровень включения, второй транзистор T2 и четвертый транзистор T4 включаются, сигнал данных, обеспечиваемый по линии D передачи данных, записывается на первый вывод третьего транзистора T3 и сигналы электрода затвора и второго вывода второго транзистора T2 получают один и тот же потенциал, чтобы позволить открыться третьему транзистору T3.

На третьем этапе P3 (этап светоизлучения), линия EM управления светоизлучением обеспечивает уровень включения, пятый транзистор T5 и шестой транзистор T6 включаются и шина VDD электропитания обеспечивает ток управления для светоизлучающего устройства OLED, чтобы управлять светоизлучающим устройством для излучения света.

В некоторых возможных реализациях, как показано на фиг. 4A, светоизлучающее устройство, представленное в настоящем раскрытии, может быть устройством OLED.

Подложка дисплея, соответствующая настоящему раскрытию, имеет затворную шину, линию передачи данных, шину электропитания, линию сигнала сброса, линию управления светоизлучением, линию сигнала инициирования и множество субпикселей. Каждый субпиксель содержит: светоизлучающее устройство и схему управления, выполненную с возможностью управления светоизлучающим устройством для излучения света. Схема управления может содержать: множество транзисторов и накопительный конденсатор. Подложка дисплея может содержать: базовую подложку и полупроводниковый слой, первый металлический слой, второй металлический слой, третий металлический слой, четвертый металлический слой и пятый металлический слой, которые располагаются последовательно на базовой подложке и изолируются друг от друга. Полупроводниковый слой содержит активные области множества транзисторов. Первый металлический слой содержит: затворную шину, линию управления светоизлучением, линию сигнала сброса, первый электрод накопительного конденсатора и электроды затворов множества транзисторов. Второй металлический слой содержит: линию сигнала инициирования и второй электрод накопительного конденсатора. Третий металлический слой содержит: электроды истока и стока множества транзисторов. Четвертый металлический слой содержит: линию передачи данных и шину электропитания. Пятый металлический слой содержит: анод светоизлучающего устройства. i-ый столбец субпикселей соединяется с i-ым столбцом линии передачи данных. Каждый столбец линии передачи данных содержит первую сублинию передачи данных и вторую сублинию передачи данных. Первая сублиния передачи данных и вторая сублиния передачи данных в i-ом столбце линии передачи данных располагаются с двух сторон субпикселей i-ого столбца, соответственно, 1 ≤ i ≤ N, где N – общее количество столбцов субпикселей.

В настоящем раскрытии организованы пять металлических слоев и путем расположения линии передачи данных и шины электропитания в слоях, отличных от электродов истока и стока множества транзисторов, объем, занимаемый субпикселями и линиями передачи данных, соединенными с субпикселями, можно уменьшить, улучшая, таким образом, разрешающую способность подложки дисплея OLED, управляемой с высокой частотой.

В некоторых возможных реализациях, как показано на фиг. 3, каждый субпиксель в подложке дисплея, соответствующей настоящему раскрытию, может быть разделен на первую область R1, вторую область R2 и третью область R3, которые располагаются последовательно в направлении прохождения линии передачи данных.

Накопительный конденсатор располагается во второй области R2. Первая область R1 и третья область R3 располагаются с двух сторон второй области R2, соответственно. Линия Vinit сигнала инициирования, затворная шина G и линия Reset сигнала сброса, соединенная со схемой управления субпикселя, располагаются в первой области R1. Линия EM управления светоизлучением, соединенная со схемой управления субпикселя, располагается в третьей области R3.

Схемы управления смежных субпикселей в одном и том же столбце соединяются с различными сублиниями передачи данных, то есть, если субпиксель в i-ой строке и j-ом столбце соединяется с первой сублинией DOj передачи данных в j-ом столбце линии передачи данных, субпиксель в i+1-ой строке и j-ом столбце соединяется со второй сублинией Dej передачи данных в j-ом столбце линии передачи данных; и если субпиксель в i-ой строке и j-ом столбце соединяется со второй сублинией DEj передачи данных в j-ом столбце линии передачи данных, субпиксель в i+1-ой строке и j-ом столбце соединяется с первой сублинией DOj передачи данных в j-ом столбце линии передачи данных.

В некоторых возможных реализациях, как можно видеть на фиг. 1 и фиг. 3, схемы управления i-ого столбца субпикселей также соединяются с i-ым столбцом шины электропитания, 1 ≤ i ≤ N. i-ый столбец шины VDDi электропитания располагается между первой сублинией DOi передачи данных и второй сублинией Dei передачи данных в i-ом столбце линии передачи данных.

На фиг. 5 представлен вид сверху множества субпикселей в подложке дисплея, соответствующей настоящему раскрытию. Как показано на фиг. 5, пиксельные структуры смежных субпикселей в одной и той же строке зеркально симметричны друг другу относительно осевой линии CL двух сублиний передачи данных между смежными субпикселями. Пиксельная структура субпикселя, расположенного в i-ой строке и j-ом столбце, является такой же, как пиксельная структура субпикселя, расположенного в i-ой строке и j+2-ом столбце. Пиксельная структура субпикселя, расположенного в i-ой строке и j+1-ом столбце, является такой же, как пиксельная структура субпикселя, расположенного в i-ой строке и j+3-ом столбце. Пиксельная структура субпикселя, расположенного в i-ой строке и j-ом столбце, является такой же, как пиксельная структура субпикселя, расположенного в i+1-ой строке и j+1-ом столбце. Пиксельная структура субпикселя, расположенного в i-ой строке и j+1-ом столбце, является такой же, как пиксельная структура субпикселя, расположенного в i+1-ой строке и j-ом столбце. Здесь, пиксельные структуры, являющиеся одинаковыми, содержат, не ограничиваясь только этим, пиксельные структуры общей формы и взаимосвязь соединений соответствующих частей и тенденции сигнального потока является одинаковой.

Как показано на фиг. 5, шины электропитания в двух смежных столбцах зеркально симметричны относительно осевой линии между шинами электропитания в двух смежных столбцах, то есть, шины электропитания смежных субпикселей симметричны друг другу. Осевая линия CL двух сублиний передачи данных, расположенных между субпикселем в i-ой строке и j-ом столбце и субпикселем в i-ой строке и j+1-ом столбце, и осевая линия, расположенная между шиной электропитания в j-ом столбце и шиной электропитания в j+1-ом столбце, может быть той же самой осевой линией.

В некоторых возможных реализациях, как показано на фиг. 5, беря в качестве примера восемь субпикселей в двух строках и четырех столбцах (зона, содержащая 2*4 субпикселей), шина электропитания в i-ом столбце содержит множество соединенных между собой сублиний S1-SN электропитания. Множество сублиний электропитания соответствуют всем субпикселям в каждом столбце субпикселей поодиночке, и множество сублиний электропитания соответственно располагаются во множестве субпикселей в столбце.

В примерном варианте осуществления форма сублинии электропитания, соответствующей субпикселю в i-ой строке и j-ом столбце, после того, как она зеркально отражается вокруг осевой линии первой сублинии передачи данных и второй сублинии передачи данных в линии передачи данных в j-ом столбце, является такой же, как форма сублинии электропитания, соответствующей субпикселю в i+1-ой строке и j-ом столбце. Здесь, формы шин электропитания, являющиеся одинаковыми, содержат, не ограничиваясь только этим, то, что общие формы, соотношение соединений соответствующих частей и тенденции сигнального потока являются одними и теми же.

В примерном варианте осуществления каждая сублиния электропитания может содержать первую часть SS1 источника электропитания, вторую часть SS2 источника электропитания и третью часть SS3 источника электропитания, последовательно расположенные во втором направлении. Вторая часть SS2 источника электропитания выполнена с возможностью соединения первой части SS1 источника электропитания и третьей части SS3 источника электропитания. Первая часть SS1 источника электропитания и третья часть SS3 источника электропитания могут быть расположены параллельно линии передачи данных. Прилежащий угол между второй частью SS2 источника электропитания и первой частью SS1 источника электропитания составляет больше 90 градусов и меньше 180 градусов, чтобы сформировать зигзагообразную сублинию электропитания. Второе направление является направлением прохождения линии передачи данных.

Здесь, "параллельный" относится к состоянию, в котором две прямые линии образуют угол -10 градусов или больше и 10 градусов или меньше и, таким образом, также содержит состояние, в котором угол составляет -5 градусов или больше и 5 градусов или меньше. Кроме того, "вертикаль" относится к состоянию, в котором две прямые линии образуют угол 80 градусов или больше и 100 градусов или меньше и, таким образом, также содержит состояние угла, равное 85 градусам или больше и 95 градусам или меньше. Здесь, первая часть источника электропитания, параллельная линии передачи данных, означает, что часть основного корпуса первой части источника электропитания параллельна основной части корпуса линии передачи данных, без ограничения, что край первой части источника электропитания параллелен краю линии передачи данных. Допускается, чтобы край первой части источника электропитания и край линии передачи данных быть неровными из-за технологических погрешностей. Область соединения, в которой первая часть источника электропитания и вторая часть источника электропитания соединяются друг с другом, может принадлежать первой части источника электропитания или может принадлежать второй части источника электропитания.

В примерном варианте осуществления первая часть SS1 источника электропитания, вторая часть SS2 источника электропитания и третья часть SS3 источника электропитания могут быть интегрированной структурой.

Как показано на фиг. 5, длина прохождения первой части SS1 источника электропитания во втором направлении больше, чем средняя ширина первой части SS1 источника электропитания, длина прохождения второй части SS2 источника электропитания в косом направлении больше, чем средняя ширина второй части SS2 источника электропитания, и длина прохождения третьей части SS3 источника электропитания во втором направлении больше, чем средняя ширина третьей части SS3 источника электропитания. Косое направление является направлением, в котором вторая часть источника электропитания и первая часть источника электропитания имеют между ними прилежащий угол. Средняя ширина третьей части SS3 источника электропитания меньше, чем средняя ширина первой части SS1 источника электропитания. Это, с одной стороны, предназначено для расположения пиксельной структуры, и, с другой стороны, поскольку третья часть SS3 источника электропитания находится относительно близко к линии передачи данных и третья часть SS3 источника электропитания обладает относительно малой средней шириной, это может уменьшать паразитную емкость. В настоящем раскрытии ширина первой части SS1 источника электропитания и третьей части SS3 источника электропитания относятся к размерам первой части SS1 источника электропитания и третьей части SS3 источника электропитания в первом направлении, ширина второй части SS2 источника электропитания относится к размеру в направлении, перпендикулярном косому направлению, средняя ширина относится к среднему значению ширины во множестве позиций, и первое направление является направлением прохождения затворной шины.

В примерном варианте осуществления, в первом направлении расстояние между осевой линией первой части SS1 источника электропитания и осевой линией третьей части SS3 источника электропитания эквивалентно средней ширине третьей части SS3 источника электропитания.

В примерном варианте осуществления первая часть SS1 источника электропитания в сублинии электропитания, соответствующей субпикселю в i-ой строке и j-ом столбце, соединяется с третьей частью SS3 источника электропитания в сублинии электропитания, соответствующей субпикселю в i-1-ой строке и j-ом столбце. Часть SS3 источника электропитания в сублинии электропитания, соответствующей субпикселю в i-ой строке и j-ом столбце, соединяется с первой частью SS1 источника электропитания в сублинии электропитания, соответствующей субпикселю в i+1-ой строке и j-ом столбце. Части источника электропитания, соединенные друг с другом, располагаются последовательно во втором направлении (направлении прохождения линии передачи данных).

Как показано на фиг. 5, шина электропитания в настоящем раскрытии может иметь зигзагообразную форму.

В примерном варианте осуществления, как показано на фиг. 5, процесс каждого работы субпикселя содержит этап сброса, этап записи и этап светоизлучения. На этапе сброса линия Reset сигнала сброса, расположенная в первом металлическом слое, и линии Vinit сигнала инициирования, расположенная во втором металлическом слое, обеспечивает сигналы для инициирования схемы управления. На этапе записи затворная шина G, расположенная в первом металлическом слое, и линия D передачи данных, расположенная в четвертом металлическом слое, обеспечивают сигналы для записи сигналов данных, обеспечиваемых линией D передачи данных, на схему управления. На этапе светоизлучения линия EM управления светоизлучением, расположенная в первом металлическом слое, обеспечивает сигналы и шина VDD электропитания обеспечивает сигналы электропитания, чтобы позволить схеме управления обеспечить ток управления для светоизлучающего устройства OLED для управления светоизлучающим устройством и излучения света.

Пиксели в одной и той же строке включаются одновременно и пиксели в смежных строках включаются последовательно.

В некоторых возможных реализациях, как показано на фиг. 2, подложка дисплея, соответствующая настоящему раскрытию, может дополнительно содержать первый изоляционный слой 11, второй изоляционный слой 12, третий изоляционный слой 13 и четвертый изоляционный слой 14.

Первый изоляционный слой 11 располагается между полупроводниковым слоем 20 и первым металлическим слоем 30, второй изоляционный слой 12 располагается между первым металлическим слоем 30 и вторым металлическим слоем 40, третий изоляционный слой 13 располагается между вторым металлическим слоем 40 и третьим металлическим слоем 50, и четвертый изоляционный слой 14 располагается между третьим металлическим слоем 50 и четвертым металлическим слоем 60.

В некоторых возможных реализациях материалами первого изоляционного слоя 11, второго изоляционного слоя 12, третьего изоляционного слоя 13 и четвертого изоляционного слоя 14 могут быть кремниевый оксид, кремниевый нитрид, или композит кремниевого оксида и кремниевого нитрида, что не ограничивается в настоящем раскрытии.

В примерном варианте осуществления, как показано на фиг. 4A, множество транзисторов каждого субпикселя может содержать первый-седьмой транзисторы. Первый вывод пятого транзистора соответственно соединяется с шиной VDD электропитания и вторым электродом C2 накопительного конденсатора.

В настоящем раскрытии для каждого субпикселя шина электропитания в каждом субпикселе соединяется со вторым электродом накопительного конденсатора через первый вывод пятого транзистора.

Вторые электроды накопительных конденсаторов смежных субпикселей, расположенных во втором металлическом слое, могут быть повторно использованы в качестве линий сигналов электропитания, которые выполнены с возможностью гарантии, что сигналы электропитания, обеспечиваемые шинами электропитания смежных субпикселей, являются одинаковыми, избегая, таким образом, плохого отображения подложки дисплея и гарантируя эффект отображения подложки дисплея.

В примерном варианте осуществления каждые четыре непрерывных субпикселя образуют пиксель. В j-ом пикселе четырьмя непрерывными субпикселями являются последовательно i-ый субпиксель, i+1-ый субпиксель, i+2-ой субпиксель и i+3-ий субпиксель в первом направлении, где i – может принимать значение 4j-3 в последовательности и j является положительным целым числом.

В примерном варианте осуществления существуют многочисленные реализации соединения вторых электродов накопительных конденсаторов множества субпикселей с шинами электропитания.

В качестве одной из реализаций, на фиг. 6A показан вид сверху субпикселей, соответствующих реализации I, и на фиг. 6B показан другой вид сверху субпикселей, соответствующих реализации I. Как показано на фиг. 6A, в четвертом изоляционном слое обеспечивается первое сквозное отверстие V1, обеспечивающее доступ к первым выводам 51 частичных пятых транзисторов, и шина электропитания соединяется с первым выводом 51 пятого транзистора через первое сквозное отверстие V1. Как показано на фиг. 6B, в третьем изоляционном слое обеспечивается второе сквозное отверстие V2, обеспечивающее доступ ко вторым электродам C2 некоторых накопительных конденсаторов, и первый вывод 51 пятого транзистора соединяется со вторым электродом C2 накопительного конденсатора через второе сквозное отверстие V2. Следует заметить, что на фиг. 3 и фиг. 5, реализация I приводится в качестве примера.

Ортогональная проекция шин электропитания, соединенных с субпикселями на базовой подложке, содержит ортогональную проекцию первого сквозного отверстия V1 на базовую подложку 10, и ортогональная проекция второго электрода накопительного конденсатора содержит ортогональную проекцию второго сквозного отверстия на базовую подложку. Здесь, “ортогональная проекция А, содержащая ортогональную проекцию B” или “ортогональная проекция B располагается в пределах диапазона ортогональной проекции А” означает, что граница ортогональной проекции B находится в пределах диапазона границы ортогональной проекции A или граница ортогональной проекции А перекрывается с границей ортогональной проекции B.

В некоторых возможных реализациях количество первых сквозных отверстий V1 может быть равно единице.

В некоторых возможных реализациях количество вторых сквозных отверстий V2 может быть по меньшей мере единицей. Поскольку ширина первого вывода пятого транзистора является относительно малой величиной, когда существуют многочисленные вторые сквозные отверстия V2, многочисленные вторые сквозные отверстия располагаются в направлении прохождения линии передачи данных. Многочисленные вторые сквозные отверстия располагаются в направлении прохождения линии передачи данных и может быть расположено множество сквозных отверстий. Чем больше сквозных отверстий, тем лучше проводимость компонентов, соединенных через сквозные отверстия. На фиг. 6A существует одно первое сквозное отверстие V1 и на фиг. 6B показан пример, в котором существуют два вторых сквозных отверстия V2, что не ограничивается в настоящем раскрытии.

В примерном варианте осуществления, как показано на фиг. 6A, в четвертом изоляционном слое дополнительно обеспечивается третье сквозное отверстие V3, обеспечивающее доступ к первому выводу четвертого транзистора T4. Линия передачи данных соединяется с первым выводом четвертого транзистора T4 через третье сквозное отверстие V3. В четвертом изоляционном слое дополнительно обеспечивается четвертое сквозное отверстие V4, обеспечивающее доступ ко второму выводу шестого транзистора T6.

В примерном варианте осуществления, как показано на фиг. 6B, первый изоляционный слой, второй изоляционный слой и третий изоляционный слой дополнительно содержат сквозные отверстия, обеспечивающие доступ к частичным активным областям, так что электроды истока и стока транзисторов соединяются с активными областями через эти сквозные отверстия. Электроды истока и стока транзисторов содержат первые выводы транзисторов и вторые выводы транзисторов.

В примерном варианте осуществления первый вывод пятого транзистора также соединяется с активной областью через сквозные отверстия в первом изоляционном слое, втором изоляционном слое и третьем изоляционном слое.

В примерном варианте осуществления каждый пиксель может содержать четыре субпикселя. На фиг. 7A показан вид сверху второго металлического слоя, соответствующего реализации I, и на фиг. 7B показан вид сверху третьего металлического слоя, соответствующего реализации I. Чтобы объяснить структуру подложки дисплея более ясно, на фиг. 7A и 7B показан пример двух пикселей, расположенных в направлении столбца.

Как показано на фиг. 7A, вторые электроды накопительных конденсаторов в смежных субпикселях в одной и той же строке соединяются напрямую. Как показано на фиг. 7B, первые выводы 51 пятых транзисторов в смежных субпикселях в одной и той же строке располагаются с промежутками.

В реализации I, за счет соединения вторых электродов накопительных конденсаторов, которые располагаются на втором металлическом слое во множестве субпикселей, сигналы электропитания, обеспечиваемые шинами электропитания смежных субпикселей, являются одинаковыми, таким образом избегая плохого отображения подложки дисплея и гарантируя эффект отображения подложки дисплея.

В примерном варианте осуществления, при разумном проекте расположения соединение проводящих слоев многочисленных субпикселей может быть реализовано только посредством полупроводникового слоя, или соединение проводящих слоев многочисленных субпикселей может быть реализовано только посредством первого металлического слоя или соединение проводящих слоев многочисленных субпикселей может быть реализовано только посредством второго металлического слоя, или соединение проводящих слоев многочисленных субпикселей может быть реализовано только посредством третьего металлического слоя, реализуя, таким образом, то, что шины электропитания субпикселей, расположенных в одной и той же строке, соединяются вместе в направлении прохождения затворных шин через функциональные слои, которые подробно здесь не описываются.

Как показано на фиг. 7A, по меньшей мере один субпиксель дополнительно содержит первую соединительную часть C3, которая располагается на стороне второго электрода C2 в первом направлении.