ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к устройству отображения, включающему в себя схему управления линии запоминающего конденсатора.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

В устройствах отображения на жидких кристаллах с активной матрицей отображением управляют, подавая сигнал данных на каждый электрод пиксела, таким образом, прикладывая через слой жидких кристаллов напряжение между электродом пиксела и общим электродом. Сигнал данных формируется в виде сигнала переменного тока (AC), который принимает и положительные и отрицательные полярности с общим напряжением в центре. Однако амплитуда сигнала данных является ограниченной в соответствии с ограничением от системы источника питания и/или ограничением по потребляемой мощности. Следовательно, напряжение, прикладываемое к жидким кристаллам, не всегда имеет достаточно широкий диапазон, чтобы делать возможным достижение достаточной контрастности. Соответственно, были предложены устройства отображения на жидких кристаллах, осуществляющие управление с емкостной связью. Управление с емкостной связью осуществляет смещения вверх и вниз потенциала электрода пиксела путем управления линии запоминающего конденсатора для каждого пиксела. Например, в документах 1-3 Патентной литературы раскрыты способы управления, в каждом из которых управление с емкостной связью было дополнительно усовершенствовано.

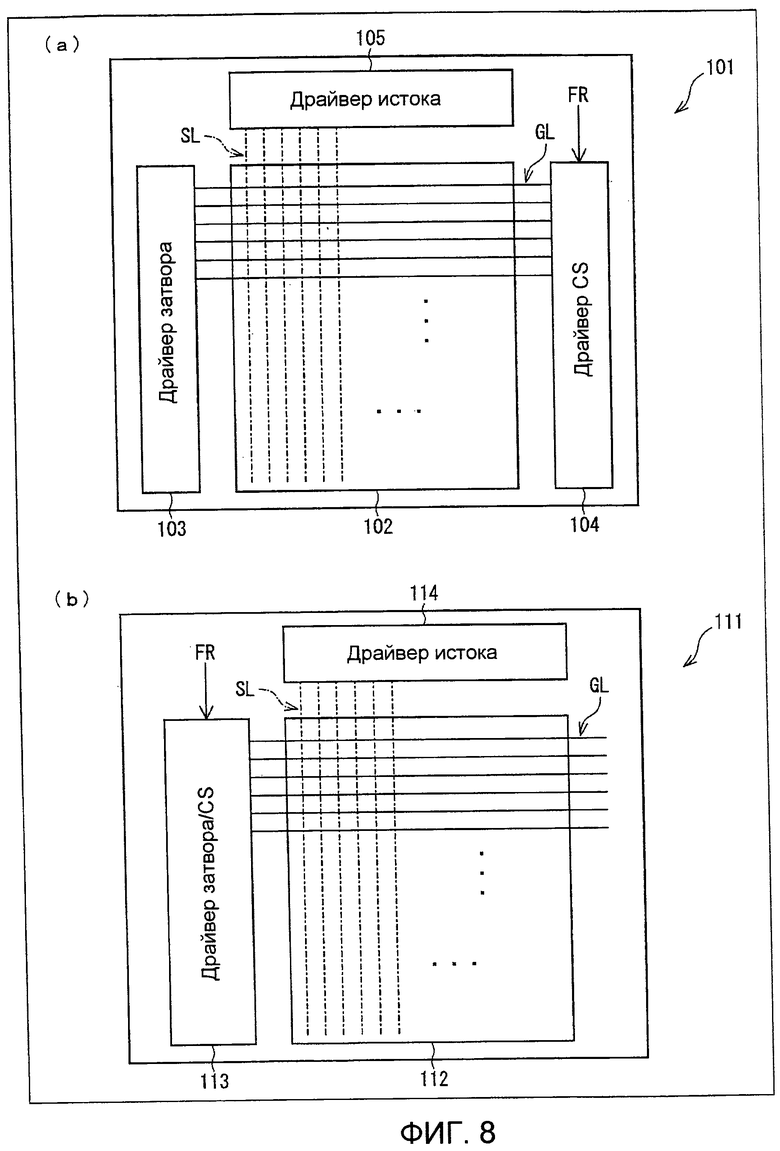

В некоторых случаях схема управления линии запоминающего конденсатора включает в себя драйвер CS (запоминающего конденсатора) 104 (схему управления линии запоминающего конденсатора), расположенный так, что секция 102 пикселов обеспечивается между драйвером 103 затвора (схемой управления линии сигнала сканирования) и драйвером 104 CS, как показано в устройстве 101 отображения на жидких кристаллах по фиг.8(a). В других случаях схема управления линии запоминающего конденсатора включает в себя драйвер CS (схему управления линии запоминающего конденсатора), объединенный с драйвером затвора (схемой управления линии сигнала сканирования) в драйвере 113, расположенном в области на одной стороне секции 112 пикселов, как показано в устройстве 111 отображения на жидких кристаллах по фиг.8(b).

Показанное на фиг.8(a) расположение драйвера 103 затвора и драйвера CS 104 соответствует сужению рамки. В этом расположении драйвер CS 104 использует сигнал сканирования, чтобы считывать сигнал FR идентификации полярности, и этот сигнал сканирования вводится в драйвер CS 104 по обеспечиваемой в области секции 102 пикселов линии GL шины затвора, после его вывода из драйвера 103 затвора. В виде отличия расположение драйвера затвора и драйвера CS, показанное на фиг.8(b), получают включением драйвера CS в состав традиционного драйвера затвора. В таком расположении драйвер CS принимает от драйвера затвора, находящегося внутри драйвера 113, сигнал сканирования, который драйвер CS использует для считывания сигнала FR идентификации полярности.

Перечень ссылок

Ссылка 1: Публикация заявки на патент Японии, Tokukai, № 2007-47703 A (дата публикации: 22 февраля 2007);

Ссылка 2: Публикация заявки на патент Японии, Tokukai, № 2006-313319 (дата публикации: 16 ноября 2006);

Ссылка 3: Публикация заявки на патент Японии, Tokukaihei, № 10-39277 (дата публикации: 13 февраля 1998).

Однако в показанном на фиг.8(a) устройстве 101 отображения на жидких кристаллах драйвер CS 104 принимает сигнал сканирования от драйвера 103 затвора по линии GL шины затвора, как показано на фиг.14. В результате драйвер CS 104 допускает передачу помехи, которая проходит из линии SL шины истока и имеет место, поскольку линия GL шины затвора пересекает шину SL истока, управляемую драйвером 105 истока. Затем, поскольку такое устройство отображения на жидких кристаллах конфигурировано схемой, использующей тонкопленочные транзисторы (TFT) одной полярности, и каждый из TFT-транзисторов выполнен из материала, такого как аморфный кремний или поликристаллический кремний, и имеет только полярность n-канала или полярность р-канала, образуется много «плавающих» точек. В случае, когда есть много плавающих точек, работает механизм, как показано на фиг.15. В результате электрические заряды плавающих точек разряжаются, что запускает ложное срабатывание последовательно соединенной схемы. В устройстве отображения с активной матрицей помеха формируется в результате изменения потенциала линии шины истока, обусловленного записью видеоданных или подобным образом, и помеха накладывается на линию затвора. Кроме того, поскольку выходной сигнал драйвера затвора установлен в Low (низкий) для большей части периода вывода драйвера затвора, почти все линии затвора соединяются электрически с напряжением питания Low драйвера затвора через транзистор. В результате помеха, которая появляется на линии затвора, передается на источник питания напряжения Low драйвера затвора. Это вызывает проблему в том, что линия затвора и источник питания напряжения Low драйвера затвора, каждый получает помеху, инициирующую упомянутую выше разрядку в плавающих точках контура, с которым соединены линия затвора и источник питания напряжения Low. Соответственно, вероятно будет происходить передача помехи в случае, когда драйвер CS через линию GL затвора электрически соединяется с шиной источника питания напряжения, линией затвора или подобным.

Дополнительно, драйвер 103 затвора и драйвер CS 104 имеют одинаковый потенциал низковольтного источника питания в случае полярности n-типа или одинаковый потенциал высоковольтного источника питания в случае полярности p-типа. Другими словами, поскольку драйвер 103 затвора и драйвер CS 104 имеют одинаковый логический уровень High и одинаковый логический уровень Low, уровень помехи для драйвера CS 104, вероятно, будет активным логическим уровнем.

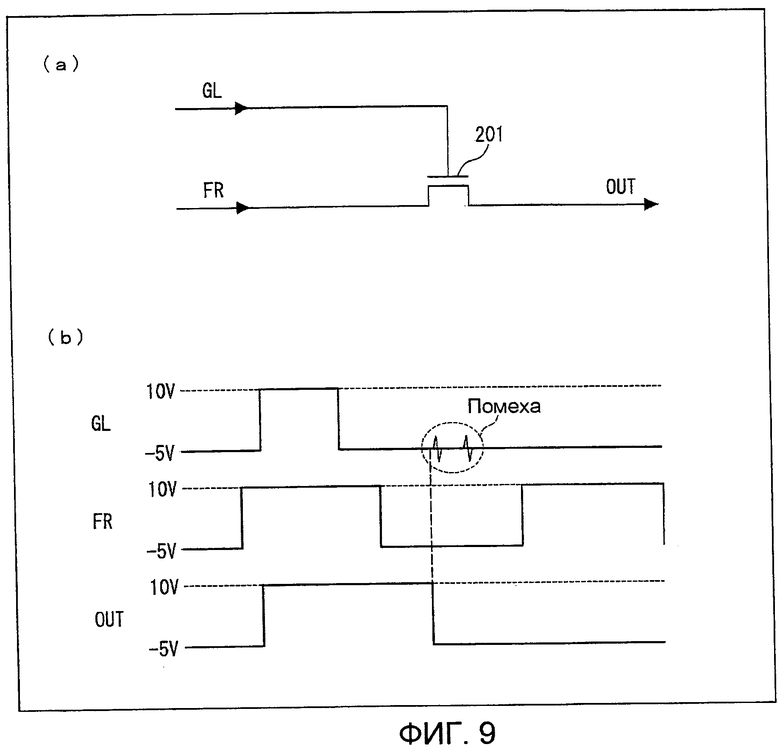

Соответственно, существует риск того, что драйвер CS 104 может хранить ошибочный сигнал полярности, вследствие ввода помехи в драйвер CS 104 в течение периода, в котором линия GL затвора установлена в потенциал OFF для сигнала сканирования. В качестве примера на фиг.9(a) показано состояние, где линия GL затвора соединена с затвором n-канала TFT 201, используемого в качестве аналогового переключателя для пропускания сигнала FR идентификации полярности. В этом состоянии, когда источники питания напряжения драйвера 103 затвора имеют напряжения 10 В и -5 В, и источники питания напряжения драйвера CS 104 имеют одинаковые напряжения, как показано на фиг.9(b), помеха на линии GL затвора открывает TFT 201 и вызывает ошибочное изменение сигнала FR идентификации полярности в выходном сигнале OUT схемы памяти. В результате драйвер CS 104 ложно срабатывает.

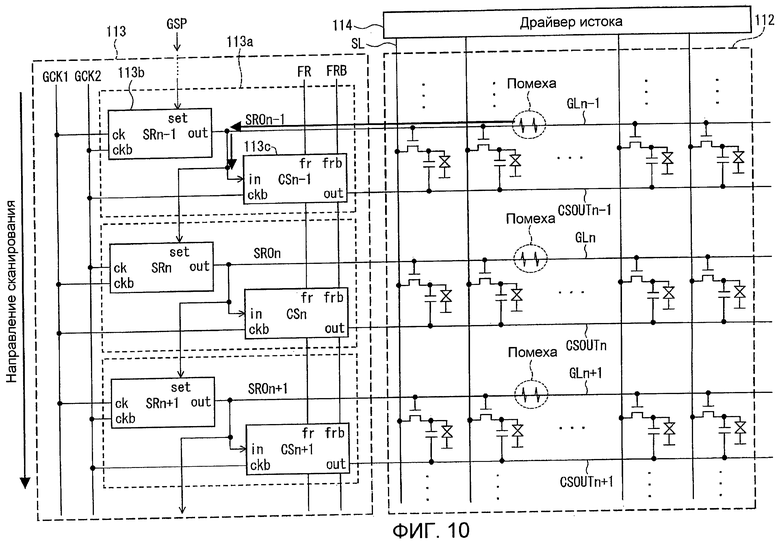

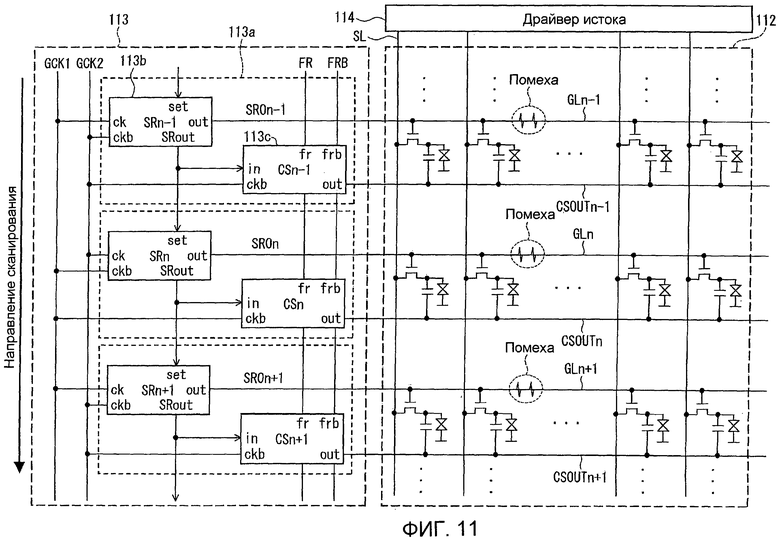

Дополнительно в показанном на фиг.8(b) устройстве 111 отображения на жидких кристаллах помеха проходит в драйвер CS по пути, показанном на фиг.10-13. В результате драйвер CS ложно срабатывает.

На фиг.10 драйвер 113 включает в себя каскад 113a, соответствующий каждой линии GL затвора. Каскад 113a включает в себя каскад 113а регистра сдвига и каскад 113b драйвера CS. Каскад 113a регистра сдвига образует драйвер затвора, и каскад 113c драйвера CS образует драйвер CS. Помеха, переданная от линии SL шины источника питания на линию GL шины затвора на секции 112 пикселов, внутри каскада 113a передается от линии GL шины затвора на вход каскада 113c драйвера CS. В результате драйвер CS ложно срабатывает и выводит ошибочный сигнал на линию CS CSOUT.

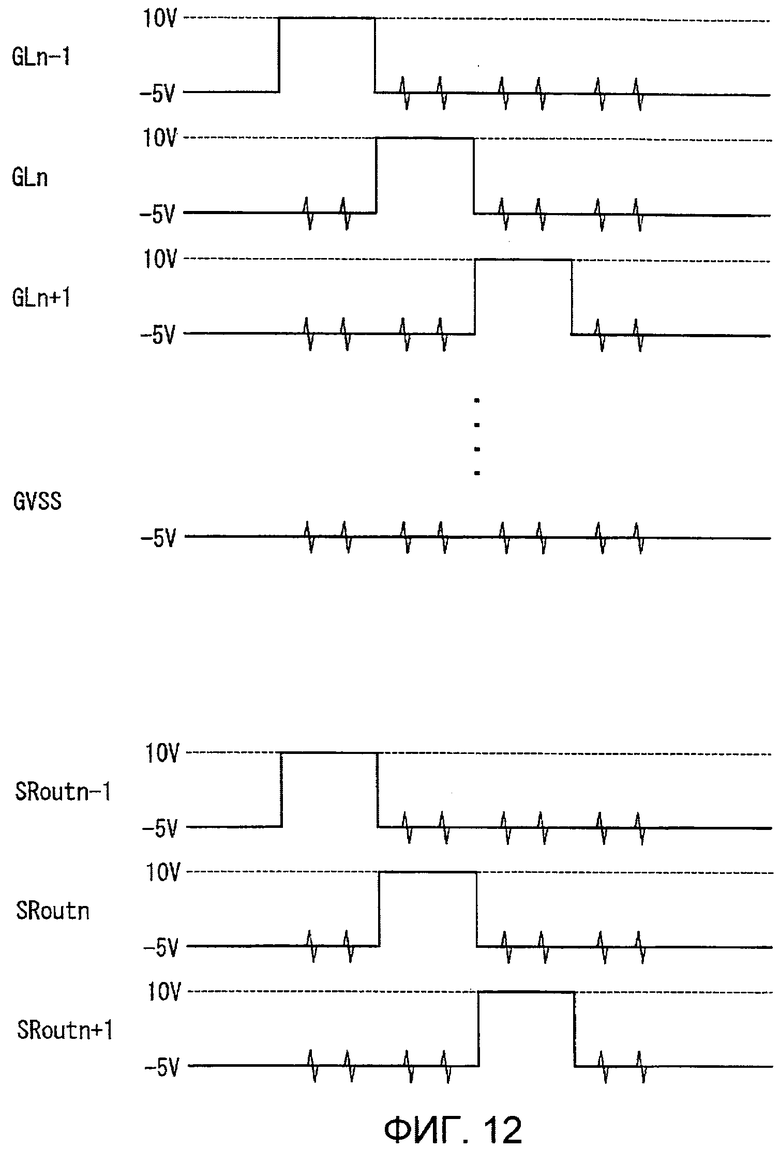

На фиг.11 показана конфигурация, в которой вход каскада 113c драйвера CS отделен от линии GL шины затвора. Однако в этом случае, а также как показано на фиг.12, помеха на линии GL шины затвора примешивается в выходной сигнал SRout сдвига для каскада 113b регистра сдвига из драйвера затвора через источник питания GVSS (являющийся низковольтным источником питания в случае полярности n-типа). Затем помеха передается на вход драйвера CS. В результате драйвер CS ложно срабатывает и выводит ошибочный сигнал на линию CS CSOUT.

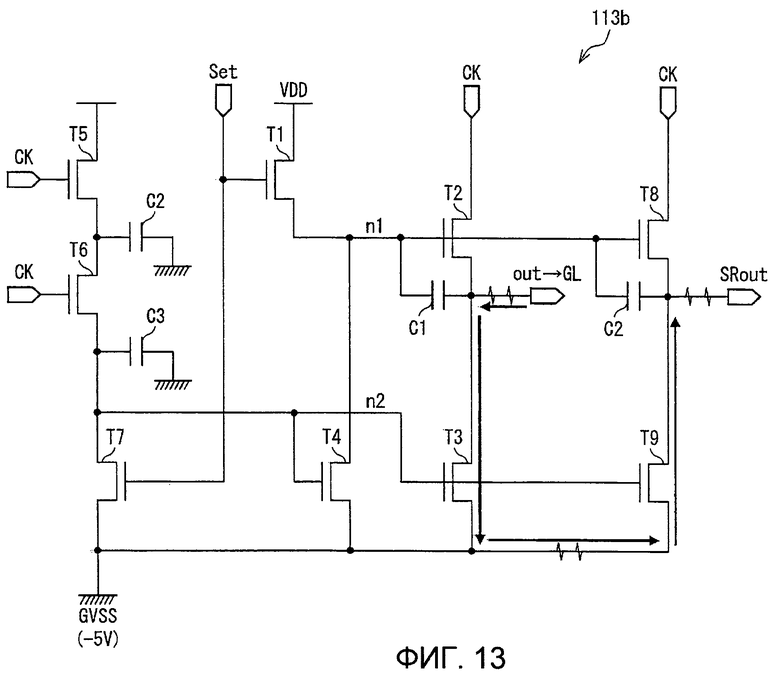

На фиг.13 показан путь передачи помехи внутри каскада 113b регистра сдвига в вышеописанном случае. Помеха проходит в каскад 113b регистра сдвига через выходной зажим out сигнала сканирования из линии GL шины затвора. Затем после прохождения через транзистор T3 помеха проходит через линию источника питания GVSS и впоследствии примешивается в выходной сигнал SRout сдвига через транзистор T9.

Таким образом, в традиционном устройстве отображения на жидких кристаллах, включающем в себя драйвер CS, имелась проблема, состоящая в том, что драйвер CS принимал помеху с линии шины затвора и ложно срабатывал.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩЕСТВА ИЗОБРЕТЕНИЯ

Настоящее изобретение направлено на устранение проблем.

Задача настоящего изобретения состоит реализации (i) схемы управления линии запоминающего конденсатора, способной исключить ложное срабатывание даже в случае, когда схема управления линии запоминающего конденсатора принимает помеху из линии сигнала сканирования, и (ii) устройства отображения, включающего в себя схему управления линии запоминающего конденсатора.

Для решения поставленной задачи схема управления линии запоминающего конденсатора в соответствии с настоящим изобретением управляет линией запоминающего конденсатора устройства отображения с активной матрицей и является управляемой выходными сигналами схемы управления линии сигнала сканирования, при этом схема управления линии запоминающего конденсатора включает в себя в качестве транзисторов множество транзисторов, имеющих одинаковый тип проводимости, при этом, по меньшей мере, одно из высоковольтного напряжения питания и низковольтного напряжения питания отличается от напряжения источника соответствующего логического уровня схемы управления линии сигнала сканирования, причем высоковольтное напряжение питания и низковольтное напряжение питания являются используемыми для формирования напряжения сигнала с предшествующего каскада на выходной каскад.

С помощью вышеупомянутого изобретения, поскольку, по меньшей мере, одно напряжение из высоковольтного напряжения питания и низковольтного напряжения питания, используемых для формирования напряжения сигнала с предшествующего каскада на выходной каскад, отличается от напряжения источника питания схемы управления линии сигнала сканирования, является возможным предотвратить нарушение помехой логического уровня схемы управления линии запоминающего конденсатора даже в случае, когда помеха на схему управления линии сигнала сканирования из линии сигнала данных проходит в схему управления линии запоминающего конденсатора. Это делает возможным исключение ложного срабатывания схемы управления линии запоминающего конденсатора.

Исходя из вышеизложенного, является возможным исключить ложное срабатывание схемы управления линии запоминающего конденсатора даже в случае, когда схема управления линии запоминающего конденсатора принимает помеху из линии сигнала сканирования.

Для решения вышеупомянутых проблем в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением все транзисторы являются транзисторами полярности n-канала.

В случае, когда транзисторы, включенные в схему управления линии запоминающего конденсатора, все являются транзисторами полярности n-канала, например, в случае схемы управления линии запоминающего конденсатора, встроенной в панель дисплея, образуется много плавающих точек. Соответственно, в изобретении, как упомянуто выше, такое различие в напряжении питания между схемой управления линии запоминающего конденсатора и схемой управления линии сигнала сканирования является очень эффективным для предотвращения вызванного помехой ложного срабатывания.

Для решения вышеупомянутых проблем в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением низковольтное напряжение питания, используемое для формирования напряжения сигнала схемы управления линии запоминающего конденсатора, выше, чем низковольтное напряжение питания, используемое для формирования выходного сигнала схемы управления линии сигнала сканирования.

В изобретении как упомянуто выше, поскольку низковольтное напряжение питания, используемое для формирования напряжения сигнала схемы управления линии запоминающего конденсатора, выше, чем низковольтное напряжение питания для формирования выходного сигнала схемы управления линии сигнала сканирования, в частности является возможным предотвращение вызванного помехой ошибочного распознавания логического Low как логического High.

Для решения вышеупомянутых проблем в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением все транзисторы являются транзисторами полярности p-канала.

В случае, когда транзисторы, включенные в схему управления линии запоминающего конденсатора, все являются транзисторами полярности p-канала, например, как в случае схемы управления линии запоминающего конденсатора, встроенной в панель дисплея, образуются множество плавающих точек. Соответственно, в изобретении, как упомянуто выше, такое различие в напряжении питания между схемой управления линии запоминающего конденсатора и схемой управления линии сигнала сканирования является очень эффективным для предотвращения вызванного помехой ложного срабатывания.

Для решения вышеупомянутых проблем в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением высоковольтное напряжение питания для формирования напряжения сигнала схемы управления линии запоминающего конденсатора ниже, чем высоковольтное напряжение питания для формирования выходного сигнала для схемы управления линии сигнала сканирования.

В изобретении, как упомянуто выше, поскольку высоковольтное напряжение питания для формирования напряжения сигнала схемы управления линии запоминающего конденсатора ниже, чем высоковольтное напряжение питания для формирования выходного сигнала схемы управления линии сигнала сканирования, в частности является возможным предотвращение вызванного помехой ошибочного распознавания логического High как логического Low.

Для решения вышеупомянутых проблем схема управления линии запоминающего конденсатора в соответствии с настоящим изобретением содержит каскады, соответствующие каждому из выходных сигналов схемы управления линии сигнала сканирования, причем каждый из каскадов включает в себя первый переключатель, первую схему памяти, первый переключатель передачи, первый аналоговый переключатель, второй переключатель, вторую схему памяти, второй переключатель передачи и второй аналоговый переключатель, причем первый аналоговый переключатель и второй аналоговый переключатель содержатся в выходном каскаде, первый переключатель предусмотрен между первой схемой памяти и входным зажимом для первого сигнала определения полярности, указывающего полярность напряжения запоминающего конденсатора, первый переключатель открывается и закрывается в соответствии с одним из выходных сигналов в качестве сигнала управления, причем одним из выходных сигналов, являющимся сигналом от схемы управления линии сигнала сканирования, соответствующей одному из каскадов, первая схема памяти хранит первый сигнал определения полярности, принимаемый через первый переключатель и выводимый в качестве первого сигнала определения полярности первого хранимого сигнала, первый переключатель передачи передает в качестве первого передаваемого сигнала первый хранимый сигнал, выводимый из первой схемы памяти, в соответствии с синхронизацией по введенному тактовому сигналу; первый аналоговый переключатель пердусмотрен между выходным зажимом на линии запоминающего конденсатора одного из каскадов и высоковольтным источником напряжения запоминающего конденсатора, первый аналоговый переключатель открывается и закрывается в соответствии с первым передаваемым сигналом в качестве сигнала управления, первый передаваемый сигнал является передаваемым от первого переключателя передачи, второй переключатель предусмотрен между второй схемой памяти и входным зажимом для второго сигнала определения полярности, имеющего полярность, противоположную таковой, для первого сигнала определения полярности, указывающего полярность напряжения запоминающего конденсатора, второй переключатель открывается и закрывается в соответствии с одним из выходных сигналов в качестве сигнала управления, причем одним из выходных сигналов является сигнал из схемы управления линии сигнала сканирования, соответствующей одному из каскадов, вторая схема памяти, хранящая второй сигнал определения полярности, принимаемый через второй переключатель и выводимый в качестве второго сигнала определения полярности второго хранимого сигнала, второй переключатель передачи, передающий в качестве второго передаваемого сигнала второй хранимый сигнал, выводимый из второй схемы памяти, в соответствии с синхронизацией по введенному тактовому сигналу, второй аналоговый переключатель, предусмотренный между выходным зажимом одного из каскадов и низковольтным источником питания напряжения запоминающего конденсатора, второй аналоговый переключатель открывается и закрывается в соответствии со вторым передаваемым сигналом в качестве сигнала управления, второй передаваемый сигнал является передаваемым от второго переключателя передачи, каждый сигнал из первого сигнала обратной полярности, первого хранимого сигнала, первого переданного сигнала, второго сигнала обратной полярности, второго хранимого сигнала и второго переданного сигнала имеет напряжение, соответствующее напряжению сигнала.

При изобретении, как упомянуто выше, схема управления линии запоминающего конденсатора может осуществлять без ложного срабатывания смену полярности напряжения запоминающего конденсатора, которое является выводимым на соответствующую линию запоминающего конденсатора, всякий раз, когда каждый выходной сигнал схемы управления линии сигнала сканирования становится активным.

Для решения вышеупомянутых проблем в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением первым переключателем и вторым переключателем являются транзисторы.

При изобретении, как упомянуто выше, становится возможным легко выполнять первый переключатель и второй переключатель.

Для решения вышеупомянутых проблем в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением первой схемой памяти является конденсатор, подключенный между (i) выходным зажимом первого переключателя и входным зажимом первого переключателя передачи на одной стороне и (ii) низковольтным питанием первого хранимого сигнала на другой стороне; и второй схемой памяти является конденсатор, подключенный между (i) выходным зажимом второго переключателя и входным зажимом второго переключателя передачи на одной стороне и (ii) низковольтным источником питания второго хранимого сигнала на другой стороне.

При изобретении, как упомянуто выше, становится возможным легко выполнять первую схему памяти и вторую схему памяти.

Для решения вышеупомянутых проблем в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением, первым переключателем передачи и вторым переключателем передачи являются транзисторы, открывающиеся и закрывающиеся в соответствии с тактовым сигналом в качестве сигнала управления.

При изобретении, как упомянуто выше, становится возможным легко формировать первый переключатель передачи и второй переключатель передачи.

Для решения вышеупомянутых проблем устройство отображения в соответствии с настоящим изобретением включает в себя схему управления линии запоминающего конденсатора. При изобретении, как упомянуто выше, является возможным осуществить схему управления линии запоминающего конденсатора, способную исключить ложное срабатывание даже в случае, когда схема управления линии запоминающего конденсатора принимает помеху из линии сигнала сканирования.

Для решения вышеупомянутых проблем в устройстве отображения в соответствии с настоящим изобретением схема управления линии запоминающего конденсатора и схема управления линии сигнала сканирования выполнены в виде прослойки линии сигнала сканирования и являются отделенными друг от друга.

В устройстве отображения согласно изобретению, как упомянуто выше, схема управления линии запоминающего конденсатора и схема управления линии сигнала сканирования выполнены так, чтобы линия сигнала сканирования находилась между схемой управления линии запоминающего конденсатора и схемой управления линии сигнала сканирования и так, чтобы являться отделенными друг от друга. В таком устройстве отображения становится возможным предотвращать ложное срабатывание схемы управления линии запоминающего конденсатора.

Для решения вышеупомянутых проблем в устройстве отображения в соответствии с настоящим изобретением и схема управления линии запоминающего конденсатора, и схема управления сигнала сканирования выполнены на одном конце линии сигнала сканирования.

В устройстве отображения согласно изобретению, как упомянуто выше, и схема управления линии запоминающего конденсатора, и схема управления сигнала сканирования выполнены на одном конце линии сигнала сканирования. В таком устройстве отображения становится возможным предотвращать ложное срабатывание схемы управления линии запоминающего конденсатора.

Более полное понимание других задач, характеристик и достоинств настоящего изобретения можно получить из нижеследующего описания. Дополнительно преимущества настоящего изобретения станут очевидными при обращении к нижеследующему описанию, рассматриваемому вместе с сопроводительными чертежами.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

В дальнейшем изобретение поясняется описанием предпочтительных вариантов воплощения со ссылками на сопроводительные чертежи, на которых:

фиг.1 изображает временную диаграмму сигнала, показывающую работу драйвера CS, в соответствии с вариантом осуществления настоящего изобретения;

фиг.2 изображает принципиальную блок-схему, иллюстрирующую конфигурацию драйвера CS, выполняющего работу, показанную на фиг.1;

фиг.3 изображает принципиальную схему, иллюстрирующую конкретный пример конфигурации драйвера CS, показанного на фиг.2;

фиг.4 изображает принципиальную схему, иллюстрирующую конфигурацию драйвера затвора;

фиг.5 изображает временную диаграмму сигнала, показывающую работу драйвера затвора, показанного на фиг.4;

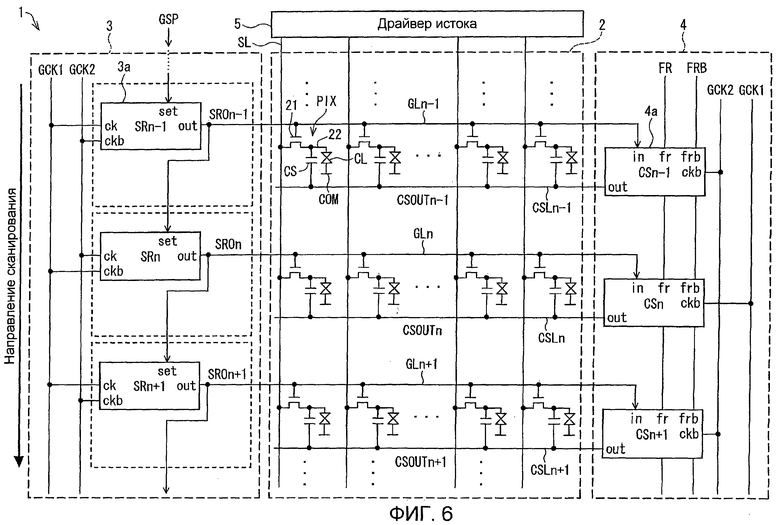

фиг.6 изображает принципиальную блок-схему, иллюстрирующую конфигурацию первого устройства отображения, в соответствии с вариантом осуществления настоящего изобретения;

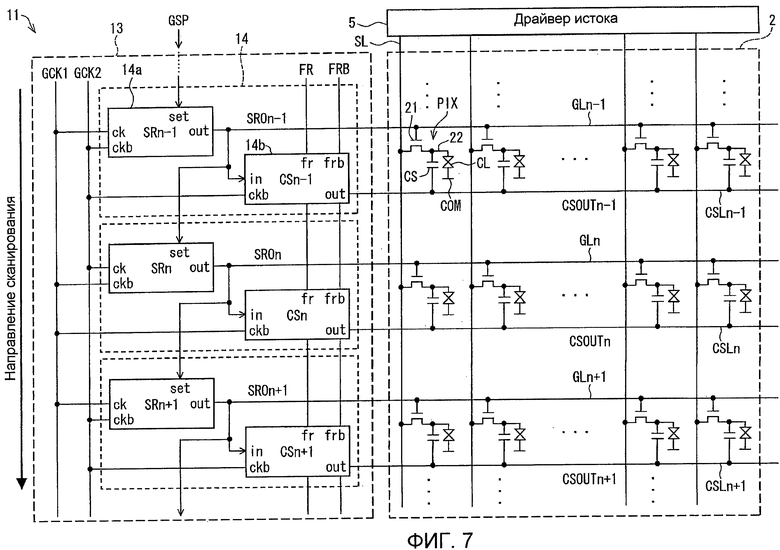

фиг.7 изображает принципиальную блок-схему, иллюстрирующую конфигурацию второго устройства отображения в соответствии с вариантом осуществления настоящего изобретения;

фиг.8 изображает традиционные способы, причем и (a), и (b) по фиг.8 являются блок-схемами, показывающими каждая конфигурацию устройства отображения;

фиг.9 изображает традиционные способы, причем и (a) по фиг.9 - принципиальная схема, показывающая первый обычный путь для поступления помехи, и (b) по фиг.9 - временная диаграмма сигнала для сигнала, на который накладывается помеха;

фиг.10 изображает принципиальную схему, показывающую второй обычный путь для поступления помехи;

фиг.11 изображает принципиальную схему, показывающую третий обычный путь для поступления помехи;

фиг.12 изображает временную диаграмму сигнала для сигнала, на который накладывается помеха через третий путь для поступления помехи;

фиг.13 изображает принципиальную схему, подробно иллюстрирующую третий путь для поступления помехи;

фиг.14 изображает блок-схему устройства отображения на жидких кристаллах, иллюстрирующую традиционные проблемы;

фиг.15 изображает принципиальную схему, показывающую механизм передачи помехи для иллюстрации традиционных проблем.

ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Нижеследующее поясняет один вариант осуществления настоящего изобретения со ссылкой на фиг.1-7.

На фиг.6 показана конфигурация устройства 1 отображения на жидких кристаллах (устройства отображения) в соответствии с настоящим вариантом осуществления.

Устройство 1 отображения на жидких кристаллах является устройством отображения с активной матрицей и включает в себя секцию 2 пикселов, драйвер 3 затвора (схема управления линии сигнала сканирования) драйвер 4 CS (схема управления линии запоминающего конденсатора), и драйвер 5 истока (линия сигнала данных). Секция 2 пикселов и драйвер 3 затвора соединены посредством линий шины затвора GL (линий сигнала сканирования), и секция 2 пикселов, и драйвер 4 CS соединены посредством линий CSL шины CS (линии запоминающего конденсатора). Дополнительно секция 2 пикселов и драйвер 5 истока соединены посредством линий SL шины истока (линий сигнала данных). Каждая строка линий CSL шины CS управляется индивидуально.

Секция 2 пикселов сконфигурирована так, чтобы множество пикселов PIX ... располагались в виде матрицы. Каждый пиксел PIX включает в себя TFT 21, жидкий кристалл-конденсатор CL и запоминающий конденсатор CS. TFT 21 является элементом выборки для каждого типа пиксела PIX активной матрицы. Затвор TFT 21 соединен с линией GL шины затвора, и исток TFT 21 соединен с линией SL шины истока. Дополнительно сток TFT 21 соединен с электродом 22 пиксела. Жидкий кристалл-конденсатор CL сконфигурирован таким образом, чтобы обеспечивался жидкокристаллический слой между электродом 22 пиксела и общим электродом COM. Запоминающий конденсатор CS сконфигурирован так, чтобы обеспечивался слой диэлектрика между электродом 22 пиксела и линией CSL запоминающего конденсатора.

Драйвер 3 затвора включает в себя регистр сдвига, включающий в себя множество каскадов 3a ... регистра сдвига в каскадном соединении. Каждый каскад 3a регистра сдвига включает в себя установочный входной зажим set, выходной зажим out и входные зажими ck и ckb тактовых сигналов.

k-ый каскад 3a регистра сдвига (k=..., n-1, n, n+1 ...) обозначается SRk, и выходной сигнал, выводимый с выходного зажима out каскада SRk, обозначается SRoutk. Каскад 3a регистра сдвига, обозначенный SRk, управляет соответствующей линией GLk затвора с использованием выходного сигнала SRoutk. Стартовый импульс GSP затвора подается на установочный входной зажим set каскада 3a первого каскада регистра сдвига. Выходной зажим out из каждого каскада 3a регистра сдвига соединен с установочным входным зажимом set следующего (k+1)-го каскада 3a регистра сдвига. Другими словами, выходной сигнал SRO, выводимый с выходного зажима out из каждого каскада 3a регистра сдвига, становится установочным сигналом каскада 3a регистра сдвига для следующего каскада.

Дополнительно для одного любого каскада из нечетно пронумерованных каскадов в составе каскадов 3a регистра сдвига и для четно пронумерованных каскадов в составе каскадов 3a регистра сдвига тактовый сигнал затвора GCK 1 подается на входные зажимы ck тактовых сигналов, тогда как тактовый сигнал затвора GCK 2 подается на входные зажимы ckb тактовых сигналов. Между тем, для другого каскада из каскадов 3a регистра сдвига для каскадов с нечетным номером и каскадов 3a регистра сдвига для каскадов с четным номером тактовый сигнал затвора GCK2 подается на входные зажимы ck тактовых сигналов, тогда как тактовый сигнал затвора GCK1 подается на входные зажимы ckb тактовых сигналов. Тактовый сигнал затвора GCK1 и тактовый сигнал затвора GCK2 имеют одинаковый период такта, и активные периоды, то есть периоды уровня High тактовых сигналов GCKL и GCK2 затвора не накладываются друг на друга.

Драйвер CS 4 выполнен так, чтобы между драйвером CS 4 и драйвером 3 затвора обеспечивалась линия GL шины затвора и включала в себя множество каскадов 4a драйвера CS в каскадном соединении. Каждый каскад 4a драйвера CS включает в себя входные зажимы fr и frb полярности, входной зажим in сигнала сканирования, выходной зажим out и тактовый входной зажим ckb. k-ый каскад 4a драйвера CS (k=..., n-1, n, n+1...) обозначается CSk, и выходной сигнал, выводимый с выходного зажима CSk, обозначается CSOUTk. Каскад 4a драйвера CS, представленный посредством CSk, управляет соответствующими линиями CSLk шины CS, используя выходной сигнал CSOUTk в качестве напряжения запоминающего конденсатора.

В каждом каскаде 4a драйвера CS сигналы определения полярности FR и FRB все вводятся одновременно. Сигналы определения полярности FR имеют обратную фазу относительно сигнала определения полярности FRB. Кроме того, тактовый сигнал затвора подается на тактовый входной зажим ckb k-го каскада 4a драйвера CS. Этот тактовый сигнал затвора является тактовым сигналом GCK1 затвора или тактовым сигналом GCK2 затвора, который подается на тактовый входной зажим ckb k-го каскада 3a регистра сдвига. Драйвер 5 истока выводит на каждую из линий SL шины затвора сигнал данных, соответствующий данным отображения, подаваемым извне.

В устройстве 1 отображения на жидких кристаллах в соответствии с вышеупомянутой конфигурацией, все компоненты из секции 2 пикселов, драйвера 3 затвора, драйвера 4 CS и драйвера 5 истока формируются на стеклянной подложке с использованием аморфного кремния, поликристаллического кремния, кремния CG или подобного. Кроме того, каждый компонент из драйвера 3 затвора, драйвера 4 CS и драйвера 5 истока включает в себя, в качестве транзисторов, только множество транзисторов, имеющих одинаковый тип проводимости. В настоящем варианте осуществления, в частности, все транзисторы выполнены из TFT-транзисторов, имеющих полярность n-канала.

Затем на фиг.2 показана блок-схема, иллюстрирующая пример конфигурации каждого каскада 4a драйвера CS, включенного в драйвер 4 CS. Дополнительно, на фиг.3 показана принципиальная схема, в которой каждый из блоков по фиг.2 образован конкретным элементом схемы.

Каскад 4a драйвера CS включает в себя аналоговые переключатели 4la и 41b, схемы 42a и 42b памяти, переключатели 43a и 43b передачи и аналоговые переключатели 44a и 44b. Должно быть отмечено, что поскольку на фиг.2 показан в качестве примера n-ый каскад 4a шины драйвера CS, в качестве соответствующего помечен ссылочный символ n. Все аналоговые переключатели 4la, 41b, 44a и 44b выполнены из TFT-транзисторов типа n-канала соответственно, как показано посредством транзисторов T1 к T4 на фиг.3.

Аналоговый переключатель 4la открывается/закрывается в соответствии с выходным сигналом SRO (который является сигналом сканирования, вводимым из линии GL шины затвора) в качестве сигнала управления, и принимает в схему памяти 42a сигнал FR определения полярности, который подается на входной зажим fr полярности. Аналоговый переключатель 41b, в соответствии с выходным сигналом SRO (который является сигналом сканирования, вводимым по линии GL шины затвора) в качестве сигнала управления, принимает в схему памяти 42b сигнал определения полярности FRB, который подается на входной зажим frb полярности. На фиг.3 аналоговый переключатель 4la образован транзистором T1, и выходной сигнал SRO подается на затвор транзистора T1. Дополнительно на фиг.3 аналоговый переключатель 41b образован транзистором T2, и выходной сигнал SRO подается на затвор транзистора T2.

Схема 42a памяти хранит сигнал FR определения полярности, который был принят через аналоговый переключатель 41а, и выводит хранимый сигнал LA. Схема памяти 42b хранит сигнал определения полярности FRB, который был принят через аналоговый переключатель 41b, и выводит хранимый сигнал LB. На фиг.3 схему памяти 42a образует конденсатор C1, и конденсатор C1 подключен между выходным зажимом аналогового переключателя 4la и источником питания VSS. На фиг.3 схему памяти 42b образует конденсатор C2, и конденсатор C2 подключен между выходным зажимом аналогового переключателя 41b и источником питания VSS.

Переключатель 43a передачи, в качестве передаваемого сигнала LAO, передает хранимый сигнал LA, выводимый из схемы памяти 42a. Хранимый сигнал LA передается синхронно с тактовым сигналом CKB (то есть CKB1 или CKB2), вводимым через тактовый входной зажим ckb. Переключатель 43b передачи в качестве передаваемого сигнала LAOB, передает хранимый сигнал LAB, выводимый из схемы памяти 42b. Хранимый сигнал LAB передается синхронно с тактовым сигналом CKB (то есть CKB1 или CKB2), вводимому через тактовый входной зажим ckb. На фиг.3 переключатель 43a передачи выполнен на транзисторе T3, и тактовый сигнал CKB подается на затвор транзистора T3. Дополнительно на фиг.3 аналоговый переключатель 43b выполнен на транзисторе T4, и тактовый сигнал CKB подается на затвор транзистора T4.

Низковольтное напряжение VSS питания (ссылочный символ VSS источника питания используется в качестве подстановочного выражения) имеет значение Low для сигналов FR и FRB определения полярности, хранимых сигналов LA и LAB и передаваемых сигналов LAO и LAOB. Низковольтное напряжение VSS питания также может быть описано в качестве низковольтного напряжения VSS питания, используемого для формирования напряжения сигнала с предшествующего каскада на выходной каскад для каскада 4a драйвера CS. Это низковольтное напряжение VSS питания имеет соотношение VSS>VCSL с низковольтным напряжением VCSL питания для каскада 4a драйвера CS на выходном каскаде (то есть выходном каскаде 4 драйвера CS), включающем в себя аналоговые переключатели 44a и 44b. Затем в настоящем варианте осуществления напряжение VSS питания устанавливается, чтобы оно было выше низковольтного напряжения GVSS питания драйвера 3 затвора.

Аналоговый переключатель 44a открывается/закрывается в соответствии с передаваемым сигналом LAO, в качестве сигнала управления, который передается от переключателя 43a передачи, и, таким образом, выводит на выходной зажим out, в качестве выходного сигнала CSOUT, высоковольтное напряжение VCSH питания линии CSL запоминающего конденсатора. Аналоговый переключатель 44b открывается/закрывается в соответствии с передаваемым сигналом LAOB, в качестве сигнала управления, который передается от переключателя 43b передачи, и, таким образом, выводит на выходной зажим out, в качестве выходного сигнала CSOUT, низковольтное напряжение VCSL питания линии CSL запоминающего конденсатора. На фиг.3 аналоговый переключатель 44a выполнен на транзисторе T5, и передаваемый сигнал LAO подается на затвор транзистора T5. Кроме того, на фиг.3 аналоговый переключатель 44b выполнен на транзистор T6, и передаваемый сигнал LAOB подается на затвор транзистора T6.

На фиг.1 показана временная диаграмма каждого сигнала для драйвера 4 CS.

Как описано выше, низковольтное напряжение VSS питания, используемое для формирования напряжения сигнала с предшествующего каскада на выходной каскад каскада 4a драйвера CS, устанавливается выше низковольтного напряжения GVSS питания драйвера 3 затвора.

В каждом каскаде 4a драйвера CS сигнал FR определения полярности принимается с синхронизацией, при которой сигнал сканирования, вводимый из линии GL шины затвора, становится High. Сигналы FR и FRB определения полярности переключаются между High и Low в том же периоде такта, что и таковые тактовые сигналы CK и CKB (то есть CKB1 и CKB2). Период импульса каждого сигнала установлен так, чтобы каждый период импульсов тактовых сигналов CK и CKB находился в рамках каждого периода импульсов сигналов FR и FRB определения полярности. Дополнительно, сигналом FR определения полярности является High в периоде, в котором тактовый сигнал CK является High, или на активном уровне, тогда как сигналом FRB определения полярности является High в периоде, в котором тактовый сигнал CKB является высоким, или на активном уровне.

Когда сигнал сканирования входит в период High в периоде, в котором тактовый сигнал CK находится на уровне High, аналоговый переключатель 4la открывается. Затем сигнал FR определения полярности сохраняется в схеме 42a памяти, и схема 42a памяти выводит сигнал High в виде хранимого сигнала LA. Этот хранимый сигнал High удерживается в одном каскаде 4 драйвера CS, пока сигнал сканирования High не войдет в следующий период High, который появляется до конца одного последующего периода кадра.

Переключатель 43a передачи передает передаваемый сигнал LAO, которым является High, совпадающим с моментом времени, в который тактовый сигнал CKB становится High немедленно после вышеописанного периода, в который тактовым сигналом CK является High, который является одним периодом строчной развертки после точки, в которой тактовый сигнал CK становится High. Поскольку участок между переключателем 43a передачи и затвором аналогового переключателя 44a становится плавающим, когда переключатель 43a передачи закрыт, передаваемый сигнал LAO поддерживает напряжение постоянным, пока переключатель 43a передачи не откроется снова. Период High передаваемого сигнала LAO продолжается, пока не будет повышения тактового сигнала CBK до High немедленно после смены хранимого сигнала LA в Low.

Полярность каждого сигнала на пути входа сигнала FRB определения полярности является противоположной таковой на пути входа сигнала FR определения полярности. Другими словами, хранимый сигнал LAB имеет обратную фазу по отношению к фазе хранимого сигнала LA, и передаваемый сигнал LAOB имеет обратную фазу по отношению к фазе передаваемого сигнала LAO.

Таким образом, в периоде, в котором передаваемым сигналом LAO является High, аналоговый переключатель 44a открыт, и аналоговый переключатель 44b закрыт. В результате выходной сигнал CSOUT становится напряжением VCSH питания на уровне High. Напротив, в периоде, в котором передаваемым сигналом LAOB является High, аналоговый переключатель 44b открыт, и аналоговый переключатель 44a закрыт. В результате выходным сигналом CSOUT становится напряжение VCSL питания на уровне Low. Таким образом, полярность напряжения линии CSL шины CS является обратной для каждого кадра.

Напряжениями VDD и VSS питания, используемыми для формирования напряжений сигнала с предшествующего каскада на выходной каскад для каскада 4a драйвера CS, являются, например, 10 В и 0 В соответственно.

При этом низковольтное напряжение VSS питания для драйвера 4 CS устанавливается выше низковольтного напряжения питания GVSS для драйвера 3 затвора (например, -5 В, как описано ниже). Это обеспечивает, что будет маловероятным, что уровень помехи станет таким же высоким, как логический High по сравнению с напряжением VSS источника питания, даже если помеха из линии SL шины истока накладывается на линию GL шины затвора и проходит в драйвер 4 CS. Соответственно, нарушение сигнала Low не вызывает ложное срабатывание драйвера 4 CS на неактивном уровне из-за помехи, которая поступила в драйвер 4 CS, и драйвер 4 CS способен выводить корректный выходной сигнал CSOUT.

Кроме того, на фиг.4 иллюстрируется пример конфигурации каждого каскада 3a регистра сдвига, включенного в драйвер 3 затвора.

Каскад 3a регистра сдвига включает в себя транзисторы T11-T17, которые выполнены из n-канальных TFT-транзисторов, и конденсаторы C11-C17.

Затвор транзистора T11 соединен с установочным входным зажимом set, и сток транзистора T11 соединен с высоковольтным источником VDD питания драйвера 3 затвора. Дополнительно исток транзистора T11 соединен со стоком транзистора T14 посредством узла n1. Затвор транзистора T12 соединен с узлом n1, и сток транзистора T12 соединен с тактовым входным зажимом ck. Кроме того, исток транзистора T12 соединен со стоком транзистора T13 в точке соединения, которая является выходным зажимом out регистра 3a сдвига. Истоки транзисторов T13 и T14 соединены с низковольтным источником GVSS питания драйвера 3 затвора, и затворы транзисторов T13 и T14 соединены с узлом n2, поясненным ниже.

Дополнительно конденсатор C11 подключен между узлом n1 и выходным зажимом out.

Затвор транзистора T15 соединен с тактовым входом ck, и сток транзистора T15 соединен с источником VDD питания. Кроме того, исток транзистора T15 и сток транзистора T16 соединены между собой. Конденсатор C12 подключен между источником GVSS питания и точкой соединения между истоком транзистора T15 и стоком транзистора T16. Затвор транзистора T16 соединен с тактовым входным зажимом ckb. Кроме того, исток транзистора 16 соединен со стоком транзистора T17 и с узлом n2. Конденсатор C13 подключен между узлом n2 и источником GVSS питания.

Затвор транзистора T17 соединен с установочным входным зажимом set, и исток транзистора T17 соединен с источником GVSS питания.

Напряжением VDD источника VDD питания (ссылочный символ VDD источника питания используется в качестве подстановочного выражения) и напряжением GVSS источника GVSS питания (ссылочный символ GVSS источника питания используется в качестве подстановочного выражения), являются, например, 10 В и -5 В соответственно.

На фиг.5 приведена временная диаграмма входного сигнала управления, используемого в показанном на фиг.4 каскаде 3a регистра сдвига.

Тактовые сигналы CK и CKB (то есть CK1 и CK2) являются такими же, как поясненные на основе фиг.1. Когда установочный сигнал Set подается на установочный входной зажим set, как проиллюстрировано на фиг.6, синхронно с периодом High тактового сигнала CKB, выходной сигнал SRO является выводимым с выходного зажима out и становится сигналом сканирования. Этот выходной сигнал SRO входит в период High в периоде High тактового сигнала CK некоторого периода затвора после ввода установочного сигнала Set. Нижеследующее кратко поясняет работу схемы. Как показано на фиг.4, пока установочным сигналом Set является High, транзисторы T11, T12 и T17 открыты, тогда как транзисторы T13 и T14 закрыты. В результате тактовый сигнал CK является выводимым в качестве выходного сигнала SRO на выходом зажиме out. Пока тактовым сигналом CK является High, транзистор 15 открыт и заряжает конденсатор C12, используя напряжение VDD питания. Транзистор T16 открыт, пока тактовым сигналом CKB является High, и повторно заряжает конденсатор С13 до напряжения VDD, используя напряжение конденсатора C12 в течение периода, в котором установочным сигналом Set является Low. Когда установочным сигналом Set становится High, и транзистор T17 открывается, конденсатор C16 электрически разряжается до достижения напряжения GVSS питания.

Затем на фиг.7 показана другая конфигурация устройства 11 отображения на жидких кристаллах (устройства отображения) в соответствии с настоящим вариантом осуществления. Устройство 11 отображения на жидких кристаллах включает в себя секцию отображения 2, драйвер 5 истока и драйвер 13. Секция 2 отображения и драйвер 5 истока имеют такую же конфигурацию, как таковые, включенные в устройство 1 отображения на жидких кристаллах. Драйвер 13 сконфигурирован с возможностью включать в себя множество каскадов 14 ... в каскадном соединении. Каждый каскад включает в себя каскад 14a регистра сдвига и каскад 14b драйвера CS.

Каскад 14a регистра сдвига имеет внутреннюю конфигурацию, такую же, как каскад 3a драйвера CS устройства 1 отображения на жидких кристаллах, и каскад 14b драйвера CS имеет такую же внутреннюю конфигурацию, как каскад 4a драйвера CS устройства 1 отображения на жидких кристаллах. Кроме того, выходной зажим out каскада 14a регистра сдвига соединен с входным зажимом сигнала сканирования в каскаде 14b драйвера CS.

В вышеупомянутом примере и драйвер CS (схема управления линии запоминающего конденсатора), и драйвер затвора (схема управления линии сигнала сканирования) выполнены на одном конце линии GL шины затвора. То есть драйвер CS и драйвер затвора целиком выполнены в области одной стороны устройства 1 отображения на жидких кристаллах. Как в устройстве 1 отображения на жидких кристаллах, в этой конфигурации низковольтное напряжение VSS питания, используемое для формирования напряжения сигнала с предшествующего каскада на выходной каскад в драйвере CS, устанавливается выше низковольтного напряжения GVSS питания драйвера затвора. Это делает возможным предотвращение ложного срабатывания драйвера CS, даже если на линию GL шины затвора накладывается помеха и из линии шины SL истока и поступает в драйвер CS.

Выше был описан вариант осуществления настоящего изобретения. В описании выше варианта осуществления настоящего изобретения все TFT-транзисторы сконфигурированы с возможностью иметь только полярность n-канала. Однако настоящее изобретение не ограничивается таковым. Все TFT-транзисторы могут конфигурироваться с возможностью иметь полярность p-канала. В таком случае путем установки высоковольтного напряжения питания, используемого для формирования напряжения сигнала с предшествующего каскада на выходной каскад в драйвере CS, выше высоковольтного напряжения питания драйвера затвора, является возможным предотвращение ложного срабатывания драйвера CS даже в случае, когда помеха накладывается на линию GL шины затвора из линии SL шины истока и поступает в драйвер CS.

Дополнительно, в вышеупомянутом примере транзисторы сконфигурированы в виде TFT-транзисторов, выполненных на стеклянной подложке. Однако настоящее изобретение не ограничивается таковым. Транзисторы могут быть сконфигурированы с использованием только типовых полевых транзисторов полярности n-канала или только полевых транзисторов полярности p-канала. Соответственно, каждый драйвер может быть внешним драйвером. Кроме того, тип проводимости, то есть полярность канала транзисторов должна быть одинаковой, по меньшей мере, между драйвером затвора и драйвером CS. Однако не является необходимым, чтобы полярность канала для других схем, например драйвера истока или подобного, была той же полярности.

Дополнительно, в вышеупомянутом примере в случае, когда транзисторами являются транзисторы полярности n-канала, низковольтное напряжение питания, используемое для формирования напряжения сигнала с предшествующего каскада на выходной каскад в драйвере CS, устанавливается выше низковольтного напряжения питания драйвера затвора. Между тем, в случае, когда транзисторами являются транзисторы полярности p-канала, высоковольтное напряжение питания, используемое для формирования напряжения сигнала с предшествующего каскада на выходной каскад в драйвере CS, установлены ниже высоковольтного напряжения питания драйвера затвора. Однако настоящее изобретение не ограничивается таковым. Например, в случае, когда транзисторами являются транзисторы полярности n-канала, высоковольтное напряжение питания, используемое для формирования напряжения сигнала с предшествующего каскада на выходной каскад в драйвере CS, может быть установлено выше высоковольтного напряжения питания драйвера затвора. Между тем, в случае, когда транзисторами являются транзисторы полярности n-канала, низковольтное напряжение питания, используемое для формирования напряжения сигнала с предшествующего каскада на выходной каскад в драйвере CS, может быть установлено ниже низковольтного напряжения питания драйвера затвора. Другими словами, чтобы транзисторы могли осуществлять различение между логическим High и логическим Low при наложенной помехе и работать, по меньшей мере, одно напряжение из высоковольтного напряжения питания и низковольтного напряжения питания, используемых для формирования сигнала с предшествующего каскада на выходной каскад в драйвере CS, должно отличаться от такового для драйвера затвора.

Дополнительно, даже в случае, как показано на фиг.10 и 11, когда драйвер затвора и драйвер CS выполняются на одном конце секции пикселов, является возможным предотвращение ложного срабатывания драйвера CS путем обеспечения, по меньшей мере, одного напряжения из высоковольтного напряжения питания и низковольтного напряжения питания, используемых для формирования сигнала с предшествующего каскада на выходной каскад в драйвере CS, отличающегося от такового для драйвера затвора.

Соответственно, выходной сигнал, используемый драйвером CS из схемы управления линии сигнала сканирования, может быть сигналом из линии сигнала сканирования, как показано на фиг.6, 7 и 10 или как показано на фиг.11, выходным сигналом может быть установочный сигнал, выводимый на другой каскад (следующий каскад по фиг.11) каждым каскадом, включая каскад регистра сдвига в составе схемы управления линии сигнала сканирования.

Дополнительно объектом настоящего изобретения является схема управления линии запоминающего конденсатора; однако настоящее изобретение подобным образом применимо к обычной схеме управления линии в случае управления планарной коммутацией (IPS).

Настоящее изобретение не ограничивается вышеописанными вариантами осуществления, и возможны различные модификации в рамках прилагаемой формулы изобретения. Другими словами, исполнения, полученные объединением технических средств, как надлежит, в рамках объема нижеследующей формулы изобретения, также включаются в рамки объема технической задачи по настоящему изобретению.

Как описано выше, в схеме управления линии запоминающего конденсатора в соответствии с настоящим изобретением, по меньшей мере, одно напряжение из высоковольтного напряжения питания и низковольтного напряжения питания, используемых для формирования сигнала с предшествующего каскада на выходной каскад, отличается от напряжения питания схемы управления линии сигнала сканирования.

Это делает возможным осуществление схемы управления запоминающего конденсатора, способной исключить ложное срабатывание даже в случае, когда схема управления запоминающего конденсатора принимает помеху из линии сигнала сканирования.

Подробные пояснения изобретения, которые были даны в связи с конкретными вариантами осуществления и примерами, предназначены просто для пояснения технической сути настоящего изобретения. Такие конкретные примеры не должны интерпретироваться лишь в ограничительном смысле и могут быть осуществлены различные модификации в рамках существа изобретения и объема нижеследующей формулы изобретения.

Промышленная применимость

Настоящее изобретение может соответствующим образом использоваться, в частности, для устройства отображения на жидких кристаллах.

Перечень ссылочных символов

1, 11 - устройство отображения на жидких кристаллах (устройство отображения)

4 - драйвер CS (схема управления линии запоминающего конденсатора)

13 - драйвер (схема управления линии запоминающего конденсатора)

VDD - напряжения источника питания (высоковольтное напряжение источника питания для схемы управления линии сигнала сканирования, высоковольтное напряжение источника питания, используемого для формирования напряжения сигнала с предшествующего каскада на выходной каскад в схеме управления линии запоминающего конденсатора)

VSS - напряжение источника питания (низковольтное напряжение источника питания, используемого для формирования напряжения сигнала с предшествующего каскада на выходной каскад в схеме управления линии запоминающего конденсатора)

GVSS - напряжение источника питания (низковольтное напряжение источника питания схемы управления линии сигнала сканирования)

VCSH - напряжение источника питания (высоковольтное напряжение источника питания схемы управления линии запоминающего конденсатора)

VCSL - напряжение источника питания (низковольтное напряжение источника питания схемы управления линии запоминающего конденсатора)

Изобретение относится к вычислительной технике. Технический результат заключается в исключении ложного срабатывания. Схема управления линии запоминающего конденсатора, управляющая линией запоминающего конденсатора устройства отображения с активной матрицей и управляемая выходными сигналами схемы управления линии сигнала сканирования, содержащая в качестве транзисторов множество транзисторов, имеющих одинаковый тип проводимости, при этом по меньшей мере, одно напряжение из высоковольтного напряжения питания и низковольтного напряжения питания отличается от напряжения питания соответствующего логического уровня для схемы управления линии сигнала сканирования, причем высоковольтное напряжение питания и низковольтное напряжение питания используются для формирования напряжения сигнала с предшествующего каскада на выходной каскад. 2 н. и 10 з.п. ф-лы, 15 ил.

1. Схема управления линии запоминающего конденсатора, управляющая линией запоминающего конденсатора устройства отображения с активной матрицей и управляемая выходными сигналами схемы управления линии сигнала сканирования, содержащая в качестве транзисторов множество транзисторов, имеющих одинаковый тип проводимости, при этом:

по меньшей мере, одно напряжение из высоковольтного напряжения питания и низковольтного напряжения питания отличается от напряжения питания соответствующего логического уровня для схемы управления линии сигнала сканирования, причем высоковольтное напряжение питания и низковольтное напряжение питания используются для формирования напряжения сигнала с предшествующего каскада на выходной каскад.

2. Схема по п.1, в которой все транзисторы являются транзисторами полярности n-канала.

3. Схема по п.2, в которой низковольтное напряжение питания для формирования напряжения сигнала схемы управления линии запоминающего конденсатора выше, чем низковольтное напряжение питания для формирования выходного сигнала схемы управления линии сигнала сканирования.

4. Схема по п.1, в которой все транзисторы являются транзисторами полярности р-канала.

5. Схема по п.4, в которой высоковольтное напряжение питания для формирования напряжения сигнала схемы управления линии запоминающего конденсатора ниже, чем высоковольтное напряжение питания для формирования выходного сигнала схемы управления линии сигнала сканирования.

6. Схема по любому из пп.1-5, содержащая каскады, соответствующие каждому из выходных сигналов схемы управления линии сигнала сканирования, причем

каждый из каскадов включает в себя первый переключатель, первую схему памяти, первый переключатель передачи, первый аналоговый переключатель, второй переключатель, вторую схему памяти, второй переключатель передачи и второй аналоговый переключатель,

первый аналоговый переключатель и второй аналоговый переключатель содержатся в выходном каскаде,

первый переключатель предусмотрен между первой схемой памяти и входным зажимом для первого сигнала определения полярности, указывающего полярность напряжения запоминающего конденсатора, первый переключатель открывается и закрывается в соответствии с используемым в качестве сигнала управления одним из выходных сигналов схемы управления линии сигнала сканирования, соответствующей одному из каскадов,

первая схема памяти предназначена для хранения первого сигнала определения полярности, принимаемого через первый переключатель и выводимого в качестве первого сигнала определения полярности первого хранимого сигнала,

причем первый переключатель передачи в качестве первого передаваемого сигнала обеспечивает передачу первого хранимого сигнала, выводимого из первой схемы памяти, в соответствии с синхронизацией по введенному тактовому сигналу;

первый аналоговый переключатель предусмотрен между выходным зажимом для линии запоминающего конденсатора одного из каскадов и высоковольтным напряжением питания запоминающего конденсатора, причем первый аналоговый переключатель открывается и закрывается в соответствии с используемым в качестве сигнала управления первым передаваемым сигналом, являющимся передаваемым от первого переключателя передачи,

второй переключатель предусмотрен между второй схемой памяти и входным зажимом для второго сигнала определения полярности, имеющий полярность, противоположную таковой, для первого сигнала определения полярности, указывающего полярность напряжения запоминающего конденсатора, причем второй переключатель открывается и закрывается в соответствии с используемым в качестве сигнала управления одним из выходных сигналов, являющимся сигналом из схемы управления линии сигнала сканирования, соответствующей одному из каскада,

вторая схема памяти предназначена для хранения второго сигнала определения полярности, принимаемого через второй переключатель и выводимый в качестве второго сигнала определения полярности второго хранимого сигнала,

причем второй переключатель передачи в качестве второго передаваемого сигнала обеспечивает передачу второго хранимого сигнала, выводимого из второй схемы памяти, в соответствии с синхронизацией по введенному тактовому сигналу,

второй аналоговый переключатель предусмотрен между выходным зажимом одного из каскадов и низковольтным питанием напряжения запоминающего конденсатора, причем второй аналоговый переключатель открывается и закрывается в соответствии с используемым в качестве сигнала управления вторым передаваемым сигналом, являющимся передаваемым от второго переключателя передачи,

каждый из первого сигнала обратной полярности, первого хранимого сигнала, первого передаваемого сигнала, второго сигнала обратной полярности, второго хранимого сигнала и второго передаваемого сигнала имеет напряжение, соответствующее напряжению сигнала.

7. Схема по п.6, в которой первым переключателем и вторым переключателем являются транзисторы.

8. Схема по п.6, в которой:

первой схемой памяти является конденсатор, подключенный между (i) выходным зажимом первого переключателя и входным зажимом первого переключателя передачи на одной стороне и (ii) низковольтным источником питания первого хранимого сигнала на другой стороне; и

второй схемой памяти является конденсатор, подключенный между (i) выходным зажимом второго переключателя и входным зажимом второго переключателя передачи на одной стороне и (ii) низковольтным источником питания второго хранимого сигнала на другой стороне.

9. Схема по п.6, в которой первым переключателем передачи и вторым переключателем передачи являются транзисторы, открывающиеся и закрывающиеся в соответствии с тактовым сигналом в качестве сигнала управления.

10. Устройство отображения, содержащее схему управления линии запоминающего конденсатора по любому из пп.1-9.

11. Устройство отображения по п.10, в котором схема управления линии запоминающего конденсатора и схема управления линии сигнала сканирования выполнены в виде прослойки линии сигнала сканирования и отделены друг от друга.

12. Устройство отображения по п.10, в котором и схема управления линии запоминающего конденсатора, и схема управления сигнала сканирования выполнены на одном конце линии сигнала сканирования.

| ЕР 1860639 A1, 28.11.2007 | |||

| Способ резки материала на мерные длины | 1988 |

|

SU1600935A1 |

| US 5337173 А, 09.08.1994 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Способ оптико-электронного контроля поверхностных дефектов и устройство для его осуществления | 1990 |

|

SU1780583A3 |

| ВЫСОКОЭФФЕКТИВНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ С ПАРАЛЛЕЛЬНЫМИ КАСКАДАМИ | 1996 |

|

RU2175809C2 |

| СХЕМА УПРАВЛЕНИЯ ДЛЯ ЭНЕРГОНЕЗАВИСИМОГО ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1998 |

|

RU2221286C2 |

Авторы

Даты

2011-12-27—Публикация

2008-08-21—Подача