Изобретение относится к программируемым элементам памяти, к способам и устройствам для их считывания, записи и программирования.

Известно устройство для программирования постоянных запоминающих устройств (патент РФ №1635207 от 16.01.89 на изобретение «Устройство для программирования запоминающих устройств», МПК: G11C 7/00, Рой Н.Н., Скурихин А.В., Строев А.А., Гришина И.А., опубл. 15.03.91, Бюл. №10), включающее блок управления, регистр старшего байта, регистр хранения, блок памяти протокола обмена, регистр режима, цифроаналоговый преобразователь. Данное устройство позволяет производить запись и контроль различных типов программируемых постоянных запоминающих устройств (ППЗУ) на микроЭВМ.

Наиболее близким по совокупности существенных признаков к предлагаемому изобретению является программатор (патент РФ №2078381 от 16.04.1991 на изобретение «Программатор», МПК: G11C 7/00, Баринов А.Е., Глинкин Е.И., Петров С.В., Власов М.Е., опубл. 27.04.1997), содержащий блок памяти, генератор сигналов записи, блок контроля, формирователь кода адреса, блок управления, блок микропрограммного управления.

Недостаток вышеупомянутых аналогов заключается в возможности непреднамеренной потери информации в блоке памяти вследствие появления ложных управляющих сигналов на выходах блока управления при подаче питающих напряжений.

Технический результат заключается в повышении надежности устройства.

Данный технический результат достигается тем, что в программаторе, содержащем блок управления, блок памяти, новым является то, что дополнительно введены блок регистров и блок защиты от непреднамеренной потери информации, содержащий первый, второй, третий, четвертый и пятый транзисторные ключи, первый, второй, третий, четвертый и пятый резисторы, n-p-n- и p-n-p-транзисторы, стабилитрон, конденсатор, источник ЭДС, триггер Шмидта, вход которого является первым входом блока защиты от непреднамеренной потери информации, а выход соединен с входом первого транзисторного ключа, первый выход которого соединен с первым выходом второго транзисторного ключа, вход которого является вторым входом блока защиты от непреднамеренной потери информации, а второй выход соединен с общей шиной, с которой соединены первый выход источника ЭДС, первые выходы третьего, четвертого и пятого транзисторных ключей, вход третьего транзисторного ключа соединен со вторым выходом первого транзисторного ключа, через первый резистор с коллектором n-p-n-транзистора и с входом четвертого транзисторного ключа, второй выход которого соединен с входом пятого транзисторного ключа, с коллектором n-p-n-транзистора, катодом стабилитрона и первым выводом второго резистора, второй вывод которого соединен с эмиттером p-n-p-транзистора, база которого соединена с анодом стабилитрона и вторым выходом пятого транзисторного ключа, второй выход третьего транзисторного ключа через третий резистор соединен с коллектором p-n-p-транзистора, базой n-p-n-транзистора, вторым выходом источника ЭДС, первым выводом четвертого резистора и через конденсатор с общей шиной, которая через пятый резистор соединена со вторым выводом четвертого резистора и входом источника ЭДС, эмиттер n-p-n-транзистора является выходом блока защиты от непреднамеренной потери информации и соединен с входом блока памяти, группа входов/выходов которого соединена с первой группой входов/выходов блока регистров, вторая группа входов/выходов которого является первой группой входов/выходов программатора, группа входов/выходов блока управления является второй группой входов/выходов программатора, первый и второй входы блока защиты от непреднамеренной потери информации являются первым и вторым входами программатора.

Применение блока защиты, состоящего из транзисторных ключей, источника тока и источника ЭДС, позволяет избежать потери информации, находящейся в блоке памяти, вследствие появления ложных управляющих сигналов на выходах блока управления при подаче питающих напряжений.

Указанная совокупность существенных признаков позволяет достигать заявленный технический результат, т.е. защиту от непреднамеренной потери данных, что повышает надежность устройства.

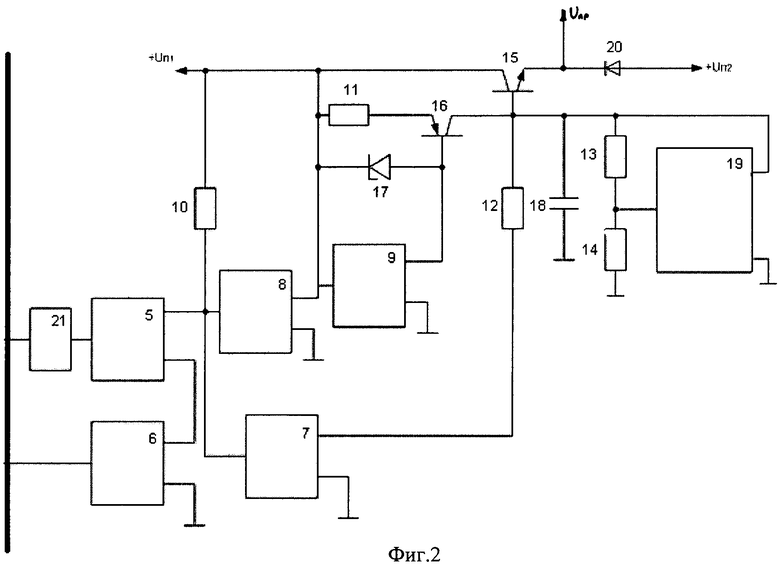

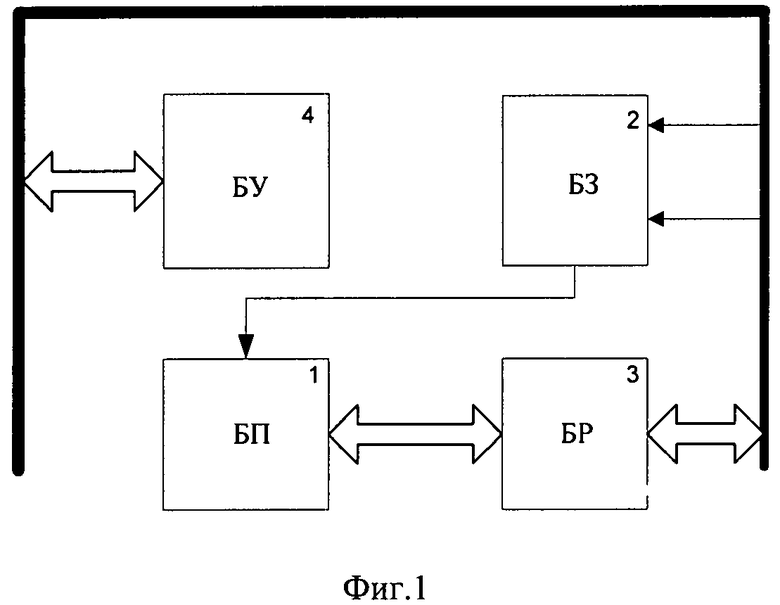

На фиг.1 представлена функциональная схема программатора. На фиг.2 представлена схема блока защиты от непреднамеренной потери информации.

Программатор содержит (фиг.1) блок 1 памяти (БП), блок 2 защиты от непреднамеренной потери информации (БЗ), блок 3 регистров (БР) и блок 4 управления (БУ).

Первый и второй входы блока 2 защиты от непреднамеренной потери информации являются первым и вторым входами программатора. Выход блока 2 защиты от непреднамеренной потери информации соединен с входом блока 1 памяти. Группа входов/выходов блока 1 памяти соединена с первой группой входов/выходов блока 3 регистров, вторая группа входов/выходов которого является первой группой входов/выходов программатора. Группа входов/выходов блока 4 управления является второй группой входов/выходов программатора.

Блок защиты от непреднамеренной потери информации содержит (фиг.2) первый 5, второй 6, третий 7, четвертый 8 и пятый 9 транзисторные ключи, первый 10, второй 11, третий 12, четвертый 13 и пятый 14 резисторы, n-p-n-транзистор 15, p-n-p-транзистор 16, стабилитрон 17, конденсатор 18, источник ЭДС 19, диод 20, триггер Шмидта 21.

Вход триггера Шмидта 21 является первым входом блока защиты от непреднамеренной потери информации. Выход триггера Шмидта 21 соединен с входом первого транзисторного ключа 5. Первый выход первого транзисторного ключа 5 соединен с первым выходом второго транзисторного ключа 6, вход которого является вторым входом блока защиты от непреднамеренной потери информации. Второй выход второго транзисторного ключа 6 соединен с общей шиной, с которой соединены первый выход источника ЭДС 20 и первые выходы третьего 7, четвертого 8 и пятого 9 транзисторных ключей. Вход третьего транзисторного ключа 7 соединен со вторым выходом первого транзисторного ключа 5, через первый резистор 10 с коллектором n-p-n-транзистора 15 и с входом четвертого транзисторного ключа 8. Второй выход четвертого транзисторного ключа 8 соединен с входом пятого транзисторного ключа 9, с катодом стабилитрона 17, первым выводом второго резистора 11 и коллектором n-p-n-транзистора 15. Второй вывод второго резистора 11 соединен с эмиттером p-n-p-транзистора 16, база которого соединена с анодом стабилитрона 17 и со вторым выходом пятого транзисторного ключа 9. Второй выход третьего транзисторного ключа 7 через третий резистор 12 соединен с коллектором p-n-p-транзистора 16, базой n-p-n-транзистора 15, вторым выходом источника ЭДС 19, первым выводом четвертого резистора 13 и через конденсатор 18 с общей шиной. Общая шина через пятый резистор 14 соединена со вторым выводом четвертого резистора 13 и входом источника ЭДС 19. Точка объединения эмиттера n-p-n-транзистора 15 и катода диода 20 является выходом блока защиты от непреднамеренной потери информации. Анод диода 22 и коллектор n-p-n-транзистора 15 являются выводами для подключения источников питания (на фиг.2 не показаны).

Совокупность элементов p-n-p-транзистора 16, второго резистора 11 и стабилитрона 17 образует источник тока.

Для реализации блока управления можно применить микроконтроллер 1886ВЕхх отечественной разработки, в качестве блока памяти - микросхему ЭСППЗУ (электрически перепрограммируемое постоянное запоминающее устройство) 558РТ2А, в блоке регистров применить микросхемы 1554ИР23, для организации транзисторных каскадов блока защиты от непреднамеренной потери информации можно использовать транзисторную матрицу 1НТ251А.

Программатор работает следующим образом.

Работа программатора основывается на совокупности программных и аппаратных средств микропроцессорной системы.

С источника питания поступают напряжения, которые необходимы для функционирования программатора - +5 В для функционирования цифровых интегральных схем и +27 В для формирования напряжения программирования БП 1. Обмен информации между БУ 4 и БП 1 осуществляется через БР 3. Информация, которую необходимо сохранить, и адрес ее расположения в БП 1 записывается в БР 3. БУ 4 формирует управляющие сигналы для БП 1, БР 3 и БЗ 2. Если сигналы управления были сформированы правильно, то БЗ 2 разрешает формирование сигнала напряжения программирования, иначе сигнал напряжения программирования формироваться не будет.

Функционирование БЗ 2 происходит по следующему алгоритму.

БУ 4 формирует сигналы записи/стирания, которые поступают на первый и второй входы БЗ 2. На входах БЗ 2 первый транзисторный ключ 5 в совокупности с триггером Шмидта 21 и вторым транзисторным ключом 6 образуют логическую схему больше или равно (обратная импликация от второго аргумента к первому). Выход первого транзисторного ключа 5 через третий 7, четвертый 8 и пятый 9 транзисторные ключи управляет работой источника тока, который, заряжая конденсатор 18, формирует фронт и срез необходимой длительности сигнала напряжения программирования ЭСППЗУ. Основное назначение БЗ 2 заключается в том, чтобы сформировать сигнал программирования при подаче определенной комбинации управляющих сигналов на его вход.

Изготовлен лабораторный макет программатора, испытания которого подтвердили работоспособность и достижение заявленного технического результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для заряда аккумуляторной батареи транспортного средства | 1986 |

|

SU1427483A1 |

| СИСТЕМА ЗАЖИГАНИЯ | 1996 |

|

RU2129663C1 |

| СИСТЕМА УПРАВЛЕНИЯ РЕЖИМАМИ РАБОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1998 |

|

RU2133549C1 |

| Устройство для управления и защиты преобразователя | 1985 |

|

SU1336171A1 |

| Экстремальный регулятор мощности | 1987 |

|

SU1408435A1 |

| ИСТОЧНИК ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ | 2003 |

|

RU2271598C2 |

| Устройство для управления и защиты преобразователя | 1986 |

|

SU1399866A2 |

| Устройство для автоматического контроля герметичности | 1989 |

|

SU1728697A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИЗОЛЯЦИИ АККУМУЛЯТОРНОЙ БАТАРЕИ ЭЛЕКТРИЧЕСКОГО ТРАНСПОРТА | 1990 |

|

RU2010735C1 |

| Устройство для управления и защиты преобразователя | 1988 |

|

SU1522345A2 |

Изобретение относится к программируемым элементам памяти, к способам и устройствам для их считывания, записи и программирования. Техническим результатом является повышение надежности устройства. Программатор содержит блок регистров, блок памяти, блок управления и блок защиты от непреднамеренной потери информации. Блок защиты от непреднамеренной потери информации содержит пять транзисторных ключей, пять резисторов, n-p-n-транзистор, p-n-p-транзистор, стабилитрон, конденсатор, источник ЭДС, триггер Шмидта. Применение блока защиты от непреднамеренной потери информации позволяет избежать потери информации, находящейся в блоке памяти, вследствие появления ложных управляющих сигналов на выходах блока управления при подаче питающих напряжений, что в свою очередь приводит к повышению надежности программатора. 2 ил.

Программатор, содержащий блок управления, блок памяти, отличающийся тем, что дополнительно введены блок регистров и блок защиты от непреднамеренной потери информации, содержащий первый, второй, третий, четвертый и пятый транзисторные ключи, первый, второй, третий, четвертый и пятый резисторы, n-p-n- и p-n-p-транзисторы, стабилитрон, конденсатор, источник ЭДС, триггер Шмидта, вход которого является первым входом блока защиты от непреднамеренной потери информации, а выход соединен с входом первого транзисторного ключа, первый выход которого соединен с первым выходом второго транзисторного ключа, вход которого является вторым входом блока защиты от непреднамеренной потери информации, а второй выход соединен с общей шиной, с которой соединены первый выход источника ЭДС, первые выходы третьего, четвертого и пятого транзисторных ключей, вход третьего транзисторного ключа соединен со вторым выходом первого транзисторного ключа, через первый резистор с коллектором n-p-n-транзистора и с входом четвертого транзисторного ключа, второй выход которого соединен с входом пятого транзисторного ключа, с коллектором n-p-n-транзистора, катодом стабилитрона и первым выводом второго резистора, второй вывод которого соединен с эмиттером p-n-p-транзистора, база которого соединена с анодом стабилитрона и вторым выходом пятого транзисторного ключа, второй выход третьего транзисторного ключа через третий резистор соединен с коллектором p-n-p-транзистора, базой n-p-n-транзистора, вторым выходом источника ЭДС, первым выводом четвертого резистора и через конденсатор с общей шиной, которая через пятый резистор соединена со вторым выводом четвертого резистора и входом источника ЭДС, эмиттер n-p-n-транзистора является выходом блока защиты от непреднамеренной потери информации и соединен с входом блока памяти, группа входов/выходов которого соединена с первой группой входов/выходов блока регистров, вторая группа входов/выходов которого является первой группой входов/выходов программатора, группа входов/выходов блока управления является второй группой входов/выходов программатора, первый и второй входы блока защиты от непреднамеренной потери информации являются первым и вторым входами программатора.

| ПРОГРАММАТОР | 1991 |

|

RU2078381C1 |

| Программатор | 1986 |

|

SU1439677A1 |

| Программатор для записи информации в полупроводниковые элементы памяти | 1985 |

|

SU1280449A2 |

| US 7301812 B2, 27.11.2007. | |||

Авторы

Даты

2012-12-20—Публикация

2011-08-11—Подача