Изобретение относится к электротехнике и может быть использовано для управления асинхронными двигателями общепромышленного применения.

Известна система управления электродвигателем (GB, 2165408A, МПК H 02 P 1/26,1986 г.).

В качестве прототипа предлагается устройство для фазового управления электродвигателем, содержащая фазосдвигающее устройство, распределитель импульсов, узел синхронизации, блок временной задержки и усилитель импульсов (СССР, 754620, МПК H 02 P 1/26,1976 г.). К недостаткам прототипа можно отнести то, что это устройство не обеспечивает управление силовыми коммутаторами при режимах комбинированного торможения, реверса и повторного включения с определенными характеристиками переходных процессов при использовании нерегулируемого асинхронного привода.

Целью изобретения является реализация режимов комбинированного торможения, реверса и повторного включения с определенными характеристиками переходных процессов при использовании нерегулируемого асинхронного привода.

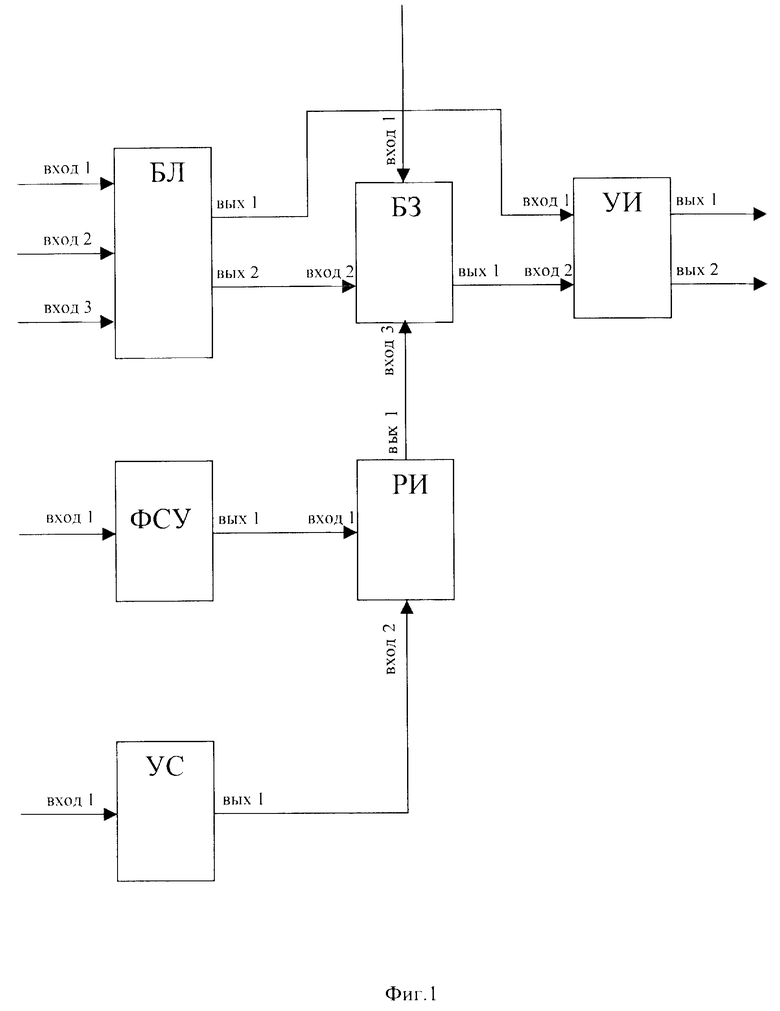

Указанный технический результат достигается тем, что система управления режимами работы асинхронного двигателя, содержащая фазосдвигающее устройство, распределитель импульсов, узел синхронизации, блок временной задержки и усилитель импульсов, снабжена блоком логики, при этом первый выход блока логики соединен с первым входом усилителя импульсов, второй выход блока логики соединен со вторым входом блока временной задержки, выход которого соединен со вторым входом усилителя импульсов, выход фазосдвигающего устройства соединен с первым входом распределителя импульсов, выход узла синхронизации соединен со вторым входом распределителя импульсов, выход которого соединен с третьим входом блока временной задержки, усилитель импульсов имеет два выхода, каждый из которых соединен со своей группой оптосимисторов.

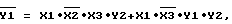

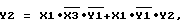

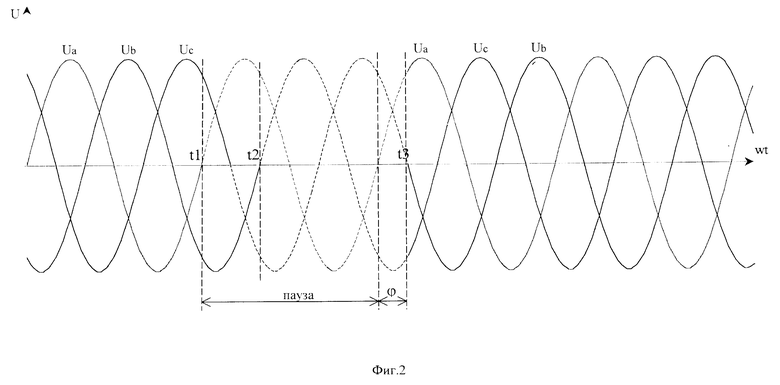

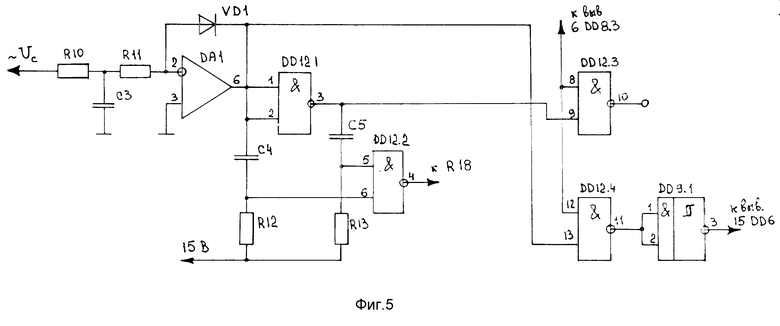

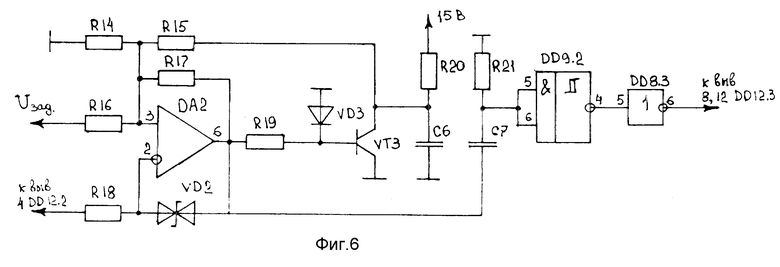

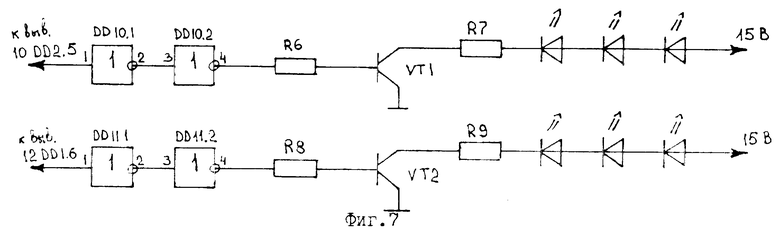

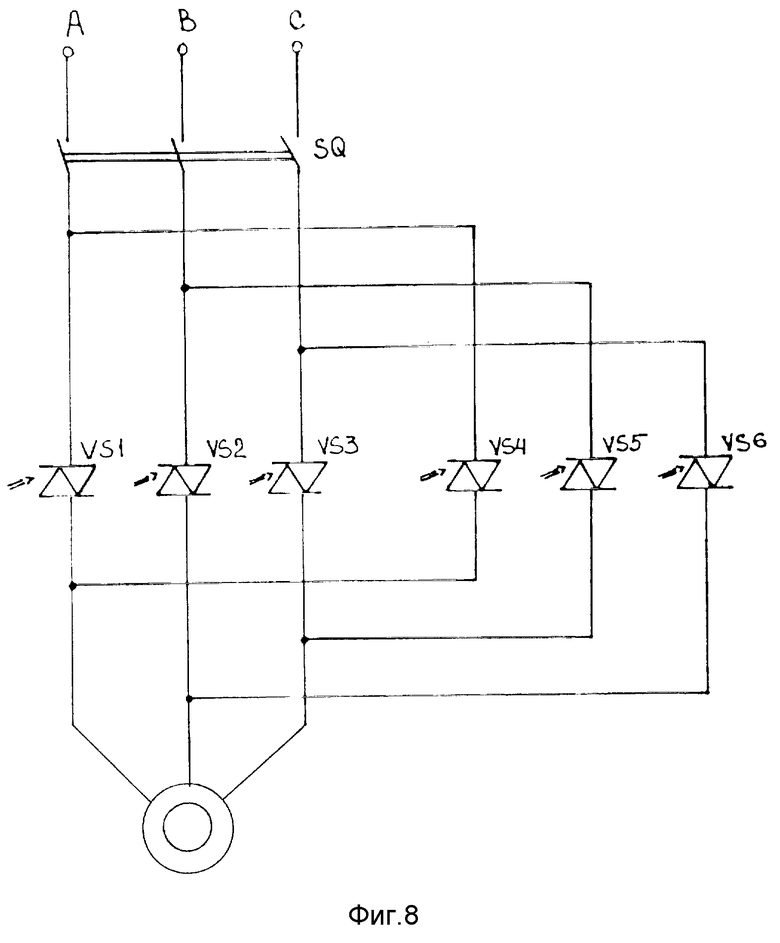

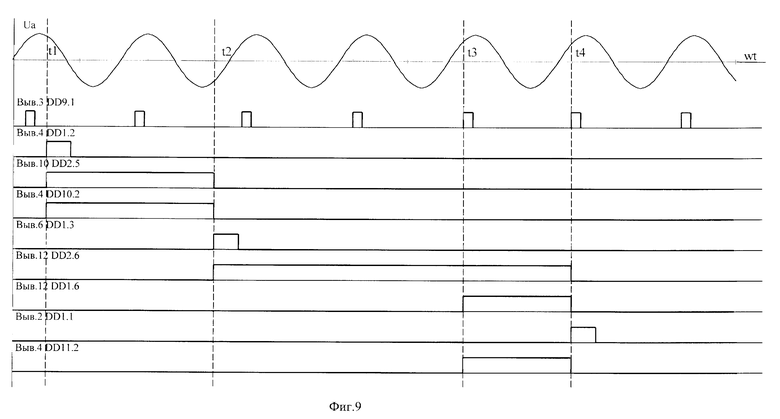

Изобретение поясняется фиг. 1 - 9, где на фиг. 1 - функциональная схема системы управления; на фиг.2 изображен график, поясняющий назначение системы управления; на фиг.3 - принципиальная электрическая схема блока логики; на фиг. 4 - принципиальная схема блока временной задержки; на фиг.5 - принципиальная схема узла синхронизации и распределителя импульсов; на фиг.6 -принципиальная схема фазосдвигающего устройства; на фиг.7 - принципиальная схема усилителя импульсов; на фиг.8 - силовая часть электрической схемы системы управления; на фиг.9 - временные диаграммы работы блока логики, блока временной задержки и усилителя импульсов.

Система управления режимами работы асинхронного двигателя (АД) содержит блок логики (БЛ), блок временной задержки (БЗ), усилитель импульсов (УИ), фазосдвигающее устройство (ФСУ), распределитель импульсов (РИ) и синхронизирующее устройство (УС).

Первый выход БЛ соединен с первым входом УИ. Второй выход БЛ соединен со вторым входом БЗ, выход которого соединен со вторым входом УИ. Выход ФСУ соединен с первым входом РИ, выход УС соединен со вторым входом РИ. Выход РИ соединен с третьим входом Б3. УИ имеет два выхода, первый выход соединен с группой оптосимисторов VS1, VS2, VS3 "Режим 1" работы АД, второй выход соединен с группой оптосимисторов VS4, VS5, VS6 "Режим 2" работы АД.

Работа системы управления режимами работы асинхронного двигателя заключается в следующем.

В исходном состоянии к оптосимисторам не поступает сигнал, АД не работает. На вход ФСУ устанавливается Uзад, соответствующее фазовому углу напряжения контролируемой фазы, при котором произойдет переключение АД из "Режима 1 " в "Режим 2". На вход УС поступает сигнал контролируемой фазы напряжения статора. На вход 1 БЗ перемычкой устанавливается число периодов задержки при переключении АД из "Режима 1" в "Режим 2". При поступлении на вход 1 БЛ сигнала "Режим 1" с выхода 1 БЛ он проходит на вход 1 УИ, с выхода 1 УИ выдается сигнал на оптосимисторы группы "Режим 1 ", они открываются, на АД поступает питающее напряжение, и АД начинает работать, осуществляя "Режим 1 ".

При поступлении на вход 2 БЛ сигнала "Режим 2" происходит снятие сигнала "Режим 1 ", соответственно закрываются оптосимисторы группы "Режим 1 ", и АД отключается от сети питающего напряжения. Одновременно с выхода 2 БЛ сигнал "Режим 2" проходит на вход 2 БЗ. На вход 3 БЗ поступают сигналы с выхода 1 РИ, которые проходят с интервалом в один период сети сдвинутые по фазе на величину фазового угла, определенного величиной Uзад на входе 1 ФСУ. На входе 1 БЗ перемычкой устанавливается число периодов задержки. При отсчете установленного числа периодов задержки с выхода 1 БЗ поступает сигнал "Режим 2" на вход 2 УИ, с выхода 2 УИ выдается сигнал на оптосимисторы группы "Режим 2", сдвинутый на установленный фазовый угол относительно контролируемой фазы напряжения статора АД. Оптосимисторы группы "Режим 2" открываются, и на АД поступает питающее напряжение через заданное число периодов паузы и в определенный момент контролируемой фазы напряжения статора, АД начинает работать, осуществляя "Режим 2".

При поступлении на вход 3 БЛ сигнала "Стоп" снимаются сигналы "Режим 1" или "Режим 2", группы оптосимисторов "Режим 1" или "Режим 2" закрываются, и АД не получает питание, т.е. находится в отключенном состоянии.

ФСУ, УС и РИ работают постоянно при подаче питания на систему управления режимами работы АД и наличии сигналов Uзад, Uсети.

Схема БЛ не позволяет переходить с "Режима 2" в "Режим 1 ", непосредственно минуя сигнал "Стоп". После сигнала "Стоп" возможно осуществить сразу "Режим 2".

Гальваническая развязка системы управления режимами работы АД с силовой частью схемы выполнена на оптосимисторах, что позволяет отказаться от разделительных импульсных трансформаторов и упростить схему усилителей импульсов, т. к. светодиоды оптосимисторов потребляют от 50 до 100 мА, и можно использовать транзисторные ключи средней мощности.

Наглядная картина работы системы управления режимами работы АД показана на фиг.2, для чтения которой даются следующие пояснения :

1) Ua - напряжение фазы A статора (контролируемая фаза);

2) Ub - напряжение фазы B;

3) Uc - напряжение фазы C;

4) в промежутке времени от 0 до t1 АД работает в "Режиме 1" (двигательный режим);

5) в момент времени t1 произведено отключение "Режима 1" (двигательного режима);

6) в промежутке времени от t1 до t2 происходит закрытие оптосимисторов группы "Режим 1";

7) в момент времени t3 производится включение АД на "Режим 2" (режим противовключения). Включение на "Режим 2" произведено с паузой в n-периодов (в данном случае один период) в заданный угол ϕ контролируемой фазы A напряжения статора;

8) "Режим 2", противовключение осуществляется путем переброса фаз B и C напряжения статора АД.

Описание работы системы управления режимами работы асинхронного двигателя.

Принципиальная схема системы управления режимами работы АД приведена на фиг. 3, 4, 5, 6, 7, 8. Работа блоков системы управления режимами работы АД заключается в следующем.

Блок логики работает следующим образом (см. фиг. 3).

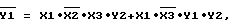

Сигналы "Стоп", "Режим 1", "Режим 2" поступают с микропереключателей S1, S2, S3, формируя логический уровень "0" или "1" на элементы ИЛИ-НЕ DD1.1, DD1.2, DD1.3, которые служат для получения прямых и инверсных сигналов "Стоп", "Режим 1", "Режим 2". Элементы 4ИЛИ-НЕ DD3.1, DD3.2, DD7.1, DD7.2, ИЛИ-НЕ DD2.1, DD2.2, DD2.3, DD2.4, DD2.5, DD2.6, 2ИЛИ-НЕ DD4.1, DD4.2 обеспечивают реализацию логических выражений

где X1 соответствует сигналу "Стоп" логического уровня "1" на входе 1 DD1.1; соответствует сигналу "Стоп" логического уровня "0" на выходе 2 DD1.1;

соответствует сигналу "Стоп" логического уровня "0" на выходе 2 DD1.1;

X2 соответствует сигналу "Режим 1" логического уровня "1" на входе 3 DD1.2; соответствует сигналу "Режим 1" логического уровня "0" на выходе 4 DD1.2,

соответствует сигналу "Режим 1" логического уровня "0" на выходе 4 DD1.2,

Х3 соответствует сигналу "Режим 2" логического уровня "1" на входе 5 DD1.3; соответствует сигналу "Режим 2" логического уровня "1" на выходе 6 DD1.3;

соответствует сигналу "Режим 2" логического уровня "1" на выходе 6 DD1.3;

Y1 соответствует сигналу логического уровня "1" на выходе 10 DD2.5; соответствует сигналу логического уровня "1 "на входе 11 DD2.5;

соответствует сигналу логического уровня "1 "на входе 11 DD2.5;

Y2 соответствует сигналу логического уровня "1" на выходе 12 DD2.6; соответствует сигналу логического уровня "1" на входе 13 DD2.6.

соответствует сигналу логического уровня "1" на входе 13 DD2.6.

При этом сигналы с вывода 10 DD2.5 Y1 и с вывода 12 DD2.6 Y2 являются промежуточными сигналами сигналов "Режим 1 " и "Режим 2" соответственно. Схема БЛ исключает одновременное появление сигналов логического уровня "1" Y1 и Y2. При появлении сигнала "Стоп" логического уровня "0" при любом состоянии схемы БЛ переводит Y1 и Y2 на логический уровень "0". При появлении сигнала Y1 логического уровня "1" на выводе 10 DD2.5 он поступает на вывод 1 DD10.1 УИ. При появлении сигнала Y2 логического уровня "1" на выводе 12 DD2.6 он поступает на интегрирующую цепочку R4 С1, исключающую помеху при переключении, сигнал с интегрирующей цепочки поступает на БЗ вывод 1 DD5.1. При подаче сигнала "Режим 2" на микровыключателе S3 логического уровня "0" он поступает на вход 5 DD1.3, на выводе 6 DD1.3 устанавливается логический уровень "1", этот сигнал поступает на дифференцирующую цепочку С2 R5, с нее сигнал поступает на элемент ИЛИ-НЕ, вывод 11 DD8.5, проинвертированный сигнал поступает на триггер Шмидта, выводы 8,9 DD9.3, с вывода 10DD9.3 снимается стробирующий импульс со сформированными фронтами и поступает в БЗ на вывод 9 DD6 и происходит инициализация счетчика.

Блок задержки работает следующим образом (см. фиг.4).

БЗ состоит из двоичного счетчика, выполненного на элементе DD6, настроенного на сложение (на выводе 10 присутствует логический уровень "1"), в разряды записи информации выводы 4, 12, 13, 3 подается логический уровень "0". На счетный вход, вывод 15 DD6, подаются импульсы с РИ, вывод 3 DD9.1, которые сдвинуты по фазе в соответствии с Uзад на ФСУ. При подаче сигнала "Режим 2" логический "0" на микропереключателе S3 с вывода 10 DD9.3 поступает стробирующий импульс, логический уровень "1", на вывод 9 DD6 инициализации счетчика, счетчик обнуляется на выводах 6, 11, 14, 2 DD6, логический уровень "0"; поступающие счетные импульсы на вывод 15 DD6 приводят к появлению логического уровня "1" на выводах 6, 11, 12, 2 через определенное количество счетных импульсов. Счетные импульсы появляются через один период напряжения сети и имеют заданный сдвиг по фазе относительно контролируемой фазы напряжения статора.

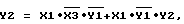

Элементы 2И-НЕ DD5.1, DD5.2, ИЛИ-НЕ DD1.4, DD1.5, DD1.6, 2ИЛИ-НЕ DD4.3 реализуют логическое выражение

Y3=Y2•X4+X1•Y3,

где Х4 соответствует сигналу логического уровня "1" с вывода 6, 11, 12, 2 DD6;

Y3 - соответствует сигналу логического уровня "1" с вывода 12 DD1.6.

Сигнал Y3 логического уровня "1" появляется после появления сигнала "Режим 2" логического уровня "0" на микропереключателе S3 через n-периодов задержки и сдвинут по фазе относительно напряжения контролируемой фазы. Число периодов задержки определяется перемычкой, соединяющей вывод 2 DD5.1 с одним из выводов DD6 11, или 14, или 2 (эта перемычка соответствует входу 1 блока задержки на функциональной схеме фиг. 1). Сигнал Y3 с вывода 12 DD1.6 устанавливается в логический "0" при появлении на выводе DD5.2 сигнала "Стоп" логического уровня "0", который приходит с микропереключателя S1. Сигнал Y3 с вывода 12 DD1.6 поступает на УИ вывод 1 DD11.1.

Усилитель импульсов работает следующим образом (см. фиг.7).

Усилитель импульсов состоит из входных инверторов ИЛИ-НЕ DD10.1, DD10.2, DD11.1, DD11.2. Дополнительное двойное инвертирование сигналов Y1 с вывода 10 DD2.5 и Y3 с вывода 12 DD1.6 обеспечивает защиту микросхем БЛ и БЗ. Сигналы с выводов 4 DD10.2 и 4 DD11.2 поступают на транзисторы VT1 и VT2, работающие в ключевом режиме. В цепи транзисторных ключей включены излучающие диоды оптосимисторов.

При подаче сигнала "Режим 1" на вывод 1 DD10.1 поступает сигнал Y1 логического уровня "1"; на базу транзистора VT1 поступает логическая "1"; VT1 открывается, и светоизлучающие диоды открывают оптосимисторы группы "Режим 1 " VS1, VS2, VS3. При появлении логического уровня "0" на выводе 1 DD10.1 транзисторный ключ на VT1 закрывается, а следовательно, закрываются оптосимисторы VS1, VS2, VS3.

Аналогично при подаче сигнала "Режим 2" на вывод 1 DD11.1 поступает сигнал Y3 логического уровня "1"; на базу VT2 поступает логическая "1", VT2 открывается, и светоизлучающие диоды открывают оптосимисторы группы "Режим 2" VS4, VS5, VS6. При появлении логического уровня "0" на выводе 1 DD11.1 транзисторный ключ на VT2 закрывается, а следовательно, закрываются оптосимисторы VS4, VS5, VS6.

Фазосдвигающее устройство работает следующим образом (см. фиг.6).

Синхронизирующие импульсы поступают от УС через резистор R18 на инвертирующий вход усилителя DA2, из-за чего на выходе устанавливается отрицательное напряжение, приблизительно равное напряжению пробоя стабилитрона VD2. При этом транзисторный ключ VT3 закрывается, и через сопротивление R36 начинается заряд конденсатора С6. Таким образом формируется пилообразное напряжение, скорость нарастания которого, а значит, и максимальный угол управления α max (т.е. угол управления при Uвх = 0) устанавливаются подбором резистора R20. При настройке устанавливается α max = 150 - 160 эл. град.

Пилообразное напряжение вместе с входным напряжением Uзад и напряжением положительной обратной связи суммируются на неинвертирующем входе DA2. Когда эта сумма превысит напряжение на инвертирующем входе, на выходе компоратора DA2 устанавливается положительное напряжение, которое удерживается за счет положительной обратной связи. Величина этого напряжения определяется напряжением пробоя стабилитрона VD2 и достаточна для открывания транзисторного ключа VT3. При этом конденсатор С6 заряжается. По переднему фронту выходного напряжения компаратора DA2 дифференцирующей цепочкой С7, R21 формируется импульс управления, поступающий на РИ. С приходом следующего синхронизирующего импульса весь процесс повторяется.

При большем напряжении Uзад необходима меньшая амплитуда пилообразного напряжения для срабатывания компаратора, переключение происходит раньше, т. е. угол управления меньше. И наоборот, если Uзад мало, то для срабатывания компаратора необходимо большее пилообразное напряжение, переключение происходит позже, т. е. угол управления увеличивается. Таким образом, изменение Uзад вызывает соответствующий сдвиг угла управления.

Устройство синхронизации работает следующим образом (см. фиг.5).

Синусоидальное напряжение синхронизации поступает на сглаживающий фильтр R10, С3. Такой фильтр, внося небольшой фазовый сдвиг (примерно 15 эл.град.), хорошо предохраняет от возможных импульсных помех питающей сети. Отфильтрованное сетевое напряжение поступает на компаратор, выполненный на операционном усилителе DA1, который формирует из синусоиды прямоугольное напряжение. Это, а также инвертированное инвертором DD12.1 напряжение используется распределителем импульсов РИ. Прямоугольные импульсы поступают на дифференцирующие цепочки C4-R12 и C5-R13. На выходах элемента И-НЕ DD12.2 с помощью резисторов R12, R13 создается логический уровень "1", в следствие чего на выходе 4 DD12.2 устанавливается логический уровень "0". С выходов дифференцирующих цепочек C4-R12 и C5-R13 на входы 5, 6 DD12.2 поступают отрицательные импульсы во время прохождения задних фронтов прямоугольных импульсов. Эти отрицательные импульсы, суммируясь с положительным напряжением смещения на входах DD12.2, приводят к появлению кратковременных уровней логического "0" поочередно на каждом входе DD12.2. Появление логического "0" на входе вызывает появление логического уровня "1" на выходы 4 DD12.2. Сигналы с вывода 4 DD12.2 являются синхронизирующими импульсами, которые подаются на R18 ФСУ.

Распределитель импульсов работает следующим образом (см. фиг.5).

РИ состоит из элементов И-НЕ DD12.3, DD12.4 и триггера Шмидта DD9.1. На вход 9 DD12.3 и вход 13 DD12.4 с УС подаются прямоугольные импульсы в противофазе. На вход 8 DD12.3 и 12 DD12.4 поступают управляющие импульсы с вывода 6 DD8.3 ФСУ логического уровня "1" каждые полпериода напряжения сети. В момент, когда на входы DD12.3 и DD12.4 приходят сигналы логического уровня "1", на выходах 10 DD12.3 и 11 DD12.4 появляются сигналы логического уровня "0", сдвинутые на угол α в соответствии с Uзад. При этом с вывода 10 элемента DD12.3 получаем сигнал от 0 до 180 эл.град., а с вывода 11 DD12.4 получаем сигнал от 180 до 360 эл.град. напряжения сети. Триггер Шмидта DD9.1 используется для инвертирования сигнала, получаемого с выводов 10 DD12.3 или 11 DD12.4, и формирования фронтов импульсов.

На временной диаграмме, поясняющей работу системы управления режимами работы асинхронного двигателя фиг.9, на шкале времени обозначены следующие моменты времени и временные интервалы: от 0 до t1 схема находится в исходном состоянии; в момент времени t1 подается сигнал "Режим 1" (например, АД начинает работать в двигательном режиме); от t1 до t2 осуществляется работа АД "Режим 1 ", работает группа оптосимисторов VS1, VS2, VS3; в момент времени t2 подается сигнал "Режим 2" (например, торможение противовключением), отключаются оптосимисторы группы "Режим 1", обнуляется счетчик Б3; от t2 до t3 происходит счет периодов паузы; в момент времени t3 включаются оптосимисторы группы "Режим 2"; от t3 до t4 осуществляется работа АД "Режим 2" (например, торможение противовключением); в момент времени t4 поступает сигнал "Стоп", отключаются оптосимисторы группы "Режим 2"; после t4 система управления режимами работы АД находится в исходном состоянии.

Данную систему управления режимами работы асинхронного двигателя целесообразно применять в следующих случаях:

1) в системах, использующих нерегулируемый асинхронный привод требующих определенные характеристики переходных процессов при переводе АД из работы в "Режиме 1 " в "Режим 2", при этом под определением "Режим 1 " и "Режим 2" понимаются следующие режимы работы АД - двигательный, противовключение, торможение противовключением, торможение коротким замыканием фаз статора, конденсаторное торможение, динамическое торможение;

2) в механизмах с асинхронным нерегулируемым приводом, когда технологический процесс требует некоторой точности позиционирования (управление осуществляется по путевым датчикам), в этом случае система управления режимами работы асинхронного двигателя осуществляет переход от двигательного режима к тормозному (примером такого механизма может служить кормораздатчик);

3) при переходе АД из "Режима 1 " в "Режим 2" после окончания "Режима 1 " имеет некоторый запас электромагнитной энергии, которая затухает в течение некоторого времени. При незатухшем электромагнитном поле АД перевод двигателя в "Режим 2" характеризуется бросками электромагнитного момента развиваемого двигателем и соответственно бросками тока фаз статора. Величина этих бросков зависит от величины запасенной АД электромагнитной энергии и фазового угла, при котором начинается "Режим 2". В механизмах с асинхронным нерегулируемым приводом, где необходимо избежать бросков момента на валу АД в момент переключения с "Режима 1 " на "Режим 2", данная система управления осуществит необходимую временную задержку (например, работа АД на редуктор или коробку передач). Если технология работы не позволяет выдержать паузу или, наоборот, требует быстродействия, тогда при минимальной паузе в 1 период питающей сети путем установления определенной величины фазового угла, при котором начинается "Режим 2", возможно влиять на характер переходного процесса, контролируя величину броска момента и токов фаз статора. Например, при аварийной остановке механизма необходим максимальный бросок момента, а при запланированной остановке можно получить бросок момента определенной величины в интервале от минимального до максимального.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования переменного напряжения | 1986 |

|

SU1415370A1 |

| Устройство для управления мостовым преобразователем с двухкратным включением вентилей | 1981 |

|

SU1020959A1 |

| Регулятор переменного напряжения | 2024 |

|

RU2832860C1 |

| Двухзонный непосредственный преобразователь частоты и числа фаз в режиме источника тока | 1982 |

|

SU1137558A1 |

| Регулятор переменного напряжения | 2024 |

|

RU2826380C1 |

| Регулятор переменного напряжения | 2024 |

|

RU2834290C1 |

| СПОСОБ ПЛАВНОГО ПУСКА И ОСТАНОВА ЭЛЕКТРОДВИГАТЕЛЯ НАСОСА | 2016 |

|

RU2624305C1 |

| Устройство для торможения асинхронного электродвигателя | 1984 |

|

SU1246310A1 |

| Фотоэлектрическая система | 1991 |

|

SU1814181A1 |

| Устройство для компенсации реактивной мощности | 1987 |

|

SU1520627A1 |

Изобретение относится к электротехнике. Система содержит блок логики (БЛ), блок временной задержки (БЗ), усилитель импульсов (УИ), фазосдвигающее устройство (ФСУ), распределитель импульсов (РИ) и синхронизирующее устройство (УС). Первый выход БЛ соединен с первым входом УИ. Второй выход БЛ соединен со вторым входом БЗ, выход которого соединен со вторым входом УИ. Выход ФСУ соединен с первым входом РИ, выход УС соединен со вторым входом РИ. Выход РИ соединен с третьим входом БЗ. УИ имеет два выхода, первый выход соединен с группой оптосимисторов "Режим 1" работы АД, второй выход соединен с группой оптосимисторов "Режим 2" работы АД. Техническим результатом является реализация режимов комбинированного торможения, реверса и повторного включения с определенными характеристиками переходных процессов при использовании нерегулируемого асинхронного привода. 9 ил.

Система управления режимами работы асинхронного двигателя, содержащая фазосдвигающее устройство, устройство синхронизации, распределитель импульсов, блок временной задержки и усилитель импульсов, отличающаяся тем, что она снабжена блоком логики, обеспечивающим реализацию логических выражений

где X1 соответствует сигналу "Стоп";

Х2 соответствует сигналу "Режим 1";

Х3 соответствует сигналу "Режим 2";

Y1 соответствует сигналу на первом выходе блока логики;

Y2 соответствует сигналу на втором выходе блока логики,

при этом первый выход блока логики соединен с первым входом усилителя импульсов, второй выход блока логики соединен со вторым входом блока временной задержки, выход которого соединен со вторым входом усилителя импульсов, выход фазосдвигающего устройства соединен с первым входом распределителя импульсов, выход узла синхронизации соединен со вторым входом распределителя импульсов, выход которого соединен с третьим входом блока временной задержки, усилитель импульсов имеет два выхода, каждый из которых соединен со своей группой оптосимисторов.

| SU 754620 A, 22.04.76 | |||

| Устройство для цифрового управления асинхронным двигателем | 1974 |

|

SU688974A1 |

| Устройство для управления асинхронным трехфазным электродвигателем | 1987 |

|

SU1534709A1 |

| Устройство для управления тиристорным коммутатором асинхронного трехфазного электродвигателя | 1977 |

|

SU657552A1 |

| СИНТЕТИЧЕСКИЕ СЛОЖНЫЕ ЭФИРЫ СМЕСЕЙ ЖИРНЫХ КИСЛОТ И СПИРТОВ ДЛЯ ПОЛУЧЕНИЯ ГИДРАВЛИЧЕСКОГО МАСЛА И ГИДРАВЛИЧЕСКОЕ МАСЛО НА ИХ ОСНОВЕ | 1995 |

|

RU2165408C2 |

Авторы

Даты

1999-07-20—Публикация

1998-02-11—Подача