W СО

&

фуе.1

Изобретение относится к вычиспи- телыюй технике и может быть исноль- зоиано при нрограммированип микросхем постоянной памяти.

Целью изобретения является расширение области применения за счет обепечения возможности программирования roiM при упрощении устройства и повышении точности контроля качества программирования.

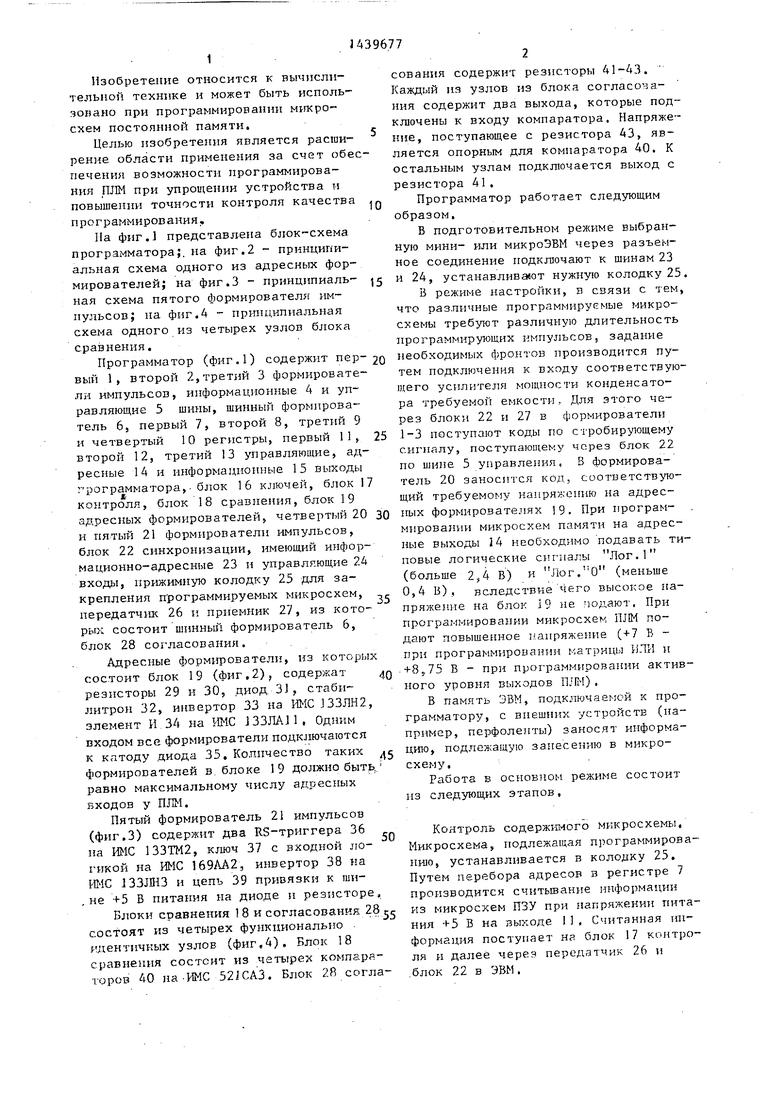

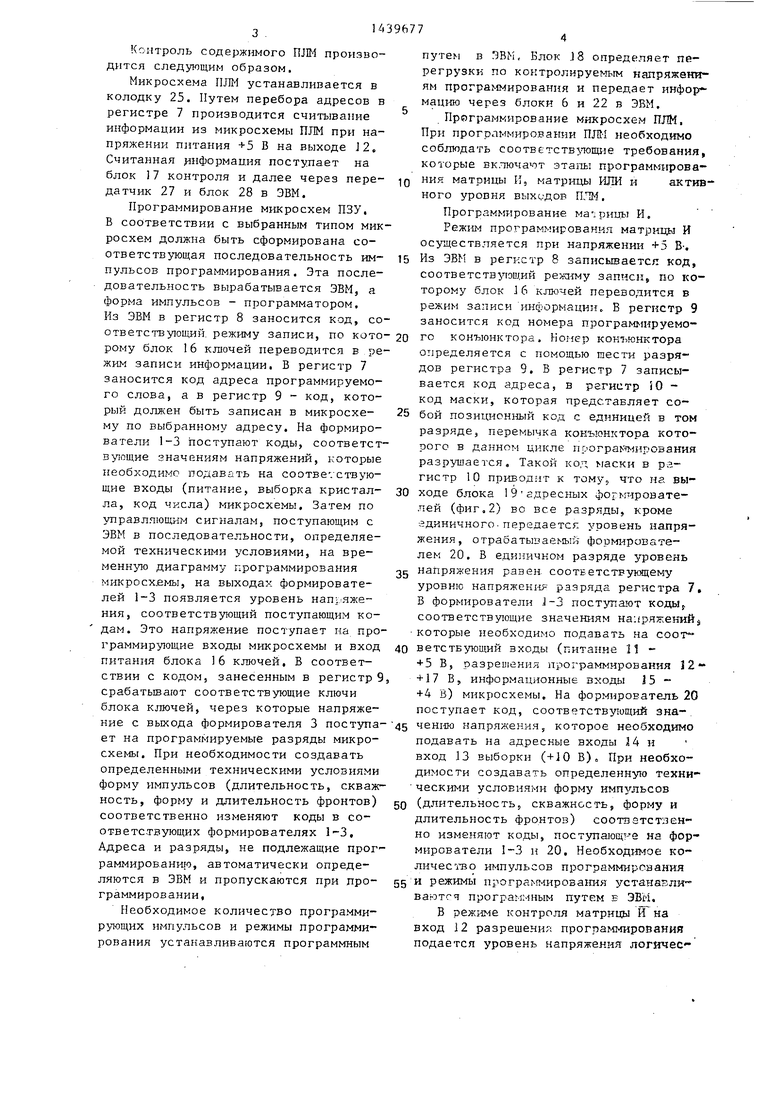

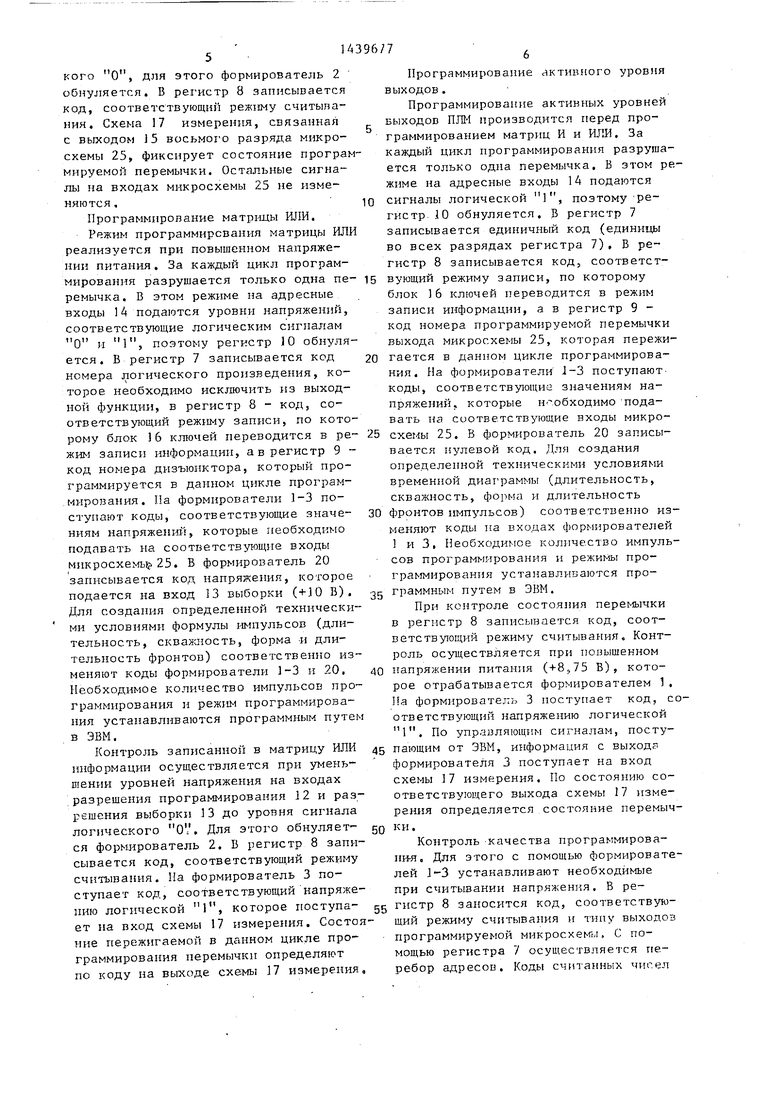

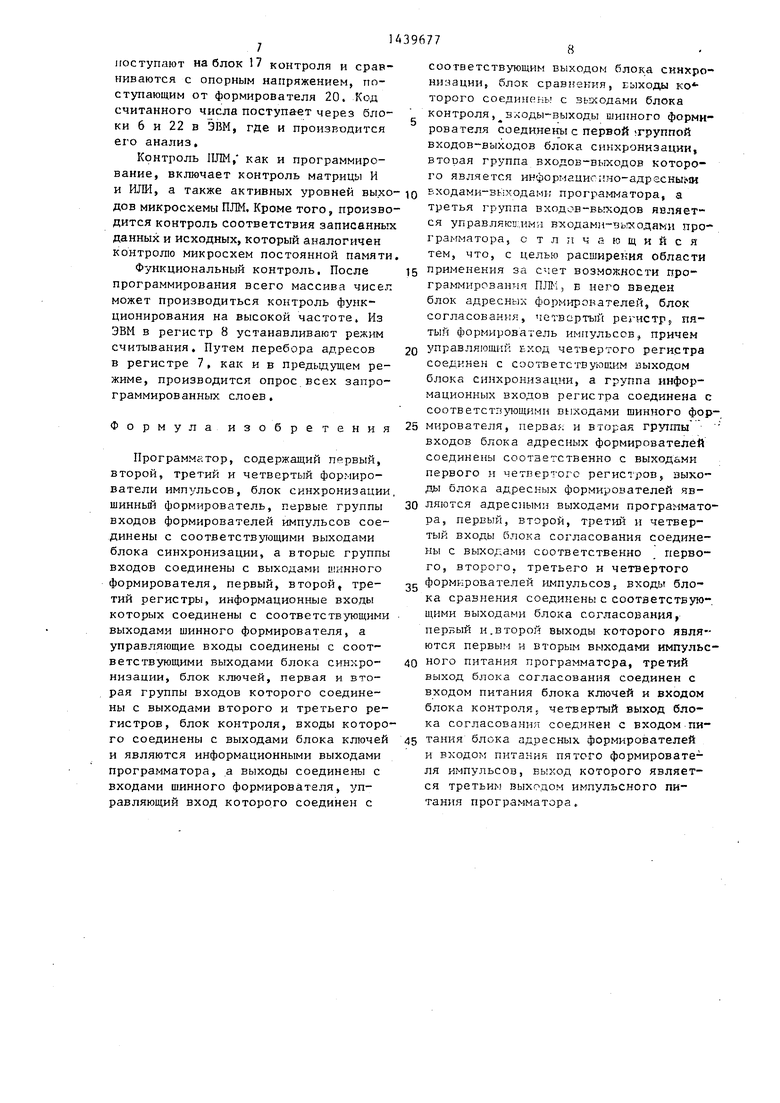

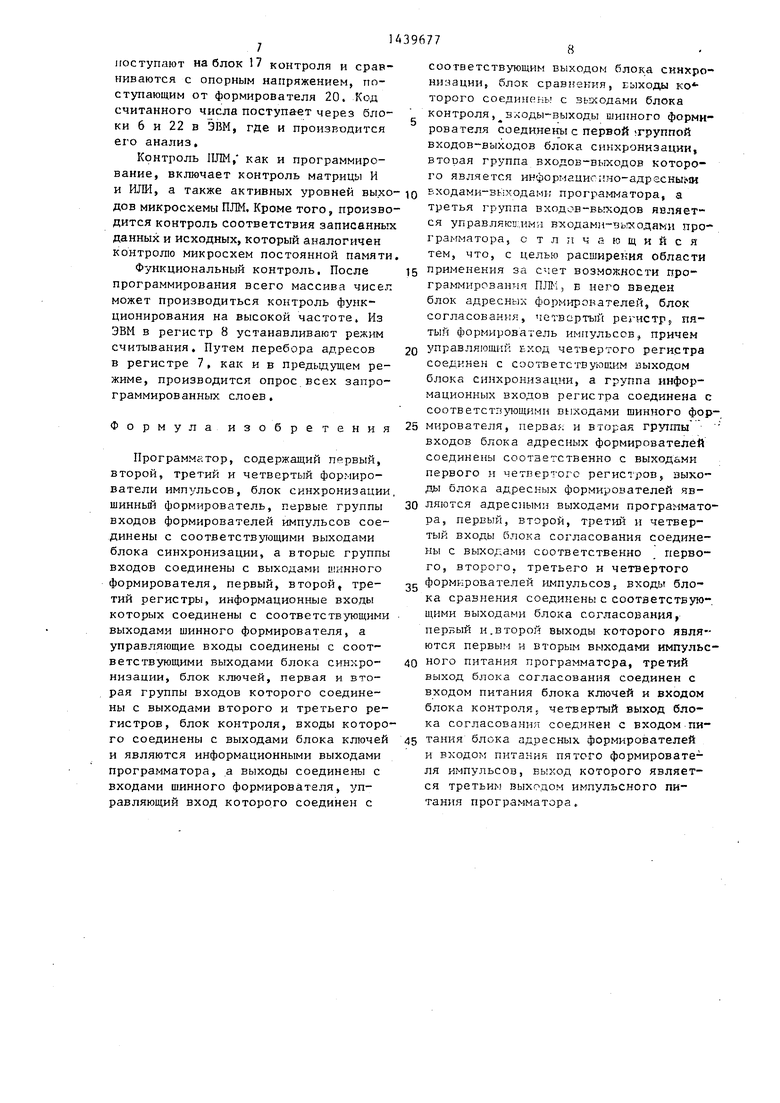

Па фиг.1 представлена блок-схема программатора;, на фиг.2 - принципиальная схема одного из адресных формирователей; на фиг.З - принципиаль- ная схема пятого формирователя импульсов; на фиг.4 - принципиальная схема одного из четырех узлов блока epaia нения.

0

сования содержит резисторы 41-43. Каждый из узлов из блока согласования содержит два выхода, которые подключены к входу компаратора. Напряжение, поступающее с резистора 43, является опорным для компаратора 40. К остальным узлам подключается выход с резистора 41.

Программатор работает следующим образом.

В подготовительном режиме выбранную мини- или микроэвм через разъемное соединение подключают к шинам 23 и 24, устанавливавот нужную колодку 25.

В режиме настройки, в связи с тем, что разл1 чные программируемые микросхемы требуют различную длительность программирующих импульсов, задание

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программирования микросхем памяти | 1986 |

|

SU1381592A1 |

| Устройство для программирования микросхем постоянной памяти | 1985 |

|

SU1285535A1 |

| Программатор | 1987 |

|

SU1541669A1 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Программатор | 1987 |

|

SU1654869A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1985 |

|

SU1297118A1 |

| Устройство для программирования ПЗУ | 1988 |

|

SU1571677A1 |

| ПРОГРАММАТОР | 1991 |

|

RU2078381C1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| Программируемое постоянное запоминающее устройство | 1984 |

|

SU1300563A1 |

Изобретение относится к вычислительной технике и может быть использовано при програ тмированик микросхем постоянной памяти. Целью изобретения является расширение области пр1- менення за счет обеспечения возможности программирования 1Ш1 при упрощении устройства и повышении точности контроля качества программиро- вания. Поставленная цель достигается за счет введения блока 9 адресиь Х формирователей, блока 28 согласования, четвертого iO регистра и пятого 2 формирователя импульсов, 4 вл.

Программатор (фиг.1) содержит пер-20 необходимых фронтов производится пувый 1, второй 2,третий 3 формировате ли импульсов, информационные 4 и управляющие 5 шины, шинный формирователь 6, первый 7, второй 8, третий 9 и четвертый 10 регистры, первый 11, второй 12, третий 13 управляющие, адресные 14 и информационные 15 выходы грограмматора,- блок 16 ключей, блок 17 контроля, блок 18 сравнения, блок 19

тем подключения к входу соответствующего усилителя МО1ЦНОСТИ конденсатора требуемой емкости. Для этого через блоки 22 и 27 в формирователи 25 1-3 поступают коды по стробирующему сигналу, поступающему через блок 22 по шипе 5 управления, В формирователь 20 заносится код, соответств то- щий требуемому напряжению на адресадресных формирователей, четвертый 20 30 1 ых формирователях 19. При нрограм- и нятый 21 формирователи импульсов, блок 22 синхронизации, имеющий информационно-адресные 23 и управляющие 24 входы, прижимную колодку 25 для закрепления программируемых микросхем, - передатчик 26 и приемник 27, из которых состоит шинный формирователь 6, блок 28 согласования.

Адресные форм фователи, из которых

состоит блок 19 (фиг.2), содержат до

резисторы 29 и 30, диод. 3J, стабилитрон 32, инвертор 33 на ШС ЗЗЛН2,

элемент И, 34 на ИМС ЗЗЛАИ, Одним

входом все формирователи подключаются

к катоду диода 35,Количество таких д

формирователей в. блоке 19 должно быть.

равно максимальному числу адресных

входов у ПЛМ.

Пятый формирователь 21 импульсов

(фиг.З) содержит два RS-триггера 36

па ШС 133ТМ2, ключ 37 с входной логикой на ИМС 169ЛА25 инвертор 38 на

ШС J33J1H3 и цепь 39 привязки к ши- . не +5 В питания на диоде и резисторе.

мировании микросхем памяти на адресные выходы 24 необходимо подавать ти повые логические сигналы Лог.1 (больше 2,4 В) и Лог.0 (меньше 0,4 В), вследствие чего высокое напряжение на блок 19 не подают, При программировании микросхем IIJM подают повышенное напряжемте (+7 В - при программировании матрицы И ЛИ и +8,75 Б - при Программировании актив ного уровня выходов njE-) .

В память ЭВМ, пoдключae Oй к программатору, с внешних устройств (например, перфоленты) заносят информацию, подлежащую занесению в микросхему .

Работа в основном режиме состоит из следующих этапов.

50

Контроль содерж1шого микросхемы. Микросхема, подлежащая программирова нию, устанавливается в колодку 25. Путем перебора адресов в регистре 7 производится считьшание информации

Блоки сравнения 1 8 и согласования 28 гс из микросхем ПЗУ при напряжении питасостоят из четырех функционально идентичных узлов (фиг,4). Блок 18 сравнения состоит из четырех компараторов 40 на.ИМС 52JСАЗ. Блок 28 соглания ь5 В на выходе 1 1 , Считанная информация поступает на блок 17 контроля и далее через передатчик 26 и блок 22 в ЭВМ.

тем подключения к входу соответствующего усилителя МО1ЦНОСТИ конденсатора требуемой емкости. Для этого через блоки 22 и 27 в формирователи 1-3 поступают коды по стробирующему сигналу, поступающему через блок 22 по шипе 5 управления, В формирователь 20 заносится код, соответств то- щий требуемому напряжению на адрес1 ых формирователях 19. При нрограм-

мировании микросхем памяти на адресные выходы 24 необходимо подавать типовые логические сигналы Лог.1 (больше 2,4 В) и Лог.0 (меньше 0,4 В), вследствие чего высокое напряжение на блок 19 не подают, При программировании микросхем IIJM подают повышенное напряжемте (+7 В - при программировании матрицы И ЛИ и +8,75 Б - при Программировании активного уровня выходов njE-) .

В память ЭВМ, пoдключae Oй к программатору, с внешних устройств (например, перфоленты) заносят информацию, подлежащую занесению в микросхему .

Работа в основном режиме состоит из следующих этапов.

Контроль содерж1шого микросхемы. Микросхема, подлежащая программированию, устанавливается в колодку 25. Путем перебора адресов в регистре 7 производится считьшание информации

ния ь5 В на выходе 1 1 , Считанная информация поступает на блок 17 контроля и далее через передатчик 26 и блок 22 в ЭВМ.

Контроль содержимого ШМ производится следующим образом.

Микросхема IIJM устанавливается в колодку 25. Путем перебора адресов в регистре 7 производится считывапие информации из микросхемы ПЛМ при напряжении питания -1-5 В на выходе 12, Считанная информация поступает на блок 17 контроля и далее через пере- датчик 27 и блок 28 в ЭВМ.

Программирование микросхем ПЗУ. В соответствии с выбранным типом микросхем должна быть сформирована соответствующая последовательность им- пульсов программирования. Эта последовательность вырабатывается ЭВМ, а форма импульсов - программатором. Из ЭВМ в регистр 8 заносится код, соответствующий, режиму записи, по кото рому блок 16 ключей переводится в режим записи информации, В регистр 7 заносится код адреса программируемого слова, а в регистр 9 - код, который должен быть записан в микросхе- му по выбранному адресу. На формирователи 1-3 поступают коды, соответствующие значениям напряжений, которые необходимо подавать на соотве - ствую- щие входы (питание, выборка кристал- ла, код числа) микросхемы. Затем по управляющим сигналам, поступающим с ЭВМ в последовательности, определяемой техническими условиями, на временную диаграмму программирования микросхемы, на выходах формирователей 1-3 появляется уровень ния, соответствующий поступающим кодам. Это напряжение поступает на программирующие входы микросхемы и вход питания блока 16 ключей, В соответствии с кодом, занесенным в регистр 9 срабатывают соответствующие ключи

Программирование ма ;рицы И, Режим программирования матрицы И осуществляется при напряжении +5 В-. Из ЭВМ в регистр 8 записьшается код, соответствующий режиму записи, по которому блок J6 ключей переводится в режим записи информации В регистр 9 заносится код номера программируемого конъюнктора. Ыонер конъюнктора определяется с помощью шести разрядов регистра 9. В регистр 7 записывается код адреса, в регистр iO - код маски, которая представляет собой позицион5а й код С единицсй в том разряде, перемычка конъюнктора которого в данном цикле програкт ирования разрушается. Такой код маски в рз- гистр 10 приводит к тому, что на выходе блока 19 адресных фогмировате- лей (фиг,2) во все разряды, кроме единичного, передаетсг. уровень напряжения, отрабатываемый формирователем 20. В единичном разряде уровень напряжения равен соответствукедему уровню напряжение разряда регистра 7, В формирователи J-3 поступают коды соответствующие значениям на:фяжекийз которые необходимо подавать на соответствующий входы (питание 11 - + 5 В, разреи ения программирования 12 +17 В, информационные входы J5 - +4 В) микросхемы. На формирователь 20 поступает код, соответствующий зна-.

блока ключей, через которые напряжение с выхода формирователя 3 поступа- 45 ченхда напряжения, которое необходимо ет на программируемые разряды микро- подавать на адресные входы 14 и

вход 13 выборки (+IQ В). При необходимости создавать определеннуто TexKH- ческими условиями форму имплопьсов 50 (длительностьS скважность, форму и длительность фронтов) соотзетстзен- но изменяют коды, поступа ощТ е на формирователи 1-3 и 20, Необходимое косхемы. При необходимости создавать определенными техническими условиями форму импульсов (длительность, скважность, форму и длительность фронтов)

соответственно изменяют коды в соответствующих формирователях 1-3, Адреса и разряды, не подлежащие прог раммиров,ани1о, автоматически определяются в ЭВМ и пропускаются при программировании,

Необходимое количество программирующих импульсов и режимы программирования устанавливаются программным

личес-шо импульсов программирснания 55 и режимы пpoгpa ft иpoвaIшя устанавливаются программным путем Е ЭВМ,

В реж1{ме контроля матрицы И на вход 12 разрешений програм: шрования подается уровень напряжения логичеС

путем в , Блок J8 определяет перегрузки по кoнтpoлиpye ым напряжениям программирования и передает инфор - мацию через блоки 6 и 22 в ЭВМ,

Программирование микросхем ПЛМ, При программировании ПЛ1-1 необходимо соблюдать соответств тощие требования, которые включают этапы программирования матрицы И, матрицы ИЛИ и активного уровня выходов ПЛМ.

Программирование ма ;рицы И, Режим программирования матрицы И осуществляется при напряжении +5 В-. Из ЭВМ в регистр 8 записьшается код, соответствующий режиму записи, по которому блок J6 ключей переводится в режим записи информации В регистр 9 заносится код номера программируемого конъюнктора. Ыонер конъюнктора определяется с помощью шести разрядов регистра 9. В регистр 7 записывается код адреса, в регистр iO - код маски, которая представляет собой позицион5а й код С единицсй в том разряде, перемычка конъюнктора которого в данном цикле програкт ирования разрушается. Такой код маски в рз- гистр 10 приводит к тому, что на выходе блока 19 адресных фогмировате- лей (фиг,2) во все разряды, кроме единичного, передаетсг. уровень напряжения, отрабатываемый формирователем 20. В единичном разряде уровень напряжения равен соответствукедему уровню напряжение разряда регистра 7, В формирователи J-3 поступают коды соответствующие значениям на:фяжекийз которые необходимо подавать на соответствующий входы (питание 11 - + 5 В, разреи ения программирования 12 +17 В, информационные входы J5 - +4 В) микросхемы. На формирователь 20 поступает код, соответствующий зна-.

ченхда напряжения, которое необходимо подавать на адресные входы 14 и

личес-шо импульсов программирснания 55 и режимы пpoгpa ft иpoвaIшя устанавливаются программным путем Е ЭВМ,

В реж1{ме контроля матрицы И на вход 12 разрешений програм: шрования подается уровень напряжения логичеС

кого О, для этого формирователь 2 обнуляется. В регистр 8 записывается код, соответствующий режиму считывания. Схема 17 измерения, связанная с выходом J5 восьмог о разряда микросхемы 25, фиксирует состояние программируемой перемычки. Остальные сигналы на входах микросхемы 25 не изменяются,

Программирование матрицы ШШ.

Режим программирования матрицы ИЛИ реализуется нри повышенном напряжеПрограммирование активных уровней выходов ПЛМ производится перед программированием матриц И и ИЛИ. За каждый цикл программирования разрушается только одна перемычка. В этом ре жиме на адресные входы 14 подаются сигналы логической 1, поэтому регистр 10 обнуляется. В регистр 7 записывается единичный код (единицы во всех разрядах регистра 7). В регистр 8 записывается код, соответстнии питания. За каждый цикл программирования разрушается только одна пе- 15 вуюш;ий режиму записи, по которому ремычка. В этом режиме на адресные блок 16 ключей переводится в режим

записи информации, а в регистр 9 - код номера программируемой перемычки выхода микросхемы 25, которая пережи- 20 гается в данном цикле программирования. Па формирователи i-3 поступаютвходы 14 подаются уровни напряжений, соответствующие логическим сигналам О и 1, поэтому регистр 10 обнуляется. В регистр 7 записывается код номера логического произведения, которое необходимо исключить ii3 выход- нон функции, в регистр 8 - код, соответствующий режиму записи, по котокоды, соответствующие значениям напряжений, которые необходимо подавать на соответствующие входы микророму блок 16 ключей переводится в ре- 25 схемы 25. В формирователь 20 записыжим записи информации, а в регистр 9 - код номера дизъюнктора, который программируется в данном цикле програм- .мирования. На формирователи 1-3 поступают коды, соответствующие значе- 30 фронтов импульсов) соответстверпю изниям напряженш, которые необходимо подавать на соответствующие входы микросхемь5 25. В формирователь 20 записывается код напряжения, которое

меняют коды на входах формирователей 1 и 3, Необходимое количество импульсов программирования и режимы программирования устанавливаются проподается на вход 13 выборки (+30 В). 35 граммным путем в ЭВМ.

Для создания определенной технически- При контроле состояния перемычки

ми условиями формулы импульсов (длительность, сквалаюсть, форма -и длительность фронтов) соответственно изменяют коды формирователи 1-3 и 20, Необходимое количество импульсов программирования и режим программирования устанавливаются программным путем в ЭВМ,

Контроль записанной в матрицу ИЛИ g пающим от ЭВМ, информация с выход информации осуществляется при умень- формирователя 3 поступает на вход п внии уровней напряжения на входах разрешения программирования 12 и разрешения выборки 13 до уровня сигнала

схемы 17 измерения. По состоянию соответствующего выхода схемы 17 измерения определяется состояние перемыч- логического OV. Для этого обнуляет- gg ися формирователь 2. В регистр 8 запи- Контроль качества программирова- сывается код, соответствуюпщй режиму нш1. Для этого с помощью формировате- считывания. На формирователь 3 по- лей 1-3 устанавливают необходимые ступает код, соответствующий напряже- при считывании напряжения, В рению логической 1, которое поступа- gg гистр 8 заносится код, соответствую- ет на вход схемы 17 измерения. Состоя- щий режиму считывания и типу выходов ние пережигаемой Б данном цикле про- программируемой микросхемгл, С по- граммирования перемычки определяют мощью регистра 7 осуществляется пе- по коду на выходе схемы 17 измерения:, ребор адресов. Коды считанных чисел

Программирование активного уровня выходов.

Программирование активных уровней выходов ПЛМ производится перед программированием матриц И и ИЛИ. За каждый цикл программирования разрушается только одна перемычка. В этом режиме на адресные входы 14 подаются сигналы логической 1, поэтому регистр 10 обнуляется. В регистр 7 записывается единичный код (единицы во всех разрядах регистра 7). В регистр 8 записывается код, соответствуюш;ий режиму записи, по которому блок 16 ключей переводится в режим

коды, соответствующие значениям напряжений, которые необходимо подавать на соответствующие входы микровается нулевой код. Для создания определенной техническими условиями временной диаграммы (длительность, скважность, форма и длительность

в регистр 8 записывается код, соответствующий режиму считывания. Контроль осуществляется при повышенном напряжении питания ( + 8,75 В), которое отрабатывается формирователем 1. На формирователь 3 поступает код, соответствующий напряжению логической 1. По управляющим сигналам, поступоступают на блок 17 контроля и сравниваются с опорным напряжением, поступающим от формирователя 20. Код считанного числа поступает через блоки 6 и 22 в ЭВМ, где и производится его анализ.

Контроль 11ПМ, как и программирование, включает контроль матрицы И и ИЛИ, а также активных уровней вы.хо дов микросхемы ПЛМ. Кроме того, производится контроль соответствия записанных данных и исходных, который аналогичен контролю микросхем постоянной памяти

Функциональный контроль. После программирования всего массива чисел может производиться контроль функционирования на высокой частоте Из ЭВМ в регистр 8 устанавливают режим считывания. Путем перебора адресов в регистре 1, как и в предыдун1ем режиме, производится опрос всех запрограммированных слоев.

Формула изобретения

Программатор, содержащий первый, второй, третий и четвертый формирователи импульсов, блок синхронизации шинньш формирователь, первые группы входов формирователей импульсов соединены с соответствующими выходами блока синхронизации, а вторые группы входов соединены с выходами шинного формирователя, первый, второй, третий регистры, информационные входы которых соединены с соответствующими выходами шинного формирователя, а управляющие входы соединены с соответствующими выходами блока синхронизации, блок ключей, первая и вторая группы входов которого соединены с выходами второго и третьего регистров, блок контроля, входы которого соединены с выходами блока ключей и являются информационными выходами программатора, а выходы соединены с входами шинного формирователя, управляющий вход которого соединен с

соответствующим выходом блока синхронизации, блок сравнения, выходы торого соединень с выходами блока контроля,входы-выходы шинного формирователя соедине шс первой группой входов-выходов блока синхронизации, вторая группа входов-выходов которого является инфopмaциcIiт o-aдpecнЫiЧИ Еходами-вь ходами проrpai-maтора, а третья группа входов-выходов является управлякз:им51 входам 1 вкходами программатора, отличающийся тем, что, с целью расширения области применения за счет возможности программирования ПШ, Б него введен блок адресных формирователей, блок согласования, чствартый регистр пятый формирователь импульсов, причем управляющий Еход четвертого регистра соединен с соответствующим выходам блока синхронизации, а группа инфор5

0

мационных входов регистра соединена с соответстпующими выходами шинного фор25 мирователя, nepaaj: и вторая группы входов блока адресных формирователей соединены соответственно с выходами первого и четвертого регистров, выходы блока адресных формирователей яв30 ляются адресными выходами программатора, первый, второй, третий и четвертый входы блока согласования соединены с выходами соответственно первого, второго, третьего и четвертого

„g формирователей импульсов, входы блока сравнения соединены с соответствующими выходами блока согласования, первый и.в торой выходы которого являются первым и вторым выходами импульс40 ного питания программатора, третий выход блока согласования соединен с входом питания блока ключей и входом блока контроля, четвертый выход блока согласования соединен с входом пи45 тания блока адресных формирователей и вxoдo питания пятого формирователя импульсов, выход которого является третьим выходом импульсного питания программатора.

1439677

11Г

Л

OrnKzj)

фиг. г

Om5f.28

5В

Авторы

Даты

1988-11-23—Публикация

1986-12-18—Подача