Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например решающих усилителях, компараторах, мостовых усилителях мощности и т.п.

Известны схемы классических дифференциальных усилителей (ДУ) с комплементарным входным каскадом, которые стали основой многих серийных аналоговых микросхем [1-11].

Кроме того, ДУ данного класса активно применяются в структуре СВЧ-устройств, реализованных на базе SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи, мостовых усилителей мощности и т.п.

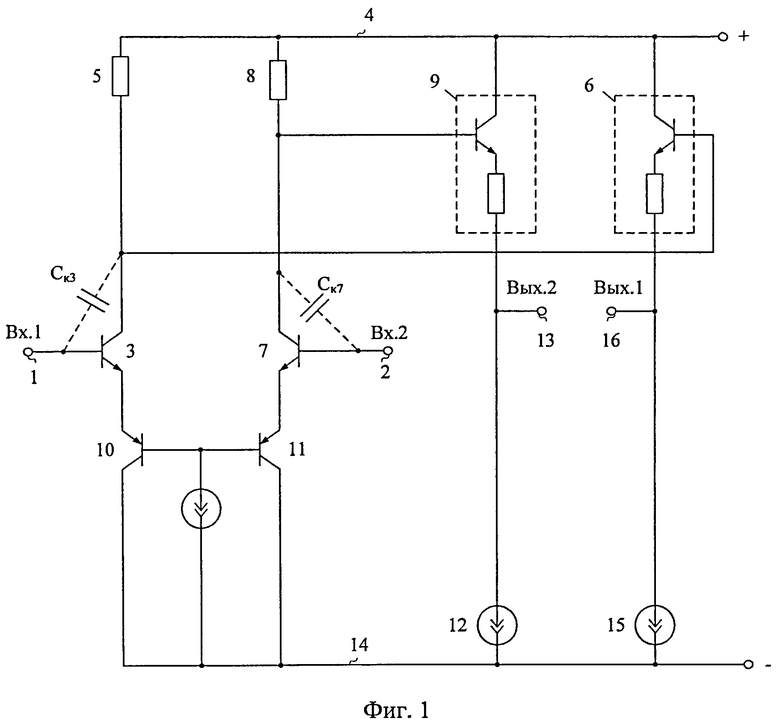

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте US 3828268, fig.5, содержащий первый 1 и второй 2 входы устройства, первый 3 входной транзистор, коллектор которого соединен с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник и связан с базой первого 6 выходного транзистора, второй 7 входной транзистор, коллектор которого соединен с первой 4 шиной источника питания через второй 8 токостабилизирующий двухполюсник и связан с базой второго 9 выходного транзистора, третий 10 входной транзистор, эмиттер которого соединен с эмиттером первого 3 входного транзистора, четвертый 11 входной транзистор, эмиттер которого соединен с эмиттером второго 7 входного транзистора, третий 12 токостабилизирующий двухполюсник, включенный между эмиттером второго 9 выходного транзистора, связанным с первым 13 выходом устройства и второй 14 шиной источника питания, четвертый 15 токостабилизирующий двухполюсник, включенный между эмиттером первого 6 выходного транзистора, связанным со вторым 16 выходом устройства и второй 14 шиной источника питания, причем коллекторы первого 6 и второго 9 выходных транзисторов связаны с первой 4 шиной источника питания, а коллекторы третьего 10 и четвертого 11 входных транзисторов соединены со второй 14 шиной источника питания.

Существенный недостаток известного ДУ состоит в том, что он не работоспособен из-за проблем со статическим режимом при высоких значениях коэффициента усиления по напряжению (Ку), зависящего от сопротивлений первого 5 и второго 8 токостабилизирующих двухполюсников, которые могут для увеличения Ку выполняться в виде источников тока.

Основная задача предлагаемого изобретения состоит в создании условий, при которых обеспечивается высокая стабильность статического режима ДУ и повышенные значения его коэффициента усиления по напряжению.

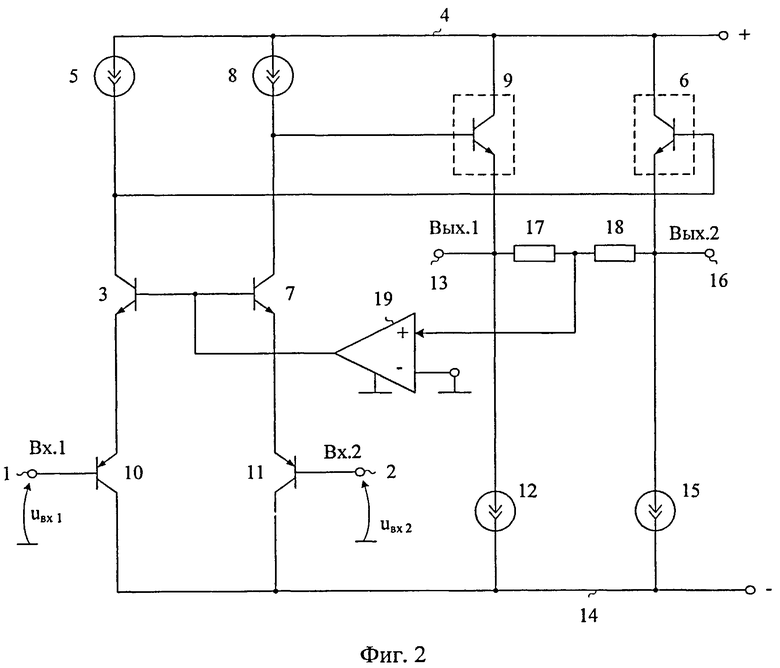

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входы устройства, первый 3 входной транзистор, коллектор которого соединен с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник и связан с базой первого 6 выходного транзистора, второй 7 входной транзистор, коллектор которого соединен с первой 4 шиной источника питания через второй 8 токостабилизирующий двухполюсник и связан с базой второго 9 выходного транзистора, третий 10 входной транзистор, эмиттер которого соединен с эмиттером первого 3 входного транзистора, четвертый 11 входной транзистор, эмиттер которого соединен с эмиттером второго 7 входного транзистора, третий 12 токостабилизирующий двухполюсник, включенный между эмиттером второго 9 выходного транзистора, связанным с первым 13 выходом устройства и второй 14 шиной источника питания, четвертый 15 токостабилизирующий двухполюсник, включенный между эмиттером первого 6 выходного транзистора, связанным со вторым 16 выходом устройства и второй 14 шиной источника питания, причем коллекторы первого 6 и второго 9 выходных транзисторов связаны с первой 4 шиной источника питания, а коллекторы третьего 10 и четвертого 11 входных транзисторов соединены со второй 14 шиной источника питания, предусмотрены новые элементы и связи - первый 1 вход устройства соединен с базой третьего 10 входного транзистора, второй 2 вход устройства соединен с базой четвертого 11 входного транзистора, между первым 13 и вторым 16 выходами устройства включены последовательно соединенные первый 17 и второй 18 дополнительные резисторы, причем общий узел первого 17 и второго 18 дополнительных резисторов связан с объединенными базами первого 3 и второго 7 входных транзисторов через дополнительный неинвертирующий усилитель 19.

На фиг.1 показана схема ДУ-прототипа.

На фиг.2 приведена схема заявляемого устройства в соответствии с формулой изобретения.

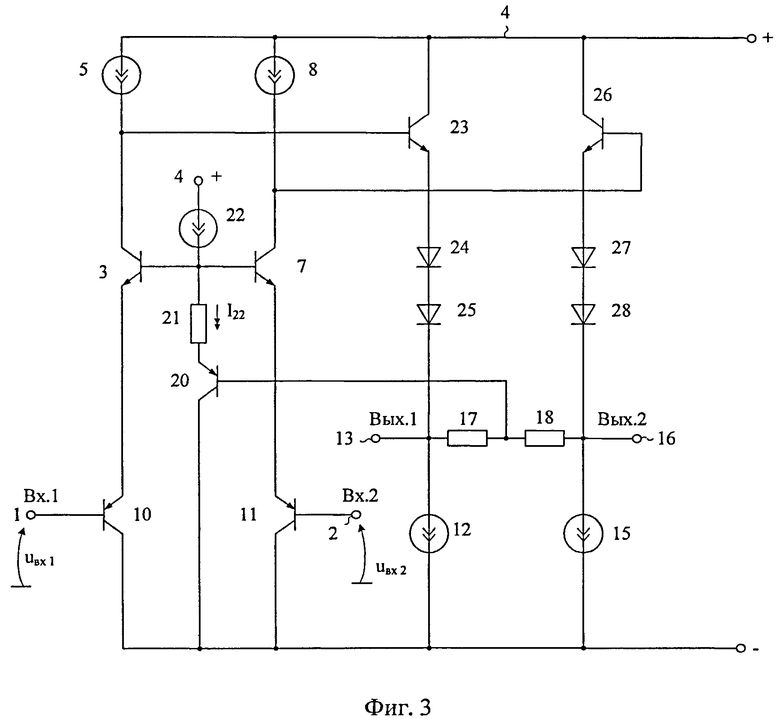

На фиг.3 представлена схема фиг.2 с конкретным выполнением дополнительного неинвертирующего усилителя 19 для случая, когда входные напряжения uвх.1, uвх.2 подаются на входы ДУ относительно общей шины.

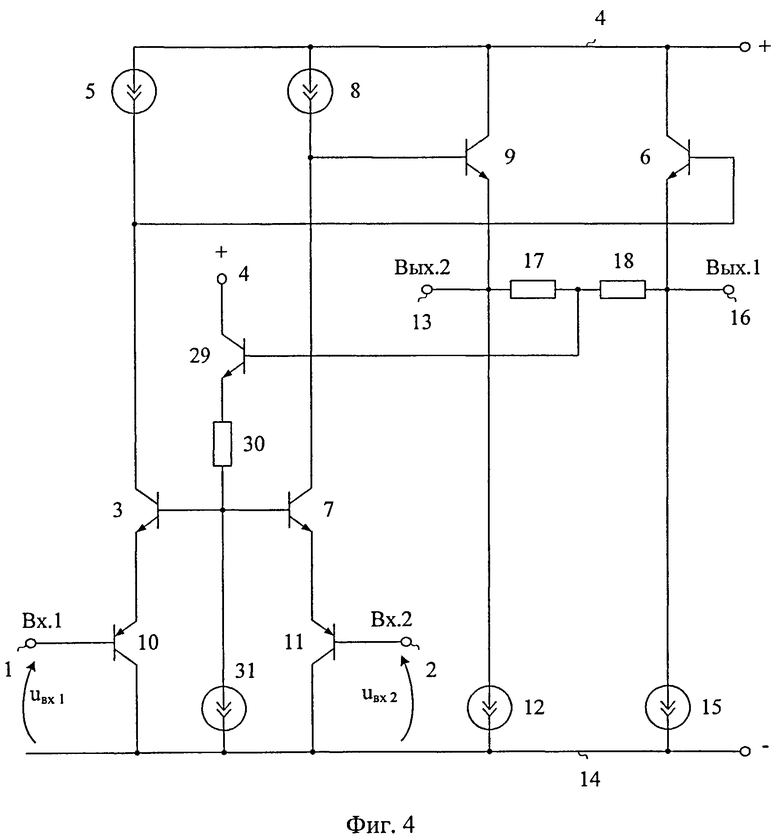

На фиг.4 представлена схема фиг.2 с конкретным выполнением дополнительного неинвертирующего усилителя 19 для случая, когда входные напряжения uвх.1, uвх.2 подаются на входы ДУ относительно второй 14 отрицательной шины источника питания.

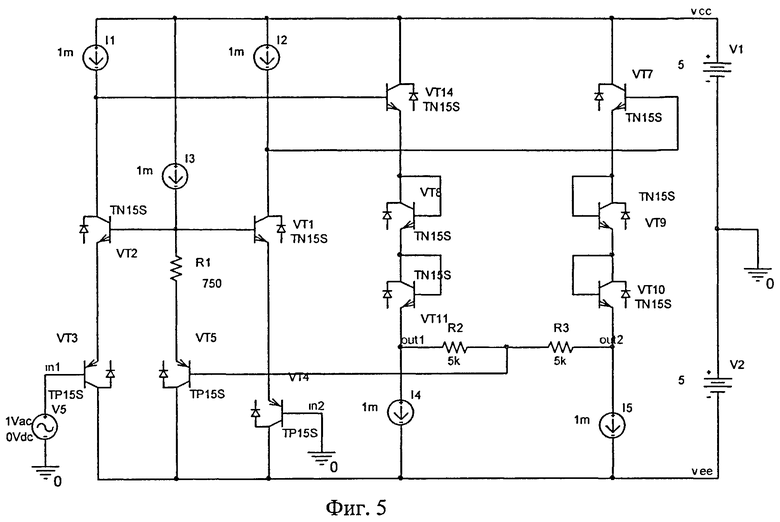

На фиг.5 приведена схема заявляемого ДУ фиг.3 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

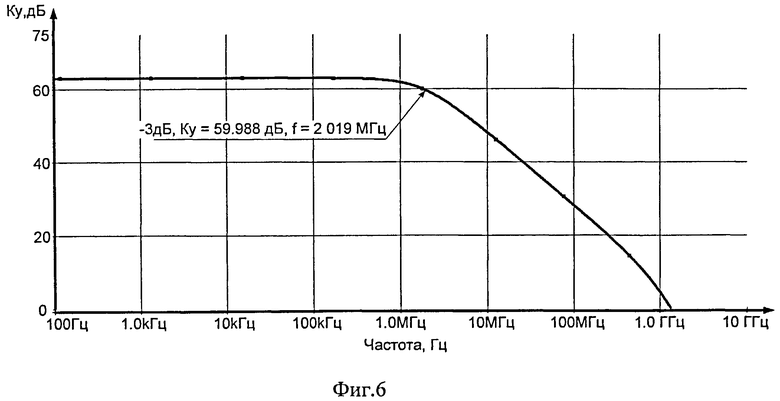

На фиг.6 показана частотная зависимость коэффициента усиления по напряжению ДУ фиг.5.

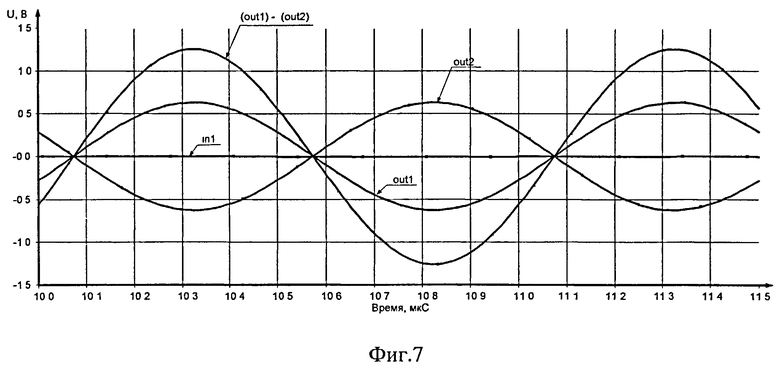

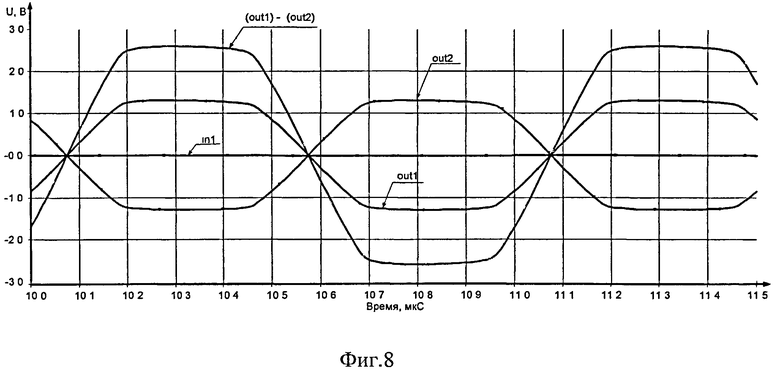

На фиг.7 показаны напряжения на выходах ДУ фиг.5 при входном сигнале Uвх=1 мВ и f=1 МГц, а на фиг.8 - напряжения на выходах при входном сигнале Uвх=3 мВ и f=1 МГц.

Дифференциальный усилитель с комплементарным входным каскадом фиг.2 содержит первый 1 и второй 2 входы устройства, первый 3 входной транзистор, коллектор которого соединен с первой 4 шиной источника питания через первый 5 токостабилизирующий двухполюсник и связан с базой первого 6 выходного транзистора, второй 7 входной транзистор, коллектор которого соединен с первой 4 шиной источника питания через второй 8 токостабилизирующий двухполюсник и связан с базой второго 9 выходного транзистора, третий 10 входной транзистор, эмиттер которого соединен с эмиттером первого 3 входного транзистора, четвертый 11 входной транзистор, эмиттер которого соединен с эмиттером второго 7 входного транзистора, третий 12 токостабилизирующий двухполюсник, включенный между эмиттером второго 9 выходного транзистора, связанным с первым 13 выходом устройства и второй 14 шиной источника питания, четвертый 15 токостабилизирующий двухполюсник, включенный между эмиттером первого 6 выходного транзистора, связанным со вторым 16 выходом устройства и второй 14 шиной источника питания, причем коллекторы первого 6 и второго 9 выходных транзисторов связаны с первой 4 шиной источника питания, а коллекторы третьего 10 и четвертого 11 входных транзисторов соединены со второй 14 шиной источника питания. Первый 1 вход устройства соединен с базой третьего 10 входного транзистора, второй 2 вход устройства соединен с базой четвертого 11 входного транзистора, между первым 13 и вторым 16 выходами устройства включены последовательно соединенные первый 17 и второй 18 дополнительные резисторы, причем общий узел первого 17 и второго 18 дополнительных резисторов связан с объединенными базами первого 3 и второго 7 входных транзисторов через дополнительный неинвертирующий усилитель 19.

В качестве транзисторов 6 и 9 могут использоваться классические составные транзисторы, включающие резисторы или p-n переходы 24, 25, 27, 28 в эмиттерных цепях. В схеме фиг.3 данные составные транзисторы 6 и 9 выполнены на элементах 23, 24, 25 и 26, 27, 28. Дополнительный неинвертирующий усилитель 19 в схеме фиг.3 реализован на транзисторе 20, резисторе 21 и источнике тока 22.

В схеме фиг.4 дополнительный неинвертирующий усилитель 19 содержит входной транзистор 29 и согласующий резистор 30. При таком построении ДУ существенно упрощается согласование статических режимов транзисторов 3, 7, 10, 11, 9 и 6.

Рассмотрим работу ДУ фиг.3.

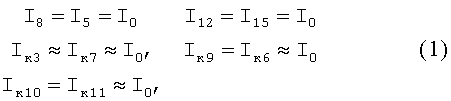

Статический режим по току транзисторов предлагаемого ДУ фиг.2 устанавливается токостабилизирующими двухполюсниками 5, 8, 12, и 15. Причем коллекторные (Iкi) токи транзисторов схемы:

где I0 - заданное значение опорного тока, например 1 мА.

Статические напряжения на выходах ДУ при нулевом входном сигнале (uвх=0) зависят только от напряжения U(-) на инвертирующем входе дополнительного усилителя 19:

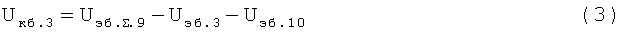

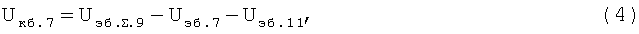

Причем напряжения коллектор-база транзисторов 3 и 7, определяющие амплитуду (Um) выходных напряжений ДУ:

где Uэб.Σ.9, Uэб.Σ.6 - напряжения эмиттер-база транзисторов 9 и 6, которые для обеспечения заданных выходных амплитуд Um в схеме фиг.3 должны выполняться в виде составных активных элементов, либо КМОП-транзисторов. В схеме фиг.4 такое построение 9 и 6 необязательно;

Uэб.3≈Uэб.7≈Uэб.10≈Uэб.11≈0,7 В - напряжения эмиттер-база транзисторов 3, 7, 10, 11.

Таким образом, статический режим транзисторов схемы фиг.2 не зависит от дифференциального сопротивления (ri=ri5=ri8) двухполюсников 5, 8, которые для повышения Ку до уровня 60÷70 дБ (фиг.6) могут выполняться в виде источников тока. В ДУ-прототипе фиг.1 такое исполнение элементов 5, 8 не приемлемо из-за проблем с устойчивостью статического режима. Повышенные значения ri=ri5=ri8 позволяют получить в схеме фиг.2 повышенные значения Ку.

Результаты компьютерного моделирования схемы фиг.5 показывают, что на основе предлагаемого ДУ реализуются широкополосные драйверы дифференциальных линий связи усилители мощности, фазорасщепители с повышенным коэффициентом усиления и т.п.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US №2010/0225392.

2. Патент US №3786362.

3. Патент US №3828268.

4. Патент US №5406222.

5. Патент US №3555402.

6. Патент US №4074205.

7. Патент US №5401995.

8. Патент SU №1107279.

9. Патент JP №57-5364.

10. Патент US №4/030/044.

11. Патент US №4/286/227.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2012 |

|

RU2513482C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2439781C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439779C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446556C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2436226C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321158C1 |

Изобретение относится к области радиотехники и связи. Техническим результатом является обеспечение высокой стабильности статического режима дифференциального усилителя и повышение значения его коэффициента усиления по напряжению. Дифференциальный усилитель с комплементарным входным каскадом содержит первый (1) и второй (2) входы устройства, первый (3) входной транзистор, коллектор которого соединен с первой (4) шиной источника питания через первый (5) токостабилизирующий двухполюсник и связан с базой первого (6) выходного транзистора, второй (7) входной транзистор, коллектор которого соединен с первой (4) шиной источника питания через второй (8) токостабилизирующий двухполюсник и связан с базой второго (9) выходного транзистора, третий (10) входной транзистор, эмиттер которого соединен с эмиттером первого (3) входного транзистора, четвертый (11) входной транзистор, эмиттер которого соединен с эмиттером второго (7) входного транзистора, третий (12) токостабилизирующий двухполюсник, включенный между эмиттером второго (9) выходного транзистора, четвертый (15) токостабилизирующий двухполюсник, включенный между эмиттером первого (6) выходного транзистора. Между первым (13) и вторым (16) выходами устройства включены последовательно соединенные первый (17) и второй (18) дополнительные резисторы, причем общий узел первого (17) и второго (18) дополнительных резисторов связан с объединенными базами первого (3) и второго (7) входных транзисторов через дополнительный неинвертирующий усилитель (19). 8 ил.

Дифференциальный усилитель с комплементарным входным каскадом, содержащий первый (1) и второй (2) входы устройства, первый (3) входной транзистор, коллектор которого соединен с первой (4) шиной источника питания через первый (5) токостабилизирующий двухполюсник и связан с базой первого (6) выходного транзистора, второй (7) входной транзистор, коллектор которого соединен с первой (4) шиной источника питания через второй (8) токостабилизирующий двухполюсник и связан с базой второго (9) выходного транзистора, третий (10) входной транзистор, эмиттер которого соединен с эмиттером первого (3) входного транзистора, четвертый (11) входной транзистор, эмиттер которого соединен с эмиттером второго (7) входного транзистора, третий (12) токостабилизирующий двухполюсник, включенный между эмиттером второго (9) выходного транзистора, связанным с первым (13) выходом устройства и второй (14) шиной источника питания, четвертый (15) токостабилизирующий двухполюсник, включенный между эмиттером первого (6) выходного транзистора, связанным со вторым (16) выходом устройства и второй (14) шиной источника питания, причем коллекторы первого (6) и второго (9) выходных транзисторов связаны с первой (4) шиной источника питания, а коллекторы третьего (10) и четвертого (11) входных транзисторов соединены со второй (14) шиной источника питания, отличающийся тем, что первый (1) вход устройства соединен с базой третьего (10) входного транзистора, второй (2) вход устройства соединен с базой четвертого (11) входного транзистора, между первым (13) и вторым (16) выходами устройства включены последовательно соединенные первый (17) и второй (18) дополнительные резисторы, причем общий узел первого (17) и второго (18) дополнительных резисторов связан с объединенными базами первого (3) и второго (7) входных транзисторов через дополнительный неинвертирующий усилитель (19).

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Дифференциальный усилитель | 1979 |

|

SU849420A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ12 | 0 |

|

SU365797A1 |

| Усилитель | 1985 |

|

SU1246338A1 |

Авторы

Даты

2013-02-20—Публикация

2012-01-10—Подача