Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, фазорасщипителях, компараторах, драйверах дифференциальных линий связи т.п.).

В современной микроэлектронике широко применяются комплементарные каскодные дифференциальные операционные усилители (ДУ) на p-n-p и n-p-n транзисторах, архитектура которых впервые была использована в микросхеме µA741 [1÷5].

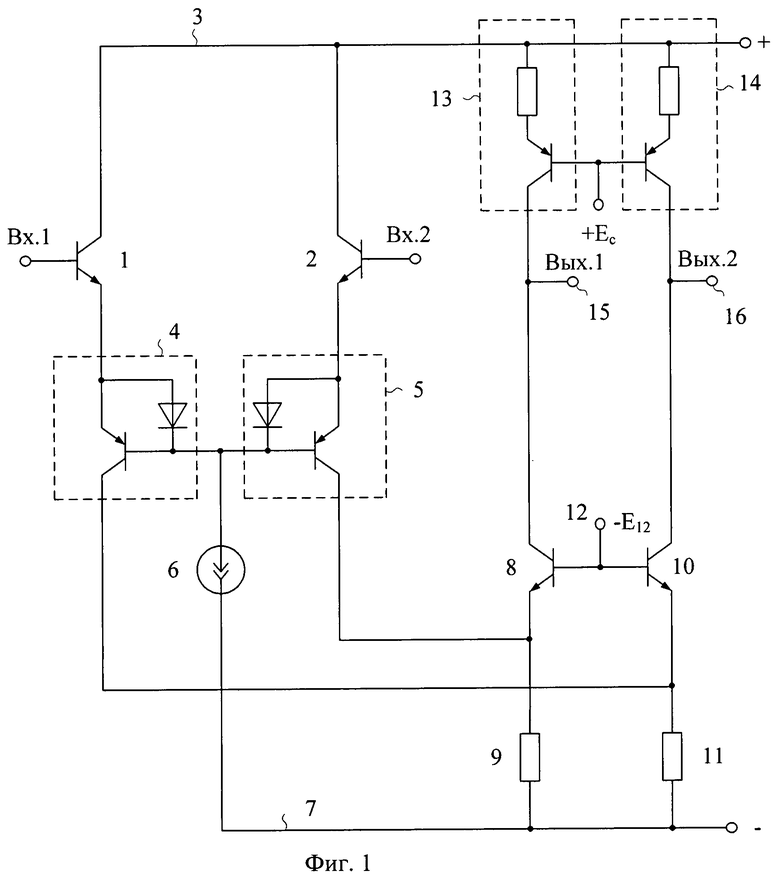

Ближайшим прототипом (фиг.1) заявляемого устройства является ДУ, представленный в структуре микросхемы по патенту US 5.521.552, fig.3, содержащий первый 1 и второй 2 входные транзисторы, коллекторы которых соединены с первой 3 шиной источника питания, базы связаны с соответствующими входами устройства, первое 4 токовое зеркало, эмиттерный вход которого соединен с эмиттером первого 1 входного транзистора, второе 5 токовое зеркало, эмиттерный вход которого соединен с эмиттером второго 2 входного транзистора, первый 6 источник опорного тока, включенный между объединенными базовыми входами первого 4 и второго 5 токовых зеркал и второй 7 шиной источника питания, первый 8 выходной транзистор, эмиттер которого соединен с коллекторным выходом второго 5 токового зеркала и связан со второй 7 шиной источника питания через первый 9 токостабилизирующий двухполюсник, второй 10 выходной транзистор, эмиттер которого соединен с коллекторным выходом первого 4 токового зеркала и связан со второй 7 шиной источника питания через второй 11 токостабилизирующий двухполюсник, источник вспомогательного напряжения 12, соединенный с базами первого 8 и второго 10 выходных транзисторов, второй 13 источник опорного тока, включенный между шиной первого 3 источника питания и коллектором первого 8 выходного транзистора, третий 14 источник опорного тока, включенный между шиной первого 3 источника питания и коллектором второго 10 выходного транзистора, первый 15 и второй 16 парафазные выходы устройства.

Существенный недостаток известного ДУ состоит в том, что он имеет нестабильный уровень выходного синфазного напряжения, зависящий от параметров второго 13 и третьего 14 источников опорного тока. Это значительно затрудняет его согласование с последующими функциональными узлами.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение.

Поставленная задача решается тем, что в комплементарном каскодном дифференциальном усилителе с парафазным выходом фиг.1, содержащем первый 1 и второй 2 входные транзисторы, коллекторы которых соединены с первой 3 шиной источника питания, базы связаны с соответствующими входами устройства, первое 4 токовое зеркало, эмиттерный вход которого соединен с эмиттером первого 1 входного транзистора, второе 5 токовое зеркало, эмиттерный вход которого соединен с эмиттером второго 2 входного транзистора, первый 6 источник опорного тока, включенный между объединенными базовыми входами первого 4 и второго 5 токовых зеркал и второй 7 шиной источника питания, первый 8 выходной транзистор, эмиттер которого соединен с коллекторным выходом второго 5 токового зеркала и связан со второй 7 шиной источника питания через первый 9 токостабилизирующий двухполюсник, второй 10 выходной транзистор, эмиттер которого соединен с коллекторным выходом первого 4 токового зеркала и связан со второй 7 шиной источника питания через второй 11 токостабилизирующий двухполюсник, источник вспомогательного напряжения 12, соединенный с базами первого 8 и второго 10 выходных транзисторов, второй 13 источник опорного тока, включенный между шиной первого 3 источника питания и коллектором первого 8 выходного транзистора, третий 14 источник опорного тока, включенный между шиной первого 3 источника питания и коллектором второго 10 выходного транзистора, первый 15 и второй 16 парафазные выходы устройства, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 17, коллектор которого соединен с первой 3 шиной источника питания, эмиттер связан с объединенными базовыми входами первого 4 и второго 5 токовых зеркал через двухполюсник цепи смещения потенциалов 18, причем коллектор первого 8 выходного транзистора связан с базой дополнительного транзистора 17 через последовательно соединенные первый 19 дополнительный буферный усилитель и первый дополнительный резистор 20, коллектор второго 10 выходного транзистора связан с базой дополнительного транзистора 17 через последовательно соединенный второй 21 дополнительный буферный усилитель и второй 22 дополнительный резистор, а в качестве первого 15 и второго 16 выходов устройства используются выходы соответствующих первого 19 и второго 21 дополнительных буферных усилителей.

На фиг.1 показана схема ДУ-прототипа.

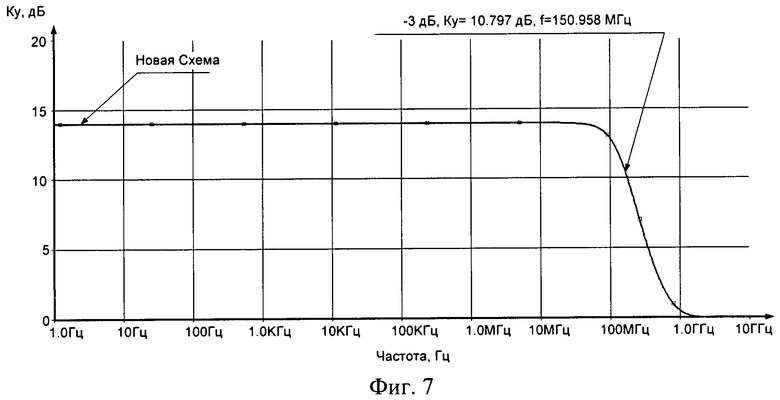

На фиг.2 показана схема заявляемого устройства в соответствии с формулой изобретения.

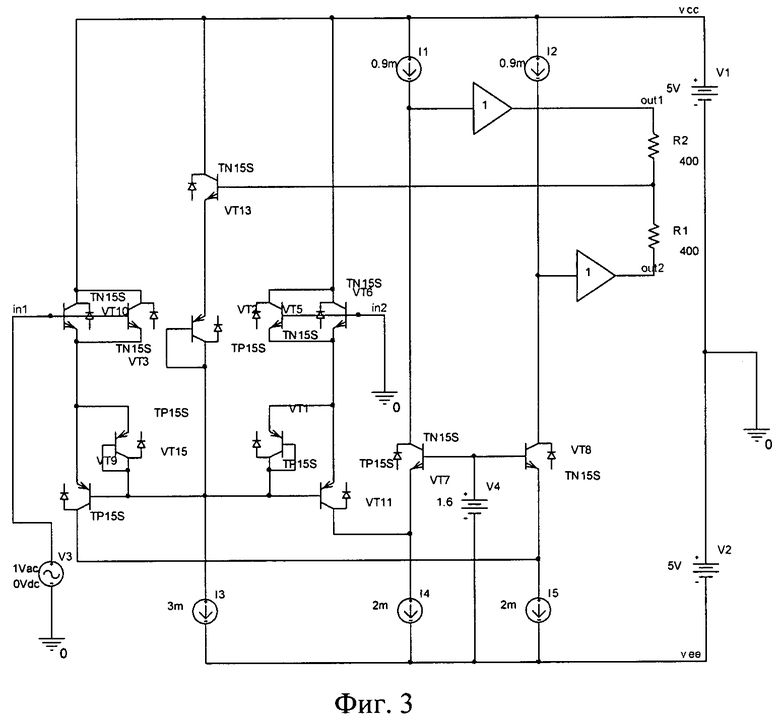

На фиг.3 показана схема заявляемого ДУ фиг.2 в среде компьютерного моделирования PSipce на моделях интегральных транзисторов ФГУП НПП «Пульсар».

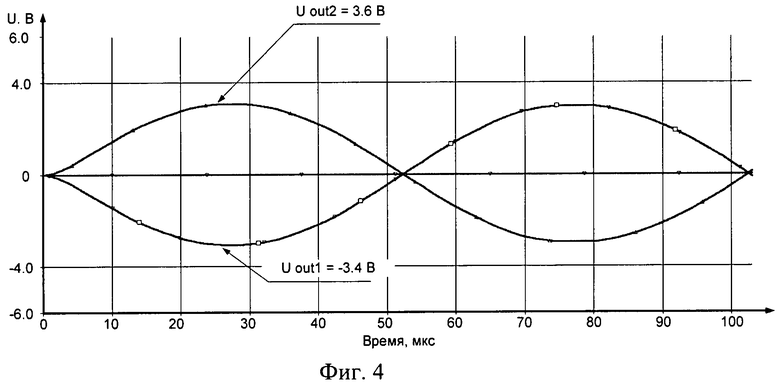

На фиг.4 представлена зависимость выходных напряжений для парафазных выходов ДУ фиг.3 от входного синусоидального напряжения с амплитудой uвх=1 мВ. Графики фиг.4 показывают, что заявляемый ДУ имеет два противофазных выходных напряжения и нулевой уровень выходного синфазного статического напряжения.

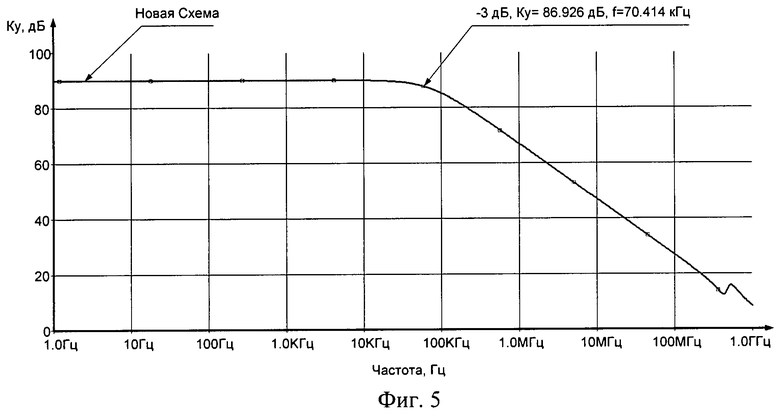

На фиг.5 - зависимость коэффициента усиления по напряжению ДУ фиг.3 от частоты.

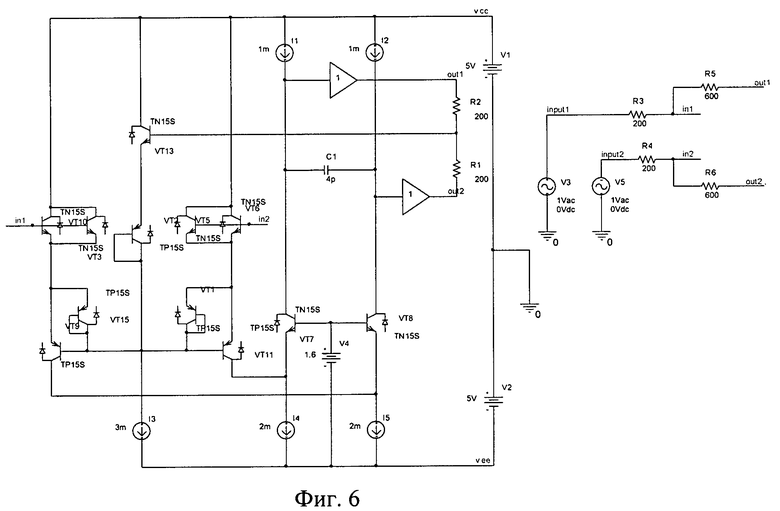

На фиг.6 показана схема включения предлагаемого ДУ в структуре драйвера дифференциальной линии связи, который реализуется за счет введения отрицательной обратной связи (элементы R3, R4, R5, R6).

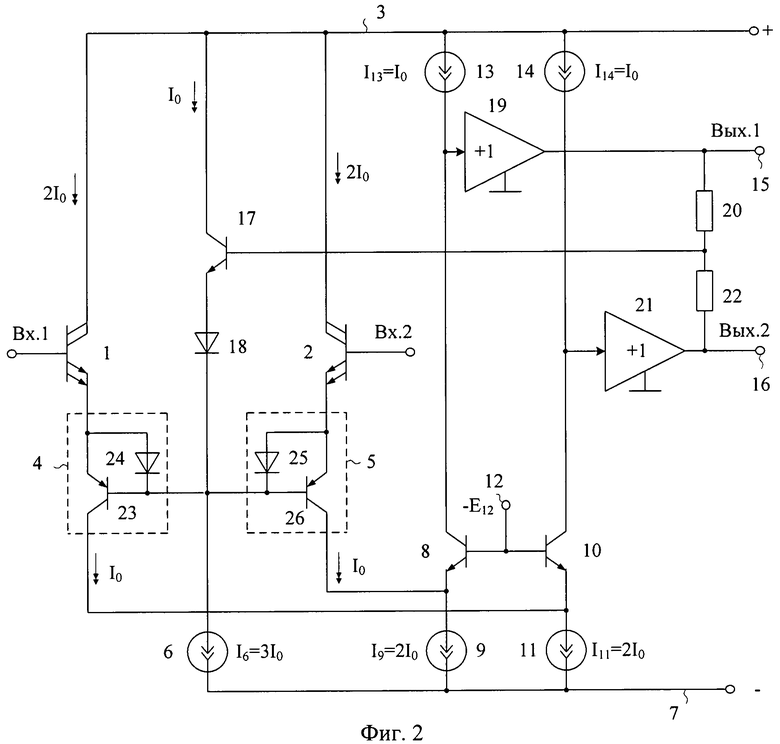

На фиг.7 приведена частотная зависимость дифференциального коэффициента усиления драйвера фиг.6.

Комплементарный каскодный дифференциальный усилитель с парафазным выходом фиг.2 содержит первый 1 и второй 2 входные транзисторы, коллекторы которых соединены с первой 3 шиной источника питания, базы связаны с соответствующими входами устройства, первое 4 токовое зеркало, эмиттерный вход которого соединен с эмиттером первого 1 входного транзистора, второе 5 токовое зеркало, эмиттерный вход которого соединен с эмиттером второго 2 входного транзистора, первый 6 источник опорного тока, включенный между объединенными базовыми входами первого 4 и второго 5 токовых зеркал и второй 7 шиной источника питания, первый 8 выходной транзистор, эмиттер которого соединен с коллекторным выходом второго 5 токового зеркала и связан со второй 7 шиной источника питания через первый 9 токостабилизирующий двухполюсник, второй 10 выходной транзистор, эмиттер которого соединен с коллекторным выходом первого 4 токового зеркала и связан со второй 7 шиной источника питания через второй 11 токостабилизирующий двухполюсник, источник вспомогательного напряжения 12, соединенный с базами первого 8 и второго 10 выходных транзисторов, второй 13 источник опорного тока, включенный между шиной первого 3 источника питания и коллектором первого 8 выходного транзистора, третий 14 источник опорного тока, включенный между шиной первого 3 источника питания и коллектором второго 10 выходного транзистора, первый 15 и второй 16 парафазные выходы устройства. В схему введен дополнительный транзистор 17, коллектор которого соединен с первой 3 шиной источника питания, эмиттер связан с объединенными базовыми входами первого 4 и второго 5 токовых зеркал через двухполюсник цепи смещения потенциалов 18, причем коллектор первого 8 выходного транзистора связан с базой дополнительного транзистора 17 через последовательно соединенные первый 19 дополнительный буферный усилитель и первый дополнительный резистор 20, коллектор второго 10 выходного транзистора связан с базой дополнительного транзистора 17 через последовательно соединенный второй 21 дополнительный буферный усилитель и второй 22 дополнительный резистор, а в качестве первого 15 и второго 16 выходов устройства используются выходы соответствующих первого 19 и второго 21 дополнительных буферных усилителей.

В качестве первого 6, второго 13 и третьего 14 источников опорного тока, а также первого 9 и второго 11 токостабилизирующих двухполюсников авторы рекомендуют использовать классические стабилизаторы тока на транзисторах или высокоомные резисторы.

Первый 19 и второй 21 буферные усилители могут быть реализованы на основе классических эмиттерных повторителей, в том числе на основе составных n-p-n и p-n-p транзисторов.

Рассмотрим работу ДУ фиг.2.

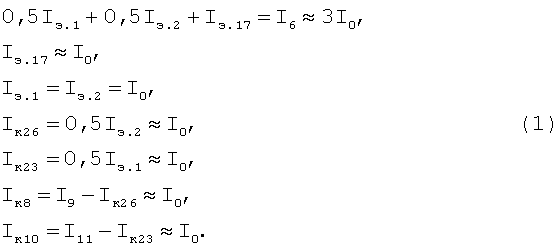

Статический режим по току транзисторов предлагаемого ДУ устанавливается двухполюсниками 6, 9, 11, 13 и 14. Причем коллекторные и эмиттерные токи транзисторов схемы:

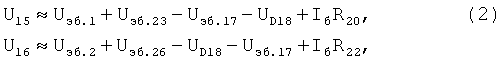

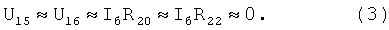

Статическое напряжение U15 на выходе Вых.1 (15) и U16 на Вых.2 (16) ДУ фиг.2 при нулевом входном сигнале (uвх=0) можно найти из уравнения:

где Uэб.1=Uэб.2=Uэб.23=Uэб.26=UD18 - напряжения «эмиттер-база» входных транзисторов 1 и 2, транзисторов 23, 26 токовых зеркал 4 и 5, двухполюсника цепи смещения потенциалов 18;

Iб - составляющая тока базы дополнительного транзистора 17 в дополнительном резисторе 20 (22).

Таким образом, при типовых значениях тока базы дополнительного транзистора 17, а также при R20=R22=500÷1000 Ом выходное синфазное напряжение ДУ фиг.2 практически равно нулю в широком диапазоне температурных и радиационных воздействий, а также изменений напряжений питания.

Это весьма существенно для согласования заявляемого ДУ с последующими функциональными узлами радиоэлектронной аппаратуры.

При синфазном изменении напряжений на входах Вх.1 и Вх.2 изменяются синфазно и напряжения на выходах 15 (U15) и 16 (U16). Однако при этом эмиттерный (коллекторный) ток дополнительного транзистора 17 остается постоянным. Поэтому коэффициент ослабления входных синфазных напряжений в заявляемом ДУ достаточно высок.

В схеме фиг.2 из-за наличия дополнительных буферных усилителей 19 и 21 значительно снижаются требования к величине сопротивлений дополнительных резисторов 20 и 22, что позволяет получить на выходах Вых.*1 и Вых.*2 нулевые уровни статических напряжений  независимо от статических параметров дополнительных буферных усилителей 19 и 21. Однако в схеме фиг.2 в низкоомной нагрузке, включенной между выходами Вых.*1 и Вых.*2, могут быть получены значительно большие мощности, которые определяются свойствами буферных усилителей 19 и 21. Кроме этого, в архитектуре фиг.2 максимальные амплитуды выходных напряжений положительной и отрицательной полярностей близки к сумме напряжений первого 3 и второго 7 источников питания.

независимо от статических параметров дополнительных буферных усилителей 19 и 21. Однако в схеме фиг.2 в низкоомной нагрузке, включенной между выходами Вых.*1 и Вых.*2, могут быть получены значительно большие мощности, которые определяются свойствами буферных усилителей 19 и 21. Кроме этого, в архитектуре фиг.2 максимальные амплитуды выходных напряжений положительной и отрицательной полярностей близки к сумме напряжений первого 3 и второго 7 источников питания.

Таким образом, предлагаемый ДУ имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US №5.521.552, fig.3.

2. Патент SU №736110.

3. Патент US №5.789.949.

4. Патент SU №843164.

5. Патент SU №4.389.579.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| ДВУХКАНАЛЬНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2452078C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2468504C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ И ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2010 |

|

RU2426221C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2436226C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455758C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Достигаемый технический результат - повышение стабильности выходного статического синфазного напряжения дифференциального усилителя. Технический результат достигается за счет введения в комплементарный каскодный дифференциальный усилитель с парафазным выходом дополнительного транзистора (17), коллектор которого соединен с первой (3) шиной источника питания, эмиттер связан с объединенными базовыми входами первого (4) и второго (5) токовых зеркал через двухполюсник цепи смещения потенциалов (18), причем коллектор первого (8) выходного транзистора связан с базой дополнительного транзистора (17) через последовательно соединенные первый (19) дополнительный буферный усилитель и первый дополнительный резистор (20), коллектор второго (10) выходного транзистора связан с базой дополнительного транзистора (17) через последовательно соединенные второй (21) дополнительный буферный усилитель и второй (22) дополнительный резистор, а в качестве первого (15) и второго (16) выходов устройства используются выходы соответствующих первого (19) и второго (21) дополнительных буферных усилителей. 7 ил.

Комплементарный каскодный дифференциальный усилитель с парафазным выходом, содержащий первый (1) и второй (2) входные транзисторы, коллекторы которых соединены с первой (3) шиной источника питания, базы связаны с соответствующими входами устройства, первое (4) токовое зеркало, эмиттерный вход которого соединен с эмиттером первого (1) входного транзистора, второе (5) токовое зеркало, эмиттерный вход которого соединен с эмиттером второго (2) входного транзистора, первый (6) источник опорного тока, включенный между объединенными базовыми входами первого (4) и второго (5) токовых зеркал и второй (7) шиной источника питания, первый (8) выходной транзистор, эмиттер которого соединен с коллекторным выходом второго (5) токового зеркала и связан со второй (7) шиной источника питания через первый (9) токостабилизирующий двухполюсник, второй (10) выходной транзистор, эмиттер которого соединен с коллекторным выходом первого (4) токового зеркала и связан со второй (7) шиной источника питания через второй (11) токостабилизирующий двухполюсник, источник вспомогательного напряжения (12), соединенный с базами первого (8) и второго (10) выходных транзисторов, второй (13) источник опорного тока, включенный между шиной первого (3) источника питания и коллектором первого (8) выходного транзистора, третий (14) источник опорного тока, включенный между шиной первого (3) источника питания и коллектором второго (10) выходного транзистора, первый (15) и второй (16) парафазные выходы устройства, отличающийся тем, что в схему введен дополнительный транзистор (17), коллектор которого соединен с первой (3) шиной источника питания, эмиттер связан с объединенными базовыми входами первого (4) и второго (5) токовых зеркал через двухполюсник цепи смещения потенциалов (18), причем коллектор первого (8) выходного транзистора связан с базой дополнительного транзистора (17) через последовательно соединенные первый (19) дополнительный буферный усилитель и первый дополнительный резистор (20), коллектор второго (10) выходного транзистора связан с базой дополнительного транзистора (17) через последовательно соединенный второй (21) дополнительный буферный усилитель и второй (22) дополнительный резистор, а в качестве первого (15) и второго (16) выходов устройства используются выходы соответствующих первого (19) и второго (21) дополнительных буферных усилителей.

| US 5521552 А, 28.05.1996 | |||

| КАСКОДНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2337471C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390911C2 |

Авторы

Даты

2012-01-10—Публикация

2010-12-20—Подача