Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, драйверах дифференциальных линий связи, фильтрах, компараторах т.п.).

Известны схемы классических двухкаскадных дифференциальных операционных усилителей (ДУ) с парафазным выходом, которые стали основой многих серийных аналоговых микросхем [1-17]. ДУ данного класса широко применяются в структуре СВЧ-устройств [16-17], реализованных на базе SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи, драйверов дифференциальных линий связи между СФ-блоками A/d и D/a-классов и т.п. В значительной степени этому способствует простота установления статического режима ДУ при низковольтном питании (1,2÷2,1) В, которое характерно для SiGe транзисторов с предельными частотами 120÷160 ГГц.

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель по патенту US 5.684.419, fig.4, содержащий первый 1 и второй 2 входные транзисторы, базы которых соединены со входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, коллекторы которых соединены с шиной второго 9 источника питания, эмиттеры связаны с соответствующими первым 10 и вторым 11 противофазными выходами устройства, второй 12 токостабилизирующий двухполюсник, включенный между эмиттером первого 7 выходного транзистора и шиной первого 6 источника питания, третий 13 токостабилизирующий двухполюсник, включенный между эмиттером второго 8 выходного транзистора и шиной первого 6 источника питания, первый 14 двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой первого 7 выходного транзистора и коллектором первого 1 входного транзистора, второй 15 двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой второго 8 выходного транзистора и коллектором второго 2 входного транзистора.

Существенный недостаток известного ДУ состоит в том, что он имеет нестабильный уровень выходного синфазного напряжения, зависящий от параметров двухполюсников коллекторной нагрузки 14 и 15. Это значительно затрудняет его согласование с последующими функциональными узлами многокаскадных интерфейсных СФ-блоков и IP-модулей.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение при изменении параметров элементов 14, 15, 5 в широких пределах.

Поставленная задача решается тем, что в дифференциальном операционном усилителе с парафазным выходом, фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых соединены со входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, коллекторы которых соединены с шиной второго 9 источника питания, эмиттеры связаны с соответствующими первым 10 и вторым 11 противофазными выходами устройства, второй 12 токостабилизирующий двухполюсник, включенный между эмиттером первого 7 выходного транзистора и шиной первого 6 источника питания, третий 13 токостабилизирующий двухполюсник, включенный между эмиттером второго 8 выходного транзистора и шиной первого 6 источника питания, первый 14 двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой первого 7 выходного транзистора и коллектором первого 1 входного транзистора, второй 15 двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой второго 8 выходного транзистора и коллектором второго 2 входного транзистора, предусмотрены новые элементы и связи - в схему введены третий 16 и четвертый 17 входные транзисторы, эмиттеры которых связаны с эмиттерами первого 1 и второго 2 входных транзисторов, база третьего 16 входного транзистора соединена с базой первого 1 входного транзистора, база четвертого 17 входного транзистора соединена с базой второго 2 входного транзистора, коллекторы третьего 16 и четвертого 17 входных транзисторов связаны с шиной второго 9 источника питания, эмиттеры первого 1 и второго 2 входных транзисторов подключены к эмиттеру первого 18 дополнительного транзистора, коллектор которого соединен с объединенными вторыми выводами первого 14 и второго 15 двухполюсников коллекторной нагрузки и через четвертый 19 токостабилизирующий двухполюсник связан с шиной второго 9 источника питания, причем первый 10 выход устройства связан с базой первого 18 дополнительного транзистора через первый 20 резистор обратной связи, а второй 11 выход устройства связан с базой первого 18 дополнительного транзистора через второй 21 резистор обратной связи.

На фиг.1 показана схема ДУ-прототипа.

На фиг.2 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения.

Схема ДУ по п.2 формулы изобретения приведена на фиг.3.

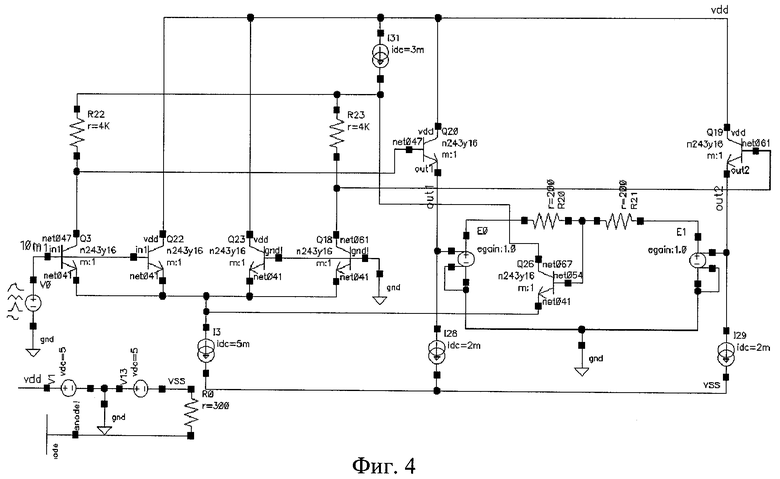

На фиг.4 показана схема заявляемого ДУ в среде компьютерного моделирования Cadance на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.5 - зависимость его коэффициента усиления по напряжению от частоты.

Дифференциальный операционный усилитель с парафазным выходом, фиг.2, содержит первый 1 и второй 2 входные транзисторы, базы которых соединены со входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, коллекторы которых соединены с шиной второго 9 источника питания, эмиттеры связаны с соответствующими первым 10 и вторым 11 противофазными выходами устройства, второй 12 токостабилизирующий двухполюсник, включенный между эмиттером первого 7 выходного транзистора и шиной первого 6 источника питания, третий 13 токостабилизирующий двухполюсник, включенный между эмиттером второго 8 выходного транзистора и шиной первого 6 источника питания, первый 14 двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой первого 7 выходного транзистора и коллектором первого 1 входного транзистора, второй 15 двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой второго 8 выходного транзистора и коллектором второго 2 входного транзистора. В схему введены третий 16 и четвертый 17 входные транзисторы, эмиттеры которых связаны с эмиттерами первого 1 и второго 2 входных транзисторов, база третьего 16 входного транзистора соединена с базой первого 1 входного транзистора, база четвертого 17 входного транзистора соединена с базой второго 2 входного транзистора, коллекторы третьего 16 и четвертого 17 входных транзисторов связаны с шиной второго 9 источника питания, эмиттеры первого 1 и второго 2 входных транзисторов подключены к эмиттеру первого 18 дополнительного транзистора, коллектор которого соединен с объединенными вторыми выводами первого 14 и второго 15 двухполюсников коллекторной нагрузки и через четвертый 19 токостабилизирующий двухполюсник связан с шиной второго 9 источника питания, причем первый 10 выход устройства связан с базой первого 18 дополнительного транзистора через первый 20 резистор обратной связи, а второй 11 выход устройства связан с базой первого 18 дополнительного транзистора через второй 21 резистор обратной связи.

На фиг.3 в соответствии с п.2 формулы изобретения первый 10 выход устройства связан с базой первого 18 дополнительного транзистора через последовательно соединенные первый 22 дополнительный буферный усилитель и первый 20 резистор обратной связи, а второй 11 выход устройства связан с базой первого 18 дополнительного транзистора через последовательно соединенные второй 23 дополнительный буферный усилитель и второй 21 резистор обратной связи.

В качестве первого 14 и второго 15 двухполюсников коллекторной нагрузки могут применяться резисторы или прямосмещенные p-n переходы.

Вместо токостабилизирующих двухполюсников 5, 12, 13, 19 авторы рекомендуют применять классические источники тока на транзисторах, а в качестве буферных усилителей 22, 23 - обычные или двухтактные эмиттерные повторители напряжения.

Рассмотрим работу ДУ, фиг.2.

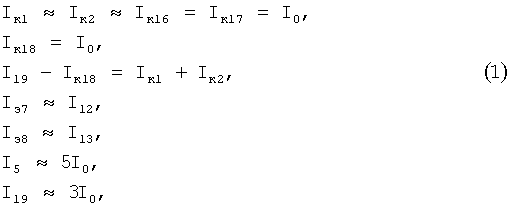

Статический режим по току предлагаемого ДУ устанавливается двухполюсниками 5, 12, 13, 19. Причем коллекторные Iкi и эмиттерные Iэi токи транзисторов:

где I0 - параметр источников опорного тока 19,5, например 1 мА.

Статическое напряжение U10 на выходах Вых.1 (10) и Вых.2 (11) ДУ при нулевом входном сигнале (uвх=0) можно найти из уравнения:

где Uэб.1=Uэб.16≈Uэб.2=Uэб.17 - напряжение «эмиттер-база» входных транзисторов 1 и 16, 2 и 17;

Iб - половина тока базы транзистора 18.

Введение транзисторов 16 и 17 обеспечивает устойчивость статического режима по петле отрицательной обратной связи «база транзистора 18 - коллектор транзистора 18 - двухполюсники 15 и 14 - базы транзисторов 7 и 8 - эмиттеры транзисторов 7 и 8 - резисторы 20 и 21 - база транзистора 18». Усиление по этой петле отрицательной обратной связи преобладает над усилением по петле положительной обратной связи «база транзистора 18 - эмиттер транзистора 18 - эмиттеры транзисторов 1 и 2 - коллекторы транзисторов 1 и 2 - эмиттеры транзисторов 7 и 8 - резисторы 20 и 21 - база транзистора 18» благодаря делению приращения тока эмиттера транзистора 18 между эмиттерами четырех транзисторов 1, 2, 16, 17.

Таким образом, при типовых, значениях токов базы транзистора 18, а также при R20=R21=500÷1000 Ом выходное синфазное напряжение ДУ, фиг.2, практически равно нулю в широком диапазоне температурных и радиационных воздействий, а также изменений напряжений питания. Это весьма существенно для согласования заявляемого ДУ с последующими функциональными узлами радиоэлектронной аппаратуры.

Таким образом, предлагаемый ДУ имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.684.419.

2. Патентная заявка WO 2009/042474, fig.5.

3. Патентная заявка WO 96/21271.

4. Патентная заявка США 2010/0019946, fig.3.

5. Патент США №6.693.489.

6. Патентная заявка WO 2005/074136, fig.1.

7. Патентная заявка США 2006/0038616, fig.1.

8. Патентная заявка США 2010/0102884, fig.2.

9. Патент США №6.285.245, fig.1.

10. Патент США №4.517.524.

11. Патент США №4.276.485, fig.1.

12. Патентная заявка США 2005/0088232.

13. Патент Франции №2409640, fig.1.

14. Патентная заявка США 2005/0110571, fig.7.

15. Патентная заявка США 2009/108882, fig.3.

16. Budyakov A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / Под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007 - С.106-110.

17. СВЧ СФ-блоки систем связи на базе полностью дифференциальных операционных усилителей / Н.Н.Прокопенко, А.С.Будяков, K.Schmalz, С.Scheytt // Проблемы разработки перспективных микро- и наноэлектронных систем - 2010. Сборник трудов /Под общ. ред. академика РАН А.Л.Стемпковского. - М.: ИППМ РАН, 2010. - С.583-586.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2012 |

|

RU2513482C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2468504C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2012 |

|

RU2481698C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2436226C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2441315C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439779C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в создании условий, при которых выходное статическое синфазное напряжение ДУ будет иметь высокую стабильность и нулевое значение при изменении параметров элементов коллекторной нагрузки и токостабилизирующего элемента эмиттерной цепи входных транзисторов в широких пределах. Дифференциальный операционный усилитель с парафазным выходом содержит с первого по четвертый входные транзисторы, с первого по четвертый стабилизирующие двухполюсники, первый и второй выходные транзисторы, первый и второй двухполюсники коллекторной нагрузки, первый дополнительный транзистор, первый и второй резисторы обратной связи. 1 з.п. ф-лы, 5 ил.

1. Дифференциальный операционный усилитель с парафазным выходом, содержащий первый (1) и второй (2) входные транзисторы, базы которых соединены со входами (3) и (4) устройства, первый (5) токостабилизирующий двухполюсник, включенный между объединенным эмиттером первого (1) и второго (2) входных транзисторов и шиной первого (6) источника питания, первый (7) и второй (8) выходные транзисторы, коллекторы которых соединены с шиной второго (9) источника питания, эмиттеры связаны с соответствующими первым (10) и вторым (11) противофазными выходами устройства, второй (12) токостабилизирующий двухполюсник, включенный между эмиттером первого (7) выходного транзистора и шиной первого (6) источника питания, третий (13) токостабилизирующий двухполюсник, включенный между эмиттером второго (8) выходного транзистора и шиной первого (6) источника питания, первый (14) двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой первого (7) выходного транзистора и коллектором первого (1) входного транзистора, второй (15) двухполюсник коллекторной нагрузки, первый вывод которого соединен с базой второго (8) выходного транзистора и коллектором второго (2) входного транзистора, отличающийся тем, что в схему введены третий (16) и четвертый (17) входные транзисторы, эмиттеры которых связаны с эмиттерами первого (1) и второго (2) входных транзисторов, база третьего (16) входного транзистора соединена с базой первого (1) входного транзистора, база четвертого (17) входного транзистора соединена с базой второго (2) входного транзистора, коллекторы третьего (16) и четвертого (17) входных транзисторов связаны с шиной второго (9) источника питания, эмиттеры первого (1) и второго (2) входных транзисторов подключены к эмиттеру первого (18) дополнительного транзистора, коллектор которого соединен с объединенными вторыми выводами первого (14) и второго (15) двухполюсников коллекторной нагрузки и через четвертый (19) токостабилизирующий двухполюсник связан с шиной второго (9) источника питания, причем первый (10) выход устройства связан с базой первого (18) дополнительного транзистора через первый (20) резистор обратной связи, а второй (11) выход устройства связан с базой первого (18) дополнительного транзистора через второй (21) резистор обратной связи.

2. Дифференциальный операционный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (10) выход устройства связан с базой первого (18) дополнительного транзистора через последовательно соединенные первый (22) дополнительный буферный усилитель и первый (20) резистор обратной связи, а второй (11) выход устройства связан с базой первого (18) дополнительного транзистора через последовательно соединенные второй (23) дополнительный буферный усилитель и второй (21) резистор обратной связи.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2007 |

|

RU2346382C1 |

| Усилитель парафазного сигнала | 1987 |

|

SU1564690A1 |

Авторы

Даты

2012-01-10—Публикация

2011-01-18—Подача