Изобретение относится к области автоматизации процессов управления и мониторинга сложных радиотехнических систем и может найти применение в широкополосных помехозащищенных системах.

Известно, что системы приема и обработки информации (СПОИ) являются одной из важнейших составных частей любых радиотехнических систем (PC) самого различного назначения и выполняют важную функцию по обеспечению требуемого уровня внутри- и межсистемного информационного взаимодействия, оказывая непосредственное влияние на основные качественные показатели функционирования всей системы. На сегодняшний день в качестве одного из наиболее распространенных типов PC, позволяющих реализовать качественно новый уровень информационного обмена за счет более высоких (по сравнению с другими PC) показателей спектральной эффективности и помехозащищенности, можно выделить весьма широко распространенные широкополосные помехозащищенные системы (ШПС). В то же время появившаяся устойчивая тенденция повышения уровня автоматизации радиофизических систем, связанная с расширением аппаратных возможностей и реализацией интеллектуальных алгоритмов цифровой обработки сигналов, приводит к созданию все более сложных структур, использующих различные методы адаптации к постоянно меняющейся помеховой обстановке. При этом особенности функционирования современных радиосредств, направленные на обеспечение своевременности доставки сигналов и сообщений в любых условиях применения и повышение надежности системы в целом, приводят к созданию внутри системы сложной информационной структуры, направленной на управление получением информации и ее обработку. Это приводит к необходимости разработки новых технологических средств, позволяющих эффективно обнаруживать неисправности и оценивать количественные показатели работоспособности системы в целом в соответствии с постоянно меняющимися требованиями к функционированию PC.

Известно устройство для диагностирования электрооборудования, описанное в [1], предоставляющее возможности функциональной диагностики непосредственно в режиме работы путем формирования входных и контроля выходных сигналов, в качестве которых могут быть как аналоговые, так и цифровые сигналы. Определение неисправностей в объекте диагностирования заключается в обнаружении конкретного элемента и обеспечивается в заявляемой системе математическим алгоритмом диагностики, содержащимся в ПЭВМ.

Недостатком устройства [1] является ограничение функциональных возможностей из-за отсутствия возможности формирования сложных сигналов с переменными параметрами. Также устройство не содержит измерителей тока, напряжения и частоты, необходимых для тестирования и контроля радиотехнических устройств в реальном времени.

Известно также устройство для поиска неисправностей, описанное в [2], позволяющее находить неисправности в динамической системе с произвольным соединением блоков в виде отклонений параметров передаточных функций блоков произвольной структуры. Работа устройства основана на использовании пробных отклонений параметров непрерывной динамической системы с номинальными характеристиками от параметров контролируемой системы. Пробное отклонение параметра, минимизирующее значение диагностического признака, указывает на наличие дефекта в этом параметре.

В качестве недостатков вышеупомянутого устройства [2] можно отметить ограничение функциональных возможностей из-за отсутствия возможности оперативно модернизировать алгоритм тестовых воздействий и отсутствие средств оперативной смены данных для тестирования предельных возможностей управляемой системы.

Наиболее близким по технической сути к заявляемому изобретению является автоматизированный ремонтный стенд, описанный в [3], принятый за прототип.

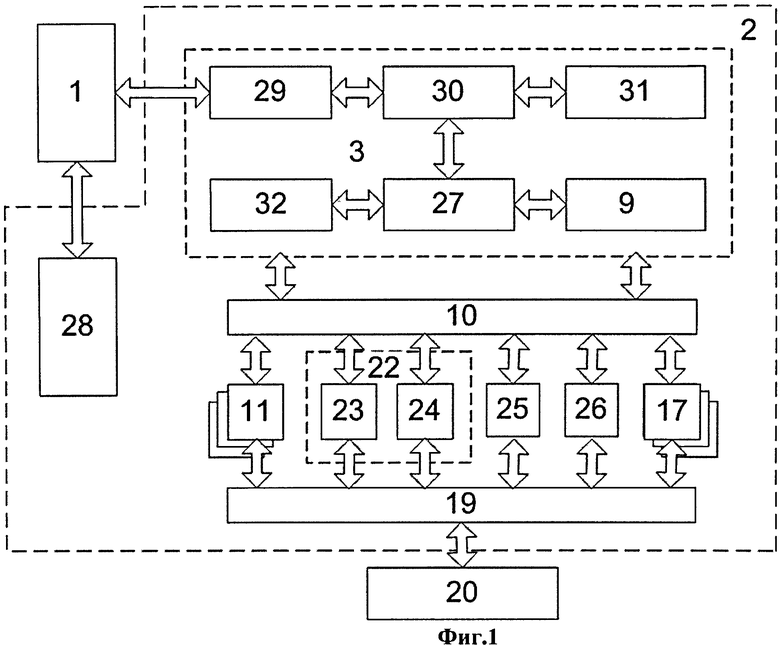

Функциональная схема устройства-прототипа приведена на фиг.1, где приняты следующие обозначения:

1 - управляющая ЭВМ;

2 - аппаратная часть;

3 - интеллектуальный контроллер;

9 - порт ввода-вывода;

10 - внутренняя локальная шина;

11 - цифровые устройства ввода-вывода;

17 - встроенный независимый блок питания с цифровым управлением;

19 - блок внешних разъемов для подключения;

20 - испытуемое устройство;

22 - аналоговый генератор;

23 - синтезатор гармонических сигналов;

24 - синтезатор импульсных сигналов;

25 - логический анализатор;

26 - блок управления реле;

27 - арбитр шины;

28 - цифровой осциллограф;

29 - шина USB;

30 - 32-разрядный процессор на кристалле NIOS-processor;

31 - оперативное запоминающее устройство;

32 - адресный порт.

Устройство-прототип состоит из управляющей ЭВМ 1 и аппаратной части 2.

В состав аппаратной части 2 входят:

- интеллектуальный контроллер 3, содержащий шину USB 29, 32-разрядный процессор на кристалле (NIOS-processor) 30, оперативное запоминающее устройство 31, арбитр шины 27, адресный порт 32 и порт ввода-вывода 9;

- внутренняя локальная шина 10;

- цифровые устройства ввода-вывода 11;

- аналоговый генератор 22, выполненный в виде синтезатора гармонических сигналов 23 и синтезатора импульсных сигналов 24;

- логический анализатор 25;

- блок управления реле 26;

- встроенный независимый блок питания 17 с цифровым управлением;

- цифровой осциллограф 28;

- блок внешних разъемов для подключения испытуемого устройства 19;

- испытуемое устройство 20.

Недостатками прототипа [3] являются ограниченные функциональные возможности, не обеспечивающие формирования сложных сигналов, необходимых для тестирования и контроля широкополосных помехозащищенных СПОИ, отсутствие управляемого генератора шума, необходимого для измерения чувствительности и помехозащищенности СПОИ, а также отстутствие измерителей тока, напряжения и частоты, необходимых для контроля функционирования радиотехнических устройств в реальном времени.

Задача, на решение которой направлено заявляемое изобретение, заключается в разработке устройства, предоставляющего возможность проверки чувствительности и помехозащищенности СПОИ (испытуемого устройства), возможность измерения напряжения и частоты контрольного аналогового сигнала, возможность формирования сложного сигнала для помехозащищенных систем со значительным уровнем априорной неопределенности параметров в целях обеспечения дополнительной информационной безопасности системы.

Достигаемый технический результат - расширение функциональных возможностей, заключающееся в следующем:

- возможность проверки чувствительности СПОИ;

- возможность проверки помехозащищенности СПОИ;

- возможность генерации заранее неизвестного сложного тестового сигнала путем введения в ЭВМ известных оператору параметров перед началом выполнения задачи;

- возможность проведения циклов непрерывного функционального и нагрузочного тестирования без присутствия оператора с записью истории тестирования в журнал событий (метод «одной кнопки»);

- возможность пошагового прохождения любого из тестовых воздействий с целью поиска неисправных узлов и блоков путем задания определенных параметров, необходимых для получения отклика на данное воздействие от необходимого блока;

- возможность выбора алгоритма управления из списка возможных действий и выбора параметров алгоритма;

- возможность корректирования управляющих воздействий или параметров прохождения без остановки основного процесса;

- возможность оперативного обновления управляющих программ функциональных узлов, содержащих высокоинтегрированную систему обработки данных, включающую высокопроизводительное х51-совместимое ядро, Flash-память и ПЛИС «ALTERA», без изменения в схемотехнике устройства;

- автоматическое изменение параметров сигнала и/или отношения сигнал/шум в процессе прохождения периодических проверок по заранее заданному алгоритму;

- автоматическая регистрация частотно-временных параметров событий с записью в журнал событий;

- автоматическая регистрация отклонений от протокола с записью в журнал событий с целью сохранения и дальнейшего анализа допущенных отклонений;

- измерение напряжений вторичных источников питания;

- измерение величины потребляемого тока с точностью 0,1 ампера;

- измерение частоты аналогового сигнала с точностью 10-7 от номинальной частоты.

Для решения поставленной задачи заявляется устройство управления и мониторинга широкополосных помехозащищенных систем, содержащее ЭВМ с программным обеспечением и аппаратную часть, связанные между собой двунаправленной связью через модуль скоростного последовательного интерфейса, при этом аппаратная часть включает:

- интеллектуальный контроллер, содержащий последовательно соединенные двунаправленными связями последовательный интерфейс цифрового ввода-вывода, многофункциональную высокоинтегрированную систему обработки данных и параллельный интерфейс цифрового ввода-вывода;

- интеллектуальный модуль, содержащий процессорный модуль управления и мониторинга, генератор тестового сигнала и порт ввода-вывода; причем процессорный модуль управления и мониторинга содержит последовательно соединенные двунаправленными связями последовательный интерфейс ввода-вывода, многофункциональный процессорный интерфейс и параллельный интерфейс ввода-вывода; генератор тестового сигнала содержит многофункциональный процессорный интерфейс, а также формирователи цифрового сигнала и цифрового шума, входы которых соединены с соответствующими выходами многофункционального процессорного интерфейса;

- блок внешних разъемов для подключения, содержащий высокочастотный интерфейс, многоканальный двунаправленный последовательный интерфейс и многоканальный двунаправленный трехстабильный параллельный интерфейс;

- измеритель напряжений, соединенный соответствующими двунаправленными связями с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга и через многоканальный двунаправленный трехстабильный параллельный интерфейс - с испытуемым устройством;

- измеритель частоты аналогового сигнала, соединенный соответствующими двунаправленными связями с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга и через многоканальный двунаправленный трехстабильный параллельный интерфейс - с испытуемым устройством;

- блок цифровых устройств ввода-вывода, соединенный соответствующими двунаправленными связями через порт ввода-вывода - с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга, а через многоканальный двунаправленный трехстабильный параллельный интерфейс - с испытуемым устройством;

- модуль доступа и хранения данных, соединенный соответствующими двунаправленными связями через внутреннюю локальную шину с параллельным интерфейсом цифрового ввода-вывода интеллектуального контроллера и с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга;

- модуль локальной визуализации, модуль считывания внешних данных и панель управления, соединенные соответствующими двунаправленными связями через порт ввода-вывода с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга;

- встроенный независимый блок питания с цифровым управлением, соединенный соответствующими двунаправленными связями через порт ввода-вывода с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга, а через устройство защиты - с испытуемым устройством;

- модуль буферных усилителей/аттенюаторов, входы которого соединены соответственно с выходами формирователей цифрового сигнала и цифрового шума, а выход через высокочастотный интерфейс подключен к испытуемому устройству;

при этом последовательный интерфейс ввода-вывода процессорного модуля управления и мониторинга соединен с генератором тестового сигнала, а соответствующими двунаправленными связями - с модулем скоростного последовательного интерфейса и с последовательным интерфейсом цифрового ввода-вывода интеллектуального контроллера; параллельный интерфейс ввода-вывода процессорного модуля управления и мониторинга двунаправленными связями через многоканальный двунаправленный последовательный интерфейс соединен с испытуемым устройством.

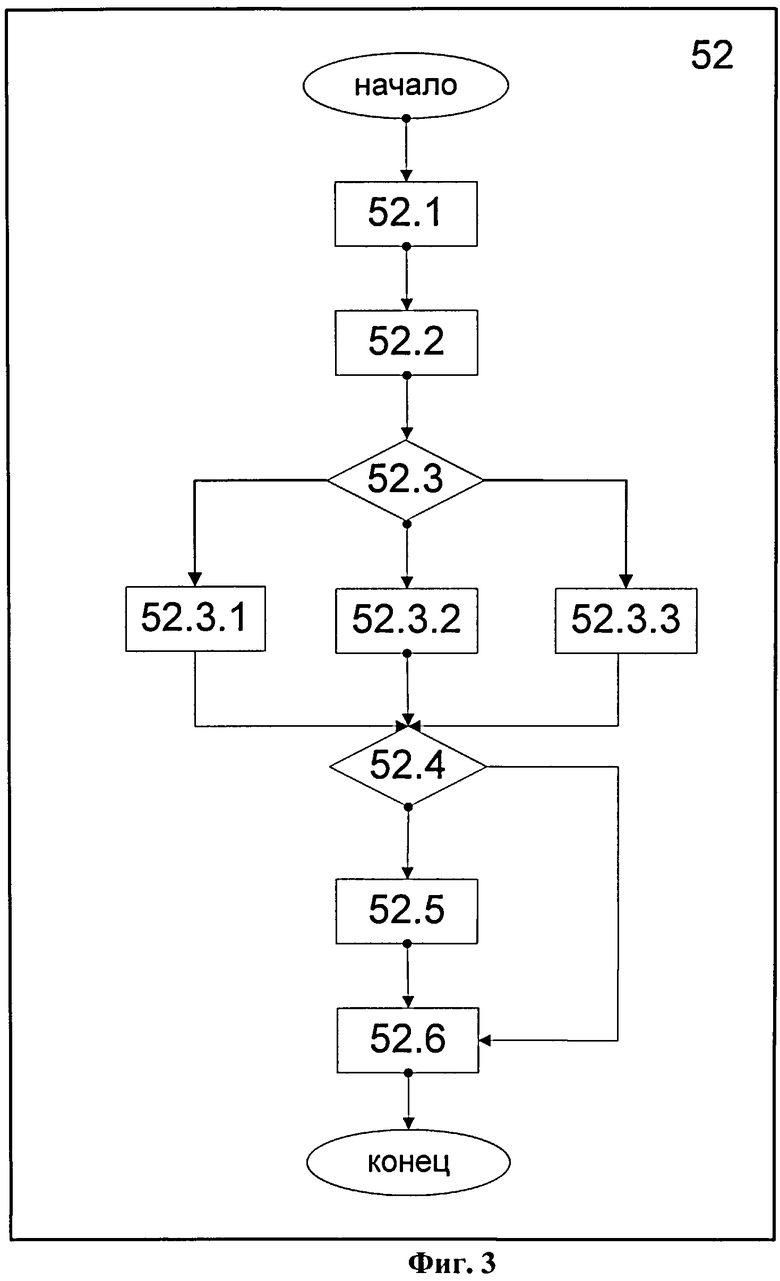

Функциональная схема заявляемого устройства приведена на фиг.2, где приняты следующие обозначения:

1 - управляющая ЭВМ;

2 - аппаратная часть;

3 - интеллектуальный контроллер:

31 - последовательный интерфейс цифрового ввода-вывода;

32 - многофункциональная высокоинтегрированная система обработки данных;

33 - параллельный интерфейс цифрового ввода-вывода;

4 - интеллектуальный модуль (ИМ);

5 - процессорный модуль управления и мониторинга:

51 - последовательный интерфейс ввода-вывода;

52 - многофункциональный процессорный интерфейс;

53 - параллельный интерфейс ввода-вывода;

6 - модуль доступа и хранения данных;

7 - модуль буферных усилителей/аттенюаторов;

8 - модуль локальной визуализации;

9 - порт ввода-вывода;

10 - внутренняя локальная шина;

11 - блок цифровых устройств ввода-вывода;

12 - генератор тестового сигнала:

121 - многофункциональный процессорный интерфейс;

122 - формирователь цифрового сигнала;

123 - формирователь цифрового шума;

13 - модуль считывания внешних данных;

14 - измеритель напряжений;

15 - измеритель частоты аналогового сигнала;

16 - устройство защиты;

17 - встроенный независимый блок питания с цифровым управлением;

18 - модуль скоростного последовательного интерфейса;

19 - блок внешних разъемов для подключения:

191 - высокочастотный интерфейс;

192 - многоканальный двунаправленный последовательный интерфейс;

193 - многоканальный двунаправленный трехстабильный параллельный интерфейс;

20 - испытуемое устройство;

21 - панель управления.

Заявляемое устройство содержит управляющую ЭВМ 1 и аппаратную часть 2, связанные между собой с помощью модуля скоростного последовательного интерфейса 18.

В состав аппаратной части 2 устройства входят:

- интеллектуальный контроллер 3, предназначенный для обработки команд управления, ассоциированных с конкретным устройством протоколов и/или алгоритмов, содержащий последовательно соединенные двунаправленными связями функциональные модули: последовательный интерфейс цифрового ввода-вывода 31, второй вход-выход которого является первым входом-выходом интеллектуального контроллера 3, многофункциональную высокоинтегрированную систему обработки данных 32 и параллельный интерфейс цифрового ввода-вывода 33, второй вход-выход которого является вторым входом-выходом интеллектуального контроллера 3;

- интеллектуальный модуль 4, осуществляющий обмен информацией с ЭВМ через модуль скоростного последовательного интерфейса 18 с целью формирования и передачи необходимых тестовых воздействий и получения ответных сигналов от испытуемого устройства 20 и включающий в себя процессорный модуль управления и мониторинга 5, генератор тестового сигнала 12 и порт ввода-вывода 9;

- модуль доступа и хранения данных 6, предназначенный для хранения передаваемых и/или принимаемых данных, вход-выход которого через внутреннюю локальную шину 10 соединен со вторым выходом-выходом интеллектуального контроллера 3 и с восьмым выходом-входом процессорного модуля управления и мониторинга 5;

- модуль буферных усилителей/аттенюаторов 7, предназначенный для подачи на испытуемое устройство аналогового сигнала переменной амплитуды и фазы в смеси с шумом, сформированного на основе установок, полученных от генератора тестового сигнала 12;

- модуль локальной визуализации 8, своим входом-выходом соединенный с третьим выходом-входом порта ввода-вывода 9 и предназначенный для визуализации контрольной информации о полученных в ходе тестирования результатах при необходимости автономной работы без управляющей ЭВМ;

- модуль считывания внешних данных 13, своим входом-выходом соединенный с четвертым выходом-входом порта ввода-вывода 9 и предназначенный для подключения и считывания внешних энергонезависимых данных, которые могут использоваться для задания параметров испытаний и параметров формирования тестового сигнала;

- устройство защиты 16, предназначенное для отключения аппаратного интерфейса и испытуемого устройства от источников питания в случае превышения допустимого порога значений напряжений;

- встроенный независимый блок питания с цифровым управлением 17, первый вход-выход которого соединен с шестым выходом-входом порта ввода-вывода 9, а второй вход-выход через устройство защиты 16 соединен с четвертым выходом-входом испытуемого устройства 20;

- блок внешних разъемов для подключения 19, содержащий высокочастотный интерфейс 191, многоканальный двунаправленный последовательный интерфейс 192 и многоканальный двунаправленный трехстабильный параллельный интерфейс 193;

- панель управления 21, своим входом-выходом соединенная с пятым выходом-входом порта ввода-вывода 9 и предназначенная для автономной работы устройства без управляющей ЭВМ 1.

При этом генератор тестового сигнала 12 содержит многофункциональный процессорный интерфейс 121, вход которого является входом генератора тестового сигнала 12, формирователь цифрового сигнала 122 и формирователь цифрового шума 123, выходы которых являются соответственно первым и вторым выходами генератора тестового сигнала. При этом первый и второй выходы многофункционального процессорного интерфейса 121 через соответствующие формирователи цифрового сигнала 122 и цифрового шума 123 соединены соответственно с первым и вторым входами модуля буферных усилителей/аттенюаторов 7, выход которого через высокочастотный интерфейс 191 соединен с первым входом испытуемого устройства 20.

Процессорный модуль управления и мониторинга 5 содержит: последовательно соединенные между собой двунаправленными связями функциональные модули: последовательный интерфейс ввода-вывода 51, многофункциональный процессорный интерфейс 52 и параллельный интерфейс ввода-вывода 53. Второй выход последовательного интерфейса ввода-вывода 51, являющийся вторым выходом процессорного модуля управления и мониторинга 5, соединен с входом генератора тестового сигнала 12; третий вход-выход последовательного интерфейса ввода-вывода 51, являющийся первым входом-выходом процессорного модуля управления и мониторинга 5, соединен со вторым выходом-входом модуля скоростного последовательного интерфейса 18, четвертый вход-выход последовательного интерфейса ввода-вывода 51, являющийся третьим входом-выходом процессорного модуля управления и мониторинга 5, соединен со вторым выходом-входом последовательного интерфейса цифрового ввода-вывода 31. Второй вход-выход параллельного интерфейса ввода-вывода 53, являющийся четвертым входом-выходом процессорного модуля управления и мониторинга 5, через многоканальный двунаправленный последовательный интерфейс 192 соединен со вторым выходом-входом испытуемого устройства; третий вход-выход параллельного интерфейса ввода-вывода 53, являющийся пятым входом-выходом процессорного модуля управления и мониторинга 5, через измеритель напряжения 14 соединен с первым выходом-входом многоканального двунаправленного трехстабильного параллельного интерфейса 193; четвертый вход-выход параллельного интерфейса ввода-вывода 53, являющийся шестым входом-выходом процессорного модуля управления и мониторинга 5, через измеритель частоты аналогового сигнала 15 соединен со вторым выходом-входом многоканального двунаправленного трехстабильного параллельного интерфейса 193; пятый вход-выход параллельного интерфейса ввода-вывода 53, являющийся седьмым входом-выходом процессорного модуля управления и мониторинга 5, соединен со вторым выходом-входом порта ввода-вывода 9, первый вход-выход которого через блок цифровых устройств ввода-вывода 11 соединен с третьим выходом-входом многоканального двунаправленного трехстабильного параллельного интерфейса 193, четвертый вход-выход которого соединен с третьим выходом-входом испытуемого устройства 20; шестой вход-выход параллельного интерфейса ввода-вывода 53, являющийся восьмым входом-выходом процессорного модуля управления и мониторинга 5, соединен с третьим выходом-входом внутренней локальной шины 10.

Заявляемое устройство работает следующим образом.

Управляющая ЭВМ 1 через модуль скоростного последовательного интерфейса 18 передает на процессорный модуль управления и мониторинга 5 стартовые данные, необходимые для конфигурации тестовых параметров и включения необходимых для выбранного режима интерфейсов. Через последовательный интерфейс ввода-вывода 51 управляющие воздействия от управляющей ЭВМ 1 подаются на интеллектуальный контроллер 3, генератор текстового сигнала 12 и многофункциональный процессорный интерфейс 52, выполненный на основе встроенного 32-разрядного процессора на кристалле NIOS, который формирует команды управления организацией маршрутизации интерфейсов и подает их на параллельный интерфейс ввода-вывода 53, который служит для формирования и передачи управляющего воздействия от многофункционального процессорного интерфейса 52 к порту ввода-вывода 9, измерителю напряжения 14 и измерителю частоты аналогового сигнала 15.

Далее, в зависимости от выбранного режима, процессорный модуль управления и мониторинга 5 формирует команды, обеспечивающие выборку данных тестовых воздействий либо из модуля считывания внешних данных 13, либо из модуля доступа и хранения данных 6. Также процессорный модуль управления и мониторинга 5 формирует команды управления для испытуемого устройства 20, генератора тестового сигнала 12, измерителя напряжений 14 и измерителя частоты аналогового сигнала 15. В соответствии с протоколом тестовых воздействий интеллектуальный контроллер 3 формирует непрерывный поток выходных данных (согласно выбранному протоколу) для передачи на испытуемое устройство 20 и обеспечивает обработку потока входных данных (согласно тому же выбранному протоколу), принимаемых от испытуемого устройства 20.

Через последовательный интерфейс цифрового ввода-вывода 31 интеллектуальный контроллер 3 осуществляет обмен данными (согласно другому протоколу, отличному от первого) с процессорным модулем управления и мониторинга 5.

Многофункциональная высокоинтегрированная система обработки данных 32, включающая высокопроизводительное х51-совместимое ядро и Flash-память, осуществляет формирование периодических команд управления и контроля времени, прошедшего между передачей команды от устройства и поступлением команды от испытуемого устройства 20; далее обработанные данные из интеллектуального контроллера 3 посредством внутренней локальной шины 10 подаются в модуль доступа и хранения данных 6.

Кроме того, результаты обработки из интеллектуального контроллера 3 передаются в процессорный модуль управления и мониторинга 5 для выдачи в управляющую ЭВМ 1. Одновременно процессорный модуль управления и мониторинга 5 принимает данные от измерителя напряжений 14 и измерителя частоты аналогового сигнала 15 для выдачи в управляющую ЭВМ 1. Кроме того, процессорный модуль управления и мониторинга 5 обменивается данными непосредственно с испытуемым устройством 20 по двунаправленному последовательному интерфейсу 192, а полученные результаты передает в управляющую ЭВМ 1.

Для проверки чувствительности на испытуемое устройство 20 подается тестовый сигнал определенной величины, формируемый генератором тестового сигнала 12, в котором имеется многофункциональный процессорный интерфейс 121 на основе встроенного 32-разрядного процессора на кристалле NIOS, выдающий команды управления формирователями цифрового сигнала 122 и цифрового шума 123, на основании команд, полученных от процессорного модуля управления и мониторинга 5. Модуль буферных усилителей-аттенюаторов 7 служит для преобразования цифровых сигнала и шума в аналоговый вид для подачи через высокочастотный интерфейс 191 на испытуемое устройство 20.

Далее управляющая ЭВМ 1 формирует команды управления, с тем чтобы на каждом шаге цикла измерения уровень сигнала уменьшался на заранее заданную величину. Оператор имеет возможность выбирать начальный уровень сигнала.

Для проверки помехозащищенности на испытуемое устройство 20 подается тестовый сигнал определенной величины, формируемый генератором тестового сигнала 12 (аналогично описанному выше); далее управляющая ЭВМ 1 формирует команды управления, с тем чтобы на каждом шаге цикла измерения уровень отношения сигнал/шум уменьшался на заранее заданную величину. Оператор имеет возможность выбирать начальный уровень сигнала и шума.

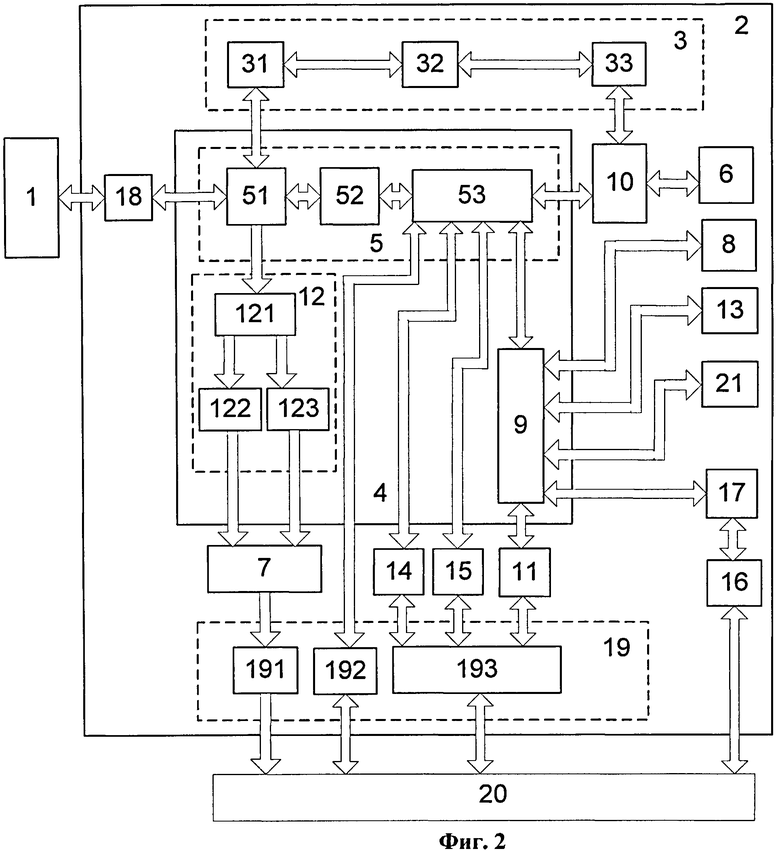

Укрупненный алгоритм работы многофункционального процессорного интерфейса 52 поясняется с помощью фиг.3.

При включении в блоке 52.1 происходят инициализация устройства и проверка наличия связи с управляющей ЭВМ 1. Далее в блоке 52.2 по команде оператора происходит выбор устройства для тестирования из списка всех поддерживаемых устройств и выбор режима работы: «пошаговая настройка» или «автоматическая проверка».

В блоке 52.3 по команде оператора происходит выбор загрузки тестовых параметров из следующих возможностей:

52.3.1 - автоматическая конфигурация (по умолчанию);

52.3.2 - загрузка установок некоторой предыдущей сессии (хранимых в модуле доступа и хранения данных 6 и/или в модуле считывания внешних данных 13);

52.3.3 - ручной ввод.

Если в блоке 52.4 была необходимость изменения предшествующих параметров конфигурации, в блоке 52.5 может выполняться динамическое конфигурирование программируемой логики процессорного модуля управления и мониторинга 5 и генератора текстового сигнала 12 из интеллектуального контроллера 3, а если нет необходимости изменения предшествующих параметров конфигурации, то выполняется переход к блоку 52.6.

В блоке 52.6 выполняется необходимый алгоритм воздействия в соответствии с выбранным режимом работы и испытуемым устройством 20 до момента окончания проверки, либо до вмешательства оператора.

Периодическая команда управления, состоящая из последовательности кодов и формируемая в автоматическом режиме, передается через модуль скоростного последовательного интерфейса 18 в интеллектуальный модуль 4 для управления и/или корректирования применяемого воздействия. Каждая периодическая команда формируется либо на основе заранее известного алгоритма функционирования испытуемого устройства, либо при необходимости может формироваться по указанию оператора. Некоторые комбинации команд управления, в соответствии с одним или несколькими вариантами осуществления управляющего алгоритма для испытуемого устройства, могут совершаться в произвольном порядке и/или одновременно с другими комбинациями. Периодические команды управления могут быть приостановлены при необходимости применения коррекций управления в ответ на принятые периодические сигналы. Очередная периодическая команда управления может быть либо ответной на соответствующий принятый сигнал от испытуемого устройства 20, либо при необходимости формироваться по указанию оператора.

При тестовом обмене с испытуемым устройством 20 заявляемое устройство контролирует правильность каждой поступающей команды по следующим критериям:

- время, прошедшее между передачей команды от заявляемого устройства и поступлением команды от испытуемого устройства 20;

- правильность всех параметров принятой команды;

- наличие сигналов, ожидаемых согласно алгоритму проверки.

Измеряются время проверки и количество безошибочных сеансов. Документируются успешные и неуспешные сеансы с привязкой к времени, причем данные могут одновременно храниться в модуле доступа и хранения данных 6 и в управляющей ЭВМ 1.

Интеллектуальный контроллер 3 может быть сконфигурирован на базе специализированного цифрового элемента, включающего высокопроизводительное х51-совместимое ядро и Flash-память [6, 9].

Интеллектуальный модуль 4 может быть сконфигурирован на базе ПЛИС фирмы «ALTERA», содержащей встроенный 32-разрядный процессор на кристалле [6, 9].

Модуль доступа и хранения данных 6 может быть выполнен на базе энергозависимых и/или энергонезависимых запоминающих устройств [4-7].

Модуль буферных усилителей/аттенюаторов 7, порт ввода-вывода 9, цифровые устройства ввода-вывода 11, модуль считывания внешних данных 13 могут быть выполнены на базе цифровых логических элементов [4].

Модуль визуализации 8 может быть выполнен на базе светодиодных и сегментных индикаторов [10].

Измеритель напряжений 14 и измеритель частоты аналогового сигнала 15 могут быть выполнены из специализированных цифровых элементов [4-6].

Устройство защиты 16 может быть выполнено из датчиков тока и специализированных цифровых элементов (микросхем), предназначенных для защиты от перегрузки по току [4, 7].

Встроенный независимый блок питания с цифровым управлением 17 может быть выполнен из специализированных цифровых элементов, позволяющих формировать из входного напряжения требуемое выходное напряжение [4, 5].

Скоростной последовательный интерфейс 18 может быть выполнен как один из стандартных стыков RS 232/422/485 или USB на базе специализированных цифровых элементов [5, 6].

Панель управления 21 может быть выполнена из коммутационных элементов с использованием индикаторов и светодиодов [10].

Таким образом, введение в предлагаемом устройстве новых блоков и связей позволяет обеспечить технический результат, заключающийся в расширении функциональных возможностей устройства, предназначенного для управления и мониторинга широкополосных помехозащищенных систем. Кроме того, наличие интеллектуального контроллера, сконфигурированного на базе многофункциональной высокоинтегрированной системы обработки данных, включающей высокопроизводительное х51-совместимое ядро и Flash-память, и интеллектуального модуля, сконфигурированного на базе ПЛИС фирмы «ALTERA», содержащей встроенный 32-разрядный процессор на кристалле, позволяет вести обработку данных в разных временных масштабах в соответствии с целевой функцией испытуемого устройства.

Источники информации

1. Патент РФ на изобретение №2430406 «Автоматизированная система диагностирования цифровых устройств». / Алешин В.Е., Спасский Н.В., Чакчир С.Я. - 2009.

2. Патент РФ на изобретение №2429518 «Способ поиска неисправностей динамического блока в непрерывной системе». / Шалобанов С.С. - 2010.

3. Патент РФ на изобретение №2421787 «Автоматизированный ремонтный стенд (БАРС)». / Боровик М.М., Криницкий Г.В., Жданов В.Е., Надельсон A.M. - 2009.

4. http://www.analog.com/ru/allProducts.html - радиоэлектронные Компоненты компании "Analog Devices"

5. http://russia.maxim-ic.com/products/ - радиоэлектронные Компоненты компании "MAXIM"

6. http://www.altera.ru/cgi-bin/go?38 - радиоэлектронные Компоненты компании "ALTERA"

7. http://www.ti.com/ww/ru/ - радиоэлектронные Компоненты компании "Texas Instruments"

8. http://www.murata.com/ - радиоэлектронные Компоненты компании "Murata Manufacturing Company, Ltd."

9. http://www.atmel.com/products/ - радиоэлектронные Компоненты компании "ATMEL"

http://www.silabs.com/products/pages/default.aspx - радиоэлектронные Компоненты компании "Silicon Labs"

10. http://www.kingbright.com/

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПЭВМ И ГАРАНТИРОВАННОГО ПРЕДОТВРАЩЕНИЯ ПОХИЩЕНИЯ ИНФОРМАЦИИ С ЕЁ ЖЕСТКОГО ДИСКА | 2017 |

|

RU2689193C2 |

| АВТОМАТИЗИРОВАННЫЙ РЕМОНТНЫЙ СТЕНД (БАРС) | 2009 |

|

RU2421787C2 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2008 |

|

RU2399088C2 |

| ПЕРЕНОСНОЙ ПРОГРАММНО-ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2007 |

|

RU2363975C2 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2023 |

|

RU2815706C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО КОНТРОЛЯ КОТЕЛЬНОЙ | 2017 |

|

RU2656670C1 |

| Многофункциональный модульный программно-аппаратный комплекс | 2023 |

|

RU2803959C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| ИНТЕГРИРОВАННАЯ МНОГОФУНКЦИОНАЛЬНАЯ СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ | 2004 |

|

RU2281614C1 |

Изобретение относится к области автоматизации процессов управления и мониторинга сложных радиотехнических систем и может найти применение в широкополосных помехозащищенных системах. Техническим результатом является расширение функциональных возможностей, заключающихся в возможности проверки чувствительности и помехозащищенности СПОИ (системы приема и обработки информации). Для достижения указанного технического результата устройство содержит управляющую ЭВМ (1) и аппаратную часть (2), включающую интеллектуальный контроллер (3), содержащий последовательный интерфейс цифрового ввода-вывода (31), многофункциональную высокоинтегрированную систему обработки данных (32), параллельный интерфейс цифрового ввода-вывода (33), интеллектуальный модуль (4), содержащий процессорный модуль управления и мониторинга (5), порт ввода-вывода (9) и генератор тестового сигнала (12), модуль доступа и хранения данных (6), модуль буферных усилителей/аттенюаторов (7), модуль локальной визуализации (8), внутреннюю локальную шину (10), блок цифровых устройств ввода-вывода (11), модуль считывания внешних данных (13), измеритель напряжений (14), измеритель частоты аналогового сигнала (15), устройство защиты (16), встроенный независимый блок питания с цифровым управлением (17), модуль скоростного последовательного интерфейса (18), блок внешних разъемов для подключения (19), испытуемое устройство (20) и панель управления (21). 3 ил.

Устройство управления и мониторинга широкополосных помехозащищенных систем, характеризующееся тем, что оно содержит ЭВМ с программным обеспечением и аппаратную часть, связанные между собой двунаправленной связью через модуль скоростного последовательного интерфейса, при этом аппаратная часть включает:

интеллектуальный контроллер, содержащий последовательно соединенные двунаправленными связями последовательный интерфейс цифрового ввода-вывода, многофункциональную высокоинтегрированную систему обработки данных и параллельный интерфейс цифрового ввода-вывода;

интеллектуальный модуль, содержащий процессорный модуль управления и мониторинга, генератор тестового сигнала и порт ввода-вывода; причем процессорный модуль управления и мониторинга содержит последовательно соединенные двунаправленными связями последовательный интерфейс ввода-вывода, многофункциональный процессорный интерфейс и параллельный интерфейс ввода-вывода; генератор тестового сигнала содержит многофункциональный процессорный интерфейс, а также формирователи цифрового сигнала и цифрового шума, входы которых соединены с соответствующими выходами многофункционального процессорного интерфейса;

блок внешних разъемов для подключения, содержащий высокочастотный интерфейс, многоканальный двунаправленный последовательный интерфейс и многоканальный двунаправленный трехстабильный параллельный интерфейс;

измеритель напряжений, соединенный соответствующими двунаправленными связями: с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга, и через многоканальный двунаправленный трехстабильный параллельный интерфейс - с испытуемым устройством;

измеритель частоты аналогового сигнала, соединенный соответствующими двунаправленными связями: с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга, и через многоканальный двунаправленный трехстабильный параллельный интерфейс - с испытуемым устройством;

блок цифровых устройств ввода-вывода, соединенный соответствующими двунаправленными связями: через порт ввода-вывода - с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга, а через многоканальный двунаправленный трехстабильный параллельный интерфейс - с испытуемым устройством;

модуль доступа и хранения данных, соединенный соответствующими двунаправленными связями через внутреннюю локальную шину: с параллельным интерфейсом цифрового ввода-вывода интеллектуального контроллера и с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга;

модуль локальной визуализации, модуль считывания внешних данных и панель управления, соединенные соответствующими двунаправленными связями через порт ввода-вывода с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга;

встроенный независимый блок питания с цифровым управлением, соединенный соответствующими двунаправленными связями: через порт ввода-вывода - с параллельным интерфейсом ввода-вывода процессорного модуля управления и мониторинга, а через устройство защиты - с испытуемым устройством;

модуль буферных усилителей/аттенюаторов, входы которого соединены соответственно с выходами формирователей цифрового сигнала и цифрового шума, а выход - через высокочастотный интерфейс подключен к испытуемому устройству;

при этом, последовательный интерфейс ввода-вывода процессорного модуля управления и мониторинга соединен с генератором тестового сигнала, а соответствующими двунаправленными связями - с модулем скоростного последовательного интерфейса и с последовательным интерфейсом цифрового ввода-вывода интеллектуального контроллера; параллельный интерфейс ввода-вывода процессорного модуля управления и мониторинга двунаправленными связями через многоканальный двунаправленный последовательный интерфейс соединен с испытуемым устройством.

| АВТОМАТИЗИРОВАННЫЙ РЕМОНТНЫЙ СТЕНД (БАРС) | 2009 |

|

RU2421787C2 |

| СПОСОБ ВЫБОРА ПОСТАВЩИКА УСЛУГИ ПЕРЕДАЧИ ДАННЫХ НА ПОЛЕВОМ УСТРОЙСТВЕ | 2006 |

|

RU2405210C2 |

| ОПТИМИЗИРОВАННОЕ РЕГУЛИРОВАНИЕ ЗАГРЯЗНЕНИЯ ВОЗДУШНОЙ СРЕДЫ | 2005 |

|

RU2381540C2 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

Авторы

Даты

2013-03-20—Публикация

2012-04-12—Подача