Изобретение относится к области вычислительной техники и может быть использовано для цифровой обработки сигналов, обработки данных и управления в радиолокационных комплексах и информационно-управляющих системах.

Из уровня техники известна электронная вычислительная машина (Патент РФ №272317, опубликован 16.08.2004, МПК G06F 15/0), содержащая центральный процессор, постоянное энергонезависимое запоминающее устройство, перепрограммируемое энергонезависимое запоминающее устройство, энергозависимое запоминающее устройство и устройство ввода-вывода данных, входы-выводы которых соединены двунаправленной шиной.

К недостаткам данной электронной вычислительной машины можно отнести то, что она не обеспечивает ввод аналоговых сигналов и не содержит специализированных устройств цифровой обработки сигналов.

Известна также вычислительная система (Патент РФ №2187148, опубликован 10.08.2002, МПК G06F 15/16), содержащая цифровые вычислительные машины, входы которых соединены с выходами первого коммутатора, входы первого коммутатора соединены с выходами процессоров цифровой обработки сигналов, входы процессоров цифровой обработки сигналов соединены с выходами второго коммутатора. Входы второго коммутатора подключены к выходам аналого-цифровых преобразователей низкочастотного канала и через дециматоры, обеспечивающие одинаковую частотную полосу на всех входах второго коммутатора, к выходам аналого-цифровых преобразователей высокочастотного канала. Цифровые вычислительные машины соединены двунаправленной информационно-управляющей магистралью с первым коммутатором и пультом оператора, содержащим монитор.

Данная вычислительная система является многоканальной, имеет дублированные каналы, информационно-управляющие магистрали, позволяет динамически изменять конфигурацию системы, что повышает ее надежность. Однако для единичного канала вычислительная система, использующая двунаправленные параллельные шины, не имеет достаточной пропускной способности для обработки широкополосных сигналов и не позволяет программно менять характеристики тракта аналого-цифровой обработки принимаемого сигнала.

Наиболее близким техническим решением является управляющий аппаратно-программный комплекс для обработки радиолокационной информации (Патент РФ №2222028, опубликован 20.01.2004, МПК G01S 13/56, G06F 15/16, H04J 9/00), выбранный в качестве прототипа.

Управляющий аппаратно-программный комплекс состоит из двух блоков: блока обработки аналоговой радиолокационной информации (РЛИ) и блока обработки вторичной РЛИ. Каждый блок выполнен на базе электронной вычислительной машины (ЭВМ). Блоки соединены локальной вычислительной сетью. Блок обработки аналоговой РЛИ содержит два канала аналого-цифровых преобразователей (АЦП) и арифметический акселератор. Блок обработки вторичной РЛИ содержит адаптер индикатора кругового обзора и адаптер мультиплексного канала, подключенный к внешней аппаратуре передачи данных.

Недостатками управляющего аппаратно-программного комплекса являются обработка принимаемого аналогового радиолокационного сигнала на видеочастоте, использование на два приемных канала одного арифметического акселератора, а не специализированного программируемого цифрового процессора обработки сигналов на каждый приемный канал и слабая функциональная связь блоков комплекса через локальную вычислительную сеть.

Таким образом, известные вычислительные системы не обладают необходимыми характеристиками по обработке широкополосных радиолокационных сигналов.

Техническим результатом предлагаемого изобретения является расширение функциональных возможностей и повышение производительности многофункционального вычислительного комплекса для обработки радиолокационных сигналов.

Технический результат достигается аналого-цифровым преобразованием сигнала на промежуточной частоте с цифровым разложением сигналов на квадратурные составляющие и цифровым переносом спектра сигнала на видеочастоту при объединении в едином функциональном комплексе и конструктивном блоке устройства синхронизации, усилителя промежуточной частоты, аналого-цифрового преобразователя, программируемых цифровых процессоров обработки сигналов, центрального процессора обработки данных, графического контроллера и интерфейсных устройств ввода-вывода, обеспечивающих обмен данными комплекса с внешними устройствами.

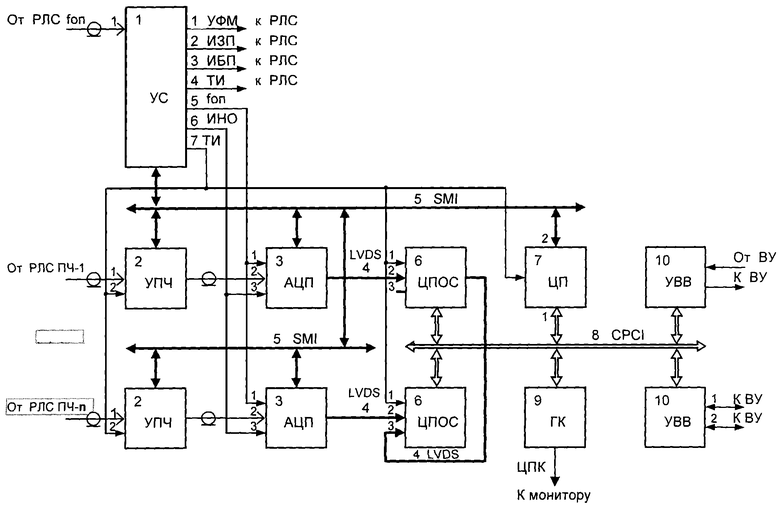

Структурная схема многофункционального вычислительного комплекса для обработки радиолокационных сигналов представлена на чертеже, где:

1 - устройство синхронизации (УС);

2 - усилитель промежуточной частоты (УПЧ);

3 - устройство аналого-цифрового преобразования (УАЦП);

4 - высокоскоростной последовательный интерфейс (LVDS);

5 - последовательный управляющий интерфейс (SMI);

6 - цифровой процессор обработки сигналов (ЦПОС);

7 - центральный процессор (ЦП);

8 - шина системной магистрали (CPCI);

9 - графический контроллер (ГК);

10 - устройство ввода-вывода (УВВ).

Многофункциональный вычислительный комплекс для обработки радиолокационных сигналов представляет собой моноблочное устройство с модульной структурой. Устройство содержит следующие модули: устройство синхронизации (УС) 1, один или несколько усилителей промежуточной частоты (УПЧ) 2, одно или несколько устройств аналого-цифрового преобразования (УАЦП) 3, один или несколько программируемых цифровых процессоров обработки сигналов (ЦПОС) 6, центральный процессор (ЦП) 7, графический контроллер (ГК) 9 и одно или несколько устройств ввода-вывода (УВВ) 10.

Центральный процессор ЦП 7 является основным вычислительным устройством и обеспечивает выполнение универсальных программ обработки данных. Центральный процессор ЦП 7 представляет собой одноплатную микро-ЭВМ и включает микропроцессор, устройство синхронизации, постоянное энергонезависимое запоминающее устройство, перепрограммируемое энергонезависимое запоминающее устройство, энергозависимое оперативное запоминающее устройство (ОЗУ), буферное устройство шины Compact PCI и устройство управления интерфейса SMI, реализованные на основе микросхем.

Микропроцессор центрального процессора (ЦП) 7 осуществляет выполнение команд основной программы.

Постоянное энергонезависимое запоминающее устройство обеспечивает однократную запись информации при изготовлении ЦП и дальнейшее ее хранение без возможности изменения.

Перепрограммируемое энергонезависимое запоминающее устройство выполнено с возможностью многократной записи информации при работе ЦП и хранения ее при выключенном состоянии ЦП.

Энергозависимое оперативное запоминающее устройство (ОЗУ) обеспечивает многократную запись и чтение информации при выполнении программы ЦП.

Буферное устройство обеспечивает согласование электрических сигналов устройств, входящих в состав центрального процессора, и шины Compact PCI системной магистрали 8.

Устройство управления интерфейса SMI обеспечивает формирование структуры данных, параллельно-последовательное преобразование и передачу сообщений в соответствии с протоколом интерфейса SMI.

Устройство синхронизации центрального процессора 7 формирует сигналы синхронизации для тактирования вычислительного ядра и внешней шины микропроцессора, а также шины Compact PCI системной магистрали 8 (33 МГц) и шины интерфейса SMI 5 (2,5 МГц).

Шина системной магистрали (CPCI) 8 является системным магистральным параллельным интерфейсом Compact PCI (Compact PCI Specification PICMG 2.0 D3.0 September 24, 1999). Интерфейс Compact PCI имеет тактовую частоту 33 МГц и 32 разрядную шину данных, что обеспечивает пиковую производительность передачи данных в 132 Мбайт/с. Интерфейс Compact PCI использует механический конструктив для промышленных магистрально-модульных систем с возможностью подключения до 8 модулей на основе плат размером 160×100 мм, соответствующих формату 3U «Евромеханика». Шина системной магистрали 8 обеспечивает сопряжение центрального процессора 7 с вычислительными и интерфейсными модулями вычислительного комплекса: ЦПОС 6, ГК 9 и УВВ 10.

Последовательный управляющий интерфейс (SMI) 5 является последовательным двунаправленным магистральным управляющим интерфейсом SMI (Serial Management Interface Std IEEE 802.3u). Интерфейс SMI выполнен в виде трехпроводной шины, включающей цепи синхронизации mdc, ввода-вывода данных mdio и общую цепь gnd. Скорость передачи данных интерфейса SMI до 2,5 Мбит/с.Интерфейс SMI используется для управления модулями аналого-цифровой части вычислительного комплекса, включающей модули УС 1, УПЧ 2 и УАЦП 3, для которых не требуется высокая производительность управляющего интерфейса, однако важным является требование электромагнитной совместимости цифровых и аналоговых устройств.

Устройство синхронизации (УС) 1 является специализированным устройством синхронизации и управления (Патент РФ №2304788, опубликован 20.08.2007), обеспечивающим формирование сигналов, синхронизирующих работу блоков высокочастотного приемника и передатчика РЛС и модулей вычислительного комплекса.

Устройство синхронизации 1 содержит высокочастотное устройство синхронизации, низкочастотное устройство синхронизации, высокочастотное буферное устройство и низкочастотное буферное устройство. Управление работой устройства синхронизации 1 производится по магистрали последовательного управляющего интерфейса SMI 5.

Тактирование устройства синхронизации 1 осуществляется сигналом опорной частоты fоп с частотой 56 МГц, поступающим с задающего генератора РЛС на вход высокочастотного устройства синхронизации. Высокочастотное устройство синхронизации формирует и через высокочастотное буферное устройство выдает на выходы устройства синхронизации 1 следующие сигналы: сигнал опорной частоты fоп и импульс начала отсчета (ИНО), соответствующий первому обрабатываемому элементу дальности, для модулей вычислительного комплекса; сигнал управления фазовым манипулятором (УФМ) РЛС, импульс запуска передатчика (ИЗП) РЛС и импульс бланкирования приемника (ИБП) РЛС.

Низкочастотное устройство синхронизации формирует и через низкочастотное буферное устройство выдает на выходы устройства синхронизации 1 тактовые импульсы (ТИ) для синхронизации модулей вычислительного комплекса и блоков РЛС. Низкочастотное устройство синхронизации также содержит устройство сопряжении с интерфейсом SMI, осуществляющее прием и преобразование последовательного сообщения интерфейса SMI в сигналы управления устройством синхронизации 1 и формирование из сигналов состояния устройства синхронизации 1 полей данных передаваемых сообщений интерфейса последовательного SMI.

Усилитель промежуточной частоты (УПЧ) 2 (Патент РФ №2291556, опубликован 10.01.2007) обеспечивает программно управляемое усиление сигнала промежуточной частоты, поступающего с СВЧ приемника РЛС, для сопряжения частотных характеристик приемника со спектром принимаемых сигналов.

Управление работой усилителя промежуточной частоты 2 производится по магистрали последовательного управляющего интерфейса SMI 5. Команды, поступающие в сообщениях, принимаемых по интерфейсу SMI, управляют коэффициентом усиления и шириной полосы пропускания усилителя промежуточной частоты 2.

Устройство аналого-цифрового преобразования (УАЦП) 3 (Патент РФ №2290662, опубликован 27.12.2006) осуществляет аналого-цифровое преобразование и первичную цифровую обработку сигнала промежуточной частоты, поступающего с СВЧ приемника РЛС.

Устройство аналого-цифрового преобразования 3 включает: формирователь частоты дискретизации, формирователь дифференциального сигнала, аналого-цифровой преобразователь, цифровой формирователь квадратур, постоянное запоминающее устройство, устройство цифрового гетеродинирования, цифровой сумматор, цифровой оптимальный фильтр, мультиплексор, контроллер интерфейса LVDS и устройство управления. Сигнал опорной частоты fоп используют для получения частоты дискретизации принимаемого сигнала. Управление работой устройства аналого-цифрового преобразования 3 осуществляют командами, поступающими по магистрали последовательного управляющего интерфейса SMI 5. Синхронизация включения режима работы устройства аналого-цифрового преобразования 3, заданного принятой по интерфейсу SMI командой, осуществляют импульсом начала обработки (ИНО).

Формирователь частоты дискретизации формирует сигнал частоты дискретизации удвоением частоты сигнала опорной частоты fоп. Принимаемый сигнал промежуточной частоты через формирователь дифференциального сигнала подают на вход аналого-цифрового преобразователя. Полученный дискретный сигнал обрабатывают цифровой схемой, выполненной на основе программируемой логической интегральной микросхемы (ПЛИС). Цифровой формирователь квадратур осуществляет представление сигнала в комплексной форме с формированием реальной и мнимой квадратурных составляющих. Постоянное запоминающее устройство содержит комплексные коэффициенты, корректирующие квадратурные составляющие сигнала цифрового формирователя квадратур.

Устройство цифрового гетеродинирования осуществляет перенос спектра сигнала на видеочастоту. Цифровой сумматор выполняет суммирование отсчетов сигнала на интервале одного элемента дальности. Количество суммируемых выборок определяется кодом, поступающим с устройства управления. После суммирования, при наличии команды включения оптимальной фильтрации, поступающей с устройства управления, сигнал проходит оптимальную фильтрацию (временное сжатие фазокодоманипулированного (ФКМ) сигнала). Затем оцифрованный сигнал поступает на мультиплексор, преобразуется контроллером интерфейса LVDS из параллельного кода в последовательный, и в виде последовательного массива 32-разрядных комплексных значений для всех элементов дальности передается в линии интерфейса LVDS. Управление работой устройств, входящих в устройство аналого-цифрового преобразования 3, обеспечивает устройство управления, которое выполняет преобразование последовательного кода сообщений, поступающих по магистрали последовательного управляющего интерфейса SMI 5 в параллельный код управляющих сигналов. Синхронизация работы устройства управления осуществляется импульсом начала обработки (ИНО), поступающим с устройства синхронизации 1.

Высокоскоростной последовательный интерфейс (LVDS) 4 является последовательным однонаправленным синхронным интерфейсом, осуществляющим соединение от одного передатчика к одному приемнику информации (топология точка-точка) по дифференциальным симметричным линиям LVDS (Low Voltage Differential Signaling Interface Std ANSI/TIA/EIA-644). Интерфейс LVDS использует передачу сигналов в симметричную дифференциальную линию с малыми сигнальными уровнями 350 мВ при токе в линии 3,5 мА. Интерфейс LVDS включает одну дифференциальную линию синхронизации и одну или несколько линий передачи данных, скорость передачи по каждой линии данных до 1 Гбит/с.

Интерфейс LVDS используют для пересылки данных от устройства аналого-цифрового преобразования 3 к цифровому процессору обработки сигналов 6 и между модулями ЦПОС. При выбранной скорости передачи данных 560 Мбит/с и использованием четырех линий передачи данных, интерфейс LVDS позволяет пересылать от одного устройства АЦП данные по двум приемным каналам для частоты 28 миллионов отсчетов в секунду по каждому приемному каналу. Используемый дифференциальный метод передачи сигналов и малый уровень сигналов LVDS позволяют снизить влияние внешних наводок и, следовательно, расширить динамический диапазон АЦП и приемника РЛС. Малое изменение напряжения, симметричные линии передачи и низкое нарастание напряжения (1 В/нс) обусловливают малый уровень наводок от интерфейса LVDS.

Цифровой процессор обработки сигналов (ЦПОС) 6 является дополнительным программируемым вычислительным устройством вычислительного комплекса и обеспечивает ввод с интерфейса LVDS и программную обработку оцифрованных сигналов. Цифровой процессор обработки сигналов 6 содержит одну или несколько микросхем цифровых сигнальных процессоров (Солонина А.И., Улахович Д.А., Яковлев Е.А. Алгоритмы и процессоры цифровой обработки сигналов. - СПб.: БВХ - Петербург, 2001, с.60), перепрограммируемое постоянное запоминающее устройство, оперативное запоминающее устройство, коммутатор данных последовательного интерфейса ввода-вывода LVDS 4 и контроллер двунаправленной шины системной магистрали 8 Compact PCI.

Графический контроллер (ГК) 9 обеспечивает накопление массива данных изображения, формирование и выдачу видеосигнала на внешнее устройство отображения (монитор). Управление графическим ГК 9 контроллером и ввод данных осуществляют по двунаправленной шине системной магистрали 8 Compact PCI. Для обеспечения помехоустойчивости передаваемого изображения сигнал изображения передается по цифровому последовательному каналу ЦПК (FIBRE CHANNEL Framing And Signaling, Rev. 1.50, ANSI For Information Technology, November 16, 2001) со скоростью передачи данных по коаксиальной линии до 266 Мбит/с. Канал ЦПК может использоваться и для обмена данными с внешней системой обработки радиолокационной информации и управления высшего уровня.

Устройства ввода-вывода (УВВ) 10 являются интерфейсными устройствами и обеспечивают обмен данными между вычислительным комплексом и внешними устройствами РЛС по универсальным или специализированным интерфейсам. Управление устройством ввода-вывода УВВ 10 и обмен данными с центральным процессором ЦП 7 осуществляют по двунаправленной шине системной магистрали 8 Compact PCI. Внешними интерфейсами устройства ввода-вывода УВВ 10 могут быть: последовательный магистральный канал информационного обмена (ГОСТ Р 52070-2003), последовательные входные и выходные радиальные каналы информационного обмена (ГОСТ 18977-79, РТМ 1495-75), входные и выходные разовые команды (ГОСТ 18977-79).

Многофункциональный вычислительный комплекс для обработки радиолокационных сигналов работает следующим образом.

При включении электропитания устройство синхронизации УС 1 устанавливает значения выходных управляющих сигналов, соответствующие наибольшему периоду импульсов запуска и наименьшей мощности излучения передатчика РЛС.

После запуска программы центральный процессор ЦП 7 инициирует программу текущего режима обработки радиолокационного сигнала и выполняет начальную установку устройств вычислительного комплекса. По шине системной магистрали CPCI 8 центральный процессор ЦП 7 загружает в оперативную память или устанавливает параметры программы, хранящейся в перепрограммируемом постоянном запоминающем устройстве, цифрового процессора обработки сигналов ЦПОС 6, устанавливает параметры обработки изображения графического контроллера ГК 9 и устанавливает параметры обмена интерфейсов устройств ввода-вывода УВВ 10.

По последовательному управляющему интерфейсу SMI 5 центральный процессор ЦП 7 устанавливает параметры сигналов синхронизации и управления устройства синхронизации УС 1, значения коэффициента усиления и ширины полосы пропускания усилителя промежуточной частоты УПЧ 2, параметры цифровой обработки сигналов устройства аналого-цифрового преобразования УАЦП 3.

Поступающие с устройства синхронизации УС 1 тактовые импульсы ТИ, период следования которых соответствует неизменному положению антенны РЛС, задают начало и время накопления радиолокационной информации.

Входные сигналы на промежуточной частоте ПЧ 1 и ПЧ 2 с высокочастотного приемника РЛС поступают на входы усилителей промежуточной частоты УПЧ 2 каждого канала. Усилитель промежуточной частоты УПЧ 2 в соответствии с установленными значениями коэффициента передачи и ширины частоты пропускания осуществляет усиление и частотную селекцию принимаемого сигнала ПЧ. Согласованный с параметрами приемного канала сигнал ПЧ поступает на вход устройства аналого-цифрового преобразования УАЦП 3.

Момент начала и период обработки принимаемого сигнала ПЧ задает импульс начала обработки ИНО, поступающий с устройства синхронизации УС 1 на вход 2 УАЦП 3. Период ИНО равен периоду импульса запуска ИЗП передатчика РЛС, а задержка ИНО относительно ИЗП соответствует временному положению первого обрабатываемого элемента дальности.

Устройство аналого-цифрового преобразования УАЦП 3 выполняет дискретизацию сигнала ПЧ на частоте, кратной частоте опорного генератора fоп, что уменьшает зеркальные составляющие в спектре преобразованного сигнала. Дискретный сигнал ПЧ проходит в устройстве аналого-цифрового преобразования УАЦП 3 первичную цифровую обработку: цифровое формирование реальной и мнимой квадратурных составляющих комплексного представления сигнала; цифровую коррекцию квадратурных составляющих сигнала; цифровое гетеродинирование с переносом спектра сигнала на видеочастоту; цифровое суммирование или накопление отсчетов сигнала на интервале одного элемента дальности; оптимальную фильтрацию или временное сжатие фазокодоманипулированного сигнала. Затем 32-разрядные комплексные значения сигнала преобразуются в последовательный код, и массив значений обрабатываемых элементов дальности текущего периода ИЗП передается через синхронный высокоскоростной последовательный интерфейс LVDS 4 на программируемый цифровой процессор обработки сигналов ЦПОС 6. Одновременно по линиям интерфейса LVDS передают реальные и мнимые квадратуры сигналов приемных каналов.

Цифровой процессор обработки сигналов ЦПОС 6 осуществляет прием данных, поступающих по интерфейсу LVDS 4. Принимаемые данные распределяются цифровым процессором обработки сигналов ЦПОС 6 между микросхемами цифровых сигнальных процессоров ЦСП. Если сигнальная обработка ведется несколькими ЦПОС, поток принимаемых данных коммутируется на выход интерфейса LVDS для передачи на другой ЦПОС. Время обработки принимаемого сигнала равно времени накопления, задаваемого периодом тактовых импульсов ТИ.

Цифровой процессор обработки сигналов ЦПОС 6 может выполнять следующие функции обработки принимаемого сигнала: накопление значений элементов дальности в периодах импульса запуска передатчика ИЗП РЛС за период импульса ТИ, преобразование сигнала из временной в частотную форму представления и обратное преобразование, фильтрацию сигнала в частотной и временной областях, функции доплеровского обужения луча и фазированной синтезированной апертуры, формирование пороговых значений сигнала и выделение целей на фоне помех. После завершения обработки данных за текущий период ТИ массив элементов дальности, обрабатываемых данным ЦПОС, пересылают по интерфейсу LVDS 4 в другой, выполняющий обработку всех элементов дальности ЦПОС, или по шине системной магистрали CPCI 8 в память центрального процессора ЦП 7.

Цифровой процессор обработки сигналов ЦПОС 6 может также обрабатывать данные за несколько периодов тактового импульса ТИ с формированием растрового (в координатах азимут-дальность) радиолокационного изображения преобразованием его в сектор видеоизображения и выдачей в режиме прямого доступа к памяти (без участия центрального процессора 7) по шине системной магистрали CPCI 8 в видеопамять графического контроллера 9.

Центральный процессор 7 выполняет функции завершающей обработки радиолокационной информации с выдачей данных по шине системной магистрали CPCI 8 на графический контроллер 9 или через устройства ввода-вывода 10 на внешние блоки радиолокационной станции.

Многофункциональный вычислительный комплекс для обработки радиолокационных сигналов обеспечивает работу радиолокационной станции во всех штатных режимах, а также в режиме встроенного контроля.

Расширение функциональных возможностей многофункционального вычислительного комплекса для обработки радиолокационных сигналов достигается обработкой принимаемого широкополосного радиолокационного сигнала с аналого-цифровым преобразованием сигнала на промежуточной частоте, цифровым формированием и коррекцией комплексных квадратурных составляющих сигнала, цифровым переносом спектра сигнала на видеочастоту, оптимальным временным ФКМ сжатием и накоплением значений сигнала, что повышает чувствительность и избирательность приемного тракта РЛС для каждого приемного канала РЛС, возможностью обработки сигналов от одного или нескольких приемных каналов РЛС, а также использованием последовательного интерфейса LVDS для пересылки больших объемов данных; выполнением программы центральным процессором 7 и одним или несколькими цифровыми процессорами обработки сигналов 6, ориентированными на цифровую обработку сигналов с использованием цифровой фильтрации и вычислительных методов, таких как доплеровское обужение луча и фазированная синтезированная апертура, для повышения разрешения РЛС по азимуту; использованием процессора цифровой обработки сигналов 6 для формирования, обработки и вывода данных изображения в память графического контроллера 9, обеспечивающего выдачу видеосигнала на внешний видеомонитор.

Повышение производительности многофункционального вычислительного комплекса для обработки радиолокационных сигналов обеспечивается распределенным процессом обработки радиолокационного сигнала: селекцией принимаемого сигнала программно управляемым аналоговым усилителем промежуточной частоты 2; первичной цифровой обработкой сигнала схемотехническими средствами устройства аналого-цифрового преобразования 3; вводом данных от устройства аналого-цифрового преобразования 3 на цифровой процессор обработки сигналов 6 по высокопроизводительному последовательному интерфейсу LVDS 4; выполнением программы обработки сигнала, наряду с центральным процессором 7, одним или несколькими цифровыми процессорами обработки сигналов 6; возможностью обмена данными между цифровыми процессорами обработки сигналов 6 как по интерфейсу LVDS 4, так и по шине системной магистрали CPCI 8, а также параллельной обработкой радиолокационного сигнала при использовании нескольких приемных каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 2009 |

|

RU2419139C1 |

| МНОГОПРОЦЕССОРНОЕ УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 2008 |

|

RU2399089C2 |

| БЛОК ПРИЕМА И СИНХРОНИЗАЦИИ | 2012 |

|

RU2497148C1 |

| МОДУЛЬ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ | 2005 |

|

RU2290662C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С УСТРОЙСТВОМ УПРАВЛЕНИЯ | 2013 |

|

RU2535931C1 |

| УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 2009 |

|

RU2402807C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С КАНАЛАМИ ВЫСОКОГО РАЗРЕШЕНИЯ | 2007 |

|

RU2344436C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК | 2007 |

|

RU2332682C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС РЕГИСТРАЦИИ И СИНТЕЗА РАДИОТЕХНИЧЕСКИХ СИГНАЛОВ | 2007 |

|

RU2351979C2 |

| Блок приема и синхронизации с функцией формирования дополнительных бланкирующих импульсов | 2023 |

|

RU2821958C1 |

Изобретение относится к вычислительной технике и предназначено для цифровой обработки сигналов и управления в составе радиолокационного комплекса. Техническим результатом является расширение функциональных возможностей и повышение производительности устройства. Устройство содержит центральный процессор, цифровые процессоры обработки сигналов, графический контроллер, устройства ввода-вывода для обмена данными между многофункциональным вычислительным комплексом и внешними устройствами радиолокационной станции, устройство синхронизации, усилители промежуточной частоты, устройства аналого-цифрового преобразования. 1 ил.

Многофункциональный вычислительный комплекс для обработки радиолокационных сигналов, содержащий центральный процессор, цифровые процессоры обработки сигналов, графический контроллер, устройства ввода-вывода для обмена данными между многофункциональным вычислительным комплексом и внешними устройствами радиолокационной станции (РЛС), при этом первый вход-выход центрального процессора соединен шиной системной магистрали с входом-выходом цифрового процессора обработки сигналов, входом-выходом графического контроллера и входом-выходом устройства ввода-вывода, отличающийся тем, что цифровых процессоров обработки сигналов и устройств ввода-вывода может быть как одно, так и несколько, а также дополнительно содержит устройство синхронизации, один или несколько усилителей промежуточной частоты, одно или несколько устройств аналого-цифрового преобразования, причем первый вход устройства синхронизации является входом опорного сигнала многофункционального вычислительного комплекса, первый выход устройства синхронизации является выходом сигнала управления фазовым манипулятором РЛС, второй выход устройства синхронизации является выходом импульса запуска передатчика РЛС, третий выход устройства синхронизации является выходом импульса бланкирования приемника РЛС, четвертый выход устройства синхронизации является выходом тактового импульса РЛС, пятый выход устройства синхронизации, являющийся выходом сигнала опорной частоты, соединен с первым входом каждого устройства аналого-цифрового преобразования, шестой выход устройства синхронизации, являющийся выходом импульса начала отсчета дальности, соединен с третьим входом каждого устройства аналого-цифрового преобразования, и седьмой выход устройства синхронизации соединен со вторым входом каждого усилителя промежуточной частоты, первым входом каждого цифрового процессора обработки сигналов и входом центрального процессора, кроме того, второй вход-выход центрального процессора соединен последовательным управляющим интерфейсом с входом-выходом устройства синхронизации, с входом-выходом усилителя промежуточной частоты и входом-выходом устройства аналого-цифрового преобразования, первый вход каждого усилителя промежуточной частоты является входом многофункционального вычислительного комплекса для принятия сигнала промежуточной частоты соответствующего канала высокочастотного приемника РЛС, выход каждого усилителя промежуточной частоты соединен со вторым входом соответствующего устройства аналого-цифрового преобразования, выход каждого устройства аналого-цифрового преобразования соединен высокоскоростным последовательным интерфейсом со вторым входом одного из цифровых процессоров обработки сигналов, выход одного цифрового процессора обработки сигналов соединен высокоскоростным последовательным интерфейсом с третьим входом другого цифрового процессора обработки сигналов, выход графического контроллера является выходом многофункционального вычислительного комплекса для связи по цифровому последовательному каналу с внешним видеомонитором.

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ГИДРОАКУСТИЧЕСКОГО КОМПЛЕКСА | 2000 |

|

RU2187148C2 |

| ЦИФРОВОЙ БЛОК ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 1995 |

|

RU2080618C1 |

| JP 2002207078 A, 26.07.2002 | |||

| Информационное устройство пункта оперативной связи | 1978 |

|

SU741305A1 |

Авторы

Даты

2010-09-10—Публикация

2008-10-28—Подача