Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству формирования изображения, такому как датчик изображения CMOS (КМОП, комплементарный металлооксидный полупроводник), способу управления устройством формирования изображения и к камере, в которой используется устройство формирования изображения.

Уровень техники

В датчике изображения типа КМОП выполняют сброс для удаления избыточного заряда из устройства фотоэлектрического преобразования, при этом электронный затвор действует так, что вызывает сохранение заряда устройством фотоэлектрического преобразования, и накопленный заряд выводят как сигнал напряжения в линию кадровой развертки. Теперь основная часть обычного датчика изображения КМОП и его работа будут кратко описаны ниже со ссылкой на фиг.13 и 14.

На фиг.13 показана эквивалентная схема основной части, представляющая пример конфигурации обычного датчика изображения типа КМОП.

На фиг.14 показана временная диаграмма датчика изображения КМОП, показанного на фиг.13. На фиг.14 (А) показан управляющий сигнал SDRN. На фиг.14 (В) показан сигнал SRST сброса. На фиг.14 (С) показан сигнал STRN передачи.

Пиксельная схема 30 датчика изображения 3 КМОП, показанная на фиг.13, установлена в пиксельном блоке 311. Пиксельная схема 30 включает в себя транзистор 32 передачи, транзистор 33 сброса и транзистор 34 усилителя, и управление ею выполняют с помощью схемы 37 управления горизонтальной разверткой. Пиксельная схема 30, выполненная, как показано на фиг.13, называется "пиксельной схемой, управляемой 3 транзисторами", "датчик изображения КМОП, управляемый 3 транзисторами" или тому подобным образом.

Схема 37 управления горизонтальной разверткой включает в себя транзистор 39 для подачи управляющего сигнала SDRN с напряжением VL низкого уровня в линию 310 управляющего сигнала и транзистор 38 для подачи управляющего сигнала SDRN с напряжением VH высокого уровня в линию 310 управляющего сигнала. Напряжение VH высокого уровня представляет собой, например, напряжение VDD источника, а напряжение VL низкого уровня является напряжением для удержания транзистора 34 усилителя в закрытом состоянии.

Когда пиксельная схема 30 представляет собой пиксельную схему, управляемую 3 транзисторами, схема 37 управления горизонтальной разверткой подает двухуровневое напряжение, состоящее из напряжения VL низкого уровня или напряжения VH высокого уровня, в линию 310 управляющего сигнала для управления пиксельной схемой 30.

В промежуток от момента t1 до момента t4 схема 37 управления горизонтальной разверткой подает напряжение VL затвора на затвор транзистора 38 для удержания транзистора 38 в открытом состоянии, и подает управляющий сигнал SDRN с напряжением VH высокого уровня в линию 310 управляющего сигнала (см. фиг.14 (А)).

Прежде чем устройство 31 фотоэлектрического преобразования начнет считывать заряд (момент t2), схема 37 управления горизонтальной разверткой подает импульс сигнала SRST сброса в линию RSTL сигнала сброса, подключенную к затвору транзистора 33 сброса (см. фиг.14 (В)). В результате происходит сброс потенциала плавающей диффузионной области (FD, ПД) до напряжения VH высокого уровня.

В момент t3 схема 37 управления горизонтальной разверткой подает импульс сигнала STRN передачи в линию TRNL сигнала передачи, подключенную к затвору транзистора 32 передачи (см. фиг.14 (С)). В результате происходит передача заряда, сохраненного устройством 31 фотоэлектрического преобразования, в плавающую диффузионную область ПД.

В этот момент на затвор транзистора 34 усилителя подан потенциал плавающей диффузионной области ПД, и напряжение VH высокого уровня подано на сток. В соответствии с этим, транзистор 34 усилителя усиливает потенциал плавающей диффузионной области ПД в зависимости от напряжения между истоком и затвором и выводит усиленный потенциал в виде сигнала напряжения в линию 35 сигнала кадровой развертки. Вывод сигнала напряжения из транзистора 34 усилителя называется "считыванием заряда", "считыванием пикселя" или тому подобное и продолжается до момента времени t4.

После считывания заряда, в промежуток от момента времени t4 до момента времени t5, схема 37 управления горизонтальной разверткой удерживает только транзистор 39 в открытом состоянии для подачи управляющего сигнала SDRN с напряжением VL низкого уровня в линию 310 управляющего сигнала (см. фиг.14 (А)) и подают импульс сигнала SRST сброса в линию RSTL сигнала сброса (см. фиг.14 (В)).

После подачи напряжения VL низкого уровня на затвор транзистора 34 усилителя (плавающая диффузионная область ПД) сигнал SRST сброса возвращается к напряжению VL низкого уровня.

В результате транзистор 34 усилителя удерживается в закрытом состоянии, обеспечивая невыбранное состояние пиксельной схемы 30, в которой вывод сигнала напряжения остановлен, что завершает операцию датчика 3 изображения КМОП в одном периоде Н горизонтальной развертки.

Как описано выше, когда выполняют считывание заряда, сигнал напряжения из пиксельной схемы 30 подается в линию 35 сигнала кадровой развертки, что вызывает изменение потенциала в линии 35 сигнала кадровой развертки.

В этот момент, даже если количество пиксельных схем 30 в невыбранном состоянии мало, когда пиксельные схемы 30 в не выбранном состоянии выводят сигналы напряжения в линию 35 сигнала кадровой развертки, такие сигналы напряжения накладываются на сигналы напряжения, выведенные из пиксельных схем 30 считываемой строки. Вследствие этого, выходное напряжение из пиксельных схем влияет на всю область пикселей, вызывая различные шумы, включающие в себя паразитный сигнал.

Эти явления тесно связаны с тем, как происходит падение управляющего сигнала SDRN в момент времени t4. Чем более круто спадает управляющий сигнал SDRN (см. фиг.14), тем более интенсивно флюктуируют потенциалы ям р-типа у транзисторов, включенных в схему 30 пикселя, в результате чего возникают явления, включающие в себя паразитный сигнал.

Таким образом, раскрыт способ ослабления явлений, включающих в себя паразитный сигнал, с помощью многозначного управляющего сигнала SDRN, имеющего разные уровни напряжения и спадающего более плавно (см. Патентные документы 1, 2).

Документ предшествующего уровня техники

Патентный документ

Патентный документ 1: JP-A-2005-217704

Патентный документ 2: JP-A-2005-311932

Сущность изобретения

Задачи, решаемые изобретением

В соответствии с Патентными документами 1, 2 в пиксельной схеме, управляемой 3 транзисторами, сток транзистора 33 сброса и сток транзистора 34 усилителя подключены к линии 310 управляющего сигнала, как показано на фиг.13.

Это увеличивает нагрузочное сопротивление проводов линии 310 управляющего сигнала, что приводит к ослаблению и задержке управляющего сигнала SDRN, что затрудняет выполнение управления пиксельной схемой 30 с высокой скоростью. В Патентных документах 1, 2 многозначный управляющий сигнал SDRN подается в линию 310 управляющего сигнала. Однако, при этом возникает тенденция замедления спадания импульса, что препятствует считыванию пикселя с высокой скоростью.

Настоящее изобретение обеспечивает устройство формирования изображения, которое может не только уменьшать шумы, включая в себя паразитный сигнал, но также позволяет считывать пиксель с высокой скоростью, способ управления устройством формирования изображения и камеру, в которой используют устройство формирования изображения.

Средство решения задачи

В соответствии с первым аспектом настоящего изобретения устройство формирования изображения включает в себя: множество пиксельных схем, расположенных в виде матрицы; линию управления выбором, соединенную с множеством пиксельных схем, расположенных в одном направлении; и схему управления выбором, выполненную с возможностью выборочной подачи сигнала управления выбором, имеющего множество разных уровней напряжения, в линию управления выбором для выбора и управления пиксельными схемами, причем каждая из пиксельных схем включает в себя: фотоэлектрический преобразователь для фотоэлектрического преобразования падающего света в заряд; узел, в который заряд передается из фотоэлектрического преобразователя; выходной транзистор, имеющий управляющий вывод, подключенный к указанному узлу, первый соединительный вывод, подключенный к источнику заданного напряжения, и второй соединительный вывод, подключенный к линии выходного сигнала, причем выходной транзистор выполнен с возможностью усиления потенциала указанного узла и вывода усиленного напряжения в линию выходного сигнала в качестве выходного сигнала; и управляющий транзистор, имеющий третий соединительный вывод, подключенный к указанному узлу, и четвертый соединительный вывод, подключенный к линии управления выбором, на которую подается сигнал управления выбором, причем управляющий транзистор выполнен с возможностью установки потенциала указанного узла, к которому подключен управляющий вывод выходного транзистора, в потенциал, зависящий от уровня напряжения, и с возможностью управления сбросом потенциала узла и выходным сигналом выходного транзистора, и при этом в промежуток времени, в течение которого выходной сигнал выходного транзистора не выводится, схема управления выбором выполнена с возможностью смещения уровня напряжения управляющего сигнала выбором, подаваемого в линию управления выбором, с первого уровня напряжения, при котором выходной транзистор удерживается в открытом состоянии, ко второму уровню напряжения, превышающему уровень опорного напряжения, при котором выходной транзистор удерживается в закрытом состоянии, и с возможностью постепенного возврата уровня напряжения управляющего сигнала выбором со второго уровня напряжения к первому уровню напряжения.

Предпочтительно, множество уровней напряжения включают в себя: уровень первого напряжения, уровень второго напряжения и уровень третьего напряжения, который представляет собой уровень опорного напряжения для удержания выходного транзистора в закрытом состоянии, при этом схема управления выбором выполнена с возможностью смещения уровня напряжения управляющего сигнала выбором, поданного в линию управления выбором, с первого уровня напряжения ко второму уровню напряжения, и возврата уровня напряжения управляющего сигнала выбором к первому уровню напряжения через третий уровень напряжения.

Предпочтительно, схема управления выбором выполнена с возможностью подачи сигнала управления выбором со вторым уровнем напряжения в линию управления выбором на более короткий промежуток времени, чем промежуток времени подачи управляющего сигнала выбором с другим уровнем напряжения, чем второй уровень напряжения.

Предпочтительно, схема управления выбором включает в себя: транзистор, имеющий пятый соединительный вывод, на который подается напряжение одного из второго и третьего уровней напряжения, причем указанный транзистор выполнен с возможностью вывода напряжения с уровнем напряжения, поданным на пятый соединительный вывод, в линию управления выбором; и транзистор противодействия короткому замыканию, имеющий такую же полярность, что и указанный транзистор, и выполненный с возможностью недопущения короткого замыкания в схеме управления выбором, причем транзистор противодействия короткому замыканию имеет седьмой соединительный вывод, подключенный к шестому соединительному выводу транзистора, и восьмой соединительный вывод, подключенный к линии управления выбором.

Предпочтительно, схема управления выбором выполнена с возможностью подачи сигнала управления выбором на оба конца линии управления выбором.

В соответствии со вторым аспектом изобретения способ управления устройством формирования изображения включает в себя: первый этап, на котором выборочно подают сигнал управления выбором, имеющий разные уровни напряжения, в линию управления выбором, соединенную с множеством пиксельных схем, расположенных в одном направлении, для выбора и управления множеством пиксельных схем, причем выбранное множество пиксельных схем выполняют фотоэлектрическое преобразование падающего света в заряд и выводят напряжение, зависящее от величины заряда, в линию вывода сигнала в качестве выходного сигнала; и второй этап, на котором прекращают вывод сигнала из множества пиксельных схем на заданный промежуток времени после считывания заряда множеством пиксельных схем, причем на первом этапе: передают заряд, полученный в результате фотоэлектрического преобразования фотоэлектрическим преобразователем, в узел, при этом управляющий транзистор, имеющий третий соединительный вывод, подключенный к указанному узлу, и четвертый соединительный вывод, на который подают сигнал управления выбором через линию управления выбором, устанавливает потенциал указанного узла, к которому подключен управляющий вывод выходного транзистора в потенциал, зависящий от уровня напряжения, и выполняет сброс потенциала указанного узла, и при этом выходной транзистор, имеющий управляющий вывод, подключенный к указанному узлу, первый соединительный вывод, подключенный к источнику заданного напряжения, и второй соединительный вывод, подключенный к линии выходного сигнала, усиливает потенциал узла и выводит усиленное напряжение в качестве выходного сигнала в линию выходного сигнала под управлением управляющего транзистора, и на втором этапе, включающий в себя: выполняют смещение уровня напряжения управляющего сигнала выбором, подаваемого через линию управления выбором, с первого уровня напряжения, при котором выходной транзистор удерживается в открытом состоянии, ко второму уровню напряжения, превышающему уровень напряжения, требуемый для удержания выходного транзистора в закрытом состоянии, и постепенно возвращают уровень напряжения управляющего сигнала выбором со второго уровня напряжения к первому уровню напряжения.

В соответствии с третьим аспектом изобретения, камера включает в себя: устройство формирования изображения; оптическую систему для направления падающего света на область пикселей устройства формирования изображения; и процессор сигналов для обработки выходного сигнала, выводимого из устройства формирования изображения, при этом устройство формирования изображения включает в себя: множество пиксельных схем, расположенных в виде матрицы; линию управления выбором, соединенную с множеством пиксельных схем, расположенных в одном направлении; и схему управления выбором, выполненную с возможностью выборочной подачи сигнала управления выбором, имеющего разные уровни напряжения, в линию управления выбором для выбора и управления пиксельными схемами, при этом каждая из пиксельных схем включает в себя: фотоэлектрический преобразователь для фотоэлектрического преобразования падающего света в заряд; узел, в который заряд передается из фотоэлектрического преобразователя; выходной транзистор, имеющий управляющий вывод, подключенный к указанному узлу, первый соединительный вывод, подключенный к источнику заданного напряжения, и второй соединительный вывод, подключенный к линии выходного сигнала, причем выходной транзистор выполнен с возможностью усиления потенциала указанного узла и вывода усиленного напряжения в линию выходного сигнала, в качестве выходного сигнала; и управляющий транзистор, имеющий третий соединительный вывод, подключенный к указанному узлу, и четвертый соединительный вывод, на который подается сигнал управления выбором через линию управления выбором, причем управляющий транзистор выполнен с возможностью установки потенциала узла, с которым соединен управляющий вывод выходного транзистора, в потенциал, зависящий от уровня напряжения, и с возможностью управления сбросом потенциала узла и выходным сигналом выходного транзистора, и при этом в промежуток времени, когда отсутствует вывод выходного сигнала выходного транзистора, схема управления выбором выполнена с возможностью смещения уровня напряжения управляющего сигнала выбором, подаваемого через линию управления выбором, с первого уровня напряжения, при котором выходной транзистор удерживается в открытом состоянии, ко второму уровню напряжения, превышающему уровень опорного напряжения, при котором выходной транзистор удерживается в закрытом состоянии, и постепенного возврата уровня напряжения управляющего сигнала выбором со второго уровня напряжения к первому уровню напряжения.

В соответствии с изобретением, выходной транзистор, имеющий управляющий вывод, подключенный к указанному узлу, первый соединительный вывод, подключенный к источнику заданного напряжения, и второй соединительный вывод, подключенный к линии вывода сигнала, усиливает потенциал узла и выводит усиленное напряжение в линию вывода сигнала в качестве выходного сигнала.

Управляющий транзистор, имеющий третий соединительный вывод, подключенный к указанному узлу, и четвертый соединительный вывод, подключенный к линии управления выбором, в которую подается сигнал управления выбором, устанавливает потенциал узла в потенциал, зависящий от уровня напряжения, и управляет сбросом потенциала узла и выходным сигналом выходного транзистора.

Схема управления выбором выборочно подает сигнал управления выбором, имеющий разные уровни напряжения, в линию управления выбором, подключенную к множеству пиксельных схем, расположенных в одном направлении, и в промежуток времени, в течение которого выходной сигнал выходного транзистора не выводится, смещает уровень напряжения, подаваемого в линию управления выбором, с первого уровня напряжения до второго уровня напряжения, и постепенно возвращает уровень напряжения со второго уровня напряжения к первому уровню напряжения.

Преимущество изобретения

В соответствии с изобретением становится возможным не только снизить уровень шумов, включающих в себя паразитный сигнал, но также считывать пиксели с высокой скоростью.

Краткое описание чертежей

На фиг.1 показана схема конфигурации, представляющая пример конфигурации датчика изображения КМОП в соответствии с первым вариантом выполнения.

На фиг.2 показана принципиальная схема, представляющая пример конфигурации пиксельной схемы и схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения.

На фиг.3 показана временная диаграмма, представляющая пример работы схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения.

На фиг.4 показана принципиальная схема, представляющая вариант схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения.

На фиг.5 схематично показан вид в разрезе транзисторов уровня, показанных на фиг.4.

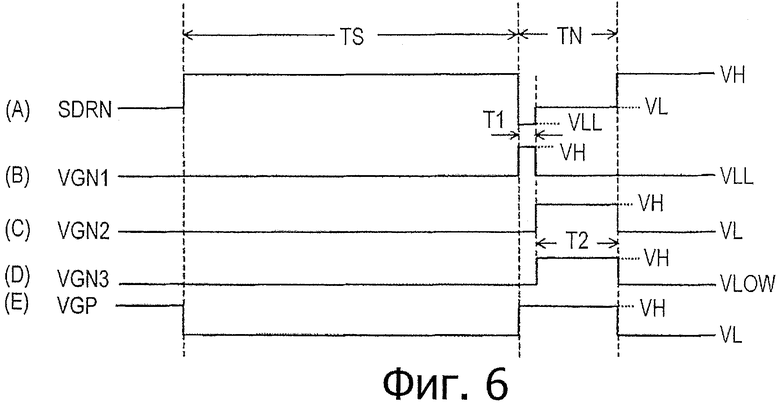

На фиг.6 показана временная диаграмма, представляющая пример работы схемы управления горизонтальной разверткой, показанной на фиг.4.

На фиг.7 показана временная диаграмма, представляющая пример работы датчика изображения КМОП в соответствии с первым вариантом выполнения.

На фиг.8 показана принципиальная схема, представляющая подробный пример пиксельного блока и схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения.

На фиг.9 показан результат моделирования датчика изображения КМОП в соответствии с первым вариантом выполнения.

На фиг.10 показан результат моделирования обычного датчика изображения КМОП.

На фиг.11 показана принципиальная схема, представляющая подробный пример пиксельного блока и схемы управления горизонтальной разверткой в соответствии со вторым вариантом выполнения.

На фиг.12 показан пример конфигурации камеры, в которой используется датчик изображения КМОП в соответствии с вариантами выполнения настоящего изобретения.

На фиг.13 показана эквивалентная схема основной части, представляющая пример конфигурации обычного датчика изображения КМОП.

На фиг.14 показана временная диаграмма датчика изображения КМОП, показанного на фиг.13.

Подробное описание изобретения

Ниже описаны варианты выполнения изобретения со ссылкой на чертежи.

Первый вариант выполнения

На фиг.1 показана схема конфигурации, представляющая пример конфигурации датчика изображения КМОП в соответствии с первым вариантом выполнения. На фиг.1 показана только основная часть датчика 1 изображения КМОП.

Как показано на фиг.1, датчик 1 изображения КМОП (КМОП) включает в себя множество пиксельных блоков 10, пиксельных схем 11, схему 12 (DRV) управления горизонтальной разверткой, схему 13 горизонтальной передачи и генератор 14 синхронизации.

Следует отметить, что устройство формирования изображения в соответствии с изобретением соответствует датчику 1 изображения КМОП, область пикселей в соответствии с изобретением соответствует пиксельному блоку 10, а схема управления выбором в соответствии с изобретением соответствует схеме 12 управления горизонтальной разверткой.

Пиксельный блок 10 представляет собой область пикселей, предназначенную для приема падающего света, и включает в себя n x m пиксельных схем 11, расположенных в виде матрицы, состоящей из n строк на m столбцов. Числа n и m представляют собой положительные целые числа, и каждое из них может составлять, например, вплоть до 2048.

Каждая пиксельная схема 11 представляет собой пиксельную схему, управляемую 3 транзисторами. Каждая пиксельная схема 11 закрыта цветным фильтром R (красного), G (зеленого) или В (синего) цвета и расположена в соответствии, например, со схемой Байера. Линия DRNL (n) управляющего сигнала, линия RSTL (n) сигнала сброса и линия TRNL (n) сигнала передачи параллельно подключены к пиксельным схемам 11, принадлежащим одной строке.

Каждая пиксельная схема 11 выполняет фотоэлектрическое преобразование падающего света в заряд (электрон) и выводит сигнал напряжения, зависящий от величины заряда, в линию VSL (m) сигнала вертикальной развертки.

Следует отметить, что линия управления выбором в соответствии с изобретением соответствует линии DRNL (n) управляющего сигнала, линия выходного сигнала в соответствии с изобретением соответствует линии VSL (m) сигнала вертикальной развертки, и выходной сигнал в соответствии с изобретением соответствует цифровому сигналу.

Схема 12 управления горизонтальной разверткой выбирает строку для сканирования и осуществляет управление схемами 11 пикселя, принадлежащими одной строке. В частности, схема 12 управления горизонтальной разверткой подает управляющий сигнал SDRN в линию DRNL (n) управляющего сигнала, подает сигнал SRST сброса в линию RSTL (n) сигнала сброса и подает сигнал STRN передачи в линию TRNL (n) сигнала передачи.

Схема 13 горизонтальной передачи включает в себя, например, схему 31 столбца, предусмотренную для каждого столбца, переключатель 132 для выбора линии VSL (m) сигнала вертикальной развертки для каждого столбца, и линию HSCNL сигнала горизонтальной передачи.

Схема 13 горизонтальной передачи последовательно выбирает линию VSL (m) сигнала вертикальной развертки, открывая/закрывая переключатель 132 для каждого столбца, и считывает заряд (сигнал напряжения) пиксельных схем 11 выбранного столбца. В этот момент схема 131 столбца преобразует сигнал аналогового напряжения, подаваемый в линию (m) сигнала вертикальной развертки, в цифровой сигнал, выполняет обработку двойной коррелированной выборки (CDS) на уровне сброса и уровне сигнала и выводит этот цифровой сигнал в линию HSCNL сигнала горизонтальной передачи. Затем схема 13 горизонтальной передачи выводит цифровой сигнал после CDS обработки в качестве выходного сигнала SIG в процессор сигналов, который является внешним для датчика 1 изображения КМОП.

Генератор 14 синхронизации предоставляет сигналы тактовой частоты в схему 12 управления горизонтальной разверткой, схему 13 горизонтальной передачи, в схемы, включенные в датчик 1 изображения КМОП, и т.п.

Далее, со ссылкой на фиг.2 будут описаны пиксельные схемы 11 и схема 12 управления горизонтальной разверткой.

На фиг.2 показана принципиальная схема, представляющая пример конфигурации пиксельной схемы и схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения. На фиг.2 показана одна пиксельная схема 11, расположенная в n-м ряду и в m-м столбце пиксельного блока 10, и только основная часть схемы 12 управления горизонтальной разверткой.

Вначале будет описан пример конфигурации схемы для пиксельной схемы 11.

Как показано на фиг.2, пиксельная схема 11 пиксельного блока 10 пикселя включает в себя устройство 111 фотоэлектрического преобразования, транзистор 112 передачи, транзистор 113 сброса, транзистор 114 усилителя и плавающую диффузионную область ПД. Пиксельная схема 11 представляет собой пиксельную схему, управляемую 3 транзисторами.

Следует отметить, что выходной транзистор в соответствии с изобретением соответствует транзистору 114 усилителя, транзистору управления в соответствии с изобретением соответствует транзистор 113 сброса, а узел в соответствии с изобретением соответствует плавающей диффузионной области ПД. Источник заданного напряжения в соответствии с изобретением соответствует напряжению VDD источника, подключаемому к стоку транзистора 114 усилителя.

Устройство 111 фотоэлектрического преобразования представляет собой, например, фотодиод. Устройство 111 фотоэлектрического преобразования имеет анод, подключенный к земле (GND), и катод, подключенный к истоку 112 транзистора передачи. Устройство 111 фотоэлектрического преобразования выполняет фотоэлектрическое преобразование падающего света в заряд (в данном варианте выполнения в электрон) в зависимости от количества света и сохраняет этот заряд. Сохранение заряда устройством 111 фотоэлектрического преобразования именуется "пиксельная схема сохраняет заряд". Время, в течение которого устройство 111 фотоэлектрического преобразования сохраняет заряд, называется временем сохранения заряда.

Например, в качестве транзисторов пиксельной схемы 11 используют n-канальный MOSFET (МОП, полевой транзистор со структурой металл-оксид полупроводник). Эти транзисторы подключены следующим образом.

Исток транзистора 112 передачи подключен к катоду устройства 111 фотоэлектрического преобразования, сток подключен к плавающей диффузионной области ПД, а затвор подключен к линии TRNL (n) сигнала передачи.

Сток транзистора 112 передачи, исток транзистора 113 сброса и затвор транзистора 114 усилителя подключены к плавающей диффузионной области ПД.

Исток (третий соединительный вывод) транзистора 113 сброса подключен к плавающей диффузионной области ПД, сток (четвертый соединительный вывод) подключен к линии DRNL (n) управляющего сигнала, а затвор подключен к линии RSTL (n) сигнала сброса.

Исток (второй соединительный вывод) транзистора 114 усилителя подключен к линии VSL (m) сигнала вертикальной развертки, сток (первый соединительный вывод) подключен к напряжению VDD источника, а затвор подключен к плавающей диффузионной области ПД. Транзистор 114 усилителя и схема 15 источника постоянного тока формируют схему истокового повторителя.

Как описано выше, первый вариант выполнения отличается тем, что на сток транзистора 113 сброса и сток транзистора 114 усилителя подано напряжение из разных источников напряжения.

Каждая пиксельная схема 11 выполняет "сброс" для установки потенциала плавающей диффузионной области ПД равным потенциалу линии DRNL (n) управляющего сигнала (напряжение VH высокого уровня).

Затем заряд, сохраненный в устройстве 111 фотоэлектрического преобразования, передают в плавающую диффузионную область ПД для считывания.

Далее описан пример конфигурации основной части схемы 12 управления горизонтальной разверткой.

Схема 12 управления горизонтальной разверткой включает в себя транзисторы 121, 122, 123 уровня для каждой строки. На фиг.2 показана только часть, относящаяся к n-й строке схемы, включающей в себя транзисторы 121,122, 123 уровня.

Например, в качестве транзисторов 121 и 122 уровня используют n-канальные МОП-транзисторы, а в качестве транзистора 123 уровня используют р-канальный ПТМОП.

Исток транзисторов 121 уровня соединен с источником напряжения VLL самого низкого уровня, а сток соединен с узлом ND1.

Стоки транзисторов 122 уровня и 123 уровня параллельно подключены к узлу ND2. Исток транзистора 122 уровня соединен с источником напряжения VL низкого уровня. Исток транзистора 123 уровня соединен с источником напряжения VH высокого уровня.

Узлы ND1 и ND2 параллельно подключены к линии DRNL (n) управляющего сигнала.

Напряжение VH высокого уровня представляет собой, например, напряжение VDD источника. Напряжение VLL самого низкого уровня ниже напряжения VL низкого уровня (VL>VLL) и представляет собой, например, потенциал GND земли.

Напряжение VL низкого уровня ниже напряжения VH высокого уровня и выше напряжения VLL самого низкого уровня (VH>VL>VLL). В частности, напряжение VL низкого уровня представляет собой опорное напряжение (например, 0,6 В), которое может удерживать транзистор 114 усилителя в закрытом состоянии, когда оно подано на затвор транзистора 114 усилителя.

Следует отметить, что первый уровень напряжения в соответствии с изобретением соответствует напряжению VH высокого уровня, второй уровень напряжения в соответствии изобретением соответствует напряжению VLL самого низкого уровня, и третий уровень напряжения в соответствии с изобретением соответствует напряжению VL низкого уровня.

Схема 12 управления горизонтальной разверткой, выполненная как описано выше, выборочно подает управляющий сигнал SDRN, имеющий три значения уровня напряжения, в линию DRNL (n) управляющего сигнала, эти три значения уровня напряжения включают в себя напряжение VH высокого уровня, напряжение VL низкого уровня и напряжение VLL самого низкого уровня. Работа схемы 12 управления горизонтальной разверткой описана ниже со ссылкой на фиг.3.

На фиг.3 показана временная диаграмма, представляющая пример работы схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения.

На фиг.3 (А) показан управляющий сигнал SDRN. На фиг.3 (В) показано напряжение VGN1 затвора, поданное на затвор транзистора 121 уровня. На фиг.3 (С) показано напряжение VGN2 затвора, поданное на затвор транзистора 122 уровня. На фиг.3 (D) показано напряжение VGP затвора, поданное на затвор транзистора 123 уровня.

Для подачи управляющего сигнала SDRN, показанного на фиг.3 (А), в линию DRNL (n) управляющего сигнала схема 12 управления горизонтальной разверткой работает следующим образом.

В период TS выбранного состояния пиксельной схемы 11 в n-той строке для активации транзистора 113 сброса для управления выходом транзистора 114 усилителя, схема 12 управления горизонтальной разверткой подает управляющий сигнал SDRN с напряжением VH высокого уровня в линию DRNL (n) управляющего сигнала.

Следует отметить, что период TS выбранного состояния представляет собой период, в течение которого пиксельная схема 11 завершает считывание заряда.

В этот момент схема 12 управления горизонтальной разверткой подает напряжение VL низкого уровня только к затвору транзистора 123 уровня (см. фиг.3 (D)). Поскольку напряжение VGP затвора представляет собой напряжение VL низкого уровня, транзистор 123 уровня удерживается в открытом состоянии в течение периода TS выбранного состояния, и управляющий сигнал SDRN с напряжением VH высокого уровня подается в линию DRNL (n) управляющего сигнала.

С другой стороны, в период TN установки "невыбранного состояния" для пиксельной схемы 11 для прекращения выходного сигнала транзистора 114 усилителя схема 12 управления горизонтальной разверткой подает управляющий сигнал SDRN с напряжением VL низкого уровня в линию DRNL (n) управляющего сигнала.

Однако в начале периода TN установки "невыбранного состояния" схема 12 управления горизонтальной разверткой быстро снижает уровень напряжения управляющего сигнала SDRN с напряжения VH высокого уровня до напряжения VLL самого низкого уровня.

Следует отметить, что период TN установки "не выбранного состояния" представляет собой период, в течение которого схема 12 управления горизонтальной разверткой подает напряжение VL низкого уровня в линию DRNL (n) управляющего сигнала, чтобы обеспечить прекращение вывода сигнала напряжения транзистором 114 усилителя в линию VSL (m) сигнала вертикальной развертки.

Более подробно, в этот момент схема 12 управления горизонтальной разверткой подает напряжение VH высокого уровня на затвор транзистора 123 уровня (см. фиг.3 (D)). Поскольку напряжение VGP затвора представляет собой напряжение VH высокого уровня, транзистор 123 уровня удерживается в закрытом состоянии в течение периода TN установки "не выбранного состояния".

В начале периода TN установки "невыбранного состояния" схема 12 управления горизонтальной разверткой подает короткий импульс напряжения VH высокого уровня с длительностью импульса Т1 на затвор транзистора 121 уровня (см. фиг.3 (В)). Следует отметить, что во время этого импульса транзистор 122 уровня удерживается в закрытом состоянии.

Поскольку напряжение VGN1 затвора представляет собой напряжение VH высокого уровня, только транзистор 121 уровня удерживается в открытом состоянии, а управляющий сигнал SDRN с напряжением VLL самого низкого уровня подается в линию DRNL (n) управляющего сигнала.

В результате, как показано на фиг.3 (А), управляющий сигнал SDRN быстро падает с напряжения VH высокого уровня до напряжения VLL самого низкого уровня,

В начале следующего периода TS выбранного состояния управляющий сигнал SDRN должен повыситься с напряжения VLL самого низкого уровня до напряжения VH высокого уровня. В этот момент схема 12 управления горизонтальной разверткой обеспечивает постепенный возврат управляющего сигнала SDRN от напряжения VLL самого низкого уровня к напряжению VH высокого уровня.

В частности, после подачи короткого импульса напряжения VH высокого уровня на затвор транзистора 121 уровня схема 12 управления горизонтальной разверткой подает напряжение VH высокого уровня к затвору транзистора 122 уровня в течение периода Т2 до конца периода TN установки "невыбранного состояния" (см. фиг.3 (С)). Разумеется, длительность импульса Т1 значительно короче периода Т2 (Т2>>Т1).

Поскольку напряжение VGN2 затвора представляет собой напряжение VH высокого уровня, только транзистор 122 уровня удерживают в открытом состоянии, и управляющий сигнал SDRN с напряжением VL низкого уровня подают в линию DRNL (n) управляющего сигнала.

В результате, как показано на фиг.3 (А), управляющий сигнал SDRN повышается от напряжения VLL самого низкого уровня до напряжения VL низкого уровня для перевода транзистора 114 усилителя в закрытое состояние, а затем медленно возвращается к напряжению VH высокого уровня. Напряжение, до которого управляющий сигнал SDRN быстро спадает в начале периода TN установки "невыбранного состояния" (напряжение VLL самого низкого уровня) можно рассматривать как отрицательный выброс, выходящий за пределы напряжения VL низкого уровня.

Как описано выше, в течение периода TN установки "невыбранного состояния" схема 12 управления горизонтальной разверткой обеспечивает быстрое падение управляющего сигнала SDRN от напряжения VH высокого уровня до напряжения VLL самого низкого уровня и его повышение от напряжения VLL самого низкого уровня до напряжения VL низкого уровня с последующим медленным возвратом до напряжения VH высокого уровня, что сокращает период TN установки "невыбранного состояния" и обеспечивает управление схемой 11 пикселя с высокой скоростью.

Вариант схемы 12 управления горизонтальной разверткой

В схеме 12 управления горизонтальной разверткой, когда происходит спад управляющего сигнала SDRN, транзистор 121 уровня удерживается в открытом состоянии, а транзистор 122 уровня удерживается в закрытом состоянии (период Т1 на фиг.3).

В этот момент, поскольку напряжение VL низкого уровня выше напряжения VLL самого низкого уровня (VL>VLL), разность потенциалов между ними может привести к короткому замыканию в схеме 12 управления горизонтальной разверткой из-за паразитного диода транзистора 122 уровня.

Для недопущения описанного выше короткого замыкания схема 12а управления горизонтальной разверткой в данном варианте выполнена так, как показано на фиг.4.

На фиг.4 показана принципиальная схема, представляющая вариант схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения. На фиг.4 показана только часть схемы, относящейся к n-й строке.

Как показано на фиг.4, схема 12а управления горизонтальной разверткой включает в себя транзистор 124 уровня в дополнение к транзисторам 121, 122, 123 уровня. Например, в качестве транзистора 124 уровня используется n-канальный МОП-транзистор.

Транзистор 124 уровня помещен между узлом ND2 и транзистором 122 уровня. Более подробно, исток транзистора 124 уровня подключен к стоку транзистора 122 уровня, а сток подключен к узлу ND2.

Следует отметить, что первый транзистор в соответствии с изобретением соответствует транзистору 122 уровня, а второй транзистор в соответствии с изобретением соответствует транзистору 124 уровня.

На фиг.5 схематично показан вид в разрезе транзисторов уровня, представленных на фиг.4. Однако транзистор 123 уровня на фиг.5 не показан.

На фиг.5 S121, S122 и S124 обозначают соответственно электроды истока транзисторов 121, 122 и 124 уровня. D121, D122 и D124 обозначают соответственно электроды стоков транзисторов 121, 122 и 124 уровня. G121, G122 и G124 обозначают соответственно провода затвора транзисторов 121, 122 и 124 уровня.

Как показано на фиг.5, подложка SB 121 транзистора 121 уровня соединена с источником напряжения с напряжением VLL самого низкого уровня. Подложка SB 122 транзистора 122 уровня соединена с источником напряжения VL низкого уровня. Подложка SB 124 транзистора 124 уровня соединена с источником напряжения с напряжением VLOW самого низкого уровня.

Напряжение VLOW самого низкого уровня равно или ниже напряжения VLL самого низкого уровня (VLL≥VLOW). VLOW может представлять собой отрицательное напряжение (например, -1 В). В данном варианте VLOW представляет собой потенциал земли GND, равный напряжению VLL самого низкого уровня.

Если транзистор 124 уровня отсутствует, как показано на фиг.5, то при падении управляющего сигнала SDRN может возникать ток, протекающий через паразитный диод (ток, протекающий между уровнем потенциальной ямы р-типа и уровнем стока транзистора 122 уровня), приводя к возникновению короткого замыкания в цепи.

Благодаря помещению транзистора 124 уровня между узлом ND2 и транзистором 122 уровня, можно не допустить протекание тока из-за паразитного диода, что предотвращает возникновение короткого замыкания в цепи.

Далее будет описана работа схемы 12а управления горизонтальной разверткой, показанной на фиг.4.

На фиг.6 показана временная диаграмма, представляющая пример работы схемы управления горизонтальной разверткой, показанной на фиг.4.

Следует отметить, что на фиг.6 (D) показано напряжение VGN3 затвора, поданное на затвор транзистора 124 уровня, и на фиг.6 (Е) показано напряжение VGP затвора, поданное на затвор транзистора 123 уровня.

Управляющий сигнал SDRN, напряжение VGN1 затвора, поданное на затвор транзистора 121 уровня и напряжение VGN2 затвора, поданное на затвор транзистора 122 уровня, показанные соответственно на фиг.6 (А), 6 (В) и 6 (С), идентичны таким же сигналам в схеме 12 управления горизонтальной разверткой, показанной на фиг.3 (А), 3 (B) и 3 (С).

Как показано на фиг.6 (С) и 6 (D), схема 12а управления горизонтальной разверткой подает напряжение VGN3 затвора на затвор транзистора 124 уровня, при этом напряжение VGN3 затвора изменяется так же, как и напряжение VGN2 затвора. Таким образом, когда VGN2 напряжение затвора представляет собой напряжение VH высокого уровня, напряжение VGN3 затвора также представляет собой напряжение VH высокого уровня. Когда напряжение VGN2 затвора представляет собой напряжение VL низкого уровня, напряжение VGN3 затвора также представляет собой напряжение VLOW низкого уровня (или напряжение VL низкого уровня).

В дальнейшем описании варианта выполнения описан датчик 1 изображения КМОП, включающий в себя схему 12а управления горизонтальной разверткой, имеющую конфигурацию схемы, показанную на фиг.4.

Работа датчика изображения КМОП, в частности, работа пиксельной схемы 11 в n-й строке и в m-м столбце описана ниже со ссылкой на фиг.7.

На фиг.7 показана временная диаграмма, представляющая пример работы датчика изображения КМОП в соответствии с первым вариантом выполнения. На фиг.7 (А) показан управляющий сигнал SDRN. На фиг.7 (В) показан сигнал SRST сброса. На фиг.7 (C) показан сигнал STRN передачи.

Во время периода TS выбранного состояния с момента времени t1 до момента времени t4 схема 12а управления горизонтальной разверткой подает управляющий сигнал SDRN с напряжением VH высокого уровня в линию DRNL (n) управляющего сигнала (см. фиг.7 (А)).

В момент времени t2 схема 12а управления горизонтальной разверткой подает импульс сигнала SRST сброса (напряжение VH высокого уровня) в линию RSTL(n) сигнала сброса транзистора 113 сброса (см. фиг.7 (В)).

В течение этого импульса транзистор 113 сброса удерживается в открытом состоянии. В результате происходит сброс потенциала плавающей диффузионной области ПД до напряжения VH высокого уровня.

Во время t3 схема 12а управления горизонтальной разверткой подает импульс сигнала STRN передачи (напряжение VH высокого уровня) в линию TRNL (n) сигнала передачи транзистора 112 передачи (см. фиг.7 (С)).

В течение этого импульса транзистор 112 передачи удерживается в открытом состоянии. В результате происходит передача заряда, сохраненного в период сохранения заряда, устройством 111 фотоэлектрического преобразования в плавающую диффузионную область ПД.

Когда происходит передача заряда из устройства 111 фотоэлектрического преобразования в плавающую диффузионную область ПД, потенциал плавающей диффузионной области ПД изменяется в зависимости от величины заряда, и этот потенциал подают на затвор транзистора 114 усилителя. Поскольку на сток транзистора 114 усилителя подают напряжение VDD источника, транзистор 114 усилителя усиливает потенциал плавающей диффузионной области ПД в зависимости от напряжения между затвором и истоком и выводит усиленный потенциал в линию VSL (m) сигнала вертикальной развертки.

Схема 13 горизонтальной передачи выбирает линию VSL (m) сигнала вертикальной развертки, открывая/закрывая переключатель 132 для m-го столбца, и считывает сигнал из пиксельной схемы 11 выбранного столбца. В этот момент схема 131 столбца преобразует аналоговый сигнал напряжения, поданный в линию (m) сигнала вертикальной развертки, в цифровой сигнал и выводит этот цифровой сигнал в линию HSCNL сигнала горизонтальной передачи.

Затем схема 13 горизонтальной передачи вводит цифровой сигнал после обработки CDS в качестве выходного сигнала SIG в сигнальный процессор, который представляет собой внешнее устройство для датчика изображения КМОП.

После считывания заряда схема 12а управления горизонтальной разверткой прекращает вывод сигнала из транзистора 114 усилителя для перевода пиксельной схемы 11 в невыбранное состояние.

Более подробно, в период TN установки "невыбранного состояния", от момента времени t4 до момента времени t6, схема 12а управления горизонтальной разверткой подает импульс сигнала SRST сброса (напряжение VH высокого уровня) в линию RSTL сигнала сброса транзистора 113 сброса (см. фиг.7 (В)).

В начале периода TN установки "невыбранного состояния" схема 12а управления горизонтальной разверткой подает короткий импульс управляющего сигнала SDRN с напряжением VLL самого низкого уровня с длительностью импульса Т1 (фиг.3) в линию DRNL (n) управляющего сигнала в течение промежутка времени от момента времени t4 до момента времени t5. В результате этого происходит быстрое падение уровня напряжения управляющего сигнала SDRN с напряжения VH высокого уровня до напряжения VLL самого низкого уровня.

Далее схема 12а управления горизонтальной разверткой подает управляющий сигнал SDRN с напряжением VL низкого уровня в линию DRNL (n) управляющего сигнала в течение промежутка времени от момента времени t5 до момента времени t6.

В результате потенциал плавающей диффузионной области ПД устанавливается равным напряжению VL низкого уровня.

Таким образом, на затвор транзистора 114 усилителя подается напряжение VL низкого уровня. Когда начинается период TS выбранного состояния для следующей строки на сток транзистора 114 усилителя подается напряжение VDD источника, а в линию VSL (m) сигнала вертикальной развертки подается сигнал напряжения (более высокого, чем напряжение VL низкого уровня) в результате считывания заряда из пиксельной схемы 11 другой строки. В соответствии с этим, транзистор 114 усилителя удерживается в закрытом состоянии при выборе другого ряда.

Как описано выше, транзистор 113 сброса управляет выходным сигналом транзистора 114 усилителя путем установки потенциала плавающей диффузионной области ПД равным напряжению VH высокого уровня, напряжению VL низкого уровня или напряжению VLL самого низкого уровня.

Транзистор 114 усилителя усиливает потенциал плавающей диффузионной области ПД и выводит усиленный потенциал как сигнал напряжения в линию VSL (m) сигнала вертикальной развертки.

На этом завершается работа датчика 1 изображения КМОП в одном периоде Н горизонтальной развертки.

В соответствии с первым вариантом выполнения, в пиксельной схеме 11, управляемой 3 транзисторами, сток транзистора 113 сброса подключен к линии DRNL (n) управляющего сигнала, а сток транзистора 114 усилителя подключен к напряжению VDD источника.

В период TN установки "невыбранного состояния" для пиксельной схемы 11 схема 12а управления горизонтальной разверткой быстро снижает уровень напряжения, поданного в линию DRNL (n) управляющего сигнала с напряжения VH самого высокого уровня до напряжения VLL самого низкого уровня, затем увеличивает его с напряжения VLL самого низкого уровня до напряжения VL низкого уровня и затем постепенно возвращает его к напряжению VH высокого уровня.

Поэтому пиксельной схемой, управляемой 3 транзисторами, можно управлять с высокой скоростью для считывания пикселя с высокой частотой кадров. Этот момент описан ниже со ссылкой на фиг.8-10.

На фиг.8 показана принципиальная схема, представляющая подробный пример пиксельного блока и схемы управления горизонтальной разверткой в соответствии с первым вариантом выполнения. Однако на фиг.8 показаны пиксельные схемы 11 в n-й строке, в которой отсутствует линия RSTL сигнала сброса и т.п. Ссылочной позицией 12а (n) на фиг.8 обозначена часть схемы 12а управления горизонтальной разверткой, относящаяся к n-й строке (см. фиг.4).

В n-ой строке пиксельная схема 11 (L) в первом столбце, расположенном дальше всего от схемы 12а (n) управления горизонтальной разверткой, и пиксельная схема 11 (R), находящаяся в последнем столбце, расположенном ближе всего к схеме 12а (n) управления горизонтальной разверткой, параллельно соединены с линией DRNL (n) управляющего сигнала, в которой имеется сопротивление R проводов и паразитная емкость С.

Соответственно, происходит затухание управляющего сигнала SDRN из-за сопротивления R проводов и возникает задержка из-за паразитной емкости С на пути от пиксельной схемы 11 (R) к пиксельной схеме 11 (L). Распространение управляющего сигнала SDRN будет описано ниже со ссылкой на фиг.9 на основе моделирования с использованием компьютера.

На фиг.9 показан результат моделирования для датчика изображения КМОП в соответствии с первым вариантом выполнения.

На фиг.9 (А) показана форма управляющего сигнала SDRN (L), когда управляющий сигнал SDRN (см. фиг.7 (А)) достигает пиксельной схемы 11 (L) (см. фиг.8). На фиг.9 (В) показана форма управляющего сигнала SDRN (R), когда управляющий сигнал SDRN достигает пиксельной схемы 11 (R) (см. фиг.8).

На фиг.9 (С) показано напряжение VGN1 затвора (см. фиг.6 (В)). На фиг.9 (D) показано напряжение VGN2 затвора (см. фиг.6 (С)). На фиг.9 (Е) показано напряжение VGN3 затвора (см. фиг.6 (D)). На фиг.9 (F) показано напряжение VGP затвора (см. фиг.6 (Е)).

Следует отметить, что на фиг.9 на горизонтальной оси представлено время, и на вертикальной оси показано напряжение (в вольтах) управляющего сигнала SDRN. Напряжение VGN2 затвора повышается от напряжения VLL самого низкого уровня до напряжения VH высокого уровня несколько раньше, чем момент времени t5. Напряжение VGN3 затвора повышается так же, как и напряжение VGN2.

В пиксельной схеме 11 (R), расположенной ближе всего к схеме 12а управления горизонтальной разверткой, на сток транзистора 113 сброса подается управляющий сигнал SDRN (R), форма которого показана на фиг.9 (В). Такой сигнал SDRN (R) управления быстро спадает с напряжения VH высокого уровня к напряжению VLL самого низкого уровня в момент времени t4.

В промежуток времени, в течение которого напряжение VGN1 затвора с длительностью импульса Т1 подается на затвор транзистора 121 уровня (см. фиг.9 (С)), управляющий сигнал SDRN (R) удерживается практически постоянным на напряжении VLL самого низкого уровня (см. фиг.9 (В)). Таким образом, управляющий сигнал SDRN (R) представляет собой отрицательный выброс до напряжения VLL самого низкого уровня, выходя за пределы напряжения VL низкого уровня.

Когда управляющий сигнал SDRN достигает пиксельной схемы 11 (L), расположенной дальше всего от схемы 12а управления горизонтальной разверткой, на сток транзистора 113 сброса подается управляющий сигнал SDRN (L), форма которого показана на фиг.9 (А).

Поскольку управляющий сигнал SDRN затухает из-за наличия сопротивления R проводов, управляющий сигнал SDRN не делает отрицательный выброс до напряжения VLL самого низкого уровня, и спадание управляющего сигнала SDRN (L) гораздо меньше, чем у управляющего сигнала SDRN (R). Вследствие задержки из-за паразитной емкости С, управляющий сигнал SDRN (L) достигает напряжения VL низкого уровня от напряжения VH высокого уровня в момент времени t5.

Поэтому подача напряжения VL низкого уровня на затвор транзистора 114 усилителя пиксельной схемы 11 в n-й строке в период TN установки "невыбранного состояния" может поместить n-ю строку в "невыбранное состояние".

Таким образом, учитывая сопротивление R проводов и паразитную емкость С линии DRNL (n) управляющего сигнала, схема 12а управления горизонтальной разверткой подает сигнал SDRN отрицательного выброса в линию DRNL (n) управляющего сигнала для сокращения времени спадания управляющего сигнала SDRN.

Для обычного датчика 3 изображения КМОП, показанного на фиг.13, управляющий сигнал SDRN распространяется, как показано на фиг.10.

На фиг.10 показан результат моделирования для обычного датчика изображения КМОП.

На фиг.10 (А) показана форма управляющего сигнала SDRN (L), когда управляющий сигнал SDRN (см. фиг.14 (А)) достигает пиксельной схемы 30 (L) (см. фиг.13). На фиг.10 (В) показана форма управляющего сигнала SDRN (R), когда управляющий сигнал SDRN достигает пиксельной схемы 30 (R).

На фиг.10 (С) показано напряжение VGN затвора, подаваемое на затвор транзистора 39. На фиг.10 (D) показано напряжение VGP затвора, подаваемое на затвор транзистора 38.

Пиксельная схема 30 (L) в первом столбце, расположенном дальше всего от схемы 37 управления горизонтальной разверткой, и схема 30 (R) пикселя в последнем столбце, расположенном ближе всего к схеме 37 управления горизонтальной разверткой, параллельно подключены к линии 310 управляющего сигнала, в которой имеется сопротивление R и паразитная емкость С.

В случае обычного датчика 3 изображения КМОП для обеспечения схождения обоих управляющих сигналов SDRN (L) и SDRN (R) к напряжению VL низкого уровня в течение периода TN установки "невыбранного состояния" (см. фиг.10 (А) и 10 (В)), период TN установки "не выбранного состояния" должен быть на 0,1 мкс или около этого дольше длительности управляющих сигналов SDRN (L) и SDRN (R), показанных на фиг.9.

Сокращение периода TN установки "невыбранного состояния" существенно для высокоскоростного управления пиксельной схемой, управляемой 3 транзисторами. Как описано выше, датчик изображения КМОП в соответствии с первым вариантом выполнения может существенно сократить период TN установки "невыбранного состояния" по сравнению с обычным датчиком и обеспечивает возможность управления пиксельной схемой с высокой скоростью, а также считывания пикселя с высокой частотой кадров.

Как описано выше, несмотря на резкое падение управляющего сигнала SDRN, флуктуация потенциала ямы р-типа транзисторов, включенных в пиксельную схему 11, может быть уменьшена для недопущения паразитного сигнала. Этот момент описан ниже со ссылкой на фиг.13.

В обычном датчике 3 изображения КМОП, управляемого 3 транзисторами, имеются два канала протекания тока от пиксельной схемы 30 в линию 35 сигнала вертикальной развертки.

Первый канал I1 протекания тока идет от линии 310 управляющего сигнала до линии 35 сигнала вертикальной развертки через транзистор 33 сброса и плавающую диффузионную область ПД (см. пунктирную стрелку на фиг.13).

Второй канал I2 протекания тока идет от линии 310 управляющего сигнала до линии 35 сигнала вертикальной развертки через транзистор 34 усилителя (см. пунктирную стрелку на фиг.13).

Эти два канала протекания тока образуются в результате параллельного подключения стока транзистора 33 сброса и стока транзистора 34 усилителя к линии 310 управляющего сигнала. Кроме того, импеданс второго канала 12 протекания тока ниже импеданса первого канала I1 протекания тока, поэтому управляющий сигнал SDRN необходимо более сильно буферизировать. Такая буферизация приводит к интенсивной флуктуации потенциала ямы р-типа транзисторов, включенных в пиксельную схему 30.

С другой стороны, в первом варианте выполнения сток транзистора 113 сброса подключен к линии DRNL (n) управляющего сигнала, а сток транзистора 114 усилителя подключен к напряжению VDD источника, поэтому второй канал 12 протекания тока отсутствует, что может уменьшить описанную выше флуктуацию потенциала ямы р-типа.

Таким образом, даже если управляющий сигнал SDRN спадает круто, можно уменьшить паразитный сигнал.

Следует отметить, что напряжение VH высокого уровня, подаваемое в линию DRNL (n) управляющего сигнала, не обязательно должно быть равным напряжению VDD источника, подключенного к стоку транзистора 114 усилителя. Для достижения низкого энергопотребления напряжение VH высокого уровня может быть установлено ниже напряжения VDD источника (VDD>VH>VL). С другой стороны, напряжение VDD источника может быть установлено ниже напряжения VH высокого уровня (VH>VDD>VL).

Установка напряжения VH высокого уровня на более высокое напряжение позволяет выполнять сброс плавающей диффузионной области ПД более высоким напряжением для увеличения уровня сигнала насыщения. Кроме того, четыре или более значения уровня напряжения можно использовать для постепенного возврата управляющего сигнала SDRN с напряжения VLL самого низкого уровня до напряжения VH высокого уровня в период TN установки "невыбранного состояния".

Например, в случае использования четырех уровней напряжения, четвертый уровень напряжения, который выше напряжения VL низкого уровня и который ниже напряжения VH высокого уровня, можно использовать для обеспечения возврата управляющего сигнала SDRN от напряжения VLL самого низкого уровня до напряжения VH высокого уровня через напряжение VL низкого уровня и напряжение четвертого уровня.

Второй вариант выполнения

В первом варианте выполнения управляющий сигнал SDRN подается в один конец линии DRNL (n) управляющего сигнала (см. фиг.8). С другой стороны, во втором варианте выполнения управляющий сигнал SDRN подают в оба конца линии DRNL (n) управляющего сигнала.

На фиг.11 показаны принципиальная схема, представляющая подробный пример пиксельного блока, и схема управления горизонтальной разверткой в соответствии со вторым вариантом выполнения. Однако на фиг.11 представлены пиксельные схемы 11 в n-й строке без линии сигнала RSTL сброса и т.п. Ссылочные позиции 12а-1 (n), 12а-2 (n), показанные на фиг.11, обозначают части схем 12а-1, 12а-2 управления горизонтальной разверткой, относящиеся к n-й строке.

Как показано на фиг.11, схемы 12а-1, 12а-2 управления горизонтальной разверткой, выполненные аналогично схеме, показанной на фиг.4, размещены с обеих сторон пиксельного блока 10. Схема 12а-1 (n) управления горизонтальной разверткой подключена к одному концу линии DRNL (n) управляющего сигнала. Схема 12а-2 (n) управления горизонтальной разверткой подключена к другому концу линии DRNL (n) управляющего сигнала.

Схемы 12а-1, 12а-2 управления горизонтальной разверткой одновременно подают управляющий сигнал SDRN в линию DRNL (n) управляющего сигнала в моменты времени, показанные на фиг.6 (А).

Среди пиксельных схем 11, подключенных к линии DRNL (n) управляющего сигнала, пиксельная схема 11, помещенная в центре, принимает управляющий сигнал SDRN с обоих концов линии DRNL (n) управляющего сигнала. Таким образом, датчик изображения КМОП в соответствии со вторым вариантом выполнения может управлять пиксельной схемой 11 с более высокой скоростью, чем в соответствии с первым вариантом выполнения.

Используя такую возможность, датчик 1 изображения КМОП можно использовать в качестве устройства формирования изображения для цифровой камеры, видеокамеры и т.п.

На фиг.12 показан пример конфигурации камеры, в которой используется датчик изображения КМОП в соответствии с вариантами выполнения изобретения.

Как показано на фиг.12, камера 2 включает в себя датчик 1 изображения КМОП в качестве устройства формирования изображения, оптическую систему для направления падающего света (формирования изображения объекта) на область пикселя (пиксельный блок 10) датчика 1 изображения КМОП и процессор 22 сигналов (DSP процессор цифровых сигналов) для обработки выходного сигнала датчика 1 изображения КМОП. Оптическая система включает в себя, например, объектив 21 для фокусирования падающего света (света от изображения) на поверхность формирования изображения.

Процессор 22 сигналов выполняет обработку изображения для выходного сигнала SIG из датчика 1 изображения КМОП. Сигнал изображения, обработанный процессором 22 сигналов, записывают на носитель записи, такой как запоминающее устройство. Видеоинформацию, записанную на носитель записи, выводят в виде бумажной копии с помощью принтера или тому подобного. Сигнал изображения, обработанный процессором 22 сигналов, отображают в виде движущегося изображения на мониторе, включающем в себя жидкокристаллический дисплей.

Как описано выше, включение датчика изображения КМОП в камеру и т.п. может позволить уменьшить уровни шумов в камере, в том числе паразитный сигнал, и также может позволить считывать пиксель с высокой скоростью.

Описание ссылочных позиций и обозначений

1 датчик изображения КМОП

2 камера

3 датчик изображения КМОП

10 пиксельный блок

11 пиксельная схема

12 схема управления горизонтальной разверткой

13 схема горизонтальной передачи

14 генератор синхронизации

15 схема источника постоянного тока

21 объектив

22 процессор сигналов

111 устройство фотоэлектрического преобразования

112 транзистор передачи

113 транзистор сброса

114 транзистор усилителя

121-124 транзистор уровня

131 схема столбца

132 переключатель

DRNL Линия управляющего сигнала

ПД плавающая диффузионная область

RSTL Линия сигнала сброса

TRNL Линия сигнала передачи

Изобретение относится к устройствам формирования изображения. Техническим результатом является понижение шумов, включая паразитный сигнал, а также обеспечение возможности считывать пиксель с высокой скоростью. Результат достигается тем, что в пиксельной схеме 11, управляемой 3 транзисторами, сток транзистора 113 сброса соединен с линией DRNL (n) управляющего сигнала, а сток транзистора 114 усилителя соединен с напряжением VDD источника. Схема 12а управления горизонтальной разверткой быстро понижает уровень напряжения, поданного в линию DRNL (n) управляющего сигнала с напряжения VH высокого уровня к напряжению VLL самого низкого уровня, затем увеличивает его с напряжения VLL самого низкого уровня до напряжения VL низкого уровня и затем постепенно возвращает его к напряжению VH высокого уровня. 3 н. и 4 з.п. ф-лы, 14 ил.

1. Устройство формирования изображения, содержащее:

множество пиксельных схем, расположенных в виде матрицы;

линию управления выбором, соединенную с множеством пиксельных схем, расположенных в одном направлении; и

схему управления выбором, выполненную с возможностью выборочной подачи сигнала управления выбором, имеющего множество разных уровней напряжения, в линию управления выбором для выбора и управления пиксельными схемами,

при этом каждая из пиксельных схем содержит:

фотоэлектрический преобразователь для фотоэлектрического преобразования падающего света в заряд;

узел, в который заряд передается из фотоэлектрического преобразователя;

выходной транзистор, имеющий управляющий вывод, подключенный к указанному узлу, первый соединительный вывод, подключенный к источнику заданного напряжения, и второй соединительный вывод, подключенный к линии выходного сигнала, причем выходной транзистор выполнен с возможностью усиления потенциала указанного узла и вывода усиленного напряжения в линию выходного сигнала в качестве выходного сигнала; и

управляющий транзистор, имеющий третий соединительный вывод, подключенный к указанному узлу, и четвертый соединительный вывод, на который подается сигнал управления выбором через линию управления выбором,

причем управляющий транзистор выполнен с возможностью установки потенциала узла, к которому подключен управляющий вывод выходного транзистора, в потенциал, зависящий от уровня напряжения, и с возможностью управления сбросом потенциала указанного узла и выходным сигналом выходного транзистора,

при этом схема управления выбором выполнена с возможностью смещения уровня напряжения сигнала управления выбором, подаваемого через линию управления выбором, с первого уровня напряжения, при котором выходной транзистор удерживается в открытом состоянии, ко второму уровню напряжения, при котором выходной транзистор удерживается в закрытом состоянии, и постепенного возврата уровня напряжения сигнала управления выбором со второго уровня напряжения к первому уровню напряжения.

2. Устройство формирования изображения по п.1,

в котором множество уровней напряжения включают в себя:

первый уровень напряжения;

второй уровень напряжения; и

третий уровень напряжения, который представляет собой уровень опорного напряжения для удержания выходного транзистора в закрытом состоянии,

при этом схема управления выбором выполнена с возможностью смещения уровня напряжения сигнала управления выбором, поданного в линию управления выбором, с первого уровня напряжения ко второму уровню напряжения и возврата уровня напряжения сигнала управления выбором к первому уровню напряжения через третий уровень напряжения.

3. Устройство формирования изображения по п.2,

в котором схема управления выбором выполнена с возможностью

подачи сигнала управления выбором со вторым уровнем напряжения в линию управления выбором на более короткий промежуток времени, чем промежуток времени подачи сигнала управления выбором с уровнем напряжения, отличным от второго уровня напряжения.

4. Устройство формирования изображения по п.1,

в котором схема управления выбором содержит:

первый транзистор, имеющий пятый соединительный вывод, на который подается напряжение второго или третьего уровня напряжения, причем первый транзистор выполнен с возможностью вывода напряжения с уровнем напряжения, поданным на пятый соединительный вывод, в линию управления выбором; и

второй транзистор, имеющий ту же полярность, что и первый транзистор,

при этом второй транзистор имеет седьмой соединительный вывод, соединенный с шестым соединительным выводом первого транзистора, и имеет восьмой соединительный вывод, соединенный с линией управления выбором.

5. Устройство формирования изображения по п.1,

в котором схема управления выбором выполнена с возможностью

подачи сигнала управления выбором на оба конца линии управления выбором.

6. Способ управления устройством формирования изображения, содержащий:

первый этап, на котором выборочно подают сигнал управления выбором, имеющий множество разных уровней напряжения, в линию управления выбором, соединенную с множеством пиксельных схем, расположенных в одном направлении, для выбора и управления множеством пиксельных схем, причем выбранное множество пиксельных схем выполняют фотоэлектрическое преобразование падающего света в заряд и выводят напряжение, зависящее от величины заряда, в линию вывода сигнала в качестве выходного сигнала; и

второй этап, на котором прекращают вывод сигнала из множества пиксельных схем на заданный промежуток времени после считывания заряда множеством пиксельных схем,

при этом на первом этапе:

передают заряд, полученный в результате фотоэлектрического преобразования фотоэлектрическим преобразователем, в узел,

причем управляющий транзистор, имеющий третий соединительный вывод, подключенный к указанному узлу, и четвертый соединительный вывод, на который подают сигнал управления выбором через линию управления выбором, устанавливает потенциал указанного узла, к которому подключен управляющий вывод выходного транзистора, в потенциал, зависящий от уровня напряжения, и выполняет сброс потенциала указанного узла,

причем выходной транзистор, имеющий управляющий вывод, подключенный к указанному узлу, первый соединительный вывод, подключенный к источнику заданного напряжения, и второй соединительный вывод, подключенный к линии вывода сигнала, усиливает потенциал узла и выводит усиленное напряжение в качестве выходного сигнала в линию вывода сигнала под управлением управляющего транзистора,

при этом на втором этапе:

выполняют смещение уровня напряжения сигнала управления выбором, подаваемого через линию управления выбором, с первого уровня напряжения, при котором выходной транзистор удерживается в открытом состоянии, ко второму уровню напряжения, при котором выходной транзистор удерживается в закрытом состоянии, и постепенно возвращают уровень напряжения сигнала управления выбором со второго уровня напряжения к первому уровню напряжения.

7. Камера, содержащая:

устройство формирования изображения;

оптическую систему для направления падающего света на область пикселей устройства формирования изображения; и

процессор сигналов для обработки выходного сигнала, выводимого из устройства формирования изображения,

при этом устройство формирования изображения содержит:

множество пиксельных схем, расположенных в виде матрицы;

линию управления выбором, соединенную с множеством пиксельных схем расположенных в одном направлении; и

схему управления выбором, выполненную с возможностью выборочной подачи сигнала управления выбором, имеющего множество разных уровней напряжения, в линию управления выбором для выбора и управления пиксельными схемами,

при этом каждая из пиксельных схем содержит:

фотоэлектрический преобразователь для фотоэлектрического преобразования падающего света в заряд;

узел, в который передают заряд из фотоэлектрического преобразователя;

выходной транзистор, имеющий управляющий вывод, подключенный к указанному узлу, первый соединительный вывод, подключенный к источнику заданного напряжения, и второй соединительный вывод, подключенный к линии вывода сигнала, причем выходной транзистор выполнен с возможностью усиления потенциала указанного узла и вывода усиленного напряжения в линию выходного сигнала в качестве выходного сигнала; и

управляющий транзистор, имеющий третий соединительный вывод, подключенный к указанному узлу, и четвертый соединительный вывод, на который подается сигнал управления выбором через линию управления выбором, причем управляющий транзистор выполнен с возможностью установки потенциала узла, с которым соединен управляющий вывод выходного транзистора, в потенциал, зависящий от уровня напряжения, и с возможностью управления сбросом потенциала указанного узла и выходным сигналом выходного транзистора,

при этом схема управления выбором выполнена с возможностью смещения уровня напряжения сигнала управления выбором, подаваемого через линию управления выбором, с первого уровня напряжения, при котором выходной транзистор удерживается в открытом состоянии, ко второму уровню напряжения, при котором выходной транзистор удерживается в закрытом состоянии, и постепенного возврата уровня напряжения сигнала управления выбором со второго уровня напряжения к первому уровню напряжения.

| JP 11112018 А, 23.04.1999 | |||

| JP 9168117 А, 24.06.1997 | |||

| WO 2005069608 А1, 28.07.2005 | |||

| JP 2006101559 А, 13.04.2006 | |||

| ТВЕРДОТЕЛЬНОЕ УСТРОЙСТВО ЗАХВАТА ИЗОБРАЖЕНИЯ | 2006 |

|

RU2337502C2 |

Авторы

Даты

2013-05-10—Публикация

2009-09-16—Подача