Область техники, к которой относится изобретение

[0001] Настоящее изобретение относится к устройству фотоэлектрического преобразования и системе регистрации изображения.

Уровень техники

[0002] В выложенной японской патентной заявке № 2013-146045 раскрыто устройство фотоэлектрического преобразования, включающее в себя пиксели, которые выводят сигналы тока в соответствии с величинами заряда, генерируемого фотоэлектрическим преобразованием (фиг.2 выложенной японской патентной заявки № 2013-146045). Каждый пиксель включает в себя фотодиод и дифференциальный усилитель. Дифференциальный усилитель включает в себя первый входной транзистор и второй входной транзистор. Узел, на который переносятся заряды, генерируемые фотодиодом, подключен к затвору первого входного транзистора. Линия подачи напряжения сброса VRES подключена ко второму входному транзистору. Исток первого входного транзистора подключен к стоку первого транзистора выбора через резистор R1. Исток второго входного транзистора подключен к стоку первого транзистора выбора через резистор R2. Сток второго входного транзистора подключен к выходному узлу OUT через второй транзистор выбора. Сигнал тока, соответствующий величине заряда, генерируемого фотоэлектрическим преобразованием, выводится из выходного узла OUT. В устройстве фотоэлектрического преобразования, описанном в выложенной японской патентной заявке № 2013-146045, цифровой сигнал, соответствующий величине заряда, генерируемого фотоэлектрическим преобразованием, генерируется на основании сигнала тока, выводимого из выходного узла OUT пикселя.

[0003] Устройство фотоэлектрического преобразования, описанное в выложенной японской патентной заявке № 2013-146045, предусматривает включение дифференциального усилителя в каждый пиксель. Масштаб схемы каждого пикселя увеличивается, и не пригоден для многопиксельной конфигурации.

Раскрытие изобретения

[0004] Варианты осуществления настоящего изобретения предусматривают устройство фотоэлектрического преобразования, пригодное для упрощения конфигурации схемы каждого пикселя и получения многопиксельной конфигурации.

[0005] Один аспект настоящего изобретения предусматривает устройство фотоэлектрического преобразования, содержащее: фотоэлектрический преобразователь; транзистор, имеющий затвор, первый главный электрод и второй главный электрод, причем на затвор подается напряжение, соответствующее зарядам, генерируемым фотоэлектрическим преобразователем, линию управления, подключенную к первому главному электроду транзистора, и блок считывания, выполненный с возможностью считывания сигнала, соответствующего напряжению затвора; и регулятор напряжения, выполненный с возможностью изменения напряжения линии управления, в котором блок считывания генерирует цифровой сигнал, соответствующий напряжению затвора, на основании тока, текущего через второй главный электрод транзистора в течение периода, когда регулятор напряжения изменяет напряжение линии управления.

[0006] Дополнительные признаки настоящего изобретения явствуют из нижеследующего описания иллюстративных вариантов осуществления со ссылкой на прилагаемые чертежи.

Краткое описание чертежей

[0007] Фиг. 1 - блок-схема, демонстрирующая конфигурацию устройства фотоэлектрического преобразования согласно первому варианту осуществления;

[0008] фиг. 2 - принципиальная схема, демонстрирующая пример устройства пиксельной матрицы и регулятора напряжения согласно первому варианту осуществления;

[0009] фиг. 3 - принципиальная схема, демонстрирующая пример устройства компаратора в блоке считывания;

[0010] фиг. 4 - временная диаграмма, демонстрирующая операцию считывания сигнала из пикселя в первой строке и данном столбце согласно первому варианту осуществления;

[0011] фиг. 5 - принципиальная схема, демонстрирующая конфигурацию устройства фотоэлектрического преобразования согласно второму варианту осуществления;

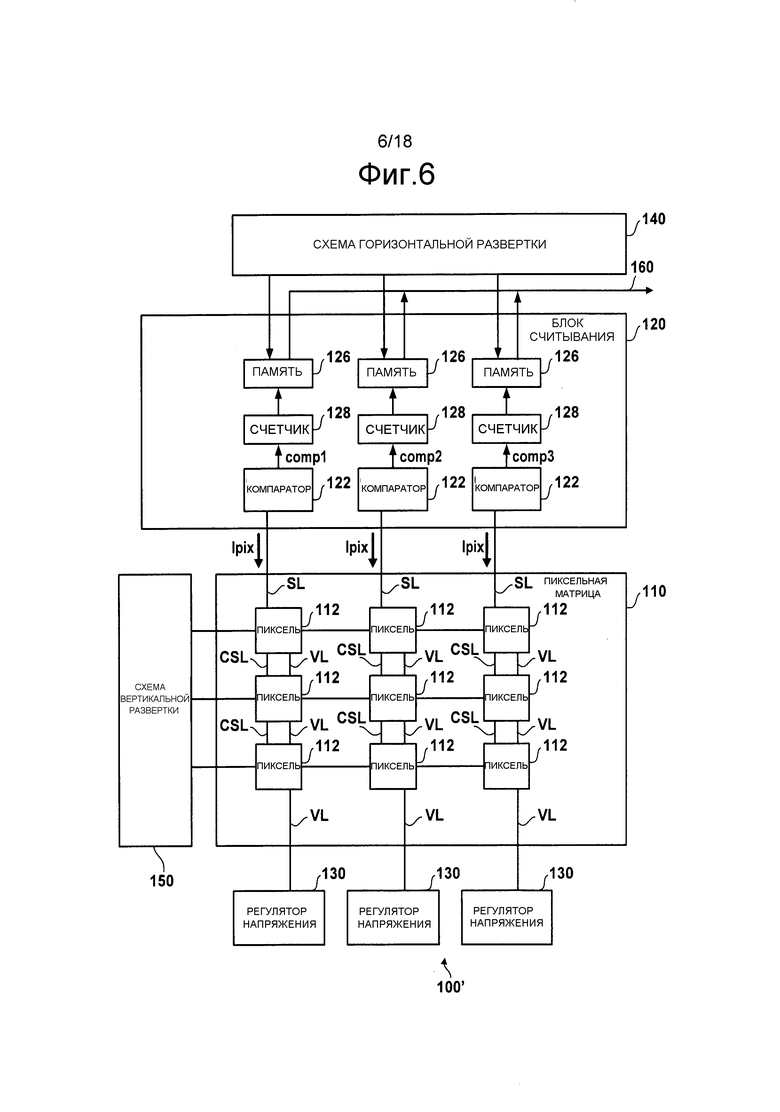

[0012] фиг. 6 - блок-схема, демонстрирующая конфигурацию устройства фотоэлектрического преобразования согласно третьему варианту осуществления;

[0013] фиг. 7 - временная диаграмма, демонстрирующая операцию считывания сигнала в первой строке и данном столбце согласно четвертому варианту осуществления;

[0014] фиг. 8 - блок-схема, демонстрирующая конфигурацию системы регистрации изображения согласно иллюстративному варианту осуществления;

[0015] фиг. 9A и 9B - принципиальные схемы, демонстрирующие конфигурацию регулятора напряжения устройства фотоэлектрического преобразования согласно пятому варианту осуществления;

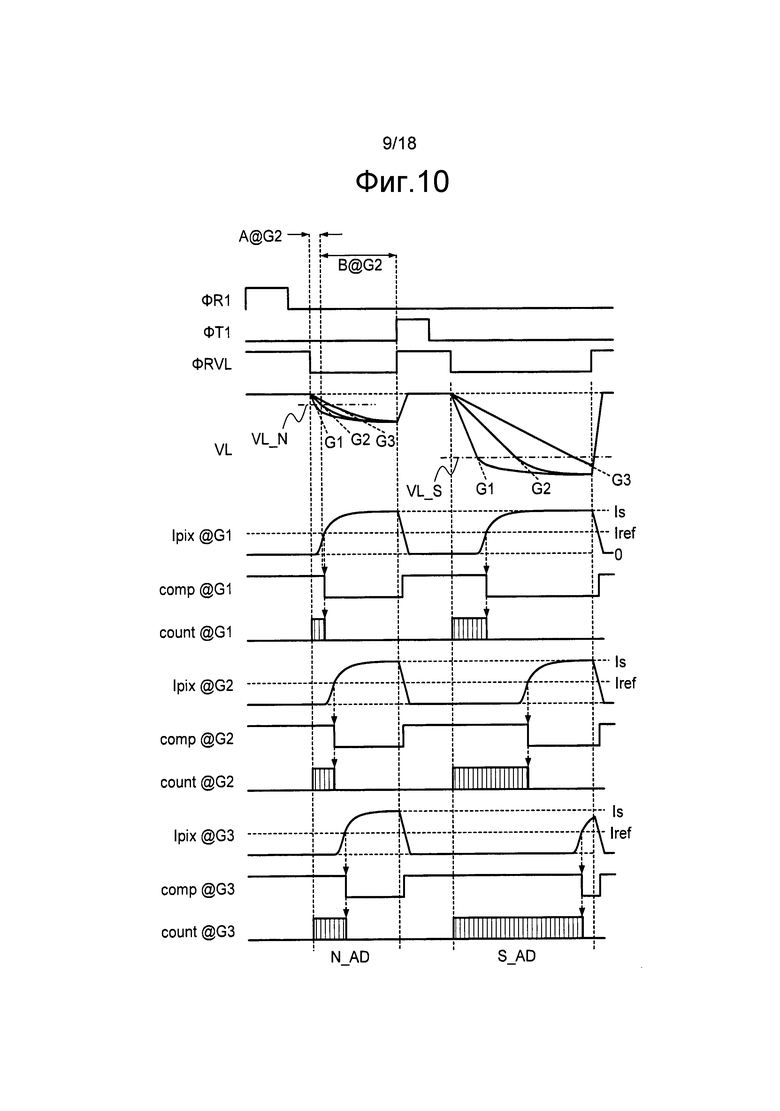

[0016] фиг. 10 - временная диаграмма, демонстрирующая операцию считывания сигнала в первой строке и данном столбце согласно пятому варианту осуществления;

[0017] фиг. 11 - принципиальная схема, демонстрирующая конфигурацию устройства фотоэлектрического преобразования согласно шестому варианту осуществления;

[0018] фиг. 12A и 12B - временные диаграммы, поясняющие операцию считывания устройства фотоэлектрического преобразования согласно шестому варианту осуществления;

[0019] фиг. 13 - принципиальная схема, демонстрирующая конфигурацию компаратора устройства фотоэлектрического преобразования согласно седьмому варианту осуществления;

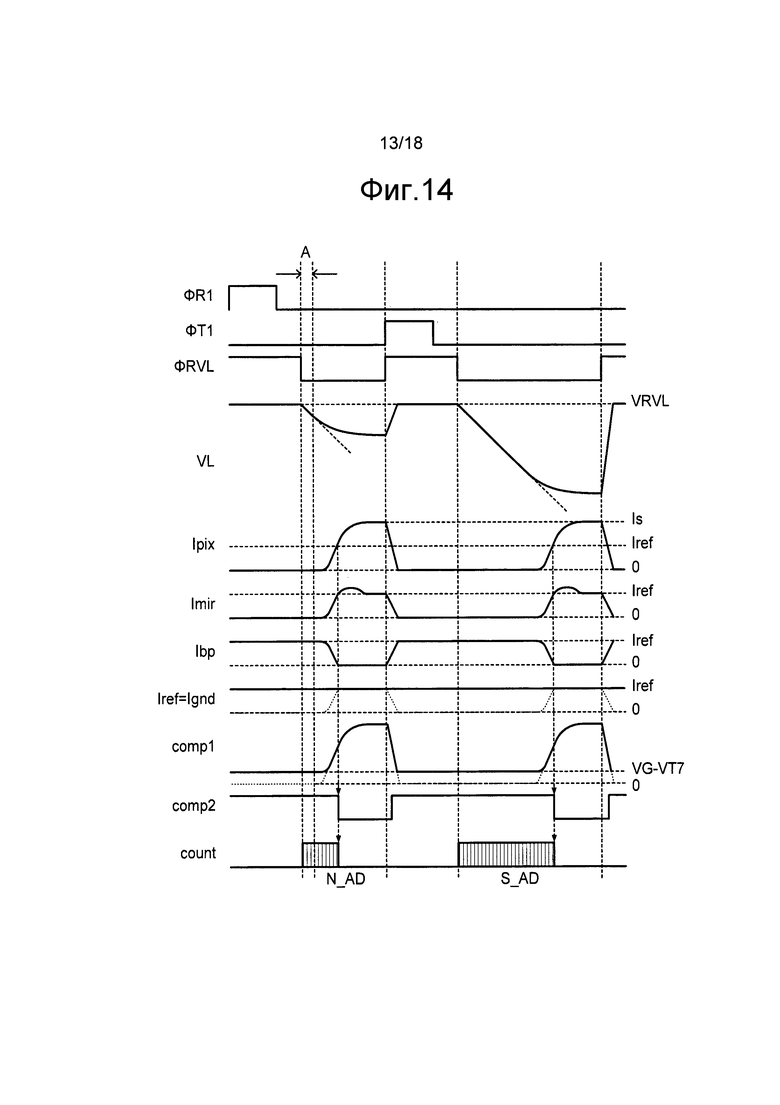

[0020] фиг. 14 - временная диаграмма, демонстрирующая операцию считывания сигнала в первой строке и данном столбце согласно седьмому варианту осуществления;

[0021] фиг. 15 - принципиальная схема, демонстрирующая конфигурацию компаратора устройства фотоэлектрического преобразования согласно восьмому варианту осуществления;

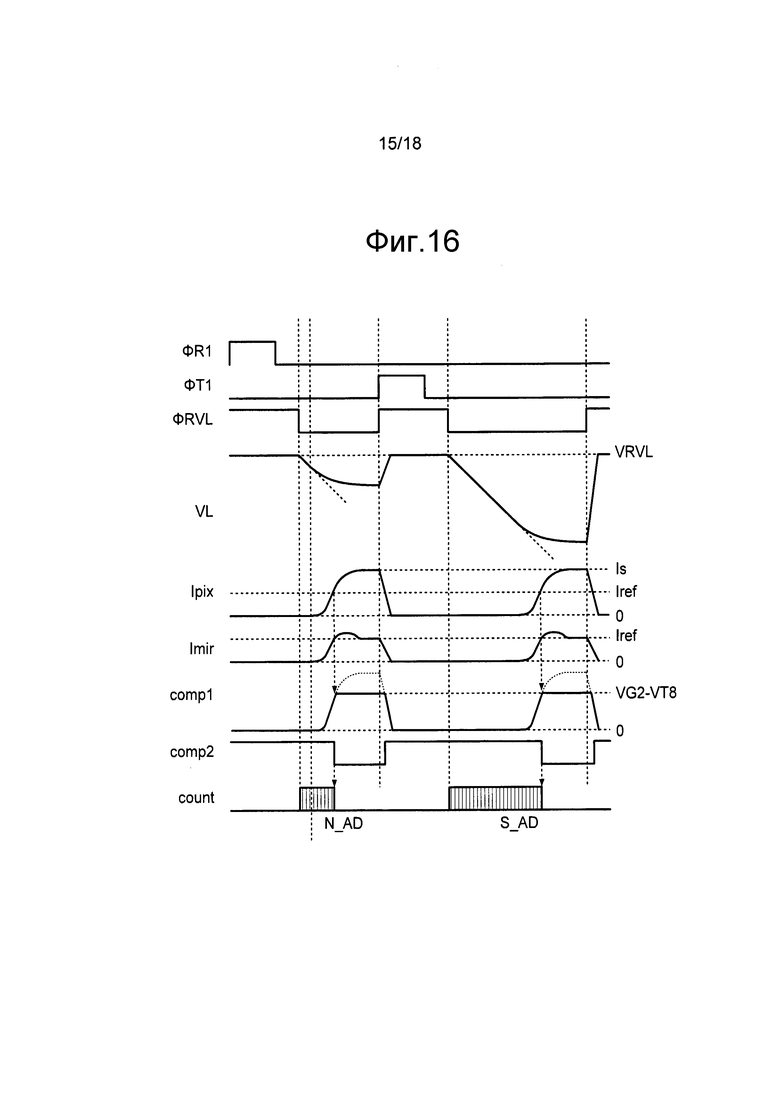

[0022] фиг. 16 - временная диаграмма, демонстрирующая операцию считывания сигнала в первой строке и данном столбце согласно восьмому варианту осуществления;

[0023] фиг. 17 - принципиальная схема, демонстрирующая конфигурацию компаратора устройства фотоэлектрического преобразования согласно девятому варианту осуществления;

[0024] фиг. 18 - временная диаграмма, демонстрирующая операцию считывания сигнала в первой строке и данном столбце согласно девятому варианту осуществления;

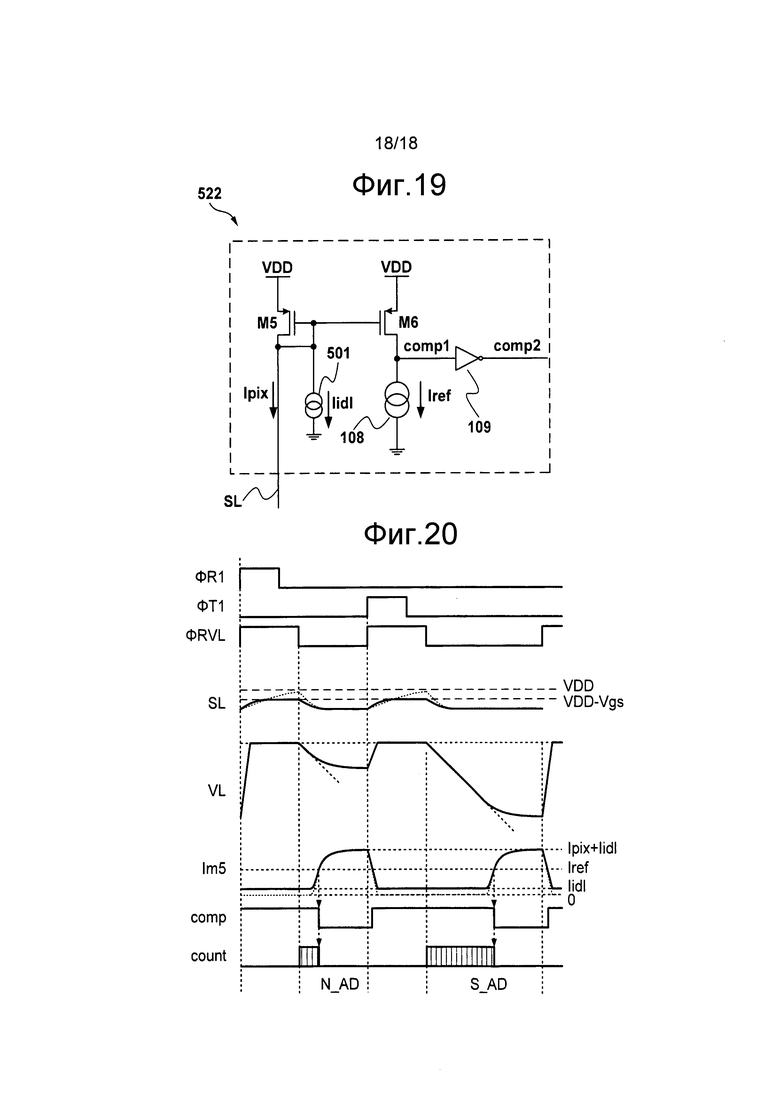

[0025] фиг. 19 - принципиальная схема, демонстрирующая конфигурацию компаратора устройства фотоэлектрического преобразования согласно десятому варианту осуществления; и

[0026] фиг. 20 - временная диаграмма, демонстрирующая операцию считывания сигнала в первой строке и данном столбце согласно десятому варианту осуществления.

Осуществление изобретения

[0027] Настоящее изобретение будет описано с использованием иллюстративных вариантов осуществления со ссылкой на прилагаемые чертежи.

[0028] На фиг. 1 показана конфигурация устройства 100 фотоэлектрического преобразования согласно первому варианту осуществления настоящего изобретения. Устройство 100 фотоэлектрического преобразования можно, в конце концов, рассматривать как устройство, которое включает в себя, по меньшей мере, один пиксель 112. Обычно устройство 100 фотоэлектрического преобразования может быть выполнить в виде полупроводникового датчика изображения, имеющего пиксельную матрицу 110, в которой множество пикселей 112 размещено в одном измерении или в двух измерениях. В примере, показанном на фиг. 1, множество пикселей 112 образует множество строк и множество столбцов, то есть размещено в двух измерениях.

[0029] Устройство 100 фотоэлектрического преобразования содержит регулятор 130 напряжения, который подает управляющее напряжение V_VL на каждый пиксель 112 по линии VL управления, и блок 120 считывания, который считывает сигнал из каждого пикселя 112 по измерительной линии SL. В этом случае, для каждого столбца пиксельной матрицы 110 предусмотрено по одному регулятору 130 напряжения.

[0030] Устройство 100 фотоэлектрического преобразования дополнительно включает в себя схему 150 вертикальной развертки (вертикальный селектор) и схему 140 горизонтальной развертки (горизонтальный селектор), которые оба выбирают пиксель 112 в качестве цели считывания сигнала. Схема 150 вертикальной развертки выбирает строку целей считывания из множества строк в пиксельной матрице 110, и блок 120 считывания считывает сигнал каждого выбранного пикселя 112 строки по измерительной линии SL. Схема 140 горизонтальной развертки выбирает пиксель 112 столбца целей считывания из цифровых сигналов множества пикселей 112 столбца, считанных блоком 120 считывания и выводит сигнал каждого пикселя 112 в линию 160 выходного сигнала. В частности, схема 140 горизонтальной развертки выбирает столбец целей считывания из множества столбцов в пиксельной матрице 110.

[0031] Каждый регулятор 130 напряжения изменяет напряжение V_VL линии VL управления. Каждый пиксель 112 строки, выбранный схемой 150 вертикальной развертки, образует путь тока в измерительной линии SL, когда напряжение V_VL линии VL управления меняется на напряжение, соответствующее величине заряда, генерируемого фотоэлектрическим преобразованием, таким образом, пропуская пиксельный ток Ipix. На основании пиксельного тока Ipix, блок 120 считывания генерирует цифровой сигнал, соответствующий величине заряда, генерируемого фотоэлектрическим преобразованием.

[0032] Блок 120 считывания включает в себя компараторы 122, счетчик 124 и блоки 126 памяти. Каждый компаратор 122 обнаруживает, что значение пиксельного тока Ipix превышает значение (порог) опорного тока Iref. Счетчик 124 начинает операцию отсчета при заранее определенном хронировании. В блоках 126 памяти удерживаются значения отсчета счетчика 124 в качестве цифровых сигналов, соответствующих сигналам пикселей 112, в соответствии с переходом сигналов comp1, comp2 и comp3 результата сравнения компараторов 122. В этом случае, "1", "2" и "3" сигналов comp1, comp2 и comp3 результата сравнения являются идентификаторами, позволяющими различать сигналы comp результата сравнения множества компараторов 122, соответственно, соответствующих множеству столбцов пиксельной матрицы 110.

[0033] На фиг. 2 показан пример устройства пиксельной матрицы 110 и регуляторов 130 напряжения. На Фиг. 3 показан пример устройства компаратора 122 блока 120 считывания. Конфигурация и принцип работы устройства 100 фотоэлектрического преобразования будут подробно описаны со ссылкой на фиг. 1 - 3.

[0034] Каждый пиксель 112 включает в себя, в качестве основных компонентов, фотоэлектрический преобразователь PD, например, фотодиод и транзистор (считывающий транзистор) M3, на затвор которого подается напряжение, соответствующее зарядам, генерируемым фотоэлектрическим преобразователем PD. Каждый пиксель 112 может включать в себя преобразователь заряда в напряжение (плавающую диффузионную область) FD, подключенный к затвору транзистора M3, и транзистор M1 переноса, который переносит заряды, генерируемые фотоэлектрическим преобразователем PD, на преобразователь FD заряда в напряжение. Каждый пиксель 112 может дополнительно включать в себя транзистор M2 сброса, который сбрасывает напряжение преобразователя FD заряда в напряжение. Каждый пиксель 112 может дополнительно включать в себя транзистор M4 выбора. Транзистор M4 выбора размещен на пути между транзистором M3 и линией VL управления или на пути между транзистором M3 и измерительной линией SL.

[0035] Транзистор M1 переноса отпирается, когда схема 150 вертикальной развертки активирует сигнал ΦT переноса (ΦT1, ΦT2, или ΦT3). Затем транзистор M1 переноса переносит заряды фотоэлектрического преобразователя PD на преобразователь FD заряда в напряжение. В этом случае, "1", "2" и "3" сигналов переноса ΦT1, ΦT2 и ΦT3 являются идентификаторами, позволяющими различать сигналы ΦT переноса, соответствующие множеству строк пиксельной матрицы 110. Транзистор M2 сброса отпирается, когда сигнал ΦR сброса (ΦR1, ΦR2 или ΦR3) активируется и сбрасывает напряжение преобразователя FD заряда в напряжение до напряжения сброса, соответствующего напряжению линии VR напряжения сброса. В этом случае, "1", "2" и "3" сигналов ΦR1, ΦR2 и ΦR3 сброса являются идентификаторами, позволяющими различать сигналы ΦR сброса, соответствующие множеству строк пиксельной матрицы 110. Транзистор M4 выбора отпирается, когда сигнал SEL выбора (SEL1, SEL2 или SEL3) активируется и устанавливает пиксель 112, соответствующий сигналу SEL выбора в состоянии выбора. В этом случае, "1", "2" и "3" сигналов SEL1, SEL2 и SEL3 выбора являются идентификаторами, позволяющими различать сигналы SEL выбора, соответствующие множеству строк пиксельной матрицы 110.

[0036] Пиксель 112 согласно первому варианту осуществления настоящего изобретения не включает в себя ни одного дифференциального усилителя, представленного в устройстве фотоэлектрического преобразования, описанном в выложенной японской патентной заявке № 2013-146045. Пиксель 112 согласно первому варианту осуществления настоящего изобретения имеет меньший масштаб схемы, чем у пикселя, описанного в патентном источнике 1, и поэтому пригоден для многопиксельной конфигурации.

[0037] Напряжение V_VL линии VL управления регулируется регулятором 130 напряжения. Каждый регулятор 130 напряжения регулирует напряжение линии VL управления для повышения напряжения между затвором транзистора M3 и истоком (первым главным электродом) транзистора M3, то есть в направлении из запертого состояния в отпертое состояние транзистора M3. Другими словами, согласно первому варианту осуществления, регулятор 130 напряжения снижает напряжение V_VL линии VL управления.

[0038] Каждый регулятор 130 напряжения включает в себя конденсатор 132, переключатель 136 и источник 134 тока. Конденсатор 132 включает в себя первый узел 137, подключенный к линии VL управления, и второй узел 138, подключенный к заранее определенному напряжению (в этом примере, напряжению земли). Переключатель 136 размещен на пути между первым узлом 137 конденсатора 132 и линией первого напряжения, на которую подается первое напряжение VRVL. Переключатель 136 устанавливает напряжение первого узла 137 конденсатора 132 и напряжение V_VL линии VL управления на напряжение, соответствующее первому напряжению VRVL, когда активирован сигнал ΦRVL сброса. Источник 134 тока размещен между первым узлом 137 (и линией VL управления) конденсатора 132 и линией второго напряжения (в этом примере, линией напряжения земли), на которую подается второе напряжение (в этом случае, напряжение земли). Когда сигнал ΦRVL сброса активируется, заряды, накопленные в конденсаторе 132, удаляются значением тока Is через источник 134 тока, таким образом, линейно снижая напряжение V_VL линии VL управления.

[0039] Компаратор 122 обнаруживает, что ток Ipix, текущий через сток (второй главный электрод) транзистора M3 каждого пикселя 112 превышает значение (порог) опорного тока Iref. Компаратор 122 включает в себя транзисторы M5 и M6, например p-МОП-транзистор, которые образуют токовое зеркало, и источник 108 тока, через который течет опорный ток Iref. Компаратор 122 включает в себя инвертор (инвертирующий усилитель) 109, вход которого подключен к узлу между стоком транзистора M6 и источником 108 тока. Опорный ток Iref, текущий из источника 108 тока, определяет эталон (порог) сравнения в компараторе 122. Затвор транзистора (второго транзистора) M5 подключен к стоку транзистора M5, измерительной линии SL и затвору транзистора (третьего транзистора) M6. Инвертор (инвертирующий усилитель) 109 выводит сигнал comp результата сравнения. Блоки 126 памяти удерживают значения отсчета счетчика 124 в качестве цифровых сигналов, соответствующих сигналам пикселей 112, в соответствии с переходом сигналов comp1, comp2 и comp3 результата сравнения компараторов 122. Инвертор 109 является примером схемы вывода и может быть заменен другим инвертирующим усилителем, например, усилителем с общим истоком.

[0040] Каждый блок 120 считывания генерирует цифровой сигнал, соответствующий напряжению преобразователя FD заряда в напряжение пикселя 112 в соответствии с хронированием, при котором значение пиксельного тока Ipix, текущего через сток (второй главный электрод) транзистора M3 пикселя 112, превышает опорный ток Iref (порог).

[0041] На фиг. 4 показана операция считывания сигнала пикселя 112 в первой строке и данном столбце согласно первому варианту осуществления. Эта операция считывания включает в себя операцию N_AD считывания уровня шума и операцию S_AD считывания оптического сигнала. Операция N_AD считывания уровня шума является операцией считывания, в качестве цифрового сигнала, сигнала, соответствующего напряжению преобразователя FD заряда в напряжение сразу после сброса преобразователя FD заряда в напряжение. Операция S_AD считывания уровня оптического сигнала является операцией считывания, в качестве цифрового сигнала, сигнала, соответствующего напряжению преобразователя FD заряда в напряжение после переноса зарядов фотоэлектрического преобразователя PD на преобразователь FD заряда в напряжение.

[0042] Когда сигнал ΦR1 сброса активируется в течение заранее определенного времени, транзистор M2 сброса отпирается. Напряжение преобразователя FD заряда в напряжение сбрасывается до напряжения сброса, соответствующего напряжению VR сброса, через транзистор M2 сброса. Сброс напряжения преобразователя FD заряда в напряжение завершается деактивацией сигнала ΦR1 сброса. Одновременно со сбросом напряжения преобразователя FD заряда в напряжение, сигнал ΦRVL сброса активируется в течение заранее определенного времени для замыкания переключателя 136. Напряжение V_VL линии VL управления сбрасывается на напряжение, соответствующее напряжению VRVL сброса, через переключатель 136. Напряжение на первом узле конденсатора 132, подключенного к линии VL управления, также сбрасывается на напряжение, соответствующее напряжению VRVL сброса. Сброс напряжения V_VL линии VL управления завершается деактивацией сигнала ΦRVL сброса. В этом случае, напряжение VRVL сброса (напряжение линии первого напряжения) определяется таким образом, что напряжение, установленное на линии VL управления благодаря замыканию переключателя 136, является напряжением, не отпирающим транзистор M3 пикселя 112.

[0043] Операция N_AD считывания уровня шума начинается с деактивации сигнала ΦRVL сброса. Деактивация сигнала ΦRVL сброса, заряды, накопленные в конденсаторе 132, удаляются значением тока Is источника 134 тока, позволяет линейно снижать напряжение V_VL линии VL управления. Период, в течение которого напряжение V_VL линии VL управления линейно снижается, указан как период A. Операция отсчета счетчика 124 начинается с деактивации сигнала ΦRVL сброса. Операция отсчета указана как "count" на фиг. 4.

[0044] Период A заканчивается, когда напряжение V_VL линии VL управления снижается до напряжения, при котором напряжение между затвором и истоком транзистора M3 пикселя 112 строки целей считывания превышает порог транзистора M3 и сдвигается в период B. Напряжение V_VL линейно изменяется в течение периода A, и нелинейно изменяется в течение периода B. Когда напряжение V_VL линии VL управления снижается до напряжения, при котором напряжение между затвором и истоком транзистора M3 пикселя 112 в качестве цели считывания превышает порог транзистора M3, транзистор M3 отпирается, чтобы начать пропускать пиксельный ток Ipix. Пиксельный ток Ipix течет в линию VL управления через транзистор M3 и транзистор M4 выбора. Значение тока, который может течь по линии VL управления, ограничивается значением тока Is источником 134 тока. Соответственно, разрядный ток из конденсатора 132 становится малым, поскольку течет пиксельный ток Ipix. Поэтому падение напряжения V_VL линии VL управления изменяется нелинейно.

[0045] После того, как начинает течь пиксельный ток Ipix, когда значение пиксельного тока Ipix превышает значение (порог) опорного тока Iref, компаратор 122 блока 120 считывания обнаруживает это. Таким образом, сигнал comp результата сравнения активируется (инвертируется), и, соответственно, значение отсчета счетчика 124 удерживается в качестве цифрового сигнала, представляющего уровень шума в памяти удержания уровня шума памяти 126. Таким образом, блок 120 считывания генерирует цифровой сигнал в течение времени, от хронирования, при котором переключатель 136 размыкается после зарядки конденсатора 132, до хронирования, при котором значение пиксельного тока Ipix, текущего через сток транзистора M3 пикселя 112, превышает значение опорного тока Iref.

[0046] Операция N_AD считывания уровня шума завершается спустя достаточное время после деактивации сигнала ΦRVL сброса. После этого, сигнал переноса ΦT1 активируется в течение заранее определенного времени, и сигнал ΦRVL сброса активируется в течение заранее определенного времени. Период B завершается активацией сигнала ΦRVL сброса. Когда сигнал переноса ΦT1 активируется, заряды фотоэлектрического преобразователя PD переносятся на преобразователь FD заряда в напряжение, таким образом, изменяя напряжение преобразователя заряда до напряжения PD. Когда сигнал ΦRVL сброса активируется в течение заранее определенного времени, переключатель 136 замыкается для сброса напряжения V_VL линии VL управления на напряжение, соответствующее напряжению VRVL сброса через переключатель 136. Сброс напряжения V_VL линии VL управления завершается деактивацией сигнала ΦRVL сброса.

[0047] Операция S_AD считывания уровня оптического сигнала начинается с деактивации сигнала ΦRVL сброса. Благодаря деактивации сигнала ΦRVL сброса, заряды, накопленные в конденсаторе 132, удаляются значением тока Is из источника 134 тока для линейного снижения напряжение V_VL линии VL управления. Последующая операция, в основном, такая же, как в операции N_AD считывания уровня шума, но время считывания длиннее, чем в операции N_AD считывания.

[0048] Когда напряжение V_VL линии VL управления снижается до напряжения, при котором напряжение между затвором и истоком транзистора M3 пикселя 112 в качестве строки целей считывания превышает порог транзистора M3, транзистор M3 отпирается, чтобы начать пропускать пиксельный ток Ipix. После того, как начинает течь пиксельный ток Ipix, когда значение пиксельного тока Ipix превышает значение (порог) опорного тока Iref, компаратор 122 блока 120 считывания обнаруживает это. Таким образом, сигнал comp результата сравнения активируется (инвертируется), и, соответственно, значение отсчета счетчика 124 удерживается в памяти удержания уровня оптического сигнала памяти 126 в качестве цифрового сигнала, представляющего уровень оптического сигнала. Таким образом, блок 120 считывания генерирует цифровой сигнал в течение времени, от хронирования, при котором переключатель 136 размыкается после зарядки конденсатора 132, до хронирования, при котором значение пиксельного тока Ipix, текущего через сток транзистора M3 пикселя 112, превышает значение опорного тока Iref.

[0049] Цифровой сигнал, представляющий уровень шума, и цифровой сигнал, представляющий уровень оптического сигнала, которые удерживаются в памяти 126, выводятся в линию 160 выходного сигнала в соответствии с командой от схемы 140 горизонтальной развертки. Цифровой сигнал, представляющий уровень шума, и цифровой сигнал, представляющий уровень оптического сигнала, могут выводиться из устройства 100 фотоэлектрического преобразования, или их разность может выводиться из устройства 100 фотоэлектрического преобразования.

[0050] Заметим, что конденсатор 132 не обязан ограничиваться конденсатором, добавленным к линии VL управления, но может быть паразитной емкостью линии VL управления.

[0051] Признак устройства 100 фотоэлектрического преобразования согласно первому варианту осуществления будет описан по сравнению с обычным устройством фотоэлектрического преобразования, включающим в себя А/Ц преобразователь. В обычном устройстве фотоэлектрического преобразования, пиксельный сигнал выводится в форме сигнала напряжения в линию сигнала столбца через транзистор усиления, размещенный в пикселе. Этот пиксельный сигнал усиливается усилителем столбца и преобразуется в цифровой сигнал А/Ц преобразователем. Согласно этому способу, после того, как устанавливается напряжение линии сигнала столбца и устанавливается выход усилителя столбца, размещенного в каждом столбце пиксельной матрицы 110, А/Ц преобразователь должен начинать А/Ц преобразование.

[0052] С другой стороны, устройство 100 фотоэлектрического преобразования согласно первому варианту осуществления осуществляет широкое А/Ц преобразование в том смысле, что сигнал, соответствующий напряжению преобразователя FD заряда в напряжение, выводится как цифровой сигнал. Однако, в устройстве 100 фотоэлектрического преобразования согласно первому варианту осуществления, напряжение преобразователя FD заряда в напряжение не считывается как аналоговый сигнал напряжения, и аналоговый сигнал напряжения не преобразуется в цифровой сигнал. Устройство 100 фотоэлектрического преобразования согласно первому варианту осуществления начинает широкое А/Ц преобразование одновременно с началом снижения напряжения V_VL линии VL управления. Устройство 100 фотоэлектрического преобразования согласно первому варианту осуществления не нужно ждать установления напряжения сигнала линия. Поэтому устройство 100 фотоэлектрического преобразования согласно первому варианту осуществления имеет преимущество в высокоскоростном считывании сигнала из пикселя 112.

[0053] На фиг. 5 показан пример устройства пиксельной матрицы 110 и регуляторов 130 напряжения в устройстве 100 фотоэлектрического преобразования согласно второму варианту осуществления настоящего изобретения. Предметы, которые не будут описаны как второй вариант осуществления, согласуются с первым вариантом осуществления. Во втором варианте осуществления, транзистор M4 выбора исключен. Во втором варианте осуществления, пиксель 112 выбирается посредством напряжения сброса для сброса преобразователь FD заряда в напряжение. В частности, напряжение преобразователя FD заряда в напряжение пикселя 112 в качестве строки целей выбора сбрасывается к первому напряжению, пригодному для считывания сигнала. С другой стороны, напряжение преобразователя FD заряда в напряжение пикселя 112 в качестве строки невыбранных целей сбрасывается ко второму напряжению, которое ниже первого напряжения и ниже нижнего предела размаха напряжения линии VL управления, соответствующим регулятором 130 напряжения.

[0054] На фиг. 6 показана конфигурация устройства 100' фотоэлектрического преобразования согласно третьему варианту осуществления настоящего изобретения. Предметы, которые не будут описаны как третий вариант осуществления, согласуются с первым или вторым вариантом осуществления. В третьем варианте осуществления, конфигурация блока 120 считывания отличается от конфигурации согласно первому или второму варианту осуществления, и для каждого столбца предусмотрен отдельный счетчик 128. Таким образом, блок 120 считывания включает в себя один компаратор 122, один счетчик 128 и одну память 126 для каждого столбца пиксельной матрицы 110. Счетчики 128 останавливают операции отсчета за счет перехода сигналов comp результата сравнения из соответствующих компараторов 122. Каждая память 126 удерживает значение отсчета соответствующего счетчика 128.

[0055] На фиг. 7 показана операция считывания сигнала пикселя 112 в первой строке и данном столбце согласно четвертому варианту осуществления настоящего изобретения. Предметы, которые, по существу, соответствуют предметам вариантов осуществления с первого по третий не будут описаны. Согласно четвертому варианту осуществления, каждый регулятор 130 напряжения включает в себя источник переменного напряжения и управляет напряжением VL_V линии VL управления с помощью источника переменного напряжения. В частности, регулятор 130 напряжения линейно снижает напряжение VL_L линии VL управления в соответствии с деактивацией сигнала ΦRVL сброса. Ток Ipix, текущий через транзистор M3, начинает течь, когда транзистор M3 отпирается, и увеличивается до тех пор, пока не прекратится изменение напряжения VL_V линии VL управления. Таким образом, примером регулятора 130 напряжения для линейного изменения напряжения VL_V линии VL управления является буфер, например, повторитель напряжения. Например, согласно фиг. 2, напряжение на узле, подключенном к источнику постоянного тока и первому узлу 137 конденсатора 132 подается в линию VL управления через повторитель напряжения.

[0056] Заметим, что напряжение линии VL управления можно регулировать в направлении от отпертого состояния к запертому состоянию транзистора M3. Таким образом, когда напряжение линии VL управления регулируется в направлении от отпертого состояния к запертому состоянию транзистора M3, состояние, в котором значение пиксельного тока Ipix становится меньше значения опорного тока Iref, можно выразить как состояние, в котором пиксельный ток Ipix превышает порог.

[0057] В каждом вышеописанном варианте осуществления, множество пикселей может совместно использовать транзистор M3. В частности, множество фотоэлектрических преобразователей может быть подключено к общей плавающей диффузионной области через разные транзисторы переноса.

[0058] Устройство фотоэлектрического преобразования согласно пятому варианту осуществления настоящего изобретения будет описано со ссылкой на фиг. 9A. Пятый вариант осуществления отличается от вариантов осуществления с первого по четвертый тем, что регулятор 130 напряжения заменен регулятором 230 напряжения. Предметы, которые соответствуют, по существу, предметам пятого варианта осуществления, не будут описаны.

[0059] Регулятор 230 напряжения изменяет напряжение V_VL линии VL управления. Регулятор 230 напряжения включает в себя переменный конденсатор 232, переключатель 136 и источник 234 переменного тока. Переменный конденсатор 232 и источник 234 переменного тока составляют регулятор 240 коэффициента усиления. Регулятор 240 коэффициента усиления может определять значение емкости переменного конденсатора 232 и значение тока Is в соответствии с сигналом управления (не показан).

[0060] Когда значение емкости переменного конденсатора 232 установлено большим, скорость изменения (наклон) напряжения V_VL линии VL управления в течение периода A может увеличиваться. Когда значение емкости переменного конденсатора 232 установлено малым, изменение (наклон) напряжения V_VL линии VL управления может уменьшаться в течение периода A. Когда значение тока Is установлено большим, в течение периода A на фиг. 4, разрядный ток из переменного конденсатора 232 увеличивается для увеличения изменения (наклона) напряжения V_VL линии VL управления. Когда значение тока Is установлено малым, изменение (наклон) напряжения V_VL линии VL управления в течение периода A может уменьшаться.

[0061] Как описано выше, регулятор 240 коэффициента усиления может увеличивать/уменьшать изменение (наклон) напряжения V_VL линии VL управления в течение периода A. Как будет описано ниже, коэффициент усиления А/Ц преобразования (то есть коэффициент усиления считывания блоком 120 считывания) может переключаться. В этом примере, значение емкости переменного конденсатора 232 и значение тока Is источника 234 переменного тока установлены переменными. Однако одно из значения емкости и значения тока можно устанавливать переменным для изменения коэффициента усиления А/Ц преобразования.

[0062] Переключение коэффициента усиления А/Ц преобразования в устройстве фотоэлектрического преобразования согласно пятому варианту осуществления будет описано со ссылкой на фиг. 10. На Фиг. 10 показано три разных коэффициента усиления G1, G2 и G3. В этом случае, коэффициент усиления А/Ц преобразования согласно фиг. 4 задается как G2, коэффициент усиления, установленный, когда наклон линии VL управления больше коэффициента усиления G2, задается как коэффициент усиления G1, и коэффициент усиления, установленный, когда наклон меньше коэффициента усиления G2 задается как коэффициент усиления G3. Как описано выше, когда, по меньшей мере, одно из значения емкости переменного конденсатора 232 и значения тока Is может изменяться для определения коэффициента усиления А/Ц преобразования. Напряжение сброса преобразователя FD заряда в напряжение и величина заряда, переносимого из фотоэлектрического преобразователя PD на преобразователь FD заряда в напряжение активацией сигнала ΦT переноса остаются неизменными для всех коэффициентов усиления А/Ц преобразования.

[0063] Сигнал ΦR1 сброса активируется в течение заранее определенного времени для отпирания транзистора M2 сброса. Напряжение преобразователя FD заряда в напряжение сбрасывается до напряжения сброса, соответствующего напряжению VR сброса, через транзистор M2 сброса. Сброс напряжения преобразователя FD заряда в напряжение завершается деактивацией сигнала ΦR1 сброса. Одновременно со сбросом напряжения преобразователя FD заряда в напряжение, сигнал ΦRVL сброса активируется в течение заранее определенного времени для замыкания переключателя 136. Напряжение V_VL линии VL управления сбрасывается на напряжение, соответствующее напряжению VRVL сброса, через переключатель 136. Напряжение на первом узле 137 переменного конденсатора 232, подключенном к линии VL управления, также сбрасывается на напряжение, соответствующее напряжению VRVL сброса. Сброс напряжения V_VL линии VL управления завершается деактивацией сигнала ΦRVL сброса. В этом случае, напряжение VRVL сброса (напряжение линии первого напряжения) определяется таким образом, что напряжение, установленное на линии VL управления благодаря замыканию переключателя 136, является напряжением, не отпирающим транзистор M3 пикселя 112.

[0064] Операция N_AD считывания уровня шума начинается с деактивации сигнала ΦRVL сброса. Напряжение V_VL линии VL управления снижается в соответствии с наклоном, соответствующим установлению коэффициента усиления G1, G2 или G3 А/Ц преобразования. Даже если выбран один из коэффициентов усиления G1, G2 и G3 А/Ц преобразования, транзистор M3 отпирается, когда напряжение V_VL линии VL управления становится напряжением VL_N, поскольку напряжение преобразователя FD заряда в напряжение остается неизменным. Пиксельный ток Ipix начинает течь. Поскольку наклон коэффициента усиления G1 А/Ц преобразования является наибольшим, пиксельный ток Ipix начинает течь с самым ранним хронированием. В случае наименьшего коэффициента усиления G3 А/Ц преобразования, пиксельный ток Ipix начинает течь с самым поздним хронированием. Ipix@G1, comp@G1 и count@G1 представляют Ipix, comp и count, соответственно, когда коэффициент усиления А/Ц преобразования равен G1. Ipix@G2, comp@G2 и count@G2 представляют Ipix, comp и count, соответственно, когда коэффициент усиления А/Ц преобразования равен G2. Аналогично, Ipix@G3, comp@G3 и count@G3 представляют Ipix, comp и count, соответственно, когда коэффициент усиления А/Ц преобразования равен G3.

[0065] В операции S_AD считывания оптического сигнала, аналогично, пиксельный ток Ipix начинает течь при хронировании, в котором напряжение V_VL линии VL управления становится VL_S. Аналогично, пиксельный ток Ipix начинает течь с самым ранним хронированием для коэффициента усиления G1 А/Ц преобразования; и с самым поздним хронированием для коэффициента усиления G3 А/Ц преобразования. Сигнал comp результата сравнения инвертируется при хронировании, в котором значение пикселя Ipix превышает значение опорного тока Iref в каждый момент времени, и при каждом коэффициенте усиления. Цифровое значение в качестве значения отсчета при этом хронировании удерживается в памяти 126.

[0066] Удерживать значение отсчета с самым ранним хронированием для коэффициента усиления G1 А/Ц преобразования означает наименьшее значение цифрового сигнала для коэффициента усиления G1 А/Ц преобразования. Удерживать значение отсчета с самым поздним хронированием для коэффициента усиления G3 А/Ц преобразования означает наибольшее значение цифрового сигнала для коэффициента усиления G3 А/Ц преобразования. Если коэффициент усиления А/Ц преобразования задается как (значение цифрового сигнала)/(уровень напряжения в преобразователе заряда в напряжение), соотношение между коэффициентом усиления А/Ц преобразования и наклоном напряжения V_BL линии VL управления выражается в виде

G1 (коэффициент усиления: низкий, наклон: большой) < G2 (коэффициент усиления: средний, наклон: средний) < G3 (коэффициент усиления: высокий, наклон: малый)

Таким образом, регулятор 240 коэффициента усиления обеспечивает функцию переключения коэффициентов усиления А/Ц преобразования с помощью блока 120 считывания.

[0067] На фиг. 9B показан пример детальной конфигурации регулятора 240 коэффициента усиления. В примере, показанном на фиг. 9B, переменный конденсатор 232 сформирован из множества параллельно соединенных блоков. Каждый блок сформирован последовательным соединением конденсатора и переключателя выбора. Управление состоянием (замкнут или разомкнут) переключателя выбора позволяет определять значение емкости переменного конденсатора 232. В частности, управляя состоянием (замкнут или разомкнут) переключателя выбора, из множества конденсаторов можно выбирать конденсатор, используемый для регулировки напряжения линии VL управления.

[0068] Когда конденсатор каждого блока выполнен в виде устройства с использованием кремниевого диффузионного слоя наподобие МОП-конденсатора, в одном из двух электродов 237 и 238 конденсатора между диффузионным слоем и ямой формируется паразитная емкость. Когда каждый конденсатор размещен между переключателем и линией VL управления, независимо от того, замкнут или разомкнут переключатель, паразитные емкости всех конденсаторов всегда добавляются в линию VL управления. В этом случае, можно не получить нужный коэффициент усиления, когда коэффициент усиления А/Ц преобразования устанавливается регулятором 240 коэффициента усиления. Наподобие примера, показанного на фиг. 9B, переключатель вставлен между конденсатором и линией VL управления для отсоединения от линии VL управления паразитной емкости конденсатора, к которому подключен разомкнутый переключатель. Эта конфигурация позволяет минимизировать ошибочную составляющую, обусловленную паразитной емкостью, и точнее осуществлять установление коэффициента усиления А/Ц преобразования.

[0069] Устройство фотоэлектрического преобразования согласно шестому варианту осуществления настоящего изобретения будет описано со ссылкой на фиг. 11. Для простоты описания, на фиг. 11 иллюстративно показаны компаратор 122 и регулятор 330 напряжения для данного столбца, и один пиксель 112 для данного столбца. В шестом варианте осуществления, регулятор 130 напряжения заменен регулятором 330 напряжения.

[0070] Регулятор 330 напряжения отличается от регулятора 130 напряжения тем, что второй электрод 138 конденсатора 132 подключен к линии третьего напряжения (в этом примере, линии напряжения питания, которая подает напряжение VDD питания). Напряжение линии третьего напряжения равно напряжению VDD питания, подаваемому на истоки транзисторов M5 и M6 компаратора 122. Регулятор 330 напряжения, показанный на фиг. 11, не имеет функции изменения коэффициента усиления А/Ц преобразования. Однако, как и в пятом варианте осуществления, регулятор 330 напряжения может иметь функцию изменения коэффициента усиления А/Ц преобразования.

[0071] На фиг. 12A показана работа, в качестве сравнительного примера, конфигурации, в которой второй электрод 138 конденсатора 132 подключен к линии второго напряжения (линии напряжения земли), как в вариантах осуществления с первого по пятый. На Фиг. 12B показана работа конфигурации шестого варианта осуществления, то есть конфигурации, в которой второй электрод 138 подключен к линии третьего напряжения (в этом примере, линии напряжения питания, которая подает напряжение VDD питания).

[0072] Ток Icap течет из конденсатора 132, и ток Ires течет через переключатель 136. Ток Icap положителен, когда течет от второго электрода 138 конденсатора 132 к первому электроду 137. Поскольку основная операция форм волны в операции N_AD считывания уровня шума такая же, как в операции S_AD считывания уровня оптического сигнала, проиллюстрирована только операция S_AD.

[0073] Согласно фиг. 12A, ток Ivdd, подаваемый из линии третьего напряжения, является суммой пиксельного тока Ipix и опорного тока Iref. Ток Icap является разрядным током из конденсатора 132 после деактивации ΦRVL и подается из линии второго напряжения (линии напряжения земли) через второй электрод 138. Ток Ignd, текущий в линию второго напряжения, получается вычитанием Icap из суммы тока Is источника тока и Iref. Как явствует из фиг. 12A, очевидно, что Ivdd и Ignd сильно флуктуируют в течение периода S_AD, в котором осуществляется А/Ц преобразование. Поскольку линия второго напряжения и линия третьего напряжения имеют соответствующие импедансы, флуктуации тока этих линий напряжения приводят к флуктуациям напряжения земли и напряжения питания. Схема конфигурации одного столбца проиллюстрирована на фиг. 11. Однако, если устройство фотоэлектрического преобразования включает в себя множество столбцов, флуктуации напряжения земли и напряжений питания, обусловленные столбцами, отличными от данного столбца, который осуществляет А/Ц преобразование, генерируют шумовую составляющую.

[0074] В примере, показанном на фиг. 12B, поскольку второй электрод 138 конденсатора 132 подключен к линии третьего напряжения, Ivdd становится суммой Ipix, Iref и Icap, и Ignd становится суммой Is и Iref. Поскольку Icap и Ipix имеют противоположные фазы, их сумма может компенсировать флуктуацию тока, таким образом, подавляя флуктуацию Ivdd. Поскольку Ignd не коррелирует с Icap, которая имеет большую флуктуацию, флуктуация Ignd также может подавляться. Соответственно, в устройстве фотоэлектрического преобразования, имеющем множество столбцов, можно подавлять флуктуации напряжения земли и напряжения питания, обусловленные операциями столбцов, отличных от данного столбца, в течение периода А/Ц преобразования. По сравнению со случаем, когда второй электрод 138 конденсатора 132 подключен к линии второго напряжения, можно снизить ухудшение качества изображения, обусловленное шумом.

[0075] Как описано выше, второй электрод 138 конденсатора 132, подключенный к линии VL управления, подключен к линии третьего напряжения, подключенной к транзисторам M5 и M6 компаратора 122, таким образом, снижая ухудшение качества изображения, обусловленное шумом.

[0076] Устройство фотоэлектрического преобразования согласно седьмому варианту осуществления настоящего изобретения будет описано со ссылкой на фиг. 13. В седьмом варианте осуществления, компаратор 122 вариантов осуществления с первого по шестой заменен компаратором 222. Компаратор 222 имеет конфигурацию, в которой шунтирующий путь 250 добавлен в конфигурацию компаратора 122. Шунтирующий путь 250 размещен параллельно транзистору M6 для шунтирования пути между истоком и стоком транзистора M6. Шунтирующий путь 250 образован n-МОП-транзистором M7, на затвор которого подается заранее определенное напряжение VG, сток которого подключен к линии третьего напряжения (в этом примере, линии напряжения питания, на которую подается напряжение VDD питания), и исток которого подключен к источнику 108 тока (входной узел comp1). Инвертор 109 имеет входной узел comp1 и выходной узел comp2.

[0077] Работа устройства фотоэлектрического преобразования согласно седьмому варианту осуществления будет описана со ссылкой на фиг. 14 с центром в точках, отличных от операции, показанной на фиг. 4. Ток Imir течет через транзистор M6. Ток Ibp течет через транзистор M7 (шунтирующий путь 250). Опорный ток Iref течет через источник 108 тока.

[0078] В течение периода A операции N_AD считывания, напряжение V_VL линии VL управления снижается линейно. Однако, поскольку транзистор M3 пикселя 112 на строке целей считывания заперт, пиксельный ток Ipix не течет. Транзистор M5 и транзистор M6 составляют токовое зеркало. Соответственно, ток Imir не течет в течение периода A. Когда заранее определенное напряжение VG устанавливается таким образом, что транзистор M7 отпирается, опорный ток Iref источника 108 тока течет через транзистор M7. В это время, напряжение узла comp1 является напряжением, полученным вычитанием порогового напряжения VT7 транзистора M7 из почти заранее определенного напряжения VG. Предпочтительно устанавливать заранее определенное напряжение VG таким образом, чтобы напряжение VG-VT7 было выше напряжения земли и ниже порога инверсии инвертора 109.

[0079] Когда напряжение V_VL линии VL управления непрерывно снижается, транзистор M3 вскоре отпирается, чтобы начать пропускать пиксельный ток Ipix. Ток Imir, соответствующий отношению размеров транзисторов M5 и M6, течет через транзистор M6. Транзисторы M6 и M7 подключены к источнику 108 тока, и сумма токов, текущих через транзисторы M6 и M7, равна Iref. Ток Ibp постепенно снижается, и напряжение узла comp1 возрастает. Пиксельный ток Ipix увеличивается, и ток Ibp обращается в нуль при хронировании, в котором ток Imir становится равным опорному току Iref. После этого, ток Imir временно превышает опорный ток Iref для зарядки паразитной емкости узла comp1 зарядами, соответствующими разности между Imir и Iref, таким образом, увеличивая напряжение узла comp1. Когда напряжение узла comp1 возрастает, напряжение между стоком и истоком транзистора M6 снижается. Ток Imir постепенно снижается и уравновешиваться, чтобы быть равным тому же значению, что и у опорного тока Iref.

[0080] В течение периода, когда напряжение узла comp1 возрастает, напряжение узла comp2 инвертируется, когда напряжение узла comp1 превышает порог инверсии инвертора 109, и значение отсчета count в это время удерживается в памяти 126. После этого, операция N_AD считывания завершается, и сигнал ΦRVL сброса активируется, таким образом, запирая транзистор M3. Ток Ipix прекращает течь. В это время также Imir не течет. Вместо этого, ток Ibp подает ток источника 108 тока, и напряжение узла comp1 возвращается к VG-VT7. Таким образом, операция считывания S_AD осуществляется так же, как N_AD, и ее описание будет опущено.

[0081] Ток Ibp течет через шунтирующий путь 250 (транзистор M7) в течение периода, когда пиксельный ток Ipix не течет, таким образом, что ток, текущий по линии напряжения земли, становится постоянным. Когда напряжение узла comp1 на низковольтной стороне устанавливается равным VG-VT7, более высоким, чем напряжение земли, амплитуда изменения напряжения на узле comp1 ограничивается. В устройстве фотоэлектрического преобразования, имеющем множество столбцов и межстолбцовый шаг, меньший нескольких микрон, данный столбец подвергается негативному влиянию сигналов большой амплитуды остальных столбцов, которые обусловлены перекрестными помехами. Это может становиться шумом, вызывающим ухудшение качества изображения. В частности, амплитуда изменения напряжения на узле comp1 ограничивается для подавления ухудшения качества изображения.

[0082] На фиг. 14 показаны пунктиром формы волны опорного тока Iref (то есть тока Ignd, текущего в линию напряжения земли) в отсутствие шунтирующего пути 250 и напряжения на узле comp1. Токи, текущие по линии напряжения земли в течение периодов операций N_AD и S_AD считывания, которые осуществляют операции А/Ц преобразования, флуктуируют ввиду отсутствия шунтирующего пути 250. Поскольку линия напряжения земли имеет соответствующий импеданс, флуктуация тока приводит к флуктуации напряжения земли. Однако, если устройство фотоэлектрического преобразования включает в себя множество столбцов, флуктуация напряжения земли, обусловленная столбцами, отличными от данного столбца, который осуществляет А/Ц преобразование, генерирует шумовую составляющую. Это приводит к ухудшению качества изображения. В частности, флуктуация тока, текущего по линии напряжения земли, подавляется шунтирующим путем, что позволяет подавлять ухудшение качества изображения.

[0083] Устройство фотоэлектрического преобразования согласно восьмому варианту осуществления настоящего изобретения будет описано со ссылкой на фиг. 15. В восьмом варианте осуществления, компаратор 122 вариантов осуществления с первого по шестой заменен компаратором 322. Компаратор 322 имеет конфигурацию, полученную путем добавления ограничителя 350 амплитуды в конфигурацию компаратора 122. Ограничитель 350 амплитуды ограничивает амплитуду напряжения на узле comp1. Ограничитель 350 амплитуды сформирован из, например, n-МОП-транзистора M8, на затвор которого подается напряжение VG2, сток которого подключен к стоку транзистора M6, и исток которого подключен к источнику 108 тока.

[0084] Затем работа устройства фотоэлектрического преобразования согласно восьмому варианту осуществления будет описана со ссылкой на фиг. 16 с центром в точках, отличных от операции, показанной на фиг. 4. Работа от начала операции N_AD считывания для отпирания транзистора M3 пикселя 112 в строке целей считывания и до тех пор, когда начинает течь пиксельный ток Ipix, такая же, как на фиг. 4. Однако, когда течет пиксельный ток Ipix, течет ток Imir, соответствующий отношению размеров транзистора M5 и транзистора M6. Соответственно, напряжение узла comp1 постепенно возрастает. Если порог транзистора M8 задается как VT8, напряжение узла comp1 становится около VG2-VT8, таким образом, подавляя напряжение узла comp1 на высоковольтной стороне. Таким образом, амплитуда напряжения на узле comp1 ограничивается. В устройстве фотоэлектрического преобразования, имеющем множество столбцов и межстолбцовый шаг, меньший нескольких микрон, данный столбец подвергается негативному влиянию сигналов большой амплитуды остальных столбцов, которые обусловлены перекрестными помехами. Это может становиться шумом, вызывающим ухудшение качества изображения. В частности, амплитуда изменения напряжения на узле comp1 ограничивается для подавления ухудшения качества изображения. Напряжение VG2 устанавливается таким образом, что VG2-VT8 выше, чем порога инверсии инвертора 109, чтобы инвертировать инвертор 109.

[0085] В примере, показанном на фиг. 15, хотя напряжение VG2 подается на затвор транзистора M8, линия разрешающего сигнала для управления компаратором 322 в рабочем или нерабочем состоянии, может быть подключена к затвору транзистора M8. Когда разрешающий сигнал активен (высокий уровень), задействуется компаратор 322. Когда разрешающий сигнал неактивен (низкий уровень), путь тока компаратора 322 разрывается. Компаратор 322 устанавливается в нерабочее состояние для снижения энергопотребления.

[0086] Устройство фотоэлектрического преобразования согласно девятому варианту осуществления настоящего изобретения будет описано со ссылкой на фиг. 17. В восьмом варианте осуществления, компаратор 122 вариантов осуществления с первого по шестой заменен компаратором 422. Компаратор 422 имеет конфигурацию, в которую включены шунтирующий путь 250 седьмого варианта осуществления и ограничитель 350 амплитуды восьмого варианта осуществления.

[0087] На фиг. 18 показана работа устройства фотоэлектрического преобразования согласно девятому варианту осуществления. Поскольку устройство фотоэлектрического преобразования включает в себя шунтирующий путь 250 и ограничитель 350 амплитуды, ток Ignd, текущий по линии напряжения земли, устанавливается постоянным, и, в то же время, амплитуда напряжения на узле comp1 ограничивается от VG2-VT8 до VG-VT7. В частности, в устройстве фотоэлектрического преобразования, имеющем множество столбцов, можно подавлять ухудшение качества изображения, обусловленное флуктуацией напряжения земли, и ухудшение качества изображения, обусловленное перекрестными помехами сигнала большой амплитуды.

[0088] Устройство фотоэлектрического преобразования согласно десятому варианту осуществления настоящего изобретения будет описано со ссылкой на фиг. 19. В десятом варианте осуществления, компаратор 122 вариантов осуществления с первого по шестой заменен компаратором 522. Компаратор 522 имеет конфигурацию, в которой к компаратору 122 добавлен источник 501 реактивного тока для обеспечения протекания реактивного тока Iidl.

[0089] Работа устройства фотоэлектрического преобразования согласно десятому варианту осуществления будет описана со ссылкой на фиг. 20 с центром в точках, отличных от операции, показанной на фиг. 4. Сигнал ΦRVL сброса активируется для запирания транзистор M3. Ток Ipix прекращает течь, и ток, текущий через транзистор M5, является чисто реактивным током Iidl. В этом состоянии, поскольку паразитная емкость измерительной линии SL заряжается реактивным током Iidl, напряжение измерительной линии SL возрастает. Если напряжение между затвором и истоком транзистора M5 задается как Vgs, напряжение измерительной линии SL устанавливается равным VDD-Vgs. Ток, амплитуда которого получена умножением реактивного тока Iidl на отношение размеров M (= (ширина затвора M6)/(ширина затвора M5) к M6 течет в транзистор M6. Согласно вариантам осуществления, длина затвора транзистора M5 и длина затвора транзистора M6 равны друг другу. Устанавливаются напряжения линии VL управления и измерительной линии SL. В то же время, сигнал ΦRVL сброса становится неактивным по завершении операции сброса или операции переноса пикселя, таким образом, начиная операцию А/Ц преобразования. Поскольку последующие операции такие же, как в вышеописанных вариантах осуществления, их подробное описание будет опущено.

[0090] Реактивный ток Iidl должен быть значением тока, удовлетворяющим следующему выражению:

Iidl < Iref/M

[0091] На фиг. 20 показано, что форма волны напряжения измерительной линии SL и форма волны тока Im5, текущего через транзистор M5, указаны пунктирными линиями в отсутствие источника 501 реактивного тока. Когда сигнал ΦRVL сброса активируется в отсутствие источника 501 реактивного тока, ток, определенный напряжением Vgs между затвором и истоком транзистора M5, подается на транзистор M5 для зарядки паразитной емкости измерительной линии SL. Соответственно, напряжение измерительной линии SL возрастает. Совместно с ростом измерительной линии SL, напряжение между затвором и истоком снижается. По этой причине, ток, подаваемый на транзистор M5, также снижается для снижения роста скорости напряжения измерительной линии SL. Когда Vgs становится ниже порогового напряжения транзистора M5, напряжение транзистора M5 падает в подпороговой области для экспоненциального снижения величины тока, подаваемого на транзистор M5. Для установления измерительной линии SL требуется много времени, поскольку ток транзистора M5 отсекается, и напряжение измерительной линии SL должно достигать VDD.

[0092] Когда начало операции А/Ц преобразования в состоянии, в котором измерительная линия SL в достаточной степени не установлено, напряжение между истоком и стоком транзистора M3 в начальном состоянии каждой операции А/Ц преобразования может изменяться. По этой причине, А/Ц преобразование приводит к проблемам позы, например, ухудшению линейности и увеличению шума фиксированной картины и случайного шума, что приводит к ухудшению качества изображения. Для получения хорошего качества изображения, нужно гарантировать время для достаточного установления измерительной линии SL.

[0093] В частности, источник 501 реактивного тока добавляется, как в десятом варианте осуществления, для сокращения времени установления измерительной линии SL, таким образом, сокращая время считывания устройства фотоэлектрического преобразования.

[0094] На фиг. 8 показана конфигурация системы регистрации изображения согласно еще одному варианту осуществления настоящего изобретения. Система 800 регистрации изображения включает в себя, например, оптический блок 810, элемент 1 регистрации изображения, процессор 830 видеосигнала, блок 840 записи/передачи, регулятор 850 хронирования, системный регулятор 860 и блок 870 воспроизведения/отображения. Датчик 820 изображения включает в себя элемент 1 регистрации изображения и процессор 830 видеосигнала. Элемент 1 регистрации изображения является полупроводниковым датчиком изображения, представленным устройством 100, 100' или 100" фотоэлектрического преобразования, описанный в вышеприведенных вариантах осуществления.

[0095] Оптический блок 810, выступающий в роли оптической системы, например линза, фокусирует свет от объекта на блоке 10 пикселей, элемента 1 регистрации изображения, в котором множество пикселей размещено в двух измерениях, таким образом, формируя изображение объекта. При хронировании на основании сигнала от регулятора 850 хронирования, элемент 1 регистрации изображения выводит сигнал, соответствующий свету, сфокусированному на блоке 10 пикселей. Сигнал, выводимым из элемента 1 регистрации изображения, поступает на процессор 830 видеосигнала. Процессор 830 видеосигнала осуществляет обработку сигнала согласно способу, определенному программой и т.п. Сигнал, полученный посредством обработки на процессоре 830 видеосигнала, отправляется на блок 840 записи/передачи в качестве данных изображения. Блок 840 записи/передачи отправляет сигнал для формирования изображения на блок 870 воспроизведения/отображения. Блок 870 воспроизведения/отображения воспроизводит и отображает движущееся или неподвижное изображение. Блок 840 записи/передачи принимает сигнал от процессора 830 видеосигнала для осуществления связи с системным регулятором 860 и записывает сигнал для формирования изображения на носителе записи (не показан).

[0096] Системный регулятор 860 полностью управляет работой системы регистрации изображения и управляет возбуждением оптического блока 810, регулятора 850 хронирования, блока 840 записи/передачи и блока 870 воспроизведения/отображения. Системный регулятор 860 включает в себя, например, запоминающее устройство (не показано) в качестве носителя записи. Программы и пр. необходимые для управления работой системы регистрации изображения, записываются в блоке хранения. Системный регулятор 860 подает сигнал для переключения режима возбуждения в соответствии, например, с операцией пользователя, на систему регистрации изображения. Подробными примерами являются изменение строки, подлежащей счету, изменение строки, подлежащей сбросу, изменение угла наблюдения для электронной трансфокации, и сдвиг угла наблюдения для электронного устранения вибрации. Регулятор 850 хронирования управляет хронированием возбуждения элемента 1 регистрации изображения и процессором 830 видеосигнала на основе системного регулятора 860.

[0097] Хотя настоящее изобретение описано со ссылкой на иллюстративные варианты осуществления, следует понимать, что изобретение не ограничивается раскрытыми иллюстративными вариантами осуществления. Объем нижеследующей формулы изобретения должен соответствовать самой широкой интерпретации, чтобы охватывать все подобные модификации и эквивалентные структуры и функции.

Изобретение относится к устройству фотоэлектрического преобразования и системе регистрации изображения. Устройство фотоэлектрического преобразования включает в себя фотоэлектрический преобразователь, транзистор, на затвор которого подается напряжение, соответствующее зарядам, генерируемым фотоэлектрическим преобразователем, линию управления, подключенную к первому главному электроду транзистора, и блок считывания, выполненный с возможностью считывания сигнала, соответствующего напряжению затвора, и регулятор напряжения, выполненный с возможностью изменения напряжения линии управления. Блок считывания генерирует цифровой сигнал, соответствующий напряжению затвора, на основании тока, текущего через второй главный электрод транзистора в течение периода, когда регулятор напряжения изменяет напряжение линии управления. Изобретение обеспечивает устройство фотоэлектрического преобразования, пригодное для упрощения конфигурации схемы каждого пикселя и получения многопиксельной конфигурации. 2 н. и 27 з.п. ф-лы, 20 ил.

1. Устройство фотоэлектрического преобразования, содержащее:

фотоэлектрический преобразователь;

транзистор, имеющий затвор, первый главный электрод и второй главный электрод, причем на затвор подается напряжение, соответствующее зарядам, генерируемым фотоэлектрическим преобразователем,

линию управления, подключенную к первому главному электроду транзистора, и

блок считывания, выполненный с возможностью считывания сигнала, соответствующего напряжению затвора; и

регулятор напряжения, выполненный с возможностью изменения напряжения линии управления,

при этом блок считывания генерирует цифровой сигнал, соответствующий напряжению затвора, на основании тока, текущего через второй главный электрод транзистора в течение периода, когда регулятор напряжения изменяет напряжение линии управления.

2. Устройство по п. 1, в котором в течение упомянутого периода регулятор напряжения изменяет напряжение линии управления для увеличения напряжения между затвором и первым главным электродом.

3. Устройство по п. 2, в котором блок считывания генерирует цифровой сигнал в соответствии с хронированием, при котором значение тока, текущего через второй главный электрод, превышает порог.

4. Устройство по п. 3, в котором блок считывания включает в себя:

компаратор, выполненный с возможностью обнаружения, что значение тока, текущего через второй главный электрод транзистора, превышает порог; и

счетчик, и

значение цифрового сигнала определяется в соответствии со значением отсчета счетчика в ответ на обнаружение, произведенное компаратором.

5. Устройство по п. 1, в котором регулятор напряжения

включает в себя:

переключатель, размещенный на пути между линией управления и линией первого напряжения; и

источник тока, размещенный на пути между линией управления и линией второго напряжения.

6. Устройство по п. 5, в котором регулятор напряжения дополнительно включает в себя конденсатор, подключенный к линии управления.

7. Устройство по п. 5, в котором линия управления имеет паразитную емкость.

8. Устройство по п. 1, в котором регулятор напряжения включает в себя:

конденсатор, имеющий первый узел, подключенный к линии управления;

переключатель, размещенный на пути между линией первого напряжения и первым узлом конденсатора; и

источник тока, размещенный на пути между линией второго напряжения и первым узлом конденсатора, и

при этом, после того, как конденсатор заряжен в соответствии с напряжением, поданным из линии первого напряжения благодаря замыканию переключателя, блок считывания генерирует цифровой сигнал в соответствии со временем от хронирования, при котором переключатель разомкнут, до хронирования, при котором значение тока, текущего через второй главный электрод транзистора, превышает порог.

9. Устройство по п. 1, в котором

линия управления имеет паразитную емкость,

регулятор напряжения включает в себя:

переключатель, размещенный на пути между линией управления и линией первого напряжения; и

источник тока, размещенный на пути между линией управления и линией второго напряжения, и

при этом, после того, как паразитная емкость заряжена в соответствии с напряжением, поданным из линии первого напряжения благодаря замыканию переключателя, блок считывания генерирует цифровой сигнал в соответствии со временем от хронирования, при

котором переключатель размокнут, до хронирования, при котором значение тока, текущего через второй главный электрод транзистора, превышает порог.

10. Устройство по п. 8, в котором

затвор транзистора подключен к преобразователю заряда в напряжение,

при этом устройство дополнительно содержит транзистор переноса, выполненный с возможностью переноса зарядов, генерируемых фотоэлектрическим преобразователем, на преобразователь заряда в напряжение, и транзистор сброса, выполненный с возможностью сброса напряжения преобразователя заряда в напряжение, и

причем по завершении сброса напряжения преобразователя заряда в напряжение транзистором сброса и завершении установления напряжения линии управления переключателем, блок считывания генерирует, в качестве сигнала, указывающего уровень шума, цифровой сигнал, соответствующий напряжению затвора в соответствии с хронированием, при котором значение тока, текущего через второй главный электрод транзистора, превышает порог, и затем

после того, как транзистор переноса перенесет заряды от фотоэлектрического преобразователя на преобразователь заряда в напряжение, и по завершении установления напряжения линии управления переключателем, блок считывания генерирует, в качестве сигнала, указывающего уровень оптического сигнала, цифровой сигнал, соответствующий напряжению затвора в соответствии с хронированием, при котором значение тока, текущего через второй главный электрод транзистора, превышает порог.

11. Устройство по п. 5, в котором напряжение линии первого напряжения определяется таким образом, что напряжение, установленное на линии управления благодаря замыканию переключателя, является напряжением, которое не отпирает транзистор.

12. Устройство по п. 1, дополнительно содержащее транзистор выбора, размещенный на пути между линией управления и первым

главным электродом транзистора.

13. Устройство по п. 1, дополнительно содержащее множество фотоэлектрических преобразователей, включающее в себя фотоэлектрический преобразователь, и множество транзисторов, включающее в себя транзистор,

при этом линия управления подключена к первым главным электродам множества транзисторов, и

блок считывания подключен ко вторым главным электродам множества транзисторов.

14. Устройство по п. 1, в котором регулятор напряжения обладает функцией переключения коэффициента усиления считывания блока считывания за счет переключения скорости изменения напряжения линии управления в течение периода.

15. Устройство по п. 1, в котором регулятор напряжения включает в себя:

переключатель, размещенный на пути между линией первого напряжения и линией управления; и

источник переменного тока, размещенный на пути между линией второго напряжения и линией управления, и

скорость изменения напряжения линии управления в течение периода переключается за счет переключения значения тока источника переменного тока, тем самым переключая коэффициент усиления считывания блока считывания.

16. Устройство по п. 1, в котором регулятор напряжения включает в себя:

переключатель, размещенный на пути между линией управления и линией первого напряжения;

источник тока, размещенный на пути между линией управления и линией второго напряжения; и

переменный конденсатор, подключенный к линии управления, и

скорость изменения напряжения линии управления в течение периода переключается за счет переключения значения емкости переменного конденсатора, тем самым переключая коэффициент усиления считывания блока считывания.

17. Устройство по п. 16, в котором переменный конденсатор включает в себя множество конденсаторов и множество

переключателей выбора, выполненных с возможностью выбора конденсатора, используемого для регулировки напряжения линии управления из множества конденсаторов.

18. Устройство по п. 17, в котором множество переключателей размещено на путях между линией управления и множеством конденсаторов.

19. Устройство по п. 1, в котором регулятор напряжения включает в себя:

переключатель, размещенный на пути между линией управления и линией первого напряжения;

источник переменного тока, размещенный на пути между линией управления и линией второго напряжения; и

переменный конденсатор, подключенный к линии управления, и

скорость изменения напряжения линии управления в течение периода переключается за счет переключения значения тока из источника переменного тока и переключения значения емкости переменного конденсатора, тем самым переключая коэффициент усиления считывания блока считывания.

20. Устройство по п. 1, в котором регулятор напряжения включает в себя:

конденсатор, имеющий первый узел, подключенный к линии управления, и второй узел;

переключатель, размещенный на пути между линией первого напряжения и первым узлом конденсатора; и

источник тока, размещенный на пути между линией второго напряжения и первым узлом конденсатора,

напряжение питания подается на второй узел конденсатора,

причем напряжение питания подается на блок считывания для обеспечения работы блока считывания, и

причем после того, как переключатель замыкается для зарядки конденсатора напряжением питания, блок считывания генерирует цифровой сигнал в соответствии со временем от хронирования, при котором переключатель разомкнут, до хронирования, при котором значение тока, текущего через второй главный электрод транзистора, превышает порог.

21. Устройство по п. 4, в котором

второй главный электрод транзистора подключен к измерительной линии, и

компаратор включает в себя:

второй транзистор, затвор и сток которого подключены к измерительной линии;

третий транзистор, затвор которого подключен к затвору второго транзистора, выполненный с возможностью, совместно со вторым транзистором, формировать токовое зеркало;

источник тока, подключенный к стоку третьего транзистора и выполненный с возможностью определения порога; и

схему вывода, выполненную с возможностью вывода сигнала, соответствующего напряжению узла между стоком третьего транзистора и источником тока.

22. Устройство по п. 21, в котором компаратор дополнительно включает в себя шунтирующий путь, выполненный с возможностью шунтирования пути между истоком и стоком третьего транзистора.

23. Устройство по п. 22, в котором

схема вывода включает в себя инвертирующий усилитель, вход которого подключен к узлу, и

шунтирующий путь образован n-МОП-транзистором, на затвор которого подается заранее определенное напряжение, и разность между заранее определенным напряжением и пороговым напряжением n-МОП-транзистора имеет положительное значение, меньшее порога инверсии инвертирующего усилителя.

24. Устройство по п. 4, в котором

второй главный электрод транзистора подключен к измерительной линии,

компаратор включает в себя:

второй транзистор, затвор и сток которого подключены к измерительной линии;

третий транзистор, выполненный с возможностью, совместно со вторым транзистором, формировать токовое зеркало, затвор которого подключен к затвору второго транзистора;

источник тока, выполненный с возможностью определения порога;

ограничитель амплитуды, размещенный между источником тока и

стоком третьего транзистора; и

схему вывода, выполненную с возможностью вывода сигнала, соответствующего напряжению узла между ограничителем амплитуды и источником тока, и

ограничитель амплитуды ограничивает амплитуду напряжения узла.

25. Устройство по п. 24, в котором

схема вывода включает в себя инвертирующий усилитель, вход которого подключен к узлу, и

ограничитель амплитуды образован n-МОП-транзистором, и разность между напряжением затвора n-МОП-транзистора и пороговым напряжением n-МОП-транзистора больше порога инверсии инвертирующего усилителя.

26. Устройство по п. 21, в котором компаратор включает в себя источник реактивного тока, подключенный к измерительной линии.

27. Устройство по п. 26, в котором, если обозначить M отношение размеров третьего транзистора ко второму транзистору и Iref значение тока источника тока, выполненного с возможностью определения порога, значение тока источника реактивного тока меньше Iref/M.

28. Устройство по п. 25, в котором разрешающий сигнал для управления компаратором в одном из рабочего и нерабочего состояний подается на затвор n-МОП-транзистора.

29. Система регистрации изображения, содержащая:

устройство фотоэлектрического преобразования по любому из пп. 1 - 28 и

процессор, выполненный с возможностью обработки сигнала из устройства фотоэлектрического преобразования.

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| СХЕМА ПИКСЕЛА, ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ И СИСТЕМА КАМЕРЫ | 2009 |

|

RU2494565C2 |

Авторы

Даты

2016-12-20—Публикация

2015-03-30—Подача