Изобретение относится к информационно-измерительной технике, в частности к преобразователям напряжения в длительность импульсов, и может быть использовано в информационно-измерительной аппаратуре, в аналого-цифровых преобразователях и т.п.

Известны интегральные преобразователи (ИП) непрерывного сигнала в длительность импульсов (частоту) [1-2].

Наиболее близким по технической сущности является ИП, который приведен в патенте RU №21 94999. Он содержит первый 1 источник положительного входного напряжения и последовательно соединенные интегратор 2 и релейный элемент 3. Погрешность преобразования напряжения известного ИП в период колебаний определяется качеством релейного элемента 3. Его интегральное исполнение для высокой точности (погрешность менее 0,1%) оказывается либо затруднительно, либо невозможно.

Основная задача предполагаемого изобретения состоит в повышении точности преобразования входного напряжения ИП в длительность импульсов. Кроме этого в предлагаемой схеме ИП реализуется преобразование в период как положительных

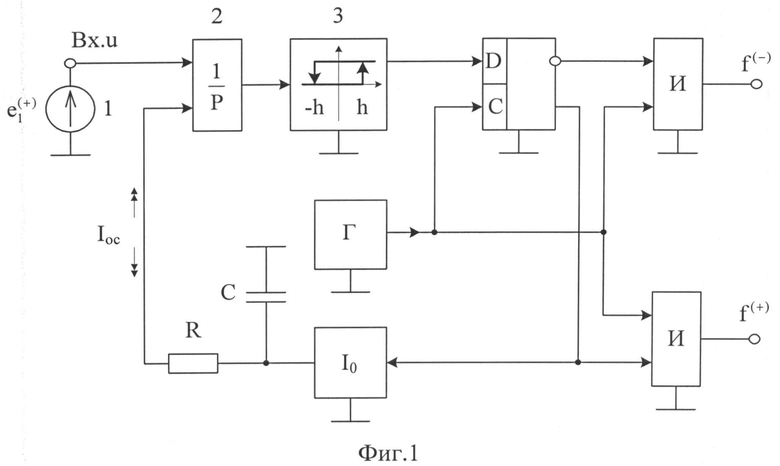

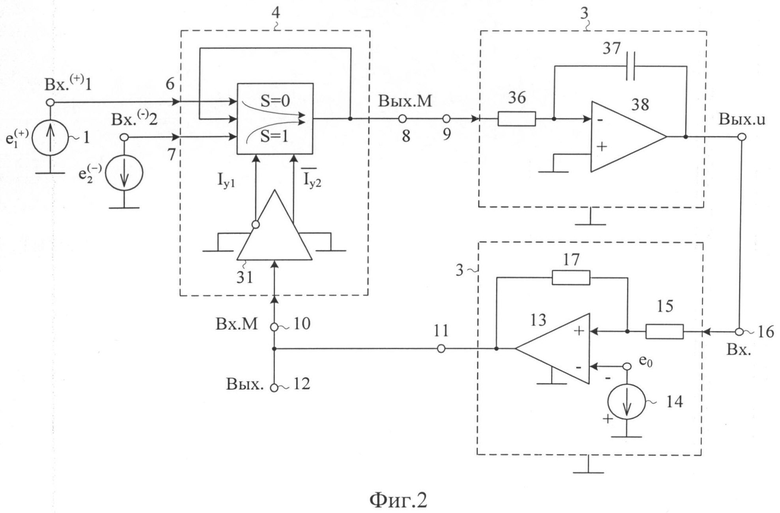

Поставленная задача достигается тем, что в преобразователе входного напряжения в длительность импульсов фиг.1, содержащем первый 1 источник положительного входного напряжения и последовательно соединенные интегратор 2 и релейный элемент 3, предусмотрены новые элементы и связи - в схему введен мультиплексор 4 первого 1 источника положительного входного напряжения и второго 5 дополнительного источника отрицательного входного напряжения, связанных с соответствующими первым 6 и вторым 7 входами мультиплексора 4, аналоговый выход 8 которого соединен со входом 9 интегратора 2, а цифровой вход 10 управления коммутацией первого 1 и второго 5 источников входных напряжений мультиплексора 4 связан с выходом 11 релейного элемента 3 и цифровым выходом 12 устройства, причем релейный элемент 3 выполнен на основе дополнительного операционного усилителя 13, инвертирующий вход которого соединен с источником опорного напряжения 14, а неинвертирующий вход - через первый 15 вспомогательный резистор соединен со входом 16 релейного элемента 3, а также через второй 17 вспомогательный резистор связан выходом 11 релейного элемента 3.

Схема преобразователя-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с П.1 формулы изобретения.

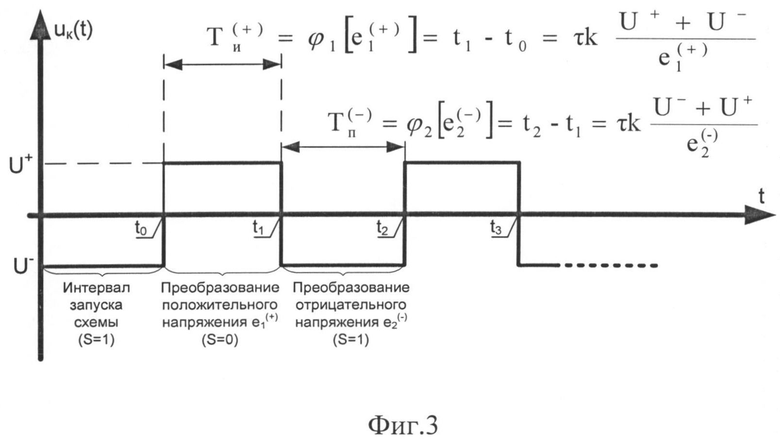

На чертеже фиг.3 показаны базовые временные диаграммы работы преобразователя входного напряжения в длительность импульсов фиг.2.

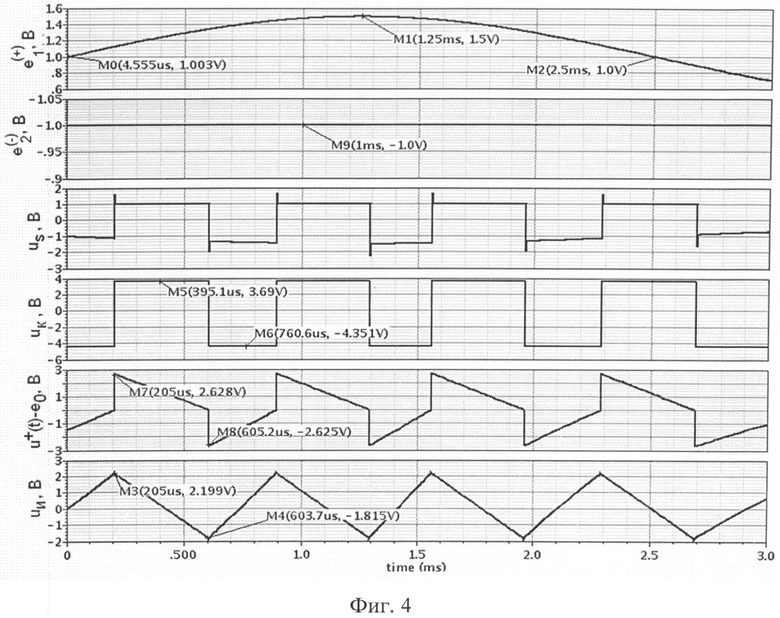

На чертеже фиг.4 показана временная диаграмма работы преобразователя входного напряжения фиг.2 в длительность импульсов при подаче на вход 1 переменного напряжения со смещением статического уровня, где сверху вниз показаны входное положительное напряжение 1

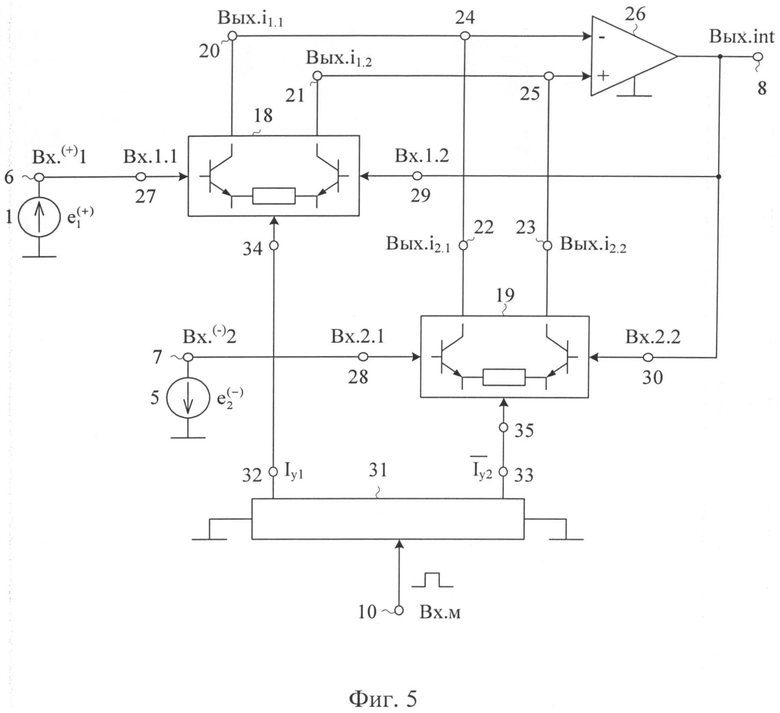

На чертеже фиг.5 приведена схема мультиплексора 4 в соответствии с П.2 формулы изобретения. Схема использовалась для исследований в среде компьютерного моделирования Cadence на моделях SiGe интегральных транзисторов.

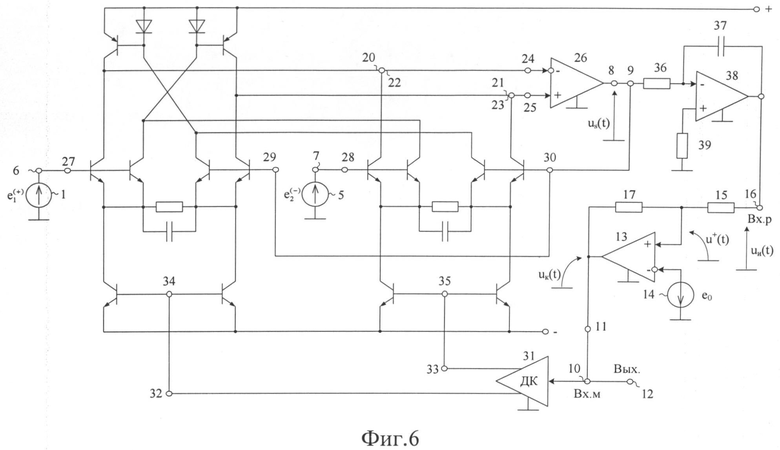

На чертеже фиг.6 приведен пример реализации базовых функциональных узлов заявляемого преобразователя на биполярных транзисторах.

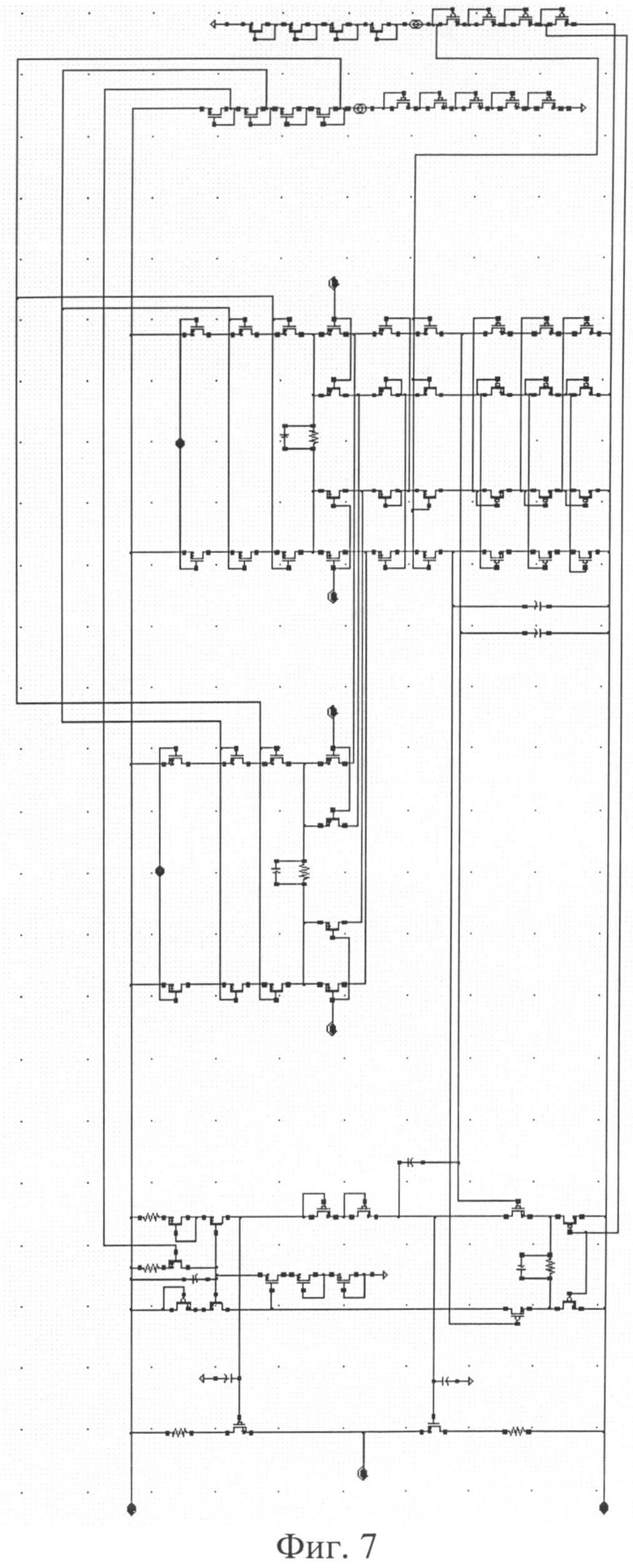

На чертеже фиг.7 приведен вариант построения мультиплексора 4 на КМОП-транзистораах.

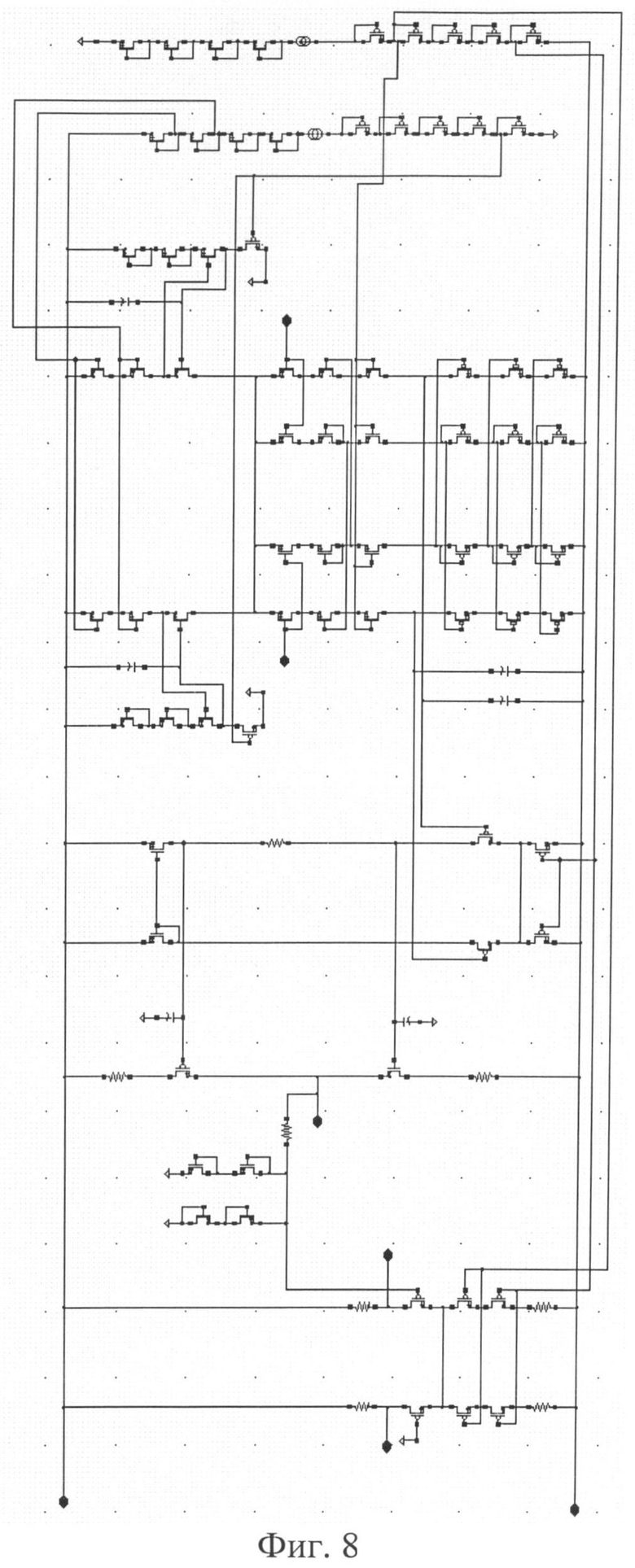

Схема релейного элемента 4 на КМОП-транзисторах показана на чертеже фиг.8.

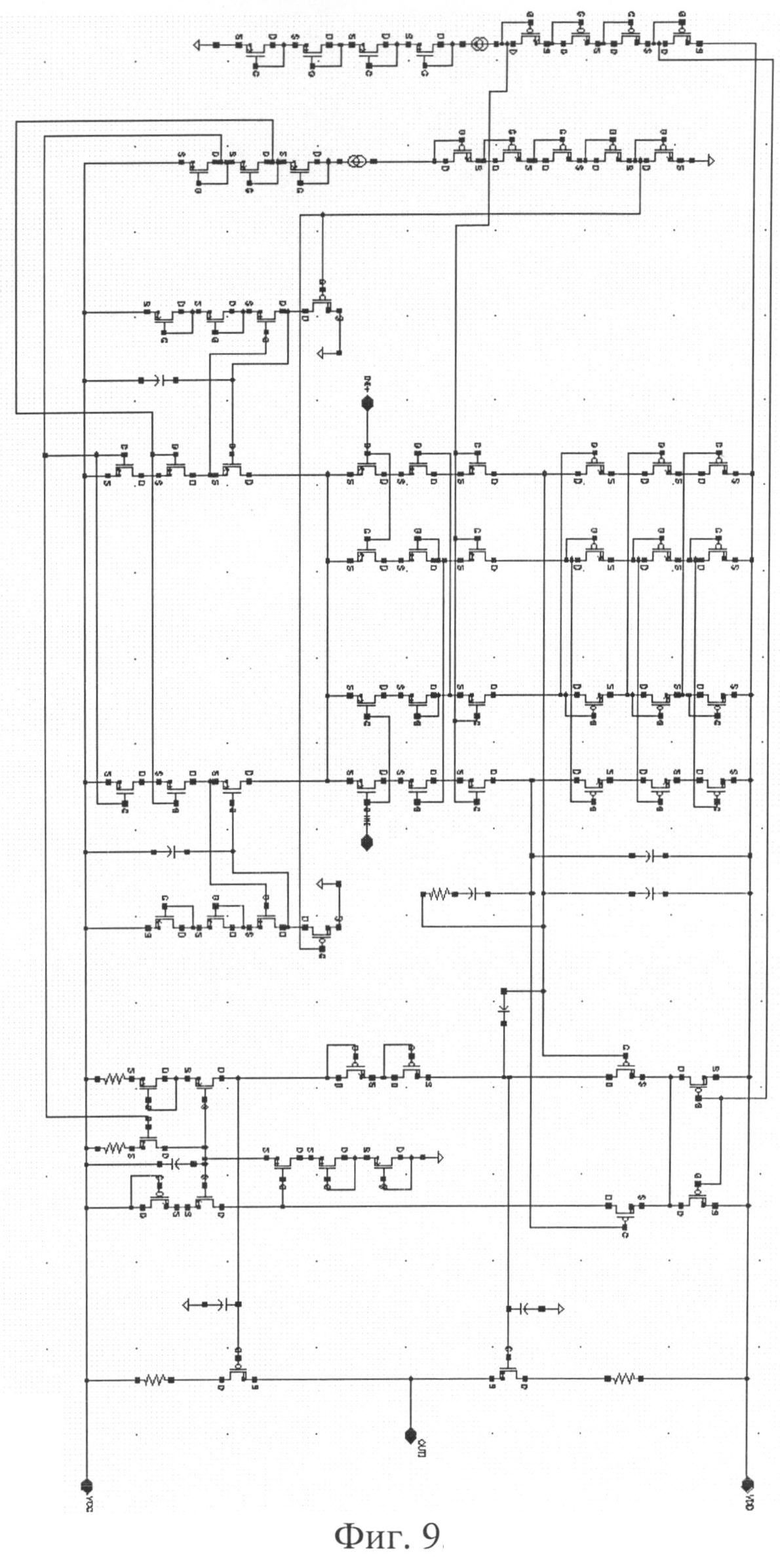

Вариант практической реализации интегратора 2 приведен на чертеже фиг.9.

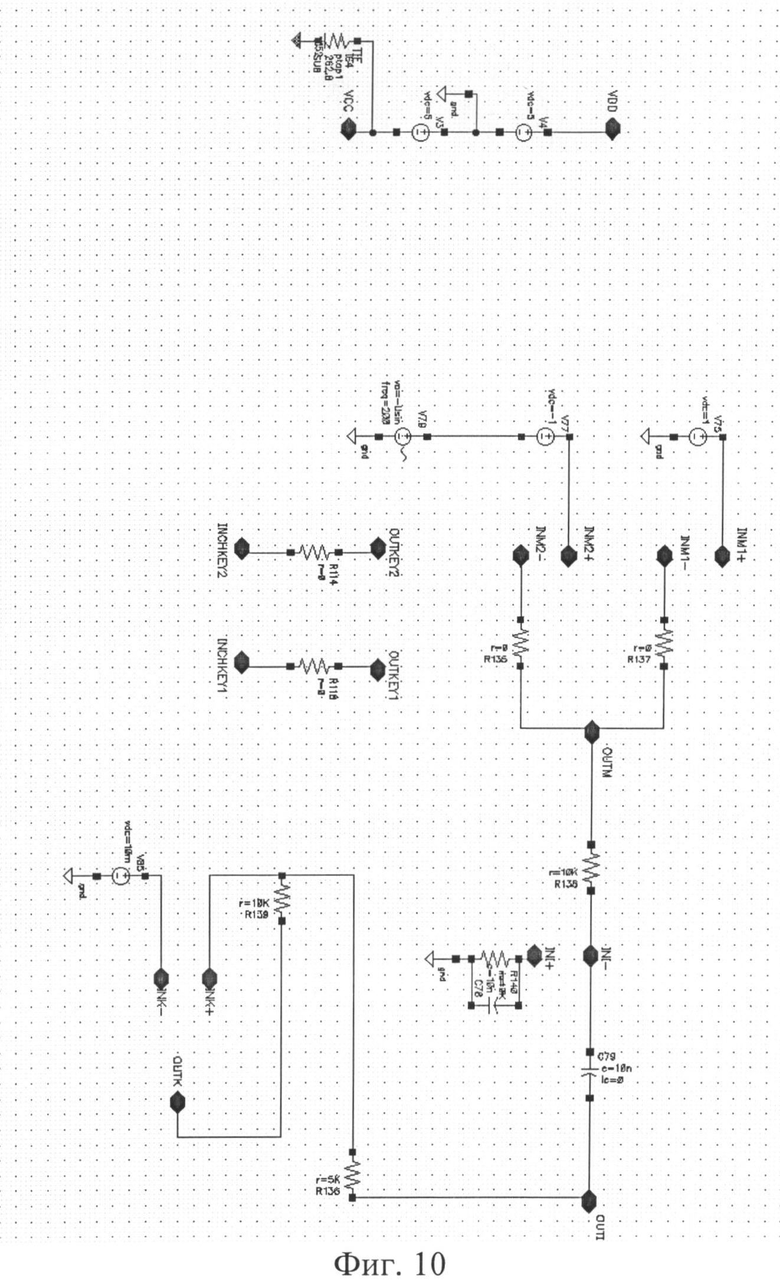

Схема соединения функциональных узлов преобразователя фиг.2 для моделирования показана на чертеже фиг.10.

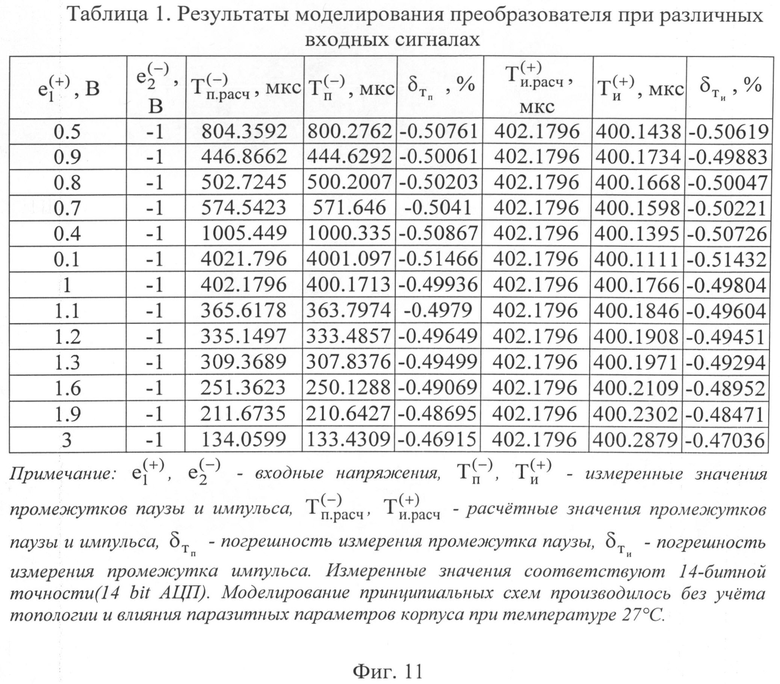

В таблице 1 (фиг.11) приведены результаты моделирования преобразователя фиг.10 при разных уровнях входных сигналов

В преобразователе напряжения в длительность импульсов фиг.2, содержащем первый 1 источник положительного входного напряжения и последовательно соединенные интегратор 2 и релейный элемент 3, введен мультиплексор 4 первого 1 источника положительного входного напряжения и второго 5 дополнительного источника отрицательного входного напряжения, связанных с соответствующими первым 6 и вторым 7 входами мультиплексора 4, аналоговый выход 8 которого соединен со входом 9 интегратора 2, а цифровой вход 10 управления коммутацией первого 1 и второго 5 источников входных напряжений мультиплексора 4 связан с выходом 11 релейного элемента 3 и цифровым выходом 12 устройства, причем релейный элемент 3 выполнен на основе дополнительного операционного усилителя 13, инвертирующий вход которого соединен с источником опорного напряжения 14, а неинвертирующий вход - через первый 15 вспомогательный резистор соединен со входом 16 релейного элемента 3, а также через второй 17 вспомогательный резистор связан выходом 11 релейного элемента 3.

Кроме этого, на чертеже фиг.5, в соответствии с П.2 формулы изобретения мультиплексор 4 содержит первый 18 и второй 19 дифференциальные каскады соответствующие противофазные токовые выходы которых 20 и 21, а также 22 и 23 соединены с соответствующими первым 24 и вторым 25 противофазными входами выходного дифференциального буферного каскада 26, первый 27 вход первого 18 дифференциального каскада соединен с первым 6 входом мультиплексора 4, первый 28 вход второго 19 дифференциального каскада соединен со вторым 7 входом мультиплексора 4, первый 28 вход второго 19 дифференциального каскада соединен со вторым 7 входом мультиплексора 4, вторые 29 и 30 входы первого 18 и второго 19 дифференциальных каскадов связаны с выходом 8 мультиплексора 4 и входом дифференциального буферного усилителя 26, причем цифровой вход 10 управления коммутацией первого 1 и второго 5 источников входных напряжений мультиплексора 4 подключен ко входу согласующего цифро-аналогового каскада 31, противофазные токовые выходы которого 32, 33 соединены с соответствующими противофазными входами 34, 35 выключения первого 18 и второго 19 дифференциальных каскадов.

Интегратор 2, показанный на чертежах фиг.2 и фиг.6, содержит резистор 36, конденсатор 37, операционный усилитель 38 и дополнительный резистор 39 (фиг.4).

Рассмотрим работу предлагаемой схемы ИП фиг.2 с мультиплексором фиг.5.

Интервал запуска схемы при нулевых начальных условиях интегратора 2 формирует напряжение интегратора 2, необходимое для последующего измерения входных величин (

После переключения релейного элемента 3, на его выходе 11 вырабатывается постоянное положительное напряжение (U+). Согласующий цифро-аналоговый каскад 31 в результате подачи на его вход 10 логической единицы (постоянного положительного напряжения на выходе 11 релейного элемента) вырабатывает на своем выходе 32 ток (Iy1), необходимый для перевода в активный режим (включения) первого 18 дифференциального каскада мультиплексора 4, а второй 19 дифференциальный каскад мультиплексора 4 переводит в режим отсечки отсутствием тока па выходе 33. Таким образом, согласующий цифро-аналоговый каскад 31 включает вход 6 мультиплексора 4 (S=0), подключая ко входу 9 интегратора 2 первый 18 дифференциальный каскад мультиплексора 4 с первым 1 источником положительного входного напряжения

После второго переключения релейный элемент 3 и мультиплексор 4 переходят в режимы аналогичные интервалу запуска схемы (S=1). Происходит преобразование подключенного к интегратору 2 входного отрицательного напряжения 5

Указанные выше процессы (исключая интервал запуска схемы) периодически повторяются, обеспечивая поочередное измерение как положительного входного напряжения 1

Покажем аналитически, что указанные выше свойства преобразователя реализуются в заявляемой схеме фиг.2.

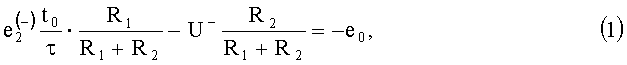

Действительно, используя методы анализа электронных схем можно показать, что для предлагаемого преобразователя (фиг.2) справедливы следующие соотношения:

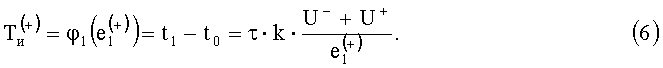

1. Время запуска схемы (S=1) в силу пренебрежимо низкого влияния

где R1 - сопротивление резистора 17, R2 - сопротивление резистора 15, τ - постоянная времени интегратора 2, U- - отрицательное выходное напряжение релейного элемента 3, е0 - напряжение опорного источника 14,

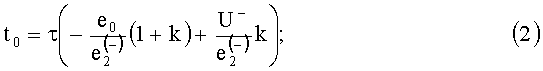

Тогда время запуска схемы определяется формулой

где (k=R2/R1) - коэффициент пропорциональности.

Таким образом, начальные условия формирования положительного напряжения импульса (этап преобразования

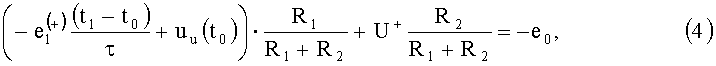

2. Время положительного импульса

где U+ - положительное выходное напряжения релейного элемента 3,

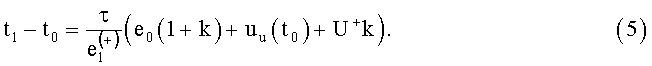

Длительность положительного импульса определяется из соотношения:

Таким образом,

Выходное напряжение интегратора 2 при этом определяет начальные условия формирования отрицательного импульса схемы:

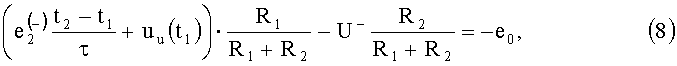

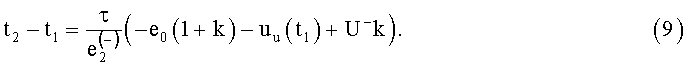

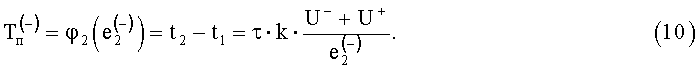

3. Время отрицательного импульса

Таким образом,

Выходное напряжение интегратора 2 uu(t2) совпадает с соотношением (3). Таким образом, обеспечивается восстановление начальных условий, необходимых для измерения

Принципиальные схемы узлов преобразователя напряжения в период колебаний на базе компонентов технологического процесса SGB25VD приведены на фиг.7-9. Схема соединения узлов преобразователя фиг.2 для моделирования показана на чертеже фиг.10. Результаты моделирования схемы показаны на фиг.4 и сведены в табл.1 (фиг.11) и показывают ее высокие метрологические свойства в силу того, что основная погрешность преобразования

Таким образом, заявляемое схемотехническое решение характеризуется высокой точностью преобразования входных положительных и отрицательных величин в частоту импульсов, высоким быстродействием при переключении входов и низким гистерезисом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2009613

2. Патент RU 2199758

3. Ав. свид. СССР №921080

4. Патент RU 2138826

5. Патент RU 2007029

6. Ав. свид. СССР №1441479

7. Ав. свид. СССР №16443 82

8. Патент на полезную модель RU 89259

9. Патент RU 2325664 C2

10. Патент RU 2194999

11. Патент SU 308506 A1

12. Патент RU 2208796

13. Патент RU 365037

14. Патент JP 63133071 A

15. Патент FR 2506463 A

16. Патент US 4931921 А

17. Патент SU 1397843 А

18. Патент RU 2160960

19. Патент GB 2082780 А

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжение-частота | 1974 |

|

SU725224A1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ МНОГОЭЛЕМЕНТНЫХ ПАССИВНЫХ ДВУХПОЛЮСНИКОВ | 2010 |

|

RU2466412C2 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ МНОГОЭЛЕМЕНТНЫХ RLC-ДВУХПОЛЮСНИКОВ | 2013 |

|

RU2556301C2 |

| Измеритель параметров многоэлементных RLC- двухполюсников | 2015 |

|

RU2615014C1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| УСТРОЙСТВО ДЛЯ СЪЕМА, РЕГИСТРАЦИИ И АНАЛИЗА ЭЛЕКТРОФИЗИОЛОГИЧЕСКИХ СИГНАЛОВ И БЛОК ЗАЩИТЫ ОТ АВАРИЙНЫХ ТОКОВ ПАЦИЕНТА | 1995 |

|

RU2102004C1 |

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Преобразователь напряжения в частоту | 1983 |

|

SU1238238A1 |

| Устройство для компенсации активно-гО TOKA уТЕчКи | 1979 |

|

SU851625A1 |

Изобретение относится к информационно-измерительной технике, в частности к преобразователям напряжения в длительность импульсов. Технический результат - повышение точности преобразования входного напряжения интегрального преобразователя (ИП) в длительность импульсов. Он достигается тем, что предложен преобразователь входного напряжения в длительность импульсов, содержащий первый источник положительного входного напряжения и последовательно соединенные интегратор и релейный элемент, при этом в схему введен мультиплексор первого источника положительного входного напряжения и второго дополнительного источника отрицательного входного напряжения, связанных с соответствующими первым и вторым входами мультиплексора, аналоговый выход которого соединен с входом интегратора, а цифровой вход управления коммутацией первого и второго источников входных напряжений мультиплексора связан с выходом релейного элемента и цифровым выходом устройства, причем релейный элемент выполнен на основе дополнительного операционного усилителя, инвертирующий вход которого соединен с источником опорного напряжения, а неинвертирующий вход - через первый вспомогательный резистор соединен с входом релейного элемента, а также через второй вспомогательный резистор связан с выходом релейного элемента. 1 з.п. ф-лы, 11 ил.

1. Преобразователь входного напряжения в длительность импульсов, содержащий первый (1) источник положительного входного напряжения и последовательно соединенные интегратор (2) и релейный элемент (3), отличающийся тем, что в схему введен мультиплексор (4) первого (1) источника положительного входного напряжения и второго (5) дополнительного источника отрицательного входного напряжения, связанных с соответствующими первым (6) и вторым (7) входами мультиплексора (4), аналоговый выход (8) которого соединен со входом (9) интегратора (2), а цифровой вход (10) управления коммутацией первого (1) и второго (5) источников входных напряжений мультиплексора (4) связан с выходом (11) релейного элемента (3) и цифровым выходом (12) устройства, причем релейный элемент (3) выполнен на основе дополнительного операционного усилителя (13), инвертирующий вход которого соединен с источником опорного напряжения (14), а неинвертирующий вход через первый (15) вспомогательный резистор соединен со входом (16) релейного элемента (3), а также через второй (17) вспомогательный резистор связан с выходом (11) релейного элемента (3).

2. Преобразователь входного напряжения в длительность импульсов по п.1, отличающийся тем, что мультиплексор (4) содержит первый (18) и второй (19) дифференциальные каскады, соответствующие противофазные токовые выходы которых (20) и (21), а также (22) и (23) соединены с соответствующими первым (24) и вторым (25) противофазными входами выходного дифференциального буферного каскада (26), первый (27) вход первого (18) дифференциального каскада соединен с первым (6) входом мультиплексора (4), первый (28) вход второго (19) дифференциального каскада соединен со вторым (7) входом мультиплексора (4), первый (28) вход второго (19) дифференциального каскада соединен со вторым (7) входом мультиплексора (4), вторые (29) и (30) входы первого (18) и второго (19) дифференциальных каскадов связаны с выходом (8) мультиплексора (4) и входом дифференциального буферного усилителя (26), причем цифровой вход (10) управления коммутацией первого (1) и второго (5) источников входных напряжений мультиплексора (4) подключен ко входу согласующего цифроаналогового каскада (31), противофазные токовые выходы которого (32), (33) соединены с соответствующими противофазными входами (34), (35) выключения первого (18) и второго (19) дифференциальных каскадов.

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2194999C1 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1999 |

|

RU2179320C2 |

| ИНТЕГРАЛЬНЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2325664C2 |

| US 7808412 B2, 05.10.2010. | |||

Авторы

Даты

2013-07-27—Публикация

2012-08-24—Подача