00 о СП

Од

Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразователях (AUII) , в пороговых устройствах прецизионной измеритель(юй аппаратуры, в частности при контроле точностных параметров микроэлектронных ПАП и АЦП.

Целью изобретения является повышение точности и разрешаюп;ей способности за счет изменения влияния дестабилизирующих факторов.

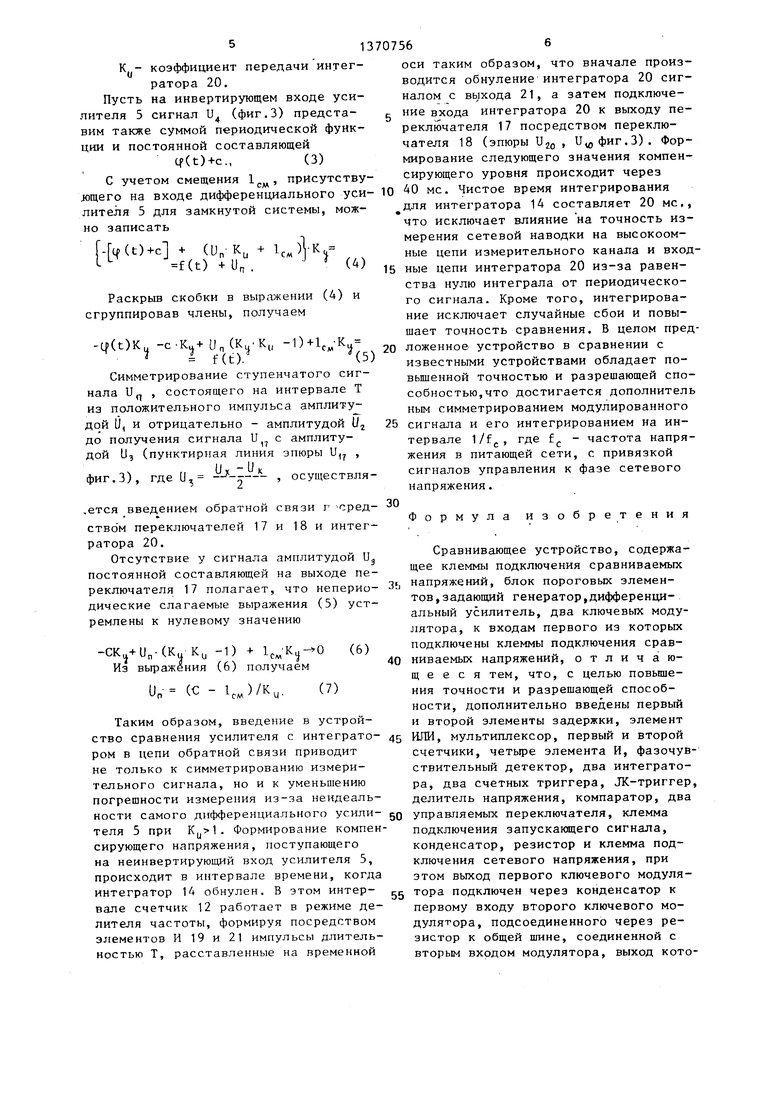

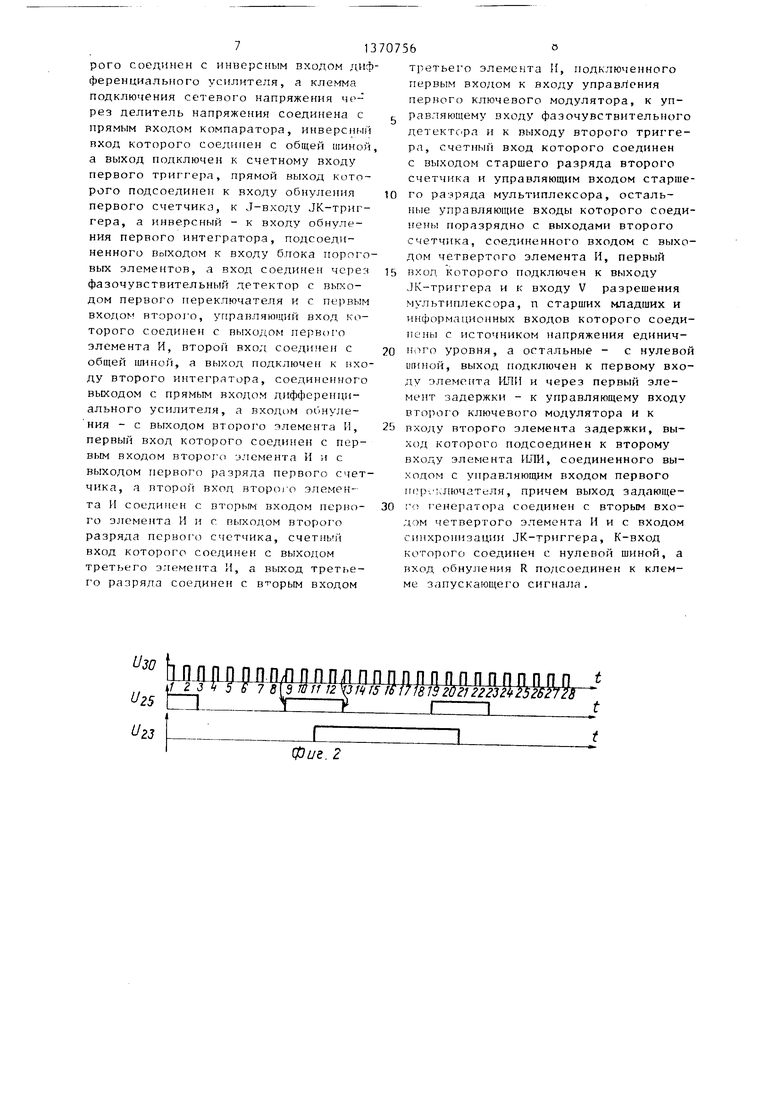

На фиг.1 изображена функциональная схема устройства , на фиг. 2 и 3 - эпюры напряжений на выходах основных элементов устройства.

Сравнивающее устройство содержит клеммы 1 и 2 подключения сравниваемы

первого элемента И 19 и с выходом второго разряда первого счетчика 12, счетный вход которого соединен с вы- ходом третьего элемента И 22, а выход третьего разряда соединен с вторым (инверсным) входом третьего элемента И 22, пер.ЫЙ вход которого подключен к входу управления первым ключевым модулятором 3, к управляющему входу фазочувствительного детектора 16 и к выходу второго триггера -23, счетный вход которого соединен с выходом старшего разряда второго счетчика 24 и с входом старшего разряда мультиплексора 25, остальные управляющие входы которого соединены поразрядно с выходами второго счетчика 24, вход которого соединен с выхо

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Устройство для измерения температуры | 1984 |

|

SU1229601A1 |

| Цифровой интегрирующий вольтметр | 1990 |

|

SU1798711A1 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| ПРЕОБРАЗОВАТЕЛЬ НЕЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН В ЦИФРОВОЙ КОД | 1991 |

|

RU2020745C1 |

| Устройство для управления возбудителем механических колебаний | 1980 |

|

SU957181A1 |

| Вторичные цифровые часы с секундомером | 1987 |

|

SU1478187A2 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразователях (АЦП), в пороговых устройствах прецизионной измерительной аппаратуры, в частности при контроле точности параметров микроэлектронных циф- роаналоговых преобразователей и АЦП. Цель изобретения - повьш1ение точности и разрешающей способности - достигается за счет исключения влияния дестабилизирующих факторов. Устройство содержит клеммы 1 и 2 для подключения сравниваемьпс напряжений, ключевые модуляторы 3 и 4, дифференциальный усилитель 5, клемму 8, делитель 9 напряжения, компаратор 10, триггеры 11, 23, счетчики 12,24, JK-триггер 13, интеграторы 14, 20, блок 15 пороговых элементов, фазо- чувствительный детектор 16, переключатели 17 и 18, элементы И 19,21 и 22,26, мультиплексор 25, элемент 27 Iira-I, элементы 28 и 29 задержки, задающий генератор 30, клемму 31 запуска. По сравнению с известными пред ложенное устройство обладает повышенной точностью и разрешающей способностью. Это обеспечивается дополнительным симметрированием модулированного сигнала и его интегрированием с привязкой сигналов управления к фазе сетевого напряжения. 3 ил. е (Л

напряжений к входам первого ключево- 20 дом четвертого элемента И 26, первый го модулятора 3, второй ключевой модулятор 4, дифференциальный усиливход которого подключен к выходу JK-триггера 13 и к входу V-разреше- ния мультиплексора 25, п старших и млад1иих информационных входов которого соединены с источником напряжения единичног о уровня, а остальные - с нулевой шиной, выход подключен к первому входу элемента Ш1И 27 и через первый элемент 28 задержки - к управ.тяющему входу второго ключевого модулятора 4 и к входу второго элемента 29 задержки, выход которого подсоединен к второму входу элемента 1ШИ 27,выход которого соединен с управляющим входом первого переключателя 17, причем выход задающего ге нератора 30 соединен с вторым входом четвертого элемента И 26 и с входом синхронизации JK-триггера 13. К-вход которого соединен с нулевой шиной, а вход обнуления R подсоединен к запускающей клемме 31.

тель 5,при этом выход первого ключевого модулятора 3 подключен через кон- де)1сатор 6 к первому входу второго ключевого модулятора 4, подсоединенно го через резистор 7 к общей шине, соединенной С вторым входом второго модулятора 4, пыход которого coojHineH с И}шерсным входом дифференциального усилителя 5, а клемма 8 подключе т сетевого напряжения через делитель 9 напряжения соединена с прямым входом компаратора 10, инверсный вход которого соединен с общеГ iiniHoii, а выход подключен к счетному входу первого триггера 11, прямой выход которого подсоединен к входу обнуления первого счетчика 12, к J-входу JK-тригге- ра 13, а инверсный - к входу обнуле- ПИЯ первого И1ггегратора 14, выход которого подсоединен к входу блока 15 пороговых элементов, а вход соединен через фазочувствительньи детектор 16 с выходом первого нере слючателя 17 и с первым входом второго 18, управляющий вход которого соединен с Biii- ходом первого элемента И 19, второй вход соединен с (збщей шиной, а выход подключен к входу второго интеграто- ра20, выход которого соединен с пря- входом дифференциального усилителя 6, а вход обнуления - с выходом втор зго элемсмгга И 21, дервьп вход которого соединен с первым входом перпого элемента И 19 и с. выходом пер Бого разряда первс5Г(т счетчика 12, а второй, инверсный вход HTiiporo элемента И 21 соединен с втор(1м BXOZTOM

0 дом четвертого элемента И 26, первый

5 0 5 0

5

0

5

вход которого подключен к выходу JK-триггера 13 и к входу V-разреше- ния мультиплексора 25, п старших и млад1иих информационных входов которого соединены с источником напряжения единичног о уровня, а остальные - с нулевой шиной, выход подключен к первому входу элемента Ш1И 27 и через первый элемент 28 задержки - к управ.тяющему входу второго ключевого модулятора 4 и к входу второго элемента 29 задержки, выход которого подсоединен к второму входу элемента 1ШИ 27,выход которого соединен с управляющим входом первого переключателя 17, причем выход задающего генератора 30 соединен с вторым входом четвертого элемента И 26 и с входом синхронизации JK-триггера 13. К-вход которого соединен с нулевой шиной, а вход обнуления R подсоединен к запускающей клемме 31.

Устройство работает следующим образ ом.

Сравниваемые напряжения U, и U подаются на клеммы 1 и 2. На клемму 8 подается переменное напряжение (предположительно, с вторичной обмотки сетевого трансформатора блока питания устройства) частотой 50 Гц.В первоначальном состоя 1ии на клемме 31 присутствует высокий уровень напряжения, который удерживает триггер 13 в нулевом состоянии. Переменное напряжение частотой 50 Гц приводится делителем 9 к уровню, необходимому для } ормальной работы компаратора 10 напряжения. Запуск устройства производится подачей на клемму 31 нулевого

потенциала (логического нуля -0). Таким образом, переключение в единичное Состояние JK-триггера 13 происходит после того, как компаратор Ю сменит свое состояние по фронту импульса, поступающего на синхровход JK-триггера 13 с выхода задающего генератора 30. При переходе JK-триггера 13 в единичное состояние откры- вается элемент И 26 и дается разрешение (вход V) на работу мультиплексора 25.

На фиг.2 показаны эпюры напряжений, формируемых на выходах мульти- плексора 25 и триггера 23,где показано, что фронт Ujj находится на середине импульса . Начало формирования указанных напряжений i про исходит по сигналу с выхода JK-триг- гера 13. Таким образом осуществляется привязка сигналов управления к фазе сигнала сети (- 50 Гц). На вход JK-триггера 13 приходят импульсы с выхода триггера 11 частотой 25 Гц и скважностью - 2. В результате 20 мс на входе обнуления R-счетчика 12 присутствует уровень, удерживающий счетчик 24 в нулевом состоянии. Единичный уровень напряжения, снимаемый с выхода JK-триггера 13, открывает элемент И 26 в момент перехода сетевого сигнала через нулевой уровень. При этом счетные импульсы поступают на вход счетчика 24,управляющего ра- ботой мультиплексора 25. На выходе мультиплексора 25 формируются при этом импульсы и 5высокой скважности. Середина этих импульсов совпадает с фронтом импульсов, снимаемых с выхо да триггера 23 (эпюры , U,,, фиг. 2) По фронтам сигналов, снимаемых с выхода триггера 23, скважность которых равна двум- и не зависит от скважности импульсов задающего генерато- ра 30, и импульсов, снимаемых с выхода элемента 28 задержки, происходит переключение ключевых модуляторов 3 и 4. В результате на резисторе 7 образуется переменное напряжение, в общем случае несимметричное относительно нулевого уровня. Это происходит из-за того, что выбросы (глитчи) в положительную область в принципе не могут быть равны выбросам в отрицательную область напряжения в свою очередь из-за различных параметров источников сравниваемых напряжений, из-за различной длины, индуктивности

- Q

J5 2025 зо ,- -дд . д

50

5

и емкости проводников, соединяющих источники сравниваемых напряжений. Выбросы на резисторе 7 (фиг.З, U), возникающие в момент переключения ключевого модулятора 3, зависят также от величин сравниваемых напряжений и в диапазоне сравниваемых напряжений 10 В могут достигать нескольких сотен милливольт.

Таким образом сигнал U , поступающий с выхода ключевого модулятора 4 на инвертирующий вход дифференциального усилителя 5, не приводит к пё енасьпцению дифференциального усилителя 5 на всей временной оси. Усиленный сигнал Uy, снимаемый с выхода усилителя 5, стробируется посредством переключателя 17 таким образом, что вы&росы, возникшие по фронтам управляющего сигнала ключевым модулятором 4, прошедшие через усилитель 5, усиленные в К,, раз (К„- коэффициент усиления дифференциального усилителя 5), не проходят на вход управляемого переключателя 17.

Элементы 28 и 29 задержки и логический элемент ИЛИ 27 формируют импульсы , и , стробирующие измерительный сигнал таким образом, что на выходе управляемого переключателя 17 отсутствуют глитчи на измерительном сигнале U,j (фиг.З).

Предположим, что цепь обратной связи дифференциального усилителя 5 через переключатели 17 и 18 и интегратор 20 разомкнута, а его неинвертирующий вход подключен к общей шине. При этом ступенчатый измерительный сигнал и не симметричен относительно нулевого уровня (фиг.З и, ), и, и Uj . Считая сигнал функцией, состоящей из суммы периодической составляющей и постоянного уровня, можно записать

и„ f(t) и,, (1)

где f(t) - периодическая функция

и„ - постоянный уровень. Если и проинтегрировать за период Т, где Т - период Uj, , то напряжение на выходе интегратора 20

равно

т

и, i J (f(t) (/„)dt |и„. )

о

где Т - постоянная времени интегратора 20;

Ку- коэффициент передачи интегратора 20.

Пусть на инвертирующем входе усилителя 5 сигнал и (фиг.З) представим также суммой периодической функции и постоянной составляющей

q (t)+c., (3)

С учетом смещения 1

присутствуоси таким образом, что вначале прои водится обнуление интегратора 20 си налом с выхода 21, а затем подключе g ние входа интегратора 20 к выходу п реключателя 17 посредством переключателя 18 (эпюры UjQ , фиг.З). Фо мирование следующего значения компе сирующего уровня происходит через

Ж)щего на входе дифференциального уси- 10 мс. Чистое время интегрирования

для интегратора 14 составляет 20 мс что исключает влияние на точность и мерения сетевой наводки на высокоом ные цепи измерительного канала и вх

лителя 5 для замкнутой системы, можно записать

- чСО-ьс

(и,-к.

+ 1

f(t) +Un

CM

Раскрью скобки в выражении группировав члены, получаем

(4) (4) и

-q (t)K. -C-KU+ Un (Ku K

f(t).

-l).K

(t); 45)

Симметрирование ступенчатого сигнала Uf. , состоящего на интервале Т из положительного импульса амплиту- (J, и отрицательно - амплитудой Uj до получения сигнала U с амплитудой УЗ (пунктирная линия эпюры U, ,

фиг.З), где Ц -- -о- - 5 осуществля- ,ется введением обратной связи г Сред

ством переключателей 17 и 18 и интегратора 20.

Отсутствие у сигнала амплитудой Uj постоянной составляющей на выходе переключателя 17 полагает, что непериодические слагаемые выражения (5) устремлены к нулевому значению

,(к. к, -1) + (6)

Из вьфажения (6) получаем

Un (С - 1.„)/К.. (7)

Таким образом, введение в устройствительный детектор, два интегратора, два счетных триггера, JK-триггер, делитель напряжения, компаратор, два

ство сравнения усилителя с интеграто- 45 ИЛИ, мультиплексор, первый и второй ром в цепи обратной связи приводит счетчики, четьфе элемента И, фазочув- не только к симметрированию измерительного сигнала, но и к уменьшению погрешности измерения из-за неидеальности самого дифференциального усили- gg управляемых переключателя, клемма теля 5 при . Формирование компенсирующего напряжения, поступающего на неинвертирующий вход усилителя 5, происходит в интервале времени, когда интегратор 14 обнулен, В этом интервале счетчик 12 работает в режиме де55

подключения запускающего сигнала, конденсатор, резистор и клемма подключения сетевого напряжения, при этом выход первого ключевого модулятора подключен через конденсатор к первому входу второго ключевого модулятора, подсоединенного через резистор к общей шине, соединенной с вторым входом модулятора, выход котолителя частоты, формируя посредством элементов И 19 и 21 импульсы длительностью Т, расставленные на временной

07566

оси таким образом, что вначале производится обнуление интегратора 20 сигналом с выхода 21, а затем подключе- g ние входа интегратора 20 к выходу переключателя 17 посредством переключателя 18 (эпюры UjQ , фиг.З). Формирование следующего значения компенсирующего уровня происходит через

мс. Чистое время интегрирования

для интегратора 14 составляет 20 мс,, что исключает влияние на точность измерения сетевой наводки на высокоом- ные цепи измерительного канала и входные цепи интегратора 20 из-за равенства нулю интеграла от периодического сигнала. Кроме того, интегрирование исключает случайные сбои и повышает точность сравнения. В целом предложенное устройство в сравнении с известными устройствами обладает повышенной точностью и разрешающей способностью,что достигается дополнитель ным симметрированием модулированного

сигнала и его интегрированием на ин - частота напря

тервале l/f., где

жения в питающей сети, с привязкой сигналов управления к фазе сетевого напряжения.

Формула изобретения

Сравнивающее устройство, содержащее клеммы подключения сравниваемых напряжений, блок пороговых элементов,задающий генератор,дифференциальный усилитель, два ключевых модулятора, к входам первого из которых подключены клеммы подключения сравниваемых напряжений, отличающееся тем, что, с целью повышения точности и разрешающей способности, дополнительно введены первый и второй элементы задержки, элемент

ствительный детектор, два интегратора, два счетных триггера, JK-триггер, делитель напряжения, компаратор, два

ИЛИ, мультиплексор, первый и второй счетчики, четьфе элемента И, фазочув- управляемых переключателя, клемма

ИЛИ, мультиплексор, первый и второй счетчики, четьфе элемента И, фазочув- управляемых переключателя, клемма

подключения запускающего сигнала, конденсатор, резистор и клемма подключения сетевого напряжения, при этом выход первого ключевого модулятора подключен через конденсатор к первому входу второго ключевого модулятора, подсоединенного через резистор к общей шине, соединенной с вторым входом модулятора, выход кото713

poro соединен с инверсным входом дифференциального усилителя, а клемма подключения сетевого напряжения через делитель напряжения соединена с прямым входом компаратора, инверсн 4Й пход которого соединен с общей шиной а выход подключен к счетному входу первого триггера, прямой выход которого подсоединен к входу обнуления первого счетчика, к J-входу JK-триг- гера, а инверсный - к входу обнуления первого интегратора, подсоединенного Впгходом к входу блока пороговых элементов, а вход соединен через фазочувствительный детектор с выходом первого переключателя и с первым входом BTopoi o, управляющий вход которого соединен с выходом первого элемента И, второй вход соединен с общей тиной, а выход подключен к входу второго интегратора, соединенного вькодом с прямым входом дифференди- ального усилителя, а входом обнуле- ния - с выходом второго элемента И, первый вход которого соединен с первым входом второго элемента И и с выходом первого разряда первого счетчика, я второй вход BTopoi o элемента И соединен с вторым входом первого элемента И и с выходом второг о разряда первого счетчика, счетный вход которого соединен с выходом третьего эттемента И, а выход третье- г о разряда соединен с входом

0756°

третьего элемента II, подключенного первым входом к входу управления первого ключевого модулятора, к управляющему входу фазочувствительного детектора и к выходу второго триггера, счетный вход которого соединен с выходом старшего разряда второго счетчика и управляющим входом старшеТО го разряда мультиплексора, остальные управляющие входы которого соединены поразрядно с выходами второго счетчика, соединенного входом с выходом четвертого элемента И, первый

15 вход которого подключен к выходу JK-триггера и к входу V разрешения мультиплексора, п старших младших и информационных входов которого соединены с источником напряжения единич20 ного уровня, а остальные - с нулевой игиной, выход подключен к первому входу элемента ИЛИ и через первый элемент задержки - к управляющему входу второго ключевого модулятора и к

25 входу второго элемента задержки, выход которого подсоединен к второму входу элемента ИЛИ, соединенного выходом с управляющим входом первого 1Г(;р ;лючателя, причем выход задающе30 о генератора соединен с вторым входом четвертого элемента И и с входом синхронизации JK-триггера, К-вход которого соединен с нулевой шиной, а вход обнуления R подсоединен к клемме запускающего сигнала.

% %

игэ иг

ТП

п

m

п

п

q

tJ2

П

п п пп

и

П1

t3Z

п п п п nt

Ui

UL

5

7

гомс

сарссинтеЩ

l

и

п п пп

П1

CSooc

интегр. 7

Шос интегр.щ.Раоотаин- t

mf}.20u

lus

фие.З

| Шляндин В.М | |||

| Цифровые измерительные преобразователи и приборы | |||

| М.: Высшая школа | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1988-01-30—Публикация

1986-04-07—Подача