Область техники, к которой относится изобретение

Настоящее изобретение относится к схеме возбуждения устройств отображения, таких как жидкокристаллические устройства отображения, имеющие жидкокристаллическую панель отображения с активной матрицей и, в частности, к схеме возбуждения устройства отображения, устройству отображения и способу возбуждения устройства отображения для возбуждения панели отображения в устройстве отображения, использующем систему возбуждения, именуемую СС-возбуждение (с зарядовой связью).

Уровень техники

Известная система возбуждения с зарядовой связью, используемая в жидкокристаллическом устройстве отображения с активной матрицей, описана, например, в Патентной Литературе 1. Принцип управления устройством отображения с использованием возбуждения с зарядовой связью объяснен на основе содержания описания изобретения в Патентной Литературе 1 в качестве примера.

На Фиг.20 показана конфигурация устройства, реализующего возбуждение с зарядовой связью. На Фиг.21 показаны формы различных сигналов в схеме возбуждения с зарядовой связью в устройстве, изображенном на Фиг.20.

Как показано на Фиг.20, жидкокристаллическое устройство отображения, использующее возбуждения с зарядовой связью, включает секцию 110 видеоустройства отображения, схема возбуждения 111 линий истоковых шин, схема возбуждения 112 линий затворных шин и схему возбуждения 113 линий шин накопительных конденсаторов (CS-линий).

Секция 110 видеоустройства отображения включает несколько истоковых линий (сигнальных линий) 101, несколько затворных линий (линий развертки) 102, переключающие элементы 103; пиксельные электроды 104; несколько линий 105 шин накопительных конденсаторов (CS-линий) (линии общих электродов), удерживающие конденсаторы 106, жидкие кристаллы 107 и контрэлектрод 109. Переключающие элементы 103 расположены возле точек пересечения между несколькими истоковыми линиями 101 и несколькими затворными линиями 102, соответственно. Пиксельные электроды 104 соединены с переключающими элементами 103, соответственно.

Линии 105 (CS-линии) шин накопительных конденсаторов спарены с затворными линиями 102, соответственно, и расположены параллельно одни другим. Один вывод каждого из удерживающих конденсаторов 106 соединен с пиксельным электродом 104, а другой вывод этого конденсатора соединен с CS-линией 105. Контрэлектрод 109 располагается напротив пиксельных электродов 104, так что жидкие кристаллы 107 вложены между этими электродами.

Схема возбуждения 111 линий истоковых шин передает сигнал в истоковые линии 101. а схема возбуждения 112 линий затворных шин передает сигналы в затворные линии 102. Кроме того, схема возбуждения 113 линий CS-шин передает сигналы в CS-линии 105.

Каждый из переключающих элементов 103 выполнен из аморфного кремния (a-Si), поликристаллического кремния (p-Si), монокристаллического кремния (c-Si) и т.п. Благодаря такой структуре между затвором и стоком переключающего элемента 103 образован конденсатор 108. Этот конденсатор 108 создает эффект, в соответствии с которым затворный импульсный сигнал из затворной линии 102 сдвигает потенциал пиксельного электрода 104 в отрицательном направлении.

Как показано на Фиг.21, потенциал Vg затворной линии 102 в жидкокристаллическом устройстве отображения равен Von только в течение того периода горизонтальной развертки (Н-периода), в котором выбрана эта затворная линия 102, и остается равным Voff в течение других периодов. Амплитуда потенциала Vs истоковой линии 101 изменяется в зависимости от видеосигнала, который нужно представить на устройстве отображения, а форма этого потенциала инвертирует свою полярность в каждом Н-периоде относительно потенциала Vcom контрэлектрода и инвертирует полярность в соседнем Н-периоде, рассматривая ту же самую затворную линию 102 (управление с инверсией линии). Поскольку на Фиг.21 предполагается, что на вход поступает равномерный видеосигнал, потенциал Vs изменяется с постоянной амплитудой.

Потенциал Vd пиксельного электрода 104 равен потенциалу Vs истоковой линии 101, поскольку переключающий элемент 103 проводит электрический ток в период, когда потенциал Vg равен Von, и, в момент, когда потенциал Vg становится равен Voff, потенциал Vd немного сдвигается в отрицательном направлении через конденсатор 108 затвор-сток.

Потенциал Vc в CS-линии 105 равен Ve+ в течение Н-периода, в котором выбрана соответствующая затворная линия 102, и в течение следующего Н-периода. Далее, потенциал Vc переключается на уровень Ve- в течение Н-периода после указанного следующего периода и затем остается на этом уровне Ve- до следующего поля. В результате этого переключения потенциал Vd сдвигается в отрицательном направлении через удерживающий конденсатор 106.

В результате потенциал Vd изменяется с большей амплитудой, чем потенциал Vs; вследствие этого амплитуду изменений потенциала Vs можно сделать меньше. Это позволит упростить схему и уменьшить потребляемую мощность в схеме возбуждения 111 линий истоковых шин.

Список литературы

Патентная литература 1

Публикация Заявки на патент Японии, Tokukai, No. 2001-83943 А (дата публикации: 30 марта 2001 г.)

Патентная литература 2

Международная публикация No. WO 2009/050926 А1 (дата публикации: 23 апреля 2009 г.)

Сущность изобретения

Техническая проблема

Жидкокристаллическим устройствам отображения, использующим возбуждение с инверсией линии и возбуждение с зарядовой связью (СС), присуща проблема, заключающаяся в том, что в первом кадре после запуска устройства отображения появляются чередующиеся яркие и темные поперечные полосы в каждой отдельной строке (каждая отдельная строка горизонтальной развертки в жидкокристаллическом устройстве отображения).

На Фиг.22 представлены временные диаграммы, показывающие работу жидкокристаллического устройства отображения, для объяснения причин этой проблемы.

На Фиг.22 GSP обозначает сигнал стартового импульса затвора, устанавливающий синхронизацию вертикальной развертки, и GCK1 (CK) и GCK2 (CKB) представляют собой тактовые сигналы затвора, передаваемые от схемы управления для установления синхронизации работы регистра сдвига. Период от одного среза (нисходящего перепада уровней) импульса GSP-сигнала до следующего среза соответствует одному периоду вертикальной развертки (1V-период). Период от фронта (восходящего перепада уровней) импульса GCK1-сигнала до фронта импульса GCK2-сигнала и период от фронта импульса GCK2-сигнала до фронта импульса GCK1-сигнала соответствуют каждый одному периоду горизонтальной развертки (1H-период). Сигнал CMI (инверсия кодовых маркеров) представляет собой сигнал полярности, инвертирующий свою полярность в каждом отдельном периоде горизонтальной развертки.

Кроме того, на Фиг.22 показаны следующие сигналы в порядке их наименования: сигнал S истока (видеосигнал), поступающий от схемы возбуждения 111 истоковых линий в истоковую линию 101 (истоковая линия 101 проходит в x-м столбце); сигнал G1 затвора, поступающий от схемы возбуждения 112 затворных линий в затворную линию 102, выполненную в первой строке; сигнал CS1, поступающий от схемы возбуждения 113 линий CS-шин в CS-линию 105, выполненную в первой строке; и потенциал Vpixl пиксельного электрода, выполненного в первой строке и в х-м столбце. Аналогично, на Фиг.3 показаны следующие сигналы в порядке их наименования: сигнал G2 затвора, поступающий в затворную линию 102, выполненную во второй строке; сигнал CS2, поступающий в CS-линию 105, выполненную во второй строке, и потенциал Vpix2 пиксельного электрода, выполненного во второй строке и в x-м столбце. Более того, на Фиг 3 показаны следующие сигналы в порядке их наименования: сигнал G3 затвора, поступающий в затворную линию 102, выполненную в третьей строке; сигнал CS3, поступающий в CS-линию 105, выполненную в третьей строке; и потенциал Vpix3 пиксельного электрода, выполненного в третьей строке и в x-м столбце.

Следует отметить, что штриховые линии на графиках потенциалов Vpix1, Vpix2 и Vpix3 указывают потенциал контрэлектрода 109.

В дальнейшем предполагается, что стартовый кадр при представлении картинки на устройстве отображения является первым кадром и что этому первому кадру предшествует начальное состояние. В этом начальном состоянии схема возбуждения 111 истоковых линий, схема возбуждения 112 затворных линий и схема возбуждения 113 линий CS-шин находятся все в подготовительных фазах или в состоянии покоя перед переходом в нормальный режим работы. Поэтому сигналы G1, G2 и G3 затворов фиксируют на уровне потенциала запирания затвора (потенциал, при котором запирается затвор переключающего элемента 103), а CS-сигналы CS1, CS2 и CS3 фиксируют на одном потенциале (например, на низком уровне).

В первом кадре после начального состояния схема возбуждения 111 истоковых линий, схема возбуждения 112 затворных линий и схема возбуждения 113 линий CS-шин работают все в нормальном режиме. В этом случае амплитуда сигнала S истока соответствует уровню полутоновой шкалы, представленному видеосигналом, а сам сигнал S инвертирует свою полярность через каждый 1H-период.

Следует отметить, что, поскольку на Фиг.22 предполагается, что на экране устройства отображения представлена равномерная картинка, амплитуда сигнала S истока остается постоянной. Тем не менее сигналы G1, G2 и G3 затворов служат отпирающими потенциалами затворов (при которых происходит отпирание затворов переключающих элементов 103) во время первого, второго и третьего 1H-периодов соответственно, и служат запирающими потенциалами затворов во время остальных периодов.

Затем происходит инверсия CS-сигналов CS1, CS2 и CS3 после того, как произойдет переход соответствующих сигналов G1, G2 и G3 затворов на низкий уровень, причем формы этих CS-сигналов последовательно инвертированы одна относительно другой. В частности в кадре с нечетным номером CS-сигнал CS2 переходит на высокий уровень после того, как соответствующий сигнал G2 затвора перейдет на низкий уровень, а CS-сигналы CS1 и CS3 переходят на низкий уровень после того, как перейдут на низкий уровень соответствующие сигналы G1 и G3 затворов. Далее, в кадре с четным номером CS-сигнал CS2 переходит на низкий уровень после того, как перешел на низкий уровень соответствующий сигнал G2 затвора, а CS-сигналы CS1 и CS3 переходят на высокий уровень после того, как перейдут на низкий уровень соответствующие сигналы G1 и G3 затворов.

Следует отметить, что соотношение между фронтами и срезами CS-сигналов CS1, CS2 и CS3 в кадрах с нечетными номерами и четными номерами могут быть противоположны соотношениям, описанным выше. Более того, моменты инверсии CS-сигналов CS1, CS2 и CS3 могут совпадать со срезами сигналов G1, G2 и G3 затворов или наступать позже, т.е. в соответствующие периоды горизонтальной развертки или позже. Например, инверсия CS-сигналов CS1, CS2 и CS3 может происходить синхронно с фронтами сигналов затворов в следующей строке.

Однако, поскольку в первом кадре все CS-сигналы CS1, CS2 и CS3 фиксированы в начальном состоянии на одном потенциале (на Фиг.22 на низком уровне), потенциалы Vpix1 и Vpix3 имеют неопределенные состояния. В частности, CS-сигнал CS2 ведет себя так же, как и в других кадрах с нечетными номерами (третий, пятый кадры,…) в том, что он переходит на высокий уровень после того, как перешел на низкий уровень соответствующий сигнал G2 затвора, но CS-сигналы CS1 и CS3 ведут себя отлично от других кадров с нечетными номерами (третий, пятый кадры,…) в том, что они сохраняют тот же потенциал (на Фиг.22 низкий уровень) после того, как соответствующие сигналы G1 и G3 затворов перешли на низкий уровень.

По этой причине в первом кадре происходит изменение потенциала CS-сигнала CS2, как обычно, в пиксельных электродах 104 во второй строке. Поэтому, хотя происходит сдвиг потенциала Vpix2, обусловленный изменением CS-сигнала CS2, потенциал CS-сигналов CS1 и CS3 в пиксельных электродах 104 в первой и третьей строках не меняется. Соответственно, потенциалы Vpix1 и Vpix3 не подвержены сдвигу потенциала (как показывают заштрихованные области на Фиг.22). В результате, несмотря на ввод сигналов S истока, соответствующих одному и тому же уровню полутоновой шкалы, возникает разница в яркости между первой и третьей строками с одной стороны и второй строкой с другой стороны вследствие разности между потенциалами Vpix1 и Vpix3 с одной стороны и потенциалом Vpix2. Эта разница в яркости проявляется в виде разности в яркости между строками с нечетными номерами и строками с четными номерами в секции видеоустройства отображения в целом. В результате появляются чередующиеся яркие и темные поперечные полосы в каждой отдельной строке первого кадра.

Технология, позволяющая не допустить появления таких поперечных полос, описана в Патентной литературе 2. Технология, рассмотренная в Патентной литературе 2, описана ниже со ссылками на Фиг.24-26. Фиг.24 представляет блок-схему, показывающую конфигурацию схем возбуждения (схема возбуждения 30 затворных линий и схема возбуждения 40 линий CS-шин), показанных в Патентной литературе 2. Фиг.25 представляет временную диаграмму, показывающую форму различных сигналов в жидкокристаллическом устройстве отображения. Фиг.26 представляет временную диаграмму, показывающую форму различных сигналов на входе схемы возбуждения линий CS-шин и на выходе этой схемы возбуждения.

Как показано на Фиг.24, схема возбуждения 40 линий CS-шин содержит несколько логических схем 41, 42, 43,…, 4n, каждая из которых соответствует одной и только одной строке. Эти логические схемы 41, 42, 43,…, 4n включают D-защелки 41a, 42a, 43a,…, 4na и схемы «ИЛИ» (OR) 41b, 42b, 43b,…, 4nb, соответственно. В последующем в качестве примера будут использованы логические схемы 41 и 42, связанные с первой и второй строками соответственно.

Входными сигналами для логической схемы 41 являются сигналы G1 и G2 затворов, сигнал POL полярности и сигнал RESET сброса (начальной установки), а входными сигналами для логической схемы 42 являются сигналы G2 и G3 затворов, сигнал РОЕ полярности и сигнал RESET сброса. Сигнал РОЕ полярности и сигнал RESET сброса поступают от схемы управления (не показана).

Схема 41b ИЛИ (OR) получает сигнал G1 затвора из соответствующей затворной линии 12 и сигнал G2 затвора из затворной линии 12 следующей строки (второй строки) и в ответ передает на выход сигнал g1, показанный на Фиг.26. Далее, схема 42b ИЛИ (OR) получает сигнал G2 затвора из соответствующей затворной линии 12 и сигнал G3 затвора из затворной линии 12 следующей строки (третьей строки) и в ответ передает на выход сигнал g2, показанный на Фиг.26.

Указанная D-защелка 41a получает сигнал RESET сброса через свою клемму СЕ, получает сигнал РОЕ полярности через свою клемму D и получает выходной сигнал g1 от схемы 41b ИЛИ через свою клемму G. В соответствии с изменением уровня потенциала 7 сигнала g1 (от низкого уровня к высокому уровню или от высокого уровня к низкому уровню), который D-защелка 41 а принимает через свою клемму G, эта D-защелка 41 а передает на выход в качестве CS-сигнала CS1 входное состояние сигнала POL полярности, получаемого защелкой через ее клемму D, и при этом упомянутый CS-сигнал CS1 указывает изменение уровня потенциала. В частности, когда потенциал сигнала g1, который D-защелка 41 а принимает через свою клемму G, имеет высокий уровень, защелка 41 а передает на выход входное состояние (низкий уровень или высокий уровень) сигнала POL полярности, принятого ею через клемму D. Когда уровень потенциала сигнала g1, принятого защелкой 41 а через ее клемму G, изменился с высокого уровня на низкий уровень, эта защелка 41 а осуществляет защелкивание входного состояния (низкий уровень или высокий уровень) сигнала POL полярности, принятого ею через клемму D, в момент изменения уровня и сохраняет защелкнутое состояние до того момента, когда уровень потенциала сигнала g1, принимаемого защелкой 41 а через ее клемму G, снова поднимется до высокого уровня. Тогда D-защелка 41 а передает защелкнутое состояние на выход в виде показанного на Фиг.26 CS-сигнала CS1, означающего изменение уровня потенциала, через свою клемму Q.

Далее, аналогично, D-защелка 42а принимает сигнал RESET сброса через свою клемму CL, принимает сигнал POL полярности через свою клемму D и принимает от схемы 42b ИЛИ выходной сигнал g2 через свою клемму G. Это позволяет D-защелке 42а передать на выход показанный на Фиг.26 CS-сигнал CS2, означающий изменение уровня потенциала, через свою клемму Q.

Описанная выше конфигурация делает потенциалы CS-сигналов CS1 и CS2 отличными один от другого в момент времени, когда первый и второй сигналы затворов переходят на низкий уровень. Поэтому, как показано на Фиг.25, происходит сдвиг потенциала Vpix1, обусловленный сдвигом потенциала CS-сигнала CS1, а также происходит сдвиг потенциала Vpix2, обусловленный сдвигом потенциала CS-сигнала CS2. Это позволит исключить такие чередующиеся яркие и темные поперечные полосы в каждой отдельной строке, как показано на Фиг.22.

Однако технология, описанная в Патентной литературе 2, требует загрузки сигнала затвора из текущей строки и сигнала затвора из следующей строки для генерации CS-сигнала, показанного на Фиг.25, создавая тем самым проблему, связанную с увеличением площади схемы. Применительно к примеру, описанному выше, CS-сигнал CS2 генерируют в логической схеме 42 с использованием сигнала g2 затвора из затворной линии во второй строке и сигнала g3 затвора из затворной линии в третьей строке. Это делает необходимым создание проводника, по которому будет происходить загрузка сигнала затвора g3 из затворной линии в третьей строке, и схемы (схема ИЛИ), выполняющей логическую операцию над сигналами g2 и g3 затворов, что влечет за собой увеличение площади схемы. Такой схема возбуждения делает затруднительным создание панели жидкокристаллического устройства отображения с узким кадром.

Настоящее изобретение сделано в свете указанных выше проблем, а целью настоящего изобретения является создание схемы возбуждения устройства отображения и способа управления устройстве отображениям, которые сделают возможным без увеличения площади схемы повысить качество изображения на экране устройства отображения путем устранения проявления поперечных полос.

Решение проблемы

Схема возбуждения устройства отображения согласно настоящему изобретению представляет собой схему возбуждения устройства отображения для использования в устройстве отображения, в котором посредством подачи сигналов для проводников удерживающих конденсаторов в проводники удерживающих конденсаторов, образующие конденсаторы вместе с пиксельными электродами, входящими в состав пикселов, изменяют потенциалы сигналов, записанные в пиксельных электродах, в направлениях, соответствующих полярностям этих потенциалов сигналов, такая схема возбуждения устройства отображения включает регистр сдвига, имеющий несколько каскадов, каждый из которых соответствует одной и только одной из нескольких линий сигналов развертки, этот схема возбуждения устройства отображения включает удерживающие схемы, каждая из которых соответствует одному и только одному каскаду регистра сдвига, в каждую из удерживающих схем вводят сигнал цели удержания, когда сигнал управления, генерируемый текущим каскадом регистра сдвига, становится активным, удерживающая схема, соответствующая текущему каскаду, загружает и удерживает сигнал цели удержания, выходной сигнал от текущего каскада регистра сдвига поступает в качестве сигнала развертки в линию сигнала развертки, соединенную с пикселами, соответствующими текущему каскаду, выходной сигнал от удерживающей схемы, соответствующей текущему каскаду, поступает в качестве сигнала для проводника удерживающих конденсаторов в проводник удерживающих конденсаторов, образующий конденсаторы во взаимодействии с пиксельными электродами пикселов, соответствующих предыдущему каскаду, предшествующему текущему каскаду.

В типовой конструкции панели устройства отображения, управляемой схемой возбуждения устройства отображения, конфигурированной, как описано выше, большое число пиксельных электродов расположено в строках и в столбцах, так что шина сигнала развертки, переключающий элемент и проводник для удерживающих конденсаторов расположены вдоль каждой строки, а шина сигнала данных проходит вдоль каждого столбца. Хотя в такой типовой конструкции термины «строки» и «столбцы» или термины «горизонтальный» и «вертикальный» часто относятся к расположению вдоль поперечного и продольного направления, соответственно, панели устройства отображения, это совсем не обязательно должно быть именно так; горизонтальное и вертикальное направления можно поменять местами. Поэтому термины «строки» и «столбцы» или термины «горизонтальный» и «вертикальный» не определяют какого-либо конкретного направления.

Схема возбуждения устройства отображения, управляющаяй такой панелью устройства отображения, использует сигналы для проводников удерживающих конденсаторов, чтобы вызвать изменение потенциалов сигналов, записанных в пиксельных электродах, в направлении, соответствующем полярностям потенциалов сигналов, чем обеспечивается управление с зарядовой связью.

Здесь следует отметить, что форма сигнала для проводника удерживающих конденсаторов, как описано выше, инвертирует потенциал после перехода на низкий уровень (выключения) сигнала затвора n-й строки. Обычно такую форму сигнала для проводника накопительных конденсаторов получают с применением конфигурации, использующей сигнал затвора n-й строки и сигнал затвора (n+1)-й строки (см. Фиг.24). В такой конфигурации необходимо создать проводники, по которым загружают выходные сигналы регистра сдвига для n-й и (n+1)-й строк (сигналы затворов) и логическую схему (схему ИЛИ), увеличивая, таким образом, площадь схемы.

В этом отношении схема возбуждения устройства отображения конфигурирована таким образом, что сигнал для проводника удерживающих конденсаторов генерируют путем ввода сигнала управления (внутреннего сигнала или выходного сигнала), сформированного текущим каскадом регистра сдвига, в удерживающую схему текущего каскада, а сам сигнал для проводника удерживающих конденсаторов подают в проводник удерживающих конденсаторов предшествующего каскада. Это позволит исключить такие аномальные сигналы, которые вызывают появление поперечных полос в первом периоде вертикальной развертки. Далее, поскольку нет необходимости в создании отдельного элемента для генерации правильного сигнала для проводника удерживающих конденсаторов, можно уменьшить площадь схемы по сравнению с известной конфигурацией. Это позволяет реализовать малогабаритный жидкокристаллический устройство отображения и панель жидкокристаллического устройства отображения с узким кадром - и то, и другое с высоким качеством изображения.

Способ управления устройстве отображениям согласно настоящему изобретению представляет собой способ управления устройстве отображениям, содержащим регистр сдвига, включающий несколько каскадов, каждый из которых соответствует одной и только одной из нескольких линий сигналов развертки, и в котором путем подачи сигналов для проводников удерживающих конденсаторов в проводники удерживающих конденсаторов, образующие конденсаторы во взаимодействии с пиксельными электродами, входящими в состав пикселов, изменяют потенциалы сигналов, записанных в пиксельных электродах, в направлении, соответствующем полярностям этих потенциалов сигналов, рассматриваемый способ управления устройстве отображениям включает этапы: ввод сигнала цели удержания в удерживающие схемы, соответствующие каскадам регистра сдвига, и, когда сигнал управления, генерируемый текущим каскадом регистра сдвига, становится активным, загрузку сигнала цели удержания и сохранение этого сигнала в удерживающей схеме, соответствующей текущему каскаду; и передачу выходного сигнала от текущего каскада регистра сдвига в качестве сигнала развертки в линию сигнала развертки, соединенную с пикселами, соответствующими текущему каскаду, и передачу выходного сигнала удерживающей схемы, соответствующей текущему каскаду, в качестве сигнала для проводника удерживающих конденсаторов в проводник удерживающих конденсаторов, образующий конденсаторы с пиксельными электродами пикселов, соответствующих предыдущему каскаду, предшествующему текущему каскаду.

С точки зрения эффекта, указанного выше в связи со схемой возбуждения устройства отображения, предлагаемый способ позволяет без увеличения площади схемы повысить качество изображения на экране устройства отображения за счет исключения возможности появления поперечных полос в первом периоде вертикальной развертки.

Преимущества изобретения

Как описано выше, схема возбуждения устройства отображения и способ управления устройством отображениям согласно настоящему изобретению отличаются следующим: предусмотрены удерживающие схемы, так что каждому каскаду регистра сдвига соответствует одна и только одна удерживающая схема; в каждую из этих удерживающих схем вводят сигнал цели удержания; когда сигнал управления, генерируемый текущим каскадом регистра сдвига, становится активным, удерживающая схема, соответствующая этому текущему каскаду, загружает и удерживает сигнал цели удержания; выходной сигнал от текущего каскада регистра сдвига передают в качестве сигнала развертки в линию сигнала развертки, соединенную с пикселами, соответствующими этому текущему каскаду; и выходной сигнал удерживающей схемы, соответствующей текущему каскаду передают в качестве сигнала для проводника удерживающих конденсаторов в проводник удерживающих конденсаторов, образующий конденсаторы с пиксельными электродами пикселов, соответствующих предыдущему каскаду, предшествующему текущего каскаду.

Указанные конфигурация и способ могут позволить без увеличения площади схемы улучшить качество изображения на устройстве отображения за счет исключения проблемы появления чередующихся ярких и темных полос в каждой отдельной строке (отдельная линия) в первом периоде вертикальной развертки (первый кадр), в котором начинают передавать на выход сигнал данных, соответствующий изображению, подлежащему представлению на устройстве отображения.

Краткое описание чертежей

Фиг.1 представляет блок-схему, показывающую конфигурацию жидкокристаллического устройства отображения согласно одному из вариантов настоящего изобретения.

Фиг.2 представляет эквивалентную схему, показывающую электрическую конфигурацию каждого пиксела в жидкокристаллическом устройстве отображения, изображенном на Фиг.1.

Фиг.3 представляет временную диаграмму, показывающую формы различных сигналов в жидкокристаллическом устройстве отображения согласно Варианту 1.

Фиг.4 представляет блок-схему, показывающую конфигурацию схемы возбуждения затворных линий и схема возбуждения линий CS-шин согласно Варианту 1.

Фиг.5 показывает конфигурацию каскада регистра сдвига согласно Варианту 1.

Фиг.6 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах каскада регистра сдвига, изображенного на Фиг.5.

Фиг.7 показывает конфигурацию логической схемы (D-защелки) согласно Варианту 1.

Фиг.8 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах D-защелки, изображенной на Фиг.7.

Фиг.9 представляет временную диаграмму, показывающую форму различных сигналов, в жидкокристаллическом устройстве отображения согласно Варианту 2.

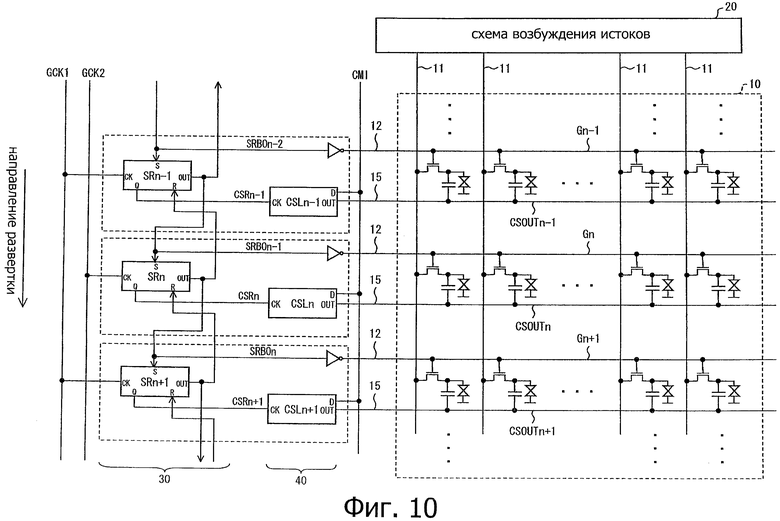

Фиг.10 представляет блок-схему, показывающую конфигурацию схемы возбуждения затворных линий и схемы возбуждения линий CS-шин согласно Варианту 2.

Фиг.11 показывает конфигурацию каскада регистра сдвига согласно Варианту 2.

Фиг.12 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах каскада регистра сдвига, изображенного на Фиг.11.

Фиг.13 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах D-защелки согласно Варианту 2.

Фиг.14 представляет временную диаграмму, показывающую форму различных сигналов, в жидкокристаллическом устройстве отображения согласно Варианту 3.

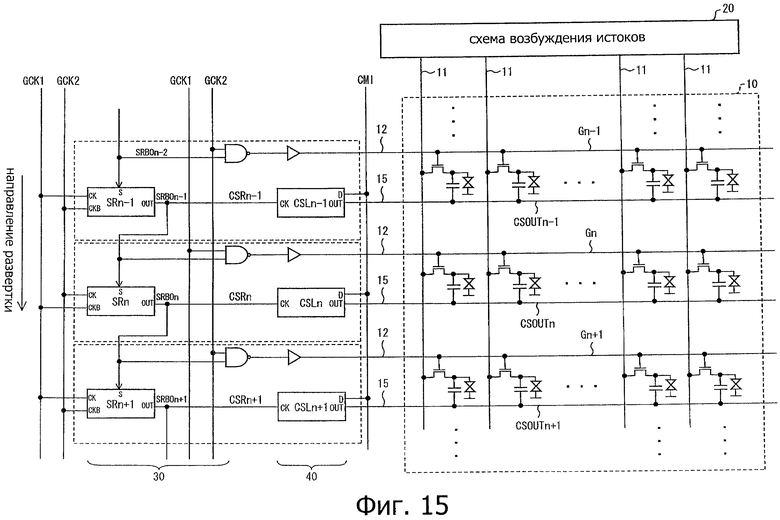

Фиг.15 представляет блок-схему, показывающую конфигурацию схемы возбуждения затворных линий и схемы возбуждения линий CS-шин согласно Варианту 3.

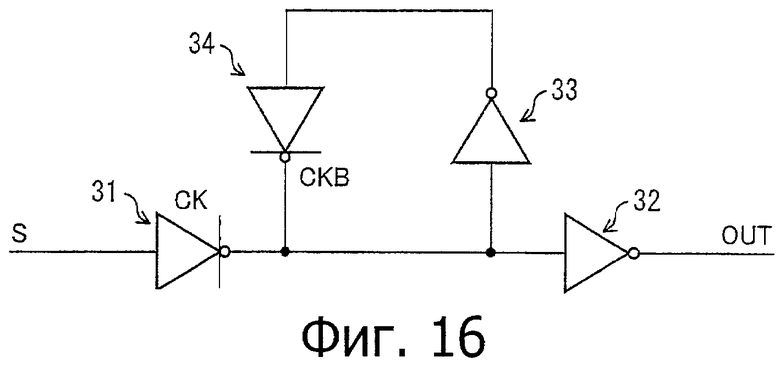

Фиг.16 показывает конфигурацию каскада регистра сдвига согласно Варианту 3.

Фиг.17 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах каскада регистра сдвига, изображенного на Фиг.16.

Фиг.18 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах D-защелки согласно Варианту 3.

Фиг.19 представляет блок-схему, показывающую другую конфигурацию схемы возбуждения затворных линий и схемы возбуждения линий CS-шин согласно Варианту 1.

Фиг.20 представляет блок-схему, показывающую конфигурацию известного жидкокристаллического устройства отображения, использующего схему возбуждения с зарядовой связью.

Фиг.21 представляет временную диаграмму, показывающую форму различных сигналов в известном жидкокристаллическом устройстве отображения.

Фиг.22 представляет временную диаграмму, показывающую сравнительные примеры форм различных сигналов в известном жидкокристаллическом устройстве отображения.

Фиг.23 представляет блок-схему, показывающую другую конфигурацию схемы возбуждения затворных линий и схемы возбуждения линий CS-шин в известном жидкокристаллическом устройстве отображения.

Фиг.24 представляют блок-схему, показывающую конфигурацию известных схем возбуждения (схема возбуждения затворных линий и схема возбуждения линий CS-шин).

Фиг.25 представляет временную диаграмму, показывающую форму различных сигналов, в жидкокристаллическом устройстве отображения, включая схемы возбуждения, изображенные на Фиг.24.

Фиг.26 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах схемы возбуждения линий CS-шин, изображенного на Фиг.24.

Фиг.27 представляет блок-схему, показывающую другую конфигурацию схемы возбуждения затворных линий и схемы возбуждения линий CS-шин согласно Варианту 1.

Фиг.28 представляет (а) схему, показывающую конфигурацию триггера согласно Варианту 1, (b) временную диаграмму, иллюстрирующую работу триггера (когда сигнал INITB не активен), и (с) таблицу истинности для триггера (когда сигнал INITB не активен).

Фиг.29 представляет временную диаграмму, показывающую форму различных сигналов, в жидкокристаллическом устройстве отображения согласно Варианту 4.

Фиг.30 представляет конфигурацию схемы возбуждения 30 затворных линий и схемы возбуждения 40 линий CS-шин согласно Варианту 4.

Фиг.31 представляет схему, показывающую другую конфигурацию удерживающей схемы в каждом каскаде схемы возбуждения линий CS-шин согласно рассматриваемому варианту.

Фиг.32 представляет временную диаграмму, показывающую работу удерживающей схемы, изображенной на Фиг.31.

Подробное описание вариантов

Один из вариантов настоящего изобретения описан ниже со ссылками на перечисленные выше чертежи.

Сначала конфигурация жидкокристаллического устройства отображения 1, соответствующего устройству отображения согласно настоящему изобретению, описана со ссылками на Фиг.1 и 2. Фиг.1 представляет блок-схему, показывающую общую конфигурацию жидкокристаллического устройства отображения 1, и Фиг.2 представляет эквивалентную схему, показывающую электрическую конфигурацию каждого пиксела в жидкокристаллическом устройстве отображения 1.

Жидкокристаллическое устройство отображения 1 включает: панель 10 жидкокристаллического устройства отображения с активной матрицей, соответствующую панели устройства отображения согласно настоящему изобретению; схема возбуждения 20 линий истоковых шин, соответствующий схеме возбуждения линий сигнала данных согласно настоящему изобретению; схема возбуждения 30 затворных линий, соответствующий схеме возбуждения линий сигнала развертки согласно настоящему изобретению; схема возбуждения 40 линий CS-шин, соответствующая схеме возбуждения проводников удерживающих конденсаторов согласно настоящему изобретению; и схему 50 управления, соответствующую схеме управления согласно настоящему изобретению.

Панель 10 жидкокристаллического устройства отображения, построенная путем вложения жидких кристаллов между подложкой с активной матрицей и контрподложкой (не показана), содержит большое число пикселов Р, расположенных по строкам и столбцам матрицы.

Более того, жидкокристаллическая панель 10 включает: линии 11 истоковых шин, которые соответствуют линиям сигналов данных согласно настоящему изобретению;

затворные линии 12, которые выполнены на подложке с активной матрицей и которые соответствуют линиям сигналов развертки согласно настоящему изобретению;

тонкопленочные транзисторы 13 (далее именуемые "TFT"), которые выполнены на подложке с активной матрицей и которые соответствуют переключающим элементам согласно настоящему изобретению; пиксельные электроды 14, которые выполнены на подложке с активной матрицей и которые соответствуют пиксельным электродам согласно настоящему изобретению; линии 15 CS-шин, которые выполнены на подложке с активной матрицей и которые соответствуют проводникам удерживающих конденсаторов согласно настоящему изобретению; и контрэлектрод 19, выполненный на контрподложке. Следует отметить, что каждый из транзисторов TFT 13, опущенных на Фиг.1, показан на Фиг.2 в единственном числе.

Линии 11 истоковых шин расположены одна за другой в столбцах параллельно одна другой в направлении столбцов (продольном направлении), а затворные линии 12 расположены одна за другой в строках параллельно одна другой в направлении строк (поперечном направлении). Каждый из транзисторов TFT 13 выполнен в соответствии с точкой пересечения между линией 11 истоковой шины и затворной линией 12, также как и пиксельные электроды 14. В каждом из транзисторов TFT 13 электрод «s» истока, соединен с линией 11 истоковой шины, электрод «g» затвора соединен с затворной линией 12, а электрод «d» стока соединен с пиксельным электродом 14. Далее, каждый из пиксельных электродов 14 образует жидкокристаллический конденсатор 17 с контрэлектродом 19, так что жидкие кристаллы вложены между этими пиксельным электродом 14 и контрэлектродом 19.

В такой конфигурации, когда сигнал затвора (сигнал развертки), поступающий в затворную линию 12, отпирает затвор транзистора TFT 13, а сигнал истока (сигнал данных) из линии 11 истоковой шины записывают в пиксельном электроде 14, этот пиксельный электрод 14 приобретает потенциал, соответствующий сигналу истока. В результате, этот потенциал, соответствующий сигналу истока, воздействует на жидкие кристаллы, вложенные между пиксельным электродом 14 и контрэлектродом 19. Это позволяет реализовать на устройстве отображения полутоновое изображение, соответствующее сигналу истока.

Линии 15 CS-шин расположены одна за другой в строках параллельно одна другой в направлении строк (поперечном направлении) таким образом, что эти линии CS-шин спарены с соответствующими затворными линиями 12. Каждая из линий 15 CS-шин образует удерживающий конденсатор 16 (именуемый также «вспомогательным конденсатором») с каждым из пиксельных электродов 14, расположенных в каждой строке, имея в результате емкостную связь с пиксельными электродами 14.

Следует отметить, что поскольку в силу самой своей конструкции транзистор TFT 13 содержит затягивающий конденсатор 18, образованный между электродом «g» затвора и электродом «d» стока, на потенциал пиксельного электрода 14 влияет (затягивает его) изменение потенциала затворной линии 12. Однако для упрощения пояснений этот эффект затягивания здесь учитываться не будет.

Конфигурированной таким образом панелью 10 жидкокристаллического устройства отображения управляют посредством схемы возбуждения 20 линий истоковых шин, схемы возбуждения 30 затворных линий и схемы возбуждения 40 линий CS-шин. Далее, схема 50 управления передает схеме возбуждения 20 линий истоковых шин, схеме возбуждения 30 затворных линий и схеме возбуждения 40 линий CS-шин различные сигналы, необходимые для управления панелью 10 жидкокристаллического устройства отображения.

В рассматриваемом варианте во время активного периода (эффективный период развертки) в составе периода вертикальной развертки, повторяемого периодически, каждой строке последовательно назначают период горизонтальной развертки и сканируют последовательно. С этой целью синхронно с периодом горизонтальной развертки схема возбуждения 30 затворных линий последовательно передает на выход сигнал затвора для отпирания транзисторов TFT 13 в затворную линию 12 этой строки. Сама такая схема возбуждения 30 затворных линий будет подробно описана позднее.

Схема возбуждения 20 линий истоковых шин передает сигнал истока в каждую линию 11 истоковых шин. Схема возбуждения 20 линий истоковых шин, принимающая видеосигнал извне жидкокристаллического устройства отображения 1 через схему 50 управления, получает этот сигнал истока, назначает видеосигнал каждому столбцу и усиливает этот видеосигнал или выполняет другую обработку видеосигнала.

Далее, например, для осуществления инверсного возбуждения n-линии (nH) схема возбуждения 20 линий истоковых шин конфигурирована таким образом, что полярность сигнала истока на выходе схемы возбуждения идентична для всех пикселов одной и той же строки и инвертируется через каждые «n» соседних строк. Например, как показано на Фиг.3, где представлено управление в режиме 1-строчной (1Н) инверсии, период горизонтальной развертки в первой строке и период горизонтальной развертки во второй строке отличаются один от другого по полярности сигнала S истока. Следует отметить, что хотя на Фиг.3 показан случай, когда полярность сигнала S истока инвертируется в каждом кадре (1-кадровая инверсия), это не накладывает каких-либо ограничений. Сигнал S истока может инвертировать полярность через каждые m-кадров (m-кадровая инверсия).

Схема возбуждения 40 линий CS-шин передает CS-сигнал, соответствующий сигналу для проводника удерживающих конденсаторов согласно настоящему изобретению, в каждую линию 15 CS-шин. Этот CS-сигнал представляют собой сигнал, потенциал которого переключается (повышается или снижается) между двумя величинами (высокий и низкий потенциалы) и которым управляют так, что потенциал этого сигнала в момент времени, когда транзисторы TFT 13 в соответствующей строке переключаются из открытого в запертое состояние (т.е. в момент времени, когда сигнал затвора переходит на низкий уровень), изменяется через каждые «n» соседних строк. Такая схема возбуждения 40 линий CS-шин будет подробно описан позже.

Схема 50 управления осуществляет управление схемой возбуждения 30 затворных линий, схемой возбуждения 20 линий истоковых шин и схемой возбуждения 40 линий CS-шин, так что каждая из этих схем возбуждения передает на свой выход сигналы, показанные на Фиг.3.

В рассматриваемом варианте внимание будет уделено характерным особенностям схемы возбуждения 30 затворных линий и схемы возбуждения 40 линий CS-шин среди компонентов, составляющих жидкокристаллический устройство отображения 1. В последующем схема возбуждения 30 затворных линий и схема возбуждения 40 линий CS-шин будут описаны подробно (Варианты 1-3).

(Вариант 1)

Фиг.3 представляет временную диаграмму, показывающую формы различных сигналов в жидкокристаллическом устройстве отображения согласно Варианту 1. В Варианте 1 осуществляется управление (возбуждение) с 1-строчной (1Н) инверсий, а сигнал S истока инвертирует свою полярность через каждый отдельный кадр (однокадровая инверсия). На Фиг.3, как и на Фиг.22, GSP обозначает сигнал стартового импульса затвора, устанавливающий синхронизацию вертикальной развертки, и GCK1 (CK) и GCK2 (CKB) представляют собой тактовые сигналы затвора, передаваемые от схемы 50 управления для установления синхронизации работы регистра сдвига. Период от одного среза импульса GSP-сигнала до следующего среза соответствует одному периоду вертикальной развертки (1V-период). Период от фронта импульса GCK1-сигнала до фронта импульса GCK2-сигнала и период от фронта импульса GCK2-сигнала до фронта импульса GCK1-сигнала соответствуют каждый одному периоду горизонтальной развертки (1H-период). Сигнал CMI (сигнал цели удержания) представляет собой сигнал полярности, инвертирующий свою полярность в каждом отдельном периоде горизонтальной развертки.

Кроме того, на Фиг.22 показаны следующие сигналы: сигнал S истока (видеосигнал), поступающий от схемы возбуждения 20 линий истоковых шин в линию 11 истоковой шины (линия 11 истоковой шины проходит в x-ом столбце); сигнал G1 затвора, поступающий от схемы возбуждения 30 затворных линий в затворную линию 12, выполненную в первой строке; CS-сигнал CS1 (CSOUT1), поступающий от схемы возбуждения 40 линий CS-шин в линию 15 CS-шины, выполненную в первой строке; и потенциал Vpix1 пиксельного электрода 14, выполненного в первой строке и в x-ом столбце. Далее, на Фиг.3 показаны следующие сигналы: сигнал G2 затвора, поступающий в затворную линию 12, выполненную во второй строке; CS-сигнал CS2 (CSOUT2), поступающий в линию 15 CS-шины, выполненную во второй строке, и потенциал Vpix2 пиксельного электрода 14, выполненного во второй строке и в x-ом столбце. Более того, на Фиг 3 показаны следующие сигналы: сигнал G3 затвора, поступающий в затворную линию 12, выполненную в третьей строке; CS-сигнал CS3 (CSOUT3), поступающий в линию 15 CS-шины, выполненную в третьей строке; и потенциал Vpix3 пиксельного электрода, выполненного в третьей строке и в x-ом столбце. Как будет описано позднее (со ссылками на Фиг.4), сигналы M1 (CSR1), М2 (CSR2) и М3 (CSR3), генерируемые каскадами SR1-SR3 регистров сдвига в строках с первой по третью, представляют собой сигналы, поступающие на входы логических схем (защелки, удерживающие схемы) CSL1-CSL3 в строках с первой по третью, соответственно.

Следует отметить, что штриховые линии на графиках потенциалов Vpix1, Vpix2 и Vpix3 указывают потенциал контрэлектрода 19.

В дальнейшем предполагается, что стартовый кадр при представлении картинки на устройстве отображения является первым кадром и что этому первому кадру предшествует начальное состояние. В Варианте 1, как показано на Фиг.3, во время начального состояния CS-сигналы CS1, CS2 и CS3 фиксируют все на одном потенциале (на Фиг.3, на низком уровне). В первом кадре CS-сигнал CS1 в первой строке и CS-сигнал CS3 в третьей строке переключаются с низкого уровня на высокий уровень синхронно с фронтами соответствующих сигналов G1 и G3 затворов, соответственно, и находятся на высоком уровне в моменты времени, соответствующие срезам этих сигналов G1 и G3 затворов. Поэтому, потенциал CS-сигнала в каждой строке в момент времени, когда имеет место срез соответствующего сигнала затвора, отличается от CS-сигнала в соседней строке в момент времени, когда имеет место срез соответствующего сигнала затвора. Например, CS-сигнал CS1 находится на высоком уровне в момент времени, когда имеет место срез соответствующего сигнала G1 затвора, CS-сигнал CS2 находится на низком уровне в момент времени, когда имеет место срез соответствующего сигнала G2 затвора, и CS-сигнал CS3 находится на высоком уровне в момент времени, когда имеет место срез соответствующего сигнала G3 затвора.

Следует отметить, что сигнал S истока представляет собой сигнал, амплитуда которого соответствует уровню полутоновой шкалы, представленному видеосигналом, а полярность инвертируется через каждый 1H-период. Далее, поскольку предполагается, что сигналы на Фиг.3 соответствуют представлению равномерной картинки на устройстве отображения, амплитуда сигнала S истока остается постоянной. Тем не менее сигналы G1, G2 и G3 затвора служат отпирающими потенциалами затворов во время первого, второго и третьего 1H-периодов, соответственно, в активном периоде (эффективный период развертки) каждого кадра и служат запирающими потенциалами затворов в другие периоды.

Затем происходит инверсия CS-сигналов CS1, CS2 и CS3 после того, как соответствующие сигналы G1, G2 и G3 затворов переходят на низкий уровень, так что формы этих CS-сигналов в соседних строках противоположны по направлению инверсии одна относительно другой. В частности, в кадре с нечетным номером (первый кадр, третий кадр…) CS-сигналы CS1 и CS3 переходят на низкий уровень после перехода соответствующих сигналов G1 и G3 на низкий уровень, а CS-сигнал CS2 переходит на высокий уровень после перехода соответствующего сигнала G2 затвора на низкий уровень. Далее, в кадре с четным номером (второй кадр, четвертый кадр…) CS-сигналы CS1 и CS3 переходят на высокий уровень после перехода на низкий уровень соответствующих сигналов G1 и G3 затворов, а CS-сигнал CS2 переходит на низкий уровень после перехода соответствующего сигнала G2 затвора на высокий уровень.

Следует отметить, что соотношение между фронтами и срезами CS-сигналов CS1, CS2 и CS3 в кадрах с нечетными номерами и в кадрах с четными номерами может быть противоположно соотношению, описанному выше.

Поскольку, как показано на Фиг.3, соседние строки отличаются одна от другой с точки зрения потенциалов CS-сигналов в моменты времени, когда происходит переход соответствующих сигналов затвора на низкий уровень в первом кадре, указанные CS-сигналы CS1, CS2 и CS3 в первом кадре имеют такую же форму, как и в обычном кадре с нечетным номером (например, в третьем кадре). Поэтому, поскольку потенциалы Vpix1, Vpix2 и Vpix3 пиксельных электродов 14 все сдвигаются должным образом посредством CS-сигналов CS1, CS2 и CS3, соответственно, подача на вход сигналов S истоков, соответствующих одному и тому же уровню полутоновой шкалы, приводит к тому, что положительные и отрицательные разности потенциалов между потенциалом контрэлектрода и сдвинутым потенциалом каждого из пиксельных электродов 14 оказываются равны одна другой. Иными словами, в первом кадре, в котором сигнал истока отрицательной полярности записывают в пикселах с нечетными номерами одного и того же столбца пикселов, а сигнал истока положительной полярности записывают в пикселы с четными номерами в указанном столбце пикселов, потенциалы CS-сигналов, соответствующих пикселам с нечетными номерами, не меняют полярности во время записи сигналов в пикселы с нечетными номерами, инвертируют полярность в отрицательном направлении после такой записи и сохраняют полярность до следующей записи, а потенциалы CS-сигналов, соответствующих пикселам с четными номерами, не меняют полярности во время записи в пикселы с четными номерами, инвертируют полярность в положительном направлении после такой записи и сохраняют полярность до следующей записи. Это приводит к исключению проявления поперечных полос в первом кадре, позволяя, таким образом, повысить качество изображения на экране устройства отображения.

Здесь описана конкретная конфигурация схемы возбуждения 30 затворных линий и схемы возбуждения 40 линий CS-шин для реализации описанного выше способа управления. На Фиг.4 показана конфигурация схемы возбуждения 30 затворных линий и схемы возбуждения 40 линий CS-шин. В последующем для удобства объяснения строка (линия) (следующая строка), которая следует за n-й строкой в направлении развертки (обозначено стрелкой на Фиг.4) будет обозначена как (n+1)-я строка, а строка (предыдущая строка), непосредственно предшествующая n-й строке в направлении развертки, будет обозначена как (n-1)-я строка.

Как показано на Фиг.4, схема возбуждения 30 затворных линий содержит несколько схем SR регистра сдвига (каскады регистра сдвига), каждая из которых соответствует своей строке, и схема возбуждения 40 линий CS-шин, имеющий несколько защелок (удерживающих схем) CSL, каждая из которых соответствует своей строке. Для удобства объяснения здесь в качестве примера взяты каскады SRn-1, SRn и SRn+1 регистра сдвига и защелки CSLn-1, CSLn и CSLn+1, которые соответствуют

(n-1)-й, n-й и (n+1)-й строкам.

Каскад SRn-1 регистра сдвига в (n-1)-й строке получает тактовый сигнал GCK1 затвора через свою тактовую клемму СК от схемы 50 управления (см. Фиг.1) и получает выходной сигнал SRBOn-2 регистра сдвига из предшествующей строки ((n-2)-я строка) через клемму SB установки в качестве сигнала установки для каскада SRn-1 регистра сдвига. Выходная клемма OUTB каскада SRn-1 регистра сдвига соединена с клеммой SB установки каскада SRn регистра сдвига следующей строки (n-я строка). Это позволяет каскаду SRn-1 регистра сдвига передать выходной сигнал SRBOn-1 регистра сдвига через свою выходную клемму OUTB в каскад SRn регистра сдвига. Выходная клемма M каскада SRn-1 регистра сдвига соединена с тактовой клеммой CK защелки CSLn-1 в текущей строке ((n-1)-я строка) для передачи сигнала M, генерируемого в каскаде SRn-1 регистра сдвига, на выход. Это позволяет каскаду SRn-1 регистра сдвига передать свой внутренний сигнал Mn-1 (сигнал CSRn-1) (сигнал управления) в защелку CSLn-1.

Далее, выходной сигнал SRBOn-2 регистра сдвига из предшествующей строки ((n-2)-я строка) подают на вход каскада SRn-1 регистра сдвига, а также передают на выход в качестве сигнала Gn-1 затвора (SROn-2: инвертированная версия сигнала SRBOn-2) в затворную линию 12 текущей строки ((n-1)-я строка) через буфер. Кроме того, каскад SRn-1 регистра сдвига получает напряжение питания (VDD).

Защелка CSLn-1 в (n-1)-й строке, построенная в виде D-защелки, принимает сигнал CMI полярности от схемы 50 управления (см. Фиг.1) и внутренний сигнал Mn-1 (сигнал CSRn-1) от каскада SRn-1 регистра сдвига. Одна выходная клемма OUT защелки CSLn-1 соединена с линией 15 CS-шины в текущей строке ((n-1)-я строка). Это позволяет защелке CSLn-1 передать на выход CS-сигнал CSOUTn-1 через ее выходную клемму OUT в линию 15 CS-шины в текущей строке ((n-1)-я строка).

Каскад SRn регистра сдвига в n-ой строке принимает тактовый сигнал GCK2 затвора через свою тактовую клемму CK от схемы 50 управления (см. Фиг.1) и принимает выходной сигнал SRBOn-1 регистра сдвига из предшествующей строки (n-1)-я строка) через свою клемму SB установки в качестве сигнала установки для каскада SRn регистра сдвига. Выходная клемма OUTB этого каскада SRn регистра сдвига соединена с клеммой SB установки каскада SRn+1 регистра сдвига следующей строки ((n+1)-я строка). Это позволяет каскаду SRn регистра сдвига передать выходной сигнал SRBOn регистра сдвига через свою выходную клемму OUTB в каскад SRn+1 регистра сдвига. Выходная клемма М каскада SRn регистра сдвига соединена с тактовой клеммой CK защелки CSLn в текущей строке (n-я строка). Это позволяет каскаду SRn регистра сдвига передать свой внутренний сигнал Mn (сигнал CSRn) на вход защелки CSLn.

Далее, выходной сигнал SRBOn-1 регистра сдвига из предшествующей строки ((n-1)-я строка) передают на вход каскада SRn регистра сдвига и передают на выход в качестве сигнала Gn затвора (SROn-1: инвертированная версия сигнала SRBOn-1) в затворную линию 12 текущей строки (n-ая строка) через буфер. Кроме того, каскад SRn регистра сдвига получает напряжение питания (VDD).

Защелка CSLn в n-й строке, построенная в виде D-защелки, принимает сигнал CMI полярности от схемы 50 управления (см. Фиг.1) и внутренний сигнал Mn (сигнал CSRn), генерируемый внутри каскада SRn регистра сдвига. Выходная клемма OUT защелки CSLn соединена с линией 15 CS-шины в текущей строке (n-я строка). Это позволяет защелке CSLn передавать на выход CS-сигнал CSOUTn через ее выходную клемму OUT в линию 15 CS-шины текущей строки.

Каскад SRn+1 регистра сдвига в (n+1)-й строке принимает тактовый сигнал GCK1 затвора через свою тактовую клемму СК от схемы 50 управления (см. Фиг.1) и принимает выходной сигнал SRBOn регистра сдвига от предшествующей строки (n-я строка) через свою клемму SB установки в качестве сигнала установки для каскада SRn+1 регистра сдвига. Выходная клемма OUTB каскада SRn+1 регистра сдвига соединена с клеммой SB установки каскада SRn+2 регистра сдвига в следующей строке ((n+2)-я строка). Это позволяет каскаду SRn+1 регистра сдвига передавать выходной сигнал SRBOn+1 регистра сдвига на выход через его выходную клемму OUTB в каскад SRn+2 регистра сдвига. Выходная клемма М каскада SRn+1 регистра сдвига соединена с тактовой клеммой CK защелки CSLn+1 в текущей строке ((n+1)-я строка). Это позволяет каскаду SRn+1 регистра сдвига передавать свой внутренний сигнал Mn+1 (сигнал С SRn+1) на вход защелки CSLn+1.

Далее, выходной сигнал SRBOn регистра сдвига из предшествующей строки (n-ая строка) передают на вход каскада SRn+1 регистра сдвига и передают на выход в качестве сигнала Gn+1 затвора (SR0n: инвертированная версия сигнала SRBOn) в затворную линию 12 текущей строки ((n+1)-я строка) через буфер. Кроме того, каскад SRn+1 регистра сдвига получает напряжение питания (VDD).

Защелка CSLn+1 в (n+1)-й строке, построенная в виде D-защелки, принимает сигнал CMI полярности от схемы 50 управления (см. Фиг.1) и внутренний сигнал Mn+1 (сигнал CSRn+1), генерируемый внутри каскада SRn+1 регистра сдвига. Выходная клемма OUT защелки CSLn+1 соединена с линией 15 CS-шины текущей строки ((n+1)-я строка). Это позволяет защелке CSLn+1 передавать на выход CS-сигнал CSOUTn+1 через свою выходную клемму OUT в линию 15 CS-шины текущей строки.

Далее дано объяснение принципа работы каждого каскада SR регистра сдвига. На Фиг.5 подробно показаны схемы каскадов SRn-1, SRn и SR+1 регистра сдвига в (n-1)-й, n-й и (n+1)-й строках. Следует отметить, что каскад SR регистра сдвига в каждой строке идентичен по конфигурации каскадам SRn-1, SRn и SR+1 регистра сдвига. Последующее пояснение сосредоточено на каскаде SRn регистра сдвига в n-ой строке.

Как показано на Фиг.5, каскад SRn регистра сдвига включает RS-триггер RS-FF, схему И-НЕ (NAND) и аналоговые переключающие схемы SW1 и SW2. Триггер RS-FF принимает выходной сигнал SRBOn-1 регистра сдвига (OUTB) через свою клемму SB установки из предыдущей строки ((n-1)-ая строка) в качестве сигнала установки, как описано выше. Первая входная клемма схемы И-НЕ соединена с выходной клеммой QB триггера RS-FF, а вторая входная клемма этой схемы соединена с выходной клеммой OUTB каскада SRn регистра сдвига. Выходная клемма М схемы И-НЕ соединена с управляющими электродами аналоговых переключающих схем SW1 и SW2 и соединена с тактовой клеммой CK (см. Фиг.4) защелки CSLn текущей строки (n-ая строка). Указанные аналоговые переключающие схемы SW1 и SW2 принимают от схемы И-НЕ внутренний сигнал Mn (который соответствует сигналу CSRn), управляющий каждой из аналоговых переключающих схем SW1 и SW2 для переключения их между открытым (ON) и запертым (OFF) состояниями. Аналоговая переключающая схема SW1 имеет первый электропроводный электрод, на который поступает тактовый сигнал СКВ (GCK2) затвора, и второй электропроводный электрод, соединенный с первым электропроводным электродом аналоговой переключающей схемы SW2, и аналоговая переключающая схема SW2 имеет второй электропроводный электрод, на который поступает напряжение питания (VDD). Аналоговые переключающие схемы SW1 и SW2 соединены одна с другой в точке «n», соединенной с выходной клеммой OUTB каскада SRn регистра сдвига, первой входной клеммой схемы И-НЕ и клеммой RB сброса триггера RS-FF в текущей строке (n-ой строке). Выходная клемма OUTB каскада SRn регистра сдвига соединена с клеммой SB установки следующей строки ((n+1)-ая строка). Это позволяет передавать выходной сигнал SRBOn (OUTB) регистра сдвига для текущей строки (n-ая строка) на выход и подавать в качестве сигнала установки в каскад SRn+1 регистра сдвига следующей строки ((n+1)-ая строка).

В описанной выше конфигурации выходной сигнал OUTB каскада SRn регистра сдвига подают в качестве сигнала сброса на клемму RB сброса триггера of RS-FF; вследствие этого каскад SRn регистра сдвига функционирует в качестве самосбрасываемого триггера. Конкретно работа такого каскада SRn регистра сдвига описана ниже.

Фиг.6 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах каскада SRn регистра сдвига.

Сначала, когда сигнал SB установки (SRBOn-1), поступающий на вход каскада SRn регистра сдвига, изменяется и переходит с высокого уровня на низкий уровень (становится активным), выходной сигнал QB триггера RS-FF изменяется и переходит с высокого уровня на низкий уровень, а внутренний сигнал Mn, представляющий собой выходной сигнал схемы И-НЕ, изменяется и переходит с низкого уровня на высокий уровень (t1). Когда внутренний сигнал Mn увеличивается до высокого уровня, аналоговая переключающая схема SW1 отпирается, вследствие чего тактовый сигнал CKB проходит на выход OUTB. Это приводит к увеличению выходного сигнала OUTB до высокого уровня. В период времени, когда на входы схемы И-НЕ подают выходной сигнал QB, находящийся на низком уровне, и выходной сигнал OUTB, находящийся на высоком уровне, (с t1 по t2), схема И-НЕ передает на свой выход внутренний сигнал Mn, имеющий высокий уровень, вследствие чего выходной сигнал OUTB возрастает до высокого уровня. В момент, когда сигнал SB установки увеличился до высокого уровня (t2), тактовый сигнал CKB по-прежнему остается на высоком уровне. Поэтому сброс триггера RS-FF не происходит, вследствие чего выходной сигнал QB остается на низком уровне, а внутренний сигнал Mn и выходной сигнал OUTB остаются на высоком уровне (с t2 по t3).

Затем, когда тактовый сигнал CKB уменьшился до низкого уровня (t3), выходной сигнал OUTB тоже падает до низкого уровня и происходит сброс триггера RS-FF в начальное состояние, вследствие чего выходной сигнал QB переходит с низкого уровня на высокий уровень. Поскольку на входы схемы И-НЕ поступают выходной сигнал QB, имеющий высокий уровень, и выходной сигнал OUTB, имеющий низкий уровень, внутренний сигнал Mn остается на высоком уровне, а выходной сигнал OUTB остается на низком уровне (с t3 по t4). Когда тактовый сигнал СКВ изменяется и переходит с низкого уровня на высокий уровень (t4), выходной сигнал OUTB возрастает до высокого уровня, а выходной сигнал QB, находящийся на высоком уровне, и выходной сигнал OUTB, находящийся на высоком уровне, поступают на входы схемы И-НЕ, так что внутренний сигнал Mn изменяется и переходит с высокого уровня на низкий уровень.

Сформированный таким способом выходной сигнал OUTB позволяет каскаду SRn+1 регистра сдвига в следующей строке ((n+1)-я строка) начать работу, а каскаду SRn регистра сдвига в текущей строке (n-я строка) выполнить операцию сброса.

Следует отметить, что внутренний Mn, сформированный внутри каскада SRn регистра сдвига, становится активным в период времени между моментом времени, когда становится активным сигнал SB установки, и моментом времени, когда становится активным сигнал RB (СКВ) сброса. Более того, внутренний сигнал Mn поступает на тактовую клемму CK защелки CSLn в текущей строке (n-я строка) (сигнал CSRn на Фиг.4).

В последующем будет описана работа каждой защелки CSL. На Фиг.7 подробно показана защелка CSLn в n-ой строке. Следует отметить, что защелка CSL в каждой строке идентична по конфигурации защелке CSLn. Последующее пояснение относится к защелке CSL в каждой строке как к D-защелке CSLn.

Указанная D-защелка CSLn принимает внутренний сигнал Mn (сигнал CSRn) через свою тактовую клемму CK от каскада SRn регистра сдвига, как описано выше. Рассматриваемая D-защелка CSLn принимает сигнал CMI полярности через свою входную клемму D от схемы 50 управления (см. Фиг.1). Это позволяет D-защелке CSLn передать на выход входное состояние сигнала CMI в качестве CS-сигнала CSOUTn в соответствии с изменением уровня потенциала внутреннего сигнала Mn (с низкого уровня на высокий уровень или с высокого уровня на низкий уровень), а CS-сигнал CSOUTn указывает на изменение уровня потенциала. В частности, когда потенциал внутреннего сигнала Mn, принимаемого D-защелкой CSLn через ее тактовую клемму CK, находится на высоком уровне, эта D-защелка CSLn передает на выход входное состояние (низкий уровень или высокий уровень) сигнала CMI полярности, который эта защелка принимает через свою входную клемму D. Когда потенциал внутреннего сигнала Mn, принимаемого D-защелкой CSLn через ее тактовую клемму CK, изменяется с высокого уровня на низкий уровень, D-защелка CSLn осуществляет защелкивание входного состояния (низкий уровень или высокий уровень) сигнала CMI полярности, принимаемого защелкой через ее входную клемму D в момент изменения, и сохраняет защелкнутое состояние до следующего момента, когда произойдет повышение уровня потенциала внутреннего сигнала Mn, принимаемого D-защелкой CSLn через ее тактовую клемму CK, до высокого уровня. Затем D-защелка CSLn передает на выход защелкнутое состояние CS-сигнала CSOUTn, указывающее факт изменения уровня потенциала, через свою выходную клемму.

Фиг.8 представляет временную диаграмму, показывающую форму различных сигналов на входах и выходах D-защелки CSLn. Фиг.8 показывает, например, временную диаграмму сигналов в D-защелке CSL1 в первой строке и сигналов в D-защелке CSL2 во второй строке.

Сначала будут описаны изменения формы различных сигналов в первой строке. В начальном состоянии D-защелка CSL1 принимает сигнал RESET сброса через свою клемму CL (см. Фиг.7). В ответ на сигнал RESET сброса потенциал CS-сигнала CS1, передаваемого D-защелкой CSL1 на выход через ее выходную клемму OUT, остается на низком уровне.

Когда в первом кадре схема возбуждения 30 затворных линий передает сигнал G1 затвора (который соответствует выходному сигналу SR0O каскада SR0 регистра сдвига) в затворную линию 12 первой строки, D-защелка CSL1 принимает через свою тактовую клемму СК внутренний сигнал Ml (сигнал CSR1), генерируемый каскадом SR1 регистра сдвига. После получения изменения уровня потенциала внутреннего сигнала Ml (с низкого уровня на высокий уровень; t11), D-защелка CSL1 передает входное состояние сигнала CMI полярности, принимаемого защелкой через ее входную клемму D в соответствующий момент времени, т.е. переходит на высокий уровень, и передает на выход это изменение потенциала сигнала CMI полярности до следующего момента, когда происходит изменение потенциала внутреннего сигнала M1 (с высокого уровня на низкий уровень; t13), который D-защелка CSL1 принимает через свою тактовую клемму CK (т.е., в период времени, в котором внутренний сигнал M1 находится на высоком уровне; с t11 по t13). Когда сигнал CMI полярности изменяется и переходит с высокого уровня на низкий уровень в период времени, в котором внутренний сигнал M1 находится на высоком уровне (t12), D-защелка CSL1 переключает свой выходной сигнал CS1 с высокого уровня на низкий уровень. Далее, после приема изменения потенциала внутреннего сигнала M1 (с высокого уровня на низкий уровень; t13) через свою тактовую клемму CK, рассматриваемая D-защелка CSL1 осуществляет защелкивание входного состояния сигнала CMI полярности, принимаемого в соответствующий момент времени, т.е. защелкивает низкий уровень. После этого D-защелка CSL1 сохраняет свой выходной сигнал CS1 на низком уровне до тех пор, пока не произойдет изменение уровня потенциала внутреннего сигнала M1 во втором кадре (с низкого уровня на высокий уровень; t14).

Когда во втором кадре схема возбуждения 30 затворных линий аналогично передает сигнал G1 затвора в затворную линию 12 в первой строке, D-защелка CSL1 принимает через свою тактовую клемму СК внутренний сигнал M1 (сигнал CSR1), генерируемый каскадом SR1 регистра сдвига. Когда внутренний сигнал M1 изменяется и переходит с низкого уровня на высокий уровень (t14), D-защелка CSL1 передает входное состояние сигнала CMI полярности, принимаемого ею через свою входную клемму в соответствующий момент времени, т.е. переходит на низкий уровень. Эта D-защелка CSL1 передает на выход изменение потенциала сигнала CMI полярности в период времени, в котором внутренний сигнал M1 находится на высоком уровне (с t14 по t16). Поэтому, когда сигнал CMI полярности изменяется и переходит с низкого уровня на высокий уровень (t15), рассматриваемая D-защелка CSL1 переключает свой выходной сигнал CS1 с низкого уровня на высокий уровень. Далее, после приема изменения потенциала внутреннего сигнала M1 (с высокого уровня на низкий уровень; t16) через свою тактовую клемму CK указанная D-защелка CSL1 осуществляет защелкивание входного состояния сигнала CMI полярности, принятого в соответствующий момент времени, т.е. защелкивается на высоком уровне. После этого, D-защелка CSL1 сохраняет свой выходной сигнал CS1 на высоком уровне до тех пор, пока не произойдет изменение потенциала внутреннего сигнала M1 в третьем кадре.

Сформированный таким образом CS-сигнал CS1 передают в линию 15 CS-шины в первой строке. Следует отметить, что выходной сигнал в третьем кадре имеет форму, полученную путем инверсии уровня потенциала выходного сигнала во втором кадре, а затем в четвертом кадре и позднее передают на выход сигналы, идентичные по форме поочередно сигналам второго кадра и третьего кадра.

Далее, будут описаны изменения формы различных сигналов во второй строке.

В первоначальном состоянии D-защелка CSL2 принимает сигнал RESET сброса через свою клемму CL (см. Фиг.7). Благодаря этому сигналу RESET сброса потенциал CS-сигнала CS2, который защелка CSL2 передает на выход через свою выходную клемму OUT, остается на низком уровне.

Когда в первом кадре схема возбуждения 30 затворных линий передает сигнал G2 затвора (который соответствует выходному сигналу SR01 от каскада SR1 регистра сдвига) в затворную линию 12 второй строки, D-защелка CSL2 принимает через свою тактовую клемму CK внутренний сигнал М2 (сигнал CSR2), генерируемый каскадом SR2 регистра сдвига. После получения изменения потенциала внутреннего сигнала М2 (с низкого уровня на высокий уровень; t21) указанная D-защелка CSL2 передает входное состояние сигнала CMI полярности, принятого ею через свою входную клемму D в соответствующий момент времени, т.е. передает низкий уровень, и передает на выход изменение потенциала сигнала CMI полярности до тех пор, пока не произойдет следующее изменение потенциала внутреннего сигнала М2 (с высокого уровня на низкий уровень; t23), которое эта D-защелка CSL2 принимает через свою тактовую клемму CK (т.е., в период времени, когда внутренний сигнал М2 остается на высоком уровне; с t21 по t23). Когда сигнал CMI полярности изменяется и переходит с низкого уровня на высокий уровень в пределах периода времени, когда внутренний сигнал М2 находится на высоком уровне (t22), рассматриваемая D-защелка CSL2 переключает свой выходной сигнал CS2 с низкого уровня на высокий уровень. Далее, после приема изменения потенциала внутреннего сигнала М2 (с высокого уровня на низкий уровень; t23) через свою тактовую клемму CK, эта D-защелка CSL2 осуществляет защелкивание входного состояния сигнала CMI полярности, принимаемого в соответствующий момент времени, т.е. защелкивается на высоком уровне. После этого, D-защелка CSL2 сохраняет свой выходной сигнал CS2 на высоком уровне, пока не произойдет изменение потенциала внутреннего сигнала М2 во втором кадре (с низкого уровня на высокий уровень; t24).

Когда во втором кадре схема возбуждения 30 затворных линий аналогично передает сигнал G2 затвора в затворную линию 12 второй строки, D-защелка CSL2 принимает через свою тактовую клемму СК внутренний сигнал М2 (сигнал CSR2), генерируемый каскадом SR2 регистра сдвига. Когда внутренний сигнал М2 изменяется и переходит с низкого уровня на высокий уровень (t24), D-защелка CSL2 передает входное состояние сигнала CMI полярности, принятое ею через свою входную клемму D в соответствующий момент времени, т.е. передает высокий уровень. Рассматриваемая D-защелка CSL2 передает на выход изменение потенциала сигнала CMI полярности в период времени, когда внутренний сигнал М2 имеет высокий уровень (с t24 по t26). Поэтому, когда сигнал CMI полярности изменяется и переходит с высокого уровня на низкий уровень (t25), указанная D-защелка CSL2 переключает свой выходной сигнал CS2 с высокого уровня на низкий уровень. Далее, после приема изменения потенциала внутреннего сигнала М2 (с высокого уровня на низкий уровень; t26) через свою тактовую клемму СК эта D-защелка CSL2 осуществляет защелкивание входного состояния сигнала CMI полярности, принимаемого в соответствующий момент времени, т.е. защелкивает низкий уровень. После этого, D-защелка CSL2 сохраняет свой выходной сигнал CS2 на низком уровне до тех пор, пока не произойдет изменение потенциала внутреннего сигнала М2 в третьем кадре.

Сформированный таким способом CS-сигнал CS2 передают в линию 15 CS-шины второй строки. Следует отметить, что в третьем кадре и позже передают на выход сигналы, форма которых соответствует поочередно сигналам первого и второго кадров.

Более того, операции в первой и второй строках соответствуют операциям D-защелки в каждой строке с нечетным номером и в каждой строке с четным номером.

Таким образом, D-защелки CSL1, CSL2, CSL3,…, каждая из которых соответствует своей и только своей строке, передают на выход CS-сигналы, так что во всех кадрах, включая первый кадр, потенциалы CS-сигналов в моменты времени, когда сигналы затворов в соответствующих строках снижаются (переходят на низкий уровень) (в моменты времени, когда транзисторы TFT 13 переключаются из открытого состояния в запертое состояния) отличаются при переходе от одной строки к соседней строке. Это делает возможным для схемы возбуждения 40 линий CS-шин правильно работать также и в первом кадре. Это позволяет исключить сигналы аномальной формы, вызывающие появление поперечных полос в первом кадре, и тем самым повысить качество изображения на экране устройства отображения за счет предотвращения появления поперечных полос в первом кадре.

Далее, этот эффект реализован без увеличения площади схемы по сравнению с известным жидкокристаллическим устройстве отображениям. Фиг.23 представляет блок-схему, показывающую пример конфигурации схемы возбуждения затворных линий и схемы возбуждения линий CS-шин в известном жидкокристаллическом устройстве отображения с целью реализации управления согласно Фиг.22. Как показано на Фиг.23 защелка в n-й строке (D-защелка CSLn) принимает выходной сигнал SRBOn+1 от каскада SRn+1 регистра сдвига в следующей строке ((n+1)-я строка). В результате этого CS-сигнал CSn в n-й строке изменяет свой потенциал синхронно с фронтом сигнала Gn+1 затвора в (n+1)-й строке (см. Фиг.22). В этой конфигурации необходимо загрузить выходной сигнал SRBOn+1 регистра сдвига из следующей строки ((n+1)-я строка) в защелку CSLn в текущей строке (n-я строка). Это ведет к увеличению площади схема из-за дополнительных проводников и т.п.

Далее, как показано на Фиг.24, известный схема возбуждения устройства отображения, который способен исключить появление таких поперечных полос, нуждается в проводниках, по которым загружают сигнал g2 затвора из текущей строки (n-я строка) и сигнал g3 затвора из следующей строки ((n+1)-я строка), и в схеме (схема ИЛИ), выполняющей логическую функцию над сигналами g2 и g3 затворов, что также увеличивает площадь схемы.

В этом отношении, в конфигурации согласно Варианту 1 сигнал (внутренний сигнал М), генерируемый внутри каскада SRn регистра сдвига, вводят непосредственно в защелку CSLn той же самой строки (n-й строки), в результате чего происходит генерация правильного CS-сигнала CSn, позволяющего исключить появление поперечных полос. Поэтому, по сравнению с известными схемами возбуждения устройства отображения (затворная схема возбуждения, CS-схема возбуждения), появляется возможность обойтись без проводника, проходящего от каскада регистра сдвига следующей строки, равно как нет необходимости создавать отдельный элемент для генерации правильного CS-сигнала CSn. Это позволяет схему возбуждения устройства отображения, способную исключить появление рассматриваемых поперечных полос, сделать меньше по площади по сравнению с известной конфигурацией, и тем самым дает возможность реализовать малогабаритное жидкокристаллическое устройство отображения с высоким качеством изображения и панель жидкокристаллического устройства отображения с узким кадром.

На Фиг.4 выходной сигнал SRBOn-1 от каскада SRn-1 регистра сдвига в (n-1)-й строке соответствует сигналу Gn затвора для n-й строки и поступает в затворную линию n-й строки, а внутренний сигнал Mn (CSRn) от каскада SRn регистра сдвига в n-й строке поступает на вход защелки CSLn в n-й строке, и CS-сигнал CSOUTn поступает в линию CS-шины n-й строки. Однако возможна также конфигурация, показанная на Фиг.27. На Фиг.27 выходной сигнал SRBOn от каскада SRn регистра сдвига в n-ой строке соответствует сигналу Gn затвора в n-й строке и поступает в затворную линию n-й строки, а внутренний сигнал Мn+1 (CSRn+1) от каскада SRn+1 регистра сдвига в (n+1)-й строке поступает на вход защелки CSLn в n-й строке и CS-сигнал CSOUTn поступает в линию CS-шины n-й строки.

Здесь будет подробно описан триггер согласно Варианту 1. Фиг.28 (а) представляет собой схему, показывающую конфигурацию триггера согласно Варианту 1. Как показано на Фиг.28 (а) триггер (FF201) включает: p-канальный транзистор р6 и n-канальный транзистор п5, составляющие КМОП-схему; p-канальный транзистор р8 и n-канальный транзистор n7, составляющие КМОП-схему; p-канальные транзисторы р5 и р7; n-канальные транзисторы n6 и n8; клемму SB; клемму RB; клемму INITB; и клеммы Q и QB. Триггер (FF201) конфигурирован таким образом, что затвор транзистора р6, затвор транзистора n5, сток транзистора р7, сток транзистора р8, сток транзистора n7 и клемма QB соединены одно с другими; сток транзистора р6, сток транзистора n5, сток транзистора р5, затвор транзистора р8, затвор транзистора n7 и клемма Q соединены одно с другими; исток транзистора n5 и сток транзистора n6 соединены один с другим; исток транзистора n7 и сток транзистора n8 соединены один с другим; клемма SB соединена с затвором транзистора р5 и затвором транзистора n6; клемма RB соединена с истоком транзистора р5, с затвором транзистора р7 и с затвором транзистора n8; клемма INITB соединена с истоком транзистора р6; истоки транзисторов р7 и р8 соединены с клеммой напряжения питания VDD и истоки транзисторов n6 и n8 соединены с клеммой VSS. Здесь следует отметить, что транзисторы р6, n5, р8 и n7 составляют защелку LC, транзистор р5 служит транзистором ST установки, транзистор р7 служит транзистором RT сброса и каждый из транзисторов n6 и n8 служит транзистором LRT отпускания защелки.

Фиг.28 (b) представляет временную диаграмму, показывающую работу триггера FF201 (когда сигнал INITB неактивен), и Фиг.28 (с) представляет таблицу истинности для триггера FF201 (когда сигнал INITB неактивен). Как показано на Фиг.28 (b) и (с), сигнал на клемме Q триггера FF201 имеет низкий уровень (Low) (неактивный) в период времени, когда сигнал на клемме SB имеет низкий уровень (Low) (активный) и сигнал на клемме RB имеет низкий уровень (Low) (активный); имеет высокий уровень (High) (активный) в период времени, когда сигнал SB имеет низкий уровень (Low) (активный) и сигнал RB имеет высокий уровень (High) (неактивный); имеет низкий уровень (Low) (неактивный) в период времени, когда сигнал SB сигнал имеет высокий уровень (High) (неактивный) и сигнал RB имеет низкий уровень (Low) (активный); а также сохраняет свою величину в период времени, когда сигнал SB имеет высокий уровень (High) (неактивный) и сигнал RB имеет высокий уровень (High) (неактивный).

Например, на интервале t1 на Фиг.28 (b) напряжение Vdd от клеммы RB передают на клемму Q, в результате чего транзистор n7 отпирается (ON), так что напряжение Vss (низкий уровень (Low)) проходит на клемму QB. На интервале t2 сигнал SB повышают до высокого уровня (High), так что транзистор р5 запирается (OFF), а транзистор п6 отпирается, так что сохраняется состояние, имевшее место на интервале t1. На интервале t3 сигнал RB снижается до низкого уровня (Low), вследствие чего транзистор р7 отпирается, так что высокий уровень Vdd (High) поступает на клемму QB, и более того, транзистор n5 отпирается, так что напряжение Vss проходит на клемму Q. Следует отметить, что когда оба сигнала - SB и RB, переходят на низкий уровень (Low) (активный), транзистор р7 отпирается, так что напряжение высокого уровня Vdd (High) проходит на клемму QB, а напряжение Vss+Vth (пороговое напряжение транзистора р5) передают на клемму Q через транзистор р5.

Более того, когда сигнал SB и сигнал RB стали неактивными в период времени в котором сигнал INITB активен, сигналы Q и QB на выходах триггера FF201 становятся неактивными.

Например, предположим, что в период времени, в котором сигнал INITB имеет низкий уровень (Low) (активен), происходит переход из состояния, в котором оба сигнала - SB и RB, имеют низкий уровень (Low) (активны) (состояние А), в состояние, в котором оба эти сигнала - SB и RB, имеют высокий уровень (High) (неактивны) (состояние X). В состоянии А транзистор р7 открыт и транзистор р6 заперт, напряжение высокого уровня Vdd (High) проходит на клемму QB, а напряжение Vss низкого уровня проходит на клемму Q. В состоянии Х транзистор р6 остается заперт, вследствие чего выходные сигналы на клеммах Q и QB остаются такими же, как и в состоянии А. Далее, предположим, что в период времени, когда сигнал INITB имеет низкий уровень (Low) (активный), происходит изменение из состояния, в котором сигнал SB имеет высокий уровень (High) (неактивный) и сигнал RB имеет низкий уровень (Low) (активный) (состояние В), в состояние, в котором оба сигнала - SB и RB, имеют высокий уровень (High) (неактивный) (состояние X). В состоянии В транзисторы р7 и n5 открыты, и напряжение Vdd (High) высокого уровня проходит на клемму QB, а напряжение Vss (Low) низкого уровня проходит на клемму Q. В состоянии Х транзистор р6 остается заперт; поэтому выходные сигналы на клеммах Q и QB остаются такими же, как и в состоянии В. Более того, предположим, в течение периода времени, когда сигнал INITB имеет низкий уровень (Low) (активный), происходит изменение из состояния, в котором сигнал SB имеет низкий уровень (Low) (активный) и сигнал RB имеет высокий уровень (High) (неактивный) (состояние С), в состояние, в котором оба сигнала - SB и RB, имеют высокий уровень (High) (неактивный) (состояние X). В состоянии С выходные сигналы на обеих клеммах - Q и QB, становятся неопределенными. В состоянии Х транзистор р6 открыт; поэтому напряжение Vss+Vth (пороговое напряжение транзистора р5) поступает на клемму Q, а напряжение Vdd (High) высокого уровня поступает на клемму QB.

Таким образом, в триггере FF201 транзисторы р6, n5, р8 и n7 (две КМОП-схемы) составляют защелку; клемма RB соединена с затвором транзистора р7, который служит транзистором RT сброса, и с истоком транзистора р5, который служит транзистором ST установки; и исток транзистора р6 соединен с клеммой INITB, в результате чего определен порядок приоритетности сигналов установки, защелкивания, сброса, SB и RB, если они становятся активными в одно и то же время, и реализована процедура инициализации. В триггере FF201, как описано выше, когда сигнал SB и сигнал RB становятся активными в одно и то же время, сигнал RB (сброс) имеет приоритет, так что выходной сигнал QB становится неактивным. (Вариант 2)

Другой вариант настоящего изобретения описан ниже со ссылками на Фиг.9-13. Для удобства пояснения тем элементам, которые имеют такие же функции, как описаны выше в Варианте 1, присвоены такие же цифровые позиционные обозначения, а сами элементы не будут описаны ниже. Далее, термины, определенные применительно к Варианту 1, определены в рассматриваемом варианте таким же образом, если не указано иначе.