Область техники, к которой относится изобретение

Настоящее изобретение относится к схеме возбуждения устройства отображения и способу возбуждения устройства отображения для возбуждения панели отображения в устройстве отображения, таком как жидкокристаллическое устройство отображения, имеющее жидкокристаллическую панель отображения с активной матрицей.

Уровень техники

Известное жидкокристаллическое устройство отображения с активной матрицей, включающее в себя шины накопительных конденсаторов, имеет недостаток, связанный с тем, что при выполнении возбуждения с реверсивной полярностью во время включения питания (то есть, в начальный период времени) нельзя получить равномерное отображение. Это происходит из-за того, что сразу после включения питания жидкокристаллического устройства отображения потенциалы питающего потенциала на шинах накопительных конденсаторов становятся неопределенными.

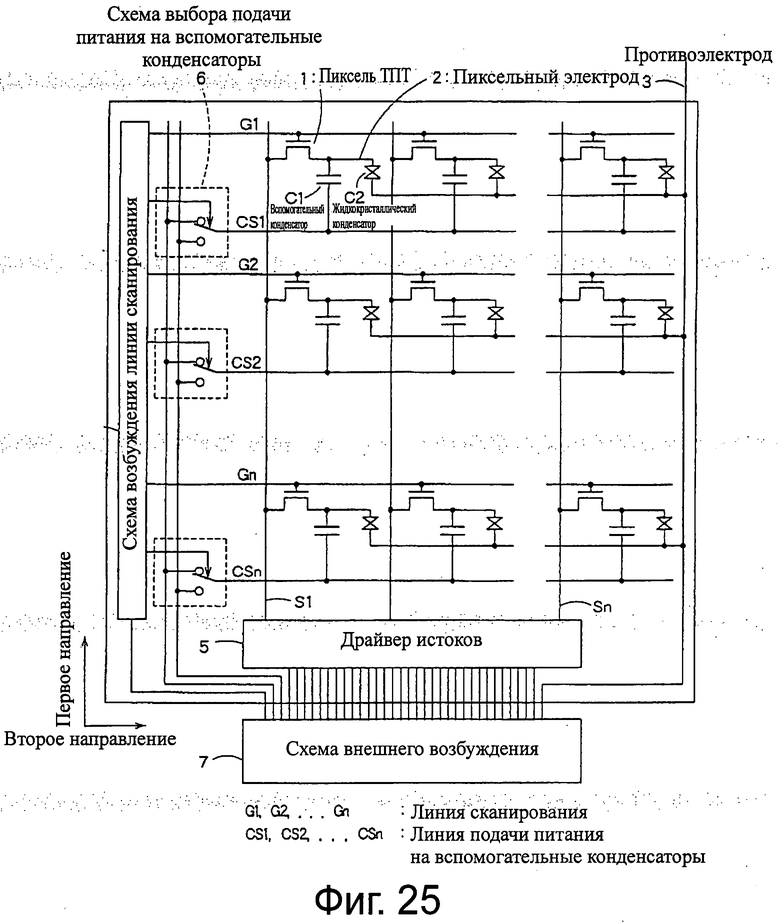

Способ устранения этого недостатка отображения во время включения питания раскрыт, например, в патентной литературе 1. На фиг.25 изображена блок-схема, схематично показывающая конфигурацию жидкокристаллического устройства отображения, согласно патентной литературе 1.

Жидкокристаллическое устройство отображения включает в себя: сигнальные линии S1-Sn данных, выполненные на стеклянной подложке и размещенные вдоль второго направления; сигнальные линии G1-Gn сканирования, выполненные на стеклянной подложке и размещенные вдоль первого направления; пиксельные тонкопленочные транзисторы (ТПТ) 1, каждый из которых выполнен в зоне около точки пересечения между сигнальной линией данных и сигнальной линией сканирования; вспомогательные конденсаторы (накопительные конденсаторы) С1, каждый из которых подсоединен к стоковому выводу пиксельного ТПТ1; пиксельные электроды 2, каждый из которых подсоединен к стоковому выводу пиксельного ТПТ1; жидкокристаллические конденсаторы С2, каждый из которых выполнен между пиксельным электродом 2 и противоэлектродом 3, размещенным напротив пиксельного электрода 2, с помощью жидкокристаллического слоя, расположенного между ними; схему возбуждения линий сканирования (схему возбуждения сигнальных линий сканирования) 4, которая возбуждает линии сканирования (сигнальные линии сканирования); возбудитель истоков (схема возбуждения сигнальных линий данных) 5, которая возбуждает сигнальные линии данных; линии CS1-CSn питания вспомогательных конденсаторов (шины накопительных конденсаторов), каждая из которых подсоединена к концу каждого одного из ряда вспомогательных конденсаторов С1, размещенных вдоль линий сканирования (вдоль второго направления); и схема выбора питания вспомогательных конденсаторов (схема возбуждения шин накопительных конденсаторов) 6, которая устанавливает потенциалы на линиях CS1-CSn питания вспомогательных конденсаторов.

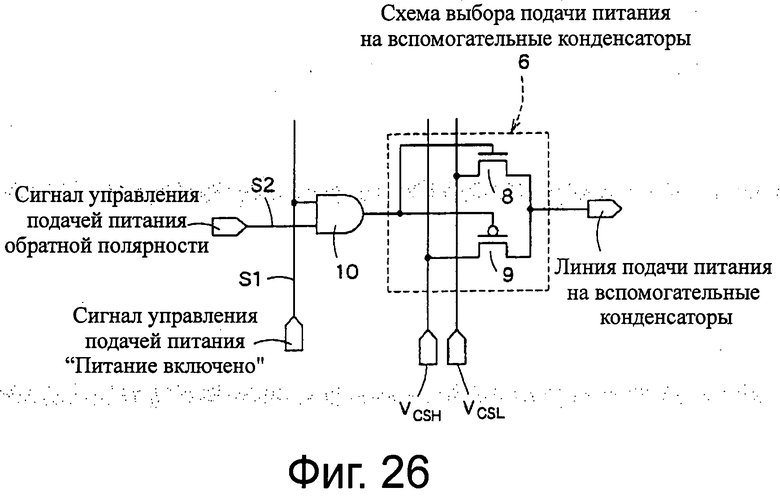

Фиг.26 изображает схему, подробно показывающую конфигурацию схемы 6 выбора питания вспомогательных конденсаторов. Как показано на фиг.26, схема 6 выбора питания вспомогательных конденсаторов имеет рМОП-транзистор 9, который выбирает, подавать или нет первое опорное напряжение VcsH на линии CS1-CSn питания вспомогательных конденсаторов, и nМОП-транзистор 8, который выбирает, подавать или нет второе опорное напряжение VcsL (<VcsH) на линии CS1-CSn питания вспомогательных конденсаторов, и эти транзисторы 8 и 9 включаются/выключаются под управлением вентиля 10 И, который выполнен в схеме 4 возбуждения линий сканирования.

Вентиль 10 И вычисляет логическое произведение (i) сигнала s1 управления подачей питания для управления потенциалами линий CS1-CSn питания вспомогательных конденсаторов во время включения питания и (ii) сигнала s2 управления питанием обратной полярности для управления потенциалами линий CS1-CSn питания вспомогательных конденсаторов во время изменения полярности потенциала, и на основании полученного результата вычисления переключает транзисторы 8 и 9 между двумя состояниями "включено" и "выключено".

В этой конфигурации, во время предопределенного периода времени после момента включения питания, сигнал s1 управления включением питания имеет низкий уровень (0 В), посредством чего выходной сигнал вентиля 10 И (см. фиг.26) в схеме 4 возбуждения линий сканирования имеет низкий уровень, и рМОП-транзистор включается, в результате чего первое опорное напряжение VcsH подается на линии CS1-CSn питания вспомогательных конденсаторов. Поскольку первое опорное напряжение VcsH выше, чем второе опорное напряжение VcsL, потенциала на всех линиях CS1-CSn питания вспомогательных конденсаторов имеют высокий уровень во время предопределенного периода времени после момента включения питания. Когда потенциала на линиях CS1-CSn питания вспомогательных конденсаторов имеют высокий уровень, напряжение на каждом пиксельном электроде 2 также имеет относительно высокий уровень, и напряжение на выводах каждого жидкокристаллического конденсатора С2 (то есть, разность потенциалов между противоэлектродом 3 и каждым пиксельным электродом 2) является маленьким. После этого, например, жидкокристаллическое устройство отображения в режиме "нормального белого" (которое выполняет отображение в режиме "нормального белого" при отсутствии сигнала) выполняет отображение, близкое к белому отображению даже в случае, когда оно выключается, в результате чего нельзя увидеть яркую линию. Затем, по истечении предопределенного периода времени схема 6 выбора питания вспомогательных емкостей (фиг.26) повышает напряжение сигнала s1 управления включением питания до высокого уровня. Это приводит к переключению логических уровней вентиля 10 И в соответствии с изменением логических уровней сигнала s2 управления питанием обратной полярности. Соответственно, включение и выключение пМОП-транзистора 8 и рМОП-транзистора 9 изменяется в соответствии с циклом возбуждения напряжением обратной полярности. Это вызывает потенциала линий CS1-CSn питания вспомогательных конденсаторов с первым опорным напряжением VcsH или вторым опорным напряжением VcsL в соответствии с циклом возбуждения напряжением обратной полярности.

Таким образом, в этой конфигурации, поскольку во время предопределенного периода времени после момента включения питания в каждой из линий CS1-CSn питания вспомогательных конденсаторов устанавливается одинаковое напряжение питания (первое опорное напряжение), то в линиях CS1-CSn питания вспомогательных конденсаторов не происходит изменение уровня потенциала. Это позволяет устранить недостаток отображения во время включения питания.

Перечень цитируемой литературы

Патентная литература 1

Публикация заявки на патент Японии, Токукай (Tokukai), №2005-49849 А, дата подачи: 4 февраля 2005 года.

Сущность изобретения

Техническая задача

Однако для жидкокристаллического устройства отображения требуется, чтобы сигнальные линии и схема управления обеспечивали подачу предопределенного потенциала в линии питания вспомогательных конденсаторов сразу после включения жидкокристаллического устройства отображения, что, таким образом, приводит к увеличению площади схемы возбуждения. Это затрудняет использование схемы возбуждения в жидкокристаллической панели отображения с узким кадром.

Настоящее изобретение выполнено с учетом вышеупомянутых недостатков, и задача настоящего изобретения заключается в том, чтобы выполнить схему возбуждения устройства отображения и способ возбуждения устройства отображения, которые не приводят к увеличению площади схемы, что позволяет повысить качество отображения во время включения питания.

Решение задачи

Схема возбуждения устройства отображения, согласно настоящему изобретению, представляет собой схему возбуждения устройства отображения, предназначенную для возбуждения панели отображения, выполненной с шинами накопительных конденсаторов, которые образуют конденсаторы с пиксельными электродами, включенными в пиксели, причем схема возбуждения устройства отображения включает в себя сдвиговый регистр, включающий в себя множество каскадов, выполненных таким способом, чтобы соответствовать множеству сигнальных линий сканирования, соответственно, при этом схема возбуждения устройства отображения имеет схемы удержания, выполненные таким образом, чтобы один к одному соответствовать каскадам сдвигового регистра, причем сигнал цели удержания вводится в каждую из схем удержания, когда сигнал управления, выработанный с помощью одного из каскадов сдвигового регистра становится активным, при этом схема удержания соответствует этому каскаду, загружающему и удерживающему сигнал цели удержания, причем выходной сигнал, поступающий из схемы удержания, подается на шину накопительных конденсаторов в качестве сигнала шины накопительных конденсаторов, при этом сигнал управления, которой вырабатывается в каждом каскаде сдвигового регистра, становится активным перед первым периодом вертикального сканирования картинки отображения.

Согласно вышеупомянутой конфигурации, когда сигнал управления, который вырабатывается на каждом из каскадов сдвигового регистра (внутренний сигнал или внешний сигнал), становится активным перед первым периодом вертикального сканирования (первый кадр) картинки отображения (в начальный период), сигнал цели удержания (сигнал CMI полярности) удерживается в схеме удержания (в схеме защелки или запоминающей схеме) соответствующего каскада. Поэтому, например, в случае, где в начальный период времени, сигнал цели удержания устанавливается с определенным уровнем потенциала (высоким уровнем или низким уровнем), сигнал определенного потенциала выводится из схемы удержания и подается в линию накопительных конденсаторов. Это позволяет зафиксировать потенциал сигнала шины накопительных конденсаторов после включения питания и до начала первого кадра, таким образом, позволяя устранить недостаток отображения в начальный период из-за вышеупомянутого неопределенного состояния.

Кроме того, вышеупомянутая конфигурация устраняет необходимость выполнения схемы управления для фиксации потенциала сигнала шины накопительных конденсаторов (то есть, известной схемы выбора питания накопительных конденсаторов) или т.п., и поэтому схему возбуждения можно выполнить с меньшей площадью. Следовательно, используя схему возбуждения устройства отображения, жидкокристаллическую панель отображения можно выполнить с более узким кадром.

Способ возбуждения устройства отображения, согласно настоящему изобретению, представляет собой способ возбуждения устройства отображения, предназначенный для возбуждения панели отображения, выполненной с шинами накопительных конденсаторов, которые образуют конденсаторы с пиксельными электродами, включенными в пиксели, которая включает в себя сдвиговый регистр, включающий в себя множество каскадов, выполненных таким образом, чтобы соответствовать множеству сигнальных линий сканирования, соответственно, причем способ возбуждения устройства отображения включает в себя этапы, на которых: вводят сигнал цели удержания в схемы удержания, выполненные таким образом, чтобы соответствовать каскадам сдвигового регистра, соответственно, и, когда сигнал управления, выработанный текущим каскадом сдвигового регистра, становится активным, побуждают схему удержания, соответствующую текущему каскаду, загружать и удерживать сигнал цели удержания; подают выходной сигнал из схемы удержания на шину накопительных конденсаторов в качестве сигнала шины накопительных конденсаторов; и перед первым периодом вертикального сканирования картинки отображения, приводят в активное состояние сигнал управления, который вырабатывается каждым из каскадов сдвигового регистра.

Способ приводит к тому же самому эффекту, а именно изложенному в отношении схемы возбуждения устройства отображения, то есть, к эффекту, не вызывающему увеличение площади схемы, что позволяет повысить качество отображения во время включения питания.

Преимущественные эффекты изобретения

Как описано выше, схема возбуждения устройства отображения и способ возбуждения устройства отображения, согласно настоящему изобретению, выполнены так, чтобы сигнал управления, который вырабатывается каждым из каскадов сдвигового регистра и в дальнейшем подается в схему удержания, становился активным перед первым периодом вертикального сканирования картинки отображения. Это позволяет зафиксировать потенциал сигнала шины накопительных конденсаторов, получая, таким образом, эффект, который не приводит к увеличению площади схемы, что позволяет повысить качество отображения во время включения питания.

Краткое описание чертежей

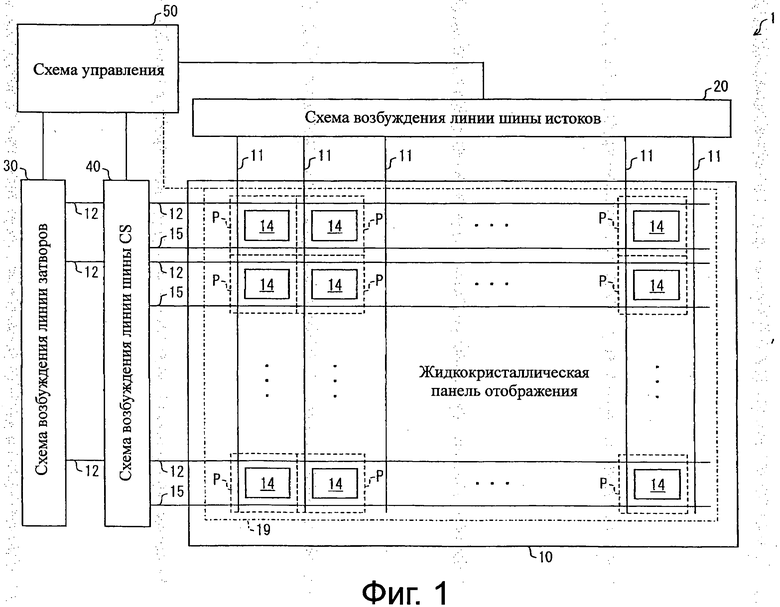

Фиг.1 - блок-схема, показывающая конфигурацию жидкокристаллического устройства отображения, согласно варианту осуществления настоящего изобретения.

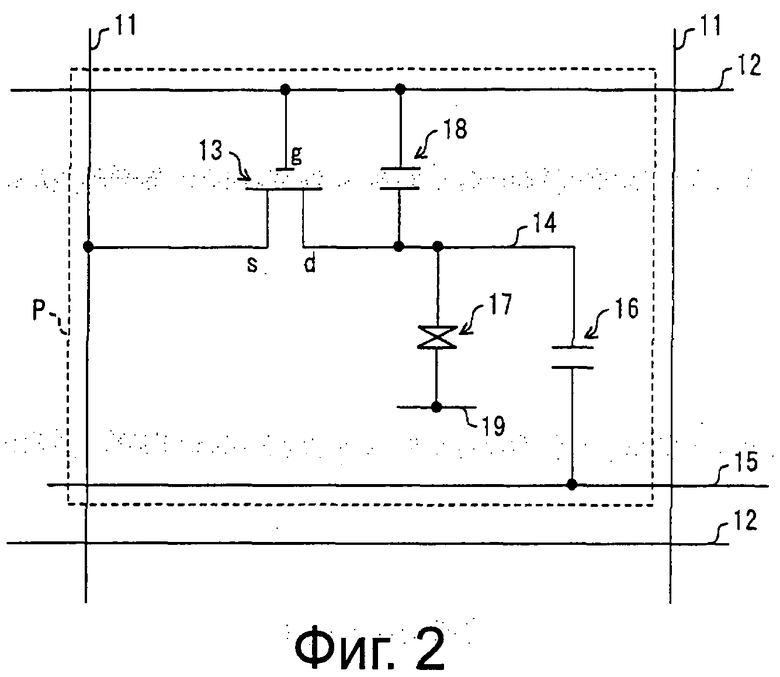

Фиг.2 - эквивалентная схема, показывающая электрическую конфигурацию каждого пикселя в жидкокристаллическом устройстве отображения (фиг.1).

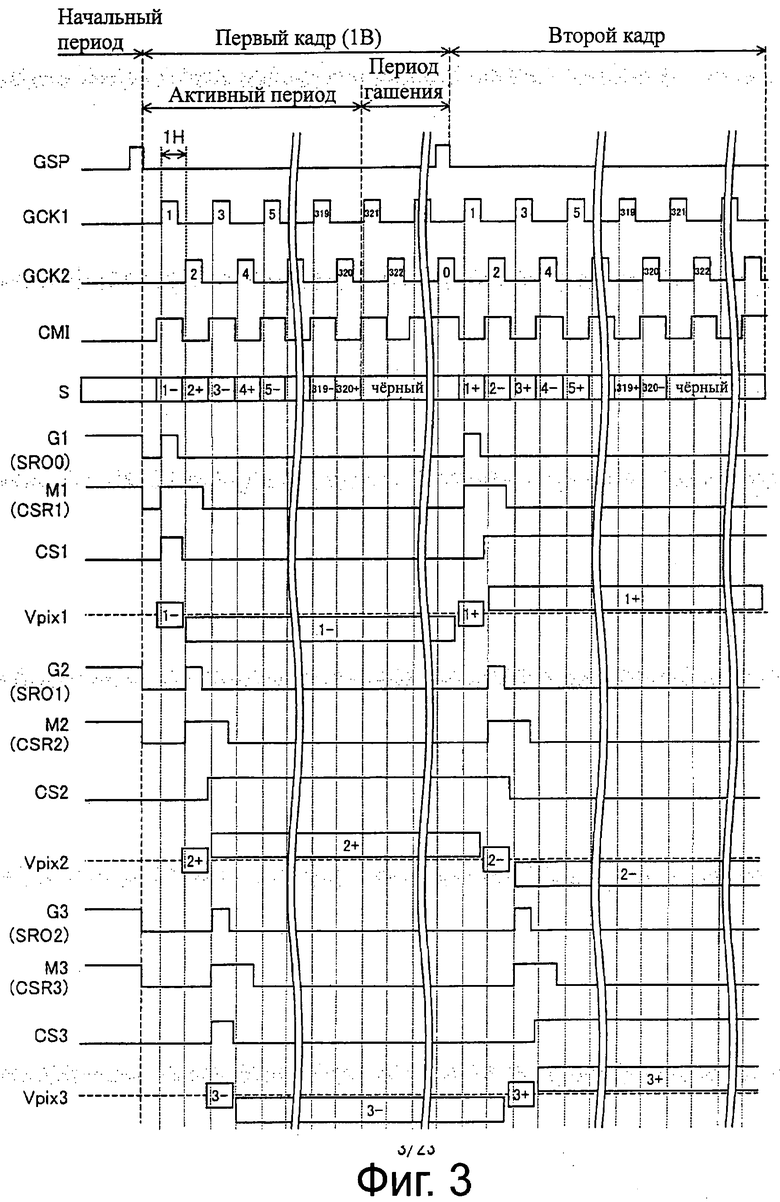

Фиг.3 - временные диаграммы, показывающие формы различных сигналов жидкокристаллического устройства отображения, согласно варианту 1 осуществления.

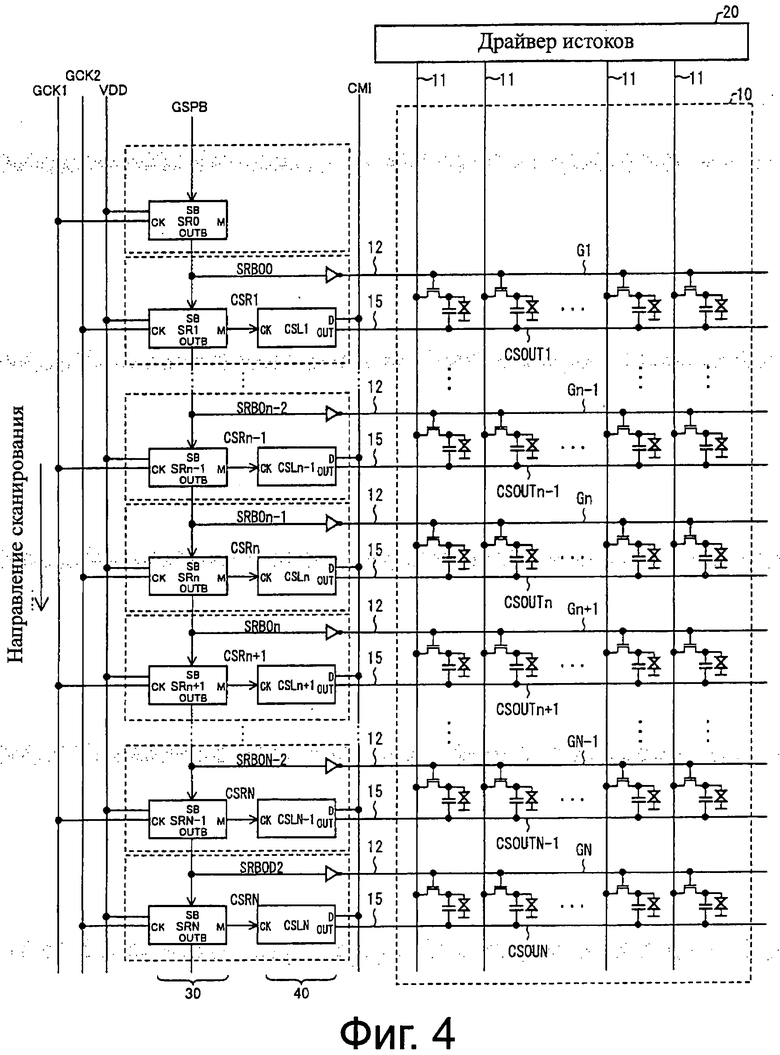

Фиг.4 - блок-схема, показывающая конфигурацию схемы возбуждения линии затворов и схемы возбуждения линии шины CS, согласно варианту 1 осуществления.

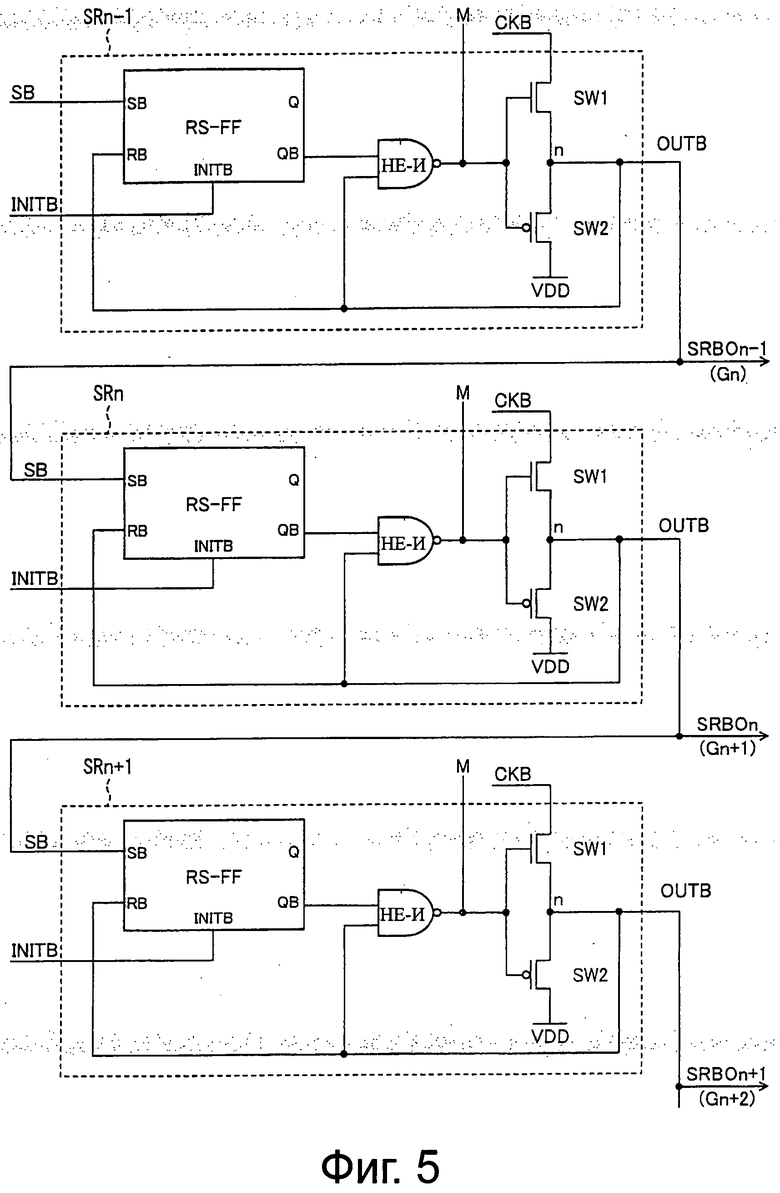

Фиг.5 показывает конфигурацию схемы сдвигового регистра, согласно варианту 1 осуществления.

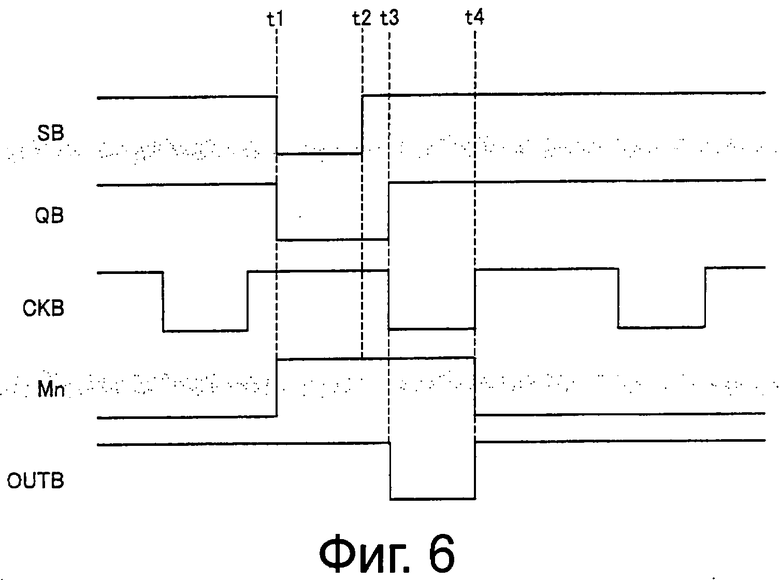

Фиг.6 - временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схемы сдвигового регистра, показанные на фиг.5.

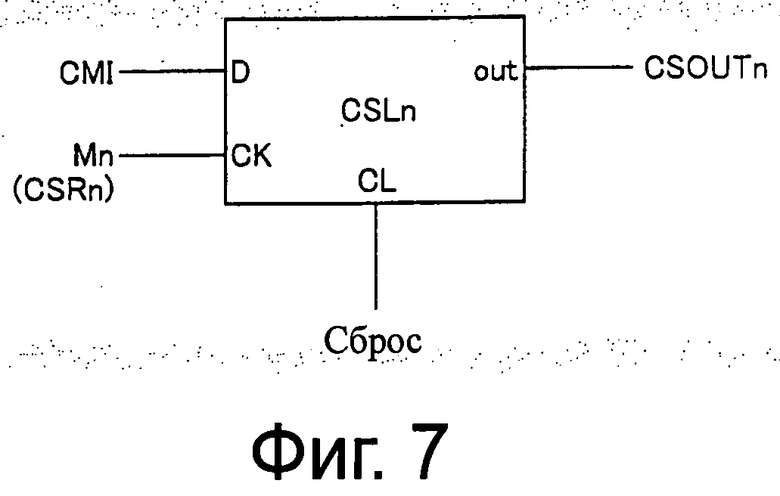

Фиг.7 показывает конфигурацию логической схемы (схемы защелки), согласно варианту 1 осуществления.

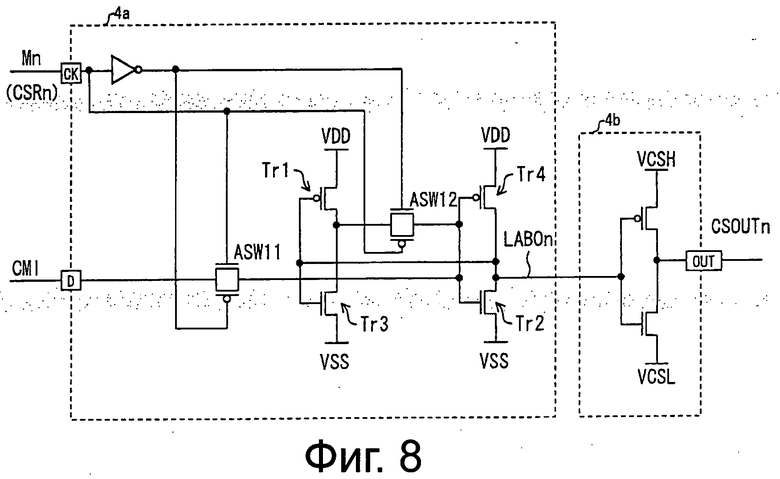

Фиг.8 - схема защелки, показанная на фиг.7.

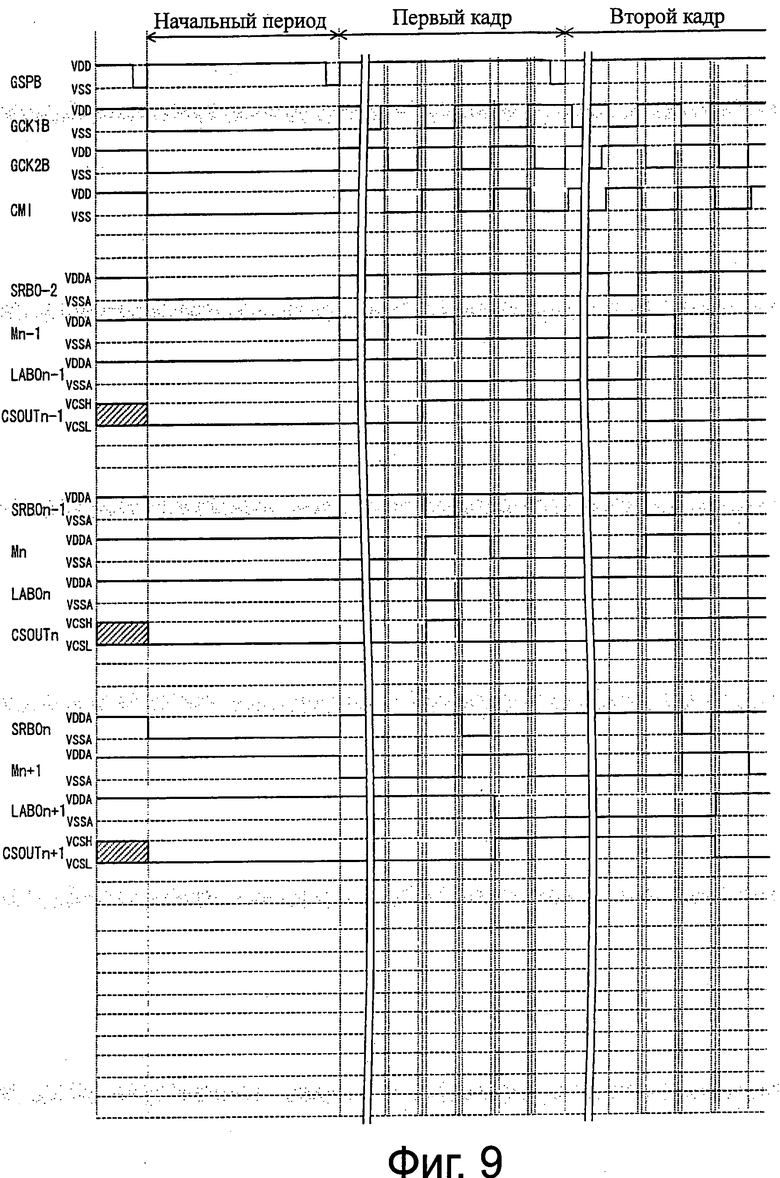

Фиг.9 - временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схемы защелки, показанной на фиг.7.

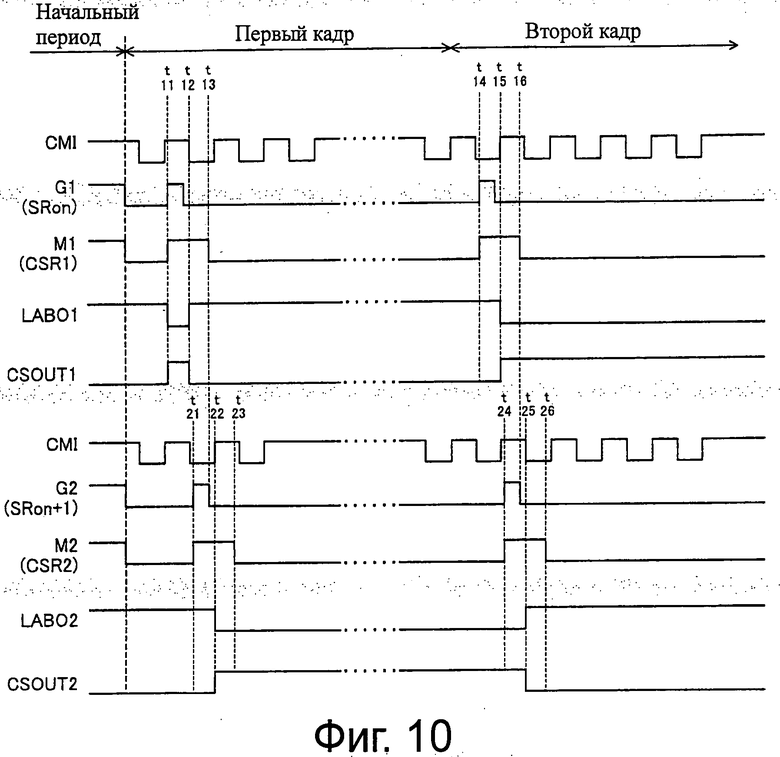

Фиг.10 - временные диаграммы, которые поясняют работу схемы защелки, показанной на фиг.7.

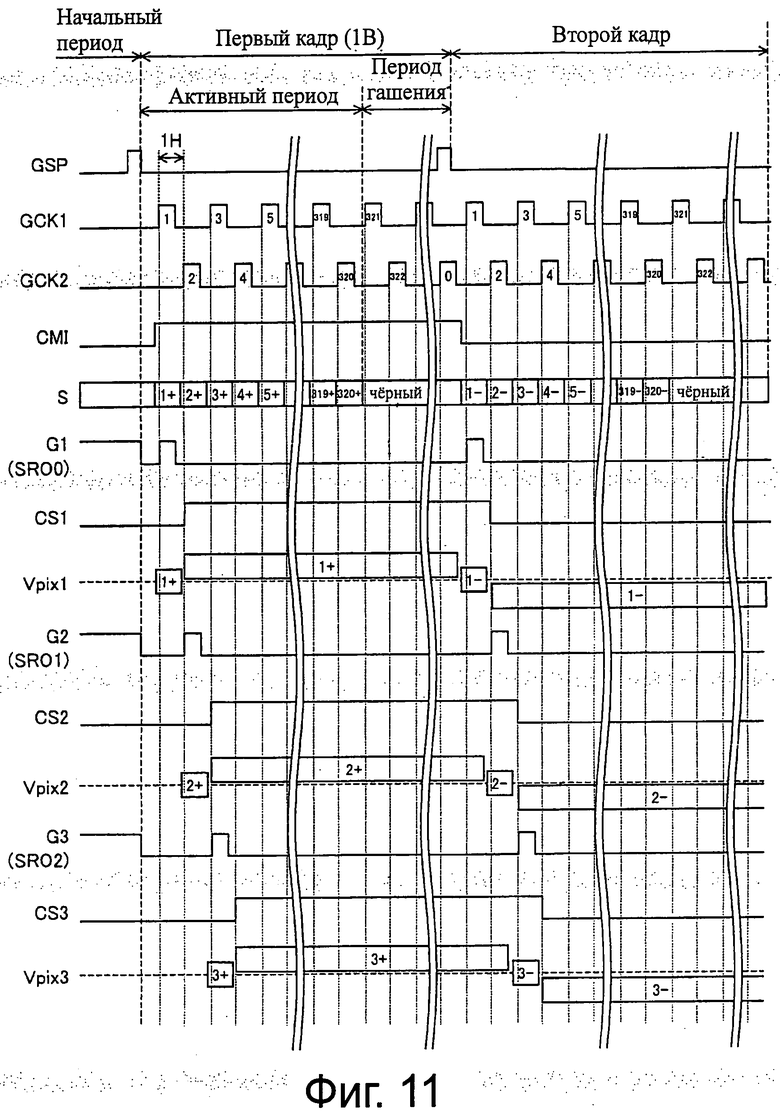

Фиг.11 - временные диаграммы, показывающие формы различных сигналов жидкокристаллического устройства отображения, согласно варианту 2 осуществления.

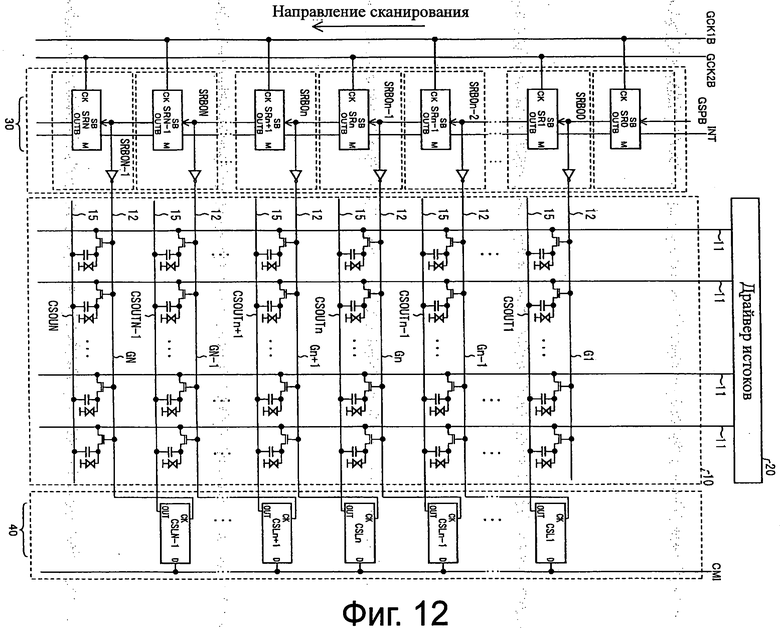

Фиг.12 - блок-схема, показывающая конфигурацию схемы возбуждения линии затворов и схемы возбуждения линии шины CS, согласно варианту 2 осуществления.

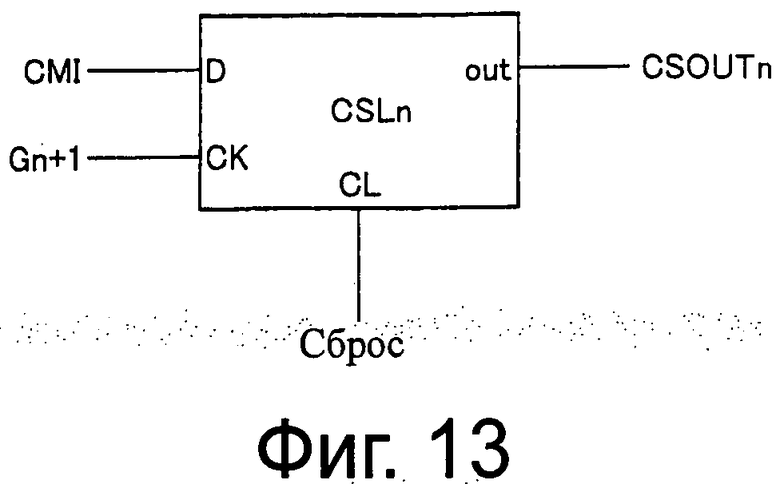

Фиг.13 - показывает конфигурацию логической схемы (схемы защелки), согласно варианту 12 осуществления.

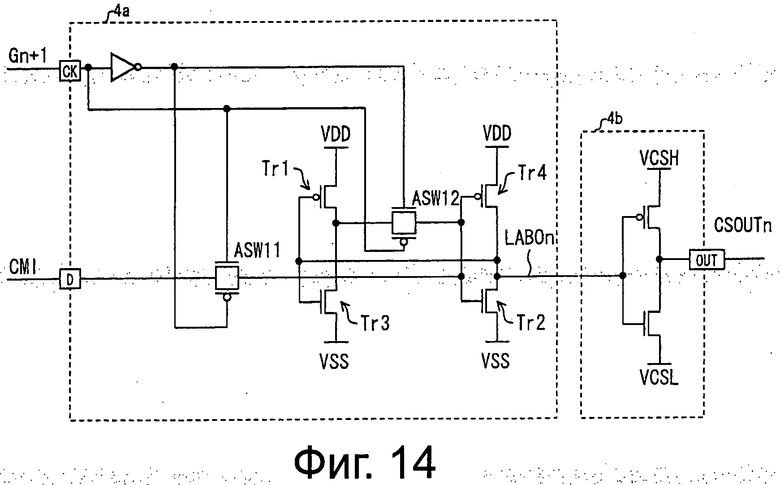

Фиг.14 - схема, защелки, показанная на фиг.13.

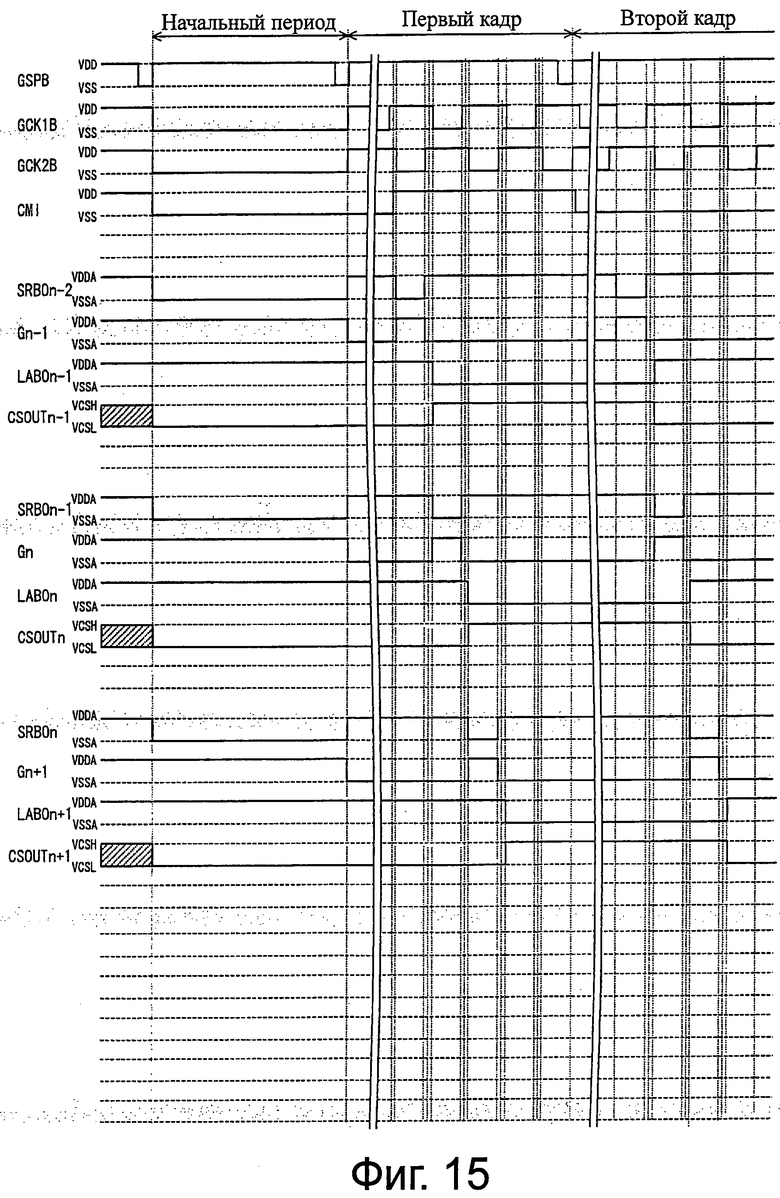

Фиг.15 - временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схемы защелки, показанной на фиг.13.

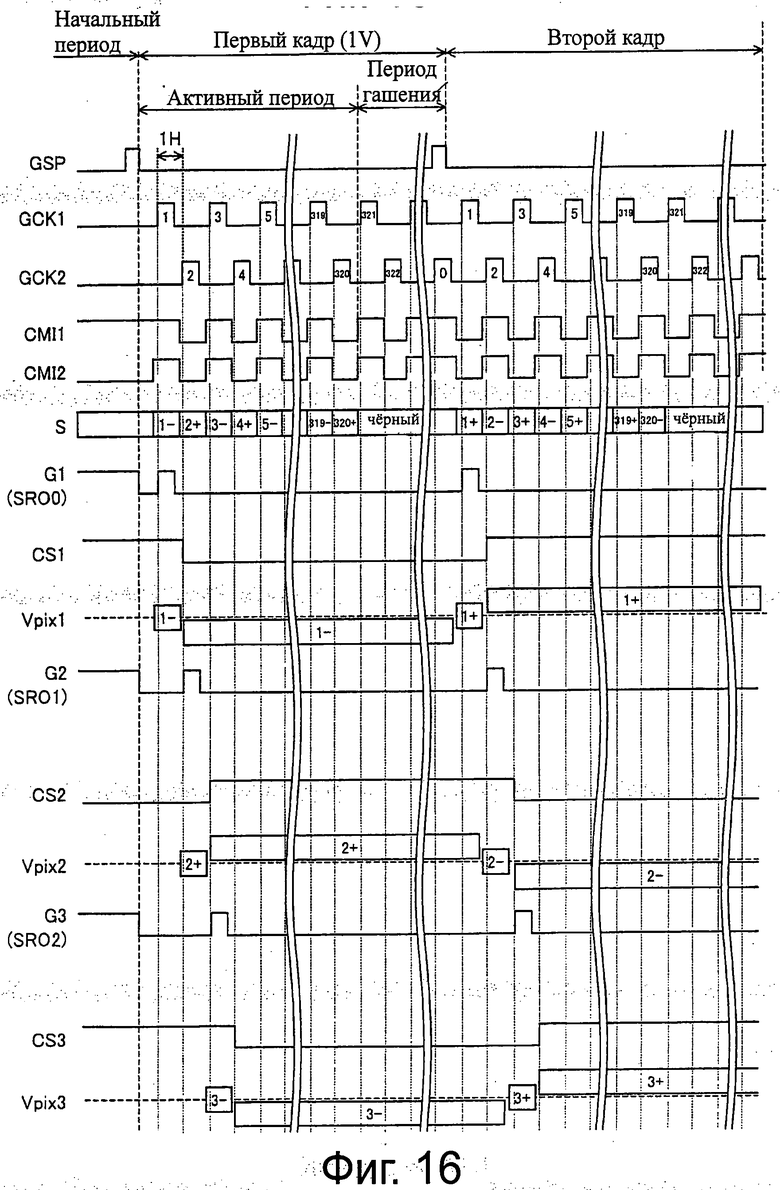

Фиг.16 - временные диаграммы, показывающие формы различных сигналов жидкокристаллического устройства отображения, согласно варианту 3 осуществления.

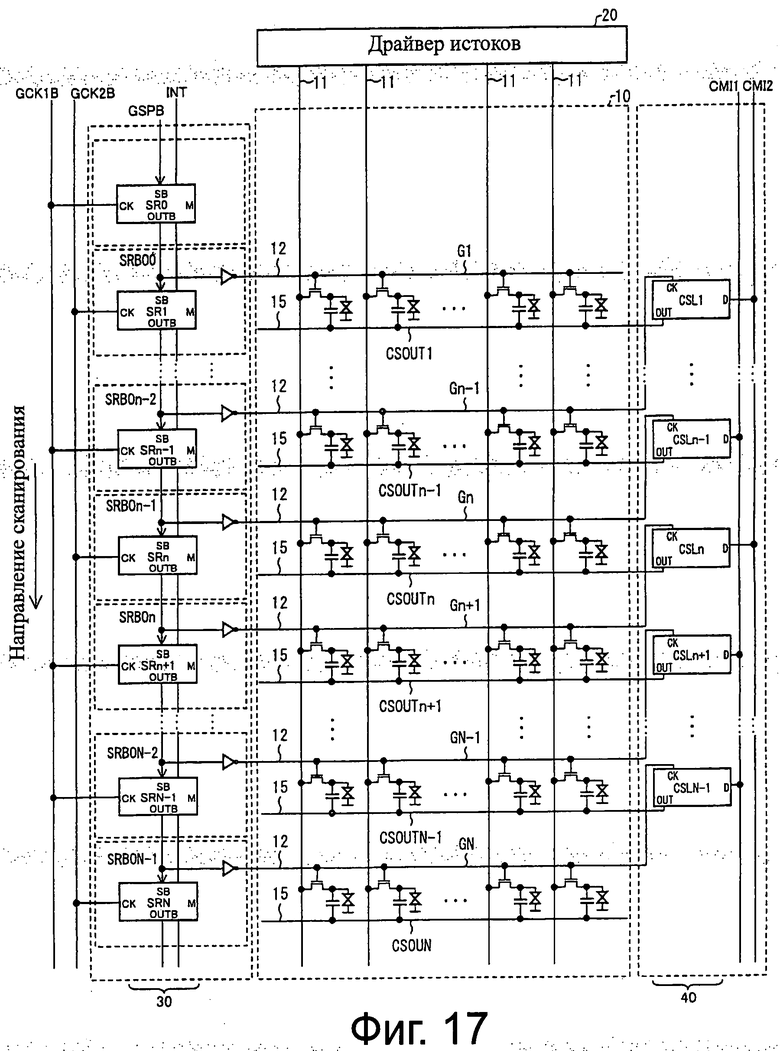

Фиг.17 - блок-схема, показывающая конфигурацию схемы возбуждения линии затворов и схемы возбуждения линии шины CS, согласно варианту 3 осуществления.

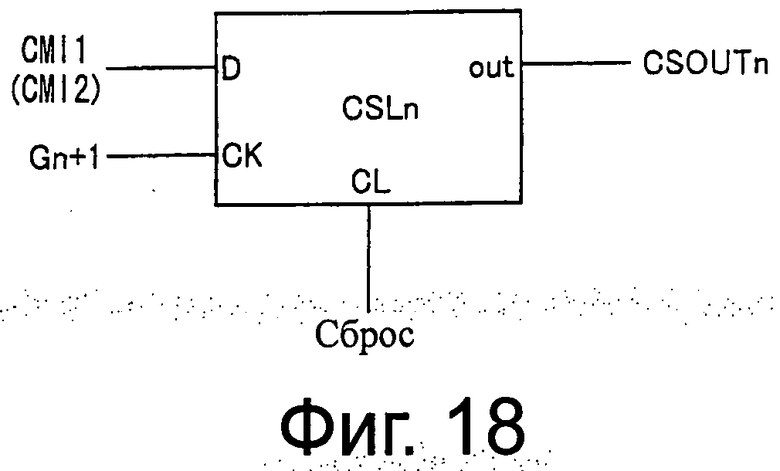

Фиг.18 показывает конфигурацию логической схемы (схемы защелки), согласно варианту 3 осуществления.

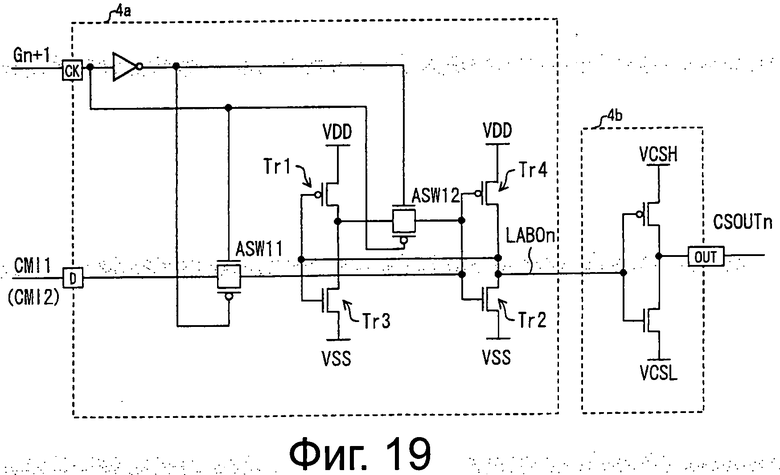

Фиг.19 - схема защелки, показанная на фиг.18.

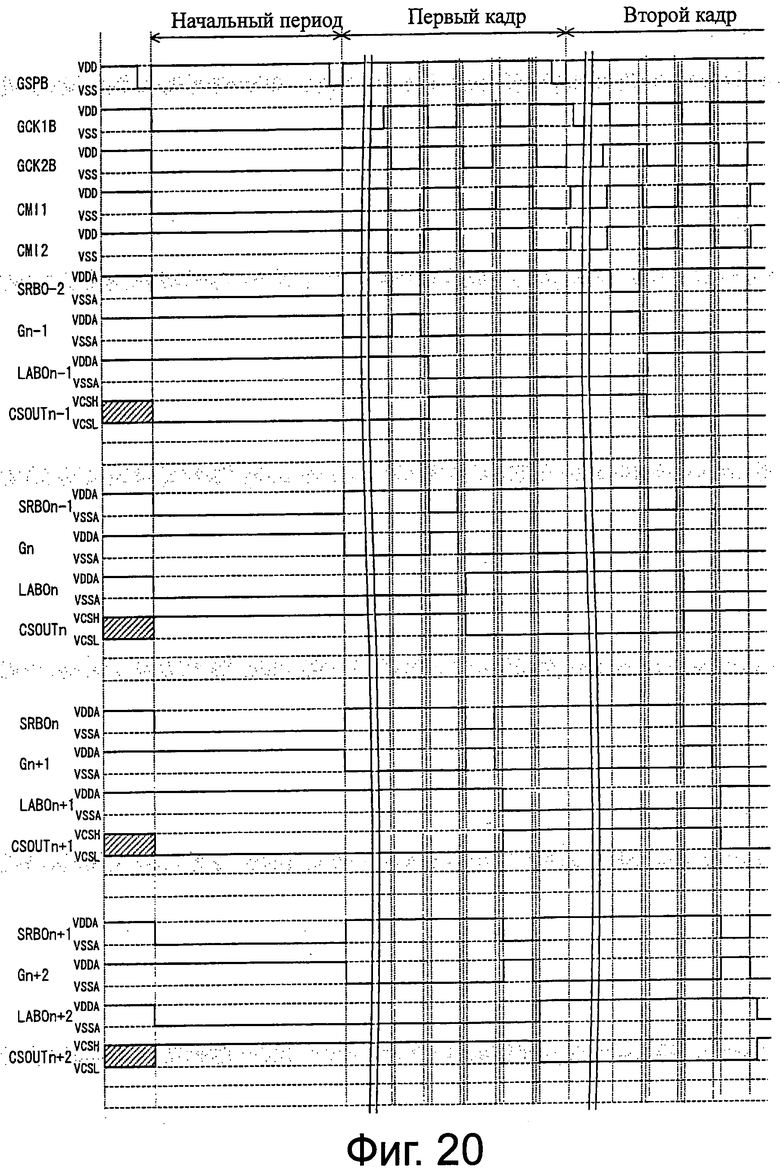

Фиг.20 - временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схемы защелки, показанной на фиг.18.

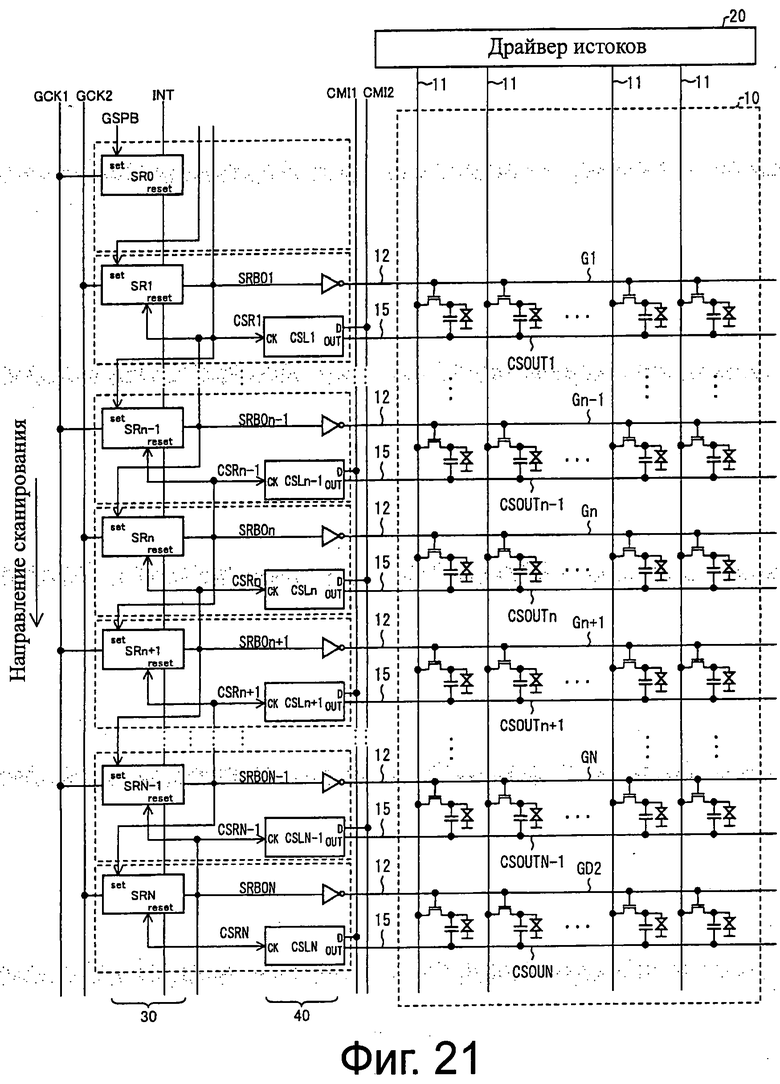

Фиг.21 - блок-схема, показывающая конфигурацию схемы возбуждения линии затворов и схемы возбуждения линии шины CS, согласно варианту 4 осуществления.

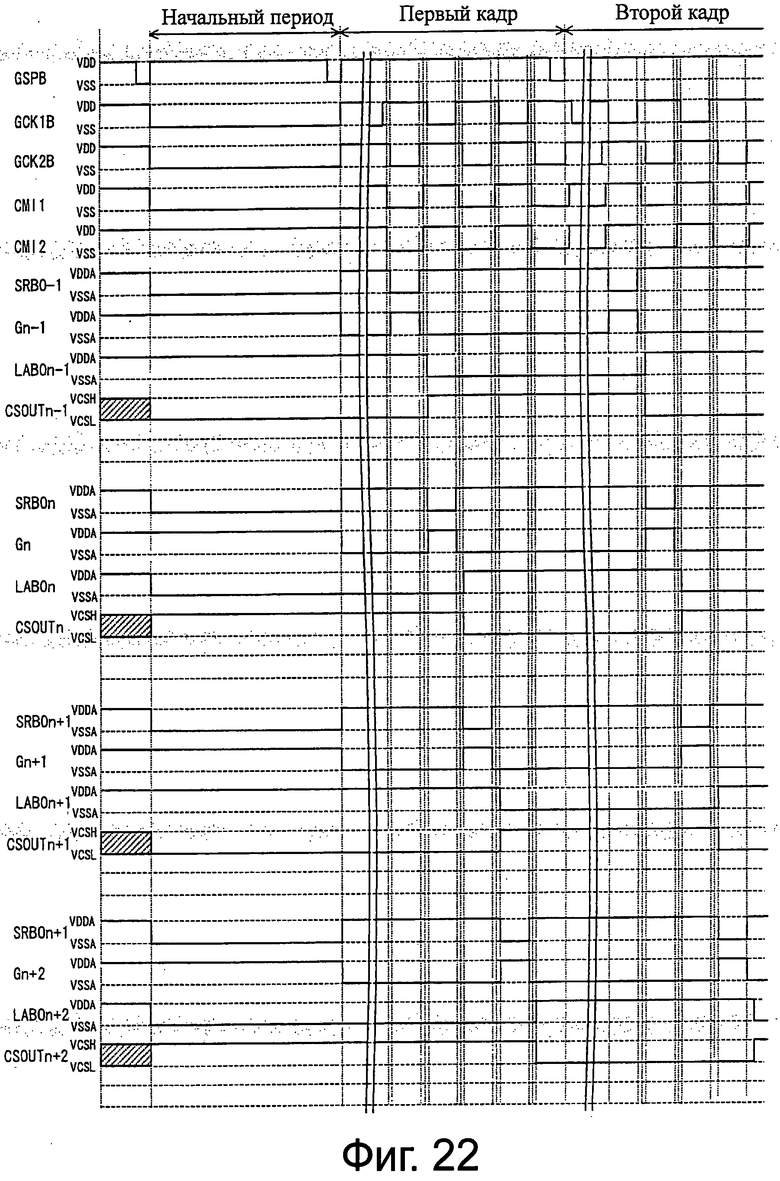

Фиг.22 - временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схемы защелки, показанной на фиг.21.

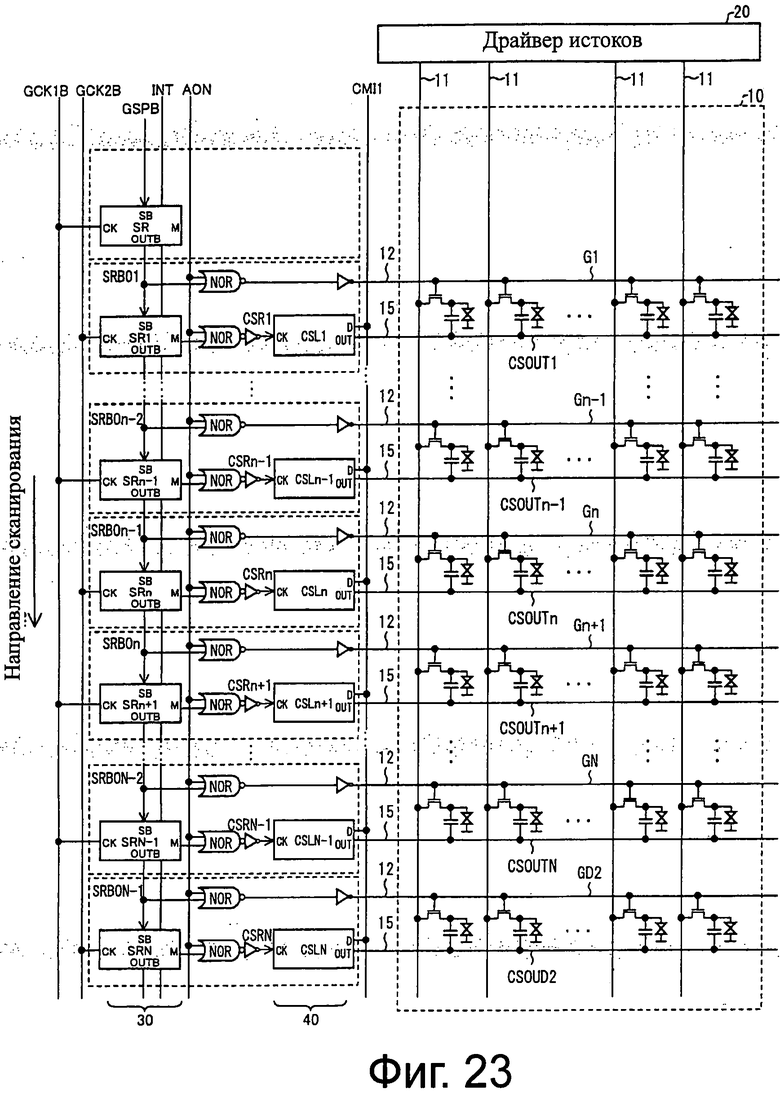

Фиг.23 - блок-схема, показывающая конфигурацию схемы возбуждения линии затворов и схемы возбуждения линии шины CS, согласно варианту 5 осуществления.

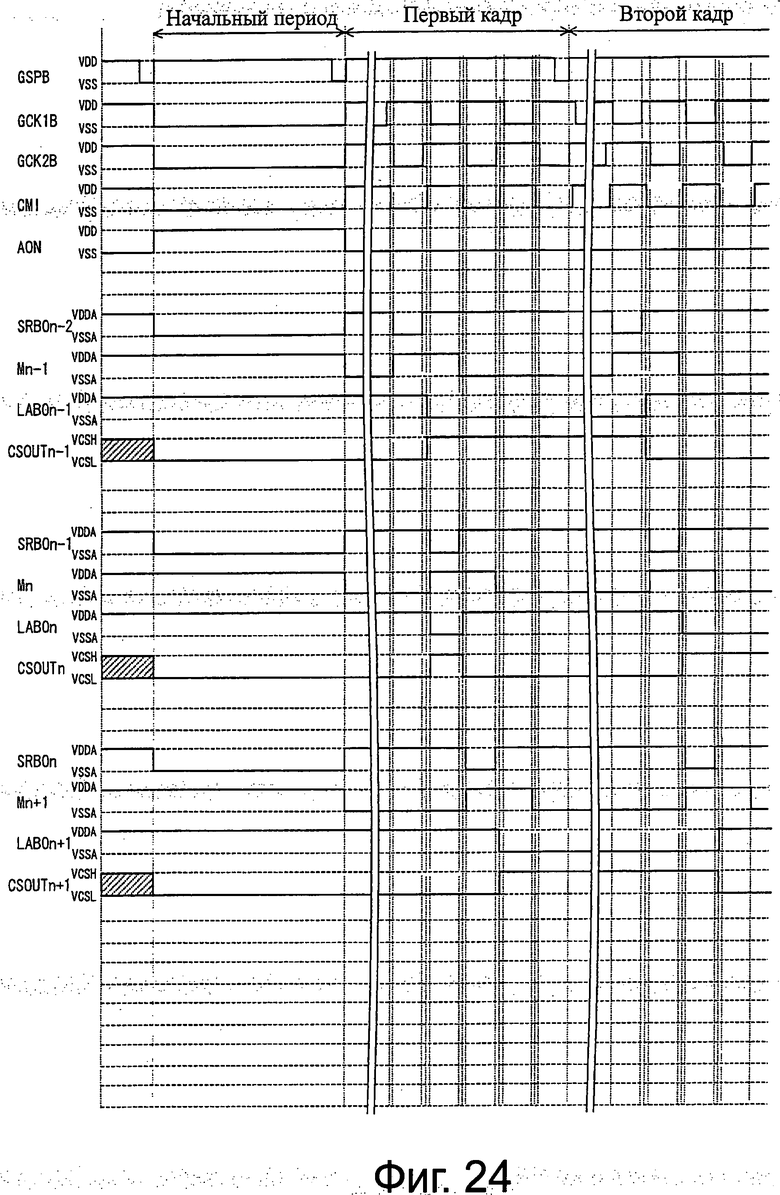

Фиг.24 - временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схемы защелки, показанной на фиг.23.

Фиг.25 - блок-схема, показывающая конфигурацию известного жидкокристаллического устройства отображения.

Фиг.26 - схема, показывающая конфигурацию схемы выбора питания вспомогательных конденсаторов в жидкокристаллическом устройстве отображения, показанном на фиг.25.

Подробное описание изобретения

Описание вариантов осуществления

Подробное описание вариантов осуществления настоящего изобретения приведено ниже со ссылкой на чертежи.

Сначала со ссылкой на фиг.1 и 2 описана конфигурация жидкокристаллического устройства 1 отображения, соответствующего устройству отображения настоящего изобретения. Фиг.1 изображает блок-схему, показывающую в целом конфигурацию жидкокристаллического устройства 1 отображения, и фиг.2 изображает эквивалентную схему, показывающую электрическую конфигурацию каждого пикселя жидкокристаллического устройства 1 отображения.

Жидкокристаллическое устройство 1 отображения включает в себя: жидкокристаллическую панель 10 отображения с активной матрицей, которая соответствует панели отображения настоящего изобретения; схему 20 возбуждения линии шины истоков, которая соответствует схеме возбуждения сигнальных линий данных настоящего изобретения; схему 30 возбуждения линии затворов, которая соответствует схеме возбуждения сигнальных линий сканирования настоящего изобретения; схему 40 возбуждения линии шины CS, которая соответствует схеме возбуждения шин накопительных конденсаторов настоящего изобретения; и схему 50 управления, которая соответствует схеме управления настоящего изобретения.

Жидкокристаллическая панель 10 отображения, образованная с помощью жидких кристаллов, расположенных между подложкой активной матрицы и противоподложкой (не показана), имеет большое число пикселей Р, размещенных по строкам и столбцам.

Более того, жидкокристаллическая панель 10 отображения включает в себя: линии 11 шины истоков, выполненные на подложке активной матрицы, которые соответствуют сигнальным линиям данных настоящего изобретения; линии 12 затворов, выполненные на подложке активной матрицы, которые соответствуют сигнальным линиям сканирования настоящего изобретения; тонкопленочные транзисторы (здесь и далее называются ТПТ) 13, выполненные на подложке активной матрицы, которые соответствуют переключающему элементу настоящего изобретения; пиксельные электроды 14, выполненные на подложке активной матрицы, которые соответствуют пиксельным электродам настоящего изобретения; линии 15 шины CS, выполненные на подложке активной матрицы, которые соответствуют шинам накопительных конденсаторов настоящего изобретения; и противоэлектрод 12, выполненный на противоподложке. Следует отметить, что каждый из ТПТ 13, не показанный на фиг.1, изображен самостоятельно на фиг.2.

Линии 11 шины истоков размещены одна за другой по столбцам параллельно друг другу вдоль направления столбцов (продольного направления), и линии 12 затворов размещены одна за другой по строкам параллельно друг другу вдоль направления строк (поперечного направления). Каждый из ТПТ 13 выполнен в соответствии с точкой пересечения между линией 11 шины истоков и линией 12 затворов, поэтому они представляют собой пиксельные электроды 14. Каждый из ТПТ 13 имеет свой электрод s истока, подсоединенный к линии 11 шины истоков, свой электрод g затвора, подсоединенный к линии 12 затворов, и свой электрод d стока, подсоединенный к пиксельному электроду 14. Кроме того, каждый из пиксельных электродов 14 образует жидкокристаллический конденсатор 17 с противоэлектродом 12 с жидкими кристаллами, расположенными между пиксельным электродом 14 и противоэлектродом 19.

Затем, когда сигнал затворов (сигнал сканирования), который подается в линию 12 затворов, побуждает затвор к включению ТПТ 13, и сигнал истоков (сигнал данных), подаваемый из линии 11 шины истоков, записывается в пиксельном электроде 14, пиксельный электрод 14 выдает потенциал, соответствующий сигналу истоков. В результате, потенциал, соответствующий сигналу истоков, подается на жидкие кристаллы, расположенные между пиксельным электродом 14 и противоэлектродом 19. Это позволяет реализовать отображение со шкалой серого цвета, соответствующее сигналу истоков.

Линии 15 шины CS размещены одна за другой по строкам параллельно друг другу вдоль направления строк (поперечного направления) таким образом, чтобы быть парными с линиями 12 затворов, соответственно. Каждая из линий 15 шины CS образует накопительный конденсатор 16 (который называется "вспомогательным конденсатором") с каждым одним из пиксельных электродов 14, которые размещены в каждой строке, таким образом, обеспечивая емкостную связь с пиксельными электродами 14.

Следует отметить, что поскольку из-за своей структуры ТПТ 13 имеет включающийся конденсатор 18, образованный между электродом g затвора и электродом d стока, потенциал пиксельного электрода 14 воздействует на (включает) изменение потенциала линии 12 затворов. Однако для упрощения объяснения такой эффект не принимается во внимание здесь.

Жидкокристаллическая панель 10 отображения, выполненная таким образом, возбуждается с помощью схемы 20 возбуждения линии шины истоков, схемы 30 возбуждения линии затворов и схемы 40 возбуждения линии CS. Кроме того, схема 50 управления обеспечивает схему 20 возбуждения линии шины истоков, схему 30 возбуждения линии затворов и схему 40 возбуждения линии шины CS различными сигналами, которые необходимы для возбуждения жидкокристаллической панели 10 отображения.

В настоящем варианте осуществления во время активного периода (эффективного периода сканирования) в вертикальном периоде сканирования, который периодически повторяется, каждая строка выделяется периоду горизонтального сканированию одна за другой и сканируются одна за другой. С этой целью, при синхронизации с периодом горизонтального сканирования в каждой строке, схема 30 возбуждения линии затворов последовательно выводит сигнал затворов для включения ТПТ 13 в линию 12 затворов в этой строке. Ниже будет подробно описана схема 30 возбуждения линии затворов.

Схема 20 возбуждения линии шины истоков выводит сигнал истоков в каждую линию 11 шины истоков. Этот сигнал истоков получается с помощью схемы 20 возбуждения линии шины истоков, которая принимает видеосигнал вне жидкокристаллического устройства 1 отображения через схему 50 управления, выделяет видеосигнал каждому столбцу и выполняет усиление видеосигнала или т.п.

Кроме того, например, для того чтобы выполнить инверсное возбуждение линии, схема 20 возбуждения линии шины истоков выполнена так, чтобы полярность ее выходных сигналов истоков была идентичной для всех пикселей в идентичной строке и изменялась на обратную в каждых соседних n (где n - натуральное число) строках. Например, как показано на фиг.3, период горизонтального сканирования в первой строке и период горизонтального сканирования во второй строке являются обратными по полярности сигнала S истоков (однолинейное инверсное возбуждение (1Н)). Следует отметить, что схема 20 возбуждения линии шины истоков в настоящем варианте осуществления не ограничивается инверсным возбуждением линии, но можно выполнить инверсное возбуждение кадра.

Схема 40 возбуждения линии шины CS выводит CS-сигнал, соответствующий сигналу шины накопительных конденсаторов настоящего изобретения, в каждую линию 15 шины CS. Этот CS-сигнал является сигналом, чей потенциал переключается (повышается или падает) между двумя значениями (высоким и низким потенциалами). Ниже будет подробно описана схема 40 возбуждения линии шины CS.

Схема 50 управления управляет схемой 30 возбуждения линии затворов, схемой 20 возбуждения линии шины истоков и схемы 40 возбуждения линии шины CS, таким образом, побуждая каждую из них выводить сигналы так, как показано на фиг.3. Хотя на фиг.1 схема 30 возбуждения линии затворов и схема 40 возбуждения линии шины CS расположены на одной стороне жидкокристаллической панели 10 отображения, это не предполагает какого-либо ограничения. Схема 30 возбуждения линии затворов и схема 40 возбуждения линии шины CS могут располагаться на различных сторонах жидкокристаллической панели 10 отображения. Такая образцовая конфигурация будет описана ниже (в варианте 2 осуществления).

В настоящем варианте осуществления, следует уделить внимание особенностям схемы 30 возбуждения линии затворов и схеме 40 возбуждения линии шины CS из числа тех элементов, которые образуют жидкокристаллическое устройство 1 отображения. Далее следует подробное описание схемы 30 возбуждения линии затворов и схемы 40 возбуждения линии шины CS. Хотя ниже приведено описание жидкокристаллического устройства отображения, которое выполняет возбуждение зарядовой связи (СС), жидкокристаллическое устройство отображения настоящего изобретения не ограничивается возбуждением СС.

Вариант 1 осуществления

Фиг.3 изображает временные диаграммы, показывающие формы различных сигналов в жидкокристаллическом устройстве 1 отображения, согласно варианту 1 осуществления. В варианте 1 осуществления в качестве примера описан случай, где выполняется однолинейное инверсное возбуждение (1Н). На фиг.3 GSP представляет собой исходный импульсный сигнал затворов, который определяет тактирование вертикального сканирования, и GCK1 (СК) и GCK2 (СКВ) представляют собой тактовые сигналы затворов, которые выводятся из схемы управления для определения тактирования работы сдвигового регистра. Период от заднего фронта до следующего заднего фронта в GCP соответствует одному периоду вертикального сканирования (период IV). Каждыйп период от переднего фронта в GCK.1 до переднего фронта в GCK2 и период от переднего фронта в GCK2 до переднего фронта в GCK1 соответствуют одному периоду горизонтального сканирования (периоду 1Н). Сигнал начальной установки (CMI) представляет собой сигнал полярности, который изменяет свою полярность на обратную каждый один период горизонтального сканирования.

Кроме того, на фиг.3 показаны следующие сигналы в следующем порядке: сигнал S истоков (видеосигнал), который подается из схемы 20 возбуждения линии шины истоков в линию 11 шины истоков (линию 11 шины истоков, выполненную в х-ом столбце); сигнал G1 затворов, который подается из схемы 30 возбуждения линии затворов в линию 12 затворов, выполненную в первой строке; CS-сигнал CS1 (CSOUT1), который подается из схемы 40 возбуждения линии шины CS в линию 15 шины CS, выполненную в первой строке; и форма потенциала Vpix1 пиксельного электрода 14, выполненного в первой строке и х-ом столбце. Кроме того, фиг.3 показывает следующие сигналы в предложенном порядке: сигнал G2 затворов, который подается в линию 12 затворов, выполненную во второй строке; CS-сигнал CS2 (CSOUT2), который подается в линию 15 шины CS, выполненную во второй строке; и форма потенциала Vpix2 пиксельного электрода 14, выполненного во второй строке и х-ом столбце. Более того, на фиг.3 показаны следующие сигналы в предложенном порядке: сигнал G3 затворов, который подается в линию 12 затворов, выполненную в третьей строке; CS-сигнал CS3 (CSOUT3), который подается в линию 15 шины CS, выполненную в третьей строке; и форма потенциала Vpix3 пиксельного электрода 14, выполненного в третьей строке и х-ом столбце.

Следует отметить, что пунктирные линии в потенциалах Vpix1, Vpix2 и Vpix3 показывают потенциал противоэлектрода 19.

Далее предполагается, что исходный кадр картинки отображения представляет собой первый кадр, и что первому кадру предшествует начальное состояние (начальный период). В варианте 1 осуществления, как показано на фиг.3, во время начального состояния после включения питания (то есть, во время периода от конца прохождения предопределенного периода времени после включения питания до начала исходного кадра (первого кадра) картинки отображения), все CS-сигналы CS1, CS2 и CS3 имеют один фиксированный потенциал (на фиг.3 низкий уровень). В первом кадре, CS-сигнал CS1 в первой строке и CS-сигнал CS3 в третьей строке переключаются с низкого уровня на высокий уровень при синхронизации по передним фронтам в своих соответствующих сигналах G1 и G3 затворов, соответственно, и имеют высокий уровень в моменты времени, где сигналы G1 и G3 затворов падают. Поэтому потенциал CS-сигнала в каждой строке в момент времени, где его соответствующий сигнал затворов падает, отличается от потенциала CS-сигнала в соседней строке в момент времени, где его соответствующий сигнал затворов падает. Например, CS-сигнал CS1 имеет высокий уровень в момент времени, где его соответствующий сигнал G1 затворов падает, и CS-сигнал CS2 имеет высокий уровень в момент времени, где его соответствующий сигнал G2 затворов падает, и CS-сигнал CS3 имеет высокий уровень в момент времени, где его соответствующий сигнал G3 затворов падает.

Следует отметить, что сигнал S истоков представляет собой сигнал, который имеет амплитуду, соответствующую шкале серого цвета, представленной видеосигналом, и который изменяет свою полярность на обратную каждый период 1Н. Кроме того, так как предполагается на фиг.3, что отображается равномерная картинка, амплитуда сигнала S истоков является постоянной. Между тем, сигналы G1, G2 и G3 затворов служат в качестве потенциалов затворов для включения транзисторов во время первого, второго и третьего периодов 1Н, соответственно, в активном периоде (эффективном периоде сканирования) каждого кадра, и служат в качестве потенциалов затворов для выключения транзисторов во время других периодов.

Затем CS-сигналы CS1, CS2 и CS3 изменяют свою полярность на обратную после того, как их соответствующие сигналы G1, G2 и G3 затворов падают, и принимают такие формы сигналов, что соседние строки являются обратными по направлению изменения друг к другу. Более конкретно, в кадре с нечетным номером (первом кадре, третьем кадре, …) CS-сигналы CS1 и CS3 падают после того, как их соответствующие сигналы G1 и G3 затворов падают, и CS-сигнал CS2 повышается после того, как его соответствующий сигнал G2 затворов падает. Кроме того, в кадре с четным номером (втором кадре, четвертом кадре, …) CS-сигналы CS1 и CS3 повышаются после того, как их соответствующие сигналы G1 и G3 затворов падают, и CS-сигнал CS2 падает после того, как падает его соответствующий сигнал G2 затворов.

Следует отметить, что соотношение между передним и задним фронтами в CS-сигналах CS1, CS2 и CS3 в кадрах с нечетными и четными номерами может быть обратным по отношению к соотношению, изложенному выше.

Поскольку на фиг.3 соседние строки отличаются друг от друга, исходя из потенциалов CS-сигналов в моменты времени, где падают сигналы затворов в первом кадре, CS-сигналы CS1, CS2 и CS3 в первом кадре принимают те же самые формы сигналов, как и в нормальном кадре с нечетным номером (например, в третьем кадре). Поэтому, так как все потенциалы Vpix1, Vpix2 и Vpix3 пиксельных электродов 14 изменяются правильно с помощью CS-сигналов CS1, CS2 и CS3, соответственно, подача сигналов S истоков той же самой шкалы серого цвета вызывает положительную и отрицательную разности потенциалов между потенциалом противоэлектрода и измененным потенциалом каждого из пиксельных электродов 14, чтобы быть равными друг другу. То есть, в первом кадре, в котором сигнал истоков отрицательной полярности записывается в пикселе с нечетными номерами в том же самом столбце пикселей, и сигнал истоков положительной полярности записывается в пикселе с четными номерами в том же самом столбце пикселей, потенциалы CS-сигналов, соответствующие пикселям с нечетными номерами не изменяют свою полярность во время записи в пикселе с нечетными номерами, изменяют свою полярность в отрицательном направлении после записи, и не изменяют свою полярность до следующей записи, и потенциалы CS-сигналов, соответствующие пикселям с четными номерами не изменяют свою полярность во время записи в пиксели с четными номерами, изменяют свою полярность в положительном направлении после записи, и не изменяют свою полярность до следующей записи.

Это возбуждение позволяет зафиксировать потенциал каждого CS-сигнала в начальном состоянии, которое будет зафиксировано на одной стороне (который имеет низкий уровень или высокий уровень), таким образом, позволяя устранить недостаток отображения в начальный период времени. Кроме того, в первом кадре и более позднем кадре потенциал каждого пиксельного электрода может изменяться правильным образом.

Специфическая конфигурация схемы 40 возбуждения линии шины CS для выполнения вышеупомянутого управления описана ниже. На фиг.4 показана конфигурация схемы 30 возбуждения линии затворов и схемы 40 возбуждения линии шины CS. Далее для удобства объяснения строка (линия) (следующая строка), следующая после n-ой строки в направлении сканирования (на фиг.4 показано стрелкой) представлена в виде (n+1)-ой строки, и строка (предыдущая строка), непосредственно предшествующая n-ой строке в направлении сканирования, представлена в виде (n-1)-ой строки.

Как показано на фиг.4, схема 30 возбуждения линии затворов имеет множество схем SR сдвиговых регистров, соответствующих их соответствующим строкам, и схема 40 возбуждения линии шины CS имеет множество схем удержания (схем защелок, запоминающих схем) CSL, соответствующих их соответствующим строкам. Для удобства объяснения, схемы SRn-1, SRn и SRn+1 сдвиговых регистров и схемы CSLn-1, CSLn и CSLn+1 защелок, которые соответствуют (n-1)-ой, n-ой и (n+1)-ой строкам, соответственно, выбраны здесь в качестве примера.

Схема SRn-1 сдвигового регистра в (n-1)-ой строке принимает тактовый сигнал GCK1 затворов через свой тактовый вывод СК из схемы 50 управления (см. фиг.1) и принимает выходной сигнал SRBOn-2 сдвигового регистра из предыдущей строки ((n-2)-ой строки) через свой входной вывод SB в качестве сигнала установки для схемы SRn-1 сдвигового регистра. Схема SRn-1 сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к входному выводу SB, схема SRn сдвигового регистра следующей строки (n-ой строки). Это позволяет схеме SRn-1 сдвигового регистра выводить выходной сигнал SRBOn-1 сдвигового регистра через свой выходной вывод OUTB в схему SRn сдвигового регистра. Схема SRn-1 сдвигового регистра имеет свой выходной вывод М, подсоединенный к тактовому выводу СК схемы CSLn-1 защелки текущей строки ((n-1)-ой строки). Это позволяет схеме SRn-1 сдвигового регистра вводить сигнал CSRn-1 внутри ее (внутренний сигнал Mn-1) (сигнал управления) в схему CSLn-1 защелки.

Кроме того, выходной сигнал SRBOn-2 сдвигового регистра из предыдущей строки ((n-2)-ой строки) вводится в схему SRn-1 сдвигового регистра и выводится в качестве сигнала Gn-1 затворов (SRBOn-2: сигнал обратной полярности SRBOn-2) в линию 12 затворов текущей строки ((n-1)-ой строки) через буфер. Кроме того, напряжение питания (VDD) подается в схему SRn-1 сдвигового регистра.

Схема CSLn-1 защелки в (n-1)-ой строке принимает сигнал CMI полярности из схемы 50 управления (см. фиг.1) и внутренний сигнал Mn-1 (сигнал CSRn-1) из схемы SRn-1 сдвигового регистра. Схема CSLn-1 защелки имеет выходной вывод OUT, подсоединенный к линии 15 шины CS текущей строки ((n-1)-ой строки). Это позволяет схеме CSLn-1 защелки выводить CS-сигнал CSOUTn-1 через свой выходной вывод OUT в линию 15 шины CS текущей строки.

Схема SRn сдвигового регистра в n-ой строке принимает тактовый сигнал GCK2 затворов через свой тактовый вывод СК из схемы 50 управления (см. фиг.1) и принимает выходной сигнал SRBOn-1 сдвигового регистра из предыдущей строки ((n-1)-ой строки) через свой входной вывод SB в качестве сигнала установки для схемы SRn сдвигового регистра. Схема SRn сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к входному выводу SB схемы SRn+1 сдвигового регистра следующей строки ((n+1)-ой строки). Это позволяет схеме SRn сдвигового регистра выводить выходной сигнал SRBOn сдвигового регистра через свой выходной вывод OUTB в схему SRn+1 сдвигового регистра. Схема SRn сдвигового регистра имеет свой выходной вывод М, подсоединенный к тактовому выводу СК схемы CSLn защелки текущий строки (n-ой строки). Это позволяет схеме SRn сдвигового регистра вводить внутренний сигнал Mn, выработанный внутри ее, (сигнал CSRn), в схему CSLn защелки.

Кроме того, выходной сигнал SRBOn-1 сдвигового регистра из предыдущей строки ((n-1)-ой строки) вводится в схему SRn сдвигового регистра и выводится в виде сигнала Gn затворов (SROn-1: сигнал обратной полярности SRBOn-1) в линию 12 затворов текущей строки (n-ой строки) через буфер. Кроме того, напряжение питания (VDD) подается в схему SRn сдвигового регистра.

Схема CSLn защелки в n-ой строке принимает сигнал CMI полярности из схемы 50 управления (см. фиг.1) и внутренний сигнал Мп (сигнал CSRn), выработанный внутри схемы SRn сдвигового регистра. Схема CSLn защелки имеет выходной вывод OUT, подсоединенный к линии 15 шины CS текущей строки (n-ой строки). Это позволяет схеме CSLn защелки выводить CS-сигнал CSOUTn через свой выходной вывод OUT в линию 15 шины CS текущей строки.

Схема SRn+1 сдвигового регистра в (n+1)-ой строке принимает тактовый сигнал GCK1 затворов через свой тактовый вывод СК из схемы 50 управления (см. фиг.1) и принимает выходной сигнал SRBOn сдвигового регистра из предыдущей строки (n-ой строки) через свой входной вывод SB в виде сигнала установки для схемы SRn+1 сдвигового регистра. Схема SRn+1 сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к входному выводу SB схемы SRn+2 сдвигового регистра следующей строки ((n+2)-ой строки). Это позволяет схеме SRn+1 сдвигового регистра выводить выходной сигнал SRBOn+1 сдвигового регистра через свой выходной вывод OUTB в схему SRn+2 сдвигового регистра. Схема SRn+1 сдвигового регистра имеет свой выходной вывод М, подсоединенный к тактовому выводу СК схемы CSLn+1 защелки текущий строки ((n+1)-ой) строки. Это позволяет схеме SRn+1 сдвигового регистра вводить внутренний сигнал Mn+1, выработанный внутри ее (сигнал CSRn+1), в схему CSLn+1 защелки.

Кроме того, выходной сигнал SRBOn сдвигового регистра из предыдущей строки (n-ой строки) вводится в схему SRn+1 сдвигового регистра и выводится в виде сигнала Gn+1 затворов (SROn: сигнал обратной полярности SRBOn) в линию 12 затворов текущей строки ((n+1)-ой строки) через буфер. Кроме того, напряжение питания (VDD) подается в схему SRn+1 сдвигового регистра.

Схема CSLn+1 защелки в (n+1)-ой строке принимает сигнал CMI полярности из схемы 50 управления (см. фиг.1) и внутренний сигнал Mn+1 (сигнал CSRn+1), выработанный внутри схемы SRn+1 сдвигового регистра. Схема CSLn+1 защелки имеет свой выходной вывод OUT, подсоединенный к линии 15 шины CS текущей строки ((n+1)-ой строки). Это позволяет схеме CSLn+1 защелки выводить CS-сигнал CSOUTn+1 через свой выходной вывод OUT в линию 15 шины CS текущей строки.

Ниже приводится объяснение работы каждой схемы SR сдвигового регистра. На фиг.5 подробно изображены SRn-1, SRn и SRn+1 сдвиговых регистров в (n-1)-ой, n-ой и (n+1)-ой строках. Следует отметить, что схема SR сдвигового регистра в каждой строке является идентичной по конфигурации схемам SRn-1, SRn и SRn+1 сдвиговых регистров. В следующем ниже объяснении внимание сосредоточено на схеме SRn сдвигового регистра n-ой строки.

Как показано на фиг5, схема SRn сдвигового регистра включает в себя триггерную схему RS-FF RS-типа, логическую схему И-НЕ и переключающие схемы SW1 и SW2. Триггерная схема RS-FF принимает выходной сигнал SRBOn-1 сдвигового регистра (OUTB) через свой входной вывод SB из предыдущей строки ((n-1)-ой строки) в виде сигнала установки, как описано выше. Схема И-НЕ имеет свой входной вывод, подсоединенный к выходному выводу QB триггерной схемы RS-FF, и свой второй входной вывод, подсоединенный к выходному выводу OUTB схемы SRn сдвигового регистра. Схема И-НЕ имеет свой выходной вывод М, подсоединенный к электродам управления аналоговых переключающих схем SW1 и SW2 и подсоединенный к тактовому выводу СК (см. фиг.4) схемы CSLn текущей строки (n-ой строки). Аналоговые переключающие схемы SW1 и SW2 принимают, из схемы И-НЕ, внутренний сигнал Mn (сигнал CSRn), который управляет каждой из аналоговых переключающих схем SW1 и SW2 так, чтобы она переключала между состояниями "Включено" и "Выключено". Аналоговая переключающая схема SW1 имеет первый проводящий электрод, в который вводится тактовый сигнал СКВ (GCK2) затворов, и второй проводящий электрод, подсоединенный к первому проводящему электроду аналоговой переключающей схемы SW2, и аналоговая переключающая схема SW2 имеет второй проводящий электрод, на который подается напряжение питания (VDD). Аналоговые переключающие схемы SW1 и SW2 подсоединены друг к другу в точке п подсоединения, подсоединенной к выходному выводу OUTB схемы SRn сдвигового регистра, первому входному выводу схемы И-НЕ и входному выводу RB триггерной схемы RS-FF текущей строки (n-ой строки). Схема SRn сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к входному выводу SB следующей строки ((n+1)-ой строки). Это позволяет выводить выходной сигнал SRBOn сдвигового регистра (OUTB) текущей строки (n-ой строки) в виде сигнала установки для схемы SRn+1 сдвигового регистра следующей строки ((n+1)-ой строки).

В приведенной ниже конфигурации выходной сигнал OUTB схемы SRn сдвигового регистра вводится в виде сигнала сброса в входной вывод RB триггерной схемы RS-FF; поэтому схема SRn сдвигового регистра функционирует в качестве самовосстанавливающегося RS-триггера.

Ниже, со ссылкой на фиг.6, описана специфическая работа схемы SRn сдвигового регистра.

Сначала, когда сигнал SB установки (SRBOn-1), который вводится в схему SRn сдвигового регистра, изменяется с высокого уровня на низкий уровень (становится активным), выходной сигнал QB из триггерной схемы RS-FF изменяется с высокого уровня на низкий уровень, и внутренний сигнал Mn, который представляет собой выходной сигнал из схемы И-Не, изменяется с низкого уровня на высокий уровень (t1). Когда внутренний сигнал Mn повысился до высокого уровня, включается аналоговая переключающая схема SW1, посредством чего тактовый сигнал СКВ подается в OUTB. Это увеличивает амплитуду выходного сигнала OUTB до высокого уровня. Во время периода времени, в котором выходной сигнал QB с низким уровнем и выходной сигнал OUTB с высоким уровнем подаются в схему И-НЕ (t1-t2), схема И-Не выводит внутренний сигнал Mn с высоким уровнем, посредством чего выходной сигнал OUTB повышается до высокого уровня. Когда сигнал SB установки увеличился до высокого уровня (t2), тактовый сигнал СКВ все еще остается на высоком уровне в этот момент времени. Поэтому триггерная схема RS-FF не сбрасывается, посредством чего выходной сигнал QB поддерживается на высоком уровне, и внутренний сигнал Mn и выходной сигнал OUTB поддерживаются на высоком уровне (t2-t3).

Затем, когда тактовый сигнал СКВ упал до низкого уровня (t3), выходной сигнал OUTB падает до низкого уровня, и триггерная схема RS-FF сбрасывается, посредством чего выходной сигнал QB изменяется с низкого уровня на высокий уровень. Поскольку выходной сигнал QB с высоким уровнем и выходной сигнал OUTB с низким уровнем вводятся в схему И-НЕ, внутренний сигнал Mn поддерживается на высоком уровне, и выходной сигнал OUTB поддерживается на низком уровне (t3-t4). Когда тактовый сигнал СКВ изменяется с низкого уровня на высокий уровень (t4), выходной сигнал OUTB увеличивается до высокого уровня, и выходной сигнал QB с высоким уровнем и выходной сигнал OUTB с высоким уровнем подаются в схему И-НЕ так, чтобы внутренний сигнал Mn изменился с высокого уровня до низкого уровня.

Выходной сигнал OUTB, выработанный таким образом, позволяет схеме SRn+1 сдвигового регистра в следующей строке ((n+1)-ой строке) начать работу и схеме SRn сдвигового регистра в текущей строке (n-ой строке) выполнить операцию сброса.

Следует отметить здесь, что внутренний сигнал Mn, который вырабатывается внутри схемы SRn сдвигового регистра, становится активным в период времени с момента времени, где сигнал SB установки становится активным в момент времени, где сигнал RB (СКВ) сброса становится активным. Более того, внутренний сигнал Mn вводится в тактовый вывод СК схемы CSLn защелки в текущей строке (n-ой строке) (сигнал CSRn на фиг.4).

Ниже приведено подробное объяснение работы каждой схемы CSL защелки. На фиг.7 подробно изображена схема CSLn защелки в n-ой строке. Следует отметить, что схема CSL защелки в каждой строке является идентичной по конфигурации схеме CSLn. Следующее ниже объяснение относится к схеме CSL защелки в каждой строке в качестве схемы CSLn защелки.

Схема CSLn защелки принимает внутренний сигнал Mn (сигнал CSRn) через свой тактовый вывод СК (см. фиг.4) из схемы SRn сдвигового регистра, как описано выше. Схема CSLn защелки принимает сигнал CMI полярности через свой входной вывод D из схемы 50 управления (см. фиг.1). Это позволяет схеме CSLn защелки выводить входное состояние сигнала CMI полярности в качестве CS-сигнала CSOUTn в соответствии с изменением уровня потенциала внутреннего сигнала Mn (с низкого уровня на высокий уровень или с высокого уровня на низкий уровень), и CS-сигнал CSOUTn показывает изменение уровня потенциала. Более конкретно, когда уровень потенциала внутреннего сигнала Mn, который схема CSLn защелки принимает через свой тактовый вывод СК, имеет высокий уровень, схема CSLn защелки выводит входное состояние (низкий уровень или высокий уровень) сигнала CMI полярности, который она получает через свой входной вывод D. Когда уровень потенциала внутреннего сигнала Mn, который схема CSLn защелки принимает через свой тактовый вывод СК, изменилась с высокого уровня на низкий уровень, схема CSLn защелки фиксирует входное состояние (низкий уровень или высокий уровень) сигнала CMI полярности, который она получает через свой входной вывод D во время изменения, и сохраняет фиксированное состояние до следующего момента времени, когда уровень потенциала внутреннего сигнала Mn, который схема CSLn защелки принимает через свой тактовый вывод СК, повышается до высокого уровня. Затем, схема CSLn защелки выводит фиксированное состояние в качестве CS-сигнала CSOUTn, который показывает изменение уровня потенциала через свой выходной вывод OUT.

Следует отметить, что схему CSLn защелки, в частности, можно конкретно выполнить, например, с помощью конфигурации, показанной на схеме фиг.8. Как показано на фиг.8, схема CSLn защелки выполнена с возможностью включать в себя сквозную схему 4а защелки и буфер 4b. Сквозная схема 4а защелки образована с помощью четырех транзисторов, двух аналоговых переключающих схем SW11 и SW12 и одного инвертора, и буфер 4b образован с помощью двух транзисторов.

Относительно начальной работы

Фиг.9 изображает временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схем SR сдвиговых регистров и схем CSL защелок D. На фиг.9 показаны формы сигналов во время начальной работы после включения жидкокристаллического устройства 1 отображения, работа в первом периоде вертикального сканирования (первом кадре) картинки отображения и работа в следующем периоде вертикального сканирования (втором кадре). Пояснение начальной работы приведено ниже.

В начальном состоянии (начальном периоде) после включения жидкокристаллического устройства 1 отображения, тактовые сигналы GCK1B и GCK2B и сигнал CMI полярности устанавливаются на низкий уровень. Более конкретно, после включения жидкокристаллического устройства 1 отображения схема 50 управления (см. фиг.1) выводит сигналы управления, такие как GSPB, в соответствии с которыми GCK1B, GCK2B и CMI выводятся с низким уровнем. В то же самое время, GSPB вводится в схему SRO сдвигового регистра первого каскада (нулевая строка).

Следует отметить здесь, что, как показано на фиг.5, схема SRn сдвигового регистра выводит СКВ или Vdd в соответствии с внутренним сигналом Mn, который управляет аналоговыми переключающими схемами SW1 и SW2. То есть, когда внутренний сигнал Mn является активным (с высоким уровнем), аналоговая переключающая схема SW1 включается так, чтобы СКВ продолжал выводиться. Более того, когда сигнал SB установки, который выводится в схему SRn сдвигового регистра, является активным, внутренний сигнал Mn поддерживается в активном состоянии. Поэтому, когда активный сигнал вводится в схему SRn сдвигового регистра, внутренний сигнал Mn становится активным, и СКВ продолжает выводиться. Поскольку в начальном состоянии СКВ устанавливается на низкий уровень, сигнал низкого уровня выводится в случае, когда активный сигнал вводится в схему SRn сдвигового регистра.

В случае этой конфигурации, в то же самое время, когда GSPB вводится в схему SRO сдвигового регистра первого каскада, сигнал низкого уровня вводится в каждую схему SR сдвигового регистра, и внутренний сигнал М и выходной сигнал OUTB (SRBO) становятся активными. Следует отметить, что внутренняя задержка в сигнальных шинах или т.п. опущена ради удобства.

В начальном состоянии, как описано выше, схема SR сдвигового регистра в каждом каскаде выводит тактовый сигнал СКВ с низким уровнем. Следует отметить, что тактовый сигнал СКВ, который выводится с низким уровнем из схемы SR сдвигового регистра в каждом каскаде, подается в соответствующую линию GL затворов через буфер (см. фиг.4), посредством чего все линии GL затворов становятся активными. Например, в этом случае, подавая потенциал Vcom противоэлектрода на каждую линию истоков, потенциалы всех пиксельных электродов в начальном состоянии можно зафиксировать на Vcom.

Во время вышеупомянутой работы, внутренний сигнал Mn из схемы SRn сдвигового регистра вводится в схему CSLn защелки, показанную на фиг.8. Когда сквозная схема 4а защелки, которая образует схему CSLn защелки, принимает активный (с высоким уровнем) внутренний сигнал Mn через свой тактовый вывод СК, аналоговая переключающая схема SW11 включается, и сигнал CMI полярности (с низким уровнем), который подается на входной вывод D, вводится в транзистор Tr1 так, чтобы транзистор Tr1 включился, посредством чего сигнал LABOn выводится с высоким уровнем (Vdd) (см. фиг.9). Когда сигнал LABOn, который выводится из сквозной схемы 4а защелки, вводится в буфер 4b, транзистор Tr2 включается, посредством чего сигнал CSOUTn выводится с низким уровнем (Vss) (см. фиг.9).

Когда сквозная схема 4а защелки принимает неактивный (с низким уровнем) внутренний сигнал Mn через свой тактовый вывод СК, аналоговая переключающая схема SW11 выключается, и аналоговая переключающая схема SW12 включается. Это побуждает аналоговую переключающую схему SW11 зафиксировать сигнал CMI полярности (с низким уровнем) в момент времени, где она включилась, посредством чего сигнал CSOUTn выводится с низким уровнем (Vss) (см. фиг.9).

В схеме CSLn защелки, как описано выше, выходной сигнал CSOUTn переключается по потенциалу в соответствии с изменением потенциала сигнала CMI полярности, когда активный сигнал подается из схемы SRn сдвигового регистра. Поэтому, поскольку в начальном состоянии сигнал CMI полярности устанавливается на низкий уровень, выходной сигнал CSOUTn, подаваемый из схемы CSLn защелки в каждой строке, фиксируется на низком уровне. Следует отметить, что в случае, где схема 50 управления (см. фиг.1) устанавливается для вывода сигнала CMI полярности с высоким уровнем, выходной сигнал CSOUTn, выводимый из схемы CSLn защелки в каждой строке, фиксируется на высоком уровне. Это устраняет неопределенное состояние (показанное на фиг.9 заштрихованными областями) сразу после включения питания, и в начале исходного кадра (первого кадра) картинки отображения, потенциал каждого сигнала CS можно фиксировать на одной стороне (низкий уровень в примере, показанном на фиг.9). Это позволяет устранить недостаток отображения после включения питания и перед началом первого кадра.

Относительно работы в первом и втором кадрах

Ниже приведено объяснение работы в первом и втором кадрах. Ниже приводится пояснение работы в основном схемы SRn сдвигового регистра и схемы CSLn защелки в n-ой строке.

Фиг.10 изображает временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схемы CSLn защелки. Фиг.10 показывает, в качестве примера, временные диаграммы в схеме CSL1 защелки в первой строке и схеме CSL2 защелки во второй строке.

Сначала описаны изменения формы различных сигналов в первой строке.

В начальном состоянии, как описано выше, потенциал CS-сигнала CSOUT1, который схема CSL1 защелки выводит через свой выходной вывод OUT, поддерживается на низком уровне.

Когда в первом кадре схема 30 возбуждения линии затворов подает сигнал G1 затворов в линию 12 затворов в первой строке, сквозная схема 4а защелки принимает внутренний сигнал M1 (сигнал CSR1) через свой тактовый вывод СК из схемы SR1 сдвигового регистра. После приема изменения потенциала внутреннего сигнала M1 (с низкого уровня на высокий; t11), сквозная схема 4а защелки передает входное состояние сигнала CMI полярности, который она получает через свой входной вывод D в этот момент времени, то есть, передает высокий уровень и выводит изменения в потенциале сигнала CMI полярности до следующего момента времени, когда происходит изменение потенциала внутреннего сигнала M1 (с высокого уровня на низкий; t13), который сквозная схема 4а защелки принимает через свой тактовый вывод СК (то есть, во время периода времени, в котором внутренний сигнал M1 находится на высоком уровне; t11-t13). Когда сигнал CMI полярности изменяется с высокого уровня на низкий уровень во время периода времени, в котором внутренний сигнал M1 находится на высоком уровне t12, сквозная схема 4а защелки переключает свой выход LAB01 с низкого уровня на высокий уровень. Затем после получения изменения потенциала внутреннего сигнала M1 (с высокого уровня на низкий; t13) через свой тактовый вывод СК, сквозная схема 4а защелки фиксирует входное состояние сигнала CMI полярности, который она получает в этот момент времени, то есть, фиксирует низкий уровень. После этого, сквозная схема 4а защелки сохраняет свой входной сигнал LABO1 на высоком уровне до тех пор, пока не произойдет изменение потенциала внутреннего сигнала M1 во втором кадре (с низкого уровня на высокий; t14). Сквозная схема 4а защелки посылает свой входной сигнал LABO1 в буфер 4b, посредством чего схема CSL1 защелки выводит сигнал CSOUT1, показанный на фиг.10 через свой выходной вывод OUT.

Когда во втором кадре схема 30 возбуждения линии затворов аналогичным образом подает сигнал G1 затворов в линию 12 затворов в первой строке, сквозная схема 4а защелки принимает внутренний сигнал M1 (сигнал CSR1) через свой тактовый вывод СК из схемы SR1 сдвигового регистра. Когда внутренний сигнал M1 изменяется с низкого уровня на высокий уровень (t14), сквозная схема 4а защелки передает входное состояние сигнала CMI полярности, который она получает через свой входной вывод D в этот момент времени, то есть, передает низкий уровень. Сквозная схема 4а защелки выводит изменение потенциала сигнала CMI полярности во время периода времени, в котором внутренний сигнал M1 находится на высоком уровне (t14-t16). Поэтому, когда сигнал CMI полярности изменяется с низкого уровня на высокий уровень (t15), сквозная схема 4а защелки переключает свой выходной сигнал LABO1 с высокого уровня на низкий уровень. Затем, после получения изменения потенциала внутреннего сигнала M1 (с высокого уровня на низкий; t16) через свой тактовый вывод СК, сквозная схема 4а защелки фиксирует входное состояние сигнала CMI полярности, который она получает в этот момент времени, то есть, фиксирует высокий уровень. После этого, сквозная схема 4а защелки сохраняет свой входной сигнал LABO1 на низком уровне до тех пор, пока не произойдет изменение потенциала внутреннего сигнала M1 в третьем кадре. Сквозная схема 4а защелки посылает свой выходной сигнал LABO1 в буфер 4b, посредством чего схема CSL1 защелки выводит CSOUT1, показанный на фиг.10, через свой выходной вывод OUT.

CS-сигнал CSOUT1, выработанный таким образом, подается в линию 15 шины CS первой строки. Следует отметить, что выходной сигнал в третьем кадре принимает форму сигнала, полученную путем изменения полярности уровня потенциала выходной формы сигнала во втором кадре, и в четвертом кадре и более позднем кадре поочередно выводятся сигналы, идентичные по форме выходного сигнала сигналам во втором и третьем кадрах.

Далее, описаны изменения формы различных сигналов во второй строке.

В начальном состоянии, как и в первой строке, потенциал CS-сигнала CSOUT2, который схема CSL2 защелки выводит через свой выходной вывод OUT, удерживается на низком уровне.

Когда в первом кадре схема 30 возбуждения линии затворов подает сигнал G2 затворов в линию 12 затворов во второй строке, сквозная схема 4а защелки принимает внутренний сигнал М2 (сигнал CSR2) через свой тактовый вывод СК из схемы SR2 сдвигового регистра. После получения изменения потенциала внутреннего сигнала М2 (с низкого уровня на высокий; t21), сквозная схема 4а защелки передает входное состояние сигнала СМ1 полярности, который она получает через свой входной вывод D в этот момент времени, то есть, передает низкий уровень и выводит изменение потенциала сигнала СМ1 полярности до следующего момента времени, когда произойдет изменение потенциала внутреннего сигнала М2 (с высокого уровня на низкий уровень; t23), который сквозная схема 4а защелки принимает через свой тактовый вывод СК (то есть, во время периода времени, в котором внутренний сигнал М2 находится на высоком уровне; t21-t23). Когда сигнал СМ1 полярности изменяется с низкого уровня на высокий уровень во время периода времени, в котором внутренний сигнал М2 находится на высоком уровне (t22), сквозная схема 4а защелки переключает свой выходной сигнал LABO2 с высокого уровня на низкий уровень. Затем после получения изменения потенциала внутреннего сигнала М2 (с высокого уровня на низкий; t23) через свой тактовый вывод СК, сквозная схема 4а защелки фиксирует входное состояние сигнала СМ1 полярности, который она получает в этот момент времени, то есть, фиксирует высокий уровень. После этого, сквозная схема 4а защелки поддерживает свой выходной сигнал LABO2 на низком уровне до тех пор, пока не произойдет изменение потенциала внутреннего сигнала М2 во втором кадре (с низкого уровня на высокий; t24). Сквозная схема 4а защелки посылает свой выходной сигнал LABO2 в буфер 4b, посредством чего схема CSL2 защелки выводит CSOUT2, показанный на фиг.10, через свой выходной вывод OUT.

Когда во втором кадре схема 30 возбуждения линии затворов аналогичным образом подает сигнал G2 затворов в линию 12 затворов во второй строке, сквозная схема 4а защелки принимает внутренний сигнал М2 (сигнал CSR2) через свой тактовый вывод СК из схемы SR2 сдвигового регистра. Когда внутренний сигнал М2 изменяется с низкого уровня на высокий уровень (t24), сквозная схема 4а защелки передает входное состояние сигнала СМ1 полярности, который она получает через свой входной вывод D в этот момент времени, то есть, передает высокий уровень. Сквозная схема 4а защелки выводит изменение потенциала сигнала СМ1 полярности во время периода времени, в котором внутренний сигнал М2 остается на высоком уровне (t24-t26). Поэтому, когда сигнал СМ1 полярности изменяется с высокого уровня на низкий уровень (t25), сквозная схема 4а защелки переключает свой выход LABO2 с низкого уровня на высокий уровень. Затем, после получения изменения потенциала внутреннего сигнала М2 (с высокого уровня на низкий; t26) через свой тактовый вывод СК, сквозная схема 4а защелки фиксирует входное состояние сигнала СМ1 полярности, который она получает в этот момент времени, то есть, фиксирует низкий уровень. После этого, сквозная схема 4а защелки поддерживает свой выход LABO2 на высоком уровне до тех пор, пока не произойдет изменение потенциала внутреннего сигнала М2 в третьем кадре. Сквозная схема 4а защелки посылает свой выходной сигнал LABO2 в буфер 4b, посредством чего схема CSL2 защелки выводит CSOUT2, показанный на фиг.10, через свой выходной вывод OUT.

CS-сигнал CSOUT2, выработанный таким образом, подается в линию 15 шины CS второй строки. Следует отметить, что в третьем кадре и более позднем кадре поочередно выводятся сигналы, идентичные по форме выходного сигнала сигналам в первом и втором кадрах.

Более того, операции в первой и второй строках соответствуют операциям схем защелок в каждой строке с нечетным номером и в каждой строке с четным номером.

Таким образом, схемы CSL1, CSL2, CSL3, … защелок, которые соответствуют своим соответствующим строкам, выводят CS-сигналы так, чтобы во всех кадрах, которые включают в себя первый кадр, падали потенциалы CS-сигналов в моменты времени, где сигналы затворов в их соответствующих строках (в моменты времени, где ТПТ13 переключаются из включенного состояния в выключенное состояние) отличались от одной строки до соседней строки. Это позволяет схеме 40 возбуждения линии шины CS правильно работать во всех кадрах.

В настоящем жидкокристаллическом устройстве 1 отображения, как описано выше, сигнал (внутренний сигнал Mn), выработанный внутри схемы SRn сдвигового регистра, подается непосредственно в схему CSLn защелки той же самой строки (n-ой строки). Кроме того, когда внутренний сигнал М всегда остается активным (с высоким уровнем в приведенном выше примере) в начальном состоянии после включения питания, в первом кадре и более позднем кадре, внутренний сигнал М переключается по уровню потенциала в соответствии с тактовым сигналом, который подается в схему сдвигового регистра. После этого, в начальном состоянии, сигнал, который принимает схема CSLn защелки через свой входной вывод D, фиксируется с одним потенциалом (который имеет низкий уровень или высокий уровень), посредством чего выходной сигнал CSOUTn (CS-сигнал), подаваемый из схемы CSLn защелки, фиксируется на этом одном потенциале (который имеет низкий уровень или высокий уровень), и в первом кадре и более позднем кадре, потенциалы в моменты времени, где сигналы затворов в своих соответствующих строках падают, отличаются от одной строки до соседней строки. Это позволяет инициализировать линии шины CS во всех строках и работать схеме 40 возбуждения линии шины CS правильным образом.

Кроме того, изложенная выше конфигурация устраняет необходимость сигнальным линиям и схеме управления инициализировать шины накопительных конденсаторов (линии шины CS), как показано на фиг.25, и поэтому схему возбуждения устройства отображения можно выполнить с меньшей площадью схемы по сравнению с известной конфигурацией. Это позволяет реализовать маленькое жидкокристаллическое устройство отображения с высоким качеством отображения и жидкокристаллическую панель отображения с узким кадром.

Вариант 2 осуществления

Другой вариант осуществления настоящего изобретения описан ниже со ссылкой на фиг.11-15. Для удобства объяснения, те элементы, которые имеют одинаковые функции, как элементы, которые были описаны выше в варианте 1 осуществления, приведены с одинаковыми ссылочными позициями и не описываются ниже. Кроме того, термины, которые определены в варианте 1 осуществления, определены тем же самым способом в настоящем варианте осуществления, если они не отмечены иным способом.

Фиг.11 изображает временные диаграммы, показывающие формы различных сигналов в жидкокристаллическом устройстве 1 отображения, согласно варианту 2 осуществления. Вариант 2 осуществления описан на примере случая, где выполняется инверсное возбуждение кадров. Различные сигналы, показанные на фиг.11, являются теми же самыми, как и те, которые показаны на фиг.3, при этом GSP представляет собой начальный импульсный сигнал затворов, GCK1 (СК) и GCK2 (CКb) представляют собой тактовые сигналы затворов, CMI представляет собой сигнал полярности. Изображенные временные диаграммы в жидкокристаллическом устройстве 1 отображения, согласно варианту 2 осуществления, отличаются от временных диаграмм варианта 1 осуществления, исходя из тактирования изменений потенциала сигнала CMI полярности, и форм выходных сигналов CS-сигналов и идентичны временным диаграммам варианта 1 осуществления в других отношениях.

В варианте 2 осуществления, как показано на фиг.11, в начальном состоянии, все CS-сигналы, CS1, CS2 и CS3 фиксируются с одним потенциалом (на фиг.11 с низким уровнем). В первом кадре, CS-сигнал CS1 в первой строке, CS-сигнал CS2 во второй строке и CS-сигнал CS3 в третьей строке переключаются с низкого уровня на высокий уровень после падения их соответствующих сигналов G1, G2 и G3 затворов, соответственно. Во втором кадре, CS-сигнал CS1 в первой строке, CS-сигнал CS2 во второй строке и CS-сигнал CS3 в третьей строке переключаются с высокого уровня на низкий уровень после того, как падают их соответствующие сигналы G1, G2 и G3 затворов, соответственно.

Следует отметить, что сигнал S истоков представляет собой сигнал, который имеет амплитуду, соответствующую шкале серого цвета, представленную с помощью видеосигнала, который изменяет свою полярность на обратную каждый один кадр. Кроме того, так как на фиг.11 предполагается, что отображается равномерная картинка, амплитуда сигнала S истоков является постоянной. Затем, CS-сигналы CS1, CS2 и CS3 изменяют свою полярность на обратную после того, как падают их соответствующие сигналы G1, G2 и G3 затворов, и принимают такие формы сигналов, чтобы соседние строки были идентичными в направлении изменения друг к другу.

Таким образом, потенциалы CS-сигналов в моменты времени, где сигналы затворов падают в первом кадре, становятся отрицательной полярности, и потенциалы CS-сигналов в моменты времени, где сигналы затворов падают во втором кадре, становятся положительной полярности во всех строках. Поэтому, поскольку все потенциалы Vpix1, Vpix2 и Vpix3 пиксельных электродов 14 полностью изменяются с помощью CS-сигналов CS1, CS2 и CS3, соответственно, ввод сигналов S истоков с той же самой шкалой серого цвета вызывает положительную и отрицательную разности потенциалов между потенциалом противоэлектрода и измененным потенциалом каждого из пиксельных электродов 14, чтобы быть равными друг другу. В результате, возбуждение СС можно правильно реализовать при инверсном возбуждении кадров.

Специфическая конфигурация схемы 30 возбуждения линии затворов и схемы 40 возбуждения линии шины CS для выполнения вышеупомянутого управления описаны ниже. На фиг.12 показана конфигурация схемы 30 возбуждения линии затворов и схемы 40 возбуждения линии шины CS. Далее, для удобства объяснения, строка (линия) (следующая строка), следующая после n-ой строки в направлении сканирования (на фиг.4 показано стрелкой) представлена в виде (n+1)-ой строки, и строка (предыдущая строка), непосредственно предшествующая n-ой строке в направлении сканирования, представлена в виде (n-1)-ой строки.

Как показано на фиг.12, схема 30 возбуждения линии затворов имеет множество схем SR сдвиговых регистров, соответствующих своим соответствующим строкам, и схема 40 возбуждения линии шины CS имеет множество схем (схем защелок, запоминающих схем) CSL удержания, соответствующих своим соответствующим строкам. Схема 30 возбуждения линии затворов выполнена на одной стороне жидкокристаллической панели 10 отображения, и схема 40 возбуждения линии шины CS выполнена на другой стороне жидкокристаллической панели 10 отображения. Для удобства объяснения, схемы SRn-1, SRn и SRn+1 сдвиговых регистров и схемы CSLn-1, CSLn и CSLn+1 защелок, которые соответствуют (n-1)-ой, n-ой и (n+1)-ой строкам, соответственно, приведены здесь в качестве примера.

Схема SRn-1 сдвигового регистра в (n-11)-ой строке принимает тактовый сигнал GCK1 затворов через свой тактовый вывод СК из схемы управления (см. фиг.1) и принимает выходной сигнал SRBOn-2 сдвигового регистра из предыдущей строки ((n-2)-ой строки) через свой входной вывод SB в качестве сигнала установки для схемы SRn-1 сдвигового регистра. Схема SRn-1 сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к входному выводу SB схемы SRn сдвигового регистра следующей строки (n-ой строки). Это позволяет схеме SRn-1 сдвигового регистра выводить выходной сигнал SRBOn-1 сдвигового регистра через свой выходной вывод OUTB в схему SRn сдвигового регистра. Схема SRn-1 сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к тактовому выводу СК схемы CSLn-1 защелки текущей строки ((n-1)-ой строки) через буфер. Это позволяет схеме SRn-1 сдвигового регистра вводить свой выходной сигнал SRBOn-1 (который соответствует сигналу Gn затворов) в схему CSLn-1 защелки.

Кроме того, выходной сигнал SRBOn-2 сдвигового регистра, подаваемый из предыдущей строки ((n-2)-ой строки), вводится в схему SRn-1 сдвигового регистра и выводится в качестве сигнала Gn-1 затворов в линию 12 затворов текущей строки ((n-1)-ой строки) через буфер. Кроме того, напряжение питания (VDD) подается в схему SRn-1 сдвигового регистра.

Схема CSLn-1 защелки в (n-1)-ой строке принимает сигнал CMI полярности из схемы 50 управления (см. фиг.1) и сигнал Gn затворов. Схема CSLn-1 защелки имеет свой выходной вывод OUT, подсоединенный к линии 15 шины CS текущей строки ((n-1)-ой строки). Это позволяет схеме CSLn-1 защелки выводить CS-сигнал CSOUTn-1 через свой выходной вывод OUT в линию 15 шины CS текущей строки.

Схема SRn сдвигового регистра в n-ой строке принимает тактовый сигнал GCK2 затворов через свой тактовый вывод СК из схемы 50 управления (см. фиг.1) и принимает выходной сигнал SRBOn-1 сдвигового регистра из предыдущей строки ((n-1)-ой строки) через свой входной вывод SB в качестве сигнала установки для схемы SRn сдвигового регистра. Схема SRn сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к входному выводу SB схемы SRn+1 сдвигового регистра следующей строки ((n+1)-ой строки). Это позволяет схеме SRn сдвигового регистра выводить выходной сигнал SRBOn сдвигового регистра через свой выходной вывод OUTB в схему SRn+1 сдвигового регистра. Схема SRn сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к тактовому выводу СК схемы CSLn защелки текущей строки (n-ой строки) через буфер. Это позволяет схеме SRn сдвигового регистра вводить свой выходной сигнал SRBOn (который соответствует сигналу Gn+1 затворов) в схему CSLn защелки.

Кроме того, выходной сигнал SRBOn-1 сдвигового регистра из предыдущей строки ((n-1)-ой строки) вводится в схему SRn сдвигового регистра и выводится в качестве сигнала Gn затворов в линию 12 затворов текущей строки (n-ой строки) через буфер. Кроме того, напряжение питания (VDD) подается в схему SRn сдвигового регистра.

Схема CSLn защелки в n-ой строке принимает сигнал CMI полярности из схемы 50 управления (см. фиг.1) и сигнал Gn+1 затворов. Схема CSLn защелки имеет свой выходной вывод OUT, подсоединенный к линиям 15 шины CS текущей строки (n-ой строки). Это позволяет схеме CSLn защелки выводить CS-сигнал CSOUTn через свой выходной вывод OUT в линию 15 шины CS текущей строки.

Схема SRn+1 сдвигового регистра в (n+1)-ой строке принимает тактовый сигнал GCK1 затворов через свой тактовый вывод СК из схемы 50 управления (см. фиг.1) и принимает выходной сигнал SRBOn сдвигового регистра из предыдущей строки (n-ой строки) через свой входной вывод SB в качестве сигнала установки для схемы SRn+1 сдвигового регистра. Схема SRn+1 сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к входному выводу SB схемы SRn+1 сдвигового регистра следующей строки ((n+2)-ой строки). Это позволяет схеме SRn+1 сдвигового регистра выводить выходной сигнал SRBOn+1 сдвигового регистра через свой выходной вывод OUTB в схему SRn+2 сдвигового регистра. Схема SRn+1 сдвигового регистра имеет свой выходной вывод OUTB, подсоединенный к тактовому выводу СК схемы CSLn+1 защелки текущей строки ((n+1)-ой строки) через буфер. Это позволяет схеме SRn+1 сдвигового регистра вводить свой выходной сигнал SRBOn+1 (который соответствует сигналу Gn+2 затворов) в схему CSLn+1 защелки.

Кроме того, выходной сигнал SRBOn сдвигового регистра из предыдущей строки (n-ой строки) вводится в схему SRn+1 сдвигового регистра и выводится в качестве сигнала Gn+1 затворов в линию 12 затворов текущей строки ((n+1)-ой строки) через буфер. Кроме того, напряжение питания (VDD) подается в схему SRn+1 сдвигового регистра.

Схема CSLn+1 защелки в (n+1)-ой строке принимает сигнал CMI полярности из схемы 50 управления (см. фиг.1) и сигнал Gn+2 затворов. Схема CSLn+1 защелки имеет свой выходной вывод OUT, подсоединенный к линии 15 шины CS текущей строки ((n+1)-ой строки). Это позволяет схеме CSLn+1 защелки выводить CS-сигнал CSOUTn+1 через свой выходной вывод OUT в линию 15 шины CS текущей строки.

Каждая схема SR сдвигового регистра является идентичной по конфигурации схеме варианта 1 осуществления, показанной на фиг.5, и ее работа представлена с помощью форм сигналов, показанных на фиг.6. Описание каждой схемы SR сдвигового регистра здесь опущено.

Работа схемы каждой схемы CSL защелки описана ниже со ссылкой на фиг.13.

Схема CSLn защелки принимает сигнал Gn+1 затворов через свой тактовый вывод СК (см. фиг.12), как описано выше. Схема CSLn защелки принимает сигнал CMI полярности через свой входной вывод D из схемы 50 управления (см. фиг.1). Это позволяет схеме CSLn защелки выводить входное состояние сигнала CMI полярности в качестве CS-сигнала CSOUTn в соответствии с изменением уровня потенциала сигнала Gn+1 затворов (с низкого уровня на высокий уровень или с высокого уровня на низкий уровень), и CS-сигнал CSOUTn показывает изменение уровня потенциала. Более конкретно, когда уровень потенциала сигнала Gn+1 затворов, который схема CSLn защелки принимает через свой тактовый вывод СК, имеет высокий уровень, схема CSLn защелки выводит входное состояние (низкий уровень или высокий уровень) сигнала CMI полярности, который она получает через свой входной вывод D. Когда уровень потенциала сигнала Gn+1 затворов, который схема CSLn защелки принимает через свой тактовый вывод СК, изменяется с высокого уровня на низкий уровень, схема CSLn защелки фиксирует входное состояние (низкий уровень или высокий уровень) сигнала CMI полярности, который она получает через свой входной вывод D в момент изменения, и сохраняет фиксированное состояние до следующего момента времени, когда уровень потенциала сигнала Gn+1 затворов, который схема CSLn защелки принимает через свой тактовый вывод СК, повышается до высокого уровня. Затем, схема CSLn защелки выводит фиксированное состояние в качестве CS-сигнала CSOUTn, который показывает изменение уровня потенциала через свой выходной вывод OUT.

Следует отметить, что схему CSLn защелки можно, в частности, выполнить, например, с помощью конфигурации, показанной на схеме фиг.14. Как показано на фиг.14, схема CSLn защелки выполнена с возможностью включать в себя сквозную схему 4а защелки и буфер 4b. Сквозная схема 4а защелки образована с помощью четырех транзисторов, двух аналоговых переключающих схем SW11 и SW12 и одного инвертора, и буфер 4b образован с помощью двух транзисторов.

Относительно начальной работы

Фиг.15 изображает временные диаграммы, показывающие формы различных сигналов, которые вводятся в и выводятся из схем SR сдвиговых регистров и схем CSL защелок D. На фиг.15 показаны формы сигналов во время начальной работы после включения жидкокристаллического устройства 1 отображения, работа в первом периоде вертикального сканирования (первый кадр) картинки отображения, и работа в следующем периоде вертикального сканирования (второй кадр).

Объяснение начального этапа работы приведено ниже.

В начальном состоянии (начальный период) после включения жидкокристаллического устройства 1 отображения, тактовые сигналы GCK1B и GCK2B и сигнал CMI полярности устанавливаются на низкий уровень. Более конкретно, после включения жидкокристаллического устройства 1 отображения, схема 50 управления (см. фиг.1) выводит сигналы управления, такие как GSPB, в соответствии с которыми GCK1B, GCK2B и CMI выводятся с низким уровнем. В это же самое время сигнал GSPB подается в схему SRO сдвигового регистра первого каскада (нулевая строка).

Следует отметить здесь, что, как показано на фиг.5, схема SRn сдвигового регистра выводит СКВ или Vdd в соответствии с внутренним сигналом Mn, который управляет аналоговыми переключающими схемами SW1 и SW2. То есть, когда внутренний сигнал Mn является активным (с высоким уровнем), аналоговая переключающая схема SW1 включается так, чтобы поддерживать вывод СКВ. Более того, когда сигнал SB установки, который выводится в схему SRn сдвигового регистра, является активным, внутренний сигнал Mn поддерживается в активном состоянии (см. фиг.6). Поэтому, когда активный сигнал вводится в схему SRn сдвигового регистра, внутренний сигнал Mn становится активным, и СКВ продолжает выводиться. Поскольку в начальном состоянии СКВ устанавливается на низкий уровень, сигнал с низким уровнем выводится, когда активный сигнал вводится в схему SRn сдвигового регистра.

В случае этой конфигурации, в то же самое время, когда GSPB вводится в схему SRO сдвигового регистра первого каскада, сигнал низкого уровня вводится в каждую схему SR сдвигового регистра, и внутренний сигнал М и выходной сигнал OUTB (SRBO) становятся активными. Следует отметить, что внутренняя задержка в сигнальных шинах или т.п. опущена ради удобства.

В начальном состоянии, как описано выше, схема SR сдвигового регистра в каждом каскаде выводит тактовый сигнал СКВ с низким уровнем. Следует отметить, что тактовый сигнал СКВ, который выводится с низким уровнем из схемы SR сдвигового регистра в каждом каскаде, подается в соответствующую линию GL затворов через буфер (см. фиг.12), посредством чего все линии GL затворов становятся активными. Например, в этом случае за счет подачи потенциала Vcom противоэлектрода на каждую линию истоков, потенциал всех пиксельных электродов в начальном состоянии можно зафиксировать на Vcom.

Во время вышеупомянутой операции, сигнал (сигнал Gn+1 затворов), который выводится из схемы SRn сдвигового регистра через буфер, вводится в схему CSLn защелки, показанную на фиг.8. Когда сквозная схема 4а защелки, которая образует схему CSLn защелки, принимает активный (с высоким уровнем) сигнал Gn+1 затворов через свой тактовый вывод СК, включается аналоговая переключающая схема SW11, и сигнал CMI полярности (с низким уровнем), который вводится во входной вывод D, вводится в транзистор Tr1 так, что транзистор Tr1 включается, посредством чего сигнал LABOn выводится с высоким уровнем (Vdd) (см. фиг.15). Когда сигнал LABOn, который выводится из сквозной схемы 4а защелки, вводится в буфер 4b, транзистор Tr2 включается, посредством чего сигнал CSOUTn выводится с низким уровнем (Vss) (см. фиг.15).

Когда сквозная схема 4а защелки принимает неактивный (с низким уровнем) сигнал Gn+1 затворов через свой тактовый вывод СК, аналоговая переключающая схема SW11 выключается, и аналоговая переключающая схема SW12 включается. Это заставляет аналоговую переключающую схему SW11 фиксировать сигнал CMI полярности (на низком уровне) в момент времени, где он был выключен, посредством чего сигнал CSOUTn выводится с низким уровнем (Vss) (см. фиг.15).

В схеме CSLn защелки, как описано выше, выходной сигнал CSOUTn переключается по потенциалу в соответствии с изменением потенциала сигнала CMI полярности, когда активный сигнал вводится из схемы SRn сдвигового регистра. Поэтому, поскольку в начальном состоянии, сигнал CMI полярности устанавливается с низким уровнем, выходной сигнал CSOUTn из схемы CSLn защелки в каждой строке фиксируется с низком уровнем. Следует отметить, что в случае, где схема 50 управления (см. фиг.1) устанавливается для вывода сигнала CMI полярности с высоким уровнем, выходной сигнал CSOUTn, подаваемый из схемы CSLn защелки в каждой строке, фиксируется с высоким уровнем. Это устраняет неопределенное состояние (на фиг.15 показано заштрихованными областями) сразу после включения питания, и в начале исходного кадра (первого кадра) картинки отображения, потенциал каждого сигнала CS можно фиксировать на одной стороне (в примере, показанном на фиг.15 низкий уровень). Это позволяет устранить недостаток отображения после включения питания и перед началом первого кадра.

Относительно работы в первом и втором кадрах

Объяснение работы в первом и втором кадрах приведено ниже со ссылкой на фиг.15. Пояснение работы схемы SRn сдвигового регистра и схемы CSLn защелки в n-ой строке в основном приведено здесь.