Притязание на приоритет

Настоящая патентная заявка притязает на приоритет предварительной заявки №60/787,915 под названием "High Speed Media Access Control", поданной 31 марта 2006 г., права на которую принадлежат заявителю настоящей заявки и, таким образом, непосредственно включенной сюда посредством ссылки.

Область техники, к которой относится изобретение

Настоящее раскрытие относится, в целом, к беспроводной связи и к высокоскоростному управлению доступом к среде.

Уровень техники

Системы беспроводной связи широко используются для обеспечения различных типов связи, например, передачи голоса и данных. Типичная система или сеть беспроводной передачи данных обеспечивает множеству пользователей доступ к одному или нескольким ресурсам общего пользования. Система может использовать различные методы множественного доступа, например мультиплексирование с частотным разделением (FDM), мультиплексирование с временным разделением (TDM), мультиплексирование с кодовым разделением (CDM), мультиплексирование с ортогональным частотным разделением (OFDM) и др.

Примерные беспроводные сети включают в себя системы передачи данных на базе сотовых технологий. Ниже приведено несколько таких примеров: (1) "TIA/EIA-95-B Mobile Station-Base Station Compatibility Standard for Dual-Mode Wideband Spread Spectrum Cellular System" (стандарт IS-95), (2) стандарт, предложенный консорциумом под названием "3rd Generation Partnership Project" (3GPP) и воплощенный в пакете документов, включающем в себя документы №№3G TS 25.211, 3G TS 25.212, 3G TS 25.213 и 3G TS 25.214 (стандарт W-CDMA), (3) стандарт, предложенный консорциумом под названием "3rd Generation Partnership Project 2" (3GPP2) и реализованный как "TR-45.5 Physical Layer Standard for cdma2000 Spread Spectrum Systems" (стандарт IS-2000), и (4) система высокоскоростной передачи данных (HDR), отвечающая стандарту TIA/EIA/IS-856 (стандарт IS-856).

Другие примеры беспроводных систем включают в себя беспроводные локальные сети (WLAN), например, IEEE 802.11 (т.е. 802.11 (a), (b) или (g)). Эти сети допускают усовершенствования, которые достигаются с применением WLAN со многими входами и многими выходами (MIMO), содержащей методы модуляции мультиплексирования с ортогональным частотным разделением (OFDM). Стандарт IEEE 802.11(e) был введен для повышения качества обслуживания (QoS) по сравнению с предыдущими стандартами 802.11.

Сейчас вводятся спецификации 802.11(n), которые определяют высокоскоростные беспроводные сети и протоколы MAC для работы с ними. Предыдущие 802.11 стандарты связаны, в основном, с приложениями передачи данных, навигации и электронной почты. Стандарт 802.11(n) призван обслуживать приложения распространения мультимедиа, для которых требуется высокие пропускная способность, стабильность характеристик и качества обслуживания. Эти требования сопряжены с необходимостью в эффективных реализациях и методах обеспечения качества обслуживания и высокого быстродействия. Таким образом, в технике существует необходимость в эффективном высокоскоростном управлении доступом к среде.

Сущность изобретения

Раскрытые здесь аспекты удовлетворяют необходимость в эффективном высокоскоростном управлении доступом к среде.

Согласно одному аспекту, описано устройство, которое включает в себя первую структуру данных, ассоциированную с пакетом, вторую структуру данных, содержащую данные из ассоциированного пакета, и в котором первая структура данных содержит поле длины, указывающее длину ассоциированного пакета, поле порядкового номера, указывающее порядковый номер ассоциированного пакета, поле указателя второй структуры данных, указывающее местоположение второй структуры данных в буфере пакетов.

Согласно еще одному аспекту, описана первая структура данных, которая способна работать со второй структурой данных, содержащая данные из ассоциированного пакета, и которая включает в себя поле длины, указывающее длину ассоциированного пакета, поле порядкового номера, указывающее порядковый номер ассоциированного пакета, и поле указателя, в котором хранится местоположение второй структуры данных в памяти.

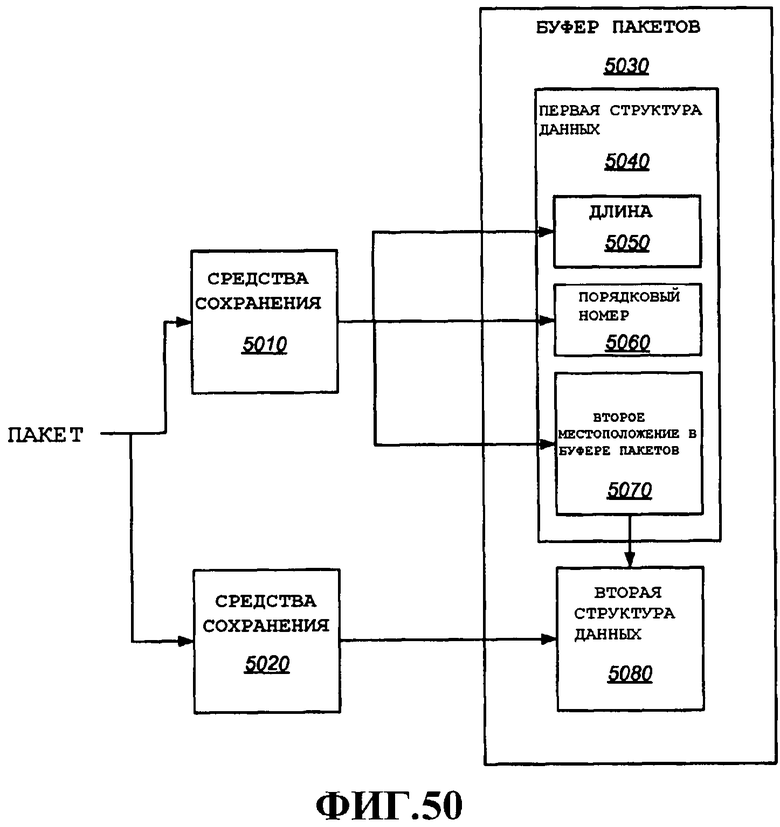

Согласно еще одному аспекту, раскрыт способ, содержащий этапы, на которых сохраняют в первой структуре данных в буфере пакетов длину первого пакета, порядковый номер пакета и второе местоположение в буфере пакетов второй структуры данных в буфере пакетов, и сохраняют данные из первого пакета во второй структуре данных, идентифицируемой сохраненным вторым местоположением в буфере пакетов.

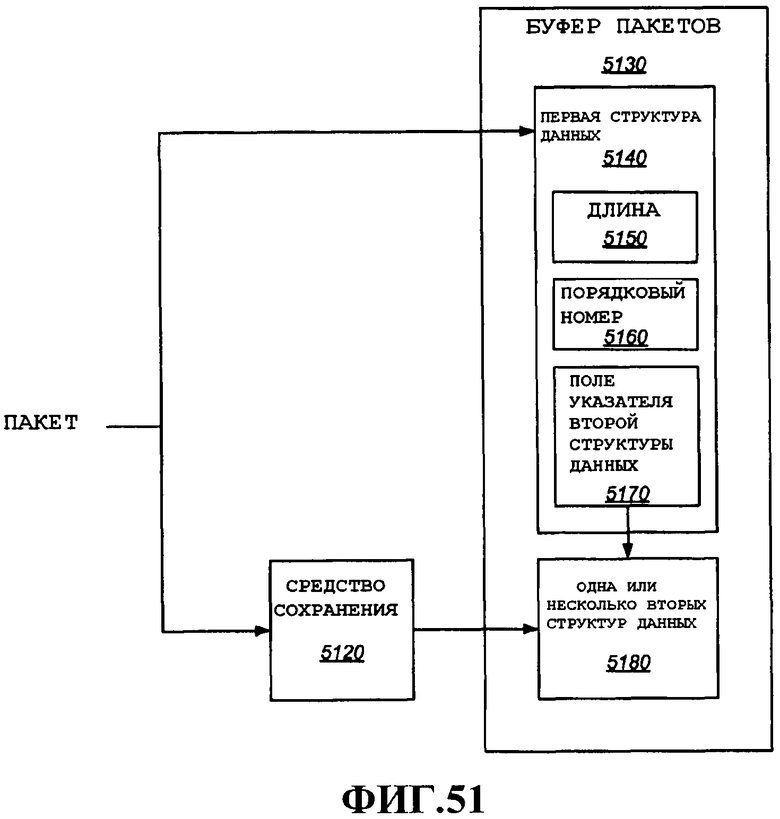

Согласно еще одному аспекту, раскрыт способ, содержащий этапы, на которых сохраняют совокупность пакетов в буфере пакетов, причем каждый пакет сохраняется с ассоциированной первой структурой данных и одной или несколькими ассоциированными вторыми структурами данных, причем одна или несколько вторых структур данных образуют связанный список; в котором каждая первая структура данных содержит поле длины, указывающее длину ассоциированного пакета, поле порядкового номера, указывающее порядковый номер ассоциированного пакета, и поле указателя второй структуры данных, указывающее местоположение в буфере пакетов первой из одной или нескольких вторых структур данных; и в котором каждая вторая структура данных содержит данные из ассоциированного пакета и поле указателя следующей второй структуры данных, указывающего следующую вторую структуру в соответствующем связанном списке, если таковая существует.

Согласно еще одному аспекту, описано устройство, которое включает в себя средства хранения в первой структуре данных в буфере пакетов длины первого пакета, порядкового номера пакета, и второго местоположения в буфере пакетов второй структуры данных в буфере пакетов, и средства хранения данных из первого пакета во второй структуре данных, идентифицируемой сохраненным вторым местоположением в буфере пакетов.

Согласно еще одному аспекту, описано устройство, которое включает в себя первую структуру данных, ассоциированную с пакетом, и одну или несколько вторых структур данных, содержащих данные из ассоциированного пакета; и в котором первая структура данных содержит поле длины, указывающее длину ассоциированного пакета, поле порядкового номера, указывающее порядковый номер ассоциированного пакета, и поле указателя второй структуры данных, указывающее местоположение в буфере пакетов одной из вторых структур данных; и средства хранения пакета в одной или нескольких вторых структур данных.

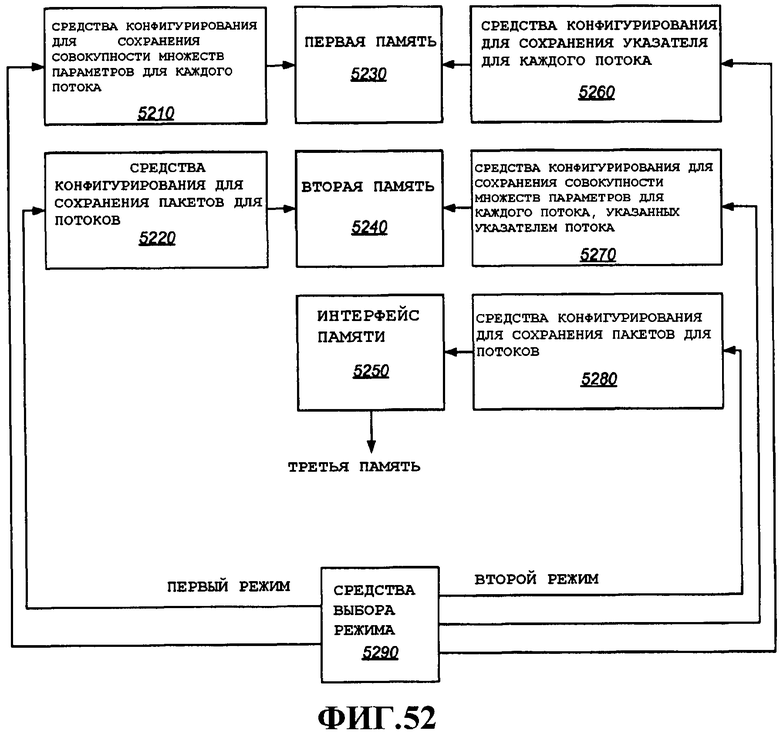

Согласно еще одному аспекту, описано устройство, которое включает в себя первую память, сконфигурированную в первом режиме для хранения одного или нескольких параметров для каждого из совокупности коммуникационных потоков и сконфигурированную во втором режиме для хранения указателя для каждого из совокупности коммуникационных потоков, причем каждый указатель указывает местоположение, ассоциированное коммуникацией с соответствующим потоком; вторую память, сконфигурированную в первом режиме для хранения пакетов для каждого из совокупности коммуникационных потоков и сконфигурированную во втором режиме для хранения совокупности множеств из одного или нескольких параметров для каждого из совокупности коммуникационных потоков, причем каждое множество из одного или нескольких параметров хранится в местоположении, указанном указателем, ассоциированным с соответствующим коммуникационным потоком; интерфейс памяти, способный работать с третьей памятью, сконфигурированной во втором режиме с возможностью хранить пакеты для каждого из совокупности коммуникационных потоков; и процессор, выбирающий выбранный режим в качестве первого режима или второго режима, конфигурирующий первую память согласно выбранному режиму, конфигурирующий вторую память согласно выбранному режиму, и конфигурирующий интерфейс памяти согласно выбранному режиму.

Согласно еще одному аспекту, описано устройство беспроводной связи, которое включает в себя первую интегральную схему, содержащую первую память, сконфигурированную в первом режиме для хранения одного или нескольких параметров для каждого из совокупности коммуникационных потоков и сконфигурированную во втором режиме для хранения указателя для каждого из совокупности коммуникационных потоков, причем каждый указатель указывает местоположение, ассоциированное с соответствующим коммуникационным потоком; вторую память, сконфигурированную в первом режиме для хранения пакетов для каждого из совокупности коммуникационных потоков и сконфигурированную во втором режиме для хранения совокупности множеств из одного или нескольких параметров для каждого из совокупности коммуникационных потоков, причем каждое множество из одного или нескольких параметров хранится в местоположении, указанном указателем, ассоциированным с соответствующим коммуникационным потоком; интерфейс памяти, способный работать с третьей памятью, сконфигурированной во втором режиме с возможностью хранения пакетов для каждого из совокупности коммуникационных потоков; и процессор, выбирающий выбранный режим в качестве первого режима или второго режима, конфигурирующий первую память согласно выбранному режиму, конфигурирующий вторую память согласно выбранному режиму, и конфигурирующий интерфейс памяти согласно выбранному режиму; и вторую интегральную схему, содержащую третью память, в которой хранятся пакеты для каждого из совокупности коммуникационных потоков, подключенную к интерфейсу памяти первой интегральной схемы.

Согласно еще одному аспекту, описано устройство беспроводной связи, которое включает в себя первую память, в которой хранятся один или несколько параметров для каждого из совокупности коммуникационных потоков; и вторую память, в которой хранятся пакеты для каждого из совокупности коммуникационных потоков, содержащую первую структуру данных, ассоциированную с пакетом; и вторую структуру данных, содержащую данные из ассоциированного пакета; и в котором первая структура данных содержит поле длины, указывающее длину ассоциированного пакета, поле порядкового номера, указывающее порядковый номер ассоциированного пакета, и поле указателя второй структуры данных, указывающее местоположение во второй памяти второй структуры данных.

Согласно еще одному аспекту, описано устройство беспроводной связи, которое включает в себя первую память, в которой хранится указатель для каждого из совокупности коммуникационных потоков, причем каждый указатель местоположение, ассоциированное с соответствующим потоком связи; и вторую память, в которой хранится совокупность множеств из одного или нескольких параметров для каждого из совокупности коммуникационных потоков, причем каждое множество из одного или нескольких параметров хранится в местоположении, указанном указателем, ассоциированным с соответствующим коммуникационным потоком; и третью память, в которой хранятся пакеты для каждого из совокупности коммуникационных потоков.

Согласно еще одному аспекту, описано устройство, которое включает в себя средства выбора первого или второго режима, средства конфигурирования первой памяти в первом режиме для хранения одного или нескольких параметров для каждого из совокупности коммуникационных потоков, средства конфигурирования первой памяти во втором режиме для хранения указателя для каждого из совокупности коммуникационных потоков, причем каждый указатель указывает местоположение, ассоциированное с соответствующим коммуникационным потоком, средства конфигурирования второй памяти в первом режиме для хранения пакетов для каждого из совокупности коммуникационных потоков, средства конфигурирования второй памяти во втором режиме для хранения совокупности множеств из одного или нескольких параметров для каждого из совокупности коммуникационных потоков, причем каждое множество из одного или нескольких параметров хранится в местоположении, указанном указателем, ассоциированным с соответствующим коммуникационным потоком, и средства конфигурирования интерфейса памяти, способного работать с третьей памятью во втором режиме с возможностью хранения пакетов для каждого из совокупности коммуникационных потоков.

Согласно еще одному аспекту, описан машиночитаемый носитель с возможностью выполнения выбора первого или второго режима, конфигурирования первой памяти в первом режиме для хранения одного или нескольких параметров для каждого из совокупности коммуникационных потоков, конфигурирования первой памяти во втором режиме для хранения указателя для каждого из совокупности коммуникационных потоков, причем каждый указатель указывает местоположение, ассоциированное с соответствующим коммуникационным потоком, конфигурирования второй памяти в первом режиме для хранения пакетов для каждого из совокупности коммуникационных потоков, конфигурирования второй памяти во втором режиме для хранения совокупности множеств из одного или нескольких параметров для каждого из совокупности коммуникационных потоков, причем каждый набор из одного или нескольких параметров хранится в местоположении, указанном указателем, ассоциированным с соответствующим коммуникационным потоком, и конфигурирования интерфейса памяти, способного работать с третьей памятью во втором режиме, с возможностью хранения пакетов для каждого из совокупности коммуникационных потоков.

Краткое описание чертежей

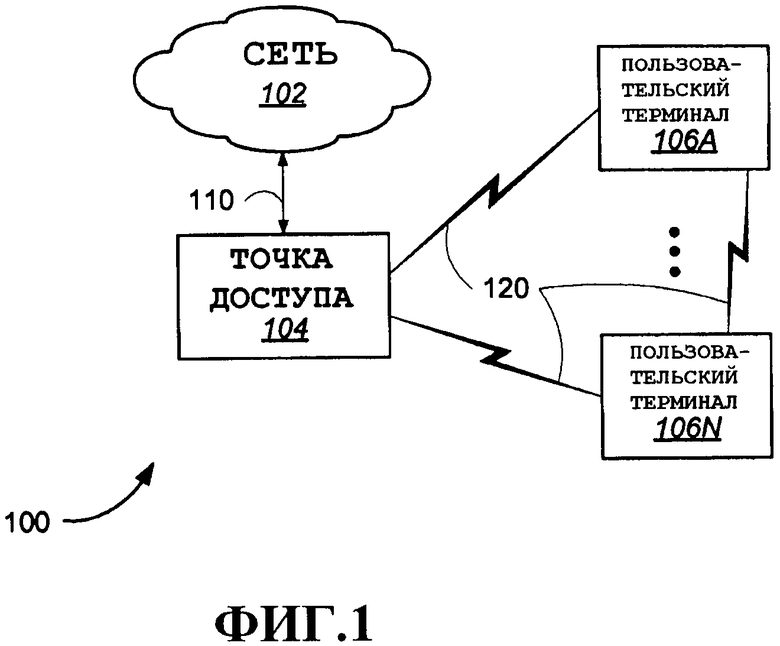

Фиг.1 - общая блок-схема системы беспроводной связи, способной поддерживать множество пользователей.

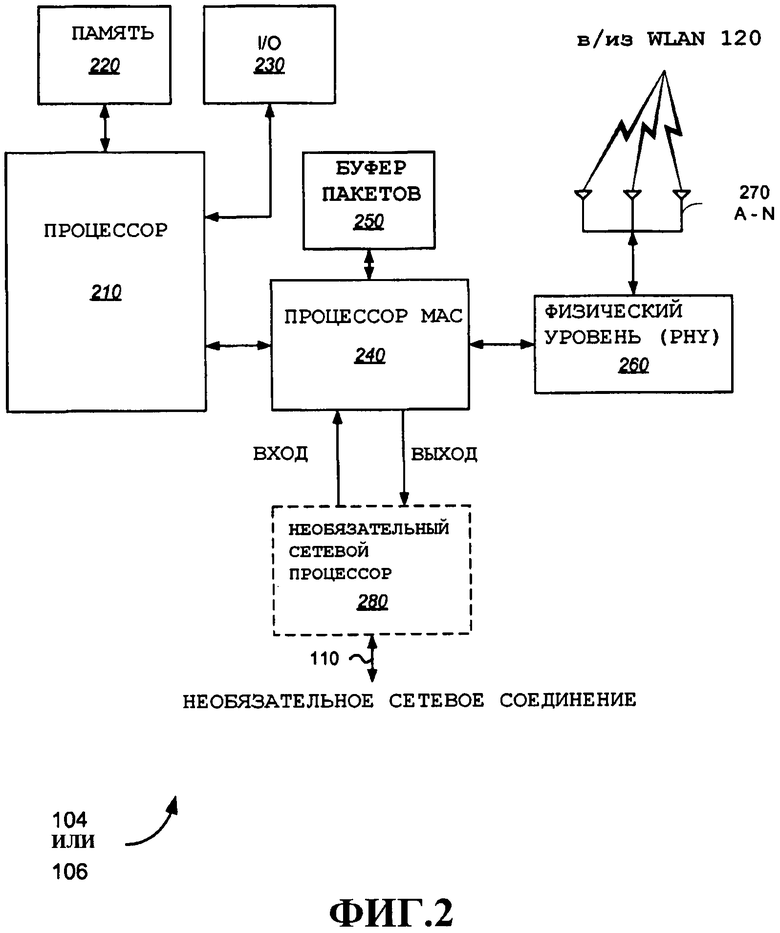

Фиг.2 - аспекты устройства беспроводной связи, которое может быть сконфигурировано как точка доступа или пользовательский терминал.

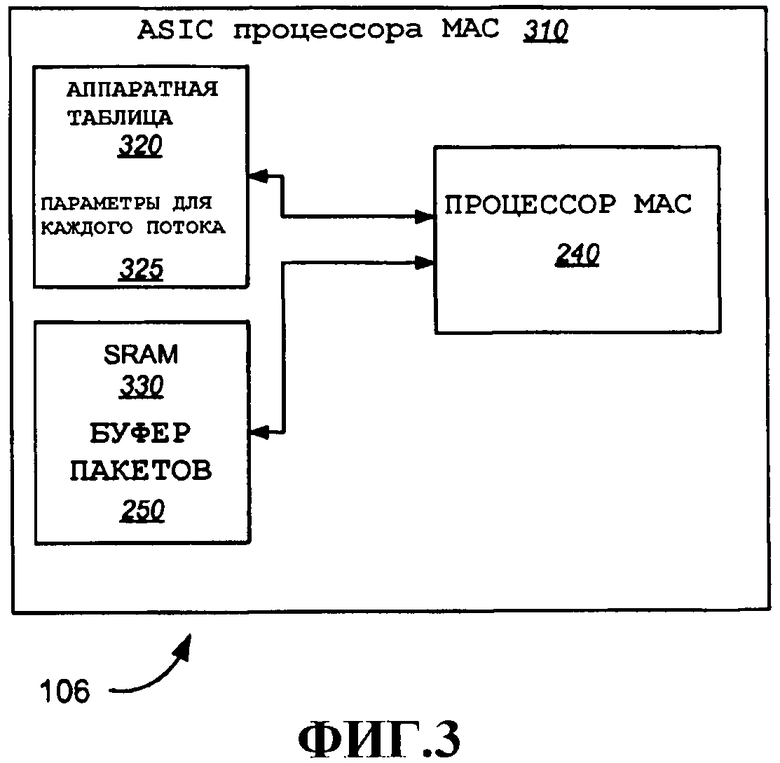

Фиг.3 - вариант осуществления процессора MAC, сконфигурированного для пользовательского терминала.

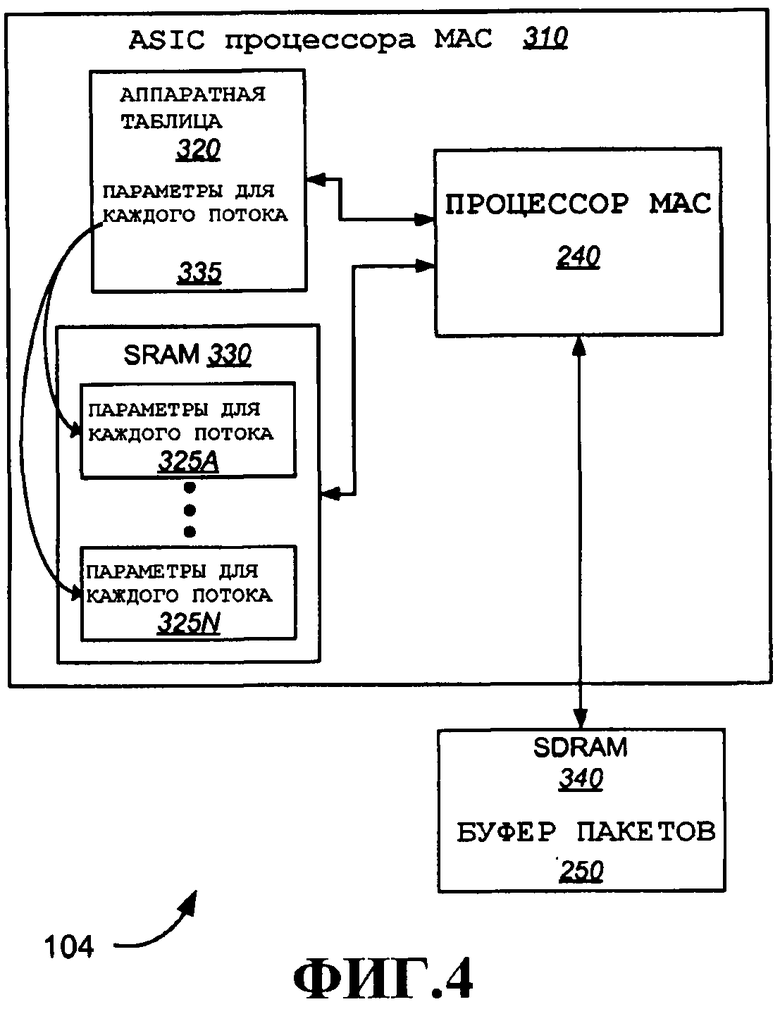

Фиг.4 - вариант осуществления процессора MAC, сконфигурированного для точки доступа.

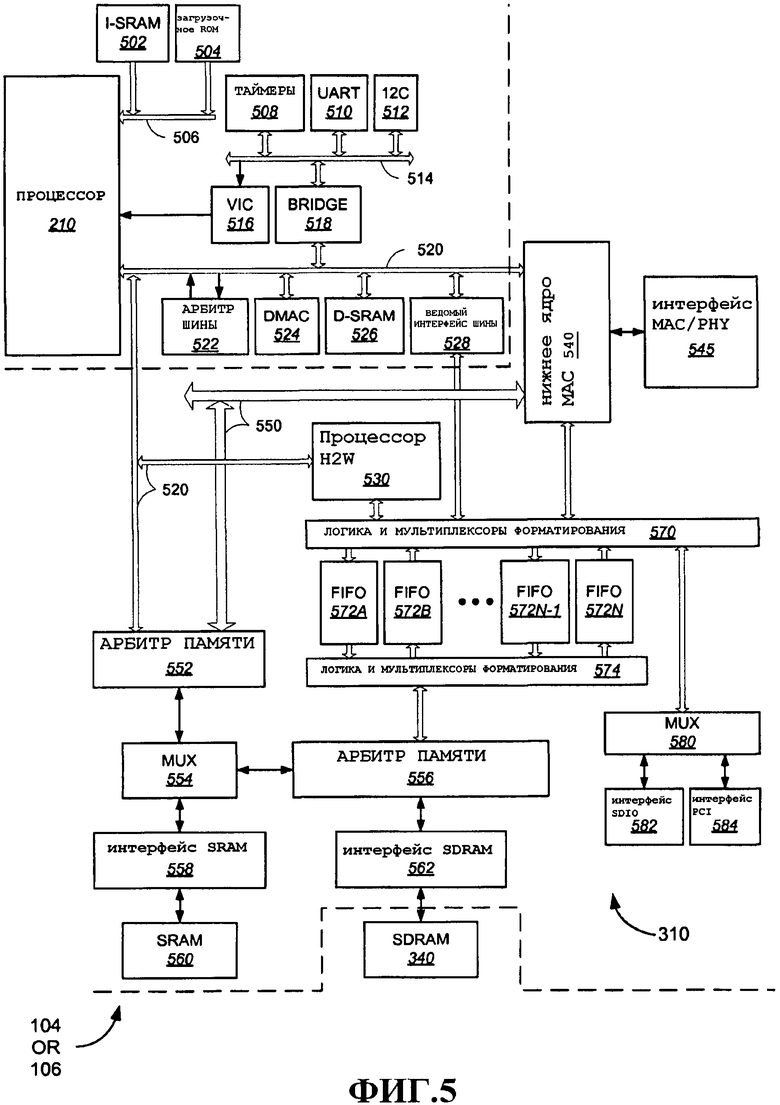

Фиг.5 - более подробный примерный вариант осуществления устройства беспроводной связи.

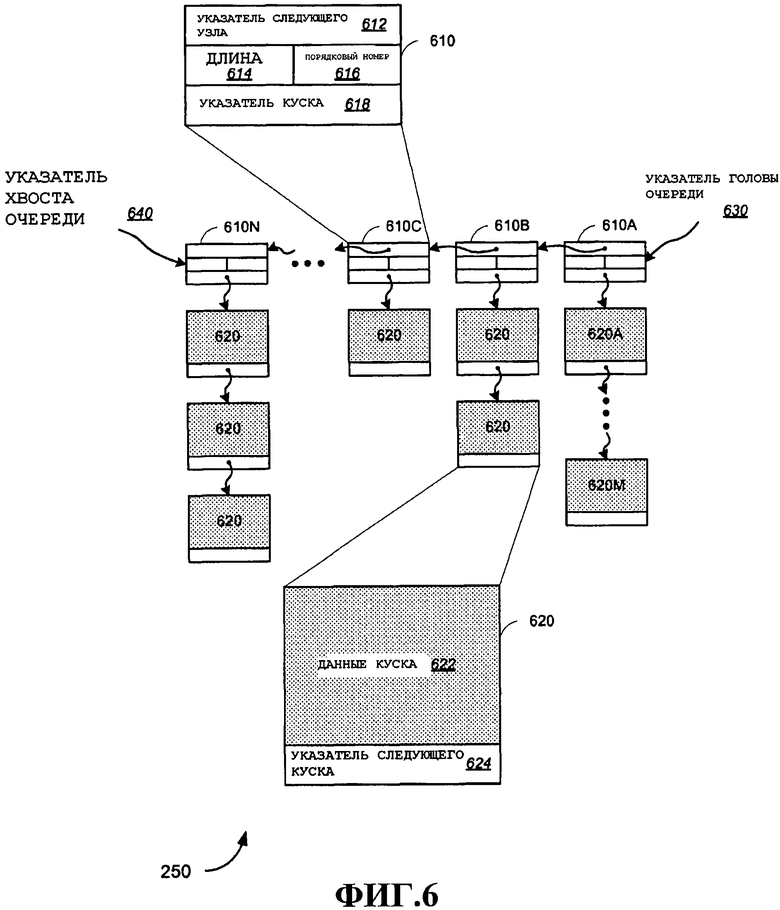

Фиг.6 - примерный вариант осуществления буфера пакетов.

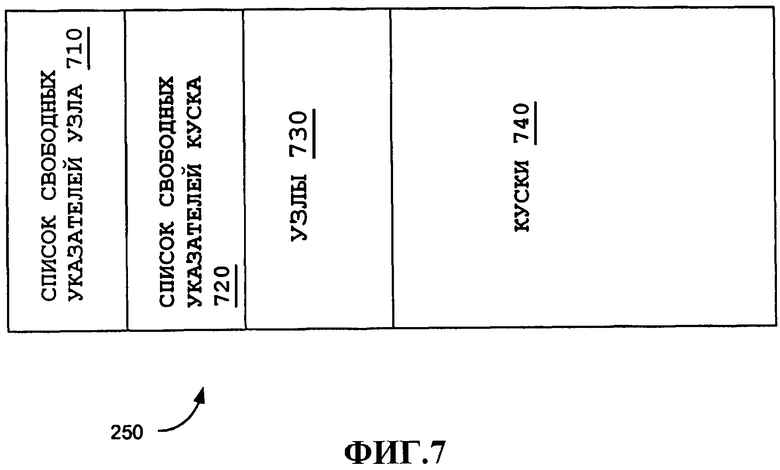

Фиг.7 - дополнительный пример буфера пакетов.

Фиг.8 - дополнительные компоненты, которые могут быть внедрены в процессоре MAC.

Фиг.9 - примерный вариант осуществления способа для записи пакетов в буфер пакетов и создания очередей.

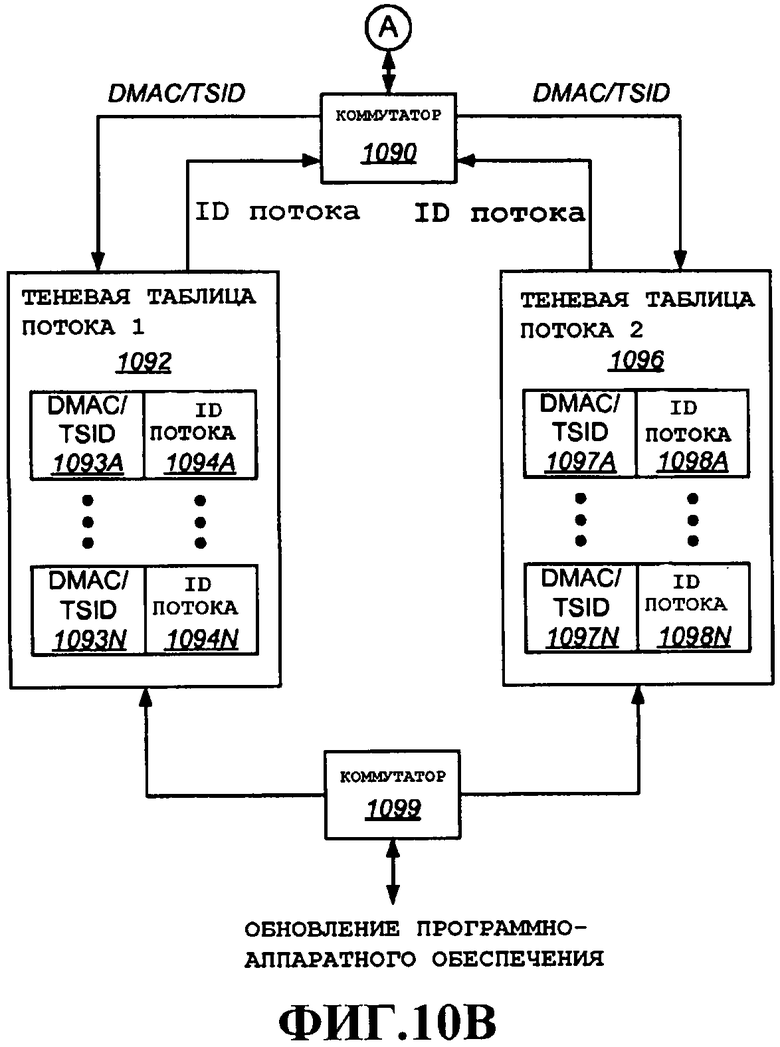

Фиг.10 - примерный вариант осуществления хоста подсистемы WLAN.

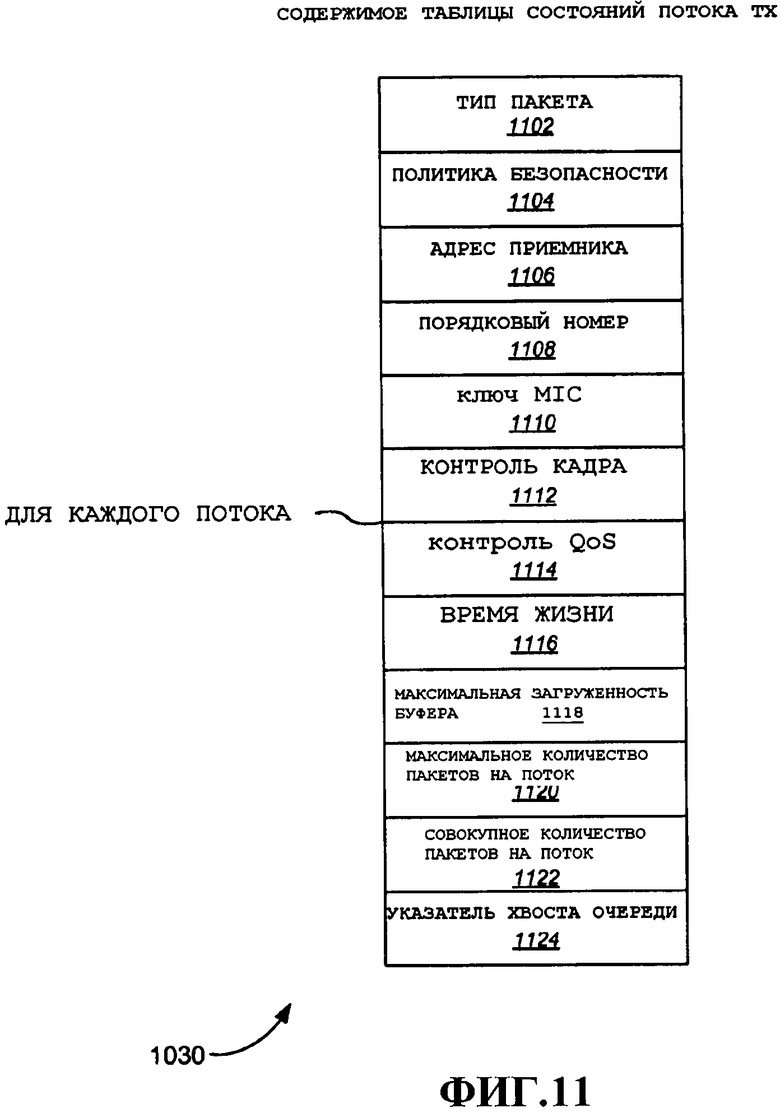

Фиг.11 - примерный вариант осуществления содержимого таблицы состояний ТХ-потока.

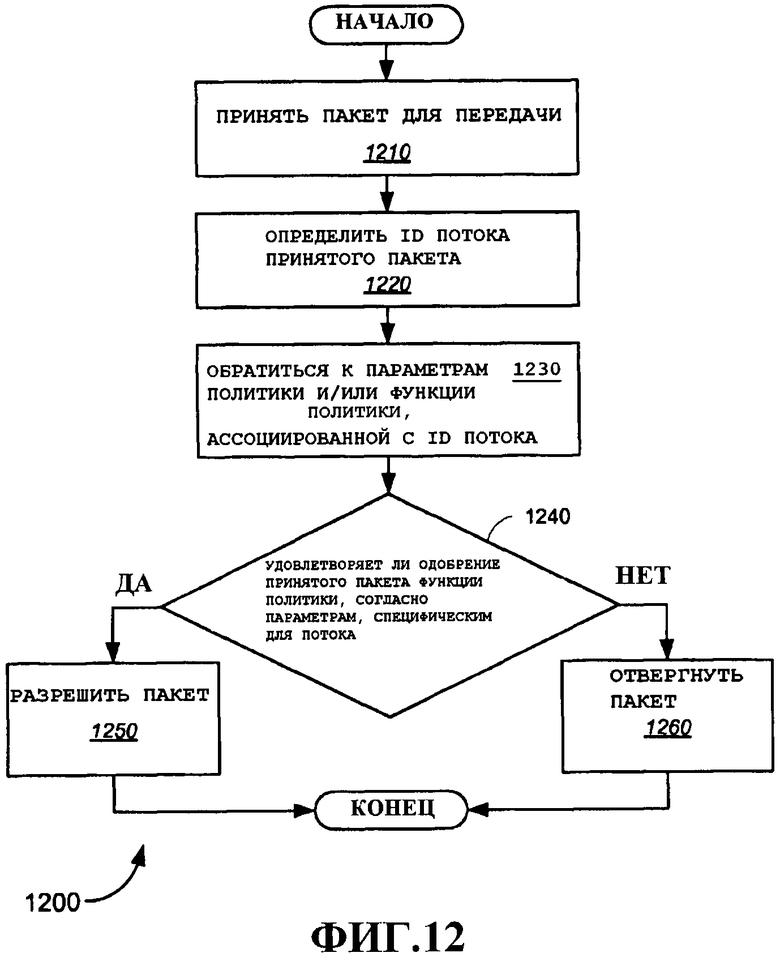

Фиг.12 - примерный вариант осуществления способа выполнения политики входа.

Фиг.13 - примерный вариант осуществления способа политики входа.

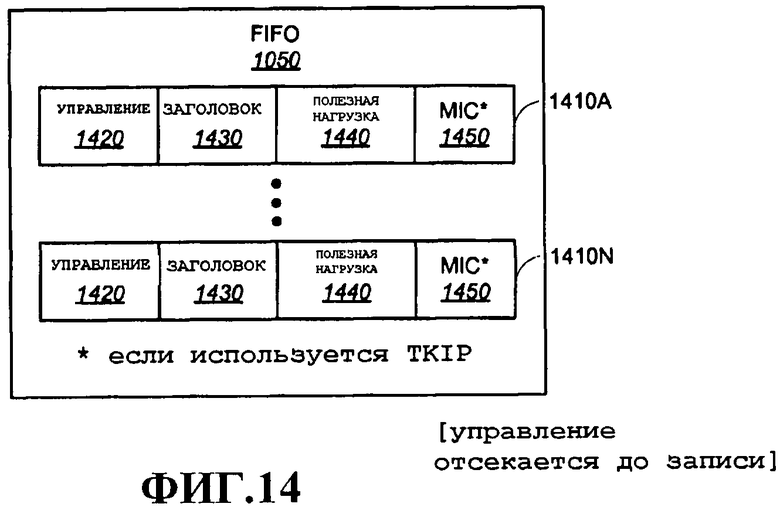

Фиг.14 - примерный вариант осуществления FIFO.

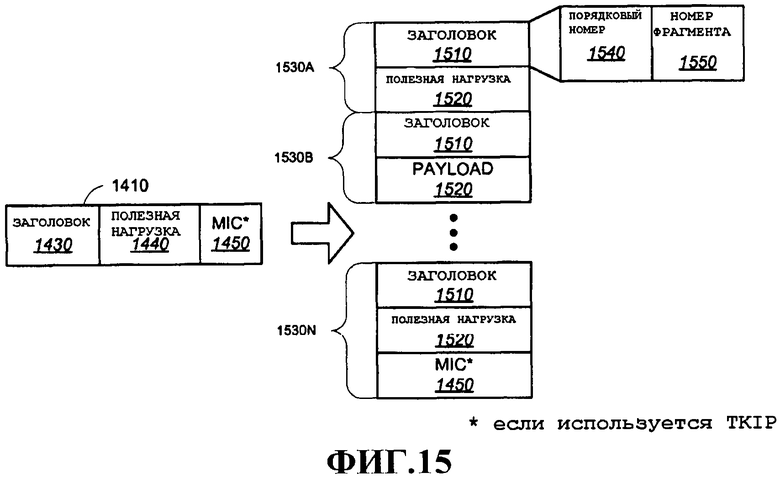

Фиг.15 - примерный процесс разбиения MSDU на один или несколько фрагментов.

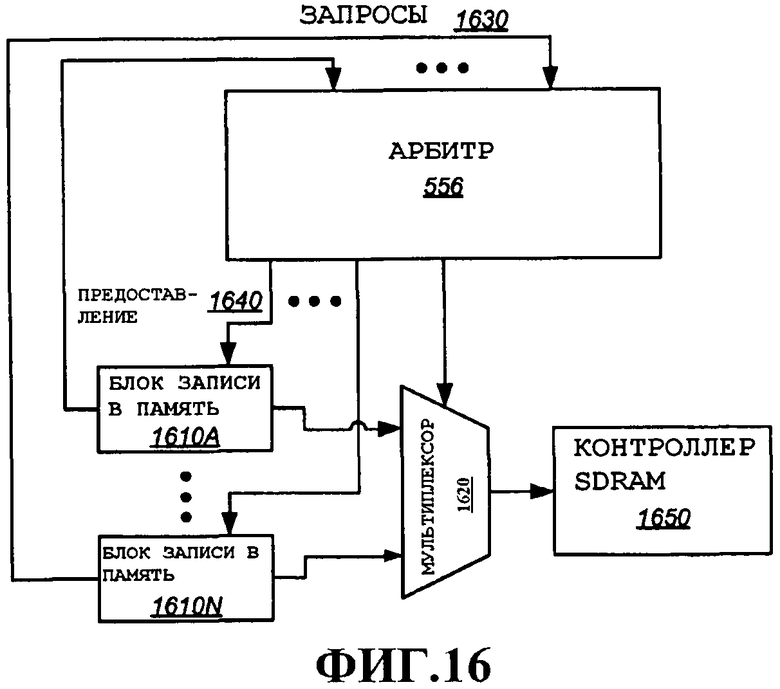

Фиг.16 - принципиальная конфигурация арбитра совместно с двумя или более блоками записи в память.

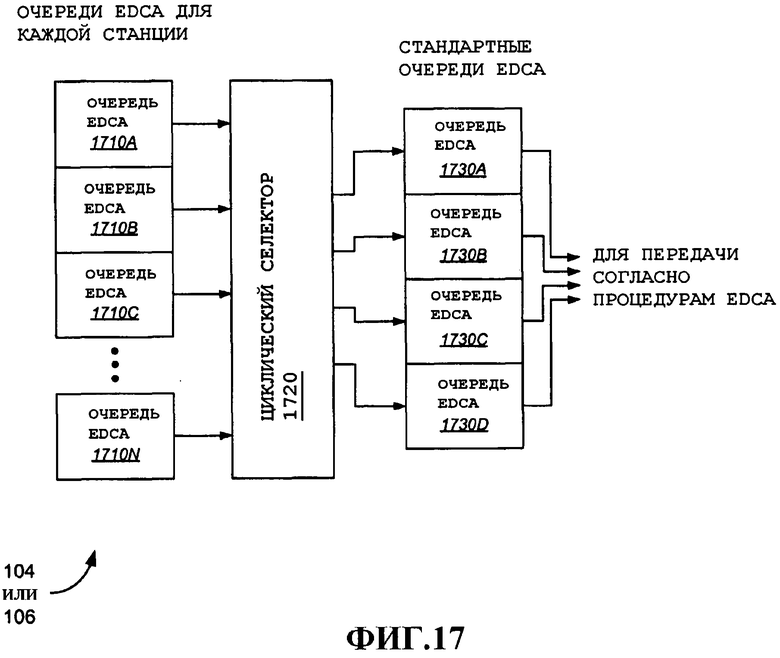

Фиг.17 - примерный вариант осуществления части устройства беспроводной связи, сконфигурированного для поддержки относительно большой совокупности очередей EDCA с использованием меньшего, фиксированного множества стандартных очередей EDCA.

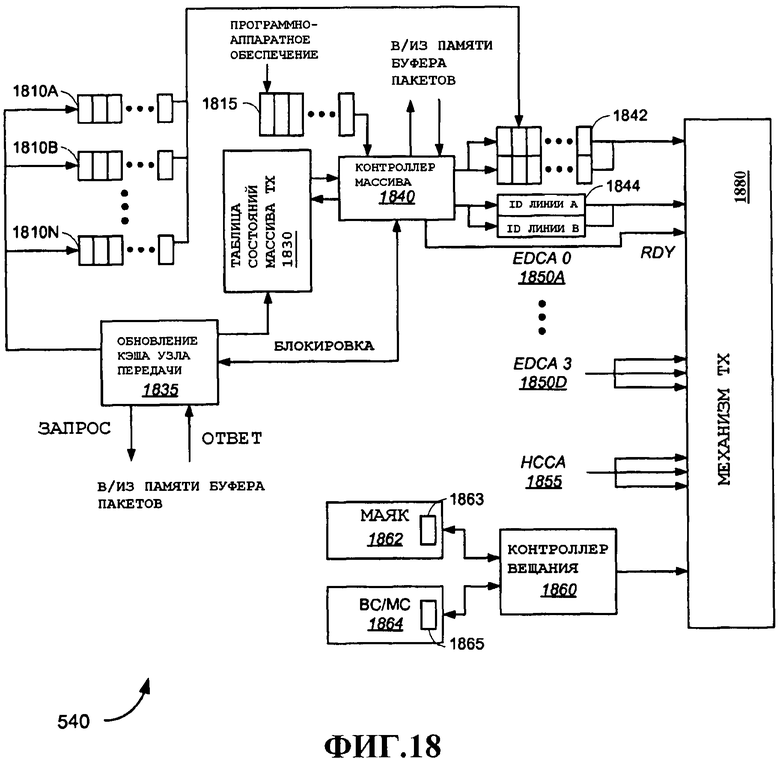

Фиг.18 - примерный вариант осуществления, демонстрирующий различные компоненты нижнего ядра MAC.

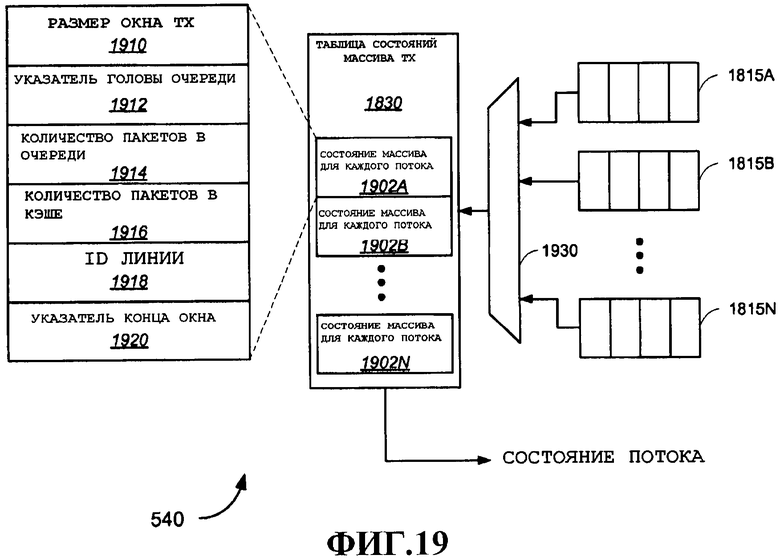

Фиг.19 - подробно описанный примерный вариант осуществления секции процессора нижнего ядра MAC.

Фиг.20 - примерная блокировка.

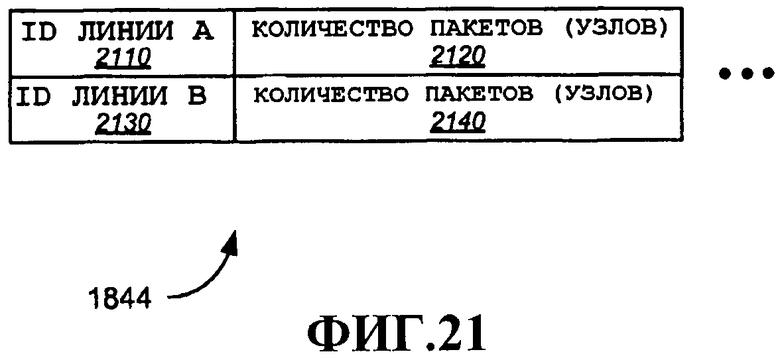

Фиг.21 - примерный вариант осуществления ID линии связи.

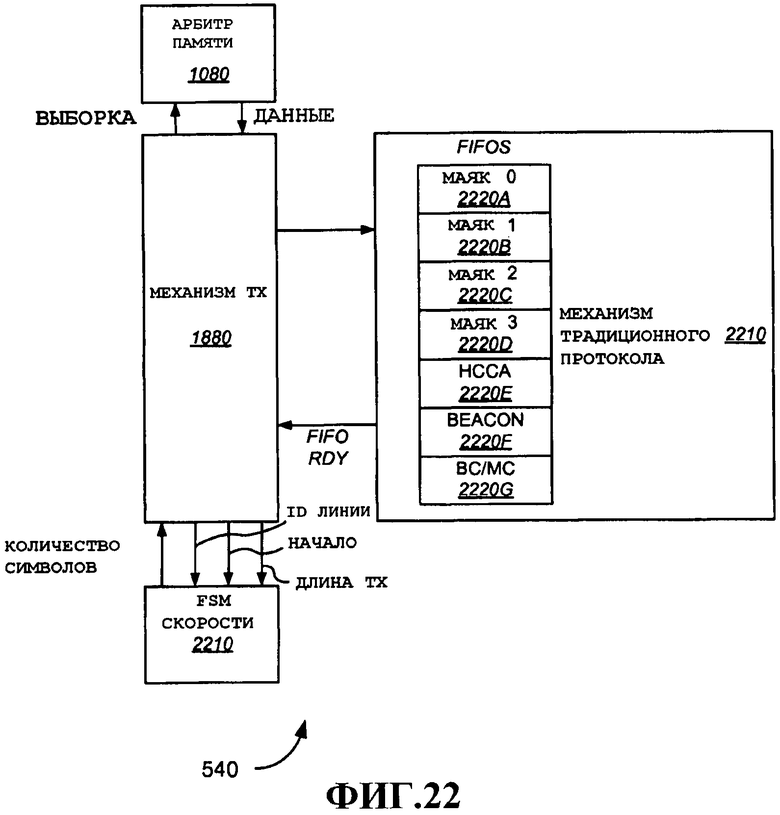

Фиг.22 - дополнительные компоненты примерного варианта осуществления нижнего ядра MAC.

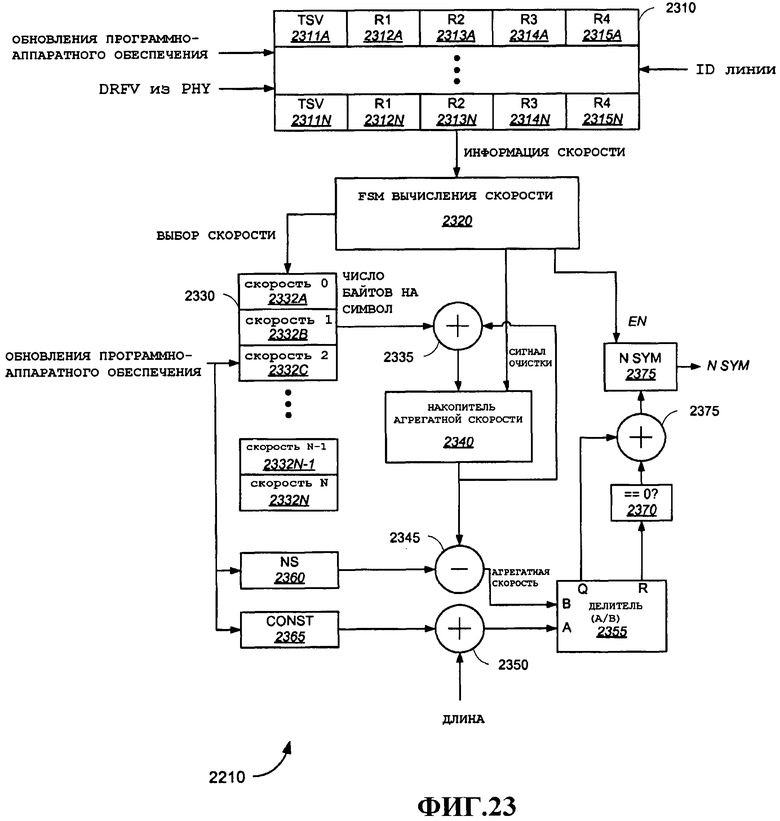

Фиг.23 - примерный вариант осуществления FSM скорости.

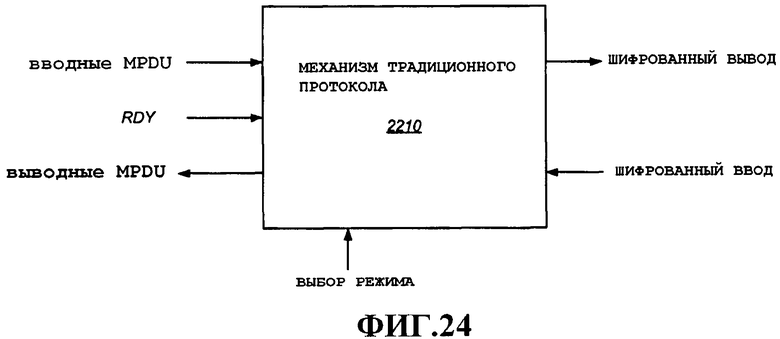

Фиг.24 - примерный механизм традиционного протокола.

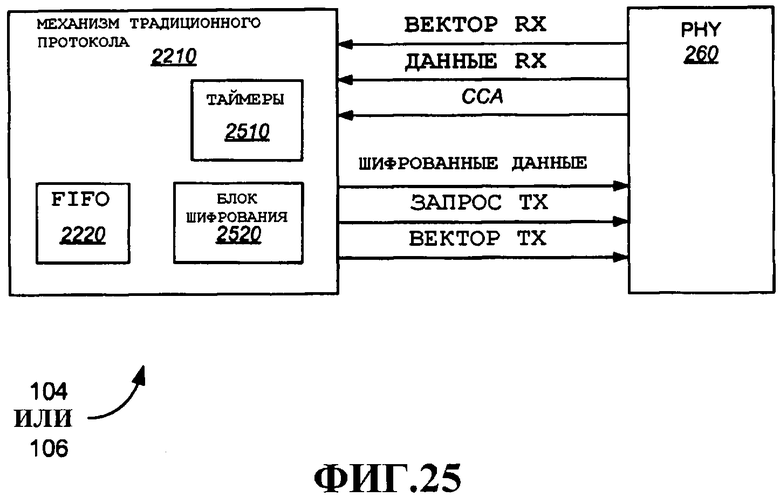

Фиг.25 - примерный механизм традиционного протокола, соединенный принципиальными линиями связи к PHY.

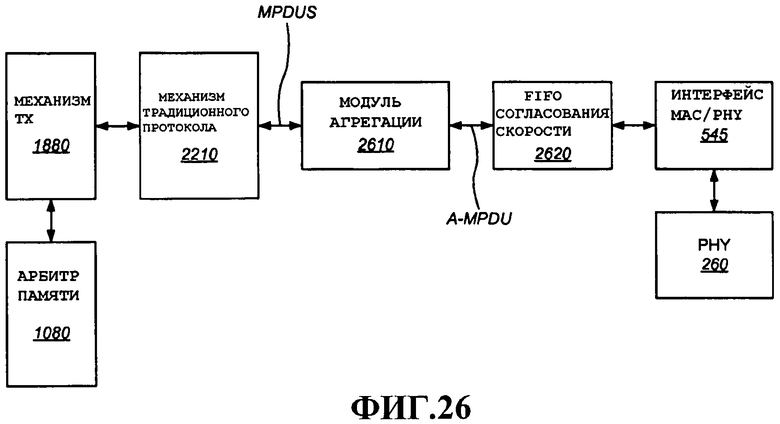

Фиг.26 - примерный механизм осуществления, дополнительно детализирующий MAC обработку пакетов передачи.

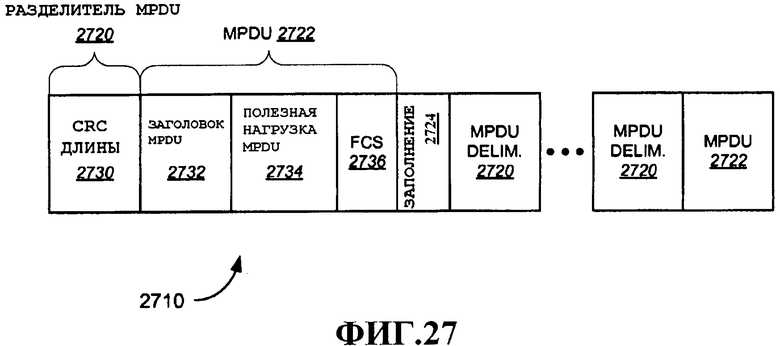

Фиг.27 - примерный формат A-MPDU.

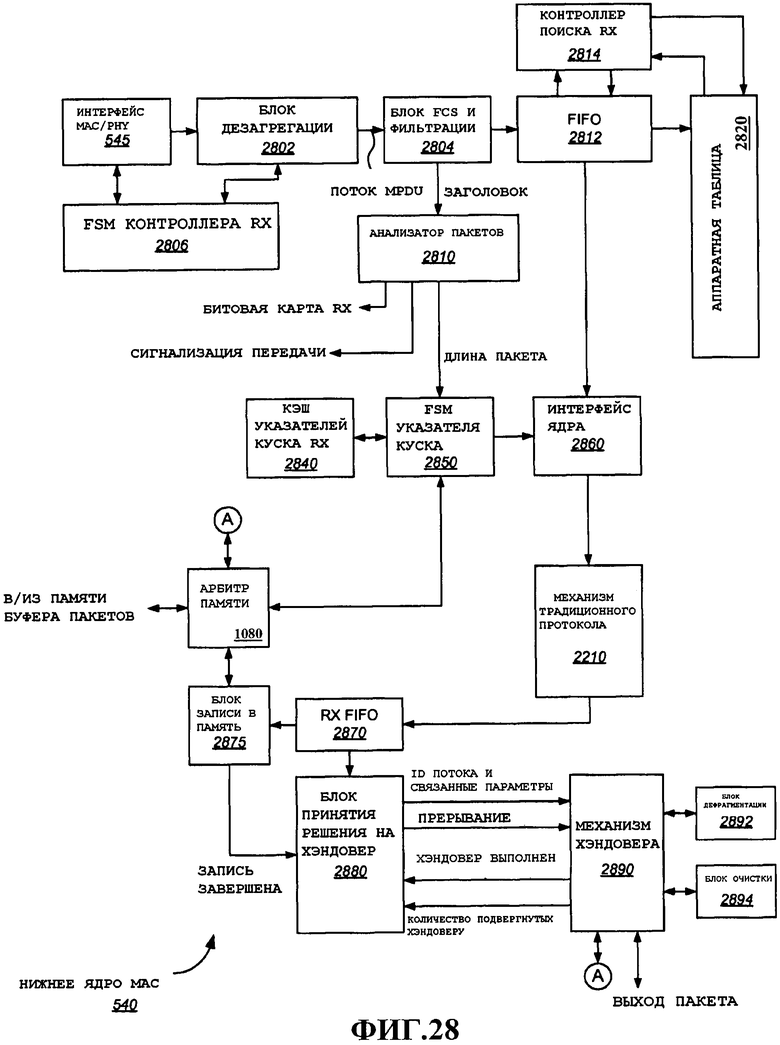

Фиг.28 - примерный вариант осуществления компонентов приема нижнего ядра MAC.

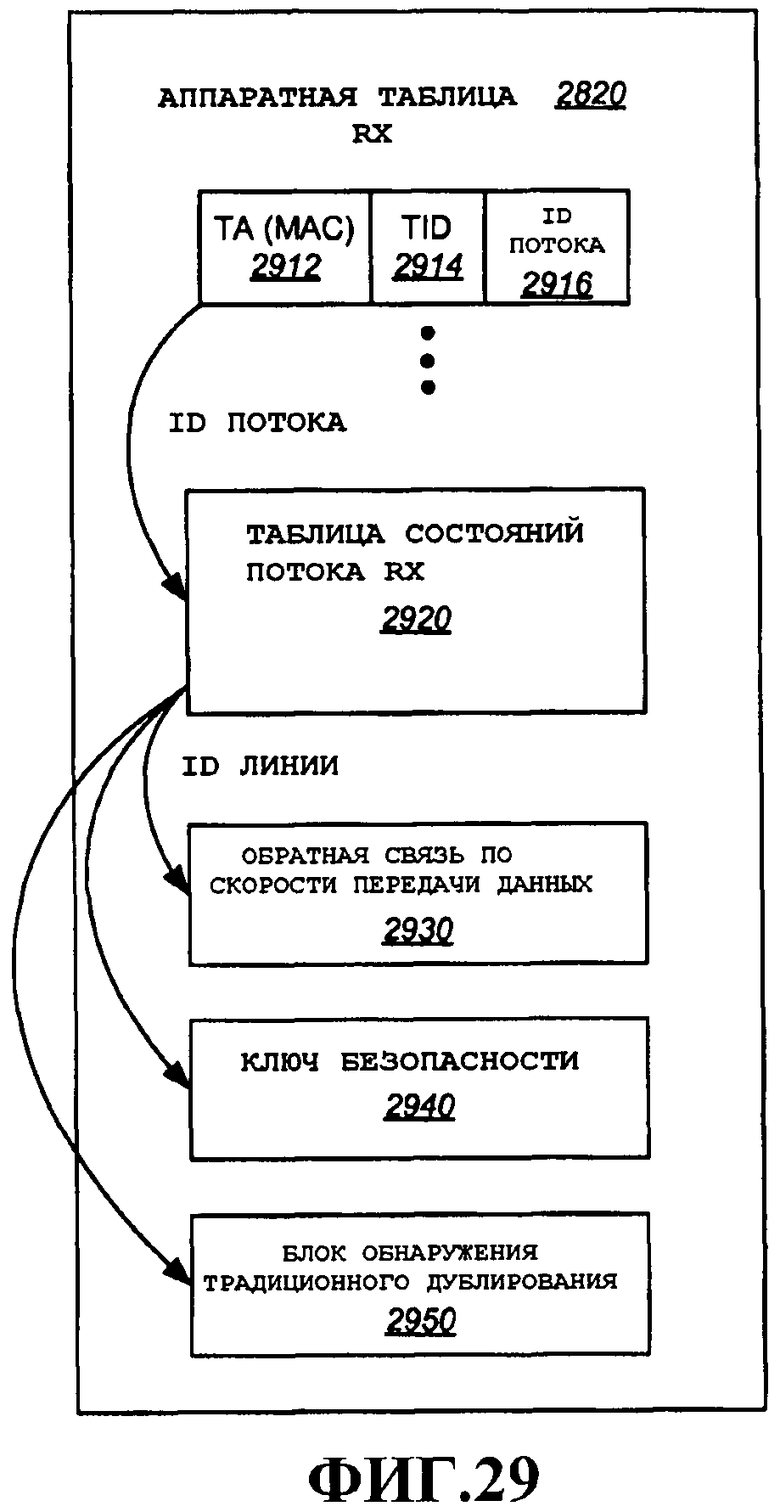

Фиг.29 - примерный вариант осуществления аппаратной таблицы, сконфигурированной для пользовательского терминала.

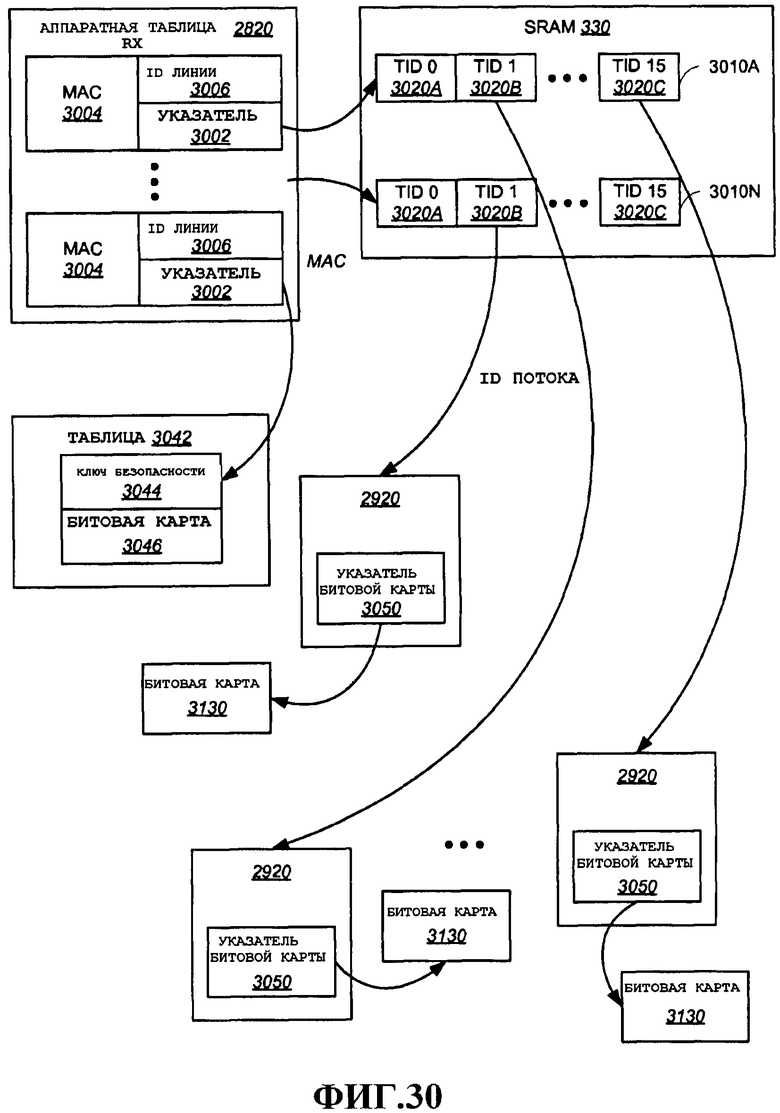

Фиг.30 - примерный вариант осуществления аппаратной таблицы, сконфигурированный для использования в точке доступа или суперстанции.

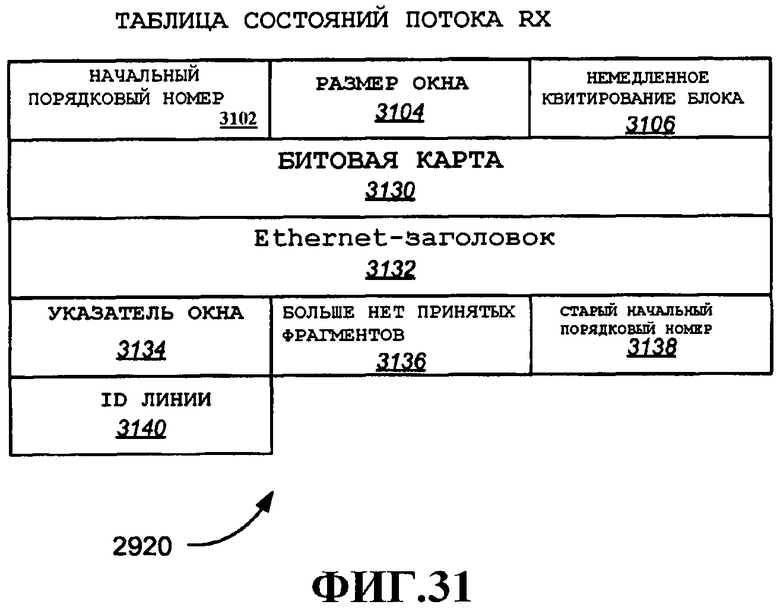

Фиг.31 - примерный вариант осуществления таблицы состояний RX-потока.

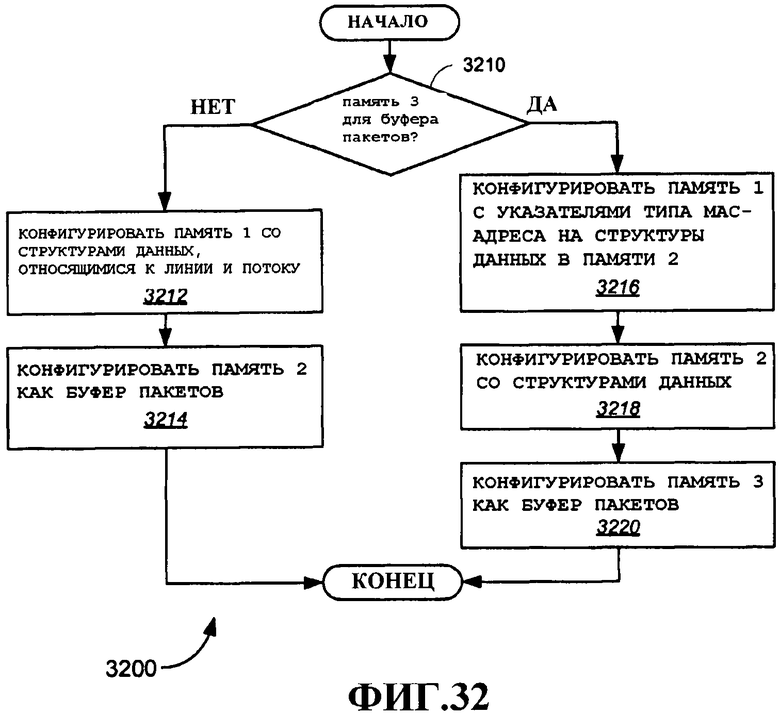

Фиг.32 - примерный вариант осуществления способа конфигурирования аппаратных таблиц и памяти в различных конфигурациях.

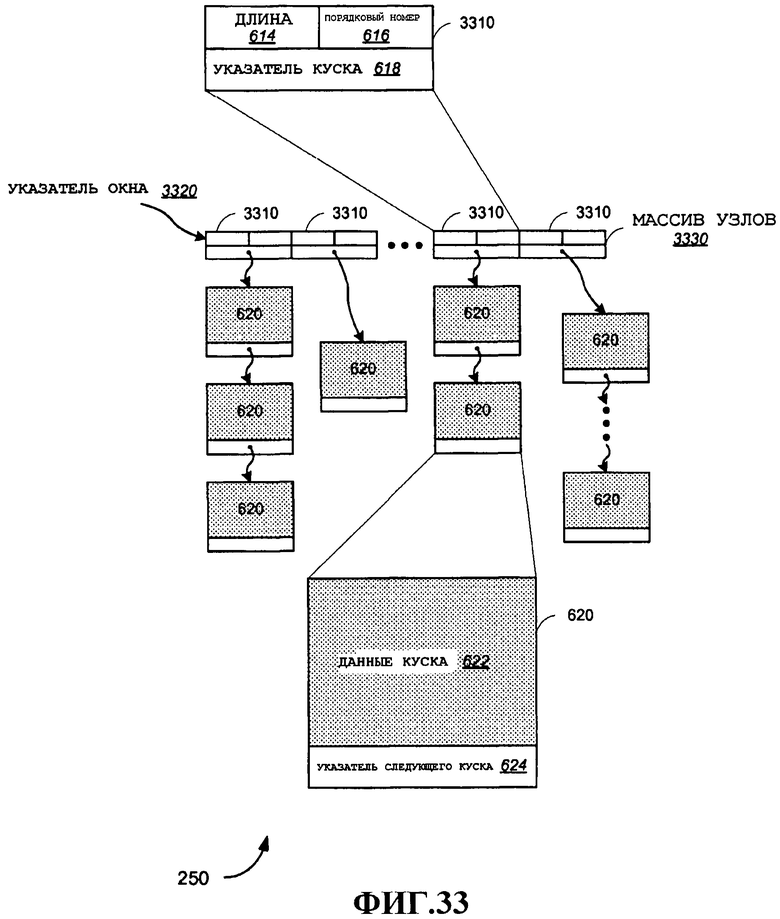

Фиг.33 - альтернативная конфигурация части буфера пакетов, сконфигурированного для поддержки массивов пакетов RX.

Фиг.34 - примерная сквозная схема приоритетов для беспроводных сетей, включающая в себя политику входа и хэндовер на основе приоритета.

Фиг.35 - примерный вариант осуществления способа, демонстрирующий работу блока решений хэндовера и механизма хэндовера.

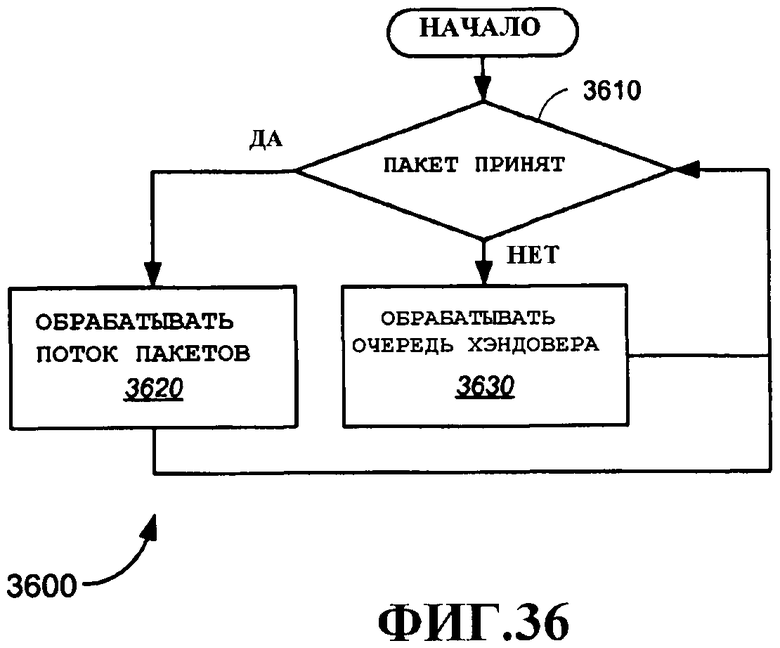

Фиг.36 - примерный вариант осуществления способа выполнения принятия решения хэндовера.

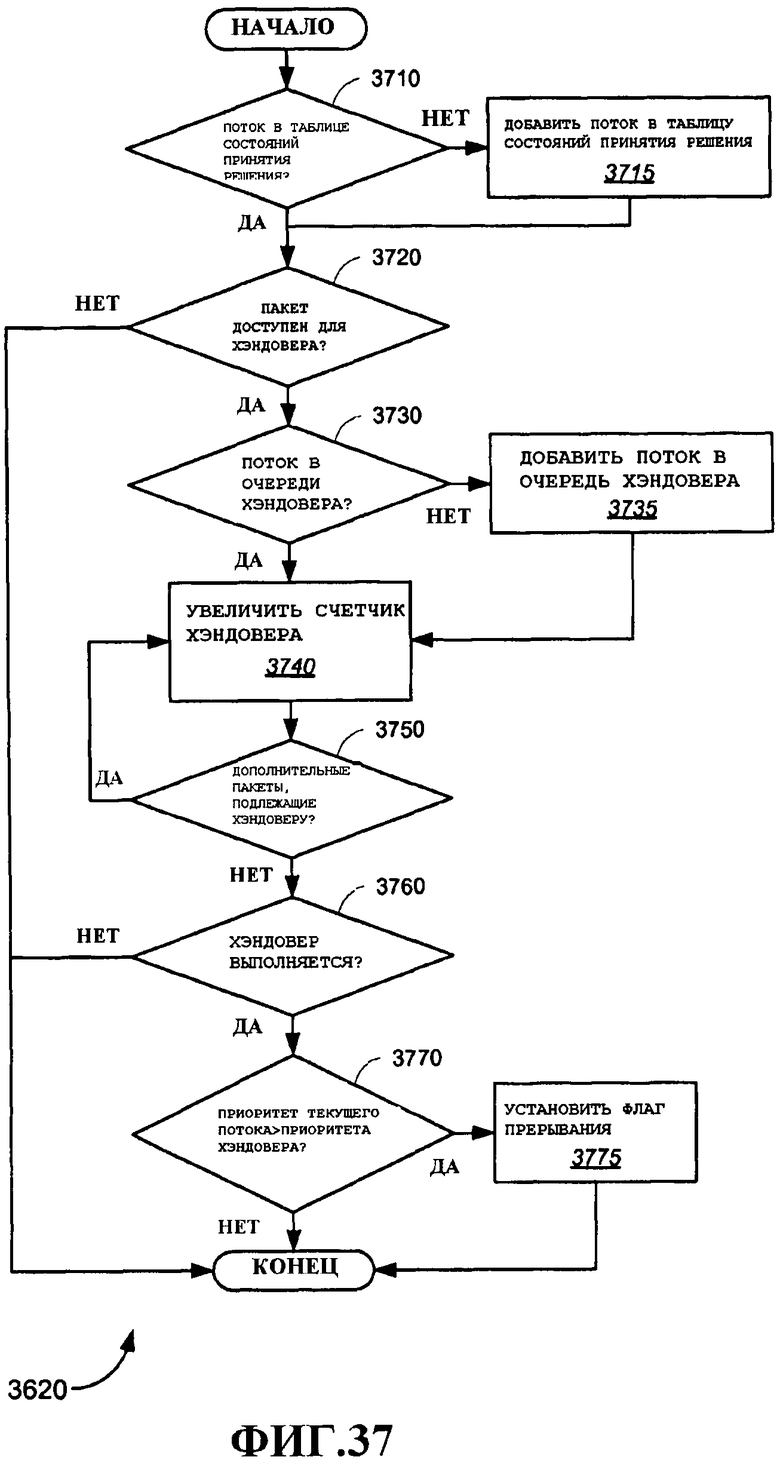

Фиг.37 - примерный вариант осуществления способа обработки принятого пакета.

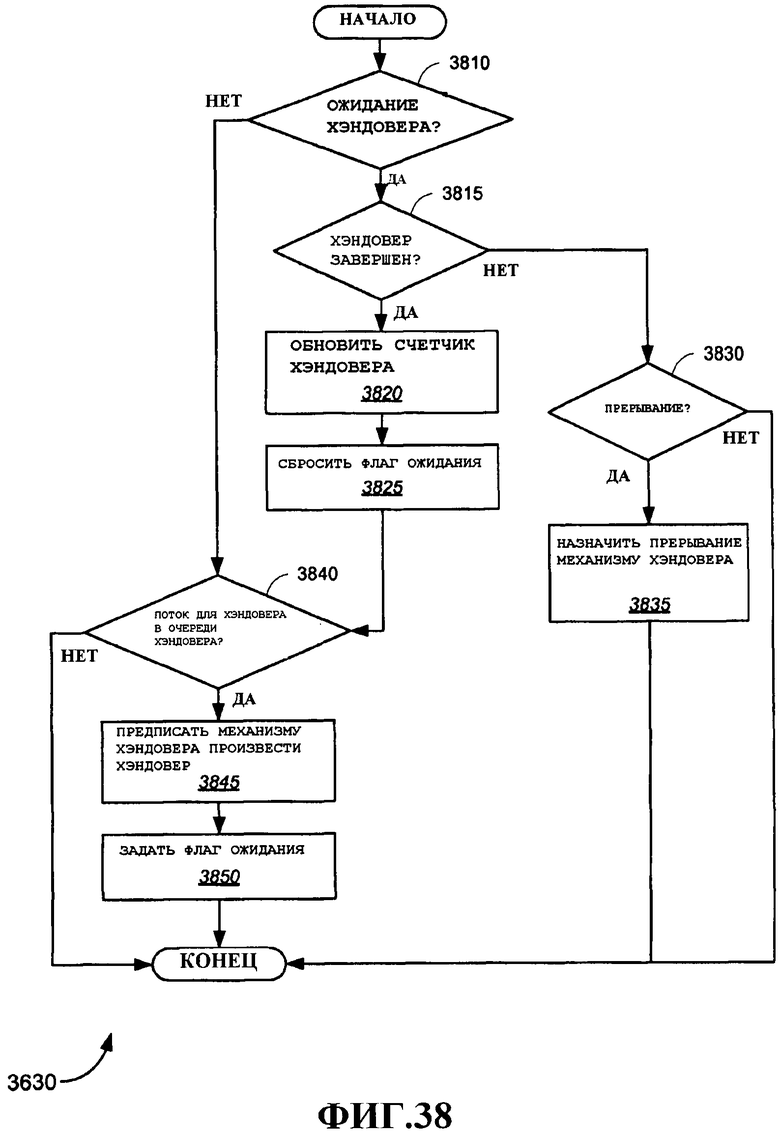

Фиг.38 - примерный вариант осуществления способа обработки одной или нескольких очередей хэндовера.

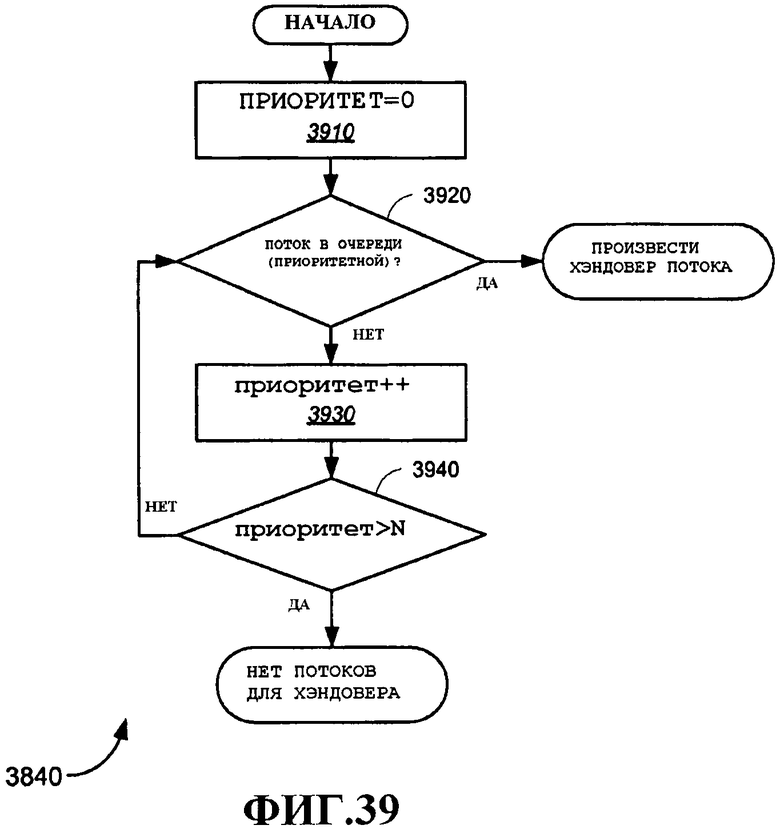

Фиг.39 - примерный вариант осуществления способа определения потоков, доступных для хэндовера.

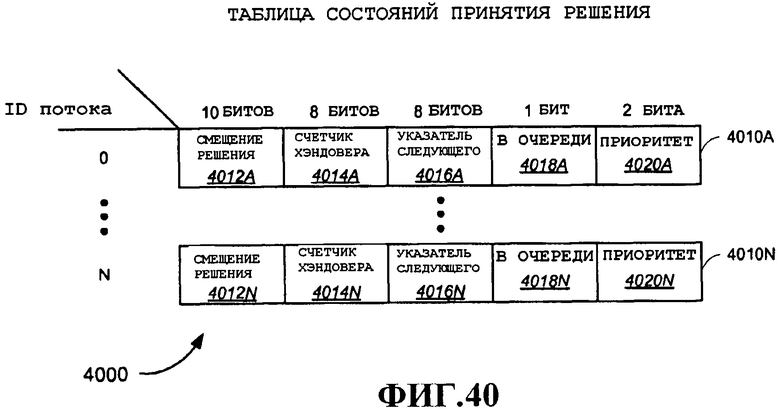

Фиг.40 - примерная таблица состояний решений.

Фиг.41 - примерный вариант осуществления очереди хэндовера.

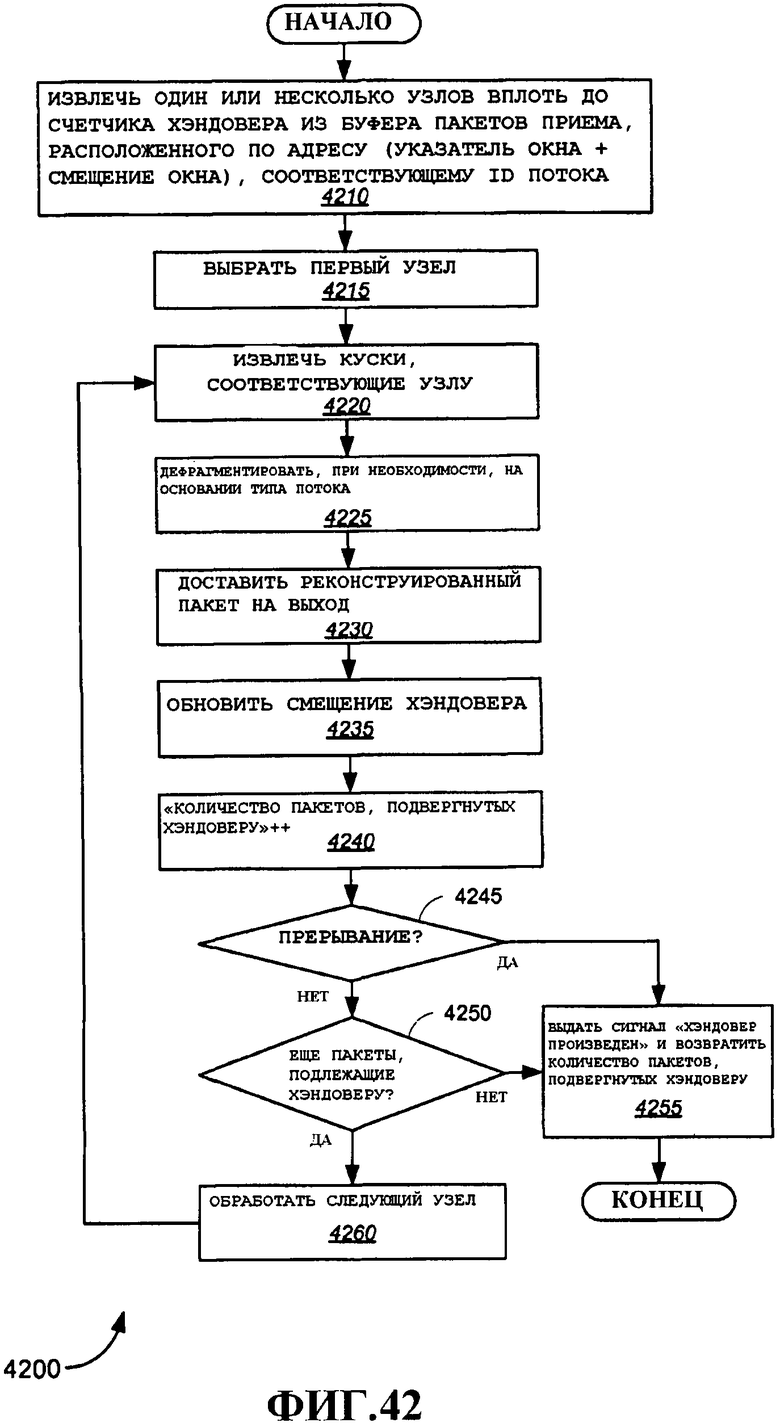

Фиг.42 - примерный вариант осуществления способа выполнения хэндовера.

Фиг.43 - примерные переменные, используемые для индексирования буфера пакетов в таблице состояний хэндовера.

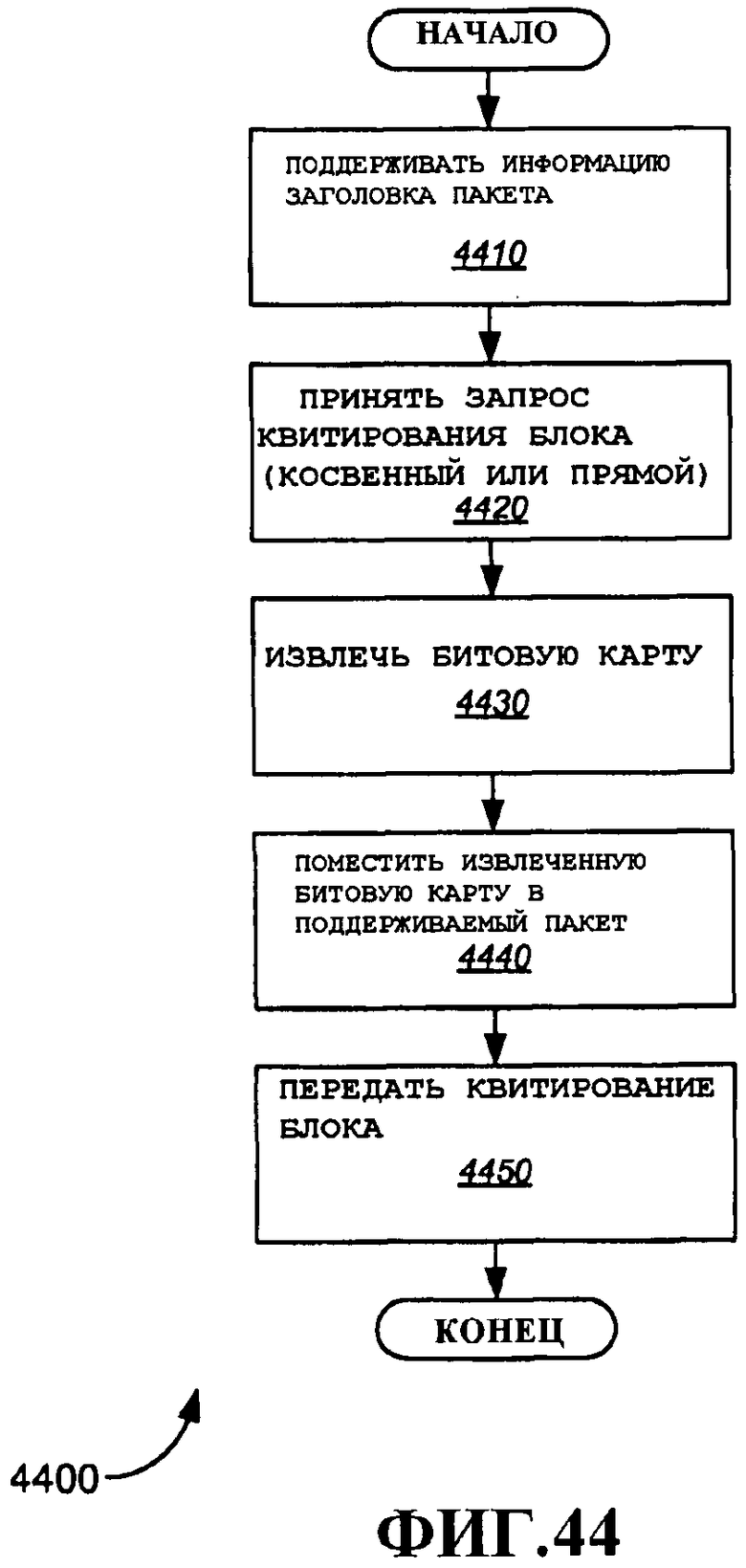

Фиг.44 - примерный вариант осуществления способа для ответа на запрос немедленного квитирования блока.

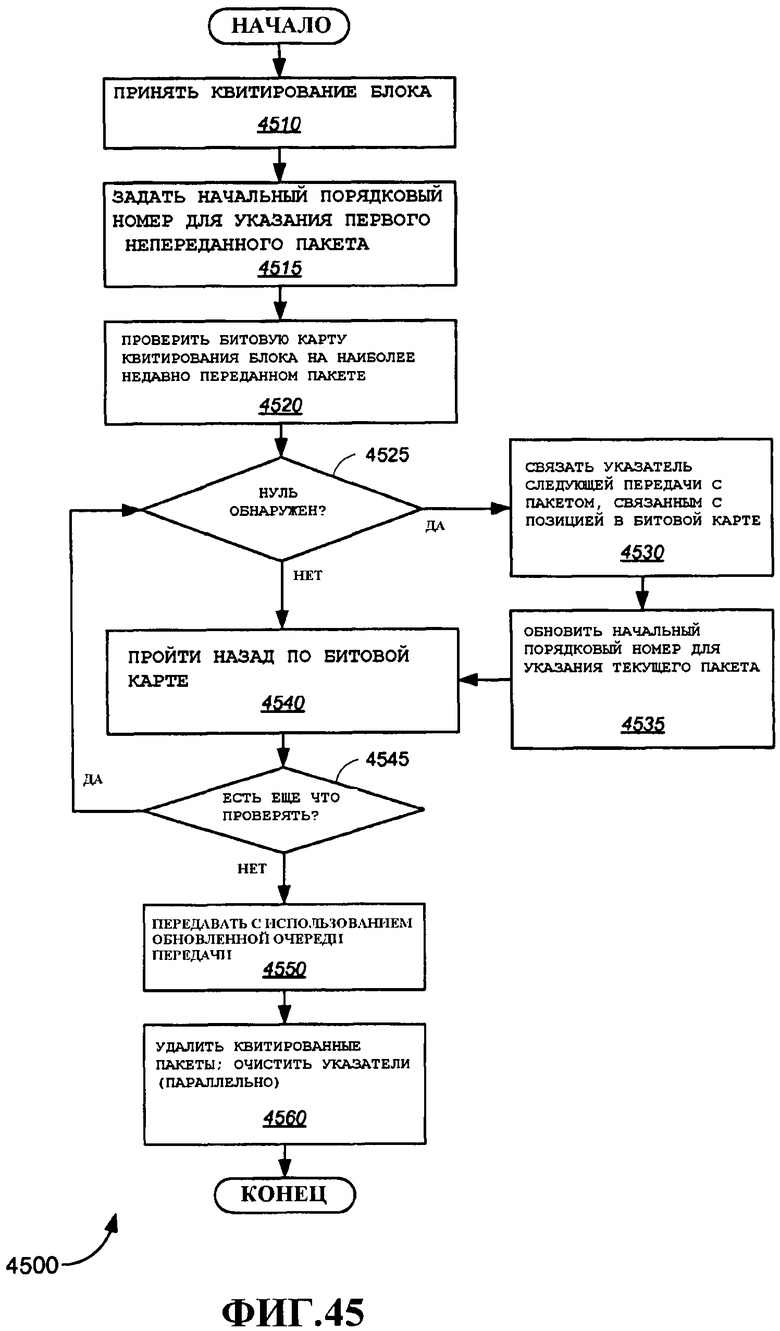

Фиг.45 - иллюстративный вариант осуществления способа для ответа на квитирование блока.

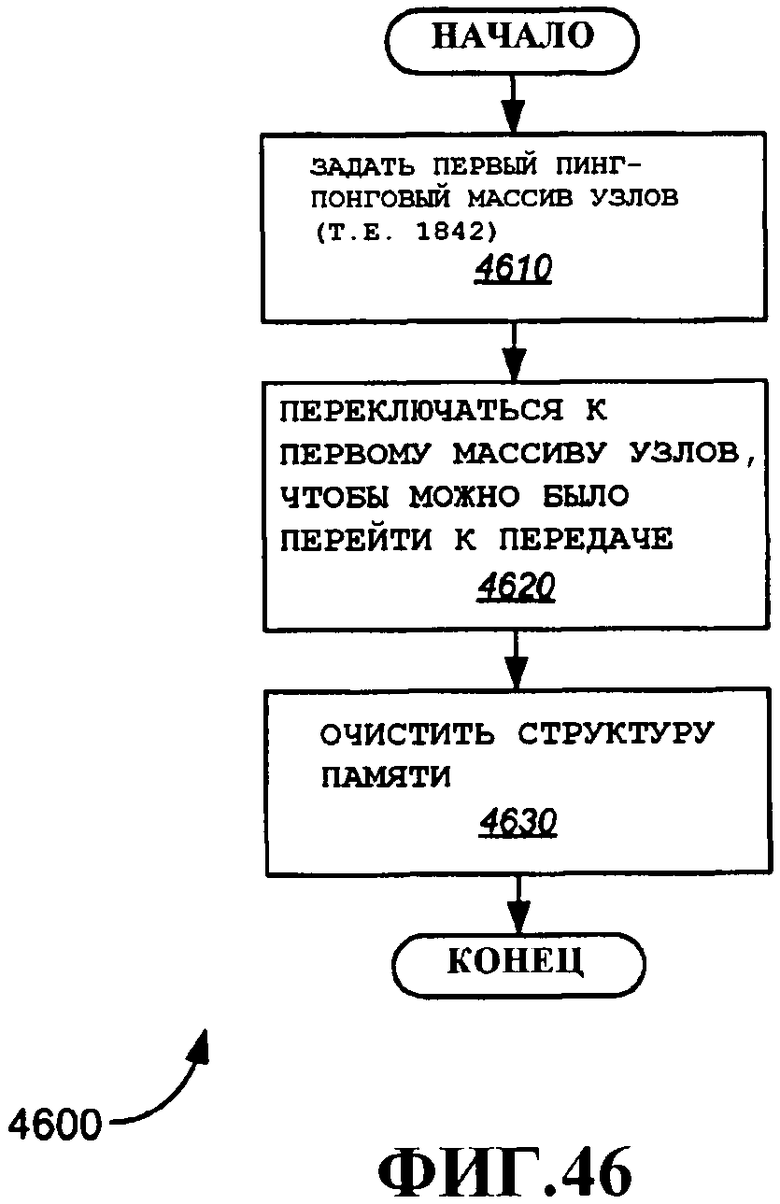

Фиг.46 - примерный вариант осуществления способа использования пинг-понгового кэша массива узлов в процессе повторной передачи.

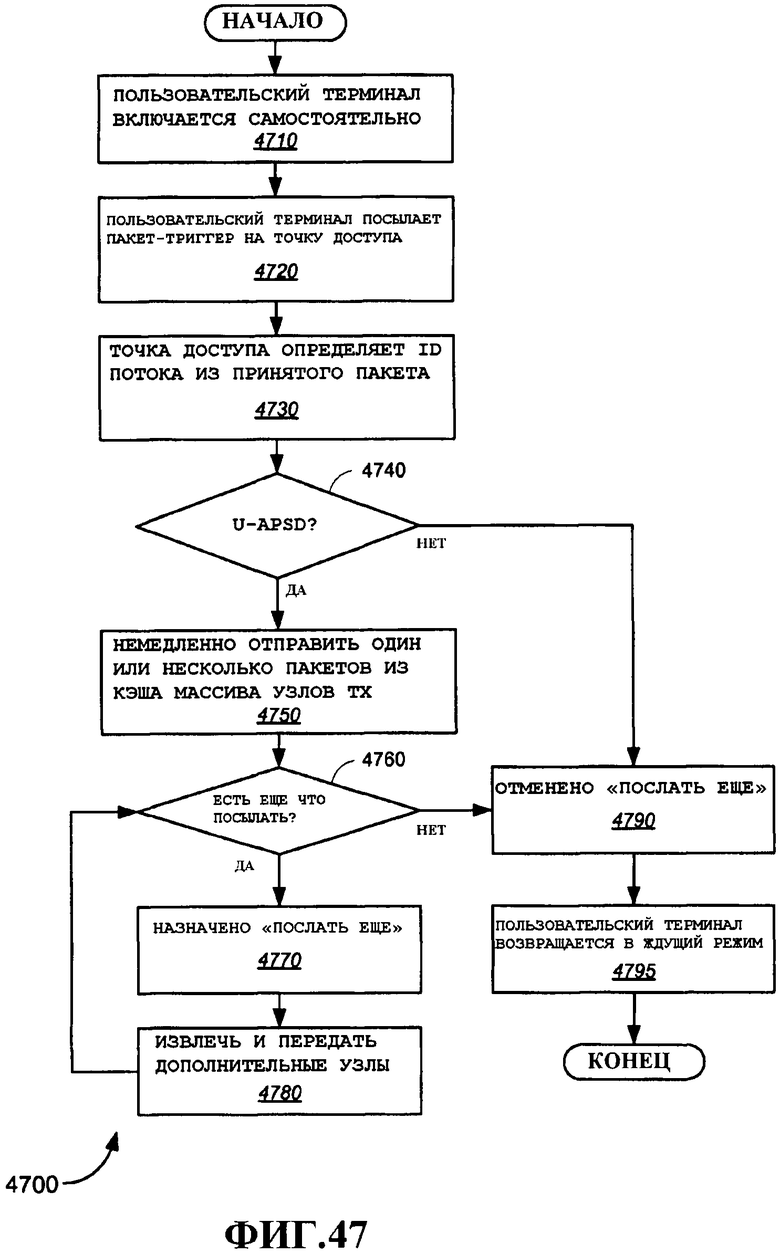

Фиг.47 - примерный вариант осуществления способа выполнения доставки незапланированного автоматического энергосбережения.

Фиг.48 - альтернативный вариант осуществления, предусматривающий более одного процессора MAC.

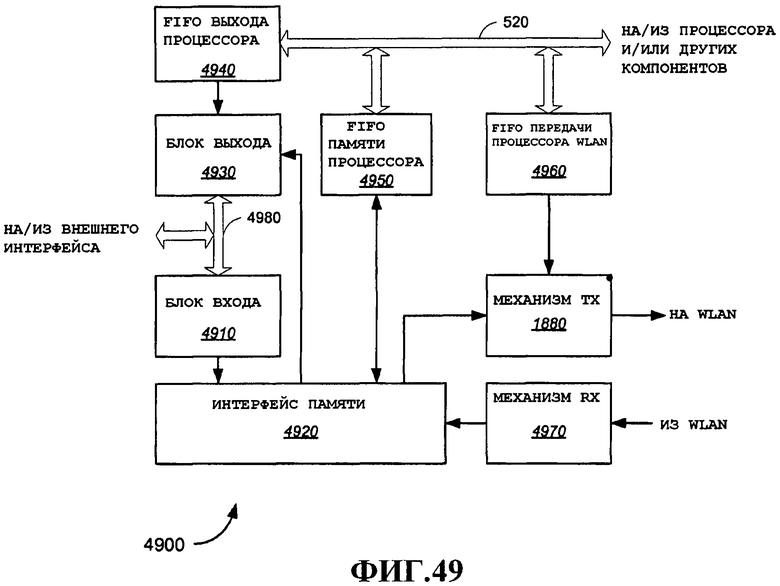

Фиг.49 - примерный вариант осуществления устройства беспроводной связи, включающего в себя два процессора MAC, включая первый процессор MAC и второй процессор MAC, реализованные в микропроцессоре.

Фиг.50 - аспекты многопоточной буферизации и очередизации пакетов.

Фиг.51 - аспекты многопоточной буферизации и очередизации пакетов.

Фиг.52 - аспекты управления памятью для высокоскоростного управления доступом к среде.

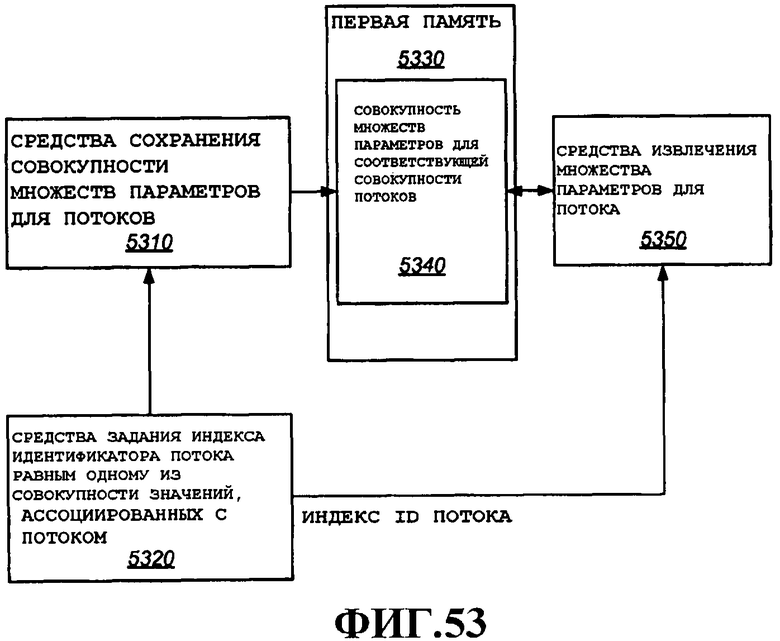

Фиг.53 - аспекты многопоточного управления доступом к середе.

Фиг.54 - аспекты многопоточного управления доступом к середе.

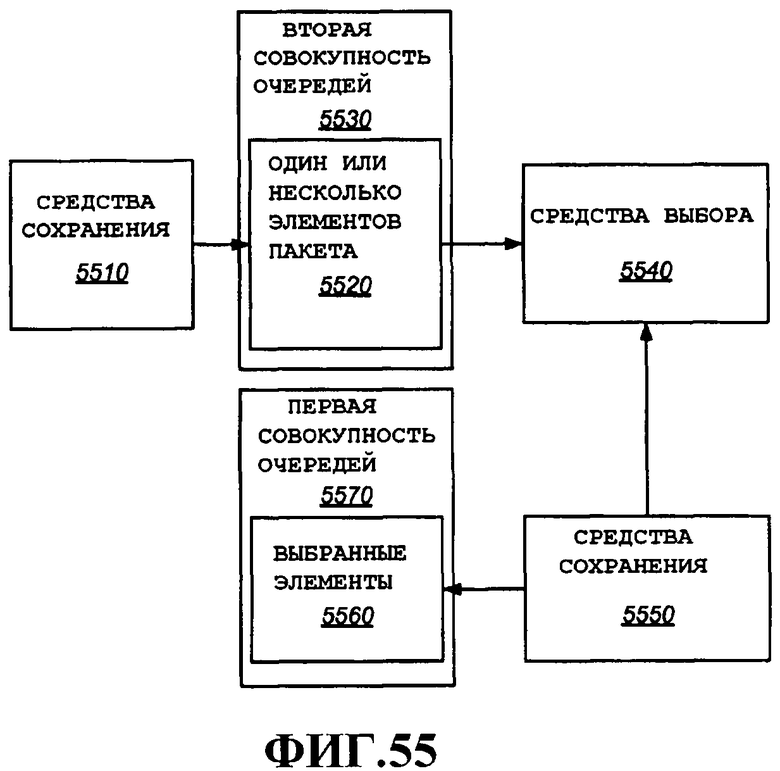

Фиг.55 - аспекты мультиплексирования множества потоков для высокоскоростного управления доступом к среде.

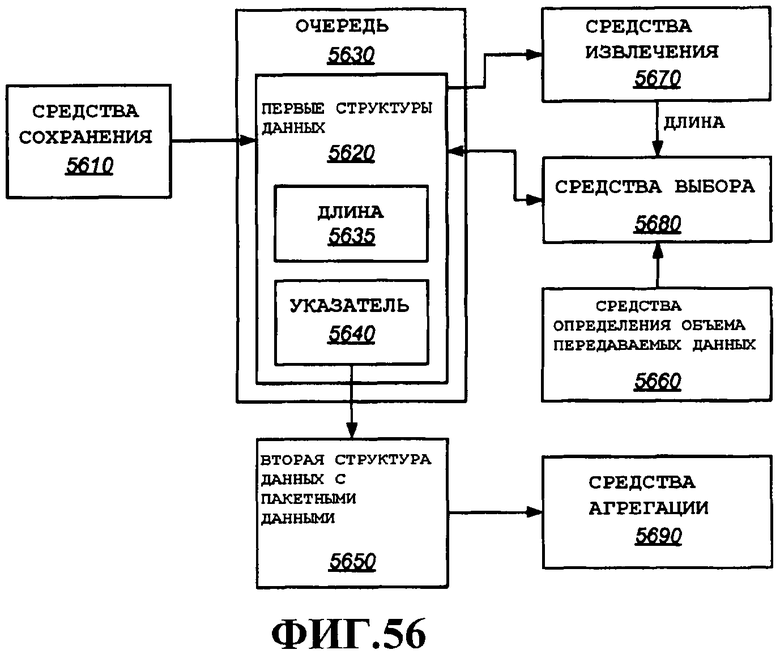

Фиг.56 - аспекты агрегации в высокосортной системе связи.

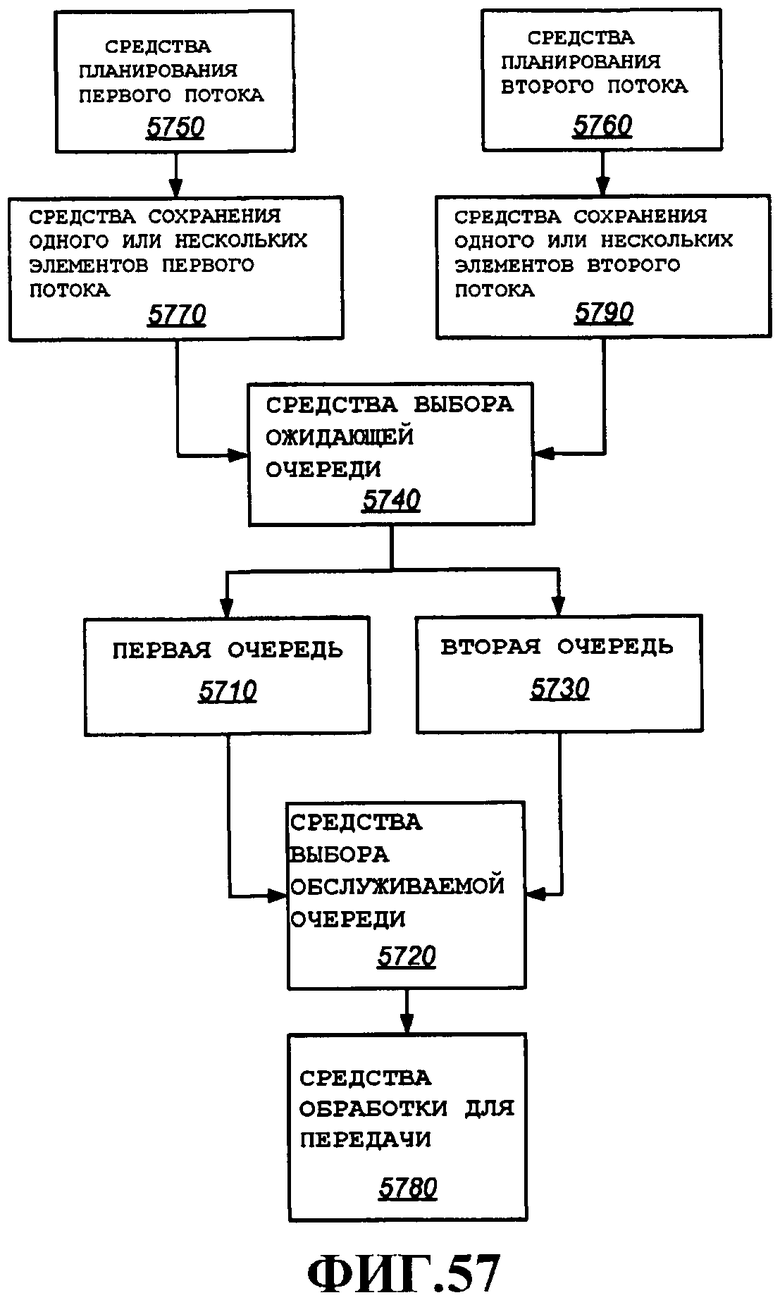

Фиг.57 - аспекты теневых кэшей, выступающих в качестве обслуживаемых очередей и ожидающих очередей.

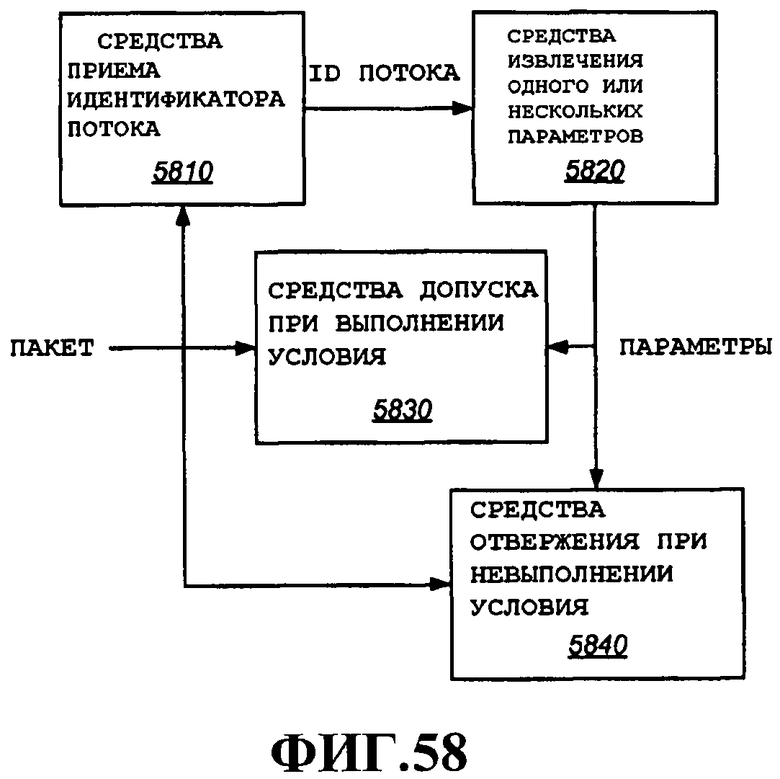

Фиг.58 - аспекты политики входа.

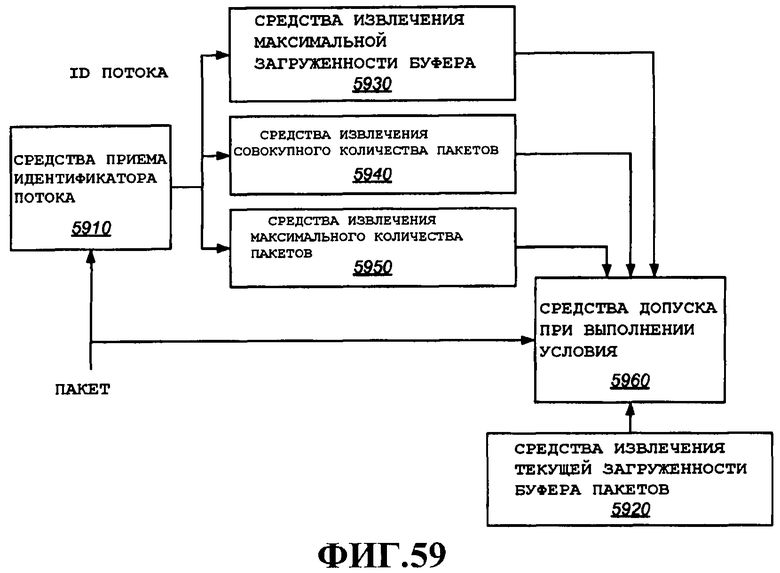

Фиг.59 - аспекты политики входа.

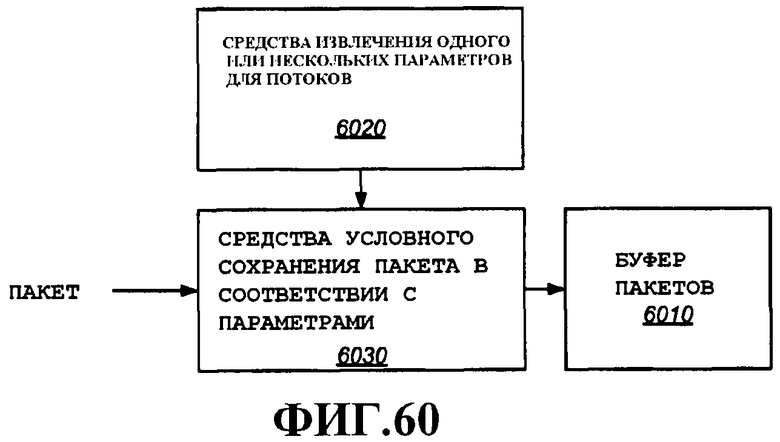

Фиг.60 - аспекты политики входа.

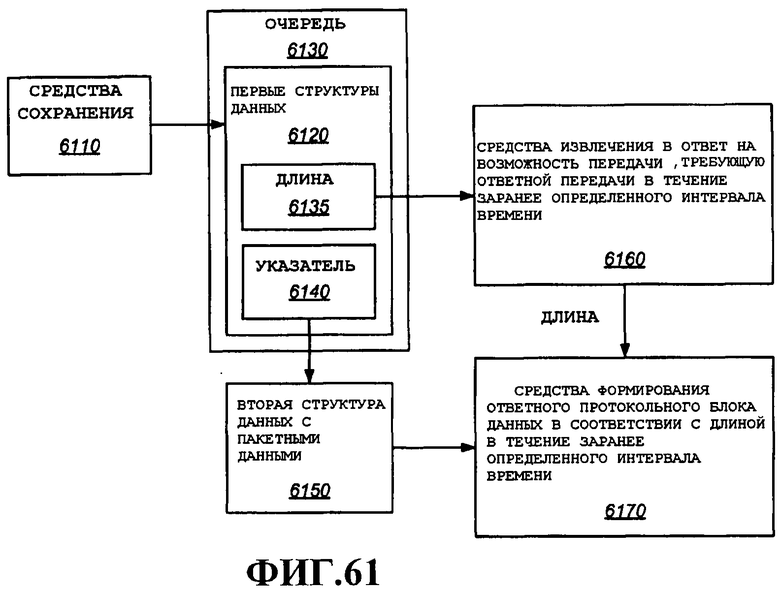

Фиг.61 - аспекты управления доступом к среде для ответа с низкой задержкой.

Подробное описание

Ниже будут подробно описаны различные аспекты, один или несколько из которых можно комбинировать в любом данном варианте осуществления. Раскрытые здесь аспекты поддерживают высокоэффективную работу WLAN с очень высокой скоростью передачи битов на физических уровнях (или аналогичные приложения с использованием новых технологий передачи). Примерная WLAN способна работать в двух частотных диапазонах, 20 МГц и 40 МГц. Она поддерживает скорости передачи битов свыше 100 Мбит/с (миллионов бит в секунду) в том числе до 300 Мбит/с на канале с полосой 20 МГц, и до 600 Мбит/с на канале с полосой 40 МГц. Также поддерживаются различные альтернативные WLAN, включая имеющие более двух частотных диапазонов, и любое количество скоростей передачи битов.

Различные аспекты сохраняют простоту и устойчивость работы распределенной координации традиционных систем WLAN, примеры которых приведены в 802.11 (a-g). Преимущества различных вариантов осуществления сочетаются с поддержанием обратной совместимости с такими традиционными системами. (Заметим, что, в нижеприведенном описании, 802.11 системы можно описывать как примерные традиционные системы. Специалистам в данной области техники очевидно, усовершенствования также могут быть совместимы с альтернативными системами и стандартами.)

Один или несколько описанных здесь примерных аспектов изложены применительно к системе беспроводной передачи данных. Хотя использование в этом контексте является преимущественным, другие варианты осуществления раскрытия могут быть включены в другие окружения или конфигурации. В общем случае, различные системы, описанные здесь, можно формировать с использованием процессоров с программным управлением, интегральных схем или дискретной логики. Данные, инструкции, команды, информация, сигналы, биты, символы и чипы, которые могут упоминаться на протяжении заявки, предпочтительно представлять напряжениями, токами, электромагнитными волнами, магнитными полями или частицами, оптическими полями или частицами, или их комбинацией. Кроме того, блоки, показанные в каждой блок-схеме, могут представлять оборудование или этапы способа. Этапы способа можно менять местами, не выходя за рамки объема настоящего раскрытия. Слово "примерный" используется здесь в смысле "служащий примером, вариантом или иллюстрацией". Любой вариант осуществления, описанный здесь как "примерный", не обязательно рассматривать как предпочтительный или преимущественный над другими вариантами осуществления.

На фиг.1 показаны примерные варианты осуществления системы 100, содержащей точку 104 доступа (AP), подключенную к одному или нескольким пользовательским терминалам (UT) 106A-N. В соответствии с терминологией 802.11, в этом документе AP и UT также именуются станциями или STA. Описанные здесь методы и аспекты также применимы к другим типам систем (примеры включают в себя стандарты сотовой связи, подробно описанные выше). Используемый здесь термин «базовая станция» можно использовать взаимозаменяемо с термином «точка доступа». Термин «пользовательский терминал» можно использовать взаимозаменяемо с терминами «пользовательское оборудование» (UE), «абонентский блок», «абонентская станция», «терминал доступа», «удаленный терминал», «мобильная станция» или другие соответствующие термины, известные в технике. Термин «мобильная станция» охватывает стационарные беспроводные применения.

Заметим также, что пользовательские терминалы 106 могут осуществлять связь непосредственно друг с другом. Direct Link Protocol (DLP), заданный в 802.11(e), позволяет STA передавать кадры непосредственно на другую STA назначения с помощью Basic Service Set [базового набора услуг] (BSS) (управляемого той же AP). В различных вариантах осуществления, как известно в технике, точка доступа не требуется. Например, Independent [независимый] BSS (IBSS) можно формировать с помощью любой комбинации STA. Можно формировать специализированные сети пользовательских терминалов, которые осуществляют связь друг с другом по беспроводной сети 120 с использованием любого из многочисленных форматов связи, известных в технике.

AP и UT осуществляют связь по беспроводной локальной сети (WLAN) 120. Согласно вариантам осуществления, подробно описанным ниже, WLAN 120 представляет собой высокоскоростную систему MIMO OFDM. Однако WLAN 120 может быть любой беспроводной LAN. В необязательно порядке, точка 104 доступа осуществляет связь с любым количеством внешних устройств или процессов по сети 102. Сетью 102 может быть Интернет, интрасеть или любая другая проводная, беспроводная или оптическая сеть. Соединение 110 переносит сигналы физического уровня из сети на точку доступа 104. Устройства или процессы могут быть подключены к сети 102 или как UT (или через соединения с ними) в WLAN 120. Примеры устройств, которые могут быть подключены либо к сети 102, либо к WLAN 120, включают в себя телефоны, карманные персональные компьютеры (PDA), компьютеры различных типов (портативные компьютеры, персональные компьютеры, рабочие станции, терминалы любого типа), видео-устройства, например, фотоаппараты, видеокамеры, веб-камеры и, в принципе, устройство обработки данных любого другого типа. Процессы могут включать в себя передачу речи, видео, данных и т.д. Различные потоки данных могут иметь изменяющиеся требования к передаче, которые могут удовлетворяться с использованием различных методов качества обслуживания (QoS).

Систему 100 может быть обеспечена централизованной AP 104. В одном варианте осуществления все UT 106 осуществляют связь с AP. В альтернативном варианте осуществления, может быть обеспечена непосредственная равноправная связь для двух UT, благодаря модификациям системы, которые очевидны специалистам в данной области техники, примеры которых проиллюстрированы ниже. Любую станцию можно настроить в качестве обозначенной AP согласно вариантам осуществления, поддерживающим обозначенные точки доступа. Управление доступом может осуществляться посредством AP или специально (т.е. на конкурсной основе).

В одном варианте осуществления, AP 104 обеспечивает адаптацию к Ethernet. В этом случае, можно обеспечить IP-маршрутизатор помимо AP для обеспечения соединения с сетью 102 (детали не показаны). Кадры Ethernet можно переносить между маршрутизатором и UT 106 по подсети WLAN (подробно описанной ниже). Адаптация и возможность подключения к Ethernet хорошо известны в технике.

В альтернативном варианте осуществления, AP 104 обеспечивает адаптацию к IP. В этом случае, AP выступает в роли шлюзового маршрутизатора для множества подключенных UT (детали не показаны). В этом случае, AP 104 может маршрутизировать датаграммы IP на UT 106 и от них. Адаптация и возможность подключения к IP хорошо известны в технике.

На фиг.2 показаны аспекты устройства беспроводной связи, которое можно сконфигурировать как точку доступа 104 или пользовательский терминал 106. Устройство беспроводной связи является примером STA, пригодной для внедрения в системе 100.

Процессор 210 обеспечен для осуществления различных задач для устройства беспроводной связи, включающих в себя задачи осуществления связи. В этом примере, процессор 210 выполняет задачи, которые называются здесь заданиями "программно-аппаратного обеспечения". Для простоты, согласно вариантам осуществления, подробно описанным ниже, ссылка на программно-аппаратное обеспечение включает в себя такие задачи, осуществляемые процессором 210, а также задачи, осуществляемые совместно с различными другими компонентами или блоками. Процессор 210 может представлять собой микропроцессор общего назначения, цифровой сигнальный процессор (DSP) или процессор специального назначения. Процессор 210 может быть соединен со специальным оборудованием для помощи в различных задачах (детали не показаны). Различные приложения могут выполняться на внешне подключенных процессорах, например, внешне подключенном компьютере или по сетевому соединению, могут выполняться на дополнительном процессоре (не показан) в устройстве беспроводной связи 104 или 106, или могут выполняться на самом процессоре 210.

Показано, что процессор 210 соединен с памятью 220, которую можно использовать для хранения данных, а также инструкций для выполнения различных описанных здесь процедур и методов, и многого другого. Специалистам в данной области техники, очевидно, что память 220 может состоять из одного или нескольких компонентов памяти различных типов, которые, полностью или частично, могут быть встроены в процессор 220. Показано, что к процессору 210 подключен блок ввода/вывода 230, который может содержать один или несколько функций ввода и/или вывода, примеры которых хорошо известны в технике.

Процессор 240 управления доступом к среде (MAC) подключен к процессору 210. Во многих вариантах осуществления, подробно описанных ниже, процессор 240 MAC осуществляет высокоскоростную обработку пакетов, т.е. на скорости линии. В общем случае, обработка на более низкой скорости, или "программно-аппаратные" задачи, будут осуществляться процессором 210 совместно с обработкой "на скорости линии", обычно производимой процессором 240 MAC. Процессор 240 MAC доставляет данные для передачи на физический уровень (PHY) 260 для передачи по WLAN 120, и обрабатывает данные из PHY 260, принятые на WLAN 120. Процессор 210 также может принимать данные физического уровня и обрабатывать данные для формирования пакетов для исходящих потоков (в целом, совместно с процессором 240 MAC, в примерах, подробно описанных ниже). Формат данных, поступающих на PHY 260 и принимаемых оттуда, будет соответствовать техническому описанию системы связи или систем, поддерживаемых устройством 104 или 106 беспроводной связи.

Процессор 240 MAC принимает и передает данные через соединение 110 согласно требованиям физического уровня сети 102. Необязательный сетевой процессор 280 можно обеспечить для приема и передачи согласно физическому уровню сети 102 на необязательном сетевом соединении 110. Сетевой процессор может принимать и передавать данные на процессор 240 MAC с использованием любого типа формата данных. Примерные пакеты данных дополнительно подробно описаны ниже (эти и альтернативные форматы данных хорошо известны специалистам в данной области техники). Эти данные можно называть здесь потоками. Потоки могут иметь разные характеристики и могут требовать различной обработки на основании типа приложения, связанного с потоком. Например, видео или голос можно охарактеризовать как потоки с низкой задержкой (видео, в целом, отличается более высокими требованиями к пропускной способности, чем голос). Многие приложения передачи данных менее чувствительны к задержке, но могут иметь более высокие требования к целостности данных (т.е. при передаче голоса может быть допустима некоторая потеря пакетов, а при передаче файлов потеря пакетов, в целом, недопустима).

Процессор 240 MAC принимает данные потока, и этот процесс мы будем называть входом, и сохраняет пакеты данных потока в буфере 250 пакетов. Процессор 240 MAC извлекает пакеты для передачи по WLAN 120, именуемые пакетами передачи или TX, и доставляет их на PHY 260. Пакеты, принятые по WLAN 120, именуемые пакетами приема или RX, поступают из PHY 260 на процессор 240 MAC, который сохраняет их в буфере 250 пакетов. Процессор 240 MAC извлекает пакеты приема из буфера 250 пакетов для доставки по сетевому соединению 110 (или на необязательный сетевой процессор 280), и этот процесс будем называть выходом. Примерные варианты осуществления буфера 250 пакетов подробно описаны ниже. Различные варианты осуществления, подробно описанные ниже, раскрывают аспекты осуществления высокоскоростной обработки пакетов для входа, передачи, приема, и выхода.

Хотя в показанном примере сеть 110 идентифицирует вход и выход, и WLAN 120 идентифицирует RX и TX, процессор 240 MAC можно надлежащим образом применять для работы с любой функцией выхода или входа, а также с любым типом функции приема или передачи. Классификацию потока может выполнять драйвер, который может быть включен в процессор 210 или сетевой процессор 280, или в любой другой пригодный компонент, что хорошо известно в технике. Можно обеспечить различные драйверы для обработки MAC различных типов данных, форматов, классов потока, и т.д.

Управление и сигнализация, связанные с WLAN (т.е. 802.11 или другие стандарты) также могут передаваться между AP и различными UT. Протокольные блоки данных MAC (MPDU), инкапсулированные в протокольные блоки данных физического уровня (PHY) (PPDU), передаются на PHY 260 и принимаются оттуда. MPDU также можно называть кадром. Когда один MPDU инкапсулирован в один PPDU, кадром иногда называют PPDU. Альтернативные варианты осуществления предусматривают использование любого метода преобразования, и терминология может варьироваться в альтернативных вариантах осуществления. Обратная связь, соответствующая различным ID MAC, может возвращаться с PHY 260 в различных целях. Обратная связь может содержать любую информацию физического уровня, включающую в себя поддерживаемые скорости для каналов (включающих в себя многоадресные, а также одноадресные трафик/пакеты), формат модуляции и различные другие параметры.

PHY 260 может представлять собой любой тип приемопередатчика (и может включать в себя приемник и передатчик, но также может быть внедрен в альтернативном варианте осуществления). В одном варианте осуществления, PHY 260 включает в себя приемопередатчик мультиплексирования с ортогональным частотным разделением (OFDM), который можно использовать с интерфейсом со многими входами и многими выходами (MIMO) или со многими входами и одним выходом (MISO).

MIMO и MISO известны специалистам в данной области техники. Различные иллюстративные приемопередатчики OFDM, MIMO и MISO подробно описаны в совместно рассматриваемой патентной заявке США №10/650,295, под названием "FREQUENCY-INDEPENDENT SPATIAL-PROCESSING FOR WIDEBAND MISO AND MIMO SYSTEMS", поданной 27 августа 2003 г., присвоенной правообладателю настоящей заявки, и включенной сюда посредством ссылки. Альтернативные варианты осуществления могут включать в себя системы с одним входом и многими выходами (SIMO) или с одним входом и одним выходом (SISO).

Показано, что PHY 260 соединен с антеннами 270 A-N. В различных вариантах осуществления может поддерживаться любое количество антенн. Антенны 270 можно использовать для передачи и приема по WLAN 120.

PHY 260 может содержать пространственный процессор, в связи с каждой из одной или нескольких антенн 270. Пространственный процессор может обрабатывать данные для передачи независимо для каждой антенны или совместно обрабатывать принятые сигналы на всех антеннах. Примеры независимой обработки могут основываться на оценках канала, обратной связи от UT, инверсии канала или различных других методов, известных в технике. Обработка осуществляется с использованием любого из различных методов пространственной обработки. Различные приемопередатчики этого типа могут передавать с использованием метода формирования пучка, управления положением почка, управления собственным вектором, или других методов пространственной обработки для повышения пропускной способности на и от данного пользовательского терминала. В некоторых вариантах осуществления, в которых передаются символы OFDM, пространственный процессор может содержать пространственные подпроцессоры для обработки каждой из поднесущих OFDM (также именуемых тонами), или бинов.

В примерной системе, AP (или любая STA, например UT) может иметь N антенн, а примерный UT может иметь M антенн. Таким образом, существует M x N путей между антеннами AP и UT. В технике известны различные методы пространственной обработки для повышения пропускной способности с использованием этого множества путей. В системе с пространственно-временным разнесением передачи (STTD) (также именуемой здесь "разнесением"), данные передачи форматируются и кодируются и передаются через все антенны как единый поток данных. При наличии M передающих антенн и N приемных антенн может существовать MIN(M,N) независимых каналов, которые можно формировать. Пространственное мультиплексирование позволяет использовать эти независимые пути и передавать разные данные по каждому из этих независимых путей, для повышения скорости передачи.

Известны различные методы для изучения или адаптации к характеристикам канала между AP и UT. С каждой передающей антенны можно передавать уникальные пилот-сигналы. В этом случае, пилот-сигналы принимаются на каждой приемной антенне и измеряются. Затем информация обратной связи по состоянию канала может возвращаться на передающее устройство для использования в передаче. Разложение измеренной матрицы канала по собственным векторам можно осуществлять для определения собственных состояний канала. Альтернативный метод, во избежание разложения измеренной матрицы канала по собственным векторам на приемнике, предусматривает использование управления собственным вектором пилот-канала и канала данных для упрощения пространственной обработки на приемнике.

Таким образом, в зависимости от текущих канальных условий, изменяющиеся скорости передачи данных могут быть доступны для передачи на различные пользовательские терминалы в системе. PHY 260 может определять поддерживаемую скорость на основании того, какая пространственная обработка используется на физической линии связи между AP и UT. Эта информация может передаваться обратно для использования при обработке MAC.

Согласно одному аспекту, единая специализированная интегральная схема (ASIC) предусмотрена для поддержки обработки MAC на устройствах беспроводной связи, включающих в себя как точки доступа, так и пользовательские терминалы. На фиг.3 и 4 показана в общем виде такая ASIC 310, сконфигурированная для использования на пользовательском терминале 106 и точке доступа 104, соответственно.

На фиг.3 показана примерная конфигурация ASIC процессора MAC 310 для пользовательского терминала 106. В этой конфигурации, процессор 240 MAC, описанный выше, подключен к аппаратной таблице 320. Аппаратная таблица 320 содержит, помимо прочего, параметры для каждого потока, который активен на станции. Таким образом, при осуществлении различных функций обработки MAC, примеры которых подробно описаны ниже, процессор 240 MAC обращается к аппаратной таблице 320 для извлечения параметров для каждого потока 325. Процессор 240 MAC также подключен к SRAM 330. В этой конфигурации, SRAM 330 адаптирована для осуществления функции буфера 250 пакетов. ASIC 310 процессора MAC может содержать различные другие компоненты, примеры которых подробно описаны ниже. Заметим, что, в этом варианте осуществления, буфер 250 пакетов размещен в ASIC 310 процессора MAC. Заметим, что аппаратная таблица 320 показана как отдельный блок лишь для ясности. В различных вариантах осуществления, аппаратная таблица 320 и SRAM 330 могут обе входить в состав процессора 240 MAC.

На фиг.4 показана ASIC процессора 310 MAC, сконфигурированная для использования в качестве точки доступа. Эту конфигурацию также можно использовать для станции, способной поддерживать большее количество потоков и/или более высокую пропускную способность, так называемой суперстанции. В примерах, подробно описанных ниже, суперстанцию и конфигурацию точки доступа можно просто именовать точкой доступа или конфигурацией точки доступа. В этом варианте осуществления, ASIC 310 процессора MAC 310 содержит процессор 240 MAC, аппаратную таблицу 320 и SRAM 330, как показано на фиг.3. Опять же, эти компоненты показаны отдельно лишь в целях иллюстрации, и один или несколько из них могут быть включены в процессор 240 MAC. В этой конфигурации, аппаратная таблица 320 уже не содержит все параметры для каждого потока, используемые для обработки MAC. В этом случае, указатели 335 для каждого потока содержатся в аппаратной таблице 320, причем каждый из них указывает на соответствующие параметры для каждого потока 325, которые сохраняются в SRAM 330. Заметим, что некоторые параметры для каждого потока по желанию также можно сохранять в аппаратной таблице 320. Заметим, что ту же самую ASIC 310 процессора, содержащую те же аппаратные компоненты, которые показаны, можно адаптировать к любой конфигурации для поддержки разных требований. В этом примере, SRAM 330 меняет свое назначение с буфера 250 пакетов в режиме STA, на хранилище параметров 325 для каждого потока в режиме точки доступа. Таким образом, процессор MAC 240 обращается к аппаратной таблице 320 на предмет параметров, и, в зависимости от конфигурации, будет извлекать эти параметры или следовать уровню косвенной адресации для извлечения их из SRAM 330. Программно-аппаратное обеспечение (выполняемое, например, процессором 210) может конфигурировать различные компоненты ASIC 310 процессора MAC для осуществления в первом режиме (режим станции) или во втором режиме (режиме точки доступа). Различные методы для выбора режимов хорошо известны в технике. Например, настройки регистров, сигналы выбора режима и пр., можно использовать для указания одному или нескольким компонентам текущего состояния конфигурации. Кроме того, программно-аппаратное обеспечение может заполнять аппаратную таблицу 320 и SRAM 330 по-разному, в зависимости от выбранной конфигурации.

Согласно фиг.4, внешняя память, в этом примере SDRAM 340, предусмотрена для осуществления функции буфера 250 пакетов. Таким образом, в режиме точки доступа, использование SRAM 330 для сохранения параметров для каждого потока позволяет поддерживать большее количество потоков, чем можно было бы поддерживать с использованием только аппаратной таблицы 320 (предполагая, что аппаратная таблица 320 меньше, чем SRAM 330). Размер SRAM 330 можно выбирать для удовлетворения требований буфера пакетов для устройства беспроводной связи в режиме станции. В одном варианте осуществления, этот размер также пригоден для хранения всех параметров для каждого потока, необходимых для количества потоков, поддерживаемого точкой доступа. В альтернативном варианте осуществления, SRAM 330 может иметь размер для поддержки большего количества потоков, для чего может потребоваться SRAM большего размера, чем в противном случае было бы необходимо для буфера пакетов. SDRAM 340 можно выбирать для согласования количества потоков, поддерживаемого точкой доступа. Специалистам в данной области техники очевидно, как выбирать пригодные размеры для аппаратной таблицы 320, SRAM 330 и SDRAM 340.

Таким образом, единая ASIC 310 процессора MAC может быть предназначена для поддержки множества режимов. Аппаратные компоненты можно повторно использовать в каждом режиме для обеспечения разных функций. Более подробно описанные примеры использования аппаратных таблиц и буферов пакетов проиллюстрированы ниже. Применение единой ASIC 310 процессора MAC, которую можно конфигурировать, как показано на фиг.3, позволяет уменьшить размер и снизить стоимость. Ту же ASIC 310 процессора MAC также можно использовать в более производительных устройствах, например, на точке доступа или суперстанции, добавив внешнюю SDRAM 340 и переконфигурировав ASIC 310 процессора MAC. Различные другие размеры SDRAM 340 можно выбирать в зависимости от требований к производительности для данной конфигурации.

На фиг.5 показан более подробный иллюстративный вариант осуществления устройства беспроводной связи, например, STA 104 или AP 106. В этом примере, будет описана обработка MAC для самых разнообразных примерных признаков пакета с использованием одного процессора MAC (описана в широком смысле). В альтернативном варианте осуществления, функции обработки MAC для разных типов пакетов можно распределить по двум или более процессорам MAC (примерные альтернативные варианты осуществления подробно описаны ниже со ссылкой на фиг.48 и 49).

Как и раньше, процессор 210 предусмотрен для выполнения программно-аппаратных задач. Показано примерное множество функций поддержки, которое может быть типичным в такой конфигурации. Различные альтернативные варианты осуществления очевидны специалистам в данной области техники. Процессор 210 осуществляет связь с SRAM 502 инструкций и загрузочным ROM 504 через шину 506 инструкций. Эти блоки памяти можно использовать для выполнения общеизвестного хранения и извлечения инструкций для использования в программно-аппаратной обработке на процессоре 210. Иллюстративные функции ввода/вывода и функции поддержки представлены компонентами, подключенными к шине 514. В этом примере, можно обеспечить таймеры 508 для выполнения различных функций отсчета времени. Можно обеспечить универсальный асинхронный приемник-передатчик (UART) 510. другим примером ввода/вывода является интерфейс I2C 512. В этом примере, различные вспомогательные компоненты подключены через шину 514 к контроллеру векторов прерывания (VIC) 516, который подключен к процессору 210. Таким образом, прерывания хронирования, прерывания ввода/вывода, и соответствующую обработку может осуществлять процессор 210 в соответствии с соответствующими предусмотренными функциями. В технике хорошо известны различные альтернативные функции для соединения с процессорами различных типов, что очевидно специалистам в данной области техники. Мост 518 соединяет компоненты, подключенные к шине 514, с другими компонентами, подключенными к шине 520. Таким образом, различные компоненты, подключенные к шине 520, включающие в себя процессор 210, могут передавать данные в шину 514 для доставки на соответствующие компоненты или их приема оттуда. В этом примере, арбитр 522 шины обеспечен для управления доступом к шине 520 контроллера DMA, дополнительные компоненты, подключенные к шине 526, включают в себя контроллер 524 прямого доступа к памяти (DMA), SRAM 526 данных и ведомый интерфейс 528 шины. Ведомый интерфейс 528 шины обеспечивает канал между шиной 520 и логикой и мультиплексорами форматирования 570, которые будут более подробно описаны ниже. Компоненты, описанные таким образом, могут принципиально идентифицироваться различными компонентами, например, процессором 210, памятью 220 и блоком ввода/вывода 230, описанными выше со ссылкой на фиг.2.

Компоненты, показанные на фиг.5, за исключением SDRAM 340, образуют части одного примерного варианта осуществления ASIC 310 процессора MAC, например, описанного выше на фиг.3 и 4. Эти компоненты можно сконфигурировать для использования в качестве конфигурации STA 106, подробно описанной на фиг.3, или точки доступа или конфигурации суперстанции, подробно описанной на фиг.4. В свете предыдущего рассмотрения, можно видеть, что различные компоненты, подробно описанные на фиг.5, могут образовывать участки процессора 240 MAC и аппаратной таблицы 320. Различные описанные компоненты можно конфигурировать в разных режимах для осуществления разных функций. Различные компоненты, например, процессор 210 и примерные вспомогательные компоненты 502-528 могут быть включены или не включены в иллюстративном варианте осуществления ASIC 310 процессора MAC.

Заметим, что процессор 210 и различные другие показанные компоненты могут осуществлять связь с компонентами процессора MAC через шину 520. В этом примере, процессор MAC содержит две главные функции, включающие в себя нижнее ядро MAC 540 и подсистему «хоста - WLAN», обозначенную как процессор 530 H2W. Иллюстративные варианты осуществления этих компонентов дополнительно подробно описаны ниже. Это разделение компонентов на различные части является лишь одним примером, и специалисты в данной области техники могут легко разместить различные описанные процессы и функции в альтернативных конфигурациях, которые очевидны в свете идей настоящего изобретения.

Доступ к SRAM 560 можно осуществлять через интерфейс 558 SRAM, который подключен к MUX 554. Мультиплексор 554 выбирает в качестве входа в интерфейс SRAM 558 соединение с арбитром 556 памяти или соединение с арбитром 552 памяти. Арбитр 552 памяти принимает запросы и принимает решение в отношении доступа к SRAM 560 из различных источников, включающих в себя компоненты на шине 520, а также шине 550. В этом примере, шина 550 обеспечивает прямое соединение между нижним ядром 540 MAC и памятью (SRAM) 560. Заметим, что также существует путь между этими компонентами через шину 520. В этом примере, предусмотрена дополнительная шина 550, чтобы гарантировать производительность доступа с SRAM 560 для извлечения и сохранения данных, чувствительных к времени, в и из нижнего ядра 540 MAC. Заметим, что, согласно фиг.3 и 4, SRAM 560 может выступать в роли буфера пакетов в одной конфигурации и в качестве хранилища параметров для каждого потока в другой конфигурации.

Нижнее ядро MAC 540 подключено к интерфейсу MAC/PHY 545, который можно использовать для доставки пакетов для передачи на PHY 260 и для обработки принятых пакетов от PHY 260. Примерные варианты осуществления компонентов в нижнем ядре 540 MAC дополнительно подробно описаны ниже.

Процессор 530 H2W обрабатывает пакеты входа, примерные варианты осуществления будут более подробно описаны ниже. В одном варианте осуществления, вход можно отключать от обработки входящих пакетов. В этом случае, пакеты входа можно записывать в буфер пакетов на скорости линии (т.е. на скорости входа). Обработка этих пакетов может осуществляться позже, путем чтения их из буфера пакетов. Это отключение позволяет осуществлять обработку на скорости, отличающейся от скорости линии входа. Недостаток этого подхода состоит в наличии дополнительных операций чтения и записи в буфер пакетов, поскольку пакеты нужно считывать, обрабатывать и помещать обратно в буфер пакетов для ожидания передачи. В некоторых вариантах осуществления это вынужденное снижение пропускной способности памяти может быть приемлемым. Альтернативный вариант осуществления, проиллюстрированный в нижеприведенных примерах, обеспечивает оперативную обработку пакетов входа. В этих иллюстративных вариантах осуществления, обработка MAC нужна для того, чтобы каждый пакет входа можно было форматировать для передачи на скорости линии, с единичной операцией записи в буфер пакетов (после которой следует операция чтения, когда наступает время для передачи пакета). Во втором случае, нагрузка на пропускную способность памяти снижается по сравнению с первым случаем. Специалисты в данной области техники могут легко адаптировать каждый подход к различным предусмотренным здесь аспектам в различных вариантах осуществления.

SDRAM 340 показана как компонент внешний по отношению к ASIC 310 процессора MAC в этом варианте осуществления. Это соответствует рассмотрению, приведенному выше со ссылкой на фиг.3 и 4, в котором устройства беспроводной связи, нуждающиеся в поддержке большего количества потоков (что приводит к необходимости в увеличении размера буфера пакетов, например, на точке доступа или суперстанции), можно согласовать с единой недорогой ASIC 310 процессора MAC и необязательной внешней памятью, например SDRAM 340. К SDRAM 340 можно общаться через интерфейс SDRAM 562, который подключен к арбитру 556 памяти. В альтернативном варианте осуществления, SDRAM 340 также может входить в состав ASIC 310 процессора MAC. Выделение компонентов, представленное на фиг.5, является лишь одним примером. Любой из показанных компонентов может быть включен в единую ASIC или может быть включен в одно или несколько внешних устройств, в зависимости от требований к площади каждой ASIC и желательной производительности.

В этом примере, вход и выход пакетов осуществляется через один из двух примерных внешних интерфейсов. Специалистам в данной области техники, очевидно, что помимо или вместо этих интерфейсов можно обеспечить альтернативные интерфейсы. В этом примере, интерфейс SDIO 582 и интерфейс PCI 584 предусмотрены для приема и хэндовера пакетов на внешние (или внутренние) устройства, осуществляющие связь с одним или несколькими из этих интерфейсов. Интерфейс SDIO 582 и интерфейс PCI 584 выбираются через MUX 580.

Для согласования интерфейсов с переменными скоростями, а также для предъявления изменяющихся требований к сохранению и обработке входящих и исходящих пакетов, можно обеспечить FIFO, мультиплексоры и логику форматирования для осуществления согласования по скорости и очереди для ослабления перегрузки при обращении к блокам памяти, например, SRAM 560 и SDRAM 340, и функции обработки MAC, например, процессор 530 H2W и нижнее ядро 540 MAC. Например, интерфейсы входа и выхода могут работать на более высоких скоростях относительно пропускной способности WLAN. Входящие потоки могут быть импульсными и высокоскоростными. Информация от процессора 210 или любого другого компонента, подключенного к шине 526, может поступать на другой скорости. Процессор 530 H2W и нижнее ядро 540 H2W будут генерировать запросы доступа и извлекать или сохранять данные, результирующие из этих запросов, по завершении обработки для различных задач, как дополнительно описано ниже. Таким образом, в этом примере, можно обеспечить FIFO 572 между логикой и мультиплексорами форматирования 570 и логикой и мультиплексорами форматирования 574. В одном примере, множество FIFO 572, один для буферизации данных из логики и мультиплексоров форматирования 570 в логику и мультиплексоры форматирования 574, и другой для буферизации данных в противоположном направлении, можно обеспечить для сопряжения с функциями входа и выхода (например, интерфейсом SDIO 582 или интерфейсом PCI 584). Другое множество FIFO 572, по одному в каждом направлении, можно обеспечить для поддержки данных на и из процессора 530 H2W. Еще одно аналогичное множество можно обеспечить для использования совместно с нижним ядром 540 MAC. Еще одно аналогичное множество можно обеспечить для сопряжения между компонентами на шине 520, доступ к которым осуществляется через ведомый интерфейс 528 шины. Специалистам в данной области техники очевидно, что эта конфигурация является всего лишь одним примером. Можно обеспечить различные альтернативные варианты осуществления, что очевидно специалистам в данной области техники в свете идей настоящего изобретения. Таким образом, примерный вариант осуществления устройства 104 или 106 беспроводной связи, показанного на фиг.5, служит для иллюстрации одного возможного межсоединения различных компонентов, детали которого описаны ниже. В рамках объема изобретения можно обеспечить многочисленные альтернативные конфигурации с использованием подмножеств этих компонентов и/или дополнительных компонентов (не показаны).

Буфер пакетов и управление памятью

На фиг.6 показан примерный вариант осуществления буфера 250 пакетов. В различных подробно описанных здесь иллюстративных вариантах осуществления, буфер 250 пакетов, показанный на фиг.6, иллюстрирует структуры данных и соответствующие связные списки, которые полезны для выполнения различных функций для обработки пакетов в процессоре 240 MAC. Хотя различные варианты осуществления, подробно описанные здесь, не требуют такой структуры, и в альтернативных вариантах осуществления можно обеспечить альтернативные буферы пакетов, варианты осуществления, подробно описанные в этом описании изобретения, будут использовать эти связные списки и структуры данных для иллюстрации их использования в этих различных функциях. Кроме того, буфер пакетов, например, описанный на фиг.6, можно обеспечить для использования в различных альтернативных функциях, помимо подробно описанных здесь. Специалисты в данной области техники могут легко адаптировать этот буфер пакетов и компоненты и их подкомпоненты в различных вариантах осуществления, включающие в себя те, для которых требуется относительно высокоскоростная обработка пакетов. Примерный буфер 250 пакетов может включать в себя дополнительные структуры данных, не показанные на фиг.6, которые дополнительно подробно описаны на фиг.7, описанной ниже.

В этом примере, каждый пакет сохраняется в буфере 250 пакетов с использованием двух типов структур данных, причем первая структура данных называется здесь узлом 610, и вторая структура данных называется здесь куском 620. Каждый пакет или фрагмент пакета (если обеспечена фрагментация, например описанная в 802.11(g) и (e)), включает в себя один узел 610 и один или несколько кусков 620. Количество кусков, необходимое для сохранения пакетных данных, будет варьироваться в зависимости от размера пакета или фрагмента. Таким образом, пакет располагается в буфере 250 пакетов в виде структуры связного списка, содержащей узел, указывающий на первый кусок, и, когда необходимы дополнительные куски, связный список содержит дополнительные куски, причем каждый кусок указывает на следующий кусок (за исключением последнего куска).

Одно преимущество такого разделения между узлами и кусками состоит в том, что информация, критическая для решений по управлению, может поддерживаться в узле, в то время, как сами данные поддерживаются в относительно более крупных кусках. Это позволяет использовать узлы, представляющие соответствующие пакеты, для обработки управления без необходимости доступа ко всему пакету.

Дополнительно, поступающие пакеты ввода, а также пакеты, ожидающие вывода, в целом, будут связаны с одним или несколькими потоками. Описанная структура узлов и кусков также облегчает эффективное формирование очередей пакетов в буфере пакетов, причем с каждой очередью связан соответствующий поток. Эта общая структура показана на фиг.6 в порядке примера единой очереди, содержащей различные узлы и куски. В этом примере, узлы 610A-N образуют связный список, ассоциированный с очередью для потока. Очередь имеет голову, идентифицируемую указателем 630 головы очереди, и указатель 640 хвоста очереди идентифицирует последний узел в очереди. В этом примере, в очереди существует N пакетов, с каждым из которых ассоциирован узел 610. Показано, что каждый узел 610 содержит ряд кусков 620A-M. С одним узлом может быть связано любое количество кусков. Остальные куски, показанные на этой фигуре, просто обозначены 620. Специалистам в данной области техники очевидно, что можно обеспечить узлы различных размеров, а также куски различных размеров. В примерном варианте осуществления, кусок имеет размер 512 байтов. Таким образом, поскольку примерные пакеты обычно имеют размер менее 2 кбайт, самое большее, 4 куска потребуется для каждого пакета (обычно меньше), включающего в себя заголовок пакета и другую ассоциированную с ним информацию. В альтернативных вариантах осуществления можно обеспечить любой размер куска в соответствии с любым размером пакета.

В этом примерном варианте осуществления, управление и данные разделены в памяти. Для передачи и приема могут потребоваться ряд манипуляций со структурами управления. Однако для полезных данных, осуществляется только одна операция записи в память (после входа или приема из WLAN) и одна операция чтения из этой памяти (после передачи по WLAN или выхода через внешний интерфейс). Таким образом, можно снизить требования к пропускной способности памяти, поскольку перенос в и из памяти относительно эффективны.

На фиг.6 показан примерный узел 610. Узел 610 содержит указатель 612 следующего узла, который используется для указания следующего узла в очереди. Включены поле 614 длины и порядковый номер 616. Эти поля полезны при обработке пакетов, которая дополнительно описана ниже, и позволяют осуществлять обработку MAC без обращения к данным или перемещения данных, содержащихся в кусках 620. Например, поле длины полезно для агрегации, при агрегации пакетов в TXOP. Порядковый номер полезен при отправке запроса квитирования блока. В общем случае, любую информацию пакета, полезную для обработки, можно добавлять к альтернативным вариантам осуществления узла. Узел 610 также включает в себя указатель 618 куска, который указывает на первый кусок, содержащий пакетные данные.

Эта структура позволяет гибко генерировать очереди любой длины, ограничиваясь только общим размером памяти буфера пакетов. Таким образом, могут поддерживаться различные другие типы потока, и поддерживаемое количество потоков не должно быть фиксировано. Например, несколько потоков, требующих малого количества пакетов, могут быть выделенным хранилищем, для которого потоки требуют большего количества пакетов, и, таким образом, буфер пакетов меньшего размера можно обеспечить для поддержки данного количества потоков. Альтернативно, можно обеспечить переменное количество потоков для любого данного размера памяти. Как можно видеть, очереди могут расти и сокращаться независимо, и, поскольку узлы и куски могут повторно использоваться любым потоком или пакетом, соответственно, структура предоставляет большую гибкость при очень эффективном управлении памятью.

Также показан примерный кусок 620. Данные 622 куска содержат пакет, включающий в себя любые поля заголовка, последовательности проверки кадров, и пр. Указатель 624 следующего куска включен в кусок для указания на следующий кусок в связанном списке, если таковой существует.

В одном варианте осуществления, куски имеют фиксированный размер. Благодаря этому, память буфера пакетов может содержать фиксированный участок памяти, выделенный кускам. Структура связного списка позволяет использовать любой кусок в любом связном списке пакетов. По мере прихода и ухода пакетов, куски можно с легкостью повторно использовать, без необходимости в дополнительной служебной нагрузке для управления памятью (например, повторного выделения места для пакетов другого размера и пр.). Эта структура также позволяет эффективно осуществлять обработку, благодаря чему, в общем случае, куски можно один раз записывать в буфер пакетов, где они остаются пока не будут готовы к передаче по WLAN или к хэндоверу на пункт назначения вывода. Пакеты также можно перемещать в очереди или перемещать в новые очереди, просто переписывая указатели (т.е. изменяя связный список). Это полезно при обработке пакетов для повторной передачи. Использование этих структур обеспечивает дополнительные эффективности, что будет дополнительно подробно описано ниже. Каждый связный список может использовать любой из различных терминаторов списка для последнего узла в очереди или последнего куска в пакете. В примерном варианте осуществления, первый и последний узлы в связном списке указываются заголовком и указателем хвоста, тогда как указатели куска сцепляются для указания последнего куска в пакете. В альтернативном варианте осуществления, может быть желательно добавлять количество кусков в заголовок узла совместно с длиной пакета и порядковым номером пакета. Также можно предусмотреть альтернативные варианты осуществления, включающие в себя переменные размеры куска.

На фиг.7 показана дополнительная иллюстрация буфера 250 пакетов. Различным типам структур данных можно выделять непрерывные куски памяти, хотя это не является обязательным требованием. Как описано выше, часть сегмента 730 можно выделить для узлов, и сегмент 740 можно выделить для кусков. В примерном варианте осуществления, каждый из этих сегментов является непрерывным пространством памяти, включающим в себя узлы и куски фиксированного размера, повторно используемые для любого пакета и/или потока, как описано выше. Кроме того, поддерживаются список 710 свободных указателей узла и список 720 свободных указателей куска. Различные структуры данных можно обеспечивать для списков свободных указателей, что очевидно специалистам в данной области техники. В одном примере, указатели узлов и указатели кусков можно проталкивать и выталкивать в соответствующие им списки указателей 710 или 720. Эти списки могут представлять собой, например, кольцевые буферы. После выталкивания указателя для формирования нового узла или куска, этот указатель будет продолжать использоваться, пока узел или кусок не освободится, после чего указатель снова можно будет протолкнуть для использования в будущем.

На фиг.8 показаны дополнительные компоненты, которые можно обеспечить в процессоре MAC, например в подробно описанных здесь иллюстративных вариантах осуществления. Эти компоненты не являются обязательными, но могут обеспечивать преимущества в определенных ситуациях в силу конкретных свойств используемого типа памяти. Например, в целом, имеет место задержка, связанная с доступом к SDRAM. Также могут иметь место неэффективности при осуществлении малых переносов (т.е. при извлечении или сохранении одного указателя узла или куска). С использованием определенных типов SDRAM, при выделении доступа к строке, доступа к столбцу и т.д., циклы служебной нагрузки могут превосходить циклы переноса фактических данных. Во избежание больших задержек, можно обеспечить различные кэши для извлечения сразу нескольких указателей для использования при обработке MAC. На фиг.8 приведены примеры нескольких из этих кэшей. Некоторые или все из этих кэшей можно обеспечить в различных альтернативных вариантах осуществления. Иллюстративные кэши, используемые в подробно описанных здесь вариантах осуществления, включают в себя кэш 810 указателей свободных узлов ТХ, кэш 820 указателей свободных кусков ТХ, кэш 830 указателей свободных узлов RX и кэш 840 указателей свободных кусков RX. Структуру данных, проиллюстрированную выше для пакетов, можно упростить для использования с пакетами приема, примерный вариант осуществления которой дополнительно подробно описан ниже со ссылкой на фиг.33. В общем случае, каждый из этих кэшей 810-840 принимает один или несколько указателей из соответствующих списков указателей узлов в буфере 250 пакетов для создания эффективностей. Совокупность указателей каждого типа можно одновременно извлекать из буфера пакетов. В этом примере, совокупность указателей можно выталкивать из соответствующего списка. Затем эти указатели заполняют соответствующий кэш, и единичные указатели можно выталкивать из соответствующего кэша для использования в различных компонентах обработки MAC. Использование указателей и соответствующих им кэшей будет дополнительно проиллюстрировано посредством различных подробно описанных ниже иллюстративных вариантов осуществления.

На фиг.9 представлен иллюстративный вариант осуществления способа 900 для записи пакетов в буфер пакетов и создания очередей. Очередь можно формировать с использованием структуры данных, в этом примере, связанного списка. Очереди также можно формировать в виде массивов (приведен пример массива узлов 3330, подробно описанного ниже). Этот способ пригоден для реализации совместно с буфером пакетов, например, описанным выше со ссылкой на фиг.6 и 7. Способ 900 иллюстрирует методы, которые можно использовать для записи пакетов входа в буфер пакетов. Аналогичные методы можно использовать для записи принятых пакетов в буфер пакетов для ожидания обработки хэндовера для выхода. Ниже будут дополнительно подробно описаны примерные варианты осуществления хэндовера. В необязательном порядке, также можно обеспечить кэши указателей (т.е. 810-840, представленные на фиг.8) и они также могут быть первичным источником новых указателей. Различные варианты осуществления можно обеспечить с кэшами или без них, и этот способ можно использовать с любой подобной конфигурацией, что очевидно специалистам в данной области техники.

На этапе 910 пакет принимается. На блоке принятия решения 912, узел выталкивается для ассоциирования с пакетом. На блоке принятия решения 914, если этот пакет является первым пакетом в соответствующей очереди, происходит переход к этапу 916 и обновление указателя головы очереди для указания на узел, связанный с новым пакетом (например, указатель головы очереди 630, проиллюстрированный на фиг.6). Затем происходит переход к 918. На блоке принятия решения 914, если этот пакет не является первым пакетом в соответствующей очереди, происходит переход к этапу 918.

На этапе 918 производится выталкивание указателя куска. Опять же, выталкивание узлов и кусков (условное обозначение для выталкивания соответствующего указателя) можно осуществлять непосредственно из буфера пакетов и, в частности, из списка свободных указателей узла или списка свободных указателей куска, соответственно. В иллюстративном варианте осуществления, указатели выталкиваются из кэша 810 свободных указателей узла передачи и кэша 820 указателей свободных кусков передачи (который может потребоваться пополнять по мере их истощения). На этапе 920 производится наполнение узла порядковым номером и длиной пакета и вставка указателя куска, извлеченного на этапе 918, в поле указателя куска узла (т.е., с использованием формата узла, например, узла 610, проиллюстрированного на фиг.6). На этапе 922 производится наполнение куска пакетными данными. Кусок 620, показанный на фиг.6, можно обеспечить в одном примере.

На блоке принятия решения 924, если определено, что требуется еще один кусок, потому что пакет больше, чем может поместиться в первый кусок, происходит переход к этапу 926. В противном случае, происходит переход к этапу 932. На этапе 926 производится выталкивание нового указателя куска. На этапе 928 производится запись нового указателя куска в поле указателя следующего куска предыдущего куска. На этапе 930 производится заполнение нового куска пакетными данными. В иллюстративном варианте осуществления, пакетные данные будут последовательно записываться в ряд кусков. Затем происходит возврат к блоку принятия решения 924 для определения, требуется ли еще один кусок. Этот цикл может повторяться, пока пакет не будет полностью записан в один или несколько кусков.

На этапе 932 процесс записи пакета завершается. Узел, связанный с пакетом, ставится в надлежащую очередь. Например, это можно осуществлять путем записи адреса узла, т.е. указателя, извлеченного на этапе 912, в указатель следующего узла хвостового узла. В этом примере, хвостовой узел идентифицируется указателем хвоста очереди (например, указателем хвоста очереди 640, представленного на фиг.6). На этапе 934 производится обновление указателя хвоста для указания на текущий узел, который станет хвостовым узлом.

На блоке принятия решения 936, если принимается еще один пакет, цикл возвращается к этапу 912, и процесс может повториться. Если еще один пакет не готов для записи в буфер пакетов, процесс может остановиться. Для ясности, детали ассоциирования пакета с ассоциированным с ним потоком, из которого будут извлечены соответствующая очередь и ассоциированные с ней указатели головы и хвоста, опущены. Примерные варианты осуществления ассоциирования пакетов с потоками более подробно показаны ниже.

Процессор H2W и политика входа

На фиг.10 показан примерный вариант осуществления подсистемы хост-WLAN, например, процессора 530 H2W. Пакет можно принимать из различных источников. В этом примере, в порядке иллюстрации, показаны два источника. Этот примерный вариант осуществления демонстрирует подмножество компонентов, которые могут содержаться в процессоре 530 H2W. Некоторые из компонентов, показанных на фиг.10, могут соответствовать компонентам, показанным на фиг.5, не включенным в процессор 530 H2W, и показаны для упрощения рассмотрения. Специалистам в данной области техники очевидно, что показанные компоненты и их разделение носят исключительно иллюстративный характер. Типичные пакеты входа, в этом примере, поступают из внешнего интерфейса, например, интерфейса SDIO 582 или интерфейса PCI 584, представленных на фиг.5. Другой примерный пакет может поступать из процессора 210 или любого другого компонента, подключенного к шине 520, как показано на фиг.5. Пакеты внешнего интерфейса поступают в процессор 530 H2W через внешний интерфейс 1006. Пакеты из шины 520, например, могут поступать через интерфейс процессора 1002. Можно обеспечивать FIFO для временного хранения одного или нескольких пакетов для обработки. Например, можно обеспечить FIFO 1004 и 1008 для временного хранения пакетов, принятых от интерфейса процессора 1002 или внешнего интерфейса 1006, соответственно. Блок 1004 можно обеспечить для временного хранения пакетов администрирования и управления, поступающих от процессора, которые необходимо передавать по WLAN. В альтернативном варианте осуществления, подробно описанном ниже со ссылкой на фиг.48, интерфейс процессора 1002 и соответствующие компоненты можно опустить, поскольку традиционные пакеты и другие пакеты более низкой пропускной способности (например) обрабатываются на процессоре 210 (или другом альтернативном процессоре MAC), и поэтому этот интерфейс может быть не нужен.

В этом примере, MAC-адрес назначения, совместно с идентификатором потока трафика [Traffic Stream Identifier] (TSID), используются для уникальной идентификации потока. В альтернативных вариантах осуществления можно обеспечить другие механизмы для отображения потока. Как упомянуто выше, обычно имеется драйвер для выполнения классификации потоков, который может действовать на уровне программно-аппаратного обеспечения, или на некотором другом внешнем процессоре. Драйвер может генерировать MAC-адрес с адресом назначения (DA), TSID, и адресом источника. В этом примере, DA и TSID можно использовать для идентификации потока. DMAC-TSID поступает на блок 1020 отображения потока, из которого возвращается ID потока, соответствующий DMAC-TSID.

Примерные варианты осуществления блока 1020 отображения потока могут использовать любой тип поисковой или другой функции для определения ID потока из данной информации идентификации. Один пример показан на фиг.10B. В примерном варианте осуществления, желательно отключать взаимодействие на уровне программно-аппаратного обеспечения от обработки на скорости линии, как описано выше. Однако может случиться так, что программно-аппаратное обеспечение пригодно для создания таблиц для отображения потока. Для отключения взаимодействия на уровне программно-аппаратного обеспечения, предусмотрены две теневые таблицы потока, таблица 1 1092 и таблица 2 1096. Процессор 530 H2W использует одну теневую таблицу, выбранную коммутатором 1090, тогда как программно-аппаратное обеспечение может обновлять другую теневую таблицу, выбранную коммутатором 1099. Таким образом, можно обеспечить пинг-понговый метод, благодаря чему программно-аппаратное обеспечение обновляет одну таблицу, тогда как другая используется для обработки MAC. Каждая теневая таблица 1092 или 1096 потока содержит элементы списка DMAC-TSID с соответствующими ID потоками. Теневая таблица потока 1 1092 содержит DMAC-TSID 1093A-N, ассоциированные с ID потока 1094A-N. Теневая таблица потока 2 1096 содержит DMAC-TSID 1097A-N, ассоциированные с ID потока 1098A-N. Таким образом, блок 1020 отображения потока доставляет DMAC-TSID в активную выбранную теневую таблицу потока, и ID потока возвращается. В примерном варианте осуществления, для выполнения быстрого поиска ID потока выполняется двоичный поиск. Программно-аппаратное обеспечение хорошо подходит для упорядочения полей DMAC-TSID для облегчения двоичного поиска. Специалистам в данной области техники очевидны альтернативные процедуры отображения потока, которые можно заменить в альтернативных вариантах осуществления.

Согласно фиг.10A, ID потока поступает в таблицу 1030 состояний потока ТХ, примерный вариант осуществления которой подробно описан ниже со ссылкой на фиг.11. Таблица 1030 состояний потока ТХ содержит различные параметры для каждого потока. Физическое местоположение таблицы 1030 состояний потока ТХ может варьироваться, как описано выше со ссылкой на фиг.3 и 4. Например, в одной конфигурации, таблица состояний потока ТХ может храниться в виде аппаратной таблицы, в процессоре 530 H2W. В альтернативном варианте осуществления аппаратная таблица может размещаться в нижнем ядре 540 MAC, детали не показаны, и оба блока 530 и 540 могут совместно использовать одну и ту же аппаратную таблицу. Альтернативно, каждый из блоков 530 и 540 может поддерживать части аппаратной таблицы, что в общем виде представлено на фиг.3 и 4. Из доставленного ID потока можно выбирать участок таблицы 1030 состояний потока ТХ, соответствующий ID потока и извлекать различные параметры. Примерные параметры будут описаны в этих вариантах осуществления.

Некоторые параметры могут поступать на блок 1010 политики. Примерные варианты осуществления блока политики дополнительно подробно описаны ниже. Если предусмотрено шифрование, блок шифрования, в этом примере код целостности сообщения [Message Integrity Code] (MIC), 1025, может иметь ключи, доставляемые для использования при шифровании.

На блоке 1025 MIC, из поступающих ключей и данных в части полезной нагрузки пакета, может генерироваться вычисление MIC. В этом варианте осуществления, отдельный компонент используется для осуществления шифрования полезной нагрузки (см. механизм 2210 традиционного протокола, подробно описанный ниже). Альтернативные методы шифрования хорошо известны в технике и могут использоваться вместо описанных выше.

Другие параметры можно доставлять на блок 1035 присоединения заголовка для создания заголовка. Сгенерированный заголовок может включать в себя поля для использования в самом заголовке пакета, а также значения управления для использования, в то время как пакет проходит через функции обработки MAC. Эти значения управления можно удалять до того, как пакет поступит для передачи. Это один примерный метод поддержания информации состояния для пакета во время выполнения обработки MAC. Специалистам в данной области техники очевидны альтернативные методы поддержания состояния пакетов при выполнении на них различных функций MAC.

Блок 1010 политики, совместно с параметрами, поступающими из таблицы 1030 состояний потока, может отвергнуть пакет, и в этом случае функции шифрования, например, вычисление MIC, не будут осуществляться, и пакет может удаляться из FIFO. Примерные варианты осуществления политики входа дополнительно подробно описаны ниже. Если блок 1010 политики разрешает пакет, то полезная нагрузка совместно с частью MIC, сгенерированной в MIC 1025, если он предусмотрен, и соответствующий заголовок поступают для хранения в FIFO 1050.

На фиг.11 показан примерный вариант осуществления содержимого таблицы 1030 состояний потока ТХ. Множества параметров поддерживаются для каждого потока. Проиллюстрированы параметры одного потока. Тип 1102 пакета указывает, какого типа пакет принимается. Например, пакет может представлять собой пакет 802.11(g), (e) или (n). Другие типы пакетов могут поддерживаться и могут указываться в поле 1102 типа пакета.

Политика безопасности 1104 указывает, будут ли использоваться методы защиты (например, шифрование). Примерный вариант осуществления поддерживает AES-CCMP (Advanced Encryption Standard - Counter Mode Cipher Block Chaining Message Authentication MAC Protocol) и RC4-TKIP (Rivest's Cipher-4 - Temporal Key Integration Protocol). Адрес 1106 приемника указывает MAC-адрес приемника, для которого предназначен пакет. Порядковый номер 1108 указывает порядковый номер пакета. Ключ 1110 MIC идентифицирует ключ MIC, если предусмотрен TKIP. Контроль 1112 кадра включает в себя информацию для построения соответствующего заголовка.

Контроль 1114 качества обслуживания (QoS) можно использовать для указания уровня QoS. В примерном варианте осуществления поддерживается четыре уровня QoS. Примеры обработки очередей для различных значений QoS дополнительно проиллюстрированы ниже.

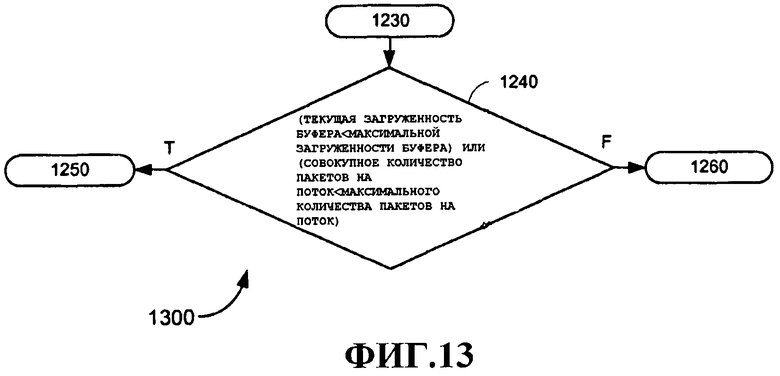

Поле 1116 «время жизни» можно использовать для указания, как долго пакет может оставаться в буфере. По истечении времени жизни пакет, например, можно очистить. Максимальная загруженность 1118 буфера, максимальное количество 1120 пакетов на поток, и совокупное количество 1122 пакетов на поток используются, в примерном варианте осуществления, для политики входа, например на блоке 1010 политики, примеры которого дополнительно подробно описаны ниже со ссылкой на фиг.12 и 13. Заметим, что глобальная переменная «Текущая загруженность буфера» можно использовать совместно с этими тремя параметрами для осуществления различных методов политики входа. Указатель 1124 хвоста очереди используется для идентификации хвостового узла, как описано выше, со ссылкой на фиг.6 и 9.

Эти переменные или параметры таблицы состояний потока ТХ приведены исключительно в целях иллюстрации. Специалистам в данной области техники очевидно, что дополнительные переменные или параметры могут быть полезны для поддержания для каждого потока и также могут быть включены. Кроме того, не все признаки необходимо поддерживать во всех вариантах осуществления, и, таким образом, можно обеспечить подмножество этих параметров.

На фиг.12 показан примерный вариант осуществления способа 1200 выполнения политики входа. Более подробное рассмотрение преимуществ политики входа приведено ниже со ссылкой на фиг.34, применительно к хэндоверу выхода и общему QoS WLAN. Как описано выше в отношении примерной таблицы 1030 состояний потока ТХ, показанной на фиг.11, различные параметры могут поддерживаться для каждого потока. Эти параметры можно регулировать, на основании уровня QoS, для более легкого одобрения или отвержения пакетов функцией политики.