Изобретение относится к вычислительной технике и может быть использовано для анализа взаимосвязи субъективных ответов респондента с его частотой сердечных сокращений (ЧСС) в процессе производимого тестирования, которая характеризует его психологическое состояние.

Заявителям неизвестно о том, чтобы такая техническая задача решалась. Это объясняется тем, что фазовая напряженность психологического состояния является основным критерием практически всех психологических опросников, а способов анализа взаимосвязи субъективных ответов респондента с его объективной ЧСС нет.

Техническим результатом заявленного решения является повышение объективности, достоверности и быстродействия проводимого тестирования за счет определения наличия и величины отклонения ЧСС респондента на каждый из вопросов теста.

Определение взаимосвязи ответов респондента с его ЧСС осуществляется следующим образом.

Общее число вопросов N теста разбивается на L групп соотносящихся вопросов (по «вопросов в каждой) для исследования конкретного признака в каждом

Респондент соотносит свое состояние с полным перечнем n признаков в L группах по ранговой шкале и фиксирует выбираемое значение i-го ранга. Таким образом, исходной информацией являются ранжированные ответы респондента:в

Aijk, i=1, …, n; j=1, …, L; k=1, …, N.

Далее вычисляются средние значения  рангов по группам исследуемых признаков. Для j-й группы формула имеет вид:

рангов по группам исследуемых признаков. Для j-й группы формула имеет вид:

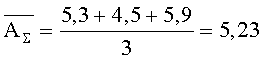

После этого определяется общий средний ранг  по следующей зависимости:

по следующей зависимости:

Эта величина позволяет судить об общепринятом в психологии показателе свойств респондента.

В дальнейшем вычисляется модуль разности Apk между  и каждым соответствующим значением Aijk:

и каждым соответствующим значением Aijk:

Затем эта величина сравнивается с допустимым значением Аpkд. Целесообразно, чтобы

Результаты этого сравнения будут использованы в последующих расчетах.

Исходной информацией для анализа ЧСС респондента является количество его сердечных сокращений за время звучания фонограммы вопроса, его обдумывания и высказывания ответа:

fijk, i=1, …,n; j=1, …, L; k=1, …, N.

Далее вычисляются средние значения  ЧСС по всем L группам:

ЧСС по всем L группам:

После этого определяется общая средняя частота  по следующей зависимости:

по следующей зависимости:

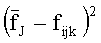

В дальнейшем осуществляется вычисление модуля разности fpk между каждым значением fijk и  :

:

Затем определяется количество f1 значений fpk1h, которые соответствуют случаю выполнения неравенства (5), а также количество f0 значений fpk0S и сами эти значения, которые не соответствуют случаю выполнения неравенства (5).

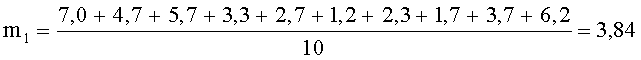

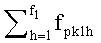

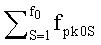

Далее необходимо найти средние величины m1 и m0 значений fpk1h и fpk0S по следующим формулам:

где h=1, …, f1,

где S=1, …, f0.

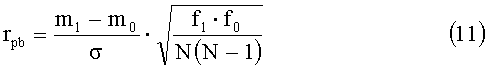

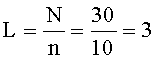

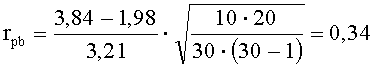

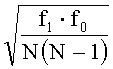

Точечно-бисериальный коэффициент корреляции rpb определяется по следующей формуле:

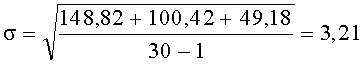

где стандартное отклонение

Этот коэффициент корреляции позволяет количественно оценить степень взаимосвязи субъективных ответов респондента и его вегетативных реакций, характеризующую его фазовую напряженность.

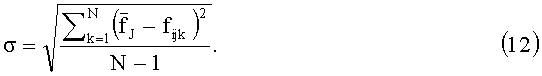

Для наглядности предложенного подхода следует привести пример. В качестве примера можно рассмотреть анкетирование респондента по широко известному опроснику САН (самочувствие, активность, настроение), приведенному в таблице 1. Тест предназначен для оперативной оценки самочувствия, активности и настроения. На основании таблицы 1 можно провести следующую классификацию вопросов:

вопросы на самочувствие - 1, 2, 7, 8, 13, 14, 19, 20, 25, 26;

вопросы на активность - 3, 4, 9, 10, 15, 16, 21, 22, 27, 28;

вопросы на настроение - 5, 6, 11, 12, 17, 18, 23, 24, 29, 30.

Респондента просят соотнести свое состояние с рядом признаков по многоступенчатой шкале. Шкала состоит из индексов (верхний ряд чисел - 3 2 1 0 1 2 3) и расположена между тридцатью парами слов противоположного значения, отражающих силу, здоровье, утомление (самочувствие), подвижность, скорость и темп протекания функций (активность), а также характеристики эмоционального состояния (настроение). Респондент должен выбрать и отметить цифру, наиболее точно отражающую его состояние.

При обработке оценки респондента производится перекодировка: индекс 3, соответствующий неудовлетворительному самочувствию, низкой активности и плохому настроению, принимается за 1 балл; следующий за ним индекс 2 - за 2; индекс 1 - за 3 балла и так до индекса 3 с противоположной стороны шкалы, который соответственно принимается за 7 баллов (нижний ряд чисел - 1 2 3 4 5 6 7, причем полюса шкалы постоянно меняются).

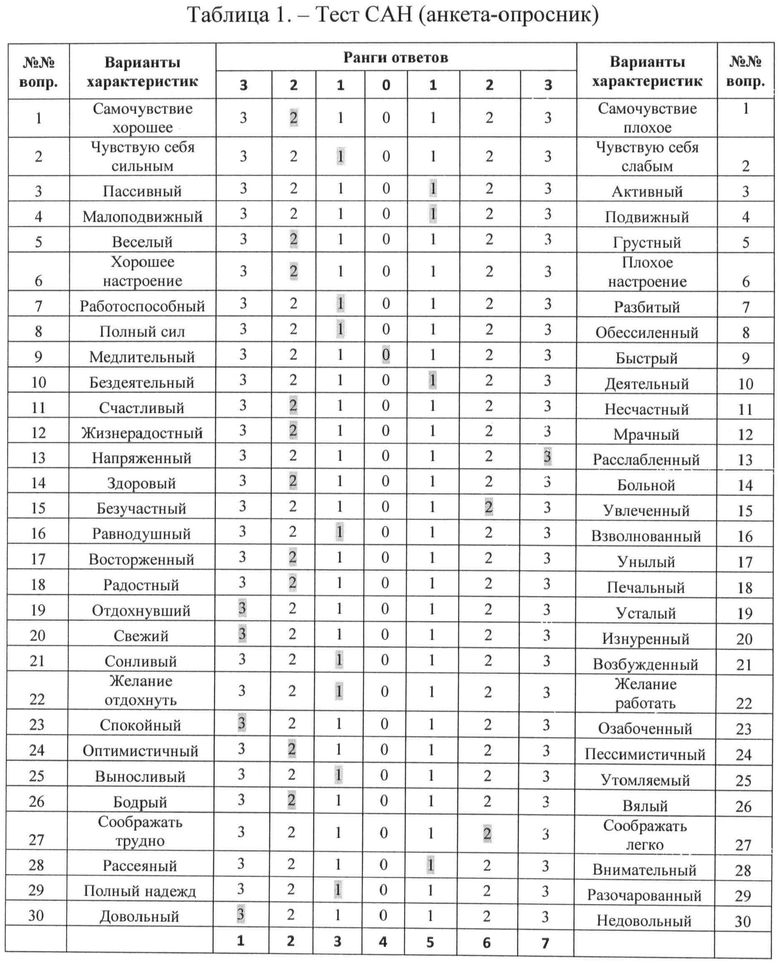

В соответствии с формулой (1) общее число вопросов N=30 теста разбивается на L групп соотносящихся вопросов (по n=10 вопросов в каждой) для исследования конкретного признака:

Респондент соотносит свое состояние с полным перечнем n признаков в L группах по ранговой шкале и фиксирует выбираемое значение ранга i-го вопроса.

Таким образом, исходной информацией для работы устройства являются ранжированные ответы респондента из таблицы 1 Aijk, (i=1, …, n; j=1, …, L; k=1, …, N).

Далее по формуле (2) вычисляются средние значения  рангов по группам исследуемых признаков (например, для L=1 имеем

рангов по группам исследуемых признаков (например, для L=1 имеем  ).

).

После этого определяется общий средний ранг  по формуле (3):

по формуле (3):

Затем вычисляются модули разности Apk между  и каждым соответствующим значением Aijk по формуле (4). Результаты вычислений сведены в таблицу 2. Рассчитанные значения величин Apk сравниваются с допустимым значением Аpkд в соответствии с формулой (5). Принимаем Apjд=1 (≈15% отклонения параметра). В случае, если Apk≤Арkд формируется сигнал логического нуля Z=0, в противоположном - логической единицы Z=1 для использования в последующих расчетах и работе устройства.

и каждым соответствующим значением Aijk по формуле (4). Результаты вычислений сведены в таблицу 2. Рассчитанные значения величин Apk сравниваются с допустимым значением Аpkд в соответствии с формулой (5). Принимаем Apjд=1 (≈15% отклонения параметра). В случае, если Apk≤Арkд формируется сигнал логического нуля Z=0, в противоположном - логической единицы Z=1 для использования в последующих расчетах и работе устройства.

По формуле (6) определяются средние значения частоты сердечных сокращений по трем группам  :

:

;

;  ;

;  .

.

Анализ ЧСС респондента проводится в соответствии с формулой (8). Исходная информация для него и промежуточные результаты этого анализа приведены в таблице 3.

Далее по формулам (9) и (10) необходимо вычислить значения m1 и m0 - средние отклонения значений ЧСС, соответствующие логическим Z=1 и Z=0 по результатам сравнения Apk и Аpkд. Результаты для расчетов представлены в таблице 4.

На основе данных таблицы 4 вычисляем по формуле (9) величину m1:

и по аналогичной формуле (10) величину m0:

m0=1,98.

Точечно-бисериальный коэффициент корреляции rpb определяется по формуле (11), но предварительно по формуле (12) надо определить стандартное отклонение ЧСС.

Для нашего случая

После этого оцениваем точечно-бисериальный коэффициент корреляции rpb:

По общей классификации корреляционных связей данное значение коэффициента свидетельствует о слабой корреляционной связи субъективных ответов респондента с его ЧСС, и, следовательно, доверять результатам его тестирования (искренности респондента) не следует.

Технический результат достигается тем, что устройство автоматической оценки фазовой напряженности респондента содержит первую и вторую группу входных регистров, каждая из которых состоит из L столбцов, включающих по n элементов каждый, третью группу входных регистров, состоящую из N элементов, первый и второй входные регистры, первую и вторую группу элементов задержки (ЭЗ), каждая из которых состоит из L столбцов, включающих каждый из них n элементов, третью и четвертую группы ЭЗ, каждая из которых состоит из N элементов, с первого по четвертый коммутаторы, первую и вторую группы накопительных сумматоров, каждая из которых состоит из L элементов, первую и вторую группу блоков деления, каждая из которых состоит из L элементов, с первого по пятый накопительные сумматоры, с первого по восьмой блоки деления, первую и вторую группы выходных регистров, каждая из которых состоит их L элементов, первый, второй и третий выходные регистры, первый и второй регистры, первый, второй и третий блоки индикации, первую и вторую группы блоков вычитания по модулю, каждая из которых состоит из L столбцов, включающих каждый из них n элементов, первую и вторую группу блоков индикации, каждая из которых состоит из L элементов, группу блоков сравнения, состоящую из N элементов, первую и вторую группы ключей, каждая из которых состоит из N элементов, первый и второй элементы ИЛИ, первый и второй счетчики, группу квадраторов и группу элементов НЕ, каждая из которых состоит из N элементов, первый, второй и третий блоки умножения, первый и второй блоки вычитания, первый и второй блоки извлечения квадратного корня, первый и второй ЭЗ, генератор тактовых импульсов и распределитель импульсов (РИ), тактовый вход которого соединен с выходом генератора тактовых импульсов, первый выход РИ, со входами записи первой, второй и третьей групп входных регистров, первого и второго входных регистров, второй выход - со входами считывания первой группы входных регистров, третий выход - со входом считывания второго входного регистра, четвертый и пятый выходы - соответственно с первым и вторым управляющими входами второго коммутатора, шестой выход - со входами записи первой группы выходных регистров, седьмой выход - со входом считывания первого входного регистра, восьмой и девятый выходы - соответственно с первым и вторым управляющими входами первого коммутатора, десятый и одиннадцатый выходы - соответственно с входами записи и считывания первого регистра, двенадцатый выход - с управляющим входом третьего коммутатора, тринадцатый выход - со входом записи первого выходного регистра, четырнадцатый и пятнадцатый выходы - со входами считывания соответственно третьей и второй групп входных регистров, шестнадцатый выход - со входами запуска первого и второго счетчиков, семнадцатый, восемнадцатый и девятнадцатый выходы - со входами записи соответственно второй группы выходных регистров, второго выходного регистра и второго регистра, двадцатый выход - со входом считывания второго регистра, двадцать первый выход - с управляющим входом четвертого коммутатора, двадцать второй выход - со входами считывания первого и второго счетчиков, двадцать третий выход - со входом записи третьего выходного регистра, двадцать четвертый выход - со входами считывания первой и второй группы выходных регистров, первого, второго и третьего выходных регистров, информационные входы первой группы входных регистров являются входами задания исходной информации, на которые поступают значения Aijk, характеризующие ранжированные ответы респондента, информационные входы второй группы входных регистров являются входами задания исходной информации, на которые поступают значения fijk, характеризующие количество сердечных сокращений респондента за время звучания фонограммы вопроса, его обдумывания и ответа, информационные входы третьей группы входных регистров являются входами задания исходной информации, на которые поступают значения Аpkд, характеризующие допустимые величины модуля разности между средним значением рангов по группам исследуемых признаков и величинами Aijk, информационные входы первого и второго входных регистров являются входами задания исходной информации, на которые поступают соответственно значение N, характеризующее общее число вопросов теста, и величина n, характеризующая количество вопросов в каждой группе, выходы первой и второй групп входных регистров соединены с входами соответственно первой и второй групп ЭЗ, выходы с первого по n-й элементов каждого из L столбцов первой и второй групп входных регистров соединены с первым по n-й входами каждого из L элементов соответственно первой и второй групп накопительных сумматоров, выходы которых подключены к входам делимого соответствующих элементов соответственно первой и второй групп блоков деления, входы делителя которых соединены соответственно с первым и вторым выходами второго коммутатора, а выходы - с информационными входами соответственно первой и второй групп выходных регистров, выходы которых подключены к входам соответственно первой и второй групп блоков индикации, выходы каждого из L элементов первой и второй групп блоков деления соединены с первым по L-й входами соответственно первого и второго накопительных сумматоров, выходы которых подключены к входам делимого соответственно второго и четвертого блоков деления, входы делителя которых соединены соответственно с первым и вторым выходами третьего коммутатора, а выходы - с информационными входами соответственно первого и второго выходных регистров, выходы которых подключены к входам соответственно первого и второго блоков индикации, каждый из L элементов первой и второй групп блоков деления соединены с входами уменьшаемого соответствующего столбца, с первого по L-й, соответственно первой и второй групп блоков вычитания по модулю, входы вычитаемого которых подключены к выходам соответственно первой и второй групп ЭЗ, выходы первой группы блоков вычитания по модулю соединены с информационными входами группы блоков сравнения, пороговые входы которых подключены к выходам соответствующих элементов третьей группы входных регистров, а выходы - к входам группы элементов НЕ и к управляющим входам первой группы ключей, информационные входы первой и второй групп ключей соединены с выходами второй группы блоков вычитания по модулю, а выходы - с входами соответственно третьей и четвертой групп ЭЗ и с первого по N-й входами соответственно третьего и пятого накопительных сумматоров, выходы которых подключены к входам делимого соответственно третьего и шестого блоков деления, входы делителя которых соединены с выходами соответственно первого и второго счетчиков, информационные входы которых подключены к выходам соответственно первого и второго элементов ИЛИ, с первого по N-й входы которых соединены с выходами с первого по N-й элементов задержки соответственно третьей и четвертой групп ЭЗ, управляющие входы второй группы ключей подключены к выходам группы элементов НЕ, выходы второй группы блоков вычитания по модулю соединены с входами группы квадраторов, выходы с первого по N-й элементов которой подключены к входам, с первого по N-й четвертого накопительного сумматора, выход которого соединен с входом делимого седьмого блока деления, вход делителя которого подключен к первому выходу четвертого коммутатора, а выход - к входу первого блока извлечения квадратного корня, выход которого соединен с входом делителя восьмого блока деления, вход делимого которого подключен к выходу второго ЭЗ, а выход - к первому входу третьего блока умножения, второй вход которого соединен с выходом первого ЭЗ, а выход - с информационным входом третьего выходного регистра, выход которого подключен к входу третьего блока индикации, вход второго ЭЗ соединен с выходом второго блока вычитания, вход первого ЭЗ подключен к выходу второго блока извлечения квадратного корня, вход которого подключен к выходу пятого блока деления, вход делителя которого соединен с выходом первого блока умножения, а вход делимого - с выходом второго блока умножения, первый и второй входы которого подключены к выходам соответственно второго и первого счетчиков, выходы первого и второго входных регистров соединены с информационными входами соответственно первого и второго коммутаторов, третий выход которого подключен к входу делителя первого блока деления, вход делимого которого соединен с первым выходом первого коммутатора, а выход - с информационным входом первого регистра, выход которого подключен к информационному входу третьего коммутатора, второй и третий выходы которого соединены соответственно с первым входом первого блока умножения и с входом уменьшаемого первого блока вычитания, выход которого подключен к информационному входу второго регистра, выход которого соединен с информационным входом четвертого коммутатора, второй выход которого подключен ко второму входу первого блока умножения, входы уменьшаемого и вычитаемого второго блока вычитания соединены с выходами соответственно третьего и шестого блоков деления.

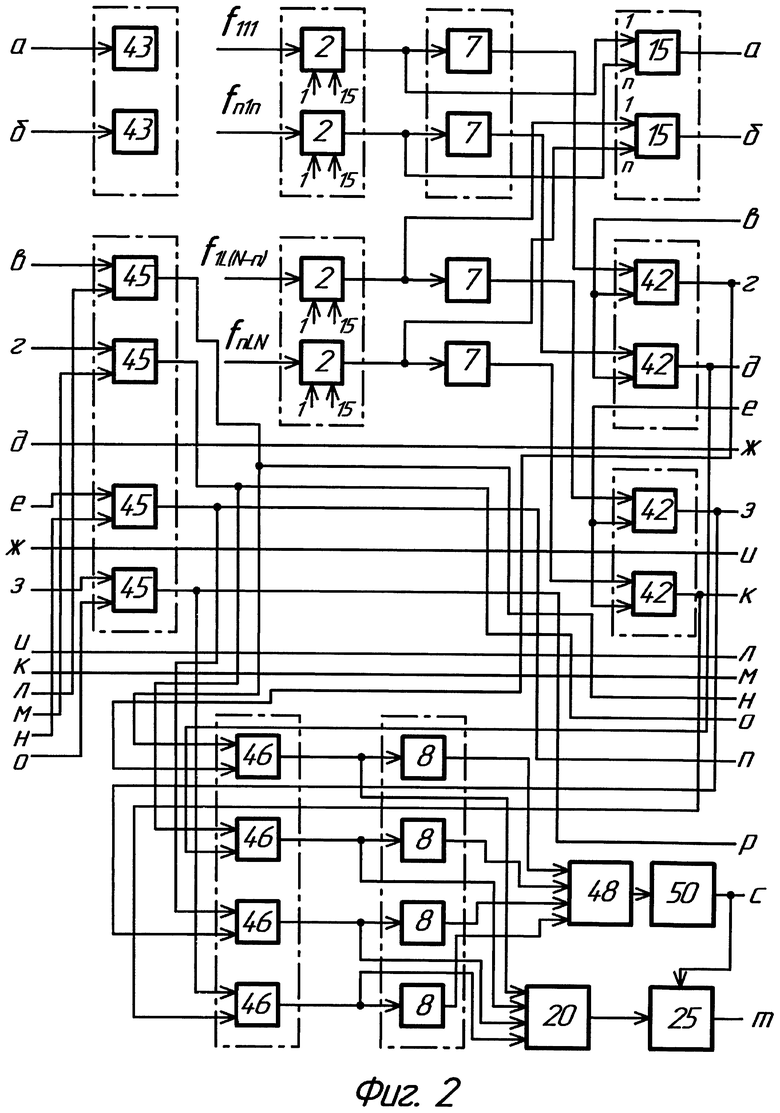

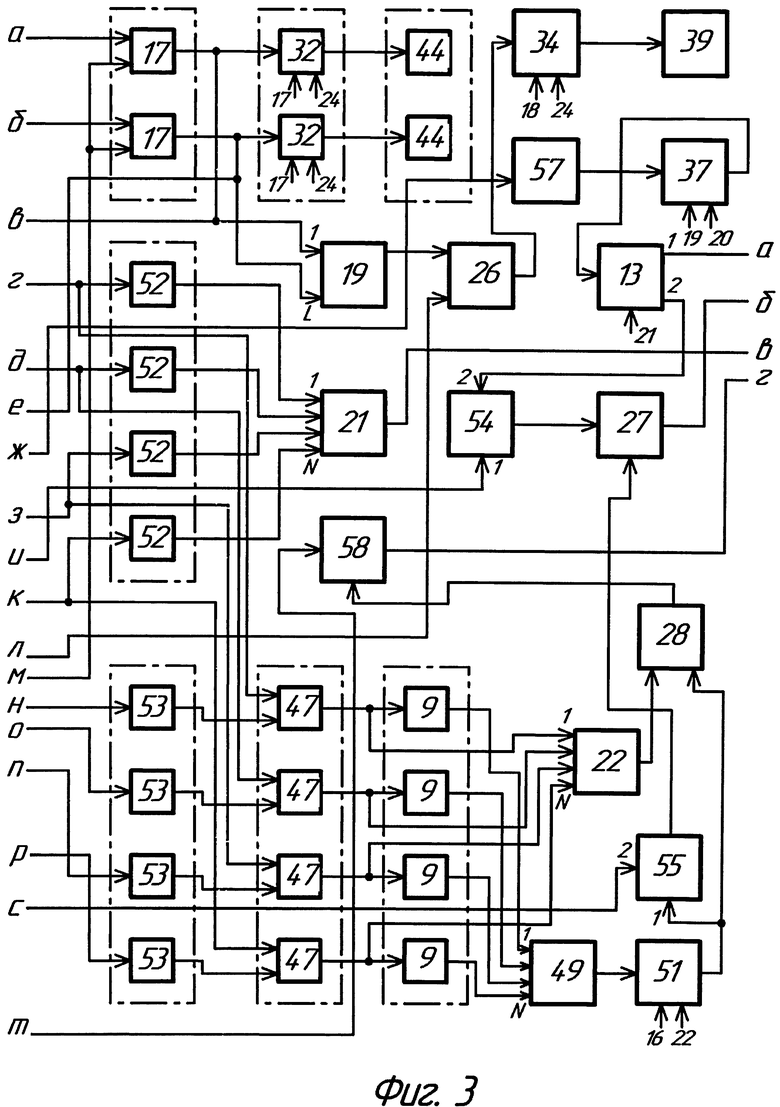

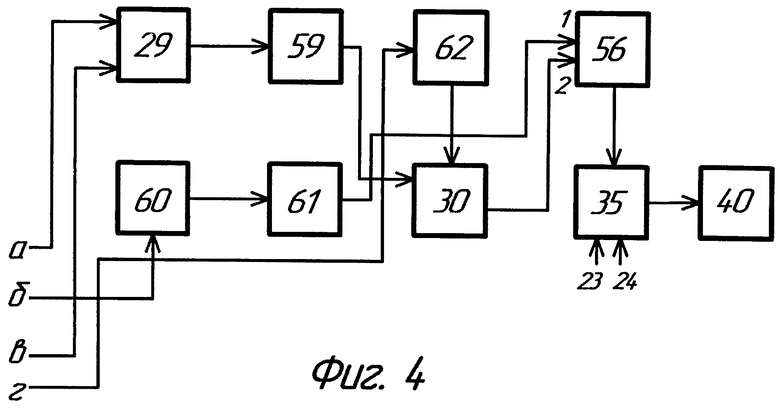

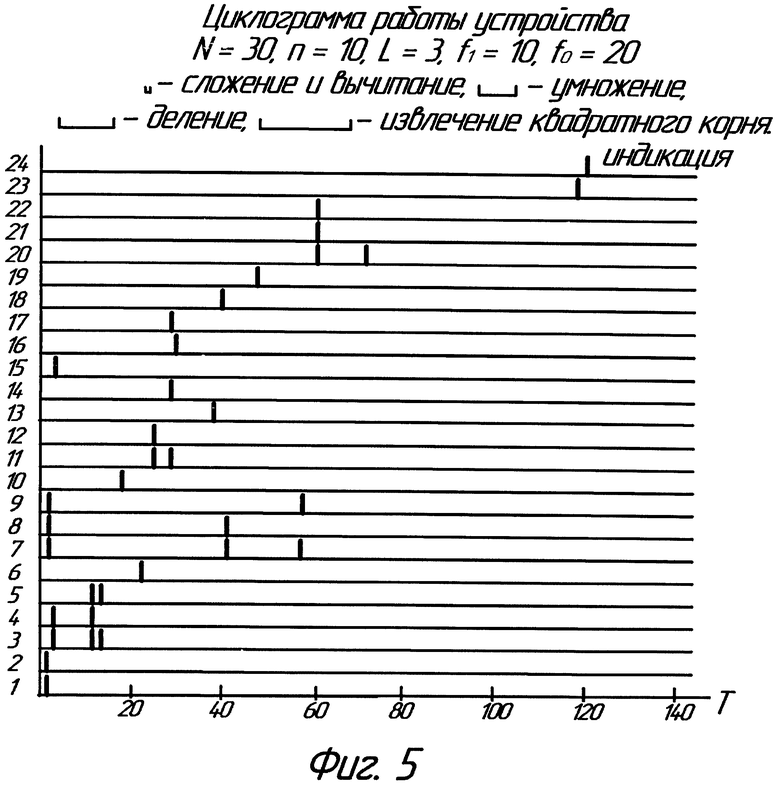

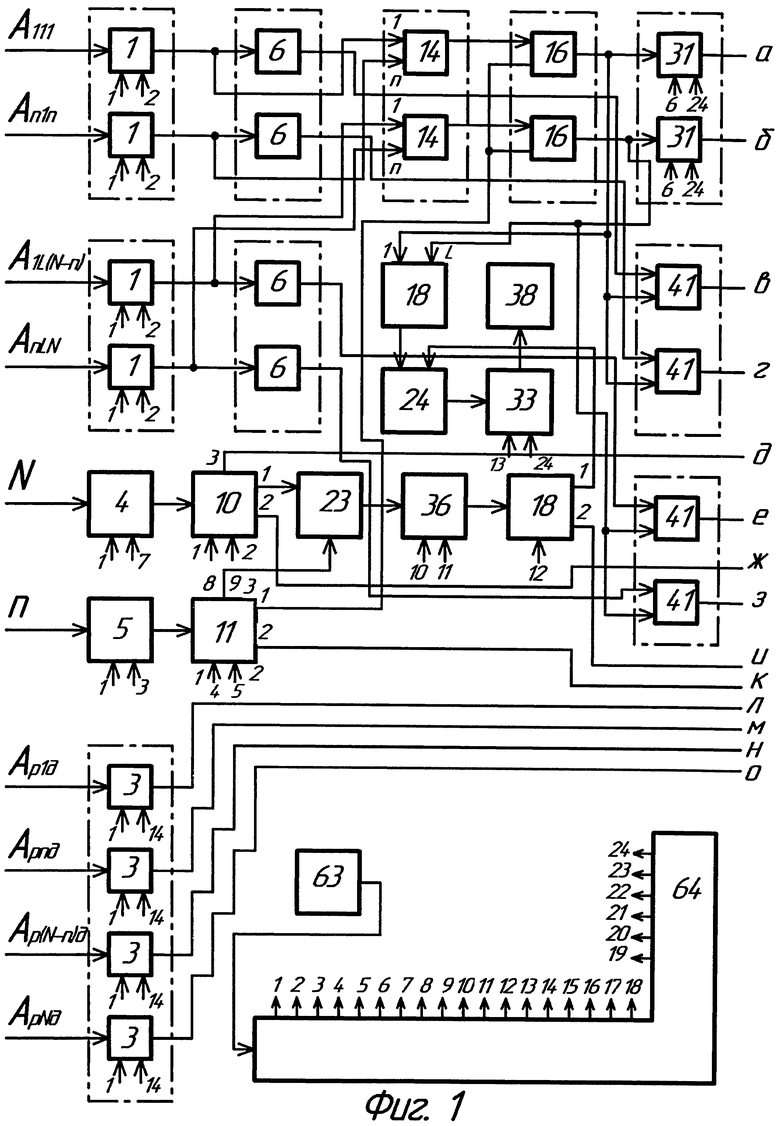

На фиг.1, 2, 3 и 4 представлена функциональная схема устройства автоматической оценки фазовой напряженности респондента (для ликвидации громоздкости связи между РИ и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов); на фиг.5 изображена циклограмма работы заявленного устройства (на оси ординат обозначены номера выходов РИ, а по оси абсцисс - число тактов), причем длительность различных вычислительных операций (сложение и вычитание - один такт, умножение - восемь тактов, деление - двенадцать тактов, извлечение квадратного корня - двадцать тактов) - в верхней части фиг.5 (для возможности исполнения циклограммы принято: N=30, n=10, L=3, f1=10, f0=20, хотя эти величины могут принимать произвольные значения).

Устройство автоматической оценки фазовой напряженности респондента (фиг.1, 2, 3 и 4) содержит первую 1 и вторую 2 группы входных регистров, каждая из которых состоит из L столбцов, включающих каждый из них n элементов, третью группу 3 входных регистров, состоящую из N элементов, первый 4 и второй 5 входные регистры, первую 6 и вторую 7 группы ЭЗ, каждая из которых состоит из L столбцов, включающих каждый из них «элементов, третью 8 и четвертую 9 группы ЭЗ, каждая из которых состоит из N элементов, первый 10, второй 11, третий 12 и четвертый 13 коммутаторы, первую 14 и вторую 15 группы накопительных сумматоров, каждая из которых состоит из L элементов, первую 16 и вторую 17 группы блоков деления, каждая из которых состоит из L элементов, первый 18, второй 19, третий 20, четвертый 21 и пятый 22 накопительные сумматоры, первый 23, второй 24, третий 25, четвертый 26, пятый 27, шестой 28, седьмой 29 и восьмой 30 блоки деления, первую 31 и вторую 32 группы выходных регистров, каждая из которых состоит из L элементов, первый 33, второй 34 и третий 35 выходные регистры, первый 36 и второй 37 регистры, первый 38, второй 39 и третий 40 блоки индикации, первую 41 и вторую 42 группы блоков вычитания по модулю, каждая из которых состоит из L столбцов, включающих каждый из них n элементов, первую 43 и вторую 44 группы блоков индикации, каждая из которых состоит из L элементов, группу 45 блоков сравнения, состоящую из N элементов, первую 46 и вторую 47 группы ключей, каждая из которых состоит из N элементов, первый 48 и второй 49 элементы ИЛИ, первый 50 и второй 51 счетчики, группу 52 квадраторов и группу 53 элементов НЕ, каждая из которых состоит из N элементов, первый 54, второй 55 и третий 56 блоки умножения, первый 57 и второй 58 блоки вычитания, первый 59 и второй 60 блоки извлечения квадратного корня, первый 61 и второй 62 ЭЗ, генератор 63 тактовых импульсов и РИ 64.

Наличие одного входа у первого блока 57 вычитания объясняется тем, что в качестве вычитаемого здесь фигурирует постоянное число, равное единице, которое «зашито» в блоке 57.

Устройство автоматической оценки фазовой напряженности респондента работает следующим образом (фиг.1, 2, 3 и 4). На информационные входы каждого из элементов первой группы 1 входных регистров засылаются значения Aijk ранжированных ответов респондента. На информационные входы каждого из элементов второй группы 2 входных регистров подаются количество сердечных сокращений респондента fijk за время звучания фонограммы вопроса, его обдумывания и высказывания ответа. На информационные входы каждого из элементов третьей группы 3 входных регистров направляются величины Apkд допустимых значений модуля разности Apk. На информационные входы первого 4 и второго 5 входных регистров засылаются соответственно число вопросов N теста и количество вопросов n в каждой из L групп. При этом управляющий сигнал на входы записи групп 1, 2 и 3 и регистров 4 и 5 подается с первого выхода РИ 64, темп работы которого задается генератором 63 тактовых импульсов.

По сигналу со второго выхода РИ 64 на входы считывания каждого из элементов первой группы 1 входных регистров величины Aijk засылаются на входы соответствующих элементов первой группы 6 ЭЗ и первой группы 14 накопительных сумматоров. По сигналам с третьего и седьмого выходов РИ 64 на входы считывания соответственно второго 5 и первого 4 входных регистров значения N и n подаются на информационные входы соответственно первого 10 и второго 11 коммутаторов. По сигналу с четвертого выхода РИ 64 на первый управляющий вход второго коммутатора 11 величина n поступает с его третьего выхода на вход делителя первого блока 23 деления, на вход делимого которого с первого выхода первого коммутатора 10 по сигналам с восьмого и девятого выходов РИ 64 на первый и второй управляющие входы блока 10 направляется значение N. C выхода блока 23 величина L, определяемая по формуле (1), засылается на информационный вход первого регистра 36. Управляющий сигнал на вход записи блока 36 подается с десятого выхода РИ 64.

С выходов элементов первой группы 14 накопительных сумматоров величины  поступают на входы делимого соответствующих элементов первой группы 16 блоков деления, на входы делителя которых с первого выхода второго коммутатора 11 по сигналам с четвертого и пятого выходов РИ 64 на первый и второй управляющие входы блока 11 направляется значение n. Это значение засылается на информационный вход второго коммутатора 11 с выхода второго входного регистра 5 по сигналу на его вход считывания с третьего выхода РИ 64. С выходов элементов группы 16 величины

поступают на входы делимого соответствующих элементов первой группы 16 блоков деления, на входы делителя которых с первого выхода второго коммутатора 11 по сигналам с четвертого и пятого выходов РИ 64 на первый и второй управляющие входы блока 11 направляется значение n. Это значение засылается на информационный вход второго коммутатора 11 с выхода второго входного регистра 5 по сигналу на его вход считывания с третьего выхода РИ 64. С выходов элементов группы 16 величины  , вычисляемые по формуле (2), подаются на информационные входы соответствующих элементов первой группы 31 выходных регистров. Управляющий сигнал на входы записи этих элементов поступает с шестого выхода РИ 64.

, вычисляемые по формуле (2), подаются на информационные входы соответствующих элементов первой группы 31 выходных регистров. Управляющий сигнал на входы записи этих элементов поступает с шестого выхода РИ 64.

Кроме того, значения  направляются на входы уменьшаемого соответствующих элементов первой группы 41 блоков вычитания по модулю (

направляются на входы уменьшаемого соответствующих элементов первой группы 41 блоков вычитания по модулю ( - на элементы первой группы,

- на элементы первой группы,  - на элементы L-й группы) и на соответствующие входы (с первого по L-й) первого накопительного сумматора 18, с выхода которого величина

- на элементы L-й группы) и на соответствующие входы (с первого по L-й) первого накопительного сумматора 18, с выхода которого величина  засылается на вход делимого второго блока 24 деления. На вход делителя этого блока с первого выхода третьего коммутатора 12 по сигналу с двенадцатого выхода РИ 64 подается значение L, которое поступает на информационный вход блока 12 с выхода первого регистра 36 по сигналу с одиннадцатого выхода РИ 64 на вход считывания блока 36. С выхода второго блока 24 деления величина

засылается на вход делимого второго блока 24 деления. На вход делителя этого блока с первого выхода третьего коммутатора 12 по сигналу с двенадцатого выхода РИ 64 подается значение L, которое поступает на информационный вход блока 12 с выхода первого регистра 36 по сигналу с одиннадцатого выхода РИ 64 на вход считывания блока 36. С выхода второго блока 24 деления величина  , определяемая по формуле (3), направляется на информационный вход первого выходного регистра 33, управляющий сигнал на вход записи которого засылается с тринадцатого выхода РИ 64.

, определяемая по формуле (3), направляется на информационный вход первого выходного регистра 33, управляющий сигнал на вход записи которого засылается с тринадцатого выхода РИ 64.

С выходов элементов первой группы 6 ЭЗ, которая обеспечивает одновременность подачи информации на различные входы блоков вычитания, величины Aijk поступают на входы вычитаемого соответствующих элементов первой группы 41 блоков вычитания по модулю, с выходов которой величины Apk, вычисляемые по формуле (4), направляются на информационные входы соответствующих элементов группы 45 блоков сравнения. На пороговые входы этой группы по сигналу с четырнадцатого выхода РИ 64 на входы считывания третьей группы 3 входных регистров с ее выходов засылаются допустимые значения Apkд. Каждый элемент группы 45 блоков сравнения настроен следующим образом: если неравенство (5) соблюдается, то на выходе этого элемента будет единица; в случае несоблюдения этого неравенства - на выходе элемента - нуль. С выходов группы 45 информация поступает на управляющие входы соответствующих элементов первой группы 46 ключей и на входы соответствующих элементов группы 53 элементов НЕ.

По сигналу с пятнадцатого выхода РИ 64 на входы считывания каждого из элементов второй группы 2 входных регистров величины fijk направляются на входы соответствующих элементов второй группы 7 ЭЗ и второй группы 15 накопительных сумматоров. С выходов элементов группы 15 величины  засылаются на входы делимого соответствующих элементов второй группы 17 блоков деления, на входы делителя которых со второго выхода второго коммутатора 11 по сигналу с пятого выхода РИ 64 на второй управляющий вход блока 11 подается значение n. Это значение поступает на информационный вход второго коммутатора 11 с выхода второго входного регистра 5 по сигналу на его вход считывания с третьего выхода РИ 64. С выходов элементов группы 17 величины

засылаются на входы делимого соответствующих элементов второй группы 17 блоков деления, на входы делителя которых со второго выхода второго коммутатора 11 по сигналу с пятого выхода РИ 64 на второй управляющий вход блока 11 подается значение n. Это значение поступает на информационный вход второго коммутатора 11 с выхода второго входного регистра 5 по сигналу на его вход считывания с третьего выхода РИ 64. С выходов элементов группы 17 величины  , вычисляемые по формуле (6), направляются на информационные входы соответствующих элементов второй группы 32 выходных регистров. Управляющий сигнал на входы записи этих элементов засылается с семнадцатого выхода РИ 64.

, вычисляемые по формуле (6), направляются на информационные входы соответствующих элементов второй группы 32 выходных регистров. Управляющий сигнал на входы записи этих элементов засылается с семнадцатого выхода РИ 64.

Кроме того, значения  подаются на входы уменьшаемого соответствующих элементов второй группы 42 блоков вычитания по модулю (

подаются на входы уменьшаемого соответствующих элементов второй группы 42 блоков вычитания по модулю ( - на элементы первой группы,

- на элементы первой группы,  - на элементы L-й группы) и на соответствующие входы (с первого по L-й) второго накопительного сумматора 19, с выхода которого величина

- на элементы L-й группы) и на соответствующие входы (с первого по L-й) второго накопительного сумматора 19, с выхода которого величина  поступает на вход делимого четвертого блока 26 деления. На вход делителя этого блока со второго выхода третьего коммутатора 12 направляется значение L, которое засылается на информационный вход блока 12 с выхода первого регистра 36 по сигналу с одиннадцатого выхода РИ 64 на вход считывания блока 36. Следует подчеркнуть, что сигнал на управляющий вход третьего коммутатора 12 с двенадцатого выхода РИ 64 в данном случае не поступает. С выхода четвертого блока 26 деления величина

поступает на вход делимого четвертого блока 26 деления. На вход делителя этого блока со второго выхода третьего коммутатора 12 направляется значение L, которое засылается на информационный вход блока 12 с выхода первого регистра 36 по сигналу с одиннадцатого выхода РИ 64 на вход считывания блока 36. Следует подчеркнуть, что сигнал на управляющий вход третьего коммутатора 12 с двенадцатого выхода РИ 64 в данном случае не поступает. С выхода четвертого блока 26 деления величина  , определяемая по формуле (7), направляется на информационный вход второго выходного регистра 34, управляющий сигнал на вход записи которого засылается с восемнадцатого выхода РИ 64.

, определяемая по формуле (7), направляется на информационный вход второго выходного регистра 34, управляющий сигнал на вход записи которого засылается с восемнадцатого выхода РИ 64.

С выходов элементов второй группы 7 ЭЗ, которая обеспечивает одновременность подачи информации на различные входы блоков вычитания, величины f1jk поступают на входы вычитаемого соответствующих элементов второй группы 42 блоков вычитания по модулю, с выходов которой величины fpk, вычисляемые по формуле (8), направляются на входы соответствующих элементов группы 52 квадраторов и на информационные входы первой 46 и второй 47 групп ключей. Если на выходе какого-либо элемента группы 45 блоков сравнения будет единица, то значение fpk из соответствующего элемента второй группы 42 блоков вычитания по модулю будет проходить через соответствующий элемент первой группы 46 ключей для дальнейших вычислений. Через вторую группу 47 ключей это значение проходить не будет благодаря наличию группы 53 элементов НЕ, которая приведет к появлению на управляющем входе соответствующего элемента группы 47 нуля. В случае когда на выходе какого-либо элемента группы 45 будет нуль, то значение fpk из соответствующего элемента группы 42 будет проходить через соответствующий элемент второй группы 47 ключей для дальнейших вычислений благодаря наличию группы 53 элементов НЕ. Через первую группу 46 ключей это значение проходить не будет, так как на управляющем входе соответствующего элемента этой группы появится нуль. Таким образом осуществляется разделение величин fpk на две группы: значения fpk1h, которые соответствуют случаю выполнения неравенства (5) и величины fpk0S, несоответствующие выполнению этого неравенства.

С выходов первой 46 и второй 47 группы ключей значения fpk1h и fpk0S подаются на входы соответственно третьей 8 и четвертой 9 групп ЭЗ, а также на входы соответственно третьего 20 и пятого 22 накопительных сумматоров. С выходов групп 8 и 9, которые обеспечивают последовательное поступление величин fpk1h и fpk0S соответственно через первый 48 и второй 49 элементы ИЛИ, эти величины направляются на информационные входы соответственно первого 50 и второго 51 счетчиков. Сигнал на входы запуска этих счетчиков засылается с шестнадцатого выхода РИ 64. С выходов третьего 20 и пятого 22 накопительных сумматоров значения  и

и  подаются на входы делимого соответственно третьего 25 и шестого 28 блоков деления. На входы делителя этих блоков по сигналу с двадцать второго выхода РИ 64 на входы считывания первого 50 и второго 51 счетчиков с их выходов поступает соответственно количество f1 значений fpk1h и f0 значений fpk0S. Следует подчеркнуть, что данные на входы блоков 25 и 28 поступает одновременно, поскольку выход сигналов с блоков 20 и 50, а также 22 и 51 осуществляется через максимальное количество тактов - N.

подаются на входы делимого соответственно третьего 25 и шестого 28 блоков деления. На входы делителя этих блоков по сигналу с двадцать второго выхода РИ 64 на входы считывания первого 50 и второго 51 счетчиков с их выходов поступает соответственно количество f1 значений fpk1h и f0 значений fpk0S. Следует подчеркнуть, что данные на входы блоков 25 и 28 поступает одновременно, поскольку выход сигналов с блоков 20 и 50, а также 22 и 51 осуществляется через максимальное количество тактов - N.

С выходов блоков 25 и 28 значения m1 и m0, вычисленные по формулам (9) и (10), направляются на входы соответственно уменьшаемого и вычитаемого второго блока 58 вычитания, с выхода которого величина (m1-m0) засылается на вход второго ЭЗ 62. Значения f1 и f0 подаются также на второй и первый входы второго блока 55 блока умножения, с выхода которого величина f1·f0 поступает на вход делимого пятого блока 27 деления.

По сигналу с седьмого выхода РИ 64 на вход считывания первого входного регистра 4 величина N направляется на информационный вход первого коммутатора 10, с третьего выхода которого по сигналу с восьмого выхода РИ 64 на его первый управляющий вход эта величина засылается на вход уменьшаемого первого блока 57 вычитания. С выхода блока 57 значение N-1 подается на информационный вход второго регистра 37, на вход записи которого поступает сигнал с девятнадцатого выхода РИ 64. По сигналу с двадцатого выхода РИ 64 на вход считывания блока 37 величина N-1 с его выхода направляется на информационный вход четвертого коммутатора 13, со второго выхода которого эта величина по сигналу на его управляющий вход с двадцать первого выхода РИ 64 засылается на второй вход первого блока 54 умножения. На первый вход этого блока со второго выхода первого коммутатора 10 по сигналу на его второй управляющий вход с девятого выхода РИ 64 подается величина N, которая поступает на информационный вход блока 10 с выхода первого входного регистра 4 по сигналу на его вход считывания с седьмого выхода РИ 64.

С выхода первого блока 54 умножения значение N(N-1) направляется на вход делителя пятого блока 27 деления, с выхода которого величина  засылается на вход второго блока 60 извлечения квадратного корня

засылается на вход второго блока 60 извлечения квадратного корня  подается на вход первого ЭЗ 61. С выходов группы 52 квадраторов величины

подается на вход первого ЭЗ 61. С выходов группы 52 квадраторов величины  поступают на соответствующие входы четвертого накопительного сумматора 21, с выхода которого значение

поступают на соответствующие входы четвертого накопительного сумматора 21, с выхода которого значение  направляется на вход делимого седьмого блока 29 деления. На вход делителя этого блока с первого выхода четвертого коммутатора 13 засылается величина N-1. При этом сигнал на управляющий вход блока 13 не подается. Значение N-1 подается на информационный вход этого блока с выхода второго регистра 37 по сигналу на его вход считывания с двадцатого выхода РИ 64.

направляется на вход делимого седьмого блока 29 деления. На вход делителя этого блока с первого выхода четвертого коммутатора 13 засылается величина N-1. При этом сигнал на управляющий вход блока 13 не подается. Значение N-1 подается на информационный вход этого блока с выхода второго регистра 37 по сигналу на его вход считывания с двадцатого выхода РИ 64.

С выхода седьмого блока 29 деления величина  поступает на вход первого блока 59 извлечения квадратного корня, с выхода которого значение стандартного отклонения σ, определяемое по формуле (12), направляется на вход делителя восьмого блока 30 деления. На вход делимого этого блока засылается с выхода второго ЭЗ 62 значение (m1-m0). На первый вход третьего блока 56 умножения с выхода восьмого блока 30 деления подается величина

поступает на вход первого блока 59 извлечения квадратного корня, с выхода которого значение стандартного отклонения σ, определяемое по формуле (12), направляется на вход делителя восьмого блока 30 деления. На вход делимого этого блока засылается с выхода второго ЭЗ 62 значение (m1-m0). На первый вход третьего блока 56 умножения с выхода восьмого блока 30 деления подается величина  , на второй вход блока 56 с выхода первого ЭЗ 61 поступает значение

, на второй вход блока 56 с выхода первого ЭЗ 61 поступает значение  , а с выхода третьего блока 56 умножения на информационный вход третьего выходного регистра 35 направляется величина коэффициента корреляции rpb, вычисляемая по формуле (11). Управляющий сигнал на вход записи этого регистра засылается с двадцать третьего выхода РИ 64.

, а с выхода третьего блока 56 умножения на информационный вход третьего выходного регистра 35 направляется величина коэффициента корреляции rpb, вычисляемая по формуле (11). Управляющий сигнал на вход записи этого регистра засылается с двадцать третьего выхода РИ 64.

Для наглядного отображения результатов работы устройства по сигналу с двадцать четвертого выхода РИ 64 на входы считывания первой 31 и второй 32 групп выходных регистров, первого 33, второго 34 и третьего 35 выходных регистров с их выходов значения  ,

,  ,

,  ,

,  и rpb подаются на входы соответственно первой 43 и второй 44 групп блоков индикации, первого 38, второго 39 и третьего 40 блоков индикации. Порядок функционирования блоков устройства представлен на циклограмме его работы (фиг.5).

и rpb подаются на входы соответственно первой 43 и второй 44 групп блоков индикации, первого 38, второго 39 и третьего 40 блоков индикации. Порядок функционирования блоков устройства представлен на циклограмме его работы (фиг.5).

Таким образом, технический результат достигается не за счет математического аппарата, а за счет технических средств (блоков и элементов), упомянутых в процессе описания работы устройства, осуществляющего повышение объективности, достоверности и быстродействия проводимого тестирования за счет определения наличия и величины отклонения ЧСС респондента на каждый из вопросов теста.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в разных областях (отраслях) при расчетах, связанных с анализом взаимосвязи субъективных ответов респондента с его частотой сердечных сокращений в процессе производимого тестирования, которая характеризует его фазовую напряженность психологического состояния.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФУНКЦИЙ ЦЕННОСТИ ЕДИНИЧНЫХ ОЦЕНОЧНЫХ ПОКАЗАТЕЛЕЙ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2010 |

|

RU2445687C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| УСТРОЙСТВО ДЛЯ ТЕХНИКО-ЭКОНОМИЧЕСКОЙ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2011 |

|

RU2470365C1 |

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРЕДПОЧТИТЕЛЬНОГО УРОВНЯ УНИФИКАЦИИ ТЕХНИЧЕСКИХ СИСТЕМ | 2010 |

|

RU2427900C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2009 |

|

RU2410750C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ И СРАВНЕНИЯ ЭФФЕКТИВНОСТИ ФУНКЦИОНИРОВАНИЯ ОДНОТИПНЫХ ОРГАНИЗАЦИЙ | 2008 |

|

RU2363042C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ВАРИАНТА ИСПЫТАНИЙ ТЕХНИЧЕСКИХ УСТРОЙСТВ | 2010 |

|

RU2417392C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ВАРИАНТА ИСПЫТАНИЙ ТЕХНИЧЕСКИХ УСТРОЙСТВ | 2009 |

|

RU2380745C1 |

Изобретение относится к вычислительной технике и может быть использовано для анализа взаимосвязи субъективных ответов респондента с его частотой сердечных сокращений (ЧСС) в процессе производимого тестирования, которая характеризует его психологическое состояние. Техническим результатом является повышение объективности, достоверности и быстродействия проводимого тестирования. Устройство содержит группы входных регистров, входные регистры, группы элементов задержки, коммутаторы, группы накопительных сумматоров, накопительные сумматоры, группы блоков деления, блоки деления, группы выходных регистров, выходные регистры, регистры, блоки индикации, группы блоков вычитания по модулю, группы блоков индикации, группу блоков сравнения, группы ключей, элементы ИЛИ, счетчики, группу квадраторов, группу элементов НЕ, блоки умножения, блоки вычитания, блоки извлечения квадратного корня, элементы задержки, генератор тактовых импульсов и распределитель импульсов. 5 ил., 4 табл.

Устройство автоматической оценки фазовой напряженности респондента, содержащее первую и вторую группу входных регистров, каждая из которых состоит их L столбцов, включающих по n элементов каждый, третью группу входных регистров, состоящую из N элементов, первый и второй входные регистры, первую и вторую группу элементов задержки (ЭЗ), каждая из которых состоит из L столбцов, включающих каждый из них n элементов, третью и четвертую группы ЭЗ, каждая из которых состоит из N элементов, с первого по четвертый коммутаторы, первую и вторую группы накопительных сумматоров, каждая из которых состоит из L элементов, первую и вторую группы блоков деления, каждая из которых состоит из L элементов, с первого по пятый накопительные сумматоры, с первого по восьмой блоки деления, первую и вторую группы выходных регистров, каждая из которых состоит их L элементов, первый, второй и третий выходные регистры, первый и второй регистры, первый, второй и третий блоки индикации, первую и вторую группы блоков вычитания по модулю, каждая из которых состоит из L столбцов, включающих каждый из них n элементов, первую и вторую группу блоков индикации, каждая из которых состоит из L элементов, группу блоков сравнения, состоящую из N элементов, первую и вторую группы ключей, каждая из которых состоит из N элементов, первый и второй элементы ИЛИ, первый и второй счетчики, группу квадраторов и группу элементов НЕ, каждая из которых состоит из N элементов, первый, второй и третий блоки умножения, первый и второй блоки вычитания, первый и второй блоки извлечения квадратного корня, первый и второй ЭЗ, генератор тактовых импульсов и распределитель импульсов (РИ), тактовый вход которого соединен с выходом генератора тактовых импульсов, первый выход РИ, со входами записи первой, второй и третьей групп входных регистров, первого и второго входных регистров, второй выход - со входами считывания первой группы входных регистров, третий выход - со входом считывания второго входного регистра, четвертый и пятый выходы - соответственно с первыми вторым управляющими входами второго коммутатора, шестой выход - со входами записи первой группы выходных регистров, седьмой выход - со входом считывания первого входного регистра, восьмой и девятый выходы - соответственно с первым и вторым управляющими входами первого коммутатора, десятый и одиннадцатый выходы - соответственно с входами записи и считывания первого регистра, двенадцатый выход - с управляющим входом третьего коммутатора, тринадцатый выход - со входом записи первого выходного регистра, четырнадцатый и пятнадцатый выходы - со входами считывания соответственно третьей и второй групп входных регистров, шестнадцатый выход - со входами запуска первого и второго счетчиков, семнадцатый, восемнадцатый и девятнадцатый выходы - со входами записи соответственно второй группы выходных регистров, второго выходного регистра и второго регистра, двадцатый выход - со входом считывания второго регистра, двадцать первый выход - с управляющим входом четвертого коммутатора, двадцать второй выход - со входами считывания первого и второго счетчиков, двадцать третий выход - со входом записи третьего выходного регистра, двадцать четвертый выход - со входами считывания первой и второй группы выходных регистров, первого, второго и третьего выходных регистров, информационные входы первой группы входных регистров являются входами задания исходной информации, на которые поступают значения Aijk, характеризующие ранжированные ответы респондента, информационные входы второй группы входных регистров являются входами задания исходной информации, на которые поступают значения fijk, характеризующие количество сердечных сокращений респондента за время звучания фонограммы вопроса, его обдумывания и ответа, информационные входы третьей группы входных регистров являются входами задания исходной информации, на которые поступают значения Apkд, характеризующие допустимые величины модуля разности между средним значением рангов по группам исследуемых признаков и величинами Aijk, информационные входы первого и второго входных регистров являются входами задания исходной информации, на которые поступают соответственно значение N, характеризующее общее число вопросов теста, и величина n, характеризующая количество вопросов в каждой группе, выходы первой и второй групп входных регистров соединены с входами соответственно первой и второй ЭЗ, выходы с первого по n-й элементов каждого из L столбцов первой и второй групп входных регистров соединены с первым по n-й входами каждого из L элементов соответственно первой и второй групп накопительных сумматоров, выходы которых подключены к входам делимого соответствующих элементов соответственно первой и второй групп блоков деления, входы делителя которых соединены соответственно с первым и вторым выходами второго коммутатора, а выходы - с информационными входами соответственно первой и второй групп выходных регистров, выходы которых подключены к входам соответственно первой и второй групп блоков индикации, выходы каждого из L элементов первой и второй групп блоков деления соединены с первым по L-й входами соответственно первого и второго накопительных сумматоров, выходы которых подключены к входам делимого соответственно второго и четвертого блоков деления, входы делителя которых соединены соответственно с первым и вторым выходами третьего коммутатора, а выходы - с информационными входами соответственно первого и второго выходных регистров, выходы которых подключены к входам соответственно первого и второго блоков индикации, каждый из L элементов первой и второй групп блоков деления соединены с входами уменьшаемого соответствующего столбца, с первого по L-й, соответственно первой и второй групп блоков вычитания по модулю, входы вычитаемого которых подключены к выходам соответственно первой и второй групп ЭЗ, выходы первой группы блоков вычитания по модулю соединены с информационными входами группы блоков сравнения, пороговые входы которых подключены к выходам соответствующих элементов третьей группы входных регистров, а выходы - к входам группы элементов НЕ и к управляющим входам первой группы ключей, информационные входы с первой и второй групп ключей соединены с выходами второй группы блоков вычитания по модулю, а выходы - с входами соответственно третьей и четвертой групп ЭЗ и с первого по N-й входами соответственно третьего и пятого накопительных сумматоров, выходы которых подключены к входам делимого соответственно третьего и шестого блоков деления, входы делителя которых соединены с выходами соответственно первого и второго счетчиков, информационные входы которых подключены к выходам соответственно первого и второго элементов ИЛИ, с первого по N-й входы которых соединены с первого по N-й элементов соответственно третьей и четвертой групп ЭЗ, управляющие входы второй группы ключей подключены к выходам группы элементов НЕ, выходы второй группы блоков вычитания по модулю соединены с входами группы квадраторов, выходы с первого по N-й элементов которой подключены к входам, с первого по N-й четвертого накопительного сумматора, выход которого соединен с входом делимого седьмого блока деления, вход делителя которого подключен к первому выходу четвертого коммутатора, а выход - к входу первого блока извлечения квадратного корня, выход которого соединен с входом делителя восьмого блока деления, вход делимого которого подключен к выходу второго ЭЗ, а выход - к первому входу третьего блока умножения, второй вход которого соединен с выходом первого ЭЗ, а выход - с информационным входом третьего выходного регистра, выход которого подключен к входу третьего блока индикации, вход второго ЭЗ соединен с выходом второго блока вычитания, вход первого ЭЗ подключен к выходу второго блока извлечения квадратного корня, вход которого подключен к выходу пятого блока деления, вход делителя которого соединен с выходом первого блока умножения, а вход делимого - с выходом второго блока умножения, первый и второй входы которого подключены к выходам соответственно второго и первого счетчиков, выходы первого и второго входных регистров соединены с информационными входами соответственно первого и второго коммутаторов, третий выход которого подключен к входу делителя первого блока деления, вход делимого которого соединен с первым выходом первого коммутатора, а выход - с информационным входом первого регистра, выход которого подключен к информационному входу третьего коммутатора, второй и третий выходы которого соединены соответственно с первым входом первого блока умножения и с входом уменьшаемого первого блока вычитания, выход которого подключен к информационному входу второго регистра, выход которого соединен с информационным входом четвертого коммутатора, второй выход которого подключен ко второму входу первого блока умножения, входы уменьшаемого и вычитаемого второго блока вычитания соединены с выходами соответственно третьего и шестого блоков деления.

| УСТРОЙСТВО ДЛЯ КОЛИЧЕСТВЕННОЙ ОЦЕНКИ КАЧЕСТВЕННОГО ПОКАЗАТЕЛЯ | 2011 |

|

RU2448364C1 |

| СПОСОБ ОЦЕНКИ ЭМОЦИОНАЛЬНОЙ И СТРЕССОВОЙ НАПРЯЖЕННОСТИ | 1995 |

|

RU2068653C1 |

| RU 2073484 C1, 20.02.1997 | |||

| US 2004148210 A1, 29.07.2004 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| US 5327899 A, 12.07.1994. | |||

Авторы

Даты

2013-09-10—Публикация

2012-05-30—Подача